# Strong Priority and Determinacy in Timed CCS

Luigi Liquori, Michael Mendler

# ▶ To cite this version:

Luigi Liquori, Michael Mendler. Strong Priority and Determinacy in Timed CCS. Inria; University of Bamberg. 2023. hal-04367635v2

# HAL Id: hal-04367635 https://inria.hal.science/hal-04367635v2

Submitted on 29 Apr 2024

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Strong Priority and Determinacy in Timed CCS

- 2 Luigi Liquori

- 3 Inria, France

- 4 Michael Mendler

- 5 University of Bamberg, Germany

#### **Abstract**

- Building on the standard theory of process algebra with priorities, we identify a new scheduling mechanism, called *constructive reduction* which is designed to capture the essence of synchronous programming. The distinctive property of this evaluation strategy is to achieve determinacy-by-construction for multi-cast concurrent communication with shared memory. In the technical setting of CCS extended by clocks and priorities, we prove for a large class of *coherent* processes a confluence property for constructive reductions. We show that under some restrictions, called *pivotability*, coherence is preserved by the operators of prefix, summation, parallel composition, restriction and hiding. Since this permits memory and sharing, we are able to cover a strictly larger class of processes compared to those in Milner's classical confluence theory for CCS without priorities.

- 2012 ACM Subject Classification Theory of computation, Process algebras

- 17 Keywords and phrases Timed process algebras, determinacy, priorities, synchronous programming

- 18 Digital Object Identifier 10.4230/LIPIcs...

- <sup>19</sup> Funding Luigi Liquori: Partially funded by ETSI.

- 20 Michael Mendler: Partially funded by UniCA/I3S.

# 1 Introduction

Concurrency, by expression or by implementation, is both a convenient and unavoidable feature of modern software systems. However, this does not mean that we must necessarily give up the requirement of functional determinism which is crucial for maintaining predictability and to manage design complexity by simple mathematical models [23, 8, 13]. While the pure  $\lambda$ -calculus is naturally deterministic by design, it cannot model shared memory. Process algebras can naturally model shared objects, but do not guarantee determinism out of the box. In this paper we use the standard mathematical formalism CCS [27] to study methods for reconciling concurrency and determinism.

#### Determinacy in Process Algebra

In CCS, the interaction of concurrent processes  $P \mid Q$  arises from the rendezvous synchronisation of an  $action \ \alpha$  of P and an associated  $co\text{-}action \ \overline{\alpha}$  from Q, generating a silent action  $\tau$ , also called a reduction. A process is in normal form if cannot reduce any more and determinate if it reduces to at most one normal form, up to some notion of structural congruence. As a simplified example for the scenarios that we are interested in, consider a triple of concurrent processes  $R \mid S \mid W$ , where  $S \stackrel{def}{=} r.S + w.\overline{r}.0$  acts as a shared resource, such as a (write-once) store, while  $R \stackrel{def}{=} \overline{r}.0$ ,  $W \stackrel{def}{=} \overline{w}.0$  are read and write processes, respectively, sharing S with each other. The store S offer a read action r (rendezvous) leaving the state unchanged, or a write action w upon which it changes its state to  $\overline{r}.0$ . At this point, the store only permits a single read and then becomes the inactive process 0. The synchronisation between the actions r, w and co-actions  $\overline{r}$ ,  $\overline{w}$  generates two sequences of reductions from  $R \mid S \mid W$ :

$0 \,|\, \overline{r}.0 \,|\, 0 \xleftarrow{\tau} 0 \,|\, S \,|\, W \xleftarrow{\tau} R \,|\, S \,|\, W \xrightarrow{\tau} R \,|\, \overline{r}.0 \,|\, 0 \xrightarrow{\tau} 0 \,|\, 0 \,|\, 0.$

Obviously,  $R \mid S \mid W$  is not determinate. It reduces to two distinct normal forms  $0 \mid \overline{r}.0 \mid 0$  and  $0 \mid 0 \mid 0$ . The final store  $\overline{r}.0$  on the left permits one more read, while 0 on the right does not. A sufficient condition for determinacy is determinism. A process P is (structurally) deterministic if for all its derivatives Q and action  $\alpha \in Act$ , if  $Q \xrightarrow{\alpha} Q_1$  and  $Q \xrightarrow{\alpha} Q_2$  then  $Q_1 \equiv Q_2$ , where  $\equiv$  is a suitable structural congruence. However, determinism is too strong. For instance, the store  $P \stackrel{\text{def}}{=} R_1 \mid S \mid R_2$  with two readers  $R_i \stackrel{\text{def}}{=} \overline{r}.R_i'$  (i=1,2) is determinate but not deterministic, when the  $R_i$  may reach structurally distinct states after reading, say,  $P \xrightarrow{\tau} R_1' \mid S \mid R_2$  and  $P \xrightarrow{\tau} R_1 \mid S \mid R_2'$  where  $R_1' \mid S \mid R_2 \not\equiv R_1 \mid S \mid R_2'$ . Moreover, determinism is not closed under parallel composition. In the above example, all process  $R_1$ ,  $R_2$ , S are deterministic, but their composition P is not. An insightful solution, proposed by Milner (Chap. 11 of [27]), is to replace determinism by the notion of confluence which still implies determinacy but turns out to be closed under parallel composition, under natural restrictions.

▶ **Definition 1.** P is (structurally) confluent<sup>1</sup> if for every derivative Q of P and reductions  $Q \xrightarrow{\alpha_1} Q_1$  and  $Q \xrightarrow{\alpha_2} Q_2$  with  $\alpha_1 \neq \alpha_2$  or  $Q_1 \not\equiv Q_2$ , there exist  $Q_1' \equiv Q_2'$  such that  $Q_1 \xrightarrow{\alpha_2} Q_1'$  and  $Q_2 \xrightarrow{\alpha_1} Q_2'$ .

Milner shows that confluence is preserved by "confluent composition"  $P|_L Q \stackrel{\text{def}}{=} (P|Q) \setminus L$ , combining the parallel and restriction operators, subject to the condition that  $\mathcal{L}(P) \cap \mathcal{L}(Q) = \{\}$  and  $\overline{\mathcal{L}(P)} \cap \mathcal{L}(Q) = L \cup \overline{L}$ , where  $\mathcal{L}(R)$  is the sort of a process R. This is a form of sort separation, ensuring that every action  $\alpha$  has at most one synchronisation partner  $\overline{\alpha}$  either inside or outside of  $(P|Q) \setminus L$ . Many practical examples of determinate systems can be understood as sort-separated compositions of confluent processes. However, this still covers only a rather limited class of applications. Most seriously, memory processes such as S above are intrinsically not confluent, and even if they were, confluent composition forbids direct multi-cast communication, because labels such as S in S could not be shared by two readers S and S due to sort-separation. This means that concurrent programming languages that support shared memory and yet have determinate reduction semantics, cannot be handled.

#### **Determinacy in Synchronous Programming**

71

81

The most prominent class of shared-memory programming languages that manage to reconcile concurrency and determinacy, is known as *Synchronous Programming* (SP). In SP, processes interact with each other asynchronously at a *micro-step* level, yet synchronise in lock-step to advance jointly in iterative cycles of synchronous *macro-steps*. The micro-step interactions taking place during a macro-step determine the final outcome of the macro-step. This outcome is defined at the point where all subsystem pause to wait for a global logical *clock*. When this clock arrives, all subsystem proceed into the next computation cycle. Under the so-called *synchrony hypothesis*, the final outcome of a macro-step for each subsystem is fully determined from the stimulus provided by the environment of that component during the micro-step interactions. As such, the interactions inside each subsystem at macro-step level can be abstracted into a global Mealy automaton with deterministic I/O. SP started with Statecharts [17] and has generated languages such as Signal [14], Lustre [16], Esterel [5], Quartz [37], SCCharts [41], just to mention a few.

When it comes to mathematical modelling it is natural to think of a clock as a broadcast action in the spirit of Hoare's CSP [19] that acts as a synchronisation barrier for a set of concurrent processes. Used with some scheduling control, it can bundle each process' actions

<sup>&</sup>lt;sup>1</sup> A variation of Milner's "strong confluence" that includes  $\tau$ -actions and uses  $\equiv$  not bisimulation  $\sim$ .

into a sequence of macro-steps that are aligned with each other in a lock-step fashion. During

each macro-step, a process executes only a temporal slice of its total behaviour, at the end of

which it waits for all other processes in the same *clock scope* to reach the end of the current

phase. When all processes have reached the barrier, they are released into the next round

of computation. This suggests a priority-based scheduling mechanism, i.e., that the clock

should fire only if the system has stabilised and no other admissible data actions are possible.

This principle, called *maximal progress*, is built into timed process algebras, see e.g. [18, 11].

### Contribution

We introduce an extension of CCS, denoted CCS<sup>spt</sup>, that brings together the concepts of priorities [10, 36, 33] and clocks [15, 11, 32] that have previously been studied for CCS, but independently. We thus obtain an adequate compositional setting for SP based on standard techniques from process algebra. This is surprising since many different customised semantics (e.g., [24, 9, 5, 1]) have been developed for SP over the years, few of which fit into the classical framework of CCS. Similar ideas might be possible for other process algebras like ATP [31], TPL [18], CSP or some synchronous variants of Milner's  $\pi$ -calculus [2], just to mention a few. We find CCS most plausible as a point of departure since the concept of priorities is already well established and the combination of asynchronous scheduling and communication via local rendezvous synchronisation makes the problem of ensuring determinacy more prominent.

Our calculus  $CCS^{spt}$  provides a natural setting to take a fresh look at confluence in CCS as an adequate mathematical model for SP. Moreover, we envisage that  $CCS^{spt}$ , extended by value-passing, can be used as a playground to study compositional embeddings of concurrent  $\lambda$ -calculi. In particular, we have in mind those with sharing, as required for the lazy semantics of Haskell and with deterministic memory such as IVars/TVars [25] and LVars [22]. At the technical level, we make the following specific contributions in this paper:

- We use broadcast actions (clocks) as global synchronisation barriers to schedule processes using priorities in a more flexible way than any of the earlier approaches. While PMC [15] has clocks but no priorities and in CSA [11] the priorities are hardwired and expressing precedence only between the rendezvous actions and the clock, we use a fully general priority scheme as in Phillips' CCS<sup>Ph</sup> [33]. By adding clocks to CCS<sup>Ph</sup> we generalise previous CCS extensions such as Milner's SCCS [26], PMC or CSA for expressing synchronous interactions of concurrent processes. To achieve this, we must strengthen Phillips' notion of weak enabling (Def. 2) by constructive enabling (Def. 3). While all classical extensions of CCS by priorities [10, 36, 33] schedule the processes by their immediate initial actions, constructive enabling takes into account all actions potentially executable up to the next clock barrier.

- We identify a strictly larger class of processes that enjoy the Church Rosser (CR) Property (and thus reduce to unique normal forms) than the "confluence class" discussed by Milner, see e.g., Chap. 11 of [27]. Since priorities are not part of the classical confluence theory, it cannot model deterministic shared objects with conflicting choice. In this paper, exploiting priorities and clocks, we enrich Milner's notion of confluence to "confluence up-to priorities" that we call *coherence* (Def. 12). We show that coherent processes are CR for constructive enabling (Thm. 14).

- We show that coherence is preserved by parallel composition under reasonable restrictions that permit sharing and memory (Thm. 24). Specifically, we construct coherent processes in a type-directed compositional fashion using the notion of *precedence policies* (Def. 16). The policy for a conformant process specifies an upper bound for its precedence-blocking behaviour (Def. 17). A policy enriches the classical sort of a process by priority information. We define the special class of *pivot policies* and call coherent processes conforming to them

### XX:4 Strong Priority and Determinacy in Timed CCS

pivotable processes (Def. 48). These are not only coherent (and thus CR) but preserved by parallel composition and other operators of the language (Thm. 24). In this fashion, we are able to extend Milner's classical results for confluent processes to cover significantly more applications, specifically Esterel-style multi-cast SP with shared objects.

• We show that each coherent process is *clock-deterministic* (Prop. 15) and that pivotable processes satisfy *maximal progress* (Prop. 23). No matter in which order we execute constructively enabled reductions, when the normal form is reached, and only then, a clock can tick. Since the normal form is uniquely determined, each pivotable process represents a "synchronous stream". As such, our work extends the classical non-deterministic theory of timed (multi-clocked) process algebras [15, 18, 11] for applications in deterministic synchronous programming.

For lack of space, four separate appendices will present (A) how research towards determinacy for process algebras passes through those above cited papers, (B) a collection of more tricky examples, and (C,D) the full proofs.

# 2 A Process Algebra with Clocks and Priorities

The syntax and operational semantics of our process algebra 'SynPaTick', denoted CCS<sup>spt</sup>, is defined in this section.

# 2.1 CCS<sup>spt</sup> Syntax

The terms in CCS<sup>spt</sup> form a set  $\mathcal{P}$  of processes. We use  $P,Q,R,S\ldots$  to range over  $\mathcal{P}$ . Let  $\mathcal{I}$  be a set of process names and let  $A,B\ldots$  range over  $\mathcal{I}$ . Let  $\mathcal{A}$  be a countably infinite set of channel names with  $a,b\ldots$  ranging over  $\mathcal{A}$ . As in CCS, the set  $\overline{\mathcal{A}}$  is a disjoint set of co-names with elements denoted by  $\overline{a},\overline{b},\overline{c}\ldots$  in bijection with  $\mathcal{A}$ ; The overbar operator switches between  $\mathcal{A}$  and  $\overline{\mathcal{A}}$ , i.e.,  $\overline{a}=a$  for all  $\overline{a}\in\overline{\mathcal{A}}$ . We will refer to the names  $a\in\mathcal{A}$  as input (or receiver) labels while the co-names  $\overline{a}\in\overline{\mathcal{A}}$  denote output (or sender) labels. Let  $\mathcal{C}$  be a countably infinite set of broadcasted clock names, disjoint from both  $\mathcal{A}$  and  $\overline{\mathcal{A}}$  and let  $\sigma$  range over  $\mathcal{C}$ . Every clock acts as its own co-name,  $\overline{\sigma}=\sigma$  and so each  $\sigma\in\mathcal{C}$  is also considered as a clock label. Let  $\mathcal{L}=\mathcal{A}\cup\overline{\mathcal{A}}\cup\mathcal{C}$  be the set of input, output and clock labels and let  $\ell$  range over  $\ell$ , while  $\ell$ ,  $\ell$  range over subsets of  $\ell$ . We write  $\ell$  for the set  $\ell$  and let  $\ell$  range over  $\ell$  be the set of all actions obtained by adjoining the silent action  $\ell$  and let  $\ell$  range over  $\ell$ . Viewed as actions, the input and output labels  $\ell$  and  $\ell$  are referred to as rendezvous actions to distinguish them from the clock actions  $\ell$  act. All symbols can appear indexed. The process terms  $\ell$  are defined thus:

Intuitively, 0 denotes the *inactive* process which stops all computations, including clock actions. The action prefix  $\alpha$ :H.P denotes a process that offers to engage in the action  $\alpha$  and then behaves as P while the blocking set  $H \subseteq \mathcal{L}$  lists all actions taking precedence over  $\alpha$ . A prefix with  $\alpha \in \mathcal{R}$  denotes a CCS-style rendezvous action. In case  $\alpha \in \mathcal{C}$ , it denotes a CSP-style broadcast action that can communicate with all the surrounding processes sharing on the same clock only when the clock is universally consumed. We assume that in every restriction  $P \setminus L$  the set  $L \subseteq \mathcal{R}$  consists of rendezvous actions, and in every hiding  $P \setminus L$  we have  $L \subseteq \mathcal{C}$ . These scoping operators act as name binders that introduce local scopes.

```

\begin{array}{llll} (\mathsf{Comm}) & P \star Q & \equiv & Q \star P & (\mathsf{Idem}_+) & P + P & \equiv & P \\ (\mathsf{Assoc}) & (P \star Q) \star R & \equiv & P \star (Q \star R) & (\mathsf{Scope}_{\wr}) & P \wr L \wr L' & \equiv & P \wr (L \cup L') \\ (\mathsf{Zero}) & P \star 0 & \equiv & P & (\mathsf{Scope}_{0}) & 0 \wr L & \equiv & 0 \\ (\mathsf{Scope}_{\alpha}) & (\alpha : H . P) \backslash L & \equiv & \begin{cases} 0 & \text{if } \alpha \in L \cup \overline{L} \\ \alpha : H . (P \backslash L) & \text{otherwise} \end{cases} \\ (\mathsf{Scope}_{\backslash}) & (P \star Q) \backslash L & \equiv & \begin{cases} P \star Q \backslash L & \text{if } \mathcal{L}(P) \cap (L \cup \overline{L}) = \{\} \\ P \backslash L + Q \backslash L & \text{if } \star = + \\ P \backslash L \mid Q \backslash L & \text{if } \star = \mid \text{ and } \mathcal{L}(P) \cap \overline{\mathcal{L}(Q)} \cap (L \cup \overline{L}) = \{\} \end{cases} \end{array}

```

**Figure 1** Structural Congruence, where  $\star \in \{|, +\}$  and  $\iota \in \{\setminus, /\}$ .

176

177

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

210

The acute reader will notice the absence of the relabelling operator P[f], useful in CCS to define the well-known "standard concurrent form"  $(P_1[f_1] | \cdots | P_2[f_n]) \setminus L$ . Because all of our examples are captured without need of relabelling, and for the sake of simplicity, relabelling will be treated in the full version of this work. A useful abbreviation is to drop the blocking sets if they are empty or drop the continuation process if it is inactive. For instance, we will typically write a.P instead of  $a:\{\}.P$  and a:H rather than a:H.0. Also, it is useful to drop the braces for the blocking set if it is a singleton, writing a:b.P instead of In our concrete notation using the abstract syntax of processes, we assume that the binary operator + is right associative and taking higher binding strength than the binary operator |, i.e., writing P+Q+R|S instead of (P+(Q+R))|S. Also, we assume that the unary operators of prefix, restriction and hiding have higher binding strength than the binary operators. Hence, we write  $P \setminus c + a.b.c.Q \mid R / \sigma$  instead of  $((P \setminus c) + (a.(b.(c.Q)))) \mid (R / \sigma)$ . The sub-processes of a P are all sub-expressions of P and (recursively) all sub-processes of Qfor definitions  $A \stackrel{\text{def}}{=} Q$  where A is a sub-expression of P. Sometimes it is useful to consider fragments of  $\mathcal{P}$ . Specifically, a process is called *unclocked* if P does not contain any clock prefix  $\sigma:H.Q$  as a sub-process. A process is called sequential or single-threaded if it does not contain any parallel sub-process  $Q \mid R$ . P is closed if all sub-processes  $\ell$ :H.Q in P occur in the scope of a restriction or hiding operator that binds  $\ell$ . As usual, we denote by  $\mathcal{L}(P) \subseteq \mathcal{L}$ the free labels, called (syntactic) sort of P, identify processes that differ only in the choice of bound labels.

Following Milner's presentation of the  $\pi$ -calculus in [28], we define a structural congruence over processes. Specifically, structural congruence  $\equiv$  is the smallest congruence over  $\mathcal{P}$  that satisfies the equations in Fig. 1. The idea of the structural congruence is to split interaction rules between agents from rules governing the "left-to-right" representation of expressions. It allows to use those equations in the derivation rules of the SOS making the latter simpler and easy to use, and it allows to set up formal equivalence of processes increasing for each program the number of legal SOS transitions that, otherwise, would be blocked. Milner divides CCS equations in static, dynamic and expressions laws. We choose an approach inspired by the work of Berry and Boudol [7] by adding an explicit structural rule in the operational semantics. Note that we do not include in our structural rules all of Milner's  $\tau$ -laws, i.e. the ones related to the presence of  $\tau$ -actions, like e.g.  $\alpha.\tau.P \equiv \alpha.P$ , or  $P + \tau.P \equiv \tau.P$ , and we have also dropped the congruence equations related to the uniqueness of solution of recursive equations and the expansion laws related to the standard concurrent form (cf. Chap. 3, Props. 2, 4(2) and 5 of [27]). Since we do not propose notions of behavioural equivalence in this paper, we prefer to take a conservative approach and only consider a minumum set of purely structural rules that do not impinge on the dynamics of expression behaviour.

### 2.2 Operational Semantics

The operational semantics for CCS<sup>spt</sup> is given using a labelled transition relation  $P \xrightarrow{\alpha} Q$  in the style of Plotkin's Structured Operational Semantics (SOS) [35, 34], where  $\alpha \in Act$  is the action that labels the SOS transition. When  $\alpha \in \mathcal{L}$ , the transition corresponds to a communication step, namely a rendezvous action or a broadcasted clock action. When  $\alpha = \tau$  is silent, then the transition corresponds to a reduction or an evaluation step. In addition, we decorate the nondeterministic SOS with annotations that provides sufficient information to express a uniform and confluent reduction strategy based on scheduling precedences. Including these annotations, our SOS judgment takes the form  $P \xrightarrow{\alpha}_{R} Q$  where  $P, Q, R \in \mathcal{P}$  are processes,  $\alpha \in Act$  is an action, and  $H \subseteq Act$  a set of actions. The semantics is defined inductively as the smallest relation closed under the rules in Fig. 2. We call each transition derivable by Fig. 2 an admissible transition. We denote by  $\alpha:H[R]$  a compound c-action consisting of the three annotations  $\alpha$ , H, and R. The information provided by such a c-action is sufficient to define our constructive reduction strategy for CCS<sup>spt</sup> that satisfies a refined confluence property. Sometimes, we write  $P \xrightarrow{\alpha} Q$  to state that there is a transition for some R and H

The intuition behind the annotations of admissible transitions is as follows:  $\alpha$  is the usual action "passed back" in the SOS. The blocking set H is the set of actions that take precedence over  $\alpha$ , and R, called the concurrent context, is a process that represents the behaviour of all threads in P that execute concurrently with the transition. i.e., all actions in R are potentially in competition with  $\alpha$ . Think of H as the resources that are required by the action and of R as the concurrent context that potentially competes for H. In a parallel composition  $P \mid Q$  of P with another process Q, the context R might interact with the environment Q to generate actions in the blocking set H. If this happens, the reduction in P with blocking set H will be considered blocked in our scheduled semantics (see Def. 28).

In the rules of Fig. 2, the reader can observe how the annotation for the concurrent context and the blocking sets are inductively built. In a nutshell: Rule (Act) is the axiom annotating in the transition the action and the (empty) environment. Rules (Restr) and (Hide) deal with "local restriction" of rendezvous actions and "local hiding" of broadcasted clocks. Rules (Par) and (Sum) are almost standard and deal with parallelism and choice. Rule (Struct) internalises in the transition the above presented structural equivalence of processes. Rule (Com) constitutes the core of our SOS. It captures, in an elegant way, both the classical CCS rendezvous communication rule and the classical CSP broadcasting communication; it has an extra race test, enriching the blocking set of the conclusion by  $\tau$ , in case P and Q interfere. The presence of  $\tau$  will block unconditionally. Finally, rule (Con) deals with process names and refers to a process whose behaviour is specified by a definitional equation  $A \stackrel{del}{=} P$ .

### 2.3 Constructive Scheduling

The operational semantics of Fig. 2 for rendezvous actions coincides with that of CCS and the rules for clock actions coincide with the semantics of CSP broadcast actions. The scheduling annotations H and R of a c-action  $\alpha:H[R]$  expose extra information about blocking and concurrent context, respectively, of the underlying action  $\alpha$ . We can use them to implement different scheduling strategies. Prioritised process algebras [10, 36, 33] block an admissible transition  $\alpha:H[R]$  when H contains the silent action  $\tau$  or an action that synchronises with some initial action of the concurrent context R. Otherwise, it is (weakly) enabled.

- ▶ **Definition 2** (Initial actions and weakly-enabled transition).

- The set  $iA(R) \subseteq Act$  of initial actions of a process R is given as  $iA(R) = \{\alpha \mid \exists Q. R \xrightarrow{\alpha} Q\}$ .

- **Figure 2** The admissible transitions of  $CCS^{spt}$  processes. See Def. 2 for the *initial actions* iA(P).

- An transition with c-action  $\alpha: H[R]$  is called weakly enabled if  $H \cap (\overline{iA}(R) \cup \{\tau\}) = \{\}$ .

Let us call a process P free if all its c-actions  $\alpha:H[R]$  have an empty blocking set  $H=\{\}$ . The weakly enabled transitions of (unclocked) free processes coincide with the semantics of CCS [27]. We call P discrete if all its c-actions  $\alpha:H[R]$  are self-blocking, i.e.  $H=\{\alpha\}$ . A process P is irreflexive if no action prefix  $\alpha:H.Q$  occurring in P blocks itself, i.e.,  $\alpha \notin H$ . One can show that for (unclocked) irreflexive processes, a transition is weakly enabled iff is derivable in the operational semantics of CCS<sup>Ph</sup> [33]<sup>2</sup>. Thus, CCS and CCS<sup>Ph</sup> correspond to theories of free and irreflexive processes of CCS<sup>spt</sup>, respectively, under weak enabling. Likewise the theories [10, 36] can be subsumed; specifically, the prioritised sum operator  $P \not = Q$  of [10] can be coded as P + Q:iA(P) in CCS<sup>spt</sup>. The theory [36] proposes two levels of labels, a:0 and a:1, where 0 denotes higher priority and 1 ordinary priority. Translated into CCS<sup>spt</sup>, the prefix a:0.P corresponds to  $a:\{\}.P$  while an action prefix a:1.P maps in CCS<sup>spt</sup> to a:Prio.P if we define Prio as the set of all high-prioritised labels.

Examples 4 and 5 below in Sec. 3 demonstrate how prioritised scheduling by weak enabling (Def. 2) can indeed help to ensure determinacy in special cases. For the general case, however, weak enabling is not sufficient. In order to prevent non-determinacy (a global property) from priorities (a purely local property), we must be able to block a c-action  $\alpha:H[R]$  not just if the initial actions iA(R) of the concurrent context R can synchronise with H, as in weak enabling, but look at the set  $iA^*(R)$  of all actions that R can potentially engage in, before it reaches a clock. Example 7 in Sec. 3 illustrates this.

▶ **Definition 3** (Potential actions and constructive enabling).

- The set  $iA^*(P) \subseteq \mathcal{L}$  of potential actions is the smallest extension  $iA(P) \cap \mathcal{L} \subseteq iA^*(P)$ such that if  $\ell \in iA^*(Q)$  and  $P \xrightarrow{\alpha} Q$  for  $\alpha \in \mathcal{R} \cup \{\tau\}$ , then  $\ell \in iA^*(P)$ .

- 280 A transition with c-action  $\alpha:H[R]$  is called constructively enabled, or c-enabled for short, if  $H \cap (\overline{iA}^*(R) \cup \{\tau\}) = \{\}.$

<sup>&</sup>lt;sup>2</sup> In  $CCS^{Ph}$  the blocking sets are written before the action,  $H:\alpha.P$ , where we write  $\alpha:H.P$  in  $CCS^{spt}$ .

The following Sec. 3 presents some motivating examples, while Sec. 4 focuses on the mathematical theory underlying CCS<sup>spt</sup>.

# 3 Examples

282

283

300

302

303

305

308

310

313

315

317

318

319

The first example shows the basic mechanism of how priorities can be used to schedule processes under weak enabling.

**Example 4** (Read Before Write). Consider a "store"  $S \stackrel{def}{=} w.r + r:w$  that offers a write action w followed by a read r, or a read action r but prefers the write over the read. The fact that 288 w takes priority over r is recorded in the blocking set  $\{w\}$  which contains the action w. If we 289 put S in parallel with a reader  $R \stackrel{\text{def}}{=} \overline{r}$ , the read actions r and  $\overline{r}$  synchronise in a reduction  $S \mid R \xrightarrow{\tau}_{0} \{w\}$  0. The blocking set  $\{w\}$  will block R's transition when a parallel writer  $W \stackrel{\text{def}}{=} \overline{w}$  is added, as well. Specifically, the reduction  $S \mid R \mid W \xrightarrow{\tau}_{w} \{w\} W$  is not weakly enabled, because  $\{w\} \cap \overline{\mathsf{iA}}(\overline{w}) = \{w\} \cap \{w\} \neq \{\}$ . The only enabled reduction is that between S and W giving  $S \mid R \mid W \xrightarrow{\tau}_{\{w\}} r \mid R$  and only then continue with the read  $r \mid R \xrightarrow{\tau}_{\{a\}} 0$ . Thus, weak enabling makes the reduction determinate. Observe that S is not confluent (Def. 1): We have  $S \xrightarrow{w} r$ and  $S \xrightarrow{r} 0$  but there is no  $P_1 \equiv P_2$  such that  $r \xrightarrow{r} P_1$  and  $0 \xrightarrow{w} P_2$ . However, S is coherent 296 (Def. 12), because the transition  $S \xrightarrow[0]{t} \{w\}$  0 interferes (Def. 11) with the former  $S \xrightarrow[0]{w} \{r\}$  as 297  $w \in \{w\}$ , whence coherence does not require confluence.

Processes can block each other from making progress. This happens under weak enabling if processes offer two-way rendezvous synchronisation with contradicting precedences.

- ▶ Example 5 (Binary Blocking). Take processes  $P \stackrel{\text{def}}{=} a:b.A + b$  and  $Q \stackrel{\text{def}}{=} \overline{b}:\overline{a}.B + \overline{a}$ . Their composition  $P \mid Q$  has two admissible reductions, through  $a:b \mid \overline{a}$  to A or through  $b \mid \overline{b}:\overline{a}$  to B. So, disregarding the precedences, it is non-deterministic if  $A \not\equiv B$ . Under weak enabling, however,  $P \mid Q$  creates a circular deadlock: P offers a unless synchronisation with  $\overline{b}$  is possible, while Q offers  $\overline{b}$  provided there is no synchronisation with a. None of the reductions is enabled. By the "race" side-condition of (Com) the synchronisation  $a:b \mid \overline{a}$  generates the c-action  $\tau:H[0]$  with  $\tau \in H$  because  $\{b\} \cap \overline{\mathsf{IA}}(Q) \not\equiv \{a\}$ . Similarly, since  $\{\overline{a}\} \cap \overline{\mathsf{IA}}(P) \not\equiv \{\overline{b}\}$ , the synchronisation  $b \mid \overline{b}:\overline{a}$  is blocked. We note that neither P nor Q is confluent, but they are coherent.

- ▶ **Example 6** (Reflexive Blocking). Consider the free process  $s \mid \overline{s}.A \mid \overline{s}.B$  where action s can be consumed by  $\overline{s}.A$  or by  $\overline{s}.B$ , generating non-deterministic  $\tau$ -transitions to  $A \mid \overline{s}.B$  or to  $\overline{s}.A \mid B$ . However, by adding self-blocking, as in  $s:s \mid \overline{s}.A \mid \overline{s}.B$ , weak enabling protects the prefix s from being consumed when both  $\overline{s}.A$  and by  $\overline{s}.B$  compete for it. If only one is present, as in  $s:s \mid \overline{s}.A$  and  $s:s \mid \overline{s}.B$ , no blocking occurs.

Blocking under weak enabling ensures determinism in the special case where the circular dependency involves only initial actions. However, parallel threads can create dependency chains through sequences of actions, e.g., when accessing a shared process that is acting as a resource. This is the general case handled by c-enabling.

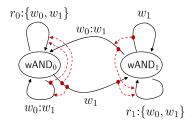

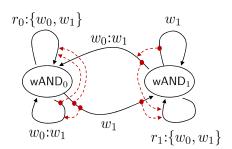

▶ Example 7 (Transitive Blocking). Consider the process  $S \stackrel{\text{def}}{=} w_0 + r_0 : w_0 \mid w_1 + r_1 : w_1$  which offers receiver actions  $w_i$  and  $r_i$  for  $i \in \{0,1\}$  such that  $w_i$  has precedence over  $r_i$ . Now take processes  $P_0 \stackrel{\text{def}}{=} \overline{r_0} . \overline{w_1}$  and  $P_1 \stackrel{\text{def}}{=} \overline{r_1} . \overline{w_0}$  which first aim to synchronise with  $r_i$  and then sequentially afterwards with  $w_{1-i}$ . The parallel composition  $P_0 \mid S \mid P_1$  has two initial  $\tau$ -reductions  $P_0 \mid w_0 + r_0 : w_0 \mid \overline{w_0} \xleftarrow{\tau} P_0 \mid w_0 + r_0 : w_0 \mid w_0$

These reductions are both weakly enabled. If we continue under weak enabling then the residual process  $\overline{w_1} | w_1 + r_1 : w_1 | P_1$  for the first reduction must first execute the synchro-325 nisation on  $w_1$  and thus proceed as  $\overline{w_1} | w_1 + r_1 : w_1 | P_1 \xrightarrow{\tau} P_1$  while the residual process 326  $P_0 \mid w_0 + r_0: w_0 \mid \overline{w_0}$  can only reduce to  $P_0$ . Hence, the resulting final outcome of executing  $P_0 \mid S \mid P_1$  is non-deterministic. Observe that none of the two reductions displayed above 328 is actually c-enabled. For the right reduction we find that its concurrent environment 329  $R_0 \stackrel{\text{\tiny def}}{=} w_1 + r_1:w_1 \mid P_1$  has a reduction sequence  $R_0 \stackrel{\tau}{\to} \overline{w_0}$  and thus  $\{w_0\} \cap \overline{\mathsf{iA}}^*(R_0) \subseteq \mathbb{I}$ 330  $\{w_0\} \cap \overline{\mathsf{IA}}^*(\overline{w_0}) = \{w_0\} \cap \{w_0\} \neq \{\}$ . Symmetrically, for the concurrent environment  $R_1 \stackrel{\text{def}}{=}$ 331  $P_0 \mid w_0 + r_0: w_0$  of the left reduction we have  $R_1 \xrightarrow{\tau} \overline{w_1}$  and hence  $\{w_1\} \cap \overline{\mathsf{iA}}^*(R_1) \neq \{\}$ . The parallel composition  $P_0 \mid S \mid P_1$  is deterministic under c-enabling. We note again, S is not 333 confluent but coherent (Def. 12). 334

The next example generalises Ex. 4 to a full memory cell.

335

336

337

338

339

342

344

345

346

347

348

349

350

351

353

354

356

**Example 8** (Read/Write Memory). Let  $w_0, w_1, r_0, r_1$  the labels of writing/reading a boolean value 0 or 1, respectively. A memory would be modelled by two mutually recursive processes

$$\begin{split} \mathsf{wAND}_0 &\stackrel{\mathit{def}}{=} & w_1.\mathsf{wAND}_1 + w_0 {:} w_1.\mathsf{wAND}_0 + r_0 {:} \{w_0, w_1\}.\mathsf{wAND}_0 \\ \mathsf{wAND}_1 &\stackrel{\mathit{def}}{=} & w_1.\mathsf{wAND}_1 + w_0 {:} w_1.\mathsf{wAND}_0 + r_1 {:} \{w_0, w_1\}.\mathsf{wAND}_1 \end{split}$$

The process wAND<sub>v</sub> represents the memory cell in a state where it has stored the value  $v \in \{0, 1\}$ . In either state, it offers to synchronise with a write action  $w_u$  to change its state to wAND<sub>u</sub>, and also with a read action  $r_v$  to transmit its stored value v to a reader. The write actions  $w_u$  do not only change the state of the memory, they also block the read actions since they appear in their blocking sets  $r_v:\{w_0, w_1\}$ .

Between the write actions, the blocking sets implement a precedence of  $w_1$  over  $w_0$ . In the picture on the right the process state transitions are visualised with the blocking sets as red dashed arrows.

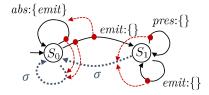

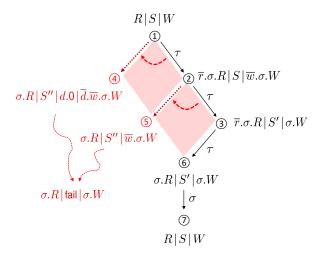

▶ Example 9 (Esterel Signals). Concurrent Esterel threads communicate via signals [6, 38]. A (pure, temporary) signal can have two statuses, present and absent. At the beginning of a synchronous macro-step, each signal is initialised to be absent, by default. The signal becomes present as soon as some thread emits it. It remains present thereafter for throughout the current macro-step, i.e., until the next clock cycle is started. The clock is a global synchronisation, taken by all threads simultaneously. The value of the signal is broadcast to all concurrent threads which can test it and branch their control-flow according to the signal's status. To maintain coherency of data-flow and deterministic behaviour, the signal status can only be read when no writing is possible any more. Esterel compilers conduct a causality analysis on the program and obtain a suitable static schedule when they generate imperative code. In Esterel hardware compilers, the scheduled to satisfy the emit-before-test protocol, or hardware that that does not stabilise are called non-constructive and rejected by the compiler. A pure, temporary signal is modelled by the following recursive behaviour:

$$\begin{array}{lll} S_0 & \stackrel{\scriptscriptstyle def}{=} & abs:emit.S_0 + emit.S_1 + \sigma:\{abs,emit\}.S_0 \\ S_1 & \stackrel{\scriptscriptstyle def}{=} & pres.S_1 + emit.S_1 + \sigma:\{pres,emit\}.S_0 \end{array}$$

which is depicted on the right and structurally coherent according to Def. 12.

360

362

364

365

366

367

371

372

373

374

375

376

377

379

380

381

382

383

384

385

387

```

ABRO \stackrel{def}{=} \sigma.(A | B | R | O | T) \setminus \{s,t\}

A \stackrel{def}{=} k_a:k_a.0 + a:\{k_a,a\}.\overline{s}:\overline{s}.0 + \sigma:\{k_a,a\}.A

B \stackrel{def}{=} k_b:k_b.0 + b:\{k_b,b\}.\overline{s}:\overline{s}.0 + \sigma:\{k_b,b\}.B

R \stackrel{def}{=} r:r.\overline{k}_a:\overline{k}_a.\overline{k}_b:\overline{k}_b.\overline{k}_s:\overline{k}_s.\overline{k}_t:\overline{k}_t.ABRO + \tau:r.\sigma.R

O \stackrel{def}{=} k_t:k_t.0 + t:\{k_t,t\}.\overline{o}:\overline{o}.0 + \sigma:\{k_t,t\}.O

T \stackrel{def}{=} k_s:k_s.0 + s:\{k_s\}.T + \overline{t}:\{k_s,\overline{t},s\}.0 + \sigma:\{k_s,\overline{t},s\}.T

```

Figure 3 ABRO as a CCS<sup>spt</sup> process, Mealy machine and SyncChart.

▶ Example 10 (ABRO). The hello word in synchronous languages, see [6], ABRO has the following behaviour: Emit the output o as soon as both inputs a and b have been received. Reset this behaviour each time the input r occurs, without emitting o in the reset cycle. [38] The behaviour of ABRO is expressed as a Mealy machine and a SyncChart, displayed in Fig. 3 on the right. The synchronous behaviour of Esterel lies in the assumption that each transition of the Mealy machine summarises a single macro-step interaction of the machine with its environment. The transitions of parallel machines synchronise so that state changes proceed in lock-step. The simultaneous execution of these transitions that make up a macro-step consists of the sending and receiving of signals. The propagation of individual signals between machines is modeled in the *micro-step* operational semantics of Esterel. module ABRO: In  $CCS^{spt}$  we represent the micro-steps as sequences of  $\tau$ -transitions, input A, B, R; output 0; i.e., rendez-vous synchronisations, whereas the macro-step is captured loop as a global clock synchronisation. Unfortunately, the Mealy machine await A || await B; formalism is not scalable because the number of states can grow emit O exponentially as the number of signals grow, while in Esterel can be each R

expressed in a linear number of code lines as seen on the right. end module The loop P each R construct of Esterel executes the behaviour of program P for an unbounded number of clock cycles, but restarts its body P when the signal R becomes present. The reset R takes priority over the behaviour of P which is preempted at the moment that the reset occurs. Note that in Esterel each signal appears exactly once, as in the specification and unlike in the Mealy machine. Other parts of Esterel also naturally arise from precedence-based scheduling. Esterel's loop P each R mechanism, for instance, can be coded using the static parallel composition operator that combines the process P to be aborted and reset with a "watchdog" process R. The latter waits for the reset signal from the environment in each clock cycle. The choice between the reset and continuing inside P is resolved by giving R higher priority. When the reset occurs, the watchdog sends "kill" signals to all threads running in P and waits for these to terminate. Only then the watchdog R restarts P from scratch. This is a form of precedence that can be expressed in the blocking sets of CCS<sup>spt</sup>. As such, Fig. 3 on the left translates the Esterel code of ABRO compositionally in  $\mathsf{CCS}^\mathsf{spt}$ . ABRO is obtained as a parallel composition  $(\mathsf{R} \,|\, \mathsf{ABO}) \setminus \{s,t\}$  combining a watchdog R with the behaviour  $ABO \stackrel{def}{=} A \mid B \mid O \mid T$ . The R is responsible to implement the reset loop at the superstate called ABO, as in the state charts. The ABO is the behaviour of the interior of this superstate, which corresponds to the statement (await A | | await B); emit O in Esterel: it is the parallel composition of A | B making up the behaviour of the region called AB with code await A | | await B. The processes T | O implement the synchronisation that waits for termination of AB to start the output process O. We assume that the channels a, b, r, o modelling interface signals A, B, R, O all have a unique sender and receiver. This is seen

in our coding from the fact that the prefixes for these channels are self-blocking.

# 4 Coherence and Determinacy for CCS<sup>spt</sup>

391

399

401

403

409

411

413

414

418

419

422

423

424

425

426

This section presents the core elements of our scheduling theory under constructive enabling:

coherence, policies, and policy-conformant processes. *Coherence* (Def. 12) corresponds to

Milner's notion of confluence, but refined "up-to" priorities. It requires structural confluence

for c-enabled and diverging c-actions only if they do not interfere with each other considering

their blocking sets and concurrent environments.

▶ **Definition 11** (Transition Interference). Two c-enabled transitions with c-actions  $\alpha_1:H_1[E_1]$  and  $\alpha_2:H_2[E_2]$  are interference-free if  $\alpha_1=\alpha_2$  or  $\alpha_i\notin H_{3-i}$  for all  $i\in\{1,2\}$ .

Observe that for free processes (i.e., with empty blocking sets) all c-actions are interference-free and they are c-enabled iff they are admissible. Confluence of interference-free c-actions is formulated using an auxiliary form of residual transition  $P \stackrel{\alpha}{\leadsto} Q$ . This is a transition from P to Q with an action that is a "factor" of  $\alpha$ . Formally, we define  $P \stackrel{\alpha}{\leadsto} Q$  if (i)  $\alpha \in \mathcal{L}$  with  $P \stackrel{\alpha}{\Longrightarrow} Q$  or  $P \equiv Q$ , or (ii)  $\alpha = \tau$  with  $P \stackrel{\tau}{\Longrightarrow} Q$  or  $P \stackrel{\ell}{\Longrightarrow} Q$  for some  $\ell \in \mathcal{R}$ .

▶ **Definition 12** (Process Coherence). A process P is (structurally) coherent if for all its derivatives Q the following holds: Given two c-enabled and interference-free transitions  $Q \xrightarrow{\alpha_1}_{E_1} H_1 Q_1$  and  $Q \xrightarrow{\alpha_2}_{E_2} H_2 Q_2$  such that  $\alpha_1 \neq \alpha_2$  or  $Q_1 \not\equiv Q_2$  or both  $\{\alpha_1, \alpha_2\} \subseteq \mathcal{R}$  and  $\alpha_i \not\in H_{3-i}$ . Then, there exist transitions  $Q_1 \xrightarrow{\alpha_2}_{E_2'} H_2' Q'$  and  $Q_2 \xrightarrow{\alpha_1}_{E_1'} H_1' Q'$  with  $H_i' \subseteq H_i$  and  $E_1 \xrightarrow{\alpha_2}_{E_1'} E_1'$  and  $E_2 \xrightarrow{\alpha_1}_{E_1'} E_2'$ .

For free processes, coherence implies confluence (Def. 1), but is strictly stronger.

- ▶ Example 13. For instance,  $Q \stackrel{\text{def}}{=} a:\{\}.0$  is confluent but not coherent. Since the prefix not self-blocking, coherence ensures that the label must consumable by arbitrarily many concurrent processes. Technically, since  $Q \stackrel{a}{\to} Q_1$  and  $Q \stackrel{a}{\to} Q_2$  for  $Q_1 \equiv 0 \equiv Q_2$ , there should be a transition  $Q_i \stackrel{a}{\to} Q'$  which is not the case. However, for discrete processes, coherence is identical with confluence: With self-blocking,  $Q \stackrel{\text{def}}{=} a:\{a\}.0$  is both confluent and coherent. It is important to note that all examples in Sec. 3 are coherent but not confluent.

- ▶ **Theorem 14** (Coherence implies Determinacy). Every coherent process is determinate under c-enabled reductions.

A coherent process cannot simultaneously offer both a clock and another distinct action without putting them in precedence order. Moreover, whenever a clock is enabled, then every further reduction of the process is blocked by the clock. Thm. 14 concerns the  $\tau$ -transitions of a coherent process. For clock transitions we have an even stronger result.

▶ **Proposition 15** (Clock Determinism). Every coherent process P is structurally clock deterministic, i.e., if  $P \xrightarrow{\sigma} P_1$  and  $P \xrightarrow{\sigma} P_2$  then  $P_1 \equiv P_2$ .

The question is now how we can obtain coherent processes by composition. In view of Milner's classical result for confluence, we expect to have to impose some form of "sort-separation" for parallel processes. It turns out that we can express such a condition and even avoid the restriction operator (thereby permit sharing) if we enrich the sorts  $\mathcal{L}(P)$ ,  $\mathcal{L}(Q)$  by priority information. We call the resulting enriched sorts  $\pi(P)$ ,  $\pi(Q)$  precedence policies.

#### XX:12 Strong Priority and Determinacy in Timed CCS

434

439

458

463

464

▶ **Definition 16** (Precedence Policy). A precedence policy is a pair  $\pi = (L, \cdots)$  where  $L \subseteq \mathcal{L}$  is a subset of visible actions, called the alphabet of  $\pi$  and  $\cdots \subseteq L \times L$  a binary relation on L, called the precedence relation.

We will write  $\ell \in \pi$  to state that  $\ell$  is in the alphabet of  $\pi$  and we write  $\ell_1 \dashrightarrow \ell_2 \in \pi$  to express that the pair  $(\ell_1, \ell_2)$  is in the precedence relation of the policy. Further, if  $\ell_1, \ell_2 \in \pi$  and both  $\ell_1 \dashrightarrow \ell_2 \notin \pi$  as well as  $\ell_2 \dashrightarrow \ell_1 \notin \pi$ , we say that  $\ell_1$  and  $\ell_2$  are concurrently independent under  $\pi$ , written (by abuse of the set-notation)  $\ell_1 \diamond \ell_2 \in \pi$ .

For any policy  $\pi = (L, \cdots)$  and set of labels  $K \subseteq \mathcal{L}$  we denote by  $\pi \setminus K$  the policy  $\pi$  restricted to the alphabet  $L - (K \cup \overline{K})$  in the standard way. There is also the normal inclusion ordering  $\pi_1 \subseteq \pi_2$  between policies defined by  $L_1 \subseteq L_2$  and  $\cdots \subseteq L_2$ .

The next Def. 17 on conformance captures how policies statically specify the externally observable scheduling behaviour of a process.

▶ **Definition 17** (Conformance). P conforms to a policy  $\pi$  if for each derivative Q of P: If  $Q \xrightarrow{\ell}_{B} H Q'$  with  $\ell \in \mathcal{L}$ , then  $\ell \in \pi$  and for all  $\ell' \in H \cap \mathcal{L}$ , then  $\ell' \dashrightarrow \ell \in \pi$ .

For a process P and policy  $\pi$ , let us write  $P \Vdash \pi$  to express that P is coherent and conforms to policy  $\pi$ . We will say that P is coherent for  $\pi$ . If  $P \Vdash \pi$  then the alphabet of  $\pi$  corresponds to the sort  $\mathcal{L}(P)$  in CCS. It gives an upper bound on the labels that can be used by the process, and the precedence relation in  $\pi$  provides a static over-approximation of the blocking, i.e., which labels can be in a choice conflict with each other. As a notational shortcut we will write  $P \Vdash \ell_1 \dashrightarrow \ell_2$  to say that there is a policy  $\pi$  with  $P \Vdash \pi$  and  $\ell_1 \dashrightarrow \ell_2 \in \pi$ . Analogously, we write  $P \Vdash \ell_1 \diamond \ell_2$  if there is a policy  $\pi$  with  $\ell_1 \diamond \ell_2 \in \pi$  and  $\ell_1 \dashrightarrow \ell_2 \in \pi$ .

- \*Example 18. The most permissive policy for a given sort  $L \subseteq \mathcal{L}$ , written  $\pi_{max}(L)$ , contains all labels from L as its alphabet but no precedences, i.e.,  $\ell_1 \diamond \ell_2 \in \pi_{max}(L)$  for all  $\ell_1, \ell_2 \in L$ . If  $P \Vdash \pi_{max}$  then P has sort L and will permit arbitrarily many concurrent processes to consume its labels L under c-enabling. The most restrictive policy, denoted  $\pi_{min}(L)$ , also has alphabet L, but full precedences, i.e.,  $\ell_1 \dashrightarrow \ell_2 \in \pi_{min}$  for all  $\ell_1, \ell_2 \in L$ . If  $P \Vdash \pi_{min}(L)$ , then P has sort L but does not permit any concurrency; it can only communicate with a single sequential thread.

- ▶ Example 19. Reflexive precedences  $\ell \dashrightarrow \ell \in \pi$  play a special role in our theory. They permit a conformant  $P \Vdash \pi$  and its derivatives to execute  $\ell$  only with a single partner. For instance, ABRO from Ex. 10 satisfies ABRO  $\not\models r \diamond r$  and so ABRO  $\mid \sigma.\overline{r} \mid \sigma.\overline{r}$  reduces but ABRO  $\mid \sigma.\overline{r} \mid \sigma.\overline{r}$  will block after the initial clock transition. In contrast, if the policy specifies  $\ell \diamond \ell \in \pi$ , then in a process  $P \Vdash \pi$  any  $\ell$ -transition is consumable arbitrarily often. For instance, the Esterel signal from Ex. 9 has  $S_1 \Vdash pres \diamond pres$  and so  $S_1 \mid \overline{pres} \mid \overline{pres}$  will not block.

Here we are interested in processes that conform to policies with special properties.

```

▶ Definition 20 (Pivot and precedence-closed policy). A policy \pi is called

pivotable if \overline{L} \subseteq L and for all \ell_1, \ell_2 \in L with \ell_1 \neq \ell_2 we have \ell_1 \diamond \ell_2 \in \pi or \overline{\ell}_1 \diamond \overline{\ell}_2 \in \pi.

precedence-closed for L \subseteq \mathcal{L} if \ell_1 \in L and \ell_1 \dashrightarrow \ell_2 \in \pi implies \ell_2 \in L.

A process is pivotable/precedence-closed if P conforms to pivot/precedence-closed policy.

```

<sup>&</sup>lt;sup>3</sup> In Milner's notation we would write  $P:\pi$ , but we already use the colon ':' for blocking sets as in  $\mathsf{CCS}^\mathsf{Ph}$ .

▶ Example 21. An Esterel signal (Ex. 9) has the alphabet  $\{emit, pres, abs\} = \mathcal{L}(S_i)$  ( $i \in \{1,2\}$  and for simplicity we ignore the clock  $\sigma$ ) and is conformant to the policy psig with  $emit --- abs \in psig$ . A typical program R accessing the signal has alphabet  $\{\overline{pres}, \overline{abs}\} \subseteq \mathcal{L}(S_i)$  and is of form  $R = \overline{pres}: \overline{pres}.R_1 + \overline{abs}: \{\overline{abs}, \overline{pres}\}.R_0$ . If the signal is present then  $R_1$  is executed, if it is absent then  $R_0$  is executed. Such R conforms to a policy prg with  $\overline{pres} --- \overline{abs} \in prg$  and  $\ell --- \to \ell \in prg$  for  $\ell \in \{\overline{pres}, \overline{abs}\}$ . Both psig and prg as well as their union  $psig \cup prg$  are pivot policies, so that  $R \mid S_i$  is pivotable. In a pivotable process, conflicting choices are resolved by the precedences in a single thread, acting as the "pivot". In  $R \mid S_i$  the pivot is the signal  $S_i$  on reading, resolving the choice  $\overline{pres} + \overline{abs}$  in R, and it is the program R on writing, resolving the choice abs + emit in  $S_i$ .

Non-pivotable processes, in general, may block because of two threads entering into a circular precedence deadlock with each other.

▶ Example 22. For example, recall the processes  $P \stackrel{def}{=} a:b.A + b$  and  $Q \stackrel{def}{=} \overline{b}:\overline{a}.B + \overline{a}$  from Example 5. Their parallel composition  $P \mid Q$  creates a deadlock under (even weak) enabling because of the contradicting precedences in the two possible interactions  $a:b \mid \overline{a}$  and  $b \mid \overline{b}:\overline{a}$ . The deadlock is reflected in the policy  $\pi$  of P satisfying  $b \dashrightarrow a \in \pi$  and  $\overline{a} \dashrightarrow \overline{b} \in \pi$  which is not a pivot policy that would instead require  $a \diamond b \in \pi$  or  $\overline{a} \diamond \overline{b} \in \pi$ .

Reductions of pivotable processes never block because of two threads entering into a circular precedence deadlock with each other. One can show that for pivotable processes of at most two threads, the three operational semantics of CCS (admissible), of CCS<sup>Ph</sup> (weak enabling) and our CCS<sup>spt</sup> (c-enabling) all coincide. This is a consequence of the fact (cf. Lem. 51 and 52) that the race test in the rule (Com) is never introducing the silent action  $\tau$  into the blocking sets. In general, pivotable processes may consist of three or more interacting threads, and blocking may occur and the semantics of CCS, CCS<sup>Ph</sup> and CCS<sup>spt</sup> are different. However, one can show that the blocking of a synchronisation is always due to the external environment. In other words, the computation of race(P,Q) in rule (Com) becomes redundant. Two single-threaded pivotable processes never block each other.

Pivotable process cannot offer a clock action and exhibit reduction at the same time. This means that in this class of processes, clocks and reductions are sequentially scheduled.

▶ **Proposition 23** (Clock Maximal Progress). Suppose P is coherent and pivotable. If  $\sigma \in iA(P)$  then P is in normal form, i.e., there is no reduction  $P \xrightarrow{\tau} P'$ .

Prop. 23 can be seen as saying that in pivotable processes all clocks take lowest precedence. As a result, clock transitions satisfy maximal progress, i.e., a clock is only enabled on normal forms, i.e., if there is no reduction possible. Thus clocks behave like time steps in the standard timed process algebras [18, 11]. More importantly (Thm. 12), all reductions are confluent. So, a pivotable process, no matter in which order the reductions are executed, when it terminates, it computes a unique normal form. At this point it either stops if there is no clock possible, or it offers a clock step (pausing) to a continuation process from which a new normal form is produced. In this way, coherent pivotable processes correspond to synchronous streams.

It remains to be seen how we can obtain coherent processes systematically by construction. The following Thm. 24 identifies a set of closure operators for coherent processes based on policy-conformance. This is our main theorem that summarises Propositions 60–66 (Appendix), which provide in CCS<sup>spt</sup> a generalisation of Milner's Confluence Class, Prop. 15-17 in [27].

#### XX:14 Strong Priority and Determinacy in Timed CCS

- Theorem 24 (Milner's Confluence Class Generalised).

- 515 (1) (Idling)  $0 \Vdash \pi$  for all policies  $\pi$ .

525

526

- (2) (Rendezvous Prefix) If  $Q \Vdash \pi$ , then for every  $\ell \in \mathcal{R}$  we have  $\ell: H.Q \Vdash \pi$  if  $\ell \in H \subseteq \{\ell' \mid \ell' --- \ell \in \pi\}$ .

- 8 (3) (Clock Prefix) If  $Q \Vdash \pi$  and clock  $\sigma \in \mathcal{C}$ , then  $\sigma:H.Q \Vdash \pi$  if  $H \subseteq \{\beta \mid \beta \dashrightarrow \sigma \in \pi\}$ .

- (4) (Choice) If  $P_1 \Vdash \pi_1$  and  $P_2 \Vdash \pi_2$  and for all pairs of initial transitions  $P \xrightarrow{\alpha_1}_{F_1} H_1 P_1$  and  $P \xrightarrow{\alpha_2}_{F_2} H_2 P_2$  such that  $\alpha_1 \neq \alpha_2$  as well as  $\alpha_1 \in H_2$  or  $\alpha_2 \in H_1$ . Then  $P_1 + P_2 \Vdash \pi$  if  $\pi_1 \subseteq \pi$  and  $\pi_2 \subseteq \pi$ .

- (5) (Parallel) If  $Q \Vdash \pi$  and  $R \Vdash \pi$  where  $\pi \setminus \mathcal{R}$  is a pivot policy, then  $(Q \mid R) \Vdash \pi$ .

- (6) (Hiding) If  $Q \Vdash \pi$  and  $\sigma \dashrightarrow \ell \in \pi$  for all  $\sigma \in L$  and  $\ell \in \pi$ , then  $Q/L \Vdash \pi$ .

- (7) (Restriction) If  $Q \Vdash \pi$  and  $\pi$  precedence-closed for  $L \cup \overline{L}$ , then  $(Q \setminus L) \Vdash \pi \setminus L$ .

The theorem is the main result of the paper, namely that under a suitable "policy decoration", a process can be run deterministically in the scheduled SOS semantics of CCS<sup>spt</sup>.

Example 25. To give a concrete example of the property stated by the above theorem, let's revisit Ex. 10: the processes A, B, R, O, T are all coherent and conform to the pivot policy  $\pi_{\mathsf{ABRO}}$  with precedences (ignoring the clock, so  $\pi \backslash \mathcal{R} = \pi$ )  $k_s \dashrightarrow \bar{t}$ ,  $k_s \dashrightarrow \bar{t}$ , for  $x \in \{a, b, s, t\}$  and  $\ell \dashrightarrow \ell$  for  $\ell \in \{r, a, b, \bar{s}, t, \bar{t}, \bar{o}\}$ . Thus, by Thm. 24(5), their composition satisfies  $\mathsf{A} \mid \mathsf{B} \mid \mathsf{R} \mid \mathsf{O} \mid \mathsf{T} \Vdash \pi_{\mathsf{ABRO}}$ . Since the policy is also precedence-closed for  $\{s, t, \bar{s}, \bar{t}\}$ , we have  $\mathsf{ABRO} \Vdash \pi'_{\mathsf{ABRO}}$  by Thm. 24(3,7), where  $\pi'_{\mathsf{ABRO}} = \pi_{\mathsf{ABRO}} \setminus \{s, t\}$ .

Note that, specifically, Thm. 24(5) is our replacement of Milner's notion of confluent composition  $(P|Q) \setminus L$ . Finally, to highlight our claim that we extend the classical result, we offer the following definition and conjecture to catch Milner's setting of CCS in CCS<sup>spt</sup>.

- ▶ **Definition 26** (Milner's Confluence Class). Milner's confluence class  $CCS^{cc} \subseteq P$  is the set of processes P such that for all derivatives Q of P, if  $Q \xrightarrow{\alpha}_{F} H Q'$ , the following holds:

- If  $\alpha \neq \tau$  then  $H = \{\alpha\}$  and  $\alpha \notin \overline{iA}^*(E)$ .

If  $\alpha = \ell \mid \overline{\ell}$  then  $H = \{\}$  and  $\{\ell, \overline{\ell}\} \cap \overline{iA}^*(E) = \{\}$ .

- **Conjecture 1** (Milner's Confluence Class is Coherent). For all  $P, Q \in CCS^{cc}$ :

- P is coherent iff P is confluent.

- A transition of P is c-enabled iff it is admissible.

- If  $\mathcal{L}(P) \cap \mathcal{L}(Q) = \{\}$  and  $\overline{\mathcal{L}(P)} \cap \mathcal{L}(Q) = L \cup \overline{L}$ , then  $(P \mid Q) \setminus L \in \mathsf{CCS^{cc}}$ .

### 5 Further work

We list in spare order some possible future works:

- We plan to study the interaction of our notion of coherence with forms of congruence (static, dynamic and interaction laws in Milner's jargon) and notions of bisimulation.

- We plan to generalise the interaction model of CCS<sup>spt</sup> to synchronisation algebras permitting action fusion in the spirit of Milner's ASCCS and Austry and Boudol's Meije (see [26, 3]).

- Thm. 24 suggests using policies as types. Among possible type disciplines we just mention: behavioural type systems, including session-types to capture rendezvous interactions; intersection-types, including non-idempotent ones to characterise termination and resources awareness, and linear-types to model consuming resources.

C-actions are somewhat related with continuation passing style, and, in some sense they are more powerful because they permit a "forecast" analysis of all possible future actions: studying this relation, possibly in relation with abstract interpretation techniques, would be worth of study.

Clocks are unordered in CCS<sup>spt</sup>: introducing a partial order could be an interesting, although economic and fine grained, way to reason about time and time priorities.

#### - References

561

- J. Aguado, M. Mendler, R. v. Hanxleden, and I. Fuhrmann. Grounding synchronous deterministic concurrency in sequential programming. In <u>Proceedings of the 23rd European Symposium on Programming (ESOP'14), LNCS 8410</u>, pages 229–248, Grenoble, France, April 2014. Springer.

- <sup>566</sup> 2 R. M. Amadio. A synchronous pi-calculus. <u>Inf. Comput.</u>, 205(9):1470–1490, 2007. URL: <sup>567</sup> https://doi.org/10.1016/j.ic.2007.02.002, doi:10.1016/J.IC.2007.02.002.

- D. Austry and G. Boudol. Algèbre de processus et synchronisation. <u>Theor. Comput. Sci.</u>, 30:91–131, 1984.

- G. Barrett. The semantics of priority and fairness in OCCAM. In M. Main, A. Melton,

M. Mislove, and D. Schmidt, editors, Proc. MFPS'89, 1989.

- 572 5 G. Berry. The Constructive Semantics of Pure Esterel. Draft Book, 1999. ftp://ftp-sop.

573 inria.fr/esterel/pub/papers/constructiveness3.ps.

- G. Berry. The Foundations of Esterel. In <u>Proof, Language and Interaction: Essays in Honour</u> of Robin Milner, pages 425–454. MIT Press, 2000.

- 7 G. Berry and G. Boudol. The chemical abstract machine. <u>Theor. Comput. Sci.,</u>

96(1):217-248, 1992. URL: https://doi.org/10.1016/0304-3975(92)90185-I, doi:10.

1016/0304-3975(92)90185-I.

- R. Bocchino, V. Adve, S. Adve, and M. Snir. Parallel programming must be deterministic by default. In Proceedings of the First USENIX conference on Hot topics in parallelism, pages 4–4, 2009.

- F. Boussinot and R. De Simone. The SL synchronous language. <u>IEEE Transactions on</u>

Software Engineering, 22(4):256–266, 1996.

- J. Camilleri and G. Winskel. CCS with priority choice. <u>Information and Computation</u>, 116(1):26–37, 1995.

- R. Cleaveland, G. Lüttgen, and M. Mendler. An algebraic theory of multiple clocks. In

A. Mazurkiewicz and J. Winkowski, editors, Proceedings of the International Conference on

Concurrency Theory CONCUR'97, pages 166–180. Springer, 1997. LNCS 1243.

- 589 12 V. Dieckert and G. Rozenberg, editors. The Book of Traces. World Scientific, 1995.

- S. A. Edwards. On determinism. In M. Lohstroh et. al., editor, <u>Lee Festschrift</u>, pages 240–253.

Springer, 2018.

- P. Le Guernic, T. Goutier, M. Le Borgne, and C. Le Maire. Programming real time applications with SIGNAL. In <u>Proceedings of the IEEE</u>, volume 79, pages 1321–1336. IEEE Press, September 1991.

- M. Mendler H. R. Andersen. An asynchronous process algebra with multiple clocks. In

D. Sannella, editor, In Proc. ESOP'94, pages 58–73, 1994.

- N. Halbwachs, P. Caspi, P. Raymond, and D. Pilaud. The synchronous data-flow programming language LUSTRE. <u>Proceedings of the IEEE</u>, 79(9):1305–1320, September 1991.

- D. Harel, A. Pnueli, J. Pruzan-Schmidt, and R. Sherman. On the formal semantics of Statecharts. In Logic in Computer Science (LICS'87), pages 54–64. IEEE Press, 1987.

- M. Hennessy and T. Regan. A process algebra for timed system. <u>Information and Computation</u>,

117:221–239, 1995.

- 603 19 C.A.R. Hoare. <u>Communicating Sequential Processes</u>. Prentice-Hall, 1985. 256 pages.

- 604 20 C. D. Kloos and P. Breuer, editors. Formal Semantics for VHDL. Kluwer, 1995.

- <sup>605</sup> 21 J. W. Klop. Combinatory reduction systems. PhD thesis, Univ. Utrecht, 1980.

- L. Kuper and R. Newton. Lvars: lattice-based data structures for deterministic parallelism.

In <u>Functional High-Performance Computing</u>, page 71–84, New York, NY, USA, 2013. ACM.

- 23 E. A. Lee. The problem with threads. Computer, 39(5):33–42, 2006.

- G. Lüttgen, M. von der Beeck, and R. Cleaveland. Statecharts via process algebra. In

CONCUR '99: Concurrency Theory, volume 1664 of Lecture Notes in Computer Science,

pages 399–414. Springer, 1999.

S. Marlow. Parallel and concurrent programming in haskell. In <u>CEFP 2011</u>, pages 339–401,

2012.

- 26 R. Milner. Calculi for synchrony and asynchrony. Theor. Comput. Sci., 25:267-310, 1983. URL: https://doi.org/10.1016/0304-3975(83)90114-7, doi:10.1016/0304-3975(83)90114-7.

- 616 27 R. Milner. Communication and Concurrency. Prentice Hall, 1989.

- 617 **28** R. Milner. Communicating and mobile systems the Pi-calculus. Cambridge University Press, 1999.

- R. Milner, J. Parrow, and D. Walker. A calculus of mobile processes, I. <u>Inf. Comput.</u>, 100(1):1-40, 1992. URL: https://doi.org/10.1016/0890-5401(92)90008-4, doi:10.1016/0890-5401(92)90008-4.

- R. Milner, J. Parrow, and D. Walker. A calculus of mobile processes, II. <u>Inf. Comput.</u>, 100(1):41-77, 1992. URL: https://doi.org/10.1016/0890-5401(92)90009-5, doi:10.1016/0890-5401(92)90009-5.

- X. Nicollin and J. Sifakis. The algebra of timed processes, ATP: theory and application.

Inf. Comput., 114(1):131-178, 1994. URL: https://doi.org/10.1006/inco.1994.1083, doi: 10.1006/INCO.1994.1083.

- B. Norton, G. Luettgen, and M. Mendler. A compositional semantic theory for componentbased synchronous design. In R. Amadio and D. Lugiez, editors, <u>Int'l Conf. on Concurrency</u> Theory (CONCUR'2003), pages 461–476, Marseille, September 2003. Springer LNCS 2761.

- I. Phillips. CCS with priority guards. In K. G. Larsen and M. Nielsen, editors,

Proc. Concur 2001, pages 305–320, 2001.

- G. D. Plotkin. The origins of structural operational semantics. <u>J. Log. Algebraic Methods</u>

<u>Program.</u>, 60-61:3-15, 2004. URL: https://doi.org/10.1016/j.jlap.2004.03.009, doi:

10.1016/J.JLAP.2004.03.009.

- G. D. Plotkin. A structural approach to operational semantics. <u>J. Log. Algebraic Methods</u>

Program., 60-61:17-139, 2004.

- V. Natarajan R. Cleaveland, G. Lüettgen. <u>Handbook of Process Agebra</u>, chapter Priority in Process Algebra. Elsevier, 2001.

- K. Schneider. The synchronous programming language Quartz. Internal Report 375,

Department of Computer Science, University of Kaiserslautern, Kaiserslautern, Germany,

December 2009.

- Esterel Technologies. The Esterel v7 reference manual version v7\_30 initial IEEE standardization proposal. Technical report, Esterel Technologies, 679 av. Dr. J. Lefebvre, 06270 Villeneuve-Loubet, France, November 2005.

- S.H. Unger. Asynchronous sequential switching circuits with unrestricted input changes. <u>IEEE</u>

<u>Transactions on Computers</u>, C-20(12):1437–1444, 1971. doi:10.1109/T-C.1971.223155.

- 40 L. G. Valiant. A bridging model for parallel computation. <u>Commun. ACM</u>, 33(8):103-111,

1990. URL: https://doi.org/10.1145/79173.79181, doi:10.1145/79173.79181.

- R. von Hanxleden, B. Duderstadt, C. Motika, S. Smyth, M. Mendler, J. Aguado, S. Mercer, and

O. O'Brien. SCCharts: Sequentially Constructive Statecharts for safety-critical applications.

In Proc. PLDI'14, Edinburgh, UK, June 2014. ACM.

# A From Asynchronous Priorities to Synchronous ones, via Clocks

This rather informal section gives to the curious reader a nice view of our personal pilgrimage of previous work looking at reaching more control and determinism in asynchronous process algebra. This trip lead us to consider adding clocks to the previous literature and reach confluence in a synchronous setting.

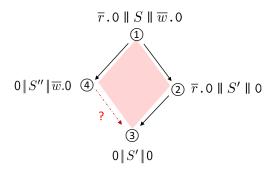

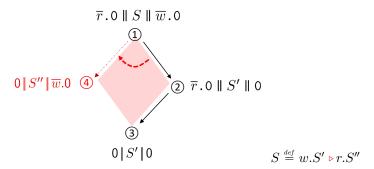

**Figure 4** Symmetric Choice. The final outcome, in states ③ and ④, is non-determinate because it depends on the order of read and write. The continuations states are  $S' \stackrel{def}{=} r.S'$  and  $S'' \stackrel{def}{=} r.S'' + e.S''$ . For confluence, the error state ③ should permit a (delayed) read to move forward and (eventually) meet with state ④, indicated by the dashed red arrow. However, this is not in general guaranteed.

# A.1 CCS with (Weak) Priorities

661

665

666

668

671

673

674

676

677

678

679

681

682

683

684

685

688

Let us look in more detail on how a precedence mechanism such as "write-before-read" might be derived from the classical priorities studied for CCS. As a simple example, suppose S is a (synchronous write, asynchronous read) memory cell that can be read at any time offering the read action r, but only be written once with the write action w. Ignoring data values, the cell would be modelled in plain CCS by the equations  $S \stackrel{\text{def}}{=} w.S' + r.S''$  where  $S' \stackrel{\text{def}}{=} r.S'$ and  $S'' \stackrel{\text{def}}{=} r.S'' + e.S''$ . Initially, memory cell S is empty and offers a choice between a read action r and a write action w. If the write action is performed, the cell receives a value and changes to state S'. In this filled state S', only read actions are admissible to access the stored value, the state does not change. When the read action is executed on the empty cell S, however, the continuation state is S'' which represents an error state. In the error state S'' only a read or an error action e is possible, but no write and the cell remains in error. Observe that only the read action is always admissible in both states S and S', while the write is admissible only in state S. If S is put in parallel with a reader offering  $\bar{r}$  and a writer offering  $\overline{w}$ , then the final state of S depends on the order between the  $\overline{r}$  and  $\overline{w}$  actions. If we synchronise with the external sequence  $\overline{r}.\overline{w}$  on S where the read action is first, the writer gets blocked on the error state S'', while if we exercise  $\overline{w}.\overline{r}$  where the write action is first, both can proceed and we obtain filled state S'. In term rewriting system jargon [21] this is called "critical pairs".

Formally, let  $R \stackrel{\text{def}}{=} \overline{r}.0$  be a reader process with a single read and  $W \stackrel{\text{def}}{=} \overline{w}.0$  the writer with a single write, both terminating in the empty behaviour 0. Then, according to the operational semantics of CCS, we have the two execution sequences  $R \mid S \mid W \xrightarrow{\tau} 0 \mid S'' \mid W$  and  $R \mid S \mid W \xrightarrow{\tau} R \mid S' \mid 0 \xrightarrow{\tau} 0 \mid S' \mid 0$ , where both configurations  $0 \mid S'' \mid W$  and  $0 \mid S'' \mid 0$  are distinct normal forms, in the sense that no reductions are possible anymore. This is pictorially illustrated in Fig. 4. Observe that the behaviour is not only *non-deterministic* in the sense that there is more than one scheduling sequence. It is also non-determinate as the final outcome depends on the scheduling decisions.

Among many CCS extension with priorities, we looked the one of Camilleri and Winskell [10], named CCS<sup>CW</sup> in the sequel. CCS<sup>CW</sup> provides a *prioritised choice* operator  $Q \stackrel{def}{=} \alpha_1.Q_1 \stackrel{}{\Rightarrow} \alpha_2.Q_2$  called "prisum" that gives the action  $\alpha_1$  priority over  $\alpha_2$  and blocks the second prefix  $\alpha_2$  in case  $\alpha_1 = \alpha_2$ . Such priorities help us resolve the issue. The problem with non-determinism originates from the preemptive behaviour of the write-read choice w.S' + r.S''. It permits the read and the write actions to compete with each other for the next state of the process

S. In data-flow and functional programming, we resolve the conflict by making the write action take precedence over the read one. First, the data-flow variable must be written by the *producer* process, then it can be read by the *consumers*, if any. This "write-before-read" scheduling policy is a *prioritised choice*, represented in  $CCS^{CW}$  as  $S \stackrel{def}{=} w.S' \not > r.S''$  in which the prisum  $\not >$  operator enforces a precedence from left to right. The store S is willing to engage in a read action r (to the right of  $\not >$ ) only if the environment does not offer a write w (on the left of  $\not >$ ) at the same time, concurrently.

Another important study in the endeavour of adding priorities to CCS is the work of Phillips [33]. In Phillips' extension of CCS with priority guards, referred to as CCS<sup>Ph</sup>, the previous behavior is expressed by  $S \stackrel{\text{def}}{=} \{\}: w. S' + \{w\}: r. S''$ , where each action is pre-annotated by a set of actions that take priority. Process S will synchronise with the reader process R to move to the error state S'' with guarded action  $\{w\}: r$ . The priority guard  $\{w\}$  states that this can only happen if the environment does not offer a write w. Otherwise, the only action available is  $\{\}: w$  which makes the cell move into state S'. The write action has an empty guard and so cannot be blocked. If both  $\overline{w}$  and  $\overline{r}$  are offered concurrently, then only the higher-prioritised write action  $\overline{w}$  will go ahead.

The standard way to implement this scheduling in prioritised CCS is via a transition relation that keeps track of blocking information. In line with the approaches of [10, 33, 36], let us write  $P \xrightarrow{\alpha}_{H} P'$  to denote that process P can engage in an action  $\alpha$  to continue as P', provided the concurrent environment does not offer any action from H. We will call H the blocking set of the transition. In Plotkin's SOS, the (selected) rules for prefix and choice in CCS<sup>CW</sup> are the following<sup>4</sup>:

$$\frac{}{\alpha.P \xrightarrow{\alpha}_{\{\}} P} (Act) \quad \frac{P \xrightarrow{\alpha}_{H} P'}{P \not\ni Q \xrightarrow{\alpha}_{L} P'} (PriSum_{1}) \quad \frac{Q \xrightarrow{\alpha}_{H} Q' \qquad \tau, \alpha \notin \mathsf{iA}(P)}{P \not\ni Q \xrightarrow{\alpha}_{H \cup \mathsf{iA}(P)} Q'} (PriSum_{2})$$

where iA(P) (defined formally later) informally represents the set of initial actions of P that are offered by P in some environment and  $\Rightarrow$  is the priority sum defined by  $CCS^{CW}$ . From rule (Act), individual prefixes generate transitions without any blocking constraints. Rules  $(PriSum_1)$  and  $(PriSum_2)$  describe how the transitions of a choice  $P \Rightarrow Q$  are obtained from the transitions of P and of P and of P more in details, rule  $(PriSum_1)$  lets all transitions of the higher-prioritised process P pass through to form a transition of the choice  $P \Rightarrow Q$  without restriction. This is different for P0, where, according to rule  $PriSum_2$ 0, an action of the lower-prioritised process P1 can only be executed, and thus P1 preempted by it, if P2 does not have an initial silent action and if it does not offer the same action P2, already. All initial actions of P3 are added to the blocking set P3 transition. This will ensure that these get blocked in concurrent contexts in which P3 has a communication partner. The blocking sets take effect in the rules for parallel composition displayed below:

$$\frac{P_1 \xrightarrow{\alpha_1}_{H_1} P_1' \quad H_1 \cap \overline{\mathsf{iA}}(P_2) = \{\}}{P_1 \mid P_2 \xrightarrow{\alpha_1}_{H} P_1' \mid P_2} (Par_1) \qquad \frac{P_2 \xrightarrow{\alpha_2}_{H_2} P_2' \quad H_2 \cap \overline{\mathsf{iA}}(P_1) = \{\}}{P_1 \mid P_2 \xrightarrow{\alpha_2}_{H_2} P_1 \mid P_2'} (Par_2)$$

<sup>&</sup>lt;sup>4</sup> For the fragment of CCS<sup>CW</sup> that we are considering, the precise connection is the following:  $\vdash_R P \xrightarrow{\alpha} P'$  in CCS<sup>CW</sup> iff R is a subset of *out*-actions and there is a subset L of *in*-actions such that  $P \xrightarrow{\alpha}_H P'$  and either  $\alpha$  is an *out*-action and  $H = \{\}$  or  $\alpha$  is an *in*-action with  $\overline{\alpha} \in R$  and  $R \cap \overline{H} = \{\}$ .

#### XX:20 Strong Priority and Determinacy in Timed CCS

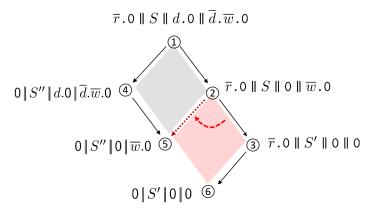

**Figure 5** Prioritised Choice. The read-write data race on memory cell S resolved by scheduling priority. The write takes precedence over the read, indicated by the dashed arrow. This removes the top left transition labelled  $\tau$ :{w}. Since there is only one execution path, the system is deterministic. The continuations states  $S' \stackrel{\text{def}}{=} r.S'$  and  $S'' \stackrel{\text{def}}{=} r.S'' + e.S''$  of the cell are the same as in Fig. 4.

$$\frac{P_1 \xrightarrow{\alpha_1}_{H_1} P_1' \qquad P_2 \xrightarrow{\alpha_2}_{H_2} P_2' \qquad \alpha_1 = \overline{\alpha}_2 \qquad H_1 \cap \overline{\mathsf{iA}}(P_2) = \{\} \qquad H_2 \cap \overline{\mathsf{iA}}(P_1) = \{\}}{P_1 \mid P_2 \xrightarrow{\tau}_{H_1 \cup H_2} P_1' \mid P_2'} (Par_3)$$

More in details, rules  $(Par_i)$  for  $i \in \{1,2\}$  define an action  $\alpha_i$  by  $P_1 \mid P_2$  offered in one of the sub-processes  $P_i$ . Such is enabled if the competing concurrent process  $P_{3-i}$  has no initial action that is in the blocking set  $H_i$  of action  $\alpha_i$ , i.e. when the condition  $H_i \cap \overline{\mathsf{IA}}(P_{3-i}) = \{\}$  is satisfied. Rule  $(Par_3)$  implements the synchronisation between an action  $\alpha_1$  in  $P_1$  and the associated matching action  $\alpha_2 = \overline{\alpha}_1$ , originating from  $P_2$ . The side-condition is the same: each process  $P_i$  only accepts the matching action call from  $P_{3-i}$  if it does not offer any action that blocks action  $\alpha_i$ . Let us see how this blocking semantics works for our running example of a write-once memory cell, where we now enforce a write-before-read priority on the empty cell  $S: S \stackrel{\text{def}}{=} w.S' \not \Rightarrow r.S''$  and  $S' \stackrel{\text{def}}{=} r.S'$  and  $S'' \stackrel{\text{def}}{=} r.S'' + e.S''$ . The cell S has two potential transitions that can be fired, namely

$$\frac{\overline{w.S' \xrightarrow{w}_{\{\}} S'}}{S \xrightarrow{w}_{\{\}} S'} \frac{(Act)}{(PriSum_1)} \quad or \quad \frac{\overline{r.S'' \xrightarrow{r}_{\{\}} S''}}{S \xrightarrow{r}_{\{w\}} S''} \frac{(Act)}{\tau, r \notin iA(w.S')}}{S \xrightarrow{r}_{\{w\}} S''} (PriSum_2)$$