# A generic framework to develop and verify security mechanisms at the microarchitectural level: application to control-flow integrity

Matthieu Baty, Pierre Wilke, Guillaume Hiet, Arnaud Fontaine, Alix Trieu

# ▶ To cite this version:

Matthieu Baty, Pierre Wilke, Guillaume Hiet, Arnaud Fontaine, Alix Trieu. A generic framework to develop and verify security mechanisms at the microarchitectural level: application to control-flow integrity. CSF 2023 - 36th IEEE Computer Security Foundations Symposium, Jul 2023, Dubrovnik, France. pp.1-16. hal-04118645

# HAL Id: hal-04118645 https://inria.hal.science/hal-04118645v1

Submitted on 20 Jun 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Copyright

# A generic framework to develop and verify security mechanisms at the microarchitectural level: application to control-flow integrity

Matthieu Baty

Inria, CNRS, University of Rennes

matthieu.baty@inria.fr

Pierre Wilke

CentraleSupélec, Inria, CNRS, University of Rennes

pierre.wilke@centralesupelec.fr

# Guillaume Hiet

CentraleSupélec, Inria, CNRS, University of Rennes guillaume.hiet@centralesupelec.fr

Arnaud Fontaine

ANSSI

arnaud.fontaine@ssi.gouv.fr

Alix Trieu

ANSSI

alix.trieu@ssi.gouv.fr

Abstract—In recent years, the disclosure of several significant security vulnerabilities has revealed the trust put in some presumed security properties of commonplace hardware to be misplaced. We propose to design hardware systems with security mechanisms, together with a formal statement of the security properties obtained, and a machine-checked proof that the hardware security mechanisms indeed implement the sought-for security property.

Formally proving security properties about hardware systems might seem prohibitively complex and expensive. In this paper, we tackle this concern by designing a realistic and accessible methodology on top of the Kôika Hardware Description Language for specifying and proving security properties during hardware development. Our methodology is centered around a verified compiler from high-level and inefficient to work with Kôika models to an equivalent lower-level representation, where side effects are made explicit and reasoning is convenient.

We apply this methodology to a concrete example: the formal specification and implementation of a shadow stack mechanism on an RV32I processor. We prove that this security mechanism is correct, i.e., any illegal modification of a return address does indeed result in the termination of the whole system. Furthermore, we show that this modification of the processor does not impact its behaviour in other, unexpected ways.

Index Terms—RISC-V, Formal Methods, Hardware Verification, Compilation

This work was supported by a grant from the French National Cybersecurity Agency (ANSSI).

# I. INTRODUCTION

Formal methods can be used to build trust in computer systems. The CompCert C compiler [20] or the seL4 microkernel [18] are examples of their successful application to software verification. Formal verification of hardware was historically mostly confined to functional correctness, as exemplified by the formal verification of the floating-point operations in Intel hardware following the discovery of the Pentium FDIV bug [17], or by the verification of protocols, e.g. for cache coherence [31].

However, hardware components also play a fundamental role in establishing security and trust in the whole hardware/-

software stack. Being at the lowest level of the stack, they pose several challenges (e.g. complex interactions with software and difficulty for patching) and open many opportunities (e.g. for providing a sound foundation for software security, protected from modifications incurred by software execution) in terms of security. Formal methods should help with developing a set of formally defined and verified security primitives at the hardware level. Despite this central position in the security foundation of computing platforms, the adoption of formal methods for hardware security is still limited. As stated by several experts of the domain in the 2016 Report on the NSF Workshop on Formal Methods for Security, there is a critical need for "methods to create, analyze, and execute formal hardware security specifications" and "new security mechanisms are needed to ease the creation and verification of higherlevel system security properties" [8]. Establishing security properties at the hardware level is also a mandatory stepping stone towards whole-system guarantees. In this article, we propose a solution to this main challenge: providing a solid, scalable and generic foundation for implementing and proving hardware security mechanisms at the microarchitectural level.

Some promising approaches for formally specifying hardware-based security mechanisms and proving that they enforce some security properties have been proposed in the research community. For example, CHERI [32] is an extended version of the Arm ISA, which includes constructs for finegrained memory protection with capabilities. Recently, the use of these capabilities (the security mechanism) in the Morello architecture was shown to enforce memory protection (the security property) [4], [24]. These properties were proved at the ISA (Instruction Set Architecture) level. However, we aim at reasoning at the microarchitectural level for two reasons. First, the ISA level prevents us from capturing low-level implementation details that may induce vulnerabilities, e.g. side channels. Second, the security properties proved at the ISA level still rely on the correct implementation of this ISA by a microarchitectural model.

Some works in formal methods for hardware verification [1], [6], [15], [21] are based on models of the actual hardware. While this makes proofs easier to come up with, this also opens a possibility for discrepancies between the model and the actual hardware, thus giving a false sense of security.

A way of avoiding this issue would be to reason directly on the model used for production. However, most Hardware Description Languages (HDLs) used in industrial settings are not equipped with formal semantics, and formal proof cannot directly be applied on the models written in these HDLs.

The challenge we tackle in this article is the following: how to provide a solid, scalable and generic foundation for implementing and proving hardware security mechanisms at the microarchitectural level?

This article proposes a realistic and accessible methodology for specifying and proving security properties during hardware development. We base our work on the Kôika language [5], a HDL embedded in the Coq proof assistant. This language comes with a compiler that produces Verilog code, which can be synthesized for FPGA boards. The Kôika project also provides a 4-stage RISC-V processor, among several examples of Kôika models.

The Kôika compiler is formally verified, which means that the compilation of Kôika models down to Verilog preserves their semantics. However, the authors of Kôika do not provide scalable tools for proving non-trivial security properties on Kôika models. Moreover, naive attempts at reasoning directly on complex models written in Kôika, e.g., on a RISC-V processor, lead to prohibitive performance issues due to the large size of the terms manipulated by Coq, among other things.

To overcome these shortcomings, we expand upon the Kôika language. First, we introduce a low-level representation which is better suited to formal reasoning and enables interactive proof on hardware models. We propose a compiler from Kôika models to this low-level representation and prove that this compiler preserves semantics, i.e. properties about the Kôika model can be proved by reasoning about the low-level representation. Then, we develop a library of verified transformation passes over these representations in order to ease reasoning. For instance, we offer transformation passes to exploit hypotheses about the values of some registers at the beginning of a cycle or to replace arithmetic operations with their results when enough of their arguments are known. A mix of transformation passes applications and case analysis is sufficient to discharge the goals we are interested in.

We rely on our methodology to verify that a security mechanism targeting the aforementioned Kôika RISC-V model enforces some security policies. More precisely, we prove that a hardware-based return address shadow stack (the security mechanism) prevents the modification of return addresses (the security property), which guards against arbitrary code execution.

Our contributions can be summarized as follows:

We propose a methodology and a framework based on Kôika to specify and implement security mechanisms and

- the security properties they are supposed to enforce;

- We define a low-level representation for Kôika that is more amenable to verification;

- We design a series of code transformations that simplify the models;

- We showcase this methodology on a hardware-based shadow stack security mechanism, and prove that it indeed enforces the integrity of return addresses, and does not affect the legitimate behaviour of the computer system;

- We synthesize the aforementioned processor equipped with a hardware shadow stack and run it successfully on an FPGA board.

Our contributions have been mechanised in Coq and are available at: https://gitlab.inria.fr/cidre-public/koika-llr.

The rest of this article is organized as follows. Section II introduces the Kôika language [5] and its semantics, showing the challenges that have to be overcome for formal verification. Section III, the main part of this work, introduces our proposed framework and proof methodology. In particular, we detail the modifications we implemented in the Kôika project. Section IV showcases an application of this methodology to the implementation of a verified hardware shadow stack. Section V presents the experimental evaluation of our solution. Section VI position our approach against related work. Section VII discusses limitations and future work, and Section VIII concludes this article.

## II. KÔIKA

Kôika [5] is an open-source formal Hardware Description Language (HDL). Being embedded in Coq, this language provides a sound basis for reasoning about the behaviour of hardware models. Kôika is based on BlueSpec [25], a general-purpose, high-level, non-formal HDL. The distinctive feature of Bluespec, compared to other traditional HDLs such as Verilog or VHDL, is that the model is expressed in rules that should run concurrently, and it is the compiler's duty to automatically generate the control logic that ensures rules do not conflict. This way of describing hardware is particularly convenient for concurrent systems such as pipelined processors.

The Kôika compiler is formally verified and outputs Verilog code. One can thus apply Verilog-compatible tools (e.g., simulators and FPGA bitstream generators) to Kôika models. Efficient simulation is possible using the project's custom simulator "Cuttlesim" [26] directly on Kôika models rather than traditional Verilog simulators. Kôika lends itself better to efficient simulation than Verilog because its form is close to regular software, which allows for the application of standard software optimization techniques.

#### A. The Kôika language

1) Syntax: The syntax of Kôika programs is given by Figure 1. A Kôika program manipulates a set of registers, that form the microarchitectural state. Programs are composed of a set of rules and a schedule that determines the order in

Fig. 1: Syntax of Kôika models

which rules should appear to execute. The rules are atomic actions describing transitions from one clock cycle to the next. Each rule approximately maps to one stage of a pipelined processor. Note that the hardware circuit will execute the rules concurrently during one single cycle, but the schedule helps to define their semantics as if they were executed sequentially.

Kôika actions produce values val, which can be bitvectors, structures, arrays or enums (see Figure 1). Each of these values is given a type, which describes respectively the size of the bitvector, the layout of the structure, the set of values of the enum and the type and number of elements of the array.

Actions can be constant values val, variables x, skip actions which do nothing, read of registers read r, write of values to registers write r a, variables bindings with the let .. in .. construct, variable assignments with the x:=a construct, conditional expressions with the construct if .. then .. else ..., function calls (f(..)), sequences of actions and abort actions which always fail. Function calls can be internal (defined themselves in terms of actions) or external (their semantics is given by global parameters of the model, and can be used e.g. to model the external RAM).

2) Semantics: The successful executions of actions produce a value alongside a log storing a sequence of read and write events on registers. The semantics is given in Figure 2, by way of a set of judgments of the form  $\Gamma \vdash (l,a) \downarrow_L^\sigma (l',v,\Gamma')$ , where  $\Gamma$  is an environment for let-bound variables, l is a "rule log", i.e. a log of events that occurred so far during the execution of the current rule, a is the action that is to be executed; and l' is an updated rule log, v is the value computed by action a and  $\Gamma'$  is an updated environment. The environment  $\Gamma$  is a stack of pairs (x,v) where x is a variable name and v is the value associated with that variable. It is updated in particular in rule BIND. We first add a binding to the environment  $((x,v_1) :: \Gamma')$ , and finally remove it when the variable goes out of scope (t1  $\Gamma''$ ), where t1 is the

Semantics of actions:

$$\begin{array}{ll} \text{CST} & \text{VAR} \\ \hline v \in \textit{val} & \Gamma(x) = v \\ \hline \Gamma \vdash (l,v) \downarrow (l,v,\Gamma) & \Gamma \vdash (l,x) \downarrow (l,v,\Gamma) \\ \hline \\ \text{BIND} & \Gamma \vdash (l,a_1) \downarrow (l',v_1,\Gamma') \\ \hline (x,v_1) :: \Gamma' \vdash (l',a_2) \downarrow (l'',v,\Gamma'') \\ \hline \Gamma \vdash (l, \text{let } x = a_1 \text{ in } a_2) \downarrow (l'',v,\text{t1 } \Gamma'') \\ \hline \\ \text{ASSIGN} & \Gamma \vdash (l,a) \downarrow (l',v,\Gamma') \\ \hline \Gamma \vdash (l,x := a) \downarrow (l',tt,\Gamma'[x \mapsto v]) \\ \hline \\ \text{COND-TRUE} & \Gamma \vdash (l,a_1) \downarrow (l',[\text{true}],\Gamma') \\ \hline \Gamma' \vdash (l',a_2) \downarrow (l'',v,\Gamma'') \\ \hline \\ \hline \\ \text{COND-FALSE} & \Gamma \vdash (l,a_1) \downarrow (l',[\text{false}],\Gamma') \\ \hline \Gamma' \vdash (l',a_3) \downarrow (l'',v,\Gamma'') \\ \hline \\ \hline \\ \text{COND-FALSE} & \Gamma \vdash (l,a_1) \downarrow (l',[\text{false}],\Gamma') \\ \hline \\ \Gamma \vdash (l,\text{if } a_1 \text{ then } a_2 \text{ else } a_3) \downarrow (l'',v,\Gamma'') \\ \hline \\ \hline \\ \text{FUNCALL} & \Gamma_0 \vdash (l_0,a_1) \downarrow (l_1,v_1,\Gamma_1) \\ \hline \\ \dots & \Gamma_{n-1} \vdash (l_{n-1},a_n) \downarrow (l_n,v_n,\Gamma_n) \\ \hline \\ \text{zip}(\text{args } f,[v_1,\dots,v_n]) \vdash (l_n,\text{body } f) \downarrow (l',v,\Gamma') \\ \hline \\ \hline \\ \hline \\ \Gamma \vdash (l,a_1) \downarrow (l',v_1,\Gamma') & \Gamma' \vdash (l',a_2) \downarrow (l'',v,\Gamma'') \\ \hline \\ \text{SEQ} & \Gamma \vdash (l,a_1) \downarrow (l',v_1,\Gamma') & \Gamma' \vdash (l',a_2) \downarrow (l'',v,\Gamma'') \\ \hline \\ \text{READ} & \text{may\_read}(L,r) \\ \hline \\ \hline \\ \hline \\ \Gamma \vdash (l,\text{read } r) \downarrow (l++[\text{rd}(r)],\sigma(r),\Gamma) \\ \hline \end{array}$$

$$\frac{\text{WRITE}}{\Gamma \vdash (l,a) \downarrow (l',v,\Gamma')} \quad \text{may\_write}(L,l',r)}{\Gamma \vdash (l, \textbf{write} \ r \ a) \downarrow (l'++\lceil \text{wr}(r,v) \rceil, tt,\Gamma')}$$

$$\begin{split} & \texttt{may\_read}(L,r) & \triangleq & \texttt{wr}(r,*) \not\in L \\ & \texttt{may\_write}(L,l,r) & \triangleq & \texttt{wr}(r,*) \not\in (L++l) \end{split}$$

Semantics of a schedule:

$$\frac{\Gamma_0 \vdash (l_0, a) \downarrow_L^{\sigma} (l, v, \Gamma) \qquad (L + + l, sch) \Downarrow L'}{(L, a :: sch) \Downarrow L'}$$

$$\frac{\Gamma_0 \vdash (l_0, a) \not\downarrow \frac{\sigma}{L} \qquad (L, sch) \Downarrow L'}{(L, a :: sch) \Downarrow L'}$$

$$\frac{(L, \Gamma) \Downarrow L}{(L, \Gamma) \Downarrow L}$$

Fig. 2: Semantics of Kôika actions and schedules

function that returns a list's tail. The rule for function calls creates a new environment for the called function with the zip function that combines two lists into a list of pairs. args f and body f give, respectively, the names of the arguments and the body of a function f. Moreover, these judgments use two components that are never updated in the semantics of actions: an environment  $\sigma$  that gives the value of each register at the beginning of the cycle, and a "schedule log" L that contains the read and write events produced by previous rules (as defined by the schedule) during the same cycle. For the sake of clarity, when there is no ambiguity about which  $\sigma$ and L should be used, we simply write  $\downarrow$  instead of the full  $\downarrow_I^{\sigma}$ . The events in the schedule log and rule log are of the form rd(r) or wr(r, v), denoting respectively a read on register r, and a write of value v on register r. Operator ++ is the concatenation of lists. The separation between the schedule log and the rule log is necessary because the effects of rules may be cancelled in the presence of conflicts between register reads and register writes. More precisely, a conflict happens in two situations: read-after-write (see rule READ in Figure 2), i.e. when a read on a register happens after a write on the same register by a previous rule (as defined by the scheduler); or write-after-write (see rule WRITE in Figure 2), i.e. when a write happens after another write on the same register by a previous rule or the same rule. The conditions under which reads and writes are permitted are decided by the may read and may write functions. Note that reading a register after a write has occurred within the same rule is allowed, and results in reading the value of the register at the beginning of the cycle.

The *read-after-write* conflict exists in order to respect the One-Rule-At-A-Time (ORAAT) semantics, i.e. the parallel execution of several rules is allowed if it cannot be distinguished from a sequential execution of these rules, in the order described by the user-provided schedule. Consider the rules A: **write** r1 0 and B: **read** r1, and assume register r1 initially holds the value 1. With the schedule [A; B], rules A and B cannot run concurrently. On the other hand, with the schedule [B; A], the two rules may execute concurrently and will result in the register r1 having value 0.

The write-after-write conflict is not necessary to satisfy ORAAT, but is rather a design choice of the authors of Kôika, who consider that overwriting registers by shadowing them is an antipattern. For instance, the rule C: write r1 1; write r2 2; write r1 3 would write twice to the same register.

In the bottom of Figure 2, we introduce three rules that describe the semantics of a schedule, built on top of the semantics of actions. We run each rule with an initially empty environment  $\Gamma_0$  and an empty rule  $\log l_0$ . We write  $\Gamma \vdash (l,a) \not\downarrow$  to denote that the execution of action a fails, i.e. does not result in a triple  $(l', v, \Gamma')$ , e.g. because of a conflict. Conflicts result in the cancellation of all the effects of the conflicting rule. In the example of rule C, this means that not only none of the writes to  $r_1$  actually happen, but the write to  $r_2$  is also ignored, because rules are considered to be atomic, i.e. execute entirely

or not at all.

These conflicts have to be detected at run-time, because the conflicting register reads or writes may be nested inside conditional expressions, and thus cannot be decided during compilation.

Kôika's compiler takes care of introducing the appropriate control logic in the generated circuit, in order to run rules in parallel, and only *commit* each rule's effects when there are no conflicts. Combined with scheduling, this behavior can be used to simplify the definition of pipelined systems: conflicts help determine how to pipeline a model without the user needing to give all the details explicitly.

Importantly, the presence of a conflict in a rule does not mean that something is wrong with the rule. For instance, in the following rule, a conflict occurs only if both a and b are equal to 0 at the beginning of a cycle (write-after-write on x).

```

Rule A:

if (read a == 0) then write x 0;

if (read b == 0) then write x 1.

```

However, in all other situations, the rule runs. The set of rules which end up running in a given cycle depends on the initial value of the registers. These values are stored in an association map which we call the environment. The constant changes in the environment throughout the execution of a model give rise to a dynamic system. For instance, in the context of pipelined systems such as processors, where rules correspond to individual stages of the pipeline, rule cancellations can represent stalls in the pipeline.

Finally, the semantics of a cycle is given by a function interp\_cycle, taking as parameters a schedule sch and an initial state for registers  $\sigma$ , and producing as a result a new state for registers. For instance interp\_cycle(sch,  $\sigma$ )(r) is the value of register r at the end of a cycle.

3) Ports: In the language we described so far, it is not possible to pass information from one rule to another during a single cycle, because one rule cannot read a value written by a previous rule. However, since this impacts performance dramatically, it is possible in Kôika to forward data from one rule to another through the use of ports. Ports (see Figure 3) are simply 0 or 1 and correspond loosely to versions of the associated register across time. Reads and writes are associated with a specific port. One can only read the value of a register on port 0 if no write has occurred on that register in the current cycle, but we can read on port 1 if no write has occurred on port 1. If a write has occurred on port 0, a read on port 1 will retrieve the value that was written, no matter whether the read and write occur in the same rule or successively.

The conflicts between reads and writes is now more subtle: reads on some port p are only allowed if no write has already occurred in a previous rule on any port  $p' \geq p$ . Writes on some port p are allowed neither after writes on ports  $p' \geq p$  nor after reads on ports p' > p. This last part means that, for example, once a read on port 1 occurred, we cannot have a write on port 1.

Fig. 3: Syntax and semantics of Kôika models with added ports

```

Registers : {r, r0, ..., r20}.

Rule tick :

write r0 0;

write r1 0;

...

write r20 0;

write r (read r + 1).

Schedule : [tick].

```

Fig. 4: A simple model with many independent writes

The notion of ports is crucial for the performance of hardware designs, but it adds some complexity to the semantics of Kôika. Ports will be ignored in the rest of this article for the sake of simplicity. However, they are fully supported in the implementation.

# B. Limitations

Although it is possible to prove some properties about the behavior of some simple Kôika circuits using the language in its current state, this becomes impractical as the models grow in complexity, for performance reasons. This issue can't be pinned on a single cause. Rather, it is the consequence of design choices in the Kôika language and of properties of the Coq language, in which the reasoning is carried out.

First, the semantics of Kôika is inherently non-modular. Consider for instance a single register write inside one of the rules of a Kôika model. In order to determine whether this register write actually occurs, one needs to check whether this rule is actually run or will be cancelled for the current cycle. Cancellation conditions, which depend on the evaluation of all the previous rules, can get quite involved. Not only is this tricky to reason with, it can also degrade the performance of proofs involving complex models.

Another limiting factor is related to the techniques for proofs by computation in Coq. When considering the behavior of programs with concrete inputs, efficient Coq tactics for complete normalization such as cbv or vm\_compute can be applied. However, for programs whose inputs are not all known, this approach amounts to complete symbolic execution

and leads all too often to a combinatorial explosion. On the other hand, tactics such as cbn or simpl are an apt tool for reasoning about program whose inputs are at least partially abstract. Indeed, these tactics can be parameterized to try and avoid running into the performance traps that would block cbv or vm\_compute. However, the existing level of control for these tactics is not sufficient for our purposes.

We introduce an example of a Kôika model in Figure 4. It contains a single rule with a sequence of writes, each of which targets a different register. The model contains a total of twenty-one registers. Real-life examples usually contain more registers and actions than this, and include more complex constructs (e.g. conditionals and let-defined variables). Note that there can't possibly be a conflict in this rule as all writes target different registers.

Consider the following property about this model, which says that register the initial and final values of r are distinct:

$$interp\_cycle([tick], \sigma)(r) \neq \sigma(r)$$

It should be rather easy to demonstrate. In fact, the first twenty writes can safely be ignored, as they don't have any influence on the final value of r, which is the only register considered in the property. The value of r is incremented on each cycle, which means that the property is trivially true.

However, there is no straightforward way of implementing this proof using vanilla Kôika and Coq. Even for such a simple program and property, we did not manage to find a proof which terminates in less than twenty minutes. This problem only gets worse when considering larger models with more registers, actions and complex constructs.

We present our methodology to find a way around Coq's and Kôika's performance issues when reasoning on large models in Section III.

#### III. PROVING SEMANTIC PROPERTIES ON KÔIKA MODELS

In order to circumvent the limitations exposed earlier, we propose a low-level representation which makes all the computations about conflicts and rule cancellation explicit. While this produces rather large terms, reifying these computations makes it possible to simplify and store them. This way, for instance, the decision of whether a rule is cancelled is computed once for all, rather than each time we need to reason about the value of any register.

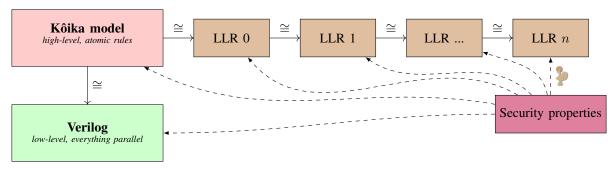

An overview of our methodology for proving security properties on Kôika models is given in Figure 5. In this figure, starting from the Kôika model, we obtain a first low-level representation (LLR) from a verified compiler that we describe in Section III-B. Then, this LLR0 is transformed into a sequence of LLRs, each simpler to reason about than the previous one. Applying these transformations is part of the proof development. It can be done either manually or through tactics which automatically apply appropriate passes depending on the form of the goal and of the hypotheses. Users can easily define additional tactics tailored to their work using Coq's built-in facilities. We describe these transformations in

Fig. 5: Overall structure of our proofs on Kôika models

```

\begin{array}{llll} \text{Low-Level Actions} \\ \textit{lla} & ::= & v \in \textit{val} \mid \textit{vx} \mid r \mid \triangleright \textit{lla} \mid \textit{lla} \bowtie \textit{lla} \\ & \mid & \textit{lla} ? \textit{lla} : \textit{lla} \\ \text{Low-Level Representation} \\ \textit{llr} & ::= & \{V: \mathbb{N} \hookrightarrow \textit{lla} \; ; \; R: \mathtt{reg} \rightarrow \mathbb{N}\} \end{array}

```

Semantics of Low-Level Actions

Fig. 6: Syntax and semantics of low-level actions

Section III-D. Each simplification pass is formally verified, hence the proofs we carry out on the transformed LLRs also hold the initial LLR. Finally, the LLR n is simple enough that we can carry out the proof of our security property directly. Because every step in our methodology is proven to preserve semantics, the security property we prove on LLR n also holds for LLR n-1, all the way up to LLR n0, but also for the Kôika model. From Kôika's compiler correctness, we have that the security property holds on the Verilog code that will be simulated or synthesized.

We propose a compiler from Kôika models to these lowerlevel representations (LLR) and prove that this compiler preserves semantics, i.e. properties about the Kôika model can be proved by reasoning about the LLR. Then, we apply a series of verified simplifications that depends on the specific goal we try to prove.

# A. A low-level representation

The type of the low-level representation we target is given in Figure 6. A low-level representation (LLR) is composed of a variable map V, which maps variable identifiers to low-level actions, and a mapping R from register names to variable identifiers. R[r] holds the identifier of the variable that corresponds to the value of register r after one clock

cycle, whose contents can be recovered from the variable map V.

A low-level action is a static counterpart to Kôika actions. These low-level actions can be constant values v, variables vx, registers r, unary operations  $\triangleright lla$ , binary operations  $lla\bowtie lla$ , or conditional expressions lla ? lla : lla, as illustrated in Figure 6. The main difference, compared with Kôika actions, is that register read and write operations have disappeared, and actions are now free of side effects.

The low-level action associated with a variable x in our low-level representation is allowed to reference only variables whose identifier y is strictly below x. This is a well-formedness condition that ensures that there is no cyclic dependency between variables. Hence, the evaluation of these expressions terminates. We can therefore define the evaluation function  $[lla]_{\sigma}^{llr}$ , which evaluates a low-level action lla into a value. It is parameterized by a low-level representation llr (for resolving variables) and an environment  $\sigma$  (that holds the initial values of registers). The definition is given in Figure 6.

Let us consider for instance the action  $\mathbf{a}+v7$ . Its evaluation  $[\![\mathbf{a}+v7]\!]_{\sigma}^{llr}$  would be decomposed into  $[\![\mathbf{a}]\!]_{\sigma}^{llr}+[\![v7]\!]_{\sigma}^{llr}$ . The first part  $[\![\mathbf{a}]\!]_{\sigma}^{llr}$ , i.e. the evaluation of register  $\mathbf{a}$  will simply be a lookup into the environment:  $\sigma(\mathbf{a})$ . The second part will lookup variable v7 in the LLR, and then recursively apply the evaluation function on the low-level action associated with v7.

Although the representation introduced in this paper is tailored to languages of the BlueSpec family, similar representations can be more generally applied for controlling partial interpretation in Coq. Indeed, as things stand, there are situations that Coq's interpretation tactics are unable to handle conveniently, as detailed in II-B.

# B. From Kôika rules to a Low-Level Representation

Our first objective is to build a low-level representation from a Kôika model. We treat each rule in the Kôika model in the order specified by the schedule. For each rule, we perform a form of abstract interpretation on the action, as shown in the definition of K2L in Figure 7. The parameters of the compiler are: 1) the Kôika action a to be compiled; 2) a projection  $\Pi: \operatorname{Reg} + \operatorname{Var} \to \mathbb{N}$  that maps Kôika variables and registers to LLR variable identifiers; 3) a mapping  $V: \mathbb{N} \to lla$  from variable identifiers (natural numbers) to low-level actions; 4) the next fresh variable identifier f; 5) the current path

condition P, as a low-level action; 6) an abstract schedule  $\log L^{\sharp}$  and 7) an abstract rule  $\log l^{\sharp}$ . The result of compiling an action with K2L is a 6-tuple  $(lla, \Pi', V', f', F, l'^{\sharp})$  where lla is the low-level action corresponding to the input Kôika action,  $\Pi'$ , V', f' and  $l'^{\sharp}$  are the updated values of  $\Pi$ , V, f and  $l^{\sharp}$ , and F is the action's failure condition, i.e. a low-level action expressing the conditions under which the current action will fail. The abstract logs record all the potential read and write events, together with a low-level action representing the condition under which these read and write events actually occurred. More precisely, abstract logs  $(L^{\sharp} \text{ and } l^{\sharp})$  are of type  $\{\text{wr}, \text{rd}\} \times \text{Reg} \to lla$ . For example,  $l^{\sharp}(\mathbf{wr},r)$  is a low-level action that represents the conditions under which a write has occurred on register r. The logs are updated when compiling register reads and writes (see Figure 7): the notation  $l^{\sharp}[(k,r) \xrightarrow{\vee} P]$  means the mapping  $l^{\sharp}$  updated for key (k,r), where the new value is  $old \vee P$ , where old is the old value of the mapping for that key. The may read<sup>‡</sup> and may write<sup>‡</sup> are the abstract counterpart to the may\_read and may\_write in Kôika semantics. For instance,  $may\_read(L, r) = wr(r, *) \notin (L)$  (see Figure 1). The abstract version may\_read $^{\sharp}(L^{\sharp},r)$  is defined as the low-level action  $\neg L^{\sharp}(wr, r)$ . The condition under which a read action fails is exactly the negation of the result of the may read function. For an action write r a, it is the logical disjunction between the negation of may\_write<sup>#</sup> and the failure condition associated with action a. The projection  $\Pi$  maps Kôika variables and registers to LLR variable identifiers. More precisely, for each register r,  $\Pi(r)$  corresponds to the variable that will hold the final value of register r, at the end of the current cycle. Initially,  $\Pi(r)$  maps to a variable that only contains the lowlevel action r. When compiling a register write (see Figure 7), the projection  $\Pi$  is updated so that  $\Pi(r)$  points to the new value, in accordance with the semantics of Kôika.

One of the most involved cases for K2L is that of conditional expressions. We construct a low-level representation for each case of the conditional expression: one when the condition evaluates to true, another when the condition evaluates to false. This is materialized by the two recursive calls to K2L, one with the path condition augmented with the condition, the other with its negation. These two calls generate two distinct projections  $\Pi_{tb}$  and  $\Pi_{fb}$ , that we merge using the binary operator  $\bigcup_{V,f}^{v_{cond}}$ . For every Kôika variable or register k, suppose  $\Pi_1(k)=v_1$  and  $\Pi_2(k)=v_2$ , then  $\Pi_1 \bigcup_{V,f}^{v_{cond}} \Pi_2$  will be a triple  $(V',\Pi_r,f')$  such that  $\Pi_r(k)=n$  and  $\llbracket n \rrbracket_\sigma^{V'} = \llbracket v_{cond} ? v_1 : v_2 \rrbracket_\sigma^{V'}$ . For instance, let us consider the first conditional expression in rule r1 from Figure 8a. Recursively analyzing the then and else branches yield two different LLRs: one when read a == 0 holds and register a receives the value 1, the other where register a keeps its previous value. The merged LLR will associate to register a the low-level action (a == 0)? 1: a.

Next, depending on whether conflicts occur or not, the effect of rules are discarded or applied. The function  $K2L^{sched}$  compiles a Kôika schedule into a LLR. Each rule is treated

```

K2L(a,\Pi,V,f,P,L^{\sharp},l^{\sharp}) =

match a with

v \to (v, \Pi, V, f, \mathtt{false}, l^{\sharp})

vx \to \mathbf{let}\ v = \Pi(vx)\ \mathbf{in}\ (v, \Pi, V, f, \mathtt{false}, l^{\sharp})

read r \to \mathbf{let} \ v = \Pi(r) \ \mathbf{in}

let mr = \text{may\_read}^{\sharp}(L^{\sharp}, r) in

(v, \Pi, V, f, \neg mr, l^{\sharp}[(\mathsf{rd}, r) \stackrel{\vee}{\mapsto} P])

write r \ a \rightarrow

let (lla, \Pi, V, f, F_a, l^{\sharp}) =

K2L(a,\Pi,V,f,P,L^{\sharp},l^{\sharp}) in

let mw = \text{may\_write}^{\sharp}(L^{\sharp}, l^{\sharp}, r) in

let (V,\Pi,f)=(V[f\mapsto lla],\Pi'[r\mapsto f],f+1) in

(\perp, \Pi, V, f, F_a \vee \neg mw, l^{\sharp}[(\mathtt{wr}, r) \stackrel{\vee}{\mapsto} P])

if c then ta else fa \rightarrow

let (lla_{cond}, \Pi, V, f, F_{cond}, l^{\sharp}) =

K2L(c,\Pi,V,f,P,L^{\sharp},l^{\sharp}) in

let (v_{cond}, f) = (f, f + 1) in

let V = V[v_{cond} \mapsto lla_{cond}] in

let (lla_{tb}, \Pi_{tb}, V, f, F_{tb}, l^{\sharp}) =

K2L(ta, \Pi, V, f, P \wedge v_{cond}, L^{\sharp}, l^{\sharp}) in

let (lla_{fb}, \Pi_{fb}, V, f, F_{fb}, l^{\sharp}) =

K2L(fa, \Pi, V, f, P \land \neg v_{cond}, L^{\sharp}, l^{\sharp}) in

let (\Pi_{merge}, V, f) = \Pi_{tb} \bigcup_{V, f}^{v_{cond}} \Pi_{fb} in

(lla_{cond}~?~lla_{tb}~:~lla_{fb}, \Pi_{merge}, V, f,

F_{cond} \vee (lla_{cond} ? F_{tb} : F_{fb}), l^{\sharp})

x := a \rightarrow

let (lla, \Pi, V, f, F, l^{\sharp}) =

K2L(a,\Pi,V,f,P,L^{\sharp},l^{\sharp}) in

let (\Pi, V) = (\Pi[x \mapsto f], V[f \mapsto lla]) in

(\perp, \Pi, V, f+1, F, l^{\sharp})

let x = a \text{ in } body \rightarrow

let (lla, \Pi, V, f, F_a, l^{\sharp}) =

K2L(a,\Pi,V,f,P,L^{\sharp},l^{\sharp}) in

let (\Pi, V) = (\Pi[x \mapsto f], V[f \mapsto lla) in

let (lla_{body}, \Pi, V, f, F_{body}, l^{\sharp}) =

K2L(body,\Pi,V,f+1,P,L^{\sharp},l^{\sharp}) in

(lla_{body}, \Pi[x \mapsto \bot], V, f, F_a \vee F\_body, l^{\sharp})

K2L^{sched}(s,\Pi,V,f,L^{\sharp}) =

match s with

[] \rightarrow (\Pi, V, f, L^{\sharp})

r::s\to

let (\_,\Pi',V,f,F_r,l^{\sharp}) =

K2L(r,\Pi,V,f,\mathsf{true},L^{\sharp},l_0^{\sharp}) in

let (v_{conflict}, f) = (f, f + 1) in

let V = V[v_{conflict} \mapsto F_r] in

K2L^{P}(s) =

let (\Pi, V, \_, \_) = K2L^{sched}(s, \Pi_0, V_0, 1, L_0^{\sharp}) in

\{R := \operatorname{fun} r \Rightarrow \Pi(r); V := V\}

```

Fig. 7: The Kôika to LLR compiler

sequentially. For each rule, we call K2L with the current projection  $\Pi$  ant the current set of variables V, the current abstract schedule  $\log L^{\sharp}$  and an empty initial rule  $\log l_0^{\sharp}$ . The failure condition  $F_r$  gives us the condition under which the rule failed. Like in the conditional expression case, we need to merge the projections using  $\bigcup_{V,f}^{v_{conflict}}$ . We also need to patch the abstract schedule  $\log L_{merge}^{\sharp}$  as described in Figure 7 so that the condition under which a read or write occurred is the disjunction of whether it already occurred in the previous schedule  $\log L^{\sharp}$  and whether it occurred in the new rule  $\log l^{\sharp}$ , while not having a conflict. This step was not needed in the if-then-else case because we injected the condition (or its negation) in the path condition, which we cannot do here because the failure condition is the result of the compiler itself.

Figures 8b and 8c illustrate a complete example of compiling a Kôika schedule into a LLR. Initially, we have one variable for each of the three registers a, b and c. The letbound variable x in rule r1 gives rise to v4 in the LLR, whose value is v2, the initial value of register b. The conditions of if-then-else actions also produce variables (v5, v8 and v13 in our example). For each register write, a variable is created that contains the low-level action being written (v6, v9 and v14), and yet another variable is created that contains the new value of the register, often an if-then-else low-level action dependent on the path condition that led us to the write (v7, v10, andv15). At the end of rule r1, v11 contains the rule's failure condition, i.e.  $v8 \wedge v5$ , i.e. "there have been two writes on a"; and v12 contains the value of register a after rule r1: "if the rule fails, the value of a is the same as at the beginning of the cycle, otherwise it is the value after the second if". Similarly, v16 contains the failure condition for rule r2: "the rule fails if a write occurred in this rule (condition v13) and a write occurred in rule r1 ( $\neg v11 \land (v5 \lor v8)$ , i.e. rule r1 did not fail and one of the writes occurred)".

# C. Correctness of the Kôika to LLR compiler

In order to reason on the LLR, we must ensure that our compiler is correct. This section walks through a series of definitions and lemmas that culminate in the proof of Theorem 2, which enables to reason about a LLR to obtain properties about a Kôika model.

We first define a relation  $\stackrel{log}{\sim}$  between a concrete and an abstract log, which establishes that a read or write event occurs in the concrete log if and only if the condition associated to that event in the abstract log evaluates to true.

$$\begin{array}{l} L \overset{log}{\sim}_V L^{\sharp} \triangleq \\ \left\{ \begin{array}{l} \forall r, \ \operatorname{wr}(r,*) \in L \iff [\![L^{\sharp}(\operatorname{wr},r)]\!]_{\sigma}^V = \operatorname{true} \\ \forall r, \ \operatorname{rd}(r) \in L \iff [\![L^{\sharp}(\operatorname{rd},r)]\!]_{\sigma}^V = \operatorname{true} \end{array} \right. \end{array}$$

We also define a relation  $\overset{reg}{\sim}$  between a concrete log and a

We also define a relation  $\stackrel{reg}{\sim}$  between a concrete log and a LLR. This relation states that the projection  $\Pi$  sends registers to LLR variables that evaluate the same as performing a read on that register in a Kôika action. This is captured by the do\_read $(l,\sigma,r)$  function, which returns a value v if  $\operatorname{wr}(r,v) \in l$ , or  $\sigma(r)$  if no such write occurred.

$$\begin{array}{l} l \overset{reg}{\sim} (\Pi, V) \triangleq \\ \forall r, \ \exists n, \ \Pi(r) = n \wedge [\![ n ]\!]^V_\sigma = \texttt{do\_read}(l, \sigma, r) \end{array}$$

We now define a matching relation between Kôika states  $(\Gamma, L, l)$  (variable environment, schedule log and rule log) and LLR states  $(V, L^{\sharp}, l^{\sharp})$  (variable mapping, abstract schedule log and abstract rule log). This relation, denoted  $\sim_{\Pi}$ , is indexed by a projection  $\Pi$ , and states that the concrete and abstract logs are related by  $\stackrel{log}{\sim}_V$ , both for the schedule and rule logs; that the projection  $\Pi$  sends Kôika variables to LLR variables that evaluate identically; and that the registers are accurately projected by  $\Pi$ , as per the  $\stackrel{reg}{\sim}$  relation.

$$\begin{cases} (\Gamma, L, l) \sim_{\Pi} (V, L^{\sharp}, l^{\sharp}) \triangleq \\ \begin{cases} L \stackrel{log}{\sim}_{V} L^{\sharp} \\ l \stackrel{log}{\sim}_{V} l^{\sharp} \\ \forall x, \exists n, \ \Pi(x) = n \wedge \llbracket n \rrbracket_{\sigma}^{V} = \Gamma(x) \\ (L + + l) \stackrel{reg}{\sim} (\Pi, V) \end{cases}$$

We prove the following lemma, about the correctness of the K2L function, which is the essence of the proof of the compiler correctness theorem.

**Lemma 1** (Correctness of K2L). Consider two matching states  $(\Gamma, L, l)$  and  $(V, L^{\sharp}, l^{\sharp})$  related by projection  $\sim_{\Pi}$ . Compiling action a with path condition P produces a low-level action lla together with a new abstract state  $(V', L^{\sharp}, l'^{\sharp})$ , and a failure condition F.

If the Kôika semantics of action a produces a new Kôika state  $(\Gamma', v, l')$ , then the low-level action lla produced by the compiler evaluates to Kôika value v, the failure condition F evaluates to false, and  $(\Gamma', L, l')$  and  $(V', L^{\sharp}, l'^{\sharp})$  stay in the matching relation.

Otherwise, if action a fails according to Kôika semantics, the failure condition produced by the compiler evaluates to true. More formally,

$$\forall \quad a \ \Pi \ V \ f \ L^{\sharp} \ l^{\sharp} \ \Gamma \ L \ l \ lla \ P \ F \ \Pi' \ V' \ f' \ l'^{\sharp} \ \Gamma', \\ K2L(a,\Pi,V,f,P,L^{\sharp},l^{\sharp}) = (lla,\Pi',V',f',F,l'^{\sharp}) \Rightarrow \\ (\Gamma,L,l) \sim_{\Pi} (V,L^{\sharp},l^{\sharp}) \Rightarrow \llbracket P \rrbracket_{\sigma}^{V} = \mathtt{true} \Rightarrow \\ \begin{pmatrix} \forall \quad l' \ v \ \Gamma', \\ \Gamma \vdash_{L} (l,a) \downarrow (l',v,\Gamma') \Rightarrow \\ \llbracket lla \rrbracket_{\sigma}^{V'} = v \land \llbracket F \rrbracket_{\sigma}^{V'} = \mathtt{false} \land \\ (\Gamma',L,l') \sim_{\Pi'} (V',L^{\sharp},l'^{\sharp}) \end{pmatrix} \\ \land \left( \Gamma \vdash_{L} (l,a) \not \!\!\!\! \downarrow \Rightarrow \llbracket F \rrbracket_{\sigma}^{V'} = \mathtt{true} \right)$$

*Proof.* By structural induction on a.

We can use this lemma to prove Theorem 1, about  $K2L^{sched}$ :

**Theorem 1** (Correctness of  $K2L^{sched}$ ).  $K2L^{sched}$  is a correct compiler of the semantics of Kôika schedules. More precisely,

$$\forall \quad s \ \Pi \ V \ f \ L^{\sharp} \ \Pi' \ V' \ f' \ L'^{\sharp},$$

$$K2L^{sched}(s,\Pi,V,f,L^{\sharp}) = (\Pi',V',f',L'^{\sharp}) \Rightarrow$$

$$(L,s) \Downarrow L' \Rightarrow$$

$$L \stackrel{log}{\sim}_{V} L^{\sharp} \wedge L \stackrel{reg}{\sim} (\Pi,V) \Rightarrow$$

$$L' \stackrel{log}{\sim}_{V'} L'^{\sharp} \wedge L' \stackrel{reg}{\sim} (\Pi',V')$$

*Proof.* By induction on the schedule s.

```

Registers : {a, b, c}.

```

```

Rule r1:

let x := read b in

if read a == 0

then write a 1;

if x == 1

then write a (x + 1).

```

Rule r2: if read c == 1then write a 3.

Schedule : [r1, r2].

(a) Kôika model

| Register | Variable Id |

|----------|-------------|

| а        | 17          |

| b        | 2           |

| С        | 3           |

(b) LLR representation (R)

| Id | Value                                        | Description                                                   |  |

|----|----------------------------------------------|---------------------------------------------------------------|--|

| 1  | a                                            | initial value of register a                                   |  |

| 2  | b                                            | initial value of register b                                   |  |

| 3  | c initial value of register c                |                                                               |  |

| 4  | v2                                           | v2 let-binding in r1                                          |  |

| 5  | v1 == 0                                      | 1 == 0 first condition in r1                                  |  |

| 6  | 1 value written in the first <b>if</b> in r1 |                                                               |  |

| 7  | v5 ? v6 : v1                                 | value of register a after first if in r1                      |  |

| 8  | v4 == 1                                      | second condition in r1                                        |  |

| 9  | v4 + 1                                       | value written in the second if in r1                          |  |

| 10 | v8 ? v9 : v7                                 | v8 ? v9 : v7 value of register a after second <b>if</b> in r1 |  |

| 11 | $v8 \wedge v5$                               | failure condition for r1                                      |  |

| 12 | v11 ? v1 : v10                               | value of register a after r1                                  |  |

| 13 | v3 == 1                                      | first condition in r2                                         |  |

| 14 | 3                                            | value written in the if in r2                                 |  |

| 15 | v13 ? v14 : v12                              | value of register a after the if in r2                        |  |

| 16 | $v13 \land \neg v11 \land (v5 \lor v8)$      | failure condition for r2                                      |  |

| 17 | v16 ? v12 : v15                              | final value of register a after r2                            |  |

(c) LLR representation (V)

Fig. 8: Compilation from Kôika to LLR

Base case. If the schedule is empty, the theorem holds trivially because  $(\Pi', V', L'^{\sharp}) = (\Pi, V, L^{\sharp})$  and L' = L.

**Inductive case.** The schedule is of the form r::sch, and we have as an induction hypothesis that our theorem holds for schedule sch.

By the definition of  $K2L^{sched}$ , we have that: 1  $(-,\Pi_1,V_1,f_1,F_r,l^{\sharp})=K2L(r,\Pi,V,f,\mathsf{true},L^{\sharp},l_0^{\sharp})$  $2 \quad V_2 = V_1[f_1 \mapsto F_r]$  $(\Pi_m, V_m, f_2) = \Pi \bigcup_{V_2, f_1 + 1}^{f_1} \Pi'$   $L_m^{\sharp} = \lambda k \to L^{\sharp}(k) \lor (l^{\sharp}(k) \land \neg v_{conflict})$   $(\Pi', V', f', L'^{\sharp}) = K2L^{sched}(sch, \Pi_m, V_m, f_2, L_m^{\sharp})$

From the semantics of a Kôika schedule (Figure 2), the next concrete schedule log, L', will be either L++l' if the execution of r yields a rule  $\log l'$ , or L if the execution of a fails to produce a rule log. In order to apply our induction hypothesis and finish the proof, all we need to show is that

$L' \stackrel{log}{\sim}_{V_m} L_m^{\sharp} \wedge L' \stackrel{reg}{\sim} (\Pi_m, V_m).$

Applying Lemma 1 on line 1 above gives the following:

$$\forall \quad L, \ L \overset{log}{\sim}_{V} \ L^{\sharp} \wedge L \overset{reg}{\sim} (\Pi, V) \Rightarrow \\ \left( \begin{array}{cc} \forall \quad l', \ \Gamma_{0} \vdash_{L} (l_{0}, r) \downarrow (l', \_, \_) \Rightarrow \\ \mathbb{F}_{r} \mathbb{J}_{\sigma}^{V_{1}} = \mathtt{false} \ \wedge \\ l' \overset{log}{\sim}_{V_{1}} \ l^{\sharp} \wedge (L + + \ l') \overset{reg}{\sim} (\Pi_{1}, V_{1}) \end{array} \right) \\ \wedge \left( \begin{array}{cc} \Gamma_{0} \vdash_{L} (l_{0}, r) \not\downarrow \Rightarrow \llbracket F_{r} \rrbracket_{\sigma}^{V_{1}} = \mathtt{true} \end{array} \right) \\ \mathrm{By} \ \mathrm{disjunction} \ \mathrm{of} \ \mathrm{cases} : \\ \mathcal{L} & = \left( \begin{array}{cc} \Gamma_{0} \vdash_{L} (l_{0}, r) \not\downarrow \Rightarrow \llbracket F_{r} \rrbracket_{\sigma}^{V_{1}} = \mathtt{true} \end{array} \right) \\ \mathrm{Exp} \ \mathrm{disjunction} \ \mathrm{of} \ \mathrm{cases} : \\ \mathcal{L} & = \left( \begin{array}{cc} \Gamma_{0} \vdash_{L} (l_{0}, r) \not\downarrow \Rightarrow \llbracket F_{r} \rrbracket_{\sigma}^{V_{1}} = \mathtt{true} \end{array} \right)$$

• Case  $\Gamma_0 \vdash_L (l_0, r) \downarrow (l', \_, \_)$ . Then,  $\llbracket f_1 \rrbracket_{\sigma}^{V_2} = \text{false}$ , hence  $\Pi_m(k) = \Pi'(k)$  for every k, and  $\llbracket L_m^{\sharp}(k) \rrbracket_{\sigma}^{V_m} = \llbracket L^{\sharp}(k) \vee l^{\sharp}(k) \rrbracket_{\sigma}^{V_m}$  for every k. It follows that  $(L++l') \stackrel{log}{\sim}_{V_m} L_m^{\sharp}$ , and  $(L++l') \stackrel{reg}{\sim}$  $(\Pi_m, V_m)$ .

• Case  $\Gamma_0 \vdash_L (l_0, r) \not\downarrow$ . Then,  $[\![f_1]\!]_{\sigma}^{V_2} = \text{true}$ , hence  $\Pi_m(k) = \Pi(k)$  for every k, and  $[\![L_m^\sharp(k)]\!]_{\sigma}^{V_m} = [\![L^\sharp(k)]\!]_{\sigma}^{V_m}$  for every k. It follows that  $L \stackrel{log}{\sim} \stackrel{m}{V_m} L_m^{\sharp}$ , and  $L \stackrel{reg}{\sim} (\Pi_m, V_m)$ .

Finally, the theorem we want to prove relates the interpretation of a cycle and the LLR obtained by compiling the schedule. We define a function  $C_{\sigma}(llr)$  which, given a LLR llr and an initial mapping for registers  $\sigma$ , results in an updated register environment  $\sigma'$ .

$$C_{\sigma}(llr)(r) \triangleq \mathbf{let} \ n = llr.R(r) \ \mathbf{in} \ [\![n]\!]_{\sigma}^{llr}$$

Theorem 2 (Kôika to LLR compiler correctness). Given a schedule s and an initial state of registers  $\sigma$ , retrieving the final value of a register r through the LLR compiled from this schedule or through the Kôika semantics gives identical results. More formally,

$$\forall s \ \sigma \ r, \ \mathcal{C}_{\sigma}(K2L^{P}(s))(r) = \mathtt{interp\_cycle}(s,\sigma)(r)$$

*Proof.* By applying Theorem 1 and applying definitions.  $\Box$

# D. Verified transformation passes

In order to use the LLR we produced in the previous section for proving properties, we develop a toolbox of theorems and tactics in Coq for reasoning about circuits in our low-level representation.

Among other things, we define a set of transformation passes that can be applied to a model in the low-level representation. In particular, the transformation passes provide a way

of exploiting hypotheses about the state of the environment. Often, a combination of simplifications and case analysis is sufficient for discharging a goal. Note that the reasoning is carried out inside of Coq, so the usual facilities and methods used in this language remain available at any time.

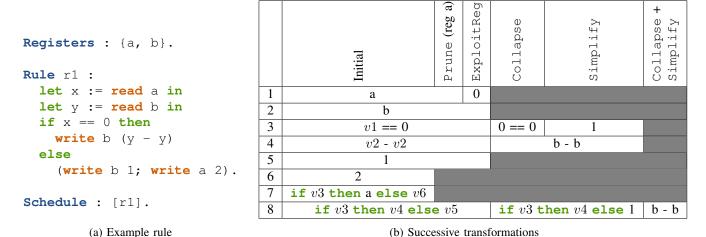

For instance, consider the model of Figure 9a, composed of a single rule. In this rule, the value of register b is updated on every cycle. Suppose we want to prove that when the value of a is 0 at the beginning of a cycle, then the value of b will be 0 at the end of this cycle. Formally, we would write this as:  $\forall \sigma \ llr, \ \sigma(a) == 0 \Rightarrow \mathcal{C}_{\sigma}(llr)(b) = 0.$

We compile the model of Figure 9a into an equivalent low-level representation, as shown in the second column of Table 9b. This LLR is then processed by a sequence of transformations which progressively simplify it. In this example, we employ the following transformation passes:

- Prune(b): remove all variables that are not used in the computation of the final value of register b. We collect all the variables that may participate in the evaluation of register b in our LLR, and prune the others. Here, the register b is represented by v8. Variables v6 and v7 can be pruned.

- ExploitReg(r,v): replace register r with value v. Applying this transformation generates a proof obligation, namely that register r holds value v at the beginning of the cycle. In our example, we have the hypothesis that register a holds the value 0.

- Collapse: replace all variables with their value if this symbolic value is simple enough (a constant, a reference to another variable or a register). In our example, we replace variables v1, v2 and v5 by their value.

- Simplify: compute the value of unary or binary operations when enough of their arguments are known, for all variables in the LLR. This is similar to constant folding in traditional compilers. We also simplify boolean conjunctions or disjunctions when one operand is known to be true or false.

All of our transformation passes preserve the semantics under some assumptions. For instance, assuming that the value of register a is known to be 0 at the beginning of a cycle, then replacing its appearances with 0 is correct. Coq verifies that this assumption is met in the current context before it can apply the transformation. Similarly, it would be invalid to evaluate a register with a LLR in which some of the required variables have been pruned away. Therefore, pruning can only be applied in contexts where the final value of a single register is being considered.

We offer additional transformation passes, such as:

- PruneList(l): remove all variables that are not used in the computation of the final value of at least one register appearing in list l

- ReplaceVar(x, v): replace variable x with value v, given a proof that this substitution is correct

- ReplaceSubact(se, v): same as ReplaceVar but for a subexpression se. All occurrences of this expression se

- in any variable of the tree can then be replaced with the given value v.

- ExploitPartialInformation: same as ExploitReg but works when only some bits of a register are known.

Coq makes it possible to define custom tactics to automate away part of the tedium. We define some general tactics which take our hypotheses into account and then attempt to simplify our model as much as possible, and even recognize some simple subgoals and solve those automatically. For simple properties, proofs can run fully automatically.

# IV. A CONCRETE EXAMPLE: IMPLEMENTING A VERIFIED SHADOW STACK FOR A RISC-V PROCESSOR

In this section, we first explain the security mechanism we aim to implement, i.e. a hardware-based shadow stack in a RISC-V processor. We formally specify the properties we wish to verify, then we give the outline of the proofs we performed, using the methodology introduced in the previous section.

# A. A RISC-V processor model in Kôika

Conveniently, Kôika includes a simple model of a pipelined RISC-V processor that can be specialized to cover part of the RV32I or the RV32E part of the standard. This model does not aim for exhaustiveness and is not proven to conform to the RISC-V specification (although it passes the test suite for all the instructions it implements). It is used as a testing place and a way to showcase Kôika's more advanced features. Our model is a slightly tweaked and expanded version of this example.

# B. The shadow stack mechanism

Memory corruptions are still one of the most significant vulnerabilities in software developed in low-level languages like C or C++. Indeed, the developer is in charge of the application memory management in those languages, which can lead to spatial and temporal memory safety errors. Attackers can exploit such vulnerabilities to leak confidential data or modify the application's intended behavior. For example, they can exploit some buffer overflow on the stack to modify return addresses, one of the most popular attacks of this type. Hardware-based security mechanisms implementing Control Flow Integrity, like Intel CET [27], are appealing solutions to protect software against such attacks. They offer more robust protection than software-based approaches, since software attacks cannot modify them.

We are interested in the property that functions do indeed return to the instruction following their call. A possible way of guaranteeing such a property is to maintain a shadow stack. The processor pushes the expected return address onto this stack for each function call and pops it whenever it returns. If the address a function tries to return to using the regular function stack is not equal to the one on top of the shadow stack, we can deduce that something went wrong and react accordingly. Of course, we must also protect this shadow stack and prevent regular writes to memory performed by application code to modify the shadow stack contents.

Fig. 9: Example rule, its transformation into a LLR, and successive transformations

Shadow stacks can be implemented either in software [19] or in hardware. Although software implementations provide some benefits (chief among them being their compatibility with existing hardware), we will focus on hardware implementations. These offer the advantage of working with any program without the need for patching.

We added a shadow stack module to the processor provided by the Kôika project. We can prove its isolation from the core model, in that the only way of acting on it is through its two methods, push and pop. These methods are called automatically when the current instruction corresponds to a function call or return. They both expect one argument: the address of the instruction following the current function call for push and the stack's return address for pop.

The push function checks for potential overflows and pushes the address onto the shadow stack, whereas the pop function checks for potential underflows, verifies that the address passed as argument matches the top of the shadow stack and pops it. If one of these checks fails, we jump to an exception handler.

## C. Detecting function calls and returns in machine code

Contrary to CISC (Complex Instruction Set Computer) ISAs such as x86, which have dedicated call and return instructions, RISC-V uses the same instruction for multiple purposes. This choice is common for RISC (Reduced Instruction Set Computer) ISAs. The JAL (*jump and link*) and JALR (*jump and link register*) instructions implement both unconditional jumps and function calls. However, the arguments that are passed to them make their role clear. The Application Binary Interface (ABI) describes which JAL/JALR instructions should be interpreted as function calls or returns, depending on their arguments. In fact, the RISC-V specification<sup>1</sup> includes information regarding how shadow stacks (which they call return-address stacks) should behave:

For RISC-V, hints as to the instructions' usage are encoded implicitly via the register numbers used. A JAL instruction should push the return address onto a return-address stack (RAS) only when rd = x1/x5. JALR instructions should push/pop a RAS as shown in the table [that follows].

|   | rd    | rs1   | rs1 = rd | RAS action     |

|---|-------|-------|----------|----------------|

| ĺ | !link | !link | _        | none           |

| ĺ | !link | link  | _        | pop            |

| ĺ | link  | !link | _        | push           |

| ĺ | link  | link  | 0        | pop, then push |

|   | link  | link  | 1        | push           |

Return-address stack prediction hints encoded in register specifiers used in the instruction.  $[\ldots]$  link is true when the register is either  $\times 1$  or  $\times 5$ .

Hence, we implement our shadow stack so that we push a return address when the destination register is x1 or x5, and we pop when the source register is x1 or x5 and the destination register is different from the source register.<sup>2</sup>

## D. Dealing with a detected stack buffer overflow

On a system with a full-fledged operating system, a stack buffer overflow detected through a shadow stack mechanism could be left for the system to manage. For instance, the affected program could be killed, and an error could be logged or displayed to the user. In our simple embedded system, these options are not all open. The two main possibilities for our exception handler are:

- ending the current execution;

- correcting the return address using the shadow stack information (or just relying purely on it and ignoring return arguments).

The latter option might be tempting. However, it comes with significant downsides. If the return address has been modified, then the rest of the stack has likely been impacted and cannot be considered safe.

<sup>&</sup>lt;sup>1</sup>https://github.com/riscv/riscv-isa-manual/releases/download/ Ratified-IMAFDQC/riscv-spec-20191213.pdf, Unprivileged specification, v.20191213, Sec.2.5

$<sup>^2</sup>Registers \, x1$  and x5 are also respectively known as ra (for return address) and t0.

Our verified stack implementation halts execution on a mismatch. In order to prove anything about our processor halting, we first need to define what this means for Kôika models — this is tricky since Kôika does not have a notion of halting execution of a model. We consider that a system is halted when it is in a sink state:

$$\texttt{is\_halted}(\sigma) \triangleq \forall n, r, \mathcal{C}^n_\sigma(llr)(r) = \sigma(r)$$

where  $C^n_\sigma(llr)$  performs n iterations of the  $C_\sigma$  function, i.e. computes the state of each register after n cycles. In fact, it suffices to demonstrate the following property to obtain a proof of is halted for an environment.

```

\begin{aligned} & \texttt{nochange}(\sigma) \triangleq \forall r, \mathcal{C}_{\sigma}(llr)(r) = \sigma(r) \\ & \texttt{nochange\_halted}(\sigma) : \forall \sigma, \texttt{nochange}(\sigma) \Rightarrow \texttt{is\_halted}(\sigma) \end{aligned}

```

We add a register called halt to our processor, and we equip each of the rules with a guard checking the value of this register. When it is true, no rules are run. We can prove that it behaves as expected:

```

halt_1_implies_halted: \forall \sigma, \sigma(halt) = 1 \Rightarrow is_halted(\sigma)

```

Applying nochange\_halted as well as transformation passes <code>ExploitReg</code>, <code>Simplify</code> and <code>Prune</code> gets us most of the way for this proof. We then need to show that the value of any individual register is left unchanged during the next cycle. At this stage, the demonstration of this property is trivial.

For simulation and synthesis, we emit an external call bound to a Verilog module which actually halts the execution of the processor whenever we set the value of halt to 1.

# E. Formally verified properties

We are interested in proving four properties. In plain English, they may be worded as:

- "any overflow in the shadow stack leads to the immediate halting of the processor";

- "any underflow in the shadow stack leads to the immediate halting of the processor";

- "when returning from a procedure, if the stack and the shadow stack disagree on the return address, then the processor halts immediately";

- "in all other situations, the behavior of the processor remains unchanged".

Hereafter are some useful definitions about the shadow stack (sstack) that we will use throughout our proof:

```

\begin{split} & \mathtt{sstack\_empty}(\sigma) \triangleq \sigma(\mathtt{sstack.sz}) == 0 \\ & \mathtt{sstack\_full}(\sigma) \triangleq \sigma(\mathtt{sstack.sz}) == \mathtt{sstack.capacity} \\ & \mathtt{sstack\_top}(\sigma) \triangleq \\ & \emptyset & \text{if } \sigma(\mathtt{sstack.sz}) \text{ is } 0 \\ & \sigma(\mathtt{sstack.stack}[\sigma(\mathtt{sstack.sz})]) & \text{otherwise} \end{split}

```

Our processor is pipelined, which implies that several instructions are in-flight at the same time. Nonetheless, there is at most one instruction at the execute stage at any point, and it just so happens that all the calls to shadow stack functions occur there.

Predicates sstack\_push and sstack\_pop express the conditions under which a push or a pop takes place. Their definitions (omitted here) simply amount to checking whether the instruction in the execute stage is a call or a return instruction. The no\_mispred construct is used for dealing with the mispredictions that can result from branch instructions. The effects of a mispredicted instruction have to be ignored. At the point where an instruction reaches the execution stage of the pipeline, it is already known whether or not it belongs to a mispredicted branch and therefore whether or not it has to be ignored. Function candidate\_return\_address gives the address that the current instruction attempts to return to, assuming it is a procedure return.

We give formal definitions for the first three properties we mentioned earlier:

```

\begin{split} & \operatorname{sstack\_uflow}(\sigma) \triangleq \\ & \operatorname{no\_mispred}(\sigma) \wedge \operatorname{sstack\_empty}(\sigma) \wedge \operatorname{sstack\_pop}(\sigma) \\ & \operatorname{sstack\_oflow}(\sigma) \triangleq \\ & \operatorname{no\_mispred}(\sigma) \wedge \operatorname{sstack\_full}(\sigma) \\ & \wedge \neg \operatorname{sstack\_pop}(\sigma) \wedge \operatorname{sstack\_push}(\sigma) \\ & \operatorname{sstack\_violation}(\sigma) \triangleq \\ & \operatorname{no\_mispred}(\sigma) \wedge \operatorname{sstack\_pop}(\sigma) \wedge \\ & \operatorname{candidate\_return\_addr}(\sigma) \neq \operatorname{sstack\_top}(\sigma) \end{split}

```

We show that these three ways of violating the shadow stack policy result in the halting of the processor.

```

• sstack_uflow_implies_halt: \forall \sigma, sstack_uflow(\sigma) \Rightarrow is_halted(\mathcal{C}_{\sigma}(llr))

• sstack_oflow_implies_halt: \forall \sigma, sstack_oflow(\sigma) \Rightarrow is_halted(\mathcal{C}_{\sigma}(llr))

• sstack_addr_violation_implies_halt: \forall \sigma, sstack_violation(\sigma) \Rightarrow is_halted(\mathcal{C}_{\sigma}(llr))

```

proofs of sstack\_uflow\_implies\_halt, sstack\_oflow\_implies\_halt sstack\_addr\_violation\_implies\_halt share some similarities. In all of them, we start by applying halt\_1\_implies\_halted. We then have to prove that the final value of halt is 1. A logical first step is to apply the Prune transformation pass: we don't care about the variables that are not relevant to the final value of halt. We can also exploit our hypotheses. For instance, for sstack underflow implies halt, we know, among other things, that the shadow stack is empty and that the instruction in the execute stage of the pipeline corresponds to a return instruction. We can exploit this information to simplify the model further. Some case analysis is required to fully exploit the information about the executed instruction. Indeed, as was shown in IV-C, a pop should occur in two situations:

- when rd is neither x1 or x5 and rs1 is either x1 or x5;

- when both rd and rs1 are x1 or x5 but rd  $\neq$  rs1.

In all branches, the rest of the proof is trivial. The proofs of the two other properties follow a similar pattern.

There still remains a last property to demonstrate. In order to prove that our shadow stack does not interfere with the rest of the processor, we need to show that, starting from the same environment and after one cycle, in the absence of a shadow stack violation, the value of the registers that were not introduced for the shadow stack is the same in the vanilla model as in the modified one.

Formally, we write this as:

```

\begin{array}{ll} \mathtt{sstack\_no\_interferences}: \\ \forall \ \sigma, \quad \sigma(\mathtt{halt}) = 0 \Rightarrow \neg \mathtt{sstack\_violation}(\sigma) \Rightarrow \\ \neg \mathtt{sstack\_uflow}(\sigma) \Rightarrow \neg \mathtt{sstack\_oflow}(\sigma) \Rightarrow \\ \forall \ r,r \neq \mathtt{sstack}[\cdot] \Rightarrow \\ \mathcal{C}_{\sigma}(llr\_basic) = \mathcal{C}_{\sigma}(llr\_sstack) \end{array}

```

Once again, we start by exploiting some known values through the ExploitReg transformation, and keep simplifying the model with Simplify and Prune (using the variant PruneList this time, with all the registers, except those that are related to the shadow stack).

The shadow stack is only ever accessed from the rule corresponding to the execute stage in our model. Furthermore, accesses to the shadow stack do not modify registers of the basic Kôika model except for halt. The only variables specific to the version equipped with a shadow stack that remain in the LLR after the call to PruneList are those that impact halt. However, it can be shown that ¬stack\_violation implies that the value written to halt is 0. In other words, the write in question does not update the value of halt. Therefore, some surgical applications of ReplaceVar allow us to remove precisely the parts which differ between our two models. Then, our two LLRs are equal, and the goal is trivially true.

## F. Quantitative summary of the proof effort

At the time of this writing, the proof framework is composed of around 19k lines of Coq, with about half of it being related to the Kôika to LLR compiler or to its correctness proof, and most of the rest being related to transformation passes and the associated proofs of correctness.

The properties we described in this section took around 2k lines of Coq to prove. Complete verification of the proofs takes around 10 minutes and uses a substantial amount of RAM (around 16GB) on a 12th Gen Intel i5 processor running at 4.4GHz with 32GB of RAM.

## V. EXPERIMENTAL EVALUATION

a) Simulation of Kôika with Cuttlesim: We verify the overall functional correctness of our modified RISC-V processor by running it on Cuttlesim, the C++ simulator provided by the Kôika project that directly interprets and simulates the Kôika language. We run a test suite that targets all the instructions in the RV32I subset separately. All the tests provided with the original Kôika still pass with our modified processor.

```

void bad() {

puts("Bad!\n");

}

int f(char* s) {

char buf[16];

strcpy(buf,s);

}

int main(int argc, char** argv) {

int attack_buf[6];

attack_buf[5] = (intptr_t)&bad;

f((char*)attack_buf);

}

```

Fig. 10: Vulnerable program that overwrites its return address

b) Experimental validation of the shadow stack: Even with the proof of Section III, it is valuable to test whether a trivial overwriting of a function's return address is indeed detected by our shadow stack. This cross-validates that the theorems we proved earlier indeed entail a security property.

Figure 10 shows a C program that exhibits a trivial buffer overflow. Buffer buf in function f is 16-byte long, and the strcpy function performs no bounds checking before copying the buffer attack\_buf, which is 24-byte long. Because we know the memory layout of this program, we know where in attack\_buf we should place the address we want to jump to so that it will overwrite the vulnerable function's return address. Our shadow stack module should detect this violation and halt our processor before we even jump to that new return address. We run this program with the Cuttlesim simulator, once with the shadow stack deactivated and once with the shadow stack activated. In the first case, the buffer overflow succeeds, and we observe that the program writes the string "Bad!" to the console. On the other hand, when run with the shadow stack activated, we observe that the execution exits abruptly. By inspecting the final state of the Kôika model manually, we see that the halt register is set, and the instruction that was being executed at that point is precisely the ret instruction in the f function.

c) Synthesis on the TinyFPGA BX board: We successfully ran the Verilog output of the Kôika compiler on our modified RISC-V processor through the Yosys synthesis suite. The shadow stack that we could fit on this board, in addition to the processor model, has a capacity of only seven return addresses and incurs an overhead of 5.9 % in the number of logical cells (LUTs) used on the FPGA. This limitation in size is only due to the limited number of LUTs and quantity of internal RAM of this inexpensive FPGA.

| Shadow     | Clock           | Used logical  | Critical |

|------------|-----------------|---------------|----------|

| stack      | frequency cells |               | path     |

|            | (MHz)           | (out of 7680) | (ns)     |

| Without    | 22.07           | 7049 (91%)    | 45.4     |

| With 20.49 |                 | 7463 (97%)    | 48.8     |

## VI. RELATED WORK

We now discuss related lines of work and how they differ from our results.

- a) ISA-level security proofs: ISAs are the specification that CPUs must implement. Thus, they form the foundation for software-level security. As such, there have been multiple recent works focusing on proving security properties at the ISA level. One such prominent line of work aims to prove various security properties for capability-enabled ISAs. Nienhuis et al. [24] prove capability monotonicity for CHERI-MIPS while Bauereiss et al. [4] prove it for the Arm Morello prototype. The work of Georges et al. [11], [12] and Skorstengaard et al. [28], [29] prove a variety of stack safety properties that can be enforced on capability machines. Similarly, Van Strydonck et al. [30] develop a library of verified wrappers around drivers leveraging capabilities for enforcing security properties. While these works also define and prove security properties about hardware, all their reasoning is done at the ISA level and must thus assume that the ISA is correctly implemented in hardware. In contrast, we reason at the register transfer level, which is much closer to the concrete hardware.

- b) HDLs for security: There have been multiple HDLs proposed in the literature for securely designing circuits. For instance, Caisson [22] and SecVerilog [33] are both HDLs that use information-flow types to ensure that generated circuits are secure. Similarly, Iodine [13] and Xenon [14] use SMT-solvers to check that cryptographic circuits execute in constant time. While these approaches allow to prove specific security properties, they cannot be used to prove more general properties related to the execution of a CPU like our work does. Furthermore, using a proof assistant like we do has a lighter TCB footprint.

- c) Formal languages compiled to Verilog: As mentioned earlier, this work uses the Kôika [5] language and its formalization to implement, specify and verify a shadow stack. Kami [7] is another language with formal semantics that can be compiled down to Verilog. Kami was developed by the same team who published Kôika and follows the same rule-based approach. However, the project is not actively maintained since Kôika offers a more precise cycle-accurate approach. Vericert [16] is a formally verified high-level synthesis tool based on CompCert that transforms C code into Verilog, but lacks support for implementing pipelines, which is crucial for implementing efficient CPUs. Similarly, HOL4 [23] has also been used for the verified synthesis of Verilog code. Specifically, it has been used for designing an in-order CPU implementing a custom instruction set. Unlike our work, theirs is not concerned with security mechanisms, and it is unknown whether they could actually implement an efficient and pipelined CPU.