# A Faithful Binary Circuit Model

Matthias Függer, Robert Najvirt, Thomas Nowak, Ulrich Schmid

# ▶ To cite this version:

Matthias Függer, Robert Najvirt, Thomas Nowak, Ulrich Schmid. A Faithful Binary Circuit Model. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2019, 39 (10), pp.2784-2797. 10.1109/TCAD.2019.2937748. hal-02395251

# HAL Id: hal-02395251 https://inria.hal.science/hal-02395251v1

Submitted on 5 Dec 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A Faithful Binary Circuit Model

Matthias Függer, Robert Najvirt, Thomas Nowak, and Ulrich Schmid

Abstract—[Függer et al., IEEE TC 2016] proved that no existing digital circuit model, including those based on pure and inertial delay channels, faithfully captures glitch propagation: For the Short-Pulse Filtration (SPF) problem similar to that of building a one-shot inertial delay, they showed that every member of the broad class of bounded single-history channels either contradicts the unsolvability of SPF in bounded time or the solvability of SPF in unbounded time in physical circuits. In this paper, we propose binary circuit models based on novel involution channels that do not suffer from this deficiency. Namely, in sharp contrast to bounded single-history channels, SPF cannot be solved in bounded time with involution channels, whereas it is easy to provide an unbounded SPF implementation. Hence, binary-valued circuit models based on involution channels allow to solve SPF precisely when this is possible in physical circuits. Additionally, using both Spice simulations and physical measurements of an inverter chain instrumented by high-speed analog amplifiers, we demonstrate that our model provides good modeling accuracy with respect to real circuits as well. Consequently, our involution channel model is not only a promising basis for sound formal verification, but also allows to seamlessly improve existing dynamic timing analysis.

Index Terms—Binary circuit models, glitch propagation

#### I. Introduction

ODERN digital circuit design relies heavily on fast timing analysis techniques. For synchronous designs, state-of-the-art *static* timing analysis tools like Synopsis Prime Time are able to very accurately predict the timing behavior of a given circuit design, and to identify setup/hold-violations and other timing-related problems. Such tools are based on elaborate timing prediction models like CCSM [1] and ECSM [2]. These models characterize the delay of a cell via (typically manufacturer-supplied) technology data. This data can include tabulated input/output current waveforms for varying parameters such as input slew rate and output capacitive load [3]. However, the timing predictions provided by static timing analysis tools do not involve any dynamic (signal trace-related) considerations.

By contrast, *dynamic* timing analysis techniques rely on signal traces generated by a circuit, in response to appropriately setup test vectors. The "golden standard" here are fully-fledged analog simulations, e.g., using Spice [4], which are based on detailed analog models of all elements of a digital standard-cell library. Since Spice simulation times of even moderately

This research was partially funded by the Austrian Science Fund (FWF) projects SIC (P26436), RiSE (S11405), and DMAC (P32431), the CNRS project PEPS DEMO, and by DigiCosme (working group HicDiesMeus).

M. Függer is with the Centre National de la Recherche Scientifique (CNRS) at the Laboratoire Spécification et Vérification, ENS Paris-Saclay, Univeristé Paris-Saclay & Inria, 94235 Cachan, France. E-mail: mfuegger@lsv.fr.

R. Najvirt and U. Schmid are with the Embedded Computing Systems Group, Vienna University of Technology, 1040 Vienna, Austria. E-mail: {rnajvirt, s}@ecs.tuwien.ac.at.

T. Nowak is with the Laboratoire de Recherche en Informatique, Université Paris-Sud, CNRS, 91405 Orsay, France. E-mail: thomas.nowak@lri.fr.

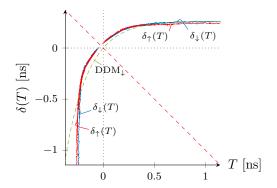

complex circuits are prohibitively excessive. However, designers have to resort to digital timing analysis/simulation tools for Mentor Graphics ModelSim, Cadence NC-Sim, or Synopsis VCS for those parts of a circuit where, e.g., the presence of glitch trains may severely affect the correctness and power consumption. Such tools are based on discrete-value (typically binary) circuit models augmented by continuous-time delays. More specifically, gate and wire delay estimates obtained via CCSM or ECSM, for example, are used to parametrize pure or inertial delay [5] channels (e.g., in VHDL-Vital or Verilog timing libraries). The resulting executable HDL simulation models are then used in subsequent simulation and dynamic timing analysis runs. Clearly, the pre-computed delays are constants here, i.e., remain the same throughout these runs. More accurate results can be expected from the Degradation Delay Model (DDM), introduced by Bellido-Díaz et al. [6], [7], which allow channel delays to vary dynamically in a trace.

However, binary-valued circuit models do not only facilitate accurate performance and power estimation [8], [9] of complex circuits at early design stages: They also pave the way to formal verification of complex circuits. A main driver for verification of digital circuits is its potential to uncover race conditions, hazardous glitches and other corner-case effects relevant for timing-closure analysis. Obviously, such capabilities rest critically on suitable foundations for a rigorous and complete timing analysis of complex circuits. The first thing to note in this context is that statements about the correctness of a circuit in a model are meaningful only if they also imply correctness of the corresponding real circuit implementation. We call a model *realistic*, if a given problem can be solved in the model if and only if it can be solved by a real circuit A model is *faithful* if it is both realistic and provides accurate timing predictions. The first question to ask is whether existing binary circuit models are faithful.

**Short-pulse filtration.** Függer et al. [10] studied the faith-fulness of existing binary circuit models with respect to glitch propagation. More specifically by their ability to solve the simple *Short-Pulse Filtration* (SPF) problem, which is essentially the problem of building a one-shot variant of an inertial delay channel: As for inertial delay channels, no short pulses may appear at the SPF output. In the case of long input pulses, however, they need not be passed unaltered. In particular, the SPF output may settle at logical 1 even if the input does not. The stronger variant of *bounded* SPF requires the output to settle in bounded time.

The (un)solvability of (bounded) SPF is indeed a suitable test for a model's ability to faithfully model glitch propagation with respect to physical circuits: On the one hand, Marino [11] formally proved that problems like SPF cannot be solved in a physical model when the output is required to stabilize in bounded time [10]. On the other hand, a simple storage loop

1

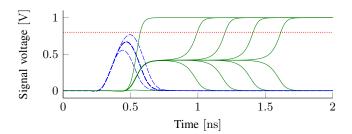

Fig. 1. Analog simulation traces of a CMOS SPF, implemented as a storage loop followed by a high-threshold buffer. The dashed (blue) curves represent the input signal, the solid (green) ones give the output of the storage loop. The horizontal line at 0.8 V marks the threshold level.

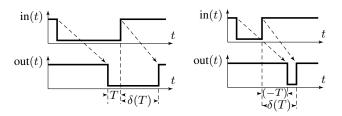

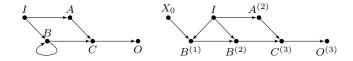

Fig. 2. Left: Input/output signal of a single-history channel, involving the previous-output-to-input delay T and the resulting input-to-output delay  $\delta(T)$ . Right: Input transition with T<0.

with a high-threshold buffer at its output (see Fig. 5) solves SPF in unbounded time: As shown in the Spice simulation traces in Fig. 1, sufficiently large input pulses (largest blue dashed one) just cause the storage loop to change its state (to 1) instantaneously (left-most green solid one), very small input pulses (smallest blue dashed one) do not affect the storage loop (bottom green solid one). Critical input pulses (middle blue dashed ones, overlapping, therefore appearing as if they were one pulse) cause the storage loop to become metastable for an unbounded time, eventually resolving to either state 0 or 1. Therefore, appending a high threshold buffer with a threshold (marked by the red dotted line) clearly above the metastability region results in a clean (= non-metastable) output signal, which either remains at 0, or makes a single (possibly delayed) transition to 1. Hence, with real circuits, SPF is solvable, while its stronger, bounded, variant is not.

Single-history channels. The circuit model used in [10] combines zero-time Boolean gates with single-history channels that model circuit delays. They are primarily characterized by a delay function  $\delta$  that maps a transition occurring at the channel input at time t to its corresponding output transition at time  $t+\delta(T)$ , where T is the previous-output-to-input delay. Fig. 2 shows two examples. Note that single-history channels not only allow to model decaying pulse propagation, but also vanishing pulses: If two succeeding input transitions would, according to  $\delta(T)$ , occur at the output in reversed order, they cancel each other. Furthermore, single-history channels allow for different rising and falling transition delays, specified by two delay functions  $\delta_{\uparrow}$  and  $\delta_{\downarrow}$ , respectively.

Well-known instances of single-history channels are pure delay channels and inertial delay channels [5]; a more advanced example are DDM channels [7], [6]. They are all bounded single-history channels, where the delay functions are upper- and lower-bounded. Függer et al. [10] proved that no bounded single-history channel can be faithful: Binary circuit models based on channels with pure (= constant) delays do not allow to solve unbounded SPF. Bounded single-history channels with non-constant delays, including inertial delay and DDM channels, allow to design circuits that solve bounded SPF. Since this contradicts reality, as argued above, no existing binary circuit model is faithful.

Main contributions and paper organization. In this paper, we propose a class of single-history channels with *unbounded* delay functions: Like their bounded counterparts, their delay is upper bounded; however, it is not bounded from below. These negative delays turn out to be crucial for accurately modeling glitch suppression. We coined the term *involution channels* for them, as we require their negative delay functions to be involutions, i.e.,  $-\delta(T)$  must form its own inverse. To increase the coverage of our class of involution channels, we actually allow the delay functions  $\delta_{\uparrow}$  and  $\delta_{\downarrow}$  for rising and falling transitions to be different, and require  $-\delta_{\downarrow}(-\delta_{\uparrow}(T)) = T$  and  $-\delta_{\uparrow}(-\delta_{\downarrow}(T)) = T$ . We prove that the solvability/unsolvability border of SPF in a binary-valued circuit model based on our involution channels is the same as in reality, and that the resulting model also accurately captures the behavior of real circuits:

- (i) In Sec. II, we demonstrate that the standard first-order model used, e.g., in [12] actually gives rise to a simple instance of general involution channels. They are introduced formally in Sec. IV. Assuming delay functions to be involutions is hence neither artificial nor (as our simulations and experiments reveal) inaccurate.

- (ii) In Sec. III, we provide our binary circuit model, as well as the SPF problem. In Sec. V, we explain how to use our model to explicitly construct output and intermediate signals of a circuit given the input signals, i.e., how to perform circuit simulation.

- (iii) In Sec. VI, we prove that the simple circuit consisting of a storage loop and a high-threshold buffer solves unbounded SPF in the involution channel model.

- (iv) In Sec. VII, we show that bounded SPF is impossible to solve with involution channels. In a nutshell, our proof inductively constructs an execution that can determine the final output only after some unbounded time. It exploits an important continuity property of the output of an involution channel with respect to the presence/absence of glitches at the channel input, which is due to the involution property (unboundedness) of our delay functions.

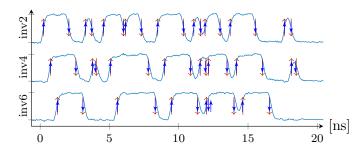

- (v) In Sec. VIII, we briefly report on the results of the experimental evaluation [13] of the accuracy of the predictions of our involution model for a real circuit, which used both simulations and measurements.

Together, as we conclude in Sec. IX, the above results reveal that our binary circuit model in conjunction with involution channels indeed allows to solve SPF precisely when this is possible in physical circuits. Moreover, some (limited) experimental evaluation also revealed good accuracy. Consequently, to the best of our knowledge, our involution model seems to

be the very first candidate for a model that indeed guarantees faithful glitch propagation.

**Related work.** Whereas there is a wealth of research devoted to the analog modeling of digital circuits (see [4], [14], [15], [16], [17] for a few references), none addressed the issue of characterizing delay functions with respect to solvability of problems. On the other hand, digital circuit models have been proposed as a general approach for modeling asynchronous sequential switching circuits long time ago: Unger [5] introduced the well-known pure and inertial delay channels, which have been heavily used both in research and in industrial timing simulators since then. Brzozowski and Ebergen [18] formally proved that it is impossible to implement Muller C-Elements and other state-holding components using only zero-time logical gates interconnected by wires without timing restrictions. Bellido-Díaz et al. [6] proposed the PID model, and justified its appropriateness both analytically and by comparing model predictions against Spice simulations. In [19], the PID model (later renamed to Delay Degradation Model DDM) was generalized from inverters to (N)AND and (N)OR gates. Thanks to considerable efforts like [20], [19] spent on the question of how to extract the DDM model parameters from technology parameters, the DDM model has already made its way into digital timing analysis tools [7].

# II. ANALOG MODELS VS. INVOLUTION CHANNELS

Restricting delay functions to satisfy the involution property  $-\delta_{\uparrow}(-\delta_{\downarrow}(T)) = -\delta_{\downarrow}(-\delta_{\uparrow}(T)) = T$  might raise concerns about whether such an assumption makes sense at all in real circuits, and whether/how it fits to existing analog models [4], [14], [15], [16], [17]. In this section, we will show that involution channels are indeed well-suited for modeling physical circuits, in the sense that they arise naturally in a (generalized) standard analog model.

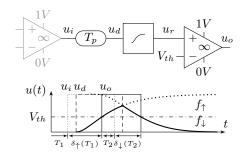

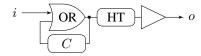

More specifically, we will show that, for any given involutions  $\delta_{\uparrow}$ ,  $\delta_{\downarrow}$ , there is an analog channel model that has  $\delta_{\uparrow}$ ,  $\delta_{\downarrow}$  as its corresponding delay functions. It consists of a pure delay component, a slew-rate limiter with generalized switching waveforms, and an ideal comparator, see Fig. 3. Note carefully, though, that we do not claim that this is the only analog model that leads to involution delay functions. There may of course be many others as well. Vice versa, the fact that some well-known analog model leads to involutions does not at all make our results incremental: Besides the fact that, to the best of our knowledge, no analog modeling paper [4], [14], [15], [16], [17] addressed the properties of corresponding delay functions, it is of course not possible to generalize results obtained for some *particular* involution to involutions in general.

As a first observation, note that the timing behavior of involution channels is fully determined by either one of the delay functions, as  $\delta_{\uparrow}(T) = -\delta_{\downarrow}^{-1}(-T)$  (and similarly for  $\delta_{\downarrow}$ ). To better understand how our delay functions integrate the behavior of both transitions, consider the ansatz  $\delta_{\uparrow}(T) = -f_{\uparrow}^{-1}(f_{\downarrow}(T))$  and  $\delta_{\downarrow}(T) = -f_{\downarrow}^{-1}(f_{\uparrow}(T))$ , where  $f_{\uparrow}$  resp.  $f_{\downarrow}$  are strictly increasing resp. decreasing functions. Intuitively, we would like  $f_{\uparrow}$  and  $f_{\downarrow}$  to represent the continuous switching

Fig. 3. Simple analog channel model.

waveforms of the output of the generalized slew rate limiter upon the occurrence of a rising respectively falling transition at its input. In the above formula, e.g., at a rising transition,  $\delta_{\uparrow}(T)$  returns the time by which  $f_{\uparrow}$  has to be shifted so that the output signal remains continuous with respect to the output caused by the previous falling transition. For realistic switching waveforms, we further need  $f_{\uparrow}(0) = 1 - f_{\downarrow}(0) = 0$  and  $\lim_{t \to \infty} f_{\uparrow}(t) = 1 - \lim_{t \to \infty} f_{\downarrow}(t) = 1$ , which requires to augment our ansatz with some additive terms, resulting in

$$\delta_{\uparrow}(T) = -f_{\uparrow}^{-1}(f_{\downarrow}(T + \delta_{\infty}^{\downarrow})) + \delta_{\infty}^{\uparrow} \quad \text{and}$$

$$\delta_{\downarrow}(T) = -f_{\downarrow}^{-1}(f_{\uparrow}(T + \delta_{\infty}^{\downarrow})) + \delta_{\infty}^{\downarrow},$$

$$(1)$$

where  $\delta_{\infty}^{\uparrow} = \lim_{T \to \infty} \delta_{\uparrow}(T)$  and  $\delta_{\infty}^{\downarrow} = \lim_{T \to \infty} \delta_{\downarrow}(T)$ .

Fig. 3 shows a block diagram of an idealized analog circuit corresponding to so constructed involution channels, and a sample waveform. The pure delay time-shifts the binaryvalued input  $u_i$  by some  $T_p$ . The slew rate limiter exchanges the step functions of the resulting  $u_d$  with instances of  $f_{\uparrow}$  and  $f_{\downarrow}$ , shifting them in time such that the output  $u_r$ is continuous and switches between strictly increasing and decreasing exactly at  $u_d$ 's switching times. The comparator generates  $u_o$  by again discretizing the value of this waveform comparing it to the threshold voltage  $V_{th}$ , effectively adding  $f_{\uparrow}^{-1}(V_{th})$  resp.  $f_{\downarrow}^{-1}(V_{th})$  to the instantiation times of  $f_{\uparrow}$ resp.  $f_{\downarrow}$ . The input-output delay of a perfectly idle channel (the last output transition was at time  $-\infty$ ), i.e.,  $\delta_{\infty}^{\uparrow}$  and  $\delta_{\infty}^{\downarrow}$ for rising respectively falling transitions, is the sum of the pure delay and the time the switching waveform needs to reach the threshold voltage  $V_{th}$ :

$$\delta_{\infty}^{\uparrow} = T_p + f_{\uparrow}^{-1}(V_{th})$$

and  $\delta_{\infty}^{\downarrow} = T_p + f_{\downarrow}^{-1}(V_{th})$  (2)

This equation and (1) can be used to transform the parameters of the model in Fig. 3 to the corresponding  $\delta$  functions. As a special case, consider a slew rate limiter implemented as a first-order RC low pass filter; the switching waveforms are  $f_{\downarrow}(t)=1-f_{\uparrow}(t)=e^{-t/\tau}$  here, with  $\tau$  being the RC time constant. Inserting these functions and their inverses into (1) and (2), we obtain what we refer to as *exp-channels* in the remainder of this paper:

$$\delta_{\uparrow}(T) = \tau \ln(1 - e^{-(T + T_p - \tau \ln(V_{th}))/\tau}) + T_p - \tau \ln(1 - V_{th})$$

$$\delta_{\downarrow}(T) = \tau \ln(1 - e^{-(T + T_p - \tau \ln(1 - V_{th}))/\tau}) + T_p - \tau \ln(V_{th}),$$

(3)

Conversely to the above, given any  $\delta_{\downarrow}$ ,  $\delta_{\uparrow}$ , there is a combination of switching waveforms  $f_{\uparrow}$  and  $f_{\downarrow}$ , pure delay  $T_p$ , and

threshold  $V_{th}$ , such that the circuit in Fig. 3 behaves exactly like the corresponding involution channel. For example, one could choose  $f_{\downarrow}(t)=e^{-t},\ f_{\uparrow}(t)=e^{\delta_{\downarrow}(t-\delta_{\infty}^{\uparrow})-\delta_{\infty}^{\downarrow}},\ T_p$  such that  $\delta_{\downarrow}(-T_p)=\delta_{\uparrow}(-T_p)=T_p$ , and  $V_{th}=e^{T_p-\delta_{\infty}^{\downarrow}}$ . However, this choice is of course not unique.

#### III. BINARY CIRCUIT MODEL

We next formally define the binary-value continuous-time circuit model used in this paper. Except for the involution channels introduced in Sec. IV, it is essentially the same as the model introduced in [10].

**Signals.** A falling transition at time t is the pair (t,0), a rising transition at time t is the pair (t,1). A signal is a (finite or infinite) list of alternating transitions such that

- S1) the initial transition is at time  $-\infty$ ; all other transitions are at times  $t \ge 0$ ,

- S2) the sequence of transition times is strictly increasing,

- S3) if there are infinitely many transitions in the list, then the set of transition times is unbounded.

To every signal s corresponds a function  $\mathbb{R} \to \{0,1\}$  whose value at time t is that of the most recent transition. We follow the convention that the function already has the new value at the time of a transition, i.e., the function is constant in the half-open interval  $[t_n, t_{n+1})$  if  $t_n$  and  $t_{n+1}$  are two consecutive transition times. A signal is uniquely determined by such a function.

**Circuits.** Circuits are obtained by interconnecting a set of input ports and a set of output ports, forming the external interface of a circuit, and a set of combinational gates via channels. We constrain the way components are interconnected in a natural way by requiring that any gate input, channel input and output port is attached to only one input port, gate output or channel output.

Formally, a *circuit* is described by a directed graph where:

- C1) Vertices are partitioned into *input ports*, *output ports*, and *gates*.

- C2) Channels are edges with a channel function that maps an input signal to an output signal. Multiple edges between two vertices are allowed. Sec. IV specifies the properties of the channel function for our involution channels. For simplicity of analysis, we use 0-delay channels as edges from input ports and to output ports.

- C3) Input ports have no incoming channels.

- C4) Output ports have exactly one incoming channel and no outgoing channel.

- C5) Every gate is assigned a Boolean gate function  $\{0,1\}^d \rightarrow \{0,1\}$ , where d is the number of incoming channels, and an initial value in  $\{0,1\}$ .

- C6) There is a fixed order on the incoming channels of every gate.

**Executions.** An *execution* of circuit  $\mathcal{C}$  is a collection of signals  $s_{\Gamma}$  for all components  $\Gamma$  (vertices and channels) of  $\mathcal{C}$  that respects the channel functions, Boolean gate functions, and initial values. Formally, the following properties hold:

E1) If I is an input port, then there are no restrictions on  $s_I$ .

- E2) If O is an output port, then  $s_O = s_C$ , where C is the unique incoming channel of O.

- E3) If C is a channel departing from vertex V, then  $s_C = f_C(s_V)$ , where  $f_C$  is the channel's function.

- E4) If B is a gate with d incoming channels  $C_1, \ldots, C_d$ , ordered according to the fixed order of condition (C6), gate function  $f_B$ , and initial value  $I_B$ , then for all times t < 0,  $s_B(t) = I_B$ , and for  $t \ge 0$ ,  $s_B(t) = f_B(s_{C_1}(t), s_{C_2}(t), \ldots, s_{C_d}(t))$ .

**Short-Pulse Filtration.** A pulse of length  $\Delta>0$  at time  $T\geq 0$  has initial value 0, one rising transition at time T, and one falling transition at time  $T+\Delta$ . A signal contains a pulse of length  $\Delta$  at time T if it contains a rising transition at time T, a falling transition at time  $T+\Delta$  and no transition in between. The zero signal has the initial transition  $(-\infty,0)$  only.

A circuit solves Short-Pulse Filtration (SPF), if it fulfills the following conditions.

- F1) The circuit has exactly one input port and exactly one output port. (Well-formedness)

- F2) If the input signal is the zero signal, then so is the output signal. (*No generation*)

- F3) There exists an input pulse such that the output signal is not the zero signal. (*Nontriviality*)

- F4) There exists an  $\varepsilon > 0$  such that for every input pulse the output signal never contains a pulse of length less than or equal to  $\varepsilon$ . (No short pulses)

Note that we allow the circuit to behave arbitrarily if the input signal is not a single pulse or the zero signal.

A circuit *solves bounded SPF* if additionally the following condition holds:

F5) There exists a K > 0 such that for every input pulse the last output transition is before time T+K, where T is the time of the last input transition. (Bounded stabilization time)

## IV. INVOLUTION CHANNELS

Intuitively, a channel propagates each transition of the input signal to a transition at the output happening after some *input-to-output* delay  $\delta(T)$ , which depends on the *previous-output-to-input* delay T. Note that T can be negative if two input transitions are close together, as in Fig. 2 (right).

Formally, an *involution channel* is characterized by two strictly increasing concave *delay functions*  $\delta_{\uparrow}:(-\delta_{\infty}^{\downarrow},\infty) \to (-\infty,\delta_{\infty}^{\uparrow})$  and  $\delta_{\downarrow}:(-\delta_{\infty}^{\uparrow},\infty) \to (-\infty,\delta_{\infty}^{\downarrow})$  such that both  $\delta_{\infty}^{\uparrow}=\lim_{T\to\infty}\delta_{\uparrow}(T)$  and  $\delta_{\omega}^{\downarrow}=\lim_{T\to\infty}\delta_{\downarrow}(T)$  are finite and

$$-\delta_{\uparrow}(-\delta_{\downarrow}(T)) = T \text{ and } -\delta_{\downarrow}(-\delta_{\uparrow}(T)) = T$$

(4)

for all applicable T. All such functions are necessarily continuous and, for simplicity, we will also assume them to be differentiable;  $\delta$  being concave thus implies that its derivative  $\delta'$  is continuous and monotonically decreasing.

The behavior of an involution channel is defined by Algorithm 1, which maps channel input signal s with event list Input to channel output signal  $f_C(s)$  with event list Output.

**Definition 1.** An involution channel is *strictly causal* if  $\delta_{\uparrow}(0) > 0$ , which is equivalent to the condition  $\delta_{\downarrow}(0) > 0$  due to (4) and the functions being strictly increasing.

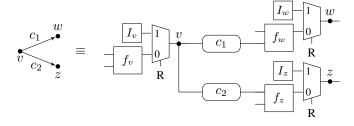

Fig. 4. A circuit (graph) with gates v, w, z, and channels  $c_1$  and  $c_2$  (on the left) and the physical equivalent (on the right). Reset R switches from 1 to 0 at time 0.

#### **Algorithm 1** Channel algorithm, up to time $\tau$

```

1: x \leftarrow \text{value at } t = -\infty \text{ in Input}

2: add (-\infty, x) to Output

3: Prev \leftarrow (-\infty, x)

4: t \leftarrow earliest time of a pending transition, otherwise +\infty

5: while t \leq \tau do

move (t, x) from Pending to Output

(t',x') \leftarrow \text{Prev}

7:

if x = 1 then \delta \leftarrow \delta_{\uparrow}(t - t') else \delta \leftarrow \delta_{\downarrow}(t - t') endif

9:

\text{Prev} \leftarrow (t + \delta, x)

if t + \delta \leq t' then

10:

11:

remove (t', x') from Pending(C)

12:

else

13:

add (t + \delta, x) to Pending(C)

14:

end if

t \leftarrow earliest time of a pending transition, otherwise +\infty

15:

16: end while

17: return Output

```

# **Lemma 2.** An exp-channel is strictly causal if and only if $T_p > 0$ .

The next lemma identifies an important parameter  $\delta_{\min}$  of a strictly causal involution channel.

**Lemma 3.** A strictly causal involution channel has a unique  $\delta_{\min}$  defined by  $\delta_{\uparrow}(-\delta_{\min}) = \delta_{\min} = \delta_{\downarrow}(-\delta_{\min})$ , which is positive. For exp-channels,  $\delta_{\min} = T_p$ .

For the derivative, we have  $\delta'_{\uparrow}(-\delta_{\downarrow}(T)) = 1/\delta'_{\downarrow}(T)$  and hence  $\delta'_{\uparrow}(-\delta_{\min}) = 1/\delta'_{\downarrow}(-\delta_{\min})$ .

*Proof.* Set  $f(T) = -T + \delta_{\uparrow}(-T)$ . This function is continuous and strictly decreasing, since  $\delta_{\uparrow}$  is continuous and strictly increasing. Because  $f(0) = \delta_{\uparrow}(0)$  is positive and the limit of f(T) as  $T \to \delta_{\infty}^{\downarrow}$  is  $-\infty$ , there exists a unique  $\delta_{\min}$  between 0 and  $\delta_{\infty}^{\downarrow}$  for which  $f(\delta_{\min}) = 0$ . Hence,  $\delta_{\uparrow}(-\delta_{\min}) = \delta_{\min}$ . The second equality follows from  $\delta_{\min} = \delta_{\downarrow}(-\delta_{\uparrow}(-\delta_{\min})) = \delta_{\downarrow}(-\delta_{\min})$  according to (4).

The second part of the lemma follows by differentiating Equation (4).

We next show that  $\delta_{\min}$  indeed deserves its name: A particular consequence of the following lemma is that the channel delay for any non-canceled transition is larger than  $\delta_{\min}$ .

**Lemma 4.** Let  $t_n$  and  $t_{n+1}$  be the times of the nth and (n+1)th input transitions. The following are equivalent:

- 1) The nth and (n+1)th pending output transitions cancel.

- 2)  $t_{n+1} \le t_n + \delta_n \delta_{\min}$

- 3)  $\delta_{n+1} \leq \delta_{\min}$

*Proof.* Let  $\delta$  be either  $\delta_{\uparrow}$  or  $\delta_{\downarrow}$ , depending on whether  $t_{n+1}$  is a rising or falling transition. By definition, the two transitions cancel if and only if

$$\delta_{n+1} = \delta(t_{n+1} - t_n - \delta_n) \le -(t_{n+1} - t_n - \delta_n) . \tag{5}$$

Set  $T=t_{n+1}-t_n-\delta_n$ . By Lemma 3, equality holds in (5) if and only if  $T=-\delta_{\min}$ . Because the left-hand side of (5) is increasing in T and the right-hand side is strictly decreasing in T, (5) is equivalent to  $T \le -\delta_{\min}$ . This in turn is equivalent to  $t_{n+1} \le t_n + \delta_n - \delta_{\min}$  and  $\delta(T) \le \delta_{\min}$ .

In the rest of the paper, we assume all channels to be strictly causal involution channels unless noted otherwise.

#### V. SIMULATING EXECUTIONS OF CIRCUITS

The definition of an execution of a circuit as given in Sec. III is "existential", in the sense that it only allows to check for a given collection of signals whether it is an execution or not. This also includes the involution channel algorithm: It specifies the channel output signal, given a *fixed* input signal. A priori, this does not give an algorithm to construct executions of circuits with feedback loops. However, we show in Theorem 8 that executions always exist and are unique for circuits with strictly causal involution channels. We can therefore give a *deterministic simulation algorithm* for arbitrary circuits (that may include feedback loops).

The simulation algorithm takes as input a time  $\tau \geq 0$  up to which the circuit should be simulated, and a list of transitions  $\operatorname{Fixed}(I) = s_I$  for every input port I. We denote by  $\operatorname{Init}(I)$  the value of the initial transition in this list (at time  $-\infty$ ). When the algorithm terminates, it outputs a list of transitions  $\operatorname{Fixed}(\Gamma)$  up to time  $\tau$  for every component  $\Gamma$  (vertices and channels) of the circuit.

During the execution of the algorithm, it distinguishes *pending* and *fixed* transitions. Pending transitions are stored in the variable  $\operatorname{Pending}(\Gamma)$ , while fixed ones are transferred to  $\operatorname{Fixed}(\Gamma)$ ; they are said to be *marked fixed* when doing so. We will show (Lemma 7) that pending transitions can still be canceled by other transitions. Fixed transitions on the other hand are guaranteed to occur in the constructed execution.

For a channel C, we write  $\operatorname{Incoming}(C)$  for its predecessor and  $\operatorname{Delay}(C)$  for the pair of its delay functions. Furthermore, we store its last generated output transition (ordered by the time of the corresponding input transitions), whether it is canceled or not, in the variable  $\operatorname{Prev}(C)$ . For a gate B, we write  $\operatorname{Incoming}(B)$  for the collection of its incoming channels,  $\operatorname{Init}(B)$  for its initial value, and  $f_B$  for its Boolean function. For an output port O,  $\operatorname{Incoming}(O)$  is its unique incoming channel. For an input port I,  $\operatorname{Outgoing}(I)$  is its unique outgoing channel.

The simulation algorithm is given in Algorithm 2. It uses the function  $\operatorname{Latest}(\Gamma,t)$  for a component  $\Gamma$  and a time t, which is equal to the Boolean value of the most recent fixed or pending transition for component  $\Gamma$  before or at time t (ordered by their transition times). Note the special handling of 0-delay channels from input ports and to output ports, which is outside of the main loop and just copies the transition lists.

If the  $\mathrm{Init}(\cdot)$ -values of the incoming neighbors are not compatible with a gate's own initial value, then line 21 generates a transition at time t=0 in the first loop iteration. Thereupon, the algorithm iteratively looks at the earliest pending transitions, declaring them as fixed, and propagating their effect through gates and channels. We highlight two noteworthy properties of the algorithm: (a) The delay  $\delta(T)$  is a function of the previous-output-to-input delay T=t-t' (see line 27). (b) A pending output transition of a channel is removed if a later input transition causes an output transition that occurs earlier (code line 29). In this case, the two transitions cancel at the channel output (pulse cancellation).

**Algorithm 2** Circuit simulation algorithm, until time  $\tau$

```

1: for all input ports I do

C \leftarrow \text{Outgoing}(I)

2:

copy all finite-time transitions from Fixed(I) to Pending(C)

3:

4: end for

5: for all channels C to gate B do

V \leftarrow \operatorname{Incoming}(C)

add (-\infty, \operatorname{Init}(V)) to \operatorname{Fixed}(C)

\operatorname{Prev}(C) \leftarrow (-\infty, \operatorname{Init}(V))

10: for all gates B do

add (-\infty, \operatorname{Init}(B)) to \operatorname{Fixed}(B)

11:

12: end for

13: t \leftarrow 0

14:

while t \leq \tau do

for all comp. \Gamma with a pending transition (t, x) at time t do

15:

move (t, x) from Pending(\Gamma) to Fixed(\Gamma)

16:

17:

end for

for all gates B do

18:

(C_1,\ldots,C_d) \leftarrow \operatorname{Incoming}(B)

19:

v \leftarrow f_B(\operatorname{Latest}(C_1, t), \dots, \operatorname{Latest}(C_d, t))

20:

if v \neq \text{Latest}(B, t) then add (t, v) to Fixed (B) endif

21:

22:

23:

for all channels C from gate B_1 to gate B_2 do

24:

(\delta_{\uparrow}, \delta_{\downarrow}) \leftarrow \text{Delay}(C)

if \exists a transition (t,x) in Fixed(B_1) at time t then

25:

26:

(t', x') \leftarrow \operatorname{Prev}(C)

if x = 1 then \delta \leftarrow \delta_{\uparrow}(t - t') else \delta \leftarrow \delta_{\downarrow}(t - t') endif

27:

\text{Prev}(C) \leftarrow (t + \delta, x)

28:

if t + \delta \leq t' then

29.

remove (t', x') from Pending(C)

30:

31:

32:

add (t + \delta, x) to Pending(C)

33:

end if

34:

end if

35:

t \leftarrow earliest time of a pending transition, otherwise +\infty

37: end while

for all output ports O do

C \leftarrow \operatorname{Incoming}(O) : V \leftarrow \operatorname{Incoming}(C)

39:

copy Fixed(V) to Fixed(C) and to Fixed(O)

41: end for

```

We now show that this algorithm indeed constructs an execution of a circuit  $\mathcal C$  (up to time  $\tau$ ). Let  $t_\ell$  be the value of t at the beginning of iteration  $\ell \geq 1$  of the algorithm (set in line 13 or 36). Denote by  $\delta_{\min}^{\mathcal C} > 0$  the minimal  $\delta_{\min}$  of all channels in circuit  $\mathcal C$  except for the 0-delay channels from inputs and to outputs.

**Lemma 5.** For all iterations  $\ell \geq 1$ , (a) no transition (s, x) with  $s \neq t_{\ell}$  is newly marked fixed in the iteration, (b) a

transition (s,x) added during iteration  $\ell$  either has time  $s=t_{\ell}$  or  $s>t_{\ell}+\delta_{\min}^{\mathcal{C}}$ , and (c) every transition at time  $t_{\ell}$  is fixed at the end of the iteration.

*Proof.* Statement (a) is implied by the fact that transitions are only marked fixed in lines 16 and 21, which act on transitions at time  $t_{\ell}$  only.

For (b), assume by contradiction that a transition (s,x) with  $s \leq t_\ell + \delta_{\min}^{\mathcal{C}}$  but different from  $t_\ell$  was added in iteration  $\ell$ . Such a transition can only be added via line 32. By our assumption and line 27,  $\delta(t_\ell - t') \leq \delta_{\min}^{\mathcal{C}} \leq \delta_{\min}$  must have held, where  $\delta \in \{\delta_\uparrow, \delta_\downarrow\}$  is the applicable channel function with minimal delay  $\delta_{\min}$  and t' is the time of the channel's last output transition. However, by Lemma 4, this requires  $t_\ell + \delta(t_\ell - t') \leq t_\ell + \delta_{\min} \leq t'$  which is in contradiction with the (negated) condition in line 29 necessary to reach line 32.

For (c), assume by contradiction that, at the end of iteration  $\ell$ , there exists a non-fixed transition  $(t_\ell,x)$ . Since line 16 marks all transitions at time  $t_\ell$  fixed and line 21 adds only fixed transitions at time  $t_\ell$ , the non-fixed transition must have been newly added by line 32. However, as in (b), we know that this requires  $\delta(t_\ell - t') \leq \delta_{\min}$ , again contradicting line 29.  $\square$

From an inductive application of Lemma 5, we obtain that the sequence of iteration start times  $(t_{\ell})_{\ell \geq 1}$  is strictly increasing without bound:

**Lemma 6.** Either the number of transitions generated by the simulation algorithm is finite, or, for all nonnegative integers  $k \geq 0$ , there exists some iteration  $\ell \geq 1$  such that  $t_{\ell} \geq k \cdot \delta_{\min}^{\mathcal{C}}$ .

*Proof.* We prove the lemma by induction. The base case k=0 is trivial since  $t_{\ell} \geq 0$  for all iterations  $\ell$ .

For the induction step, let  $t_\ell \geq k \cdot \delta_{\min}^{\mathcal{C}}$ . Let N be the number of distinct times of pending transitions in the interval  $\left[t_\ell, (k+1) \cdot \delta_{\min}^{\mathcal{C}}\right]$  at the start of iteration  $\ell$ . By Lemma 5, all pending transitions added in iterations from  $\ell$  onwards are at times  $s > t_\ell + \delta_{\min}^{\mathcal{C}} \geq (k+1) \cdot \delta_{\min}^{\mathcal{C}}$ . This means that all pending transitions before time  $(k+1) \cdot \delta_{\min}^{\mathcal{C}}$  are either removed or fixed at the end of iteration  $\ell + N - 1$ . Hence  $t_{\ell+N} \geq (k+1) \cdot \delta_{\min}^{\mathcal{C}}$ , which concludes the proof.

The following lemma proves that the generated transition lists are well-defined, in the sense that no later iteration can remove transitions that may have generated causally dependent other transitions already.

**Lemma 7.** Consider Algorithm 2 with line 30 changed to remove from set  $Pending(C) \cup Fixed(C)$ , i.e., both pending and fixed transitions. Then no fixed transition would ever be canceled.

*Proof.* Assume by contradiction that some iteration  $\ell \geq 1$  is the first in which a fixed transition is canceled. Thus, there exists a transition at time  $t_\ell$  that generated a new transition at some time  $t = t_\ell + \delta(t_\ell - t')$  that results in the cancellation of a fixed transition at time t', i.e.,  $t \leq t'$ . From the fact that the transition at time t' is already fixed at iteration  $\ell$ , Lemma 5 (a), and the fact that the sequence of  $t_\ell$ ,  $\ell \geq 1$ , generated by the modified algorithm is increasing, we obtain  $t' \leq t_\ell$ .

Fig. 5. A circuit solving unbounded SPF, consisting of an OR-gate fed-back by channel  ${\cal C}$ , and an exp-channel HT implementing a high-threshold buffer.

However, the condition in line 29 requires  $t_{\ell} + \delta(t_{\ell} - t') \leq t'$ . Since  $t_{\ell} - t' \geq 0$  and the channel is strictly causal (cf. Definition 1),  $\delta(t_{\ell} - t') > 0$  yields a contradiction.

This allows us to use the original line 30.

We are now ready for the main result of this section, which asserts the existence of a unique execution of our circuit C:

**Theorem 8.** For any  $0 \le \tau < \infty$ , the execution construction algorithm applied to circuits with strictly causal involution channels always terminates. At the end of iteration  $\ell \ge 1$ , the collection of signals  $s_{\sigma}$ , restricted to time  $[-\infty, t_{\ell}]$ , is the unique execution of circuit  $\mathcal{C}$  restricted to time  $[-\infty, t_{\ell}]$ . If the algorithm terminates at the beginning of iteration  $\ell$ , then this collection of signals is the unique execution of circuit  $\mathcal{C}$ .

*Proof.* From Lemma 6, we deduce that there is an iteration  $\ell \geq 1$  such that  $t_\ell > \tau$ , thus the algorithm terminates. From Lemma 5, we know that the algorithm does not add transitions with times  $< t_\ell$  during iteration  $\ell$ . By Lemma 7 in conjunction with the fact that lines 23–35 implement the output transition generation algorithm of Sec. IV, Algorithm 2 correctly computes channel outputs. To prove uniqueness of the execution, assume by contradiction that there is a second execution and consider the first differing transition. This contradicts either (E3) or (E4).

# VI. Possibility of Unbounded SPF

In this section, we show that unbounded SPF is solvable in our circuit model with strictly causal involution channels. We do this by verifying that the circuit shown in Fig. 5 indeed solves SPF. The circuit was inspired by the physical solution that provided Fig. 1, which consists of a fed-back OR-gate forming the storage loop and a subsequent high-threshold buffer. The high-threshold buffer is implemented by a (non-symmetric) exp-channel, with appropriately chosen parameters. Unless otherwise noted,  $\delta_{\infty}^{\uparrow}$ ,  $\delta_{\infty}^{\downarrow}$  and  $\delta_{\min}$  will refer to the parameters of the feedback channel.

We consider a pulse of length  $\Delta>0$  at time 0 at the input and reason about the behavior of the feed-back loop. Then, we show that its behavior can be translated to a legitimate SPF output by using a high-threshold buffer. We start by identifying two extremal cases: If  $\Delta$  is too small, then the pulse is filtered by the channel in the feed-back loop. If it is too large, the pulse is captured by the storage loop, leading to a stable output 1.

**Lemma 9.** If the input pulse's length  $\Delta$  satisfies  $\Delta \geq \delta_{\infty}^{\uparrow}$ , then the OR output has a unique rising transition at time 0.

**Proof.** Assigning the channel output  $s_C$  a single rising transition at time  $\delta_{\infty}^{\uparrow}$  is part of a consistent execution, in which the OR's output has a single rising transition at time 0. The lemma now follows from uniqueness of executions.

**Lemma 10.** If the input pulse's length  $\Delta$  satisfies  $\Delta \leq \delta_{\infty}^{\uparrow} - \delta_{\min}$ , then the OR output contains only the input pulse.

*Proof.* Channel C's input signal contains only two transitions: One at time  $t_1=0$  and one at time  $t_2=\Delta \leq \delta_{\infty}^{\uparrow}-\delta_{\min}$ . Since  $\delta_1=\delta_{\infty}^{\uparrow}$  and hence  $t_2\leq t_1+\delta_1-\delta_{\min}$ , the two pending transitions of C's output cancel by Lemma 4, and no further transitions are generated at the OR gate's output.

Now suppose that the input pulse length satisfies  $\delta_{\infty}^{\uparrow} - \delta_{\min} < \Delta_0 < \delta_{\infty}^{\uparrow}$ . For these pulse lengths  $\Delta_0$ , the OR output signal will contain the input pulse  $\Delta_0$ , followed by a series of pulses of lengths  $\Delta_1, \Delta_2, \ldots$  For all but one  $\Delta_0$ , this series will turn out to be either decreasing or increasing and finite, causing the output signal to be eventually 0 or eventually 1. To compute these pulse lengths, we define the auxiliary function

$$f(\Delta) = \delta_{\downarrow} (\Delta - \delta_{\uparrow}(-\Delta)) + \Delta - \delta_{\uparrow}(-\Delta) , \qquad (6)$$

which gives  $\Delta_n = f(\Delta_{n-1})$  for all  $n \geq 2$ . To see this, note that  $\Delta_{n-1}$  at the channel input is also present at the channel output, so the rising resp. falling transition is delayed by  $\delta_{\uparrow}(-\Delta_{n-1})$  resp.  $\delta_{\downarrow}(\Delta_{n-1}-\delta_{\uparrow}(-\Delta_{n-1}))$ . The first generated pulse starts from a zero channel input and thus

$$\Delta_1 = \Delta_0 - \delta_{\infty}^{\uparrow} + \delta_{\downarrow} (\Delta_0 - \delta_{\infty}^{\uparrow}). \tag{7}$$

The procedure stops if either  $f(\Delta_n) \leq 0$  (pulse canceled; the output is constant 0 thereafter), or if

$$f(\Delta_n) \ge \delta_{\min} > 0 \tag{8}$$

(pulse captured; the output is constant 1 thereafter).

The only case in which the procedure does not stop is if  $f(\Delta_1)=\Delta_1$ . There is a unique  $\Delta_1>0$  with this property, denoted  $\tilde{\Delta}_1$ : With  $\kappa=\delta_\uparrow(-\tilde{\Delta}_1)$  and hence  $\tilde{\Delta}_1=\delta_\downarrow(-\kappa)$  by the involution property, (6) reads  $\delta_\downarrow(\tilde{\Delta}_1-\kappa)=\kappa$  and hence  $\tilde{\Delta}_1-\kappa=-\delta_\uparrow(-\kappa)$ . Note carefully that  $\kappa$  is the period of the resulting periodic signal, and  $\gamma=\tilde{\Delta}_1/\kappa<1$  its duty cycle (0.5 in the case of symmetric channels, as  $\kappa=2\tilde{\Delta}_1$  here). Since the left-hand side of the resulting equation  $\delta_\downarrow(-\kappa)+\delta_\uparrow(-\kappa)-\kappa=0$  is positive for  $\kappa\to 0$  but negative for  $\kappa\to \min\{\delta_\infty^\uparrow,\delta_\infty^\downarrow\}$ , there is indeed a unique  $\kappa>0$  and a corresponding  $\tilde{\Delta}_1=\delta_\downarrow(-\kappa)<\kappa$ .

Given the upper bound on  $\Delta_0$  from Lemma 9 and (7), we must have  $\tilde{\Delta}_1 < \delta_{\downarrow}(0)$ . Since  $\Delta_1 \to \delta_{\downarrow}(0)$  as  $\Delta_0 \to \delta_{\infty}^{\uparrow}$  and  $\Delta_1 \to 0$  as  $\Delta_0 \to \delta_{\infty}^{\uparrow} - \delta_{\min}$ , there exists a unique  $\Delta_0$  such that  $\Delta_1 = \tilde{\Delta}_1$ . Denote it by  $\tilde{\Delta}_0$ .

The following lemma shows that the procedure indeed stops if and only if  $\Delta_1 \neq \tilde{\Delta}_1$ , and can be used to bound the number of steps until it stops.

**Lemma 11.** For f(.) given in (6) with fixed point  $\tilde{\Delta}_1$ , we have  $|f(\Delta_n) - \tilde{\Delta}_1| \ge (1 + \delta'_{\uparrow}(0)) \cdot |\Delta_n - \tilde{\Delta}_1|$  for all  $n \ge 1$  if  $\Delta_n > 0$ .

*Proof.* Differentiation of (6) provides  $f'(\Delta_n) = (1 + \delta'_{\uparrow}(-\Delta_n)) \cdot \delta'_{\downarrow}(\Delta_n - \delta_{\uparrow}(-\Delta_n)) + 1 + \delta'_{\uparrow}(-\Delta_n) \ge 1 + \delta'_{\uparrow}(0)$ , because  $\delta'_{\uparrow}(-\Delta_n) \ge \delta'(0)$  and  $\delta'_{\downarrow}(T) > 0$  for all T as  $\delta_{\downarrow}(.)$  is concave and increasing. The mean value theorem of calculus now implies the lemma.

**Theorem 12.** The fed-back OR gate with a strictly causal involution channel has the following output when the input pulse has length  $\Delta_0$ :

- If  $\Delta_0 > \tilde{\Delta}_0$ , then the output is eventually constant 1.

- If  $\Delta_0 < \tilde{\Delta}_0$ , then the output is eventually constant 0.

- If  $\Delta_0 = \tilde{\Delta}_0$ , then the output after the initial pulse  $\Delta_0$  is a periodic pulse train with uptime  $\tilde{\Delta}_1$ , period  $\kappa$  and duty cycle  $\gamma = \tilde{\Delta}_1/\kappa < 1$ .

Furthermore, the stabilization time in the first two cases is in the order of  $\log_a(1/|\Delta_0 - \tilde{\Delta}_0|)$  with  $a = 1 + \delta'_{\uparrow}(0)$ .

*Proof.* If  $\Delta_0 \geq \delta_{\infty}^{\uparrow}$  or  $\Delta_0 \leq \delta_{\infty}^{\uparrow} - \delta_{\min}$ , then Lemmas 9 and 10 show the theorem.

So let  $\Delta_0 \in (\delta_\infty^{\uparrow} - \delta_{\min}, \delta_\infty^{\uparrow})$ . By Lemma 11, the number of generated pulses until the procedure stops is in the order of  $\log_a(1/|\Delta_1 - \tilde{\Delta}_1|)$ . Setting  $g(\Delta_0) = \Delta_0 - \delta_\infty^{\uparrow} + \delta_{\downarrow}(\Delta_0 - \delta_\infty^{\uparrow})$  such that  $\Delta_1 = g(\Delta_0)$ , cp. (7), and applying the mean value theorem of calculus to this function, we see analogously as in the proof of Lemma 11 that

$$|\Delta_1 - \tilde{\Delta}_1| \ge (1 + \delta'_{\downarrow}(0)) \cdot |\Delta_0 - \tilde{\Delta}_0|$$

.

Hence, the number of generated pulses is also in the order of  $\log_a(1/|\Delta_0-\tilde{\Delta}_0|)$ . Since the period of the generated pulses is trivially upper-bounded by  $\delta_\infty^\uparrow$ , we have the same asymptotic bound on the stabilization time.

Finally, one can show that a high-threshold buffer with arbitrary threshold can be modeled by an exp-channel with properly chosen  $V_{th}$ :

**Lemma 13.** Let C be an exp-channel with threshold  $V_{th}$  and initial value 0, and let  $0 \le \Gamma < V_{th}$ . Then there exists some  $\Theta > 0$  such that every finite or infinite pulse train with pulse lengths  $\Theta_n \le \Theta$ ,  $n \ge 0$ , and duty cycles  $\Gamma_n \le \Gamma$ ,  $n \ge 1$ , is mapped to the zero signal by C.

*Proof.* Denote channel C's time constant by  $\tau$ , its pure delay by  $T_p$ , and its delay functions by  $\delta_{\uparrow}$  and  $\delta_{\downarrow}$  according to (3). Recall that  $\delta_{\min} = T_p$  for C.

Regarding the initial pulse  $\Theta_0$ , we observe that it is canceled by C whenever

$$\Theta_0 \le \delta_{\uparrow}(\infty) - \delta_{\min} = -\tau \ln(1 - V_{th}), \tag{9}$$

recall (3): Since the rising resp. falling transition has delay  $\delta_{\uparrow}(\infty)$  resp.  $\delta_{\downarrow}(\Theta_0 - \delta_{\uparrow}(\infty))$ , we find  $\Theta_0 + \delta_{\downarrow}(\Theta_0 - \delta_{\uparrow}(\infty)) - \delta_{\uparrow}(\infty) \le -\delta_{\min} + \delta_{\downarrow}(-\delta_{\min}) = 0$ .

For choosing an appropriate  $\Theta$  that also causes a cancellation of  $\Theta_n$ ,  $n \ge 1$ , we define the function

$$f(\theta) = \delta_{\uparrow} \left( \frac{1 - \Gamma}{\Gamma} \theta - T_p \right)$$

$$= \tau \ln \left( 1 - V_{th} e^{-\frac{1 - \Gamma}{\Gamma} \cdot \frac{\theta}{\tau}} \right) + T_p - \tau \ln(1 - V_{th}).$$

(10)

By Lemma 3, we have  $f(0) = T_p$ . Differentiating this function at  $\theta = 0$  gives

$$f'(0) = \frac{1-\Gamma}{\Gamma} \cdot \frac{V_{th}}{1-V_{th}} > 1$$

because  $\Gamma < V_{th}$ . This, by continuity of f' and  $f'(\theta)$  being decreasing, shows that there is some  $\Theta_f > 0$  such that  $f'(\theta) \ge$

1 for all  $\theta \in [0, \Theta_f]$ . Choosing  $\Theta = \min\{\Theta_f, -\tau \ln(1 - V_{th})/2\}$ , the mean value theorem of calculus applied to (10) provides

$$\forall \theta \in [0, \Theta] \colon f(\theta) \ge T_p + \theta, \tag{11}$$

and trivially

$$\Theta \le \frac{-\tau \ln(1 - V_{th})}{2} = \frac{\delta_{\uparrow}(\infty) - \delta_{\min}}{2}.$$

(12)

We now prove that this choice of  $\Theta$  satisfies the statement of our lemma. We know this already for the initial pulse  $\Theta_0$ , for the remaining pulses  $\Theta_n,\ n\geq 1$ , let  $t_1,t_2,\ldots$  be the transition times in the input pulse train with pulse lengths  $\Theta_n\leq\Theta$  and duty cycles  $\Gamma_n\leq\Gamma$ , i.e.,  $t_{2n}=t_{2n-1}+\Theta_n$  and  $t_{2n+1}=t_{2n}+\frac{1-\Gamma_n}{\Gamma_n}\Theta_n$ . Note that indeed the period length of the nth pulse is  $\Theta_n+\frac{1-\Gamma_n}{\Gamma_n}\Theta_n=\Theta_n/\Gamma_n$  and the pulse length is  $\Theta_n$ , which makes its duty cycle  $\Theta_n/(\Theta_n/\Gamma_n)=\Gamma_n$ .

We prove by induction that

$$\forall n > 0: \quad \delta_{2n-1} \ge T_p + \Theta_n \,, \tag{13}$$

where  $\delta_{2n-1}$  is the delay of the (2n-1)-st transition. From this, it then follows that all pulses get canceled by Lemma 4 using the equality  $\delta_{\min} = T_p$  of Lemma 3 ( $\delta_{\min}$  being that of the exp-channel C), because then  $\Theta_n \leq \Theta$  together with (13) implies  $t_{2n} = t_{2n-1} + \Theta_n \leq t_{2n-1} + \delta_{2n-1} - T_p$ . Thus, it only remains to prove (13).

For the base case n=1, we note that the duty cycle of the initial pulse may be arbitrary, hence  $t_1-(t_0+\Theta_0)$  may be arbitrarily small. However, we find

$$\delta_{1} = \delta_{\uparrow} (t_{1} - t_{0} - \Theta_{0} - \delta_{\downarrow}(\Theta_{0} - \delta_{\uparrow}(\infty)))$$

$$\geq \delta_{\uparrow} (-\delta_{\downarrow}(\Theta_{0} - \delta_{\uparrow}(\infty))) = \delta_{\uparrow}(\infty) - \Theta_{0}$$

$$\geq (\delta_{\uparrow}(\infty) + T_{p})/2 = \Theta + T_{p} \geq \Theta_{1} + T_{p}$$

where we used the involution property and (12).

For the induction step, we observe  $\delta_{2n} \leq T_p$  by Lemma 4 and the induction hypothesis and thus

$$\delta_{2n+1} = \delta_{\uparrow} \left( \frac{1 - \Gamma_n}{\Gamma_n} \Theta_n - \delta_{2n} \right) \ge f(\Theta_n),$$

where we used  $\Gamma_n \leq \Gamma$ . By (10), we have

$$\delta_{2n+1} \ge f(\Theta_n) \ge T_p + \Theta_n \tag{14}$$

since  $\Theta_n \leq \Theta$ , which concludes the proof.

By letting the time constant  $\tau$  grow, one can hence achieve the following result:

**Lemma 14.** Let  $\Theta > 0$  and  $0 \le \Gamma < 1$ . Then, there exists an exp-channel C such that every finite or infinite pulse train with pulse lengths  $\Theta_n \le \Theta$ ,  $n \ge 0$ , and duty cycles  $\Gamma_n \le \Gamma$ ,  $n \ge 1$ , is mapped to the zero signal by C.

*Proof.* We reuse the notation of the proof of Lemma 13.

Choose  $V_{th}$  such that  $\Gamma < V_{th} < 1$ . We show that there exists a  $\tau > 0$  for which (10) and (12) hold. After having shown this, we are done since then the exp-channel C with initial value 0, voltage threshold  $V_{th}$ , and time constant  $\tau$  satisfies the property of the lemma's statement.

We start by determining those  $\theta$  for which  $f'(\theta) \geq 1$ . A straightforward calculation reveals  $f''(\theta) < 0$  for all  $\theta$ , i.e., f' is decreasing. Furthermore, solving the equation

$$f'(\theta) = \frac{1 - \Gamma}{\Gamma} \cdot \frac{V_{th}e^{-\frac{1 - \Gamma}{\Gamma}\frac{\theta}{\tau}}}{1 - V_{th}e^{-\frac{1 - \Gamma}{\Gamma}\frac{\theta}{\tau}}} = 1 \tag{15}$$

gives the unique solution

$$\Theta_f = \tau \cdot \frac{\Gamma}{1 - \Gamma} \cdot \ln \frac{V_{th}}{\Gamma} .$$

Hence,  $f'(\theta) \geq 1$  for all  $\theta \in [0, \Theta_f]$ . Because  $\Theta_f$  as well as  $-\tau \ln(1 - V_{th})/2$  tend to infinity as  $\tau \to \infty$ , there exists a  $\tau > 0$  that satisfies (10) and (12).

By choosing  $\Gamma=\gamma(1+\varepsilon)<1$  according to Theorem 12 for some  $\varepsilon>0$  sufficiently small and  $\Theta$  sufficiently large, SPF input pulses with duration  $\Delta_0 \leq \tilde{\Delta}_0$  are mapped to a constant zero-output of the exp-channel according to Lemma 14. Let T be the time when pulse  $\Delta_n,\ n\geq 1$ , of the feed-back loop with duty cycle  $\geq \gamma(1+\varepsilon)$  has started. When choosing  $\Theta$  so large that the feed-back loop in Figure 5 has already locked to constant 1 at time  $T+\Theta$ , SPF input pulses with duration  $\Delta_0>\tilde{\Delta}_0$  lead to a single up-transition (occurring only after  $T+\Theta$ ) at the output. We can in fact establish:

**Theorem 15.** There is a circuit that solves unbounded SPF.

*Proof.* Since  $\Delta_0 \leq \tilde{\Delta}_0$  leads to a pulse train with duty cycle at most  $\gamma < \Gamma$  by Theorem 12, Lemma 14 guarantees a zero-output, provided  $\Theta$  is chosen larger than  $\tilde{\Delta}_1$ .

For  $\Delta_0 \geq \delta_\infty$ , Lemma 9 trivially guarantees a single rising transition at the output. For values  $\Delta_0$  satisfying  $\tilde{\Delta}_0 < \Delta_0 < \delta_\infty$ , there is some time T where a 1-pulse  $\Theta_n$  starts at the input of the exp-channel that will (along with its subsequent 0) have a duty cycle  $\Gamma_n \geq \Gamma > \gamma$ . By choosing  $\Theta$  so large that, by time  $T+\Theta$ , the last input transition (to 1) has already occurred, Lemma 14 in conjunction with Lemma 16 below not only guarantees that all pulses occurring before T cancel, but also the ones that occur before time  $T+\Theta$ : After all, even a single, long pulse  $\Theta_n = \Theta$  would still be canceled. Therefore, since the input of the exp-channel is already stable at 1 at time  $T+\Theta$ , only the final rising transition will eventually appear at the output.

#### VII. IMPOSSIBILITY OF BOUNDED SPF

# A. Continuity of Channels

In this subsection, we prove that strictly causal channels are continuous in a certain sense that we will define precisely.

To compare signals, we write  $s_1 \leq s_2$  if  $s_2$  is 1 whenever  $s_1$  is and denote with  $|s_1-s_2|$  the signal that is 1 whenever the value of  $s_1$  does not equal that of  $s_2$ . Consider signals  $s_1$  and  $s_2$  with  $s_1 \leq s_2$  supplied to a channel C. A simple induction on the input transitions of a signal  $s_1$  is already sufficient to show that  $f_C(s_1) \leq f_C(s_2)$  as well: Due to monotonicity of  $\delta_{\downarrow}, \delta_{\uparrow}$ , the occurrence time of every rising (resp. falling) transition can only decrease (resp. increase) when replacing an input transition at  $s_1$  by its earlier (resp. later) matching transition at  $s_2$ , irrespectively whether additional 1-pulses at  $s_2$  exist or not. We therefore obtain:

**Lemma 16.** Let  $s_1$  and  $s_2$  be signals such that  $s_1 \leq s_2$  and let C be a channel. Then, C is monotone in the sense that  $f_C(s_1) \leq f_C(s_2)$ .

We next define a distance for signals, for which channels will turn out to be continuous.

**Definition 17.** For a signal s and a time T, denote by  $\mu_T(s)$  the total duration in [0,T] where s is 1. That is,  $\mu_T(s)$  is the measure of the set  $\{t \in [0,T] \mid s(t)=1\}$ .

For any two signals  $s_1$  and  $s_2$  and every T, we define their distance up to time T by  $d_T(s_1, s_2) = \mu_T(|s_1 - s_2|)$ .

The detailed proof will start out from an arbitrary finite signal s, which consists of an arbitrary but finite number k of I-pulses (a non-zero time where s=1), separated by 0-intervals (a non-zero time where s=0), within [0,T]. We will show that inserting an arbitrary but finite sequence of K additional 1-pulses, having duration  $\varepsilon_1,\ldots,\varepsilon_K$  with total duration  $\sum_{i=1}^K \varepsilon_i \leq \varepsilon$ , during arbitrary 0-intervals leads to a signal s' with  $\mu_T(s') - \mu_T(s) \leq \varepsilon$  and  $\mu_T(f_C(s')) - \mu_T(f_C(s)) = O(\varepsilon)$  for  $\varepsilon \to 0$ . We will show this (in Theorem 24) by successively inserting  $\varepsilon_i$  into s and bounding the resulting changes of the measure. Note that doing this iteratively is enabled by Lemma 16. The changes of  $\mu_T(f_C(s')) - \mu_T(f_C(s))$  result from (i) the additional output pulse that is possibly generated by  $\varepsilon_i$ , and (ii) the inevitable shifts of all the subsequent output transitions.

We start with Lemma 18, which reveals that the worst-case effect on  $\mu_T(f_C(s'))$  is caused by an input 1-pulse that is appended at the beginning of the (final) 0-interval where it is inserted. We use the shorthand notation  $(x)_+$  for  $\max(x,0)$ . The subsequent Lemma 19 will show that  $\mu_T(f_C(s'))$  is increased by at most  $1+\delta'_\downarrow(-\delta_{\min})$  times the duration of the inserted input pulse.

**Lemma 18.** Let s be a signal that is eventually constant 0 and let C be a channel with s on its input. Denote by  $t_n$  the time of the last (falling) transition in s and by  $\delta_n$  its delay in the channel algorithm for C. Then, the maximal  $\mu_T(f_C(s'))$  among all s' obtained from s by appending one pulse of length  $\Delta > 0$  after time  $t_n$  is attained by the addition of the pulse at time  $t_n + (\delta_n - \delta_{\min})_+$  (which results in a cancellation of the last transition at the output if  $\delta_n \geq \delta_{\min}$ , and a right-shift of the last transition at the input if  $\delta_n \leq \delta_{\min}$ ).

*Proof.* We first show the lemma for  $T=\infty$  and then extend the result to finite T. Let  $s'_{\gamma}$  be the addition of the pulse of length  $\Delta$  to s at time  $t_n + \gamma$ .

For all  $0 \le \gamma \le (\delta_n - \delta_{\min})_+$ , the time from  $t_n$  to the last transition on  $f_C(s'_{\gamma})$  is

$$f(\gamma) = \gamma + \Delta + \delta_{\downarrow}(\Delta - \delta_{\uparrow}(\gamma - \delta_n))$$

.

In the class of all  $s_{\gamma}'$  with  $0 \leq \gamma \leq (\delta_n - \delta_{\min})_+$ , the maximum of  $\mu_{\infty}(f_C(s_{\gamma}'))$  is attained at the maximum of f. This is because the transition at time  $t_n + \gamma$  cancels that at time  $t_n$  in this case. The derivative of f is

$$f'(\gamma) = 1 - \delta'_{\downarrow}(\Delta - \delta_{\uparrow}(\gamma - \delta_n)) \cdot \delta'_{\uparrow}(\gamma - \delta_n) .$$

The condition  $f'(\gamma) = 0$  is equivalent to  $\delta'_{\downarrow}(\Delta - \delta(\gamma - \delta_n)) = 1/\delta'_{\uparrow}(\gamma - \delta_n)$ , which is in turn equivalent to  $\Delta = 0$ , as

$\delta'_{\downarrow}(-\delta_{\uparrow}(t))=1/\delta'_{\uparrow}(t)$  by Lemma 3. Hence,  $f'(\gamma)$  is never zero. Since  $f'(\gamma)\to 1$  as  $\gamma\to\infty$ , as the concave  $\delta_{\downarrow},\delta_{\uparrow}$  satisfy  $\lim_{t\to\infty}\delta'_{\uparrow}(t)=\lim_{t\to\infty}\delta'_{\downarrow}(t)=0$ , the derivative of f is always positive, hence f is increasing. This shows that  $\gamma=\delta_n-\delta_{\min}$  is a strictly better choice than any other  $\gamma$  in this class.

For the class of  $s'_{\gamma}$  with  $\gamma > (\delta_n - \delta_{\min})_+ \ge 0$ , the length of the appended pulse at the output is

$$g(\gamma) = \Delta + \delta_{\downarrow}(\Delta - \delta_{\uparrow}(\gamma - \delta_n)) - \delta_{\uparrow}(\gamma - \delta_n)$$

.

Since the transitions at  $t_n$  and  $t_n+\gamma$  do not cancel in this class, the maximum of  $\mu_\infty(f_C(s'_\gamma))$  is attained at the maximum of g. But it is easy to see, using the monotonicity of  $\delta$ , that g is decreasing. The maximum of g is hence attained at  $\gamma=(\delta_n-\delta_{\min})_+$ .

Consequently, the choice  $\gamma=\gamma_0=(\delta_n-\delta_{\min})_+$  maximizes  $\mu_\infty(f_C(s_\gamma'))$  in any case. By Lemma 4, this choice results in a cancellation of the last (falling) transition in  $f_C(s)$ , hence a right-shift of the latter in  $f_C(s')$ . This concludes our proof for  $T=\infty$ .

Let now T be finite. Denote by  $T_0$  the time of the last, falling, output transition in  $f_C(s'_{\gamma_0})$ . In this case, transitions of  $f_C(s)$  and  $f_C(s'_{\gamma_0})$  are the same except the last, falling, transition, which is delayed from  $t_n + \delta_n$  to  $T_0$ . We distinguish the two cases (a)  $T \leq T_0$  and (b)  $T > T_0$ . In case (a), the last transition of  $f_C(s)$  is delayed beyond T in  $f_C(s'_{\gamma_0})$ . Because all other transitions remain unchanged in all  $f_C(s'_{\gamma_0})$ , the measure  $\mu_T(f_C(s'_{\gamma_0}))$  is maximal among all  $\mu_T(f_C(s'_{\gamma_0}))$  if  $T \leq T_0$ . In case (b), we have  $\mu_T(f_C(s'_{\gamma_0})) = \mu_\infty(f_C(s'_{\gamma_0}))$ . But because  $\mu_T \leq \mu_\infty$  and  $\mu_\infty(f_C(s'_{\gamma_0}))$  is maximal among all  $\mu_T(f_C(s'_{\gamma_0}))$ , so is  $\mu_T(f_C(s'_{\gamma_0}))$  among all  $\mu_T(f_C(s'_{\gamma_0}))$ .  $\square$

Note that, owing to the above considerations, we can restrict our attention to  $T=\infty$  in the sequel.

**Lemma 19.** Let s be a signal that is eventually constant 0 and let C be a channel. Then, adding a pulse of length  $\varepsilon_1$  at or after the last transition of s causes  $\mu_T(f_C(s')) \leq \mu_T(f_C(s)) + (1 + \delta'_{\downarrow}(-\delta_{\min}))\varepsilon_1$ .

*Proof.* Denote by  $t_n$  the last transition in s and by  $\delta_n$  its delay. By Lemma 18, the worst-case effect on the  $\mu_T(f_C(s'))$  is achieved by appending the pulse at time  $t_n + (\delta_n - \delta_{\min})_+$ ; call the resulting signal s'.

We first assume  $\delta_n-\delta_{\min}>0$ . Here, the two new transitions in s' are  $t_{n+1}=t_n+\delta_n-\delta_{\min}$  and  $t_{n+2}=t_n+\delta_n-\delta_{\min}+\varepsilon_1$ . Their corresponding delays are  $\delta_{n+1}=\delta_{\min}$  and  $\delta_{n+2}=\delta_{\downarrow}(\varepsilon_1-\delta_{\min})$ . By the mean value theorem of calculus and Lemma 3, the duration of the resulting pulse is

$$\varepsilon_{1} + \delta_{n+2} - \delta_{n+1} = \varepsilon_{1} + \delta_{\downarrow}(\varepsilon_{1} - \delta_{\min}) - \delta_{\downarrow}(-\delta_{\min})

= (1 + \delta'_{1}(\xi)) \cdot \varepsilon_{1}$$

(16)

for some  $-\delta_{\min} \leq \xi \leq \varepsilon_1 - \delta_{\min}$ . Since  $\delta'_{\downarrow}(.)$  is decreasing and  $\delta'_{\downarrow}(-\delta_{\min}) > 0$ , we hence deduce  $0 \leq \delta_{n+2} - \delta_{n+1} \leq \delta'_{\downarrow}(-\delta_{\min})\varepsilon_1$ . Thus  $\mu_T(f_C(s'_1) - f_C(s)) = \varepsilon_1 + \delta_{n+2} - \delta_{n+1} \leq (1 + \delta'_{\perp}(-\delta_{\min}))\varepsilon_1$  as claimed in our lemma.

If  $\delta_n - \delta_{\min} \leq 0$ , then  $t_n$  is effectively replaced by  $t_n + \varepsilon_1$  in  $s_1'$ , i.e., right-shifted. If  $\delta_{\downarrow}(t_n - t_{n-1} + \varepsilon_1 - \delta_{n-1}) \leq \delta_{\min}$ , then the output signal is not changed since the pulse from  $t_{n-1}$

to  $t_n$  remains canceled. If  $\delta_{\downarrow}(t_n - t_{n-1} + \varepsilon_1 - \delta_{n-1}) > \delta_{\min}$ , then the measure is changed by

$$t_n + \varepsilon_1 + \delta_{\downarrow}(t_n - t_{n-1} + \varepsilon_1 - \delta_{n-1}) - t_{n-1} - \delta_{n-1}$$

.

Using Lemma 4 on s gives  $t_n \leq t_{n-1} + \delta_{n-1} - \delta_{\min}$  and thus the change in measure is at most  $\varepsilon_1 - \delta_{\min} + \delta_{\downarrow}(\varepsilon_1 - \delta_{\min}) \leq (1 + \delta'_{\downarrow}(-\delta_{\min}))\varepsilon_1$  (recall the derivation of (16)). This concludes our proof.

Note carefully that Lemma 19 can be applied iteratively for appending an arbitrary sequence of new pulses  $\varepsilon_1,\ldots,\varepsilon_K$ , one after the other: Provided  $\sum_{i=1}^K \varepsilon_i \leq \varepsilon$ , it ensures that the overall change in measure incurred by all the newly inserted pulses is at most  $(1 + \delta'_{\perp}(-\delta_{\min}))\varepsilon$ .

However, in addition to the increase of  $\mu_T(f_C(s'))$  as predicted by Lemma 19, which results from appending a new or enlarging the last pulse at the output, we also need to consider the resulting shifts of all the subsequent transitions that may already exist in  $f_C(s)$ : In particular, consider the rising transition at  $t_{n+1}$  that ends the 0-interval where a 1-pulse  $\varepsilon_1$  is inserted: The inserted pulse changes its previous output transition and, hence, the delay  $\delta_{n+1}$ .

To bound the resulting effects, we need to distinguish whether the 0-interval at the input completely vanishes when  $\varepsilon_1$  is inserted. The former will be considered in Lemma 21. Otherwise, i.e., if the 0-interval does not vanish completely, there are two possibilities: (i) The newly inserted pulse cancels, and hence right-shifts, the falling output transition caused by  $t_n$ , i.e., the beginning of the 0-interval, in the output signal. Lemma 18 revealed that this happens when the inserted pulse starts at  $t_n + (\delta_n - \delta_{\min})_+$  (possibly causing the left end of the 0-interval  $t_n$  at the input to be shifted right as well). Lemma 19 bounds the resulting shift to be at most  $(1 + \delta'_{\perp}(-\delta_{\min}))\varepsilon_1$ . Note carefully, though, that this change of measure does not include a possible effect on the delay  $\delta_{n+1}$  of the transition at time  $t_{n+1}$  that ends the 0-interval. The latter will be dealt with in Lemma 23. For the remaining case (ii), where the inserted pulse starts later than  $t_n + (\delta_n - \delta_{\min})_+$ , Lemma 20 bounds its effect on  $\delta_{n+2}$ :

**Lemma 20.** Let s be a signal that is eventually constant 1, with  $t_n$  and  $t_{n+1}$  denoting the beginning and the end of the last 0-interval of s, and  $\delta_n$  and  $\delta_{n+1}$  the delays caused by channel C. Then, inserting a pulse of length  $\varepsilon_1 < t_{n+1} - t_n$  at time  $t > t_n + (\delta_n - \delta_{\min})_+$  within this 0-interval (possibly causing the end of the 0-interval  $t_{n+1}$  to be shifted left) causes  $\delta_{n+1}$  to decrease by at most  $(1 + \delta'_{\uparrow}(-\delta_{\min}))\varepsilon_1$ , i.e.,  $\mu_T(f_C(s'))$  to increase by at most  $(1 + \delta'_{\uparrow}(-\delta_{\min}))\varepsilon_1$ .

*Proof.* Let  $a=t_{n+1}-t_n-\varepsilon_1-\delta_n$ , and  $v\geq 0$  be the difference between the falling transition of the inserted pulse  $\varepsilon_1$  and  $t_{n+1}$ . If v=0, then  $t_{n+1}$  is shifted left by  $\varepsilon_1$  at the input. We first show that  $a\geq -\delta_{\min}$ . This is trivially satisfied for  $\delta_n\leq \delta_{\min}$  since  $\varepsilon_1< t_{n+1}-t_n$ . For  $\delta_n>\delta_{\min}$ , we have  $t>t_n+\delta_n-\delta_{\min}$ . Since obviously  $t_{n+1}\geq t+\varepsilon$ ,  $a\geq -\delta_{\min}$  also holds in this case.

Let  $\eta_1 \geq 0$  be the difference between  $\delta_{n+1} = \delta_{\uparrow}(t_{n+1} - t_n - \delta_n) = \delta_{\uparrow}(a + \varepsilon_1)$  (before insertion) and  $\delta'_{n+1} = \delta_{\uparrow}(t_{n+1} - (t_{n+1} - v + \delta_d)) = \delta_{\uparrow}(v - \delta_d)$  (after insertion), with  $\delta_d$  denoting

the delay of the falling transition of the inserted pulse. As the delay  $\delta_u$  of the rising transition of the inserted pulse is  $\delta_u = \delta_\uparrow(t_{n+1} - v - \varepsilon_1 - t_n - \delta_n) = \delta_\uparrow(a-v)$ , we get  $\delta_d = \delta_\downarrow(t_{n+1} - v - t_{n+1} + v + \varepsilon_1 - \delta_u) = \delta_\downarrow(\varepsilon_1 - \delta_\uparrow(a-v))$ . We thus find

$$\eta_1 = \delta_{\uparrow}(a + \varepsilon_1) - \delta_{\uparrow}(v - \delta_{\downarrow}(\varepsilon_1 - \delta_{\uparrow}(a - v))). \tag{17}$$

Differentiating w.r.t. v, we obtain that  $\eta'_1$  is equal to

$$-\delta_{\uparrow}' (v - \delta_{\downarrow}(\varepsilon_1 - \delta_{\uparrow}(a - v))) \cdot \Big(1 - \delta_{\downarrow}' (\varepsilon_1 - \delta_{\uparrow}(a - v)) \delta_{\uparrow}' (a - v)\Big).$$

Since  $\delta'_{\downarrow}\left(\varepsilon_{1}-\delta_{\uparrow}(a-v)\right)<\delta'_{\downarrow}\left(-\delta_{\uparrow}(a-v)\right)=1/\delta'_{\uparrow}(a-v)$  by Lemma 3, we obtain  $\eta'_{1}<0$ . Therefore,  $\eta_{1}$  attains its maximum for v=0. Using the involution property, this reveals  $\eta_{1}\leq\delta_{\uparrow}(a+\varepsilon_{1})-\delta_{\uparrow}\left(-\delta_{\downarrow}(\varepsilon_{1}-\delta_{\uparrow}(a))\right)=\delta_{\uparrow}(a+\varepsilon_{1})+\varepsilon_{1}-\delta_{\uparrow}(a)$ . Using the concavity of  $\delta_{\uparrow}(.)$ , we finally obtain  $\eta_{1}\leq\varepsilon_{1}(1+\delta'_{\uparrow}(a))\leq\left(1+\delta'_{\uparrow}(-\delta_{\min})\right)\varepsilon_{1}$  since  $a\geq-\delta_{\min}$ .  $\square$

The next lemma handles the case where the inserted 1-pulse fills up the 0-intervall completely, i.e.,  $t_{n+1}-t_n=\varepsilon_1$  in the notation of Lemma 20. It is actually the dual of this lemma, in the sense that, rather than inserting a 1-pulse in a 0-interval, it deals with deleting a 0-interval in a 1-pulse.

**Lemma 21.** Let s be a signal of channel C that is eventually constant 0, with  $t_{n+2}$  denoting the last falling input transition and  $\delta_{n+2}$  its delay, with the last preceding 0-interval  $\varepsilon_1 = t_{n+1} - t_n$  starting at  $t_n > t_{n-1} + (\delta_{n-1} - \delta_{\min})_+$ . If the signal s' is obtained from s by entirely dropping the last preceding 0-interval, i.e., s' contains a single 1-pulse between  $t_{n-1}$  and  $t_{n+1}$ , then the resulting delay  $\delta'_{n+2}$  satisfies  $\delta'_{n+2} \leq \left(1 + \delta'_{\downarrow}(-\delta_{\min})\right)\varepsilon_1$ , i.e.,  $\mu_T(f_C(s'))$  increases by at most  $\left(1 + \delta'_{\downarrow}(-\delta_{\min})\right)\varepsilon_1$ .

*Proof.* It is obvious that the situation is exactly dual to Lemma 20, its proof hence applies literally after changing every rising transition to a falling one and vice versa.

The only remaining issue is to bound the propagation of the shift of a single output transition to later output transitions, which will be done in Lemma 23 below. It relies on the following technical lemma:

**Lemma 22.** Let s be a signal containing a rising transition at  $t_3$ , and let  $t_2$  and  $t_1$  be the times of the two previous transitions, respectively. With  $\Theta_2 = t_3 - t_2 > 0$  and  $\Theta_1 = t_2 - t_1 > 0$  denoting the previous 0-interval and 1-pulse, starting at  $t_2$  and  $t_1$ , respectively, and  $\delta_1$  denoting the channel delay of the transition at  $t_1$ , the other channel delays are  $\delta_2 = \delta_{\downarrow}(\Theta_1 - \delta_1)$  and  $\delta_3 = \delta_{\uparrow}(\Theta_2 - \delta_2)$ , and

$$\delta_{\uparrow}'(\Theta_2 - \delta_2)\delta_{\perp}'(\Theta_1 - \delta_1) < 1, \tag{18}$$

irrespectively of whether there are cancellations or not.

*Proof.* Due to concavity of  $\delta_{\uparrow}(.)$ , we observe

$$\delta_{3} = \delta_{\uparrow}(\Theta_{2} - \delta_{2}) = \delta_{\uparrow}(\Theta_{2} - \delta_{\downarrow}(\Theta_{1} - \delta_{1}))

\leq \delta_{\uparrow}(-\delta_{\downarrow}(\Theta_{1} - \delta_{1})) + \Theta_{2}\delta_{\uparrow}'(-\delta_{\downarrow}(\Theta_{1} - \delta_{1}))

= -\Theta_{1} + \delta_{1} + \frac{\Theta_{2}}{\delta_{\downarrow}'(\Theta_{1} - \delta_{1})};$$

(19)

in the final step, we used the involution property and Lemma 3. Invoking the latter once again, we find the following expression for  $\delta'_{\perp}(-\delta_3)$ :

$$\frac{1}{\delta'_{\uparrow}(\Theta_{2} - \delta_{\downarrow}(\Theta_{1} - \delta_{1}))} = \delta'_{\downarrow}(-\delta_{\uparrow}(\Theta_{2} - \delta_{\downarrow}(\Theta_{1} - \delta_{1})))$$

$$\geq \delta'_{\downarrow}(\Theta_{1} - \delta_{1} - \frac{\Theta_{2}}{\delta'_{\downarrow}(\Theta_{1} - \delta_{1})}) > \delta'_{\downarrow}(\Theta_{1} - \delta_{1}),$$

which implies (18) and completes our proof.

Finally, Lemma 23 considers a 1-pulse and a consecutive 0-interval and focuses on the falling and rising transition of the latter: It bounds the variation of their delays when the delay of the rising transition of the 1-pulse is decreased by  $\varepsilon_1$ , under the assumption that the 1-pulse did not cancel at the output initially. Note that Lemma 23 also holds (analogously) for the dual situation, i.e., a signal with the opposite transitions.

**Lemma 23.** Let s be an input signal of channel C containing a rising transition at  $t_3$ , with delay  $\delta_3$ , and let  $t_2$  and  $t_1$  resp.  $\delta_2$  and  $\delta_1$  be the times of the previous transitions resp. their delays. Assume that the preceding 1-pulse is not canceled at the output, i.e.,  $\delta_2 > \delta_{\min}$ . With  $\Theta_2 = t_3 - t_2 > 0$  and  $\Theta_1 = t_2 - t_1 > 0$  starting at  $t_2$  and  $t_1$ , respectively, a shifted signal  $\sigma'$  with decreased  $\delta'_1 = \delta_1 - \varepsilon_1$ ,  $\varepsilon_1 > 0$ , satisfies  $\delta_2 \leq \delta'_2 < \delta_2 + \delta'_\downarrow(-\delta_{\min})\varepsilon_1$  and  $\delta_3 \geq \delta'_3 > \delta_3 - \delta'_\uparrow(\Theta_2 - \delta'_2)\delta'_\downarrow(\Theta_1 - \delta_1)\varepsilon_1$ . If  $\delta_\downarrow(.)$  is two-times continuously differentiable and  $\varepsilon_1 \leq -\delta'_\downarrow(-\delta_{\min})/(2\delta''_\downarrow(-\delta_{\min}))$ , then  $\delta'_3 > \delta_3 - 2\varepsilon_1$ .

*Proof.* Using the concavity of  $\delta_{\downarrow}(.)$  in  $\delta_2 = \delta_{\downarrow}(\Theta_1 - \delta_1)$ , we obtain  $\delta_2' = \delta_{\downarrow}(\Theta_1 - \delta_1') = \delta_{\downarrow}(\Theta_1 - \delta_1 + \varepsilon_1) \leq \delta_{\downarrow}(\Theta_1 - \delta_1) + \varepsilon_1 \delta_{\downarrow}'(\Theta_1 - \delta_1)$ . Since  $\delta_2 > \delta_{\min}$ , Lemma 3 implies  $\Theta_1 - \delta_1 > -\delta_{\min}$  and hence  $\delta_{\downarrow}'(\Theta_1 - \delta_1) < \delta_{\downarrow}'(-\delta_{\min})$ . This confirms  $\delta_2' < \delta_2 + \delta_{\perp}'(-\delta_{\min})\varepsilon_1$ .

As for  $\delta_3^7 = \delta_{\uparrow}(\Theta_2 - \delta_2')$ , the mean value theorem of calculus yields, for some  $\xi \in [-(\delta_2' - \delta_2), 0]$ ,

$$\delta_3' = \delta_{\uparrow} (\Theta_2 - \delta_2 - (\delta_2' - \delta_2))

= \delta_{\uparrow} (\Theta_2 - \delta_2) - (\delta_2' - \delta_2) \delta_{\uparrow}' (\Theta_2 - \delta_2 + \xi)

> \delta_{\uparrow} (\Theta_2 - \delta_2) - \varepsilon_1 \delta_1' (\Theta_1 - \delta_1) \delta_{\uparrow}' (\Theta_2 - \delta_2'); (20)$$