# 8T-SRAM cell with Improved Read and Write Margins in 65 nm CMOS Technology

Farshad Moradi, Mohammad Tohidi, Behzad Zeinali, Jens K. Madsen

#### ▶ To cite this version:

Farshad Moradi, Mohammad Tohidi, Behzad Zeinali, Jens K. Madsen. 8T-SRAM cell with Improved Read and Write Margins in 65 nm CMOS Technology. 22th IFIP/IEEE International Conference on Very Large Scale Integration - System on a Chip (VLSI-SoC 2014), Oct 2014, Playa del Carmen, Mexico. pp.95-109, 10.1007/978-3-319-25279-7\_6. hal-01383730

## HAL Id: hal-01383730 https://inria.hal.science/hal-01383730

Submitted on 19 Oct 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Improved Read and Write Margins Using an 8T-SRAM Cell in 65nm CMOS Technology

Farshad Moradi, Mohammad Tohidi, Behzad Zeinali, and Jens K. Madsen

Integrated Circuits and Electronics Lab., Department of Engineering, Aarhus University, Aarhus, Denmark, {moradi, m.tohidi, beze, jkm}@eng.au.dk

Abstract—SRAM operation at subthreshold/weak inversion region provides a significant power reduction for digital circuits. SRAM arrays which contribute to a large amount of power consumption for the processors in sub-100nm technologies, however, cannot benefit from subthreshold operation. To this end, new SRAM technique on the circuit or architecture level is required. In this chapter, a novel 8T-SRAM cell is proposed which shows a significant improvement in write margin by at least 22% in comparison to the standard 6T-SRAM cell at supply voltage of 1V. Furthermore, read static noise margin of the proposed cell is improved by at least 2.2X compared to the standard 6T-SRAM cell. Although by the use of the proposed SRAM cell, the total leakage power is increased for superthreshold region, the proposed cell is able to work at supply voltages lower than 200mV through which the total power consumption and the robustness of the cell are improved significantly. The proposed circuit is designed in 65nm CMOS TSMC technology.

Keywords: SRAM; Subthreshold; Low-Power; Write Margin

#### 1 Introduction

SRAM memories take up to 80% of the total die area and up to 70% of the total power consumption of high-performance processors [1]. Therefore, there is a crucial need for high-performance, low-leakage, and highly robust SRAMs. Unfortunately by scaling the CMOS technology, particularly under scaled supply voltages, both read and write stabilities are affected by the existing intra- and inter-die variations. Furthermore, due to the use of large number of small geometry transistors in a memory array, process variations have a significant impact—leading to possible read, write, and hold failures. Furthermore, in standard 6T SRAMs, the conflict between read and write stabilities is an inevitable design constraint that needs to be considered meaning that by improving the write margin, read margin is degraded and vice versa.

To improve the SRAM cell functionality, several solutions have been proposed from device to architecture level. For instance, the use of new devices such as Fin-FETs that leads to a significant performance improvement [2-5]. At the cell level, new cells such as 7T, 8T, 9T, 10T, and 11T [6-15] have been proposed with the focus on improving read static noise margin (RSNM) or write margin (WM). At the architec-

ture level, proposed read and write assist techniques in literature can improve SRAM robustness and performance while occupying less area compared to the cell techniques (e.g. 8T and 10T) and can be used with any type of SRAM [16, 17]. To understand the existing challenges in SRAM design let us explain the operation of standard 6T-SRAM cell.

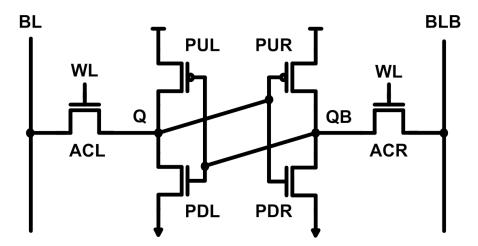

The standard 6T-SRAM cell is shown in Fig. 1 that consists of two back-to-back inverters (includes two pull-up PMOS and two pull-down NMOS transistors) and two NMOS access transistors connected to the bitlines with the gates connected to the wordline. During read, wordline is asserted and the voltage difference between bitlines is sensed using a sense amplifier. The read cycle is done via access transistors and the pull-down transistors. Stronger pull-down transistors (PDL and PDR) and weaker access transistors improves RSNM. On the other side, stronger access transistors and weaker pull-up transistors improves WM. Through upsizing, the SRAM cell can operate at very low supply voltages (i.e. low VDD<sub>min</sub>) with minimized threshold voltage variation with a penalty of increased area. However, continuously increasing process variations in sub-100nm technologies has led to a pronounced degradation in stability of SRAM cells especially at lower voltages.

Fig. 1. 6T-SRAM cell using CMOS technology.

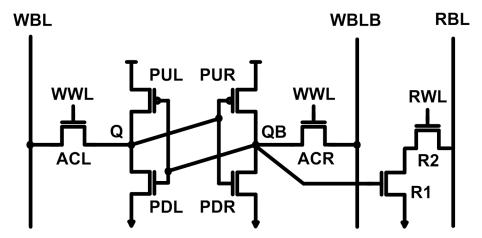

To overcome this issue, different cell techniques such as 8T-SRAM cell ameliorates the degraded robustness of the standard 6T-SRAM cell by separating read and write bitlines leading to a significant improvement in read static noise margin (RSNM) while the write margin is not affected. The standard 8T-SRAM cell is shown in Fig. 2. As it is seen, read and write cycles use different wordlines and bitlines. Noted, the standard 8T-SRAM cell uses a single-ended read scheme which reduces the swing of bitlines. The 8T-SRAM cell provides significantly improved RSNM (similar to the Hold Static Noise Margin (HSNM) of the standard 6T-SRAM cell) with similar access time, write time, and write margin. However, for the 8T-SRAM cell write assist techniques such as boosted wordline without affecting the read performance can be used.

Fig. 2. Standard 8T-SRAM cell [13].

Therefore, proposing a new SRAM cell to improve both read and write margins under scaled supply voltages is crucial for ultra-low power applications with low penalty on area, access time, and leakage power consumption

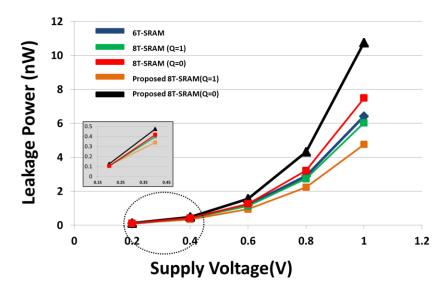

In this chapter, a novel 8T-SRAM cell is presented that improves both read and write operation margins. The proposed SRAM cell improves write and read noise margin by at least 22% and 2.2X compared to the standard 6T-SRAM cell, respectively. Furthermore, this method reduces gate leakage while increases subthreshold leakage compared to the standard 6T-SRAM cell in 65nm CMOS technology. In general, leakage power of the proposed cell increases by 67% at  $V_{\rm DD}{=}1V$  and 5.6% at  $V_{\rm DD}{=}300{\rm mV}$ . The proposed design improves the leakage power by 3% at  $V_{\rm DD}{=}200{\rm mV}$ . The threshold voltage of the transistors used in this paper is 300mV.

The rest of this chapter is structured as follows: in Section 2, the new 8T-SRAM cell is presented and described in different modes of operation. In Section 3, the simulations results are presented and discussed. We conclude in Section 4.

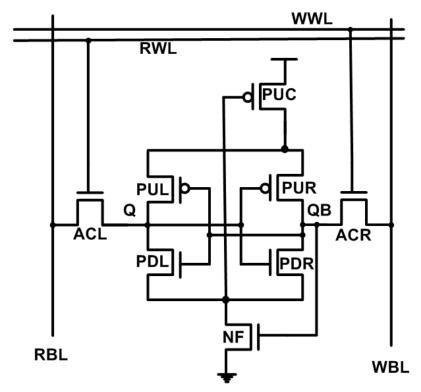

Fig. 3. Proposed 8T-SRAM cell.

#### 2 The proposed 8T-SRAM cell

Fig. 3 shows the proposed 8T-SRAM cell where two transistors, one NMOS and one PMOS are added to the standard 6T-SRAM cell while the mechanism of read is single-ended [18]. During read, only RWL is asserted while during write both WWL and RWL signals are set to high. In this SRAM cell structure, transistor PUC is used to improve the write margin of the circuit when a "1" is stored on the storage node Q. In this mode, when the value on QB is "0", the voltage on the drain of NF increases that weakens the drivability of PUC. Therefore, writing "0" on storage node becomes easier. When QB keeps "1", however, the write margin is not expected to be improved. In this case, to improve the write margin of SRAM cell, PUR is sized smaller than PUL that results in an improved write margin in this mode as well. During read, ACL turns on while ACR is kept in cut-off region. When Q holds a "0", transistors PDL and NF help to discharge the bitline capacitance to a level to be sensed by a sense amplifier. In this mode, transistors PDR, PUL, and ACR are OFF. Sizing down the transistor PDR will improve read margin due to the fact that the discharging path of QB to ground is weakened. Noted, the stacking effect lowers the current through the transistor PDR. In case the node Q holds a "1", transistor NF is OFF. Therefore, no discharging path exist from node Q to ground that results in significant improvement in read static noise margin (RSNM). In general, RSNM of the proposed circuit is improved by at least 2.2X compared to the standard 6T-SRAM cell and is similar to the standard 8T-SRAM cell considering this fact that write margin is not improved in the standard 8T-SRAM cell. During hold, both RWL and WWL signals are set to low turning off the access transistors. The data retention of this cell depends on the bit stored on the cell. When Q holds a "1" the node QB will be floating that will give an uncertainty of the circuit. Although, the level of voltage on node QB is not zero, due to the stacking effect of PDR-NF where the drain of the transistor NF goes to a level equals to the voltage on node QB, the transistor PDR will turn off completely. However, when storage node is holding a "0", the data retention improved due to the fact that both NF and PDR are ON that keeps "0" at node QB.

Similar to the standard 8T-SRAM cell, the proposed cell uses a single-ended read approach which definitely reduces the swing of the output. However, different techniques can be used to compensate this effect such as a pseudo-differential sensing scheme that can be used for our proposed SRAM cell [19]

The simulation results for the circuit for different modes will be discussed in the next section.

#### 3 Simulation Results and Comparison

Simulation results are done using 65nm CMOS technology models at room temperature (i.e. 27°C) at different supply voltages from subthreshold to superthreshold to region. In this section, the proposed SRAM cell is simulated at different modes of operation.

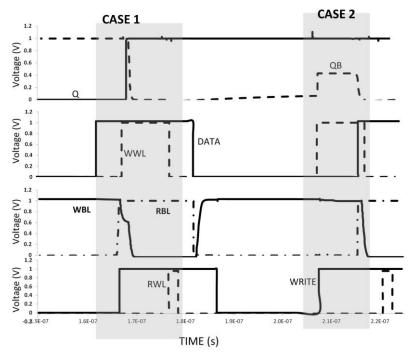

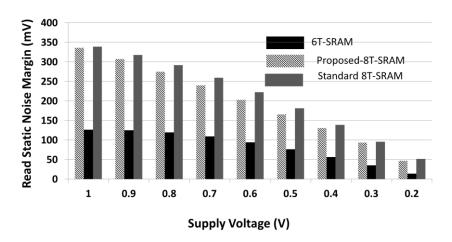

To evaluate the read stability of an SRAM cell Read Static Noise Margin (RSNM) is used. RSNM is defined as the length of the side of the largest square that can fit into the lobes of the butterfly curve. Butterfly curve is obtained by drawing and mirroring the inverter characteristics while access transistors are ON and bitlines are precharged to V<sub>DD</sub> [20]. For the proposed SRAM cell, however, only left side of the circuit defines the stability of the circuit. The reason is attributed to this fact that, when Q holds "1", increasing the value of QB even to very large values does not change the data stored on node Q. To this end, we simulate the proposed SRAM cell for cases Q="0", WWL="1", and RWL="0" (i.e. CASE 1) and also Q="1", WWL="1", and RWL="0" (i.e. CASE 2). The shadowed part of Fig. 4 shows the operation of the proposed SRAM cell when WWL is asserted and RWL signal is low. Here, we consider two cases. In CASE 1, node OB discharges via transistor ACR to ground that is a successful write while RWL is kept at "0". However, in CASE 2 where Q holds "1", although the voltage on node QB increases to 0.4V, the value on node Q is not flipped. This proves a very high robustness of circuit even at very high input noises when Q stores "1". This concludes that single ended writing will fail (i.e. CASE 2) that leads us to turn on both access transistors during write cycle. The results for RSNM of the proposed SRAM cell compared to the standard 6T-SRAM cell at different supply voltages are shown in Fig. 5. As it is shown, 2.66 X improvements in RSNM is achieved by the use of the proposed 8T-SRAM cell compared to the standard 6T-SRAM cell. At lower supply voltages such as 200mV, the proposed 8T-SRAM cell shows 4.86X improved RSNM. Due to this fact, the proposed SRAM cell is able to operate with a high margin at very low supply voltages (i.e. subthreshold/weak inversion region). However, the standard 8T-SRAM cell shows slightly better RSNM compared to the proposed 8T-SRAM cell.

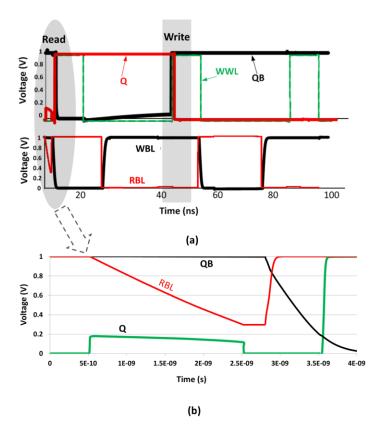

**Fig. 4.** Waveforms of the proposed 8T-SRAM cell (Shadowed part shows when WWL="1" and QB=1 or "0").

Fig. 5. RSNM results for the standard 6T-SRAM, 8T-SRAM and the proposed 8T-SRAM cell.

To clarify the operation of the proposed circuit, the SRAM operation at different modes is shown in Fig. 6. As it is shown, during read, when Q holds "0", while the BL has been discharged to 300mV, voltage on node Q is not increased higher than 0.2V that is due to the stacking effect of transistors from node QB to ground and the small size of the transistor PDR in the cell (Fig. 6(b)). This confirms the robustness of the proposed circuit during read (i.e. RSNM). The successful writing "0" is shown in Fig. 6(a) when both RWL and WWL are set to high.

Fig. 6. (a) The proposed 8T-SRAM cell waveforms (b) Read operation.

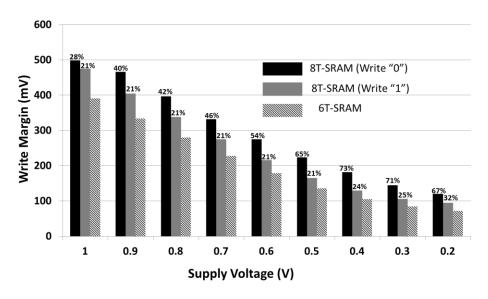

Write margin is another metric used to evaluate the stability of an SRAM cell in write mode. Different methods have been used to find the WM of an SRAM cell [21]. For the WM simulations, we choose the Word-Line (WL) voltage sweep method. In this method the bitline will be connected to the appropriate voltages to enable flipping the data on the storage node. Then WL and WLB are swept from 0V to 1V and 1V to 0V, respectively. WM is calculated as the difference between V<sub>DD</sub> and WL voltage when the data stored in the cell is flipped. Fig. 7 illustrates the write margin of the proposed 8T-SRAM cell versus the standard 6T-SRAM cell. As it can be seen, when writing "0", the proposed 8T-SRAM improves the write margin between 28%-73% at different supply voltages. The proposed 8T-SRAM cell improves write margin by at least 21% when writing "1". As it is shown in Fig. 7, improvement in write margin of the proposed circuit is increased at lower supply voltages enabling this circuit to work at extremely low supply voltages. Fig. 8 shows an example of writing "0".

**Fig. 7.** Write margin of the proposed 8T-SRAM cell versus the standard 6T-SRAM cell when writing "0" and "1" (the standard 8T-SRAM provide negligibly smaller WM in comparison to the standard 6T-SRAM cell).

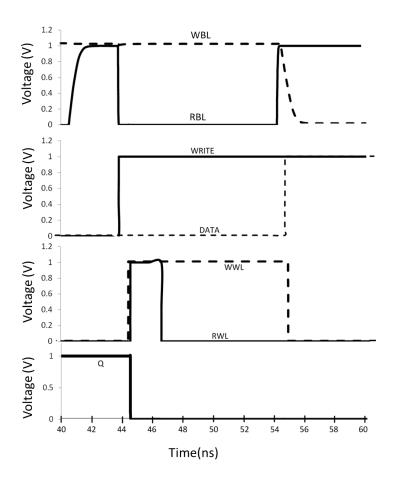

Fig. 8. Write "0" for the proposed 8T-SRAM cell.

To achieve improvements in both read and write, the proposed 8T-SRAM cell must be sized carefully. To achieve the best write improvement when writing "1", PUR is sized smaller than PUL. In addition, improved read noise margin can be achieved by down-sizing the PDR transistor. The sizing of the proposed 8T-SRAM cell used is tabulated in Table.1.

**Table 1.** Sizing of the standard 6T, 8T and the proposed 8T-SRAM cells.

| 6T-SRAM Cell |      | Proposed 8T- | SRAM | Standard 8T-SRAM |      |  |

|--------------|------|--------------|------|------------------|------|--|

| ACL,ACR      | 180n | ACL, ACR     | 180n | ACL, ACR         | 180n |  |

| PDR          | 230n | PDR          | 200n | PDR,PDL          | 200n |  |

| PUL          | 230n | PUL          | 150n | PUL              | 150n |  |

| PUR, PDR     | 150n | PUR          | 120n | PUR              | 150n |  |

|              |      | PUC          | 150n | R1               | 180n |  |

|              |      | PDL, NF      | 300n | R2               | 230n |  |

**Table 2.** the leakage current of the standard 6T and the proposed 8T SRAM cells.

| 6T-SRAM Current (nA).<br>G:gate, D: Drain, and S:<br>Source |       |       | Proposed 8T-SRAM Current<br>(nA). G:gate, D: Drain, and S:<br>Source |     |       | Standard 8T-SRAM Current<br>(nA). G:gate, D: Drain, and S:<br>Source |       |     |       |       |       |

|-------------------------------------------------------------|-------|-------|----------------------------------------------------------------------|-----|-------|----------------------------------------------------------------------|-------|-----|-------|-------|-------|

| Tr.                                                         | G     | D     | S                                                                    | Tr. | G     | D                                                                    | S     | Tr  | G     | D     | S     |

| ACL                                                         | 0.323 | 0.017 | 0.15                                                                 | ACL | 0.36  | 0.084                                                                | 0.209 | ACL | 0.1   | 1.3   | 1.16  |

| ACR                                                         | 0.153 | 1.802 | 1.853                                                                | ACR | 0.144 | 0.178                                                                | 0.187 | ACR | 0.23  | 0.098 | 0.104 |

| PUL                                                         | 0.563 | 4.191 | 4.767                                                                | PUL | 0.462 | 2.95                                                                 | 3.428 | PUL | 0.115 | 1.13  | 1.01  |

| PUR                                                         | 0.208 | 1.856 | 1.66                                                                 | PUR | 0.122 | 1.132                                                                | 0.979 | PUR | 0.31  | 2.69  | 2.68  |

| PDL                                                         | 0.234 | 2.361 | 2.103                                                                | PDL | 0.246 | 1.497                                                                | 1.73  | PDL | 0.52  | 2.72  | 3.24  |

| PDR                                                         | 1.47  | 4.455 | 5.892                                                                | PDR | 0.887 | 3                                                                    | 2.02  | PDR | 0.114 | 1.37  | 1.24  |

|                                                             |       |       |                                                                      | PUC | 0.47  | 4.42                                                                 | 4.896 | R1  | 1.10  | 3.90  | 1.13  |

|                                                             |       |       |                                                                      | NF  | 0.001 | 4.967                                                                | 5.025 | R2  | 0.57  | 1.02  | 0.075 |

|                                                             |       |       |                                                                      |     |       |                                                                      |       |     |       |       |       |

Another important metric for An SRAM cell is leakage power consumption. To measure the leakage power consumption of the proposed SRAM cell compared to the standard 6T-SRAM cell, the leakage current of each transistor was measured that is shown in table 2. As it is shown the leakage through access transistors is reduced significantly that is attributed to the raised voltage level of storage node holding "0". However, the total leakage current of the proposed cell is increased when the stored bit is "1" while in case of Q="0", the total leakage of the proposed cell is less than the standard 6T and 8T-SRAM cells. For this simulation a bitline capacitance of 200fF and the supply voltage of V<sub>DD</sub> equals to 1 V at room temperature have been considered. To show the power degradation of the proposed SRAM cell at different supply voltage, we calculate the total power consumption of the proposed cell versus the standard 6T-SRAM and 8T-SRAM cells for V<sub>DD</sub>=1V to V<sub>DD</sub>=200mV. As it is shown in Fig. 9, leakage power of the proposed SRAM cell compared to the standard 6T-SRAM cell is degraded by 14.2% and 67% for supply voltages of 0.2V and 1V, respectively when the stored bit is "0" while for the case of Q="1", the proposed cell improves the leakage power by 34% and 23% at supply voltage of 1V and 0.4V, respectively. In comparison to the standard 8T-SRAM cell for the case of Q="1", leakage current is degraded by 7% to 21% for VDD=0.2 V and 1V, respectively while for the case of Q="0", the leakage current of the proposed cell increases by 20% and 43% for VDD=0.2V and 1V, respectively.

**Fig. 9.** Leakage power increase percentage for proposed 8T-SRAM cell versus the standard 6T-SRAM cell.

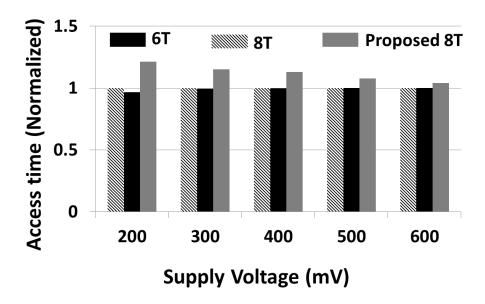

In this part, the access time and the write time of the proposed circuit is explored in comparison with the standard 6T and 8T-SRAM cells [6]. Access time is measured as the time required for discharging the bitline voltage so that the difference between bitline voltage and  $V_{\rm DD}$  (i.e.  $V_{\rm sense}$ ) can be sensed by the sense amplifier circuit. To this end, we simulate the proposed 8T-SRAM cell at supply voltage of  $V_{\rm DD}{=}300 mV$  at room temperature. Fig. 10 illustrates the comparison between the proposed 8T-SRAM cell versus standard 6T-SRAM and the 8T-SRAM cells. As it is seen, the maximum degradation is at lower supply voltage due to the weakened drivability of the transistors at lower supply voltages. The maximum degradation is at 200mV (21%) which improved by increasing the supply voltage. For instance, at  $V_{\rm DD}{=}600 mV$ , the access time degradation is only 4% compared to the standard 6T and 8T-SRAM cells and all the circuit show similar access time at  $V_{\rm DD}{=}800 mV$  and above.

**Fig. 10.** Access time comparison for different SRAM cells (Access time is normalized to the access time of the standard 6T-SRAM cell at different supply voltages).

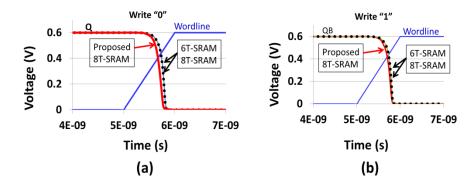

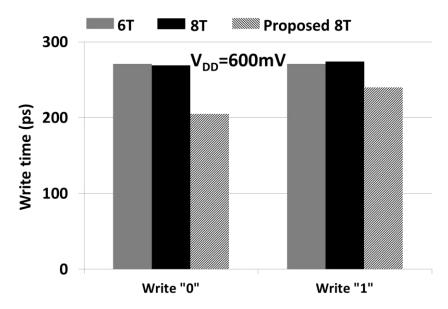

Another metric to compare different SRAM topologies is write time. In the proposed circuit due to the increased write margin, it is expected a faster data flipping on storage nodes during write cycle. Due to the asymmetry nature of the proposed SRAM cell, we simulate the cell for write "0" and write "1". Fig. 11 (a) and (b) illustrate the proposed SRAM cell behavior for both cases. As it is seen, the proposed SRAM cell provides faster write during write "0" compared to write "1" that is attributed to the weakened pull-up path through which the contention between PMOSs and access transistors is reduced. Fig. 12 shows a comparison between the proposed SRAM cell versus the standard 6T and 8T SRAM cells at supply voltage of 600mV. Here, the write time improvement percentages provided by the proposed cell over the standard 6T and 8T SRAM cells during write "0" and write "1" are 25% and 12%, respectively. Noted, the improvement for write time at lower supply voltages is degraded due to the weakened driving current of transistors in the stacked configuration of the proposed SRAM cell. To this end, the use of low-Vth transistors can help to solve the low drivability of the stacked transistors with the penalty of area overhead.

Fig. 11. (a) write "0" and (b) write "1" for the proposed 8T-SRAM cell at  $V_{DD}$ =0.6V.

**Fig. 12.** Write time comparison between the standard 6T and 8T SRAM cells with the proposed 8T-SRAM cell.

One of the main issues for the proposed 8T-SRAM cell is floating storage node (QB) when the stored data is "1". Therefore, a thorough discussion for the proposed cell is required to evaluate the cell operation. As mentioned, during hold, read "1", and write "1", the storage node QB is grounded which turns off the NF transistor disconnecting the floating node from ground. Therefore, the proposed circuit is simulated for each cycle. During hold, the drain of NF is charged to a voltage equals to 53.5 mV which is equals to the voltage on node QB. The circuit was simulated for a long stay in hold time which shows the voltage on nodes QB and the drain of NF becomes equal and fixed at 53.5 mV. This leads to a turned-off transistor PDR which reduces the leakage

current through storage node to ground. All three SRAM cells were simulated to measure their leakage current through storage nodes to ground under same condition. During hold, we measured the leakage through transistors connected to ground to get an estimation of the total leakage when the node QB is floating. Simulation results show a fixed leakage current of 1.72nA through pull-down transistors to ground while the standard 6T and 8T SRAM cells show a total leakage current of 2.59nA and 2.63nA through transistors connected to ground, respectively. However, as shown before, the total leakage power of the proposed circuit is higher than as for the standard 6T-SRAM cell when the stored data is "0".

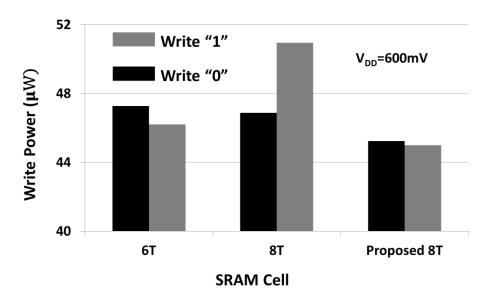

During write "0", as explained in section 2, the QB node is floating which helps to improve the write margin and write time. Based on this fact, the total write power is reduced, as well. To this end, the total power consumption of the standard 6T and 8T is compared with the proposed 8T-SRAM cell which is shown in Fig. 13. As it is seen, the proposed design provides minimum write power consumption during write "0" which is attributed to the floating node QB and drain of transistor NF.

Fig. 13. Write power consumption for different SRAM cells.

During read due to the single-ended structure of the proposed circuit in which the node QB is decoupled from bitline, it will not affect the read process. Assuming that the voltage on node QB is 53.5mV, it will continue to keep this voltage during read, as well. To evaluate the cells during read "1", the read power consumption of each circuit was measured. The standard 6T and 8T SRAM cells consume a read power of 119.46nW and 1.9758nW, respectively, while the proposed 8T-SRAM consumes 0.93nW (930pW). Consequently, we can claim that the floating node QB has no effect on the performance as well as it improves the power consumption during read and write.

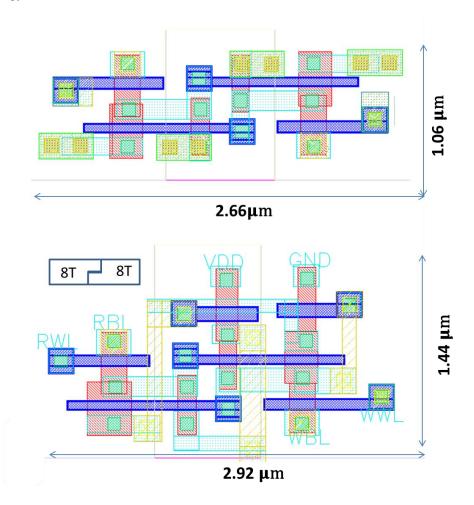

Finally, the area of the proposed circuit in comparison to the standard 6T-SRAM cell is shown for a single cell. As it is shown in Fig. 14, the proposed technique increases the area by 49% in comparison the standard 6T-SRAM cell. However, due to the L-shape of the cell layout, the total area overhead of the cell will be reduced. The standard 8T-SRAM cell, however, introduces 33% area overhead in TSMC 65nm technology.

Fig. 14. Write power consumption for different SRAM cells.

All in all, the proposed SRAM cell, similar to the standard 8T-SRAM cell, improves read margin significantly while the write margin is improved, as well. Therefore, the proposed design has the advantages of improved write margin and write-time over the standard 6T and 8T-SRAM cells. Due to the asymmetric nature of the proposed SRAM cell, write margin improvement when writing "0" is larger than the case of "1". Therefore, as mentioned, by careful sizing of the transistors in our design, higher

write margin (i.e. more symmetric write) will be achieved that enables designers to scale the supply voltage aggressively for ultra-low power applications.

#### 4 CONCLUSIONS

In this chapter, a new 8T-SRAM cell was discussed which shows improvement in read and write margins by 2.2X and 22%, respectively, compared to the standard 6T-SRAM cell. In addition, the proposed design improves the gate leakage power consumption while increases the subthreshold leakage compared to the 6T-SRAM cell. All in all, the proposed design improves read and write margins without any penalty in leakage power at subthreshold region compared to the standard 6T-SRAM cell. Furthermore, the proposed 8T-SRAM cell has a superior advantage of improved write margin in comparison to the standard 8T-SRAM cell.

#### References

- M. Horowitz, "Scaling, power, and the future of MOS," in IEDM Tech. Dig., pp. 9–15, Dec. 2005.

- F. Moradi, S.K. Gupta, G. Panagopoulos, D.T. Wisland, H. Mahmoodi, and K. Roy, "Asymmetrically doped FinFETs for low-power robust SRAMs," IEEE Trans. Electron Devices, vol. 58, no. 12, pp.4241-4249, Dec. 2011.

- N. Collaert, A. De Keersgieter, A. Dixit, I. Ferain, L.-S. Lai, D. Lenoble, A. Mercha, A. Nackaerts, B. J. Pawlak, R. Rooyackers, T. Schulz, K. T. Sar, N. J. Son, M. J. H. Van Dal, P. Verheyen, K. von Arnim, L. Witters, M. De, S. Biesemans, and M. Jurczak, "Multi-gate devices for the 32 nm technology node and beyond," in Proc. 37th ESSDERC, Sep. 11–13, 2007, pp. 143–146.

- 4. A. B. Sachid, and C. Hu, "Denser and more stable SRAM using FinFETs with multiple fin heights," IEEE Trans. Electron Devices, vol. 59, no. 8, pp. 2037-2041, Aug. 2012.

- S. A. Tawfik, and V. Kursun, "Multi-threshold voltage FinFET sequential circuits," IEEE Trans. VLSI systems, vol. 19, no. 1, pp. 151-156, Jan. 2011.

- N. Verma and A. Chandrakasan, "A 256 kb 65 nm 8T subthreshold SRAM employing sense-amplifier redundancy," IEEE J. Solid-State Circuits, vol. 43, no. 1, pp. 141–149, Jan. 2008.

- 7. R. E. Aly and M. A. Bayoumi, "Low-power cache design using 7T SRAM cell," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 54, no. 4, pp. 318–322, Apr. 2007.

- 8. B. Madiwalar and B.S. Kariyappa, "Single bit-line 7T SRAM cell for low power and high SNM" International Multi-Conference on iMac4s, pp. 223-228, Mar 2013.

- 9. L. Wen, Z. Li, and Y. Li, "Differential-read 8T SRAM cell with tunable access and pull-down transistors," Electronics Letters, vol. 48, no. 20, pp. 1260-1261, Sep. 2012.

- M. H. Tu, J.-Y. Lin, M.-C. Tsai, C.-Y. Lu, Y.-J. Lin, M.-H. Wang, H.-S. Huang, K.-D. Lee, W.-C. Shih, S.-J. Jou, and C.-T. Chuang, "A single-ended disturb-Free 9T subthreshold SRAM with cross-point data-aware write word-line structure, negative bit-line, and adaptive read operation timing tracing," IEEE J. Solid-State Circuits, vol. 47, no. 6, pp. 1469–1482, Jun. 2012.

- 11. I. J. Chang, J. Kim, S. P. Park, and K. Roy, "A 32 kb 10T sub-threshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS," IEEE J. Solid State Circuits, vol. 44, no. 2, pp. 650–658, Feb. 2009.

- 12. F. Moradi, D. T. Wisland, S. Aunet, H. Mahmoodi, and C. Tuan Vu, "65NM sub-threshold 11T-SRAM for ultra-low voltage applications," in SOC Conference, IEEE International, 2008, pp. 113-118.

- 13. B. H. Calhoun, and A. P. Chandrakasan, "Static noise margin variation for sub-threshold SRAM in 65 nm CMOS," IEEE J. Solid-State Circuits, vol. 41, pp.1673-1679, Jan. 2006

- F. Moradi, J.K. Madsen, "Robust subthreshold 7T-SRAM cell for low-power applications," IEEE Midwest Symposium on Circuits and Systems (MWSCAS), pp.893,896, 3-6 Aug. 2014

- F. Moradi, J.K. Madsen, "Improved read and write margins using a novel 8T-SRAM cell" International Conference on Very Large Scale Integration (VLSI-SoC), pp.1,5, 6-8 Oct. 2014

- F. Moradi, D.T. Wisland, H. Mahmoodi, Y. Berg, T. V. Cao, "New SRAM design using body bias technique for ultra-low power applications," 11th International Symposium on Quality Electronic Design (ISQED), pp.468,471, 22-24 March 2010.

- 17. H. Farkhani, A. Peiravi, F. Moradi, "A new asymmetric 6T SRAM cell with a write assist technique in 65nm CMOS technology" (2014) Microelectronics Journal, 2014

- 18. F. Moradi and Jens K. Madsen, "Improved read and write margins using a novel 8T-SRAM cell," Very Large Scale Integration (VLSI-SoC), 2014 22nd International Conference on , vol., no., pp.1,5, 6-8 Oct. 2014

- 19. S. Nalam, V. Chandra, C. Pietrzyk, R. Aitken, and B. Calhoun, "Asymmetric 6T SRAM with two-phase write and split bitline differential sensing for low voltage operation," in Proc. 11th Int. Symp. Quality Electronic Design (ISQED), Mar. 2010, pp. 139–146

- 20. E. Seevinck, F. J. List, and J. Lohstroh, "Static-noise margin analysis of MOS SRAM cells," IEEE J. Solid-State Circuits, vol. sc-22, pp. 748-754, Oct. 1987.

- J. Wang, S. Nalam, and B. H. Calhoun, "Analyzing static and dynamic write margin for nanometer SRAMs," in Proc. Int. Symp. Low Power Electron. Design, New York, 2008, pp. 129–134