### Methodology for the formal verification of temporal properties for real-time safety-critical applications based on logical time

Fabien Siron

#### ► To cite this version:

Fabien Siron. Methodology for the formal verification of temporal properties for real-time safety-critical applications based on logical time. Embedded Systems. Université cote d'azur, 2023. English. NNT: . tel-04355316v1

#### HAL Id: tel-04355316 https://inria.hal.science/tel-04355316v1

Submitted on 20 Dec 2023 (v1), last revised 11 Mar 2024 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

ÉCOLE DOCTORALE SCIENCES ET TECHNOLOGIES DE L'INFORMATION ET DE LA COMMUNICATION

# THÈSE DE DOCTORAT

Méthodologie de vérification formelle de propriétés temporelles pour les applications temps-réel critiques basées sur le concept de temps logique

### **Fabien SIRON**

Equipe Kairos, Centre Inria d'Université Côte d'Azur

Safe

**Présentée en vue de l'obtention du grade de docteur en** Informatique **d'**Université Côte d'Azur

Dirigée par : Dumitru POTOP-BUTUCARU, Chargé de recherche, Centre Inria d'Université Côte d'Azur Co-dirigée par : Robert DE SIMONE, Directeur de recherche, Centre Inria d'Université Côte d'Azur Soutenue le : 11 Décembre 2023

#### **Devant le jury, composé de :** Reinhard VON HANXLEDEN, Professor, Kiel University Pierre-Loïc GAROCHE, Professeur, École

Nationale de l'Aviation Civile Timothy BOURKE, Chargé de recherche, Centre Inria de Paris Damien CHABROL, Responsable Innovation et Stratégie Produit, Krono-Safe Amira METHNI, Architecte logiciel, Krono-

#### MÉTHODOLOGIE DE VÉRIFICATION FORMELLE DE PROPRIÉTÉS TEMPORELLES POUR LES APPLICATIONS TEMPS-RÉEL CRITIQUES BASÉES SUR LE CONCEPT DE TEMPS LOGIQUE

Methodology for the formal verification of temporal properties for real-time safety-critical applications based on logical time

**Fabien SIRON**

$\bowtie$

#### Jury :

#### Rapporteurs

Reinhard VON HANXLEDEN, Professor, Kiel University Pierre-Loïc GAROCHE, Professeur, École Nationale de l'Aviation Civile

#### Examinateurs

Timothy BOURKE, Chargé de recherche, Centre Inria de Paris

#### Directeur de thèse

Dumitru POTOP-BUTUCARU, Chargé de recherche, Centre Inria d'Université Côte d'Azur

#### Co-directeur de thèse

Robert DE SIMONE, Directeur de recherche, Centre Inria d'Université Côte d'Azur

#### Membres invités

Damien CHABROL, Responsable Innovation et Stratégie Produit, Krono-Safe Amira METHNI, Architecte logiciel, Krono-Safe Université Côte d'Azur

À mon grand-père.

#### Méthodologie de vérification formelle de propriétés temporelles pour les applications temps-réel critiques basées sur le concept de temps logique

#### Résumé

Les systèmes temps-réel critiques doivent respecter des contraintes temporelles strictes qui doivent être considérées tout au long du cycle logiciel. Cependant, du fait que les temps d'exécution exacts ne sont généralement pas connus lors de la conception, le temps logique fournit un moyen d'abstraire les contraintes temporelles et les exécutions du temps physique, dépendant de la plateforme. Dans cette thèse, nous nous concentrons sur deux formalismes basés sur le temps logique. L'approche Synchrone-Réactive abstrait totalement le temps physique en utilisant des bases de temps discrète sur lesquelles les calculs sont déclenchés. L'approche de Temps d'Exécution Logique utilise des bases de temps logique pour représenter non seulement les instants de déclenchement, mais aussi les durées des calculs élémentaires. Dans notre travail, nous commençons par définir une unification des approches Synchrone-Réactives et de Temps *d'Exécution Logique*, fournissant un cadre formel naturel pour définir la sémantique de PSYC, un langage temps-réel industriel expressif. Nous définissons deux sémantiques pour celui-ci : une sémantique native à grands pas, préservant les durées logiques des intervalles de temps, définie par des règles structurelles opérationnelles; et une sémantique synchrone à petits pas définie par traduction vers un langage Synchrone-Réactif étendant les durées des intervalles de temps à une succession de transitions atomiques. Nous montrons que les deux sémantiques sont équivalentes. Cette formalisation de la sémantique de PSYC nous permet de définir une méthodologie de vérification formelle pour PSYC basée sur du *model-checking symbolique*. Pour réduire l'espace d'état pendant le model checking, nous définissons une technique d'optimisation inspirée du model-checking temporisé. Enfin, nous spécifions les exigences temporelles que nous voulons vérifier via un langage de spécification de contrainte d'horloge - CCSL qui sont ensuite traduites en observateurs synchrones.

**Mots-clés :** Systèmes Temps-Réel, Temps d'Exécution Logique, Langages Synchrone-Réactifs, Vérification Formelle.

#### Methodology for the formal verification of temporal properties for real-time safety-critical applications based on logical time

#### Abstract

Safety-critical real-time systems have to respect strict timing constraints. Thus, timing constraints must be considered throughout the software development cycle. As exact computation execution time are generally not known during design, *logical time* provides a way to abstract time constraints and execution from platform-dependent physical time. In this thesis, we focus on two main formalisms based on logical time. The Synchronous-Reactive approach totally abstracts physical time by discrete time bases on which computations are triggered. The Logical Execution Time approach uses logical time bases to represent not only triggering instants but also the durations of elementary computations. In this thesis, we start by unifying Synchronous-Reactive and Logical Execution Time approaches. This provides the natural formal framework for defining the semantics of PSYC, an expressive industrial real-time language. We define two formal semantics for PSYC: a native *big-step* semantics preserving the logical durations of time intervals defined by structural operational rules and a synchronous *small-step* semantics defined by translation to a Synchronous-Reactive language expanding time interval durations to a succession of atomic transitions. We show that the two semantics definitions are equivalent. This formalization of the PSYC semantics enables us to define a formal verification methodology for PSYC based on symbolic model-checking. To reduce the state space during model-checking, we also define an optimization technique inspired by timed automata model-checking. Finally, we show how to encode high-level timing requirements into a clock constraint specification language - CCSL - which are then translated to synchronous observers.

**Keywords:** Real-Time Systems, Logical Execution Time, Synchronous-Reactive Languages, Formal Verification.

### Remerciements

Cette thèse a été menée conjointement avec la société KRONO-SAFE — renommé depuis ASTERIOS TECHNOLOGIES — et l'équipe-projet KAIROS de l'INRIA. Je remercie grandement ces deux entités d'avoir permis cette collaboration et d'avoir montré un intérêt commun pour ce travail.

\* \* \*

Je tiens ainsi à remercier mes directeurs de thèse — Dumitru POTOP-BUTUCARU et Robert DE SIMONE — qui ont fait preuve d'un soutien sans faille tout au long de cette thèse. Ils ont été particulièrement présents, malgré la distance géographique, et malgré les périodes de confinement. C'est d'abord grâce à eux que je dois cette initiation au monde de la recherche académique ainsi que l'aboutissement de ce travail. Je remercie aussi l'équipe KAIROS pour son accueil, ainsi que plus globalement l'INRIA, pour toutes les discussions intéressantes que j'ai pu avoir, avec Marc POUZET, Yves BERTOT, Julien DEANTONI, Frédéric MALLET, Timothy BOURKE, et bien d'autres. Je remercie aussi l'EPITA dont la formation m'a été précieuse, et plus particulièrement Geoffrey L.G. qui m'a permis de m'initier à l'enseignement. Je n'oublierai pas non plus les multiples rencontres que j'ai pu avoir pendant cette thèse au cours des différents évènements : Adrien R., Nan L., João C., Hugo P., et d'autres.

Ensuite, je tiens aussi à remercier l'entreprise KRONO-SAFE pour le support qu'elle a fourni, ainsi que l'encadrement de Damien CHABROL et Amira METHNI dont les conseils ont été cruciaux tout au long de cette thèse. Après avoir été recruté par cette entreprise, mon espoir de faire une thèse de doctorat s'était amenuisé, remplacé néanmoins par un travail prometteur sur des sujets intéressants. Ce n'est toutefois sans compter sur l'intérêt et la confiance de Damien et Amira qui ont transformé ma volonté initiale en un projet solide et défendable. L'entreprise a fait preuve d'une grande confiance en co-finançant cette aventure avec le support de l'ANRT\*. Je tiens ainsi à remercier l'ensemble des collègues qui ont encouragé ou contribué, directement ou indirectement, au succès de ce travail par de précieuses discussions : Frédéric T., Christophe A., Jean G., Stéphane-Jean M., Florian A., Guillaume P., et bien d'autres. Je remercie aussi chaleureusment l'entreprise PROVER TECHNOLOGY, et plus particulièrement Nicolas A. pour son aide et son encouragement.

\* \* \*

Je souhaite aussi remercier particulièrement Pierre-Loic GAROCHE et Reinhardt VON HANX-LEDEN d'avoir accepté de rapporter cette thèse et d'y avoir consacré leur temps, ainsi que Timothy BOURKE d'avoir accepté de faire partie du jury de cette thèse.

<sup>\*.</sup> Association Nationale de la Recherche et de la technologie

Sur une touche plus personnelle, je souhaite aussi remercier mes parents, ma famille, mes amis, ainsi que celle qui est devenue ma femme. Cette aventure a été particulièrement marquée par un évènement heureux, mon mariage, ainsi que par un évènement malheureux, la perte de mon grand-père, qui ne pourra malheureusement pas voir l'aboutissement de ce travail. L'accomplissement de cette thèse est grandement lié à eux.

## **Contents**

| 1 | Intr | Introduction                    |   |  |  |  |

|---|------|---------------------------------|---|--|--|--|

|   | 1.1  | General context                 | 1 |  |  |  |

|   | 1.2  | Contributions                   | 2 |  |  |  |

|   | 1.3  | Thesis Outline                  | 4 |  |  |  |

|   | 1.4  | Publications and Communications | 4 |  |  |  |

#### Background

| 2 | Safety-Critical Real-Time Systems          |         |                                               | 9  |  |

|---|--------------------------------------------|---------|-----------------------------------------------|----|--|

| 3 | Languages and Models for Real-Time Systems |         |                                               |    |  |

|   | 3.1                                        | Real-ti | ime scheduling models                         | 15 |  |

|   |                                            | 3.1.1   | Task models                                   | 16 |  |

|   |                                            | 3.1.2   | Scheduling policy and schedulability analysis | 16 |  |

|   | 3.2                                        | Real-ti | ime languages and programming models          | 17 |  |

|   |                                            | 3.2.1   | Process algebra                               | 18 |  |

|   |                                            | 3.2.2   | Synchronous-Reactive languages                | 18 |  |

|   |                                            | 3.2.3   | Logical Execution Time languages              | 22 |  |

|   |                                            | 3.2.4   | Other languages based on logical time         | 22 |  |

|   | 3.3                                        | Tempo   | oral Requirements Formalisms                  | 26 |  |

|   |                                            | 3.3.1   | Temporal logic                                | 27 |  |

|   |                                            | 3.3.2   | Clock Constraint Specification Language       | 28 |  |

|   |                                            | 3.3.3   | Synchronous observers                         | 29 |  |

#### Language and Semantics

| 4 | Syn | chronou | us Logical Execution Time in PSYC                 | 33 |

|---|-----|---------|---------------------------------------------------|----|

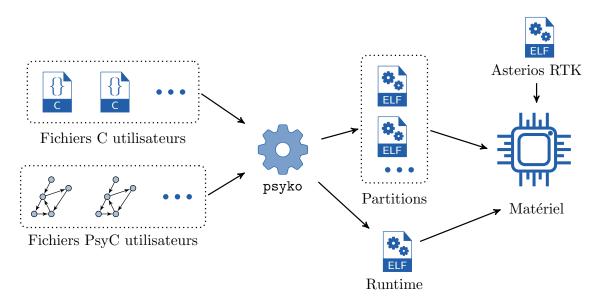

|   | 4.1 | The A   | STERIOS Software Suite                            | 34 |

|   |     | 4.1.1   | Origins of the technology                         | 34 |

|   |     | 4.1.2   | Industrial context                                | 34 |

|   |     | 4.1.3   | Tooling                                           | 35 |

|   | 4.2 | A sync  | chronous generalization of Logical Execution Time | 35 |

|   |     | 4.2.1   | Overview of synchronous Logical Execution Time    | 36 |

|   |     | 4.2.2   | Definitions                                       | 36 |

|   |     | 4.2.3   | About functional and temporal determinism         | 38 |

|   | 4.3 | The Pa  | SYC language                                      | 38 |

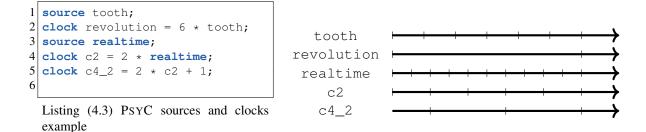

|   |     | 4.3.1   | Source and clocks                                 | 38 |

|   |     | 4.3.2   | Tasks                                             | 40 |

|   |     | 4.3.3   | Inter-task communication channels                 | 43 |

|   | 4.4 | Summ    | ary                                               | 48 |

| 5 | For | mal Sen | nantics of PSYC                                   | 51 |

|   | 5.1 | Abstra  | act Syntax of PSYC                                | 52 |

|   | 5.2 | Native  | "big-step" Semantics of PSYC                      | 52 |

|   |     | 5.2.1   | Native semantics of one PsyC agent                | 53 |

|   |     | 5.2.2   | Native semantics of a PsyC agent network          | 58 |

|   | 5.3 | Synch   | ronous "small-step" Semantics of PSYC             | 63 |

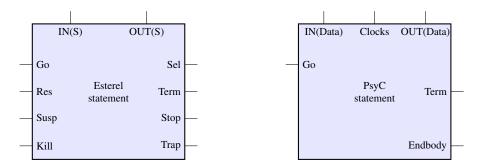

|   |     | 5.3.1   | The ESTEREL language                              | 63 |

|   |     | 5.3.2   | ESTEREL translation principle                     | 66 |

|   |     | 5.3.3   | Translation Rules                                 | 67 |

|   | 5.4 | Equiva  | alence between both semantics                     | 73 |

xiii

#### Formal Verification for synchronous LET

| 6 | Tem  | mporal Requirements                                   |    |  |

|---|------|-------------------------------------------------------|----|--|

|   | 6.1  | Temporal requirements for PSYC                        | 80 |  |

|   | 6.2  | The CCSL language                                     | 81 |  |

|   |      | 6.2.1 Time model                                      | 81 |  |

|   |      | 6.2.2 Constraints and Expressions                     | 82 |  |

|   |      | 6.2.3 Synchronous observers                           | 84 |  |

|   | 6.3  | Encoding requirements in CCSL                         | 84 |  |

|   |      | 6.3.1 Repetition requirement                          | 85 |  |

|   |      | 6.3.2 Synchronization requirements                    | 85 |  |

|   |      | 6.3.3 Causality requirements                          | 86 |  |

|   |      | 6.3.4 Delay and Latency requirements                  | 86 |  |

|   |      | 6.3.5 Functional chains                               | 87 |  |

|   | 6.4  | Example                                               | 88 |  |

|   | 6.5  | Summary                                               | 88 |  |

| 7 | Vori | fication: General Case                                | 89 |  |

| , |      |                                                       |    |  |

|   | 7.1  | Background                                            | 90 |  |

|   |      | 7.1.1 Circuit semantics of Esterel                    | 90 |  |

|   |      | 7.1.2 Symbolic Transition System                      | 91 |  |

|   |      | 7.1.3 Symbolic Model-checking                         | 92 |  |

|   | 7.2  | Translating PSYC to Symbolic Transition Systems       | 93 |  |

|   |      | 7.2.1 Extending PSYC agents with verification signals | 93 |  |

|   |      | 7.2.2 Translation principle                           | 93 |  |

|   |                    | 7.2.3                                        | Sources and clocks                                                                                                                | 94                              |

|---|--------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|   |                    | 7.2.4                                        | Statements                                                                                                                        | 94                              |

|   |                    | 7.2.5                                        | Agents                                                                                                                            | 97                              |

|   |                    | 7.2.6                                        | Example                                                                                                                           | 98                              |

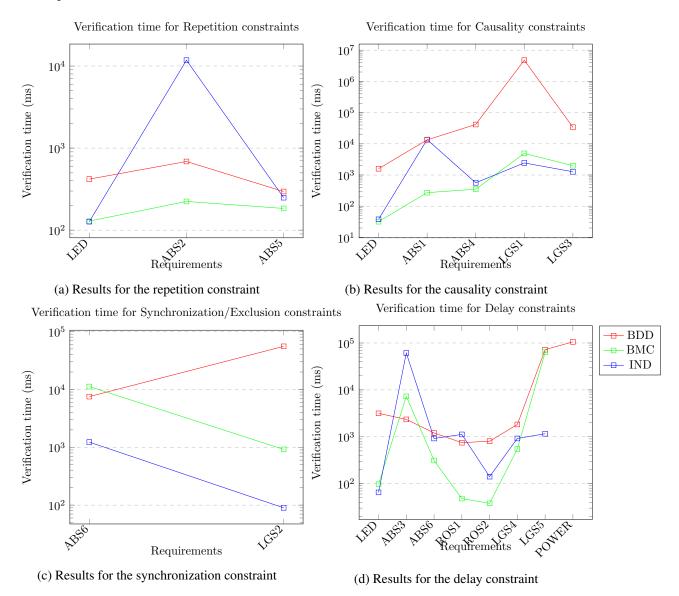

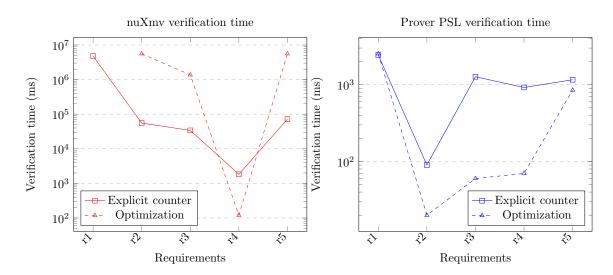

|   | 7.3                | Experi                                       | ments                                                                                                                             | 99                              |

|   |                    | 7.3.1                                        | Implementation                                                                                                                    | 100                             |

|   |                    | 7.3.2                                        | Benchmarks                                                                                                                        | 100                             |

|   |                    | 7.3.3                                        | Evaluation                                                                                                                        | 101                             |

|   | 7.4                | Summ                                         | ary                                                                                                                               | 103                             |

|   |                    |                                              |                                                                                                                                   |                                 |

| 8 | Veri               | fication                                     | : Mono-Source Case                                                                                                                | 105                             |

| 8 | <b>Veri</b><br>8.1 |                                              | : Mono-Source Case                                                                                                                | <b>105</b><br>105               |

| 8 |                    | Proble                                       |                                                                                                                                   |                                 |

| 8 | 8.1                | Proble                                       | m statement                                                                                                                       | 105                             |

| 8 | 8.1                | Proble<br>A temj                             | m statement                                                                                                                       | 105<br>107                      |

| 8 | 8.1                | Proble<br>A temp<br>8.2.1<br>8.2.2           | m statement                                                                                                                       | 105<br>107<br>107               |

| 8 | 8.1<br>8.2         | Proble<br>A temp<br>8.2.1<br>8.2.2           | m statement                                                                                                                       | 105<br>107<br>107<br>108        |

| 8 | 8.1<br>8.2         | Proble<br>A temp<br>8.2.1<br>8.2.2<br>Experi | m statement   poral optimization approach   Symbolic Transition System with durations   Symbolic abstraction of durations   ments | 105<br>107<br>107<br>108<br>108 |

#### **Conclusion and Perspectives**

| 9 Conclusion |     |              |     |  |  |

|--------------|-----|--------------|-----|--|--|

|              | 9.1 | Summary      | 115 |  |  |

|              | 9.2 | Perspectives | 116 |  |  |

| Bibliography     | 119 |

|------------------|-----|

| List of Figures  | 125 |

| List of listings | 130 |

xv

#### Appendix

| A | Equi | Equivalence Criterion Proof |     |  |  |  |  |

|---|------|-----------------------------|-----|--|--|--|--|

|   | А    | Syntax                      | 133 |  |  |  |  |

|   | В    | ESTEREL Semantics           | 134 |  |  |  |  |

|   | С    | Sources and clocks          | 135 |  |  |  |  |

|   | D    | Equivalence proof           | 136 |  |  |  |  |

# CHAPTER 1

## Introduction

| 1.1 | General context                 | 1 |

|-----|---------------------------------|---|

| 1.2 | Contributions                   | 2 |

| 1.3 | Thesis Outline                  | 4 |

| 1.4 | Publications and Communications | 4 |

#### **1.1 General context**

Safety-critical real-time systems have to respect strict time constraints. Thus, time constraints must be considered throughout the software development cycle: from system specification to integration on a specific hardware platform. However, the exact execution time of computations is generally not known during the system specification and design phases, as they depend on a specific target. The *Logical Time* concept provides a way to abstract time constraints and execution from hardware *Physical Time* by providing discrete time bases on which computations react. At integration time, analyses are then used to ensure those physical time constraints — mainly execution time estimations — satisfy the logical time constraints necessary to ensure the system's safety.

In this thesis, we focus on two main formalisms based on logical time. The *Synchronous-Reactive* (SR) approach totally abstracts physical time by discrete time bases — called *logical clocks* — on which computations are executed atomically on specific ticks. Although SR is very expressive (partly due to its logical clocks), it suffers from implementation difficulties when using multi-scale time constraints. As an alternative, the *Logical Execution Time* approach uses logical time bases to represent not only triggering instants but also the durations of elementary computations. This defines time windows which contain the actual computation and on which communication can only happen on the boundaries of those logical time intervals. Both SR and LET provide a deterministic and concurrent way to deal with logical time constraints. ESTEREL and LUSTRE are examples of Synchronous-Reactive languages, while GIOTTO and TDL are examples of Logical Execution Time languages. However, LET suffers from expressivity limitations; in particular, timing durations are based on a unique chronometrical time base, and thus, cannot express timing constraints based on multiform logical time. XGIOTTO, LINGUA FRANCA and PSYC are examples of languages that include features from both SR and LET:

- XGIOTTO is an imperative language that extends GIOTTO and LET with events via a mechanism called event scoping [GHKS04];

- LINGUA FRANCA is a dataflow coordination language developed in Berkeley university which supports LET while having a semantics closer to the SR approach [LL22];

- PSYC is a real-time integration language developed initially at the CEA\*, and now by KRONO-SAFE, which extends LET with synchronous instants [ACA+96].

This thesis is focused on the PSYC language, developed by the company KRONO-SAFE – now renamed ASTERIOS TECHNOLOGIES as a SAFRAN ELECTRONICS & DEFENSE subsidiary — who is funding this work.

Those languages are typically used to design a specific program satisfying a set of high-level timing requirements such as constraints among the timing of various components (e.g., period, synchronizations) or constraints on data propagation among various components (e.g. end-toend latency). In a safety-critical process, those requirements should be verified very carefully in the program. Traditionally, this activity is done manually by code inspection or by simulation. However, formal verification provides stronger guarantee to ensure that those requirements are satisfied.

#### **1.2 Contributions**

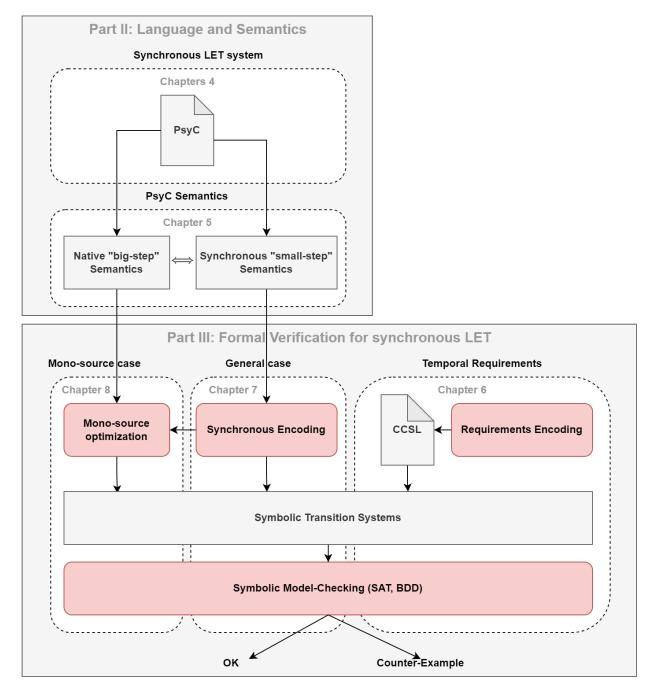

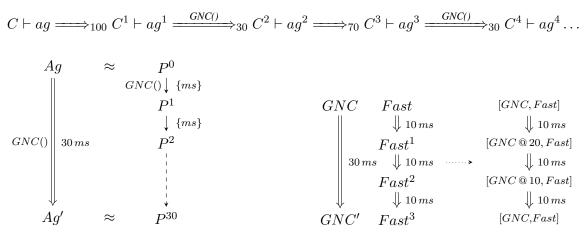

We now describe the main contributions of this thesis illustrated in Figure 1.1 which are split in two topics: language semantics and formal verification.

**Language Semantics** PSYC inherits from both the Synchronous-Reactive (SR) and the Logical Execution Time (LET) approach. By identifying how SR and LET formalisms relate, we define in this thesis a synchronous generalization of LET called *synchronous LET* in which time interval boundaries are specified by synchronous instants. We use sLET as a semantics foundation for PSYC: we define a native *big-step* semantics preserving the logical durations of time intervals — which is close to the one used in the compiler today — defined by structural operational rules and a synchronous *small-step* semantics defined by translation to the synchronous language ES-TEREL expanding time interval durations to a succession of atomic transitions. We show that both semantics definitions are equivalent on the boundaries of the LET time intervals.

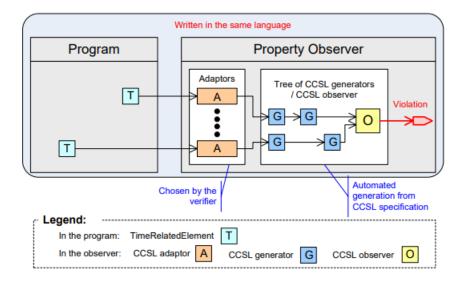

**Formal Verification** From the synchronous semantics of PSYC, this thesis also defines a verification methodology for PSYC based on symbolic model-checking and on the modelization of timing requirements as synchronous observers. However, as the synchronous semantics expand all LET intervals in atomic transitions, this approach does not scale well. To solve this problem, we define an optimization technique inspired by *timed automata* model-checking, which preserves durations from the native semantics assuming that only one base clock is used in the program. Finally, we show how to encode our requirements in a clock constraint logic — CCSL — instead

<sup>\*.</sup> French Alternative Energies and Atomic Energy Commission

Figure 1.1 – Global methodology proposed in this thesis

of a more traditional temporal logic — such as LTL — as the program typically has multiple time scales among components. In both cases, however, requirements belonging to the *safety* class can be translated to synchronous observers.

#### **1.3** Thesis Outline

The outline of this thesis is composed of three main parts:

- The first part presents the overall context and background of this thesis, both academically and industrially. In Chapter 2, we describe the overall context and industrial background. Then, in Chapter 3, we give an overview of various languages and formalisms used to specify, design and implement real-time systems.

- The second part focuses on semantics foundations for the PSYC language. Chapter 4 gives an overview of the PSYC language and defines synchronous LET as being a synchronous generalization of Logical Execution Time. It is then used in Chapter 5 to define the native and the synchronous semantics of PSYC. We also give an equivalence criterion between those semantics, which proof is sketched in Appendix A.

- The third part focuses on a verification methodology based on the semantics defined on the second part. Chapter 6 formalizes the different temporal requirements that we want to verify on PSYC programs. Then, Chapter 7 describes the overall verification methodology for the general case of PSYC programs. Finally, Chapter 8 focuses on the subcase of PSYC programs using only one base clock to define an optimization method compressing the state space.

- In chapter 9, as a final part, we give a global conclusion of this thesis as well as various perspectives.

#### **1.4 Publications and Communications**

In this thesis, we did multiple publications and communications. This section describes them by category.

#### **International Conferences and Workshops**

- Fabien Siron, Dumitru Potop-Butucaru, Robert De Simone, Damien Chabrol, and Amira Methni. Semantics fondations of PsyC based on synchronous Logical Execution Time. In *TCRS 2023 - Time Centrics Reactive Systems*, San Antonio, Texas, U.S.A., May 2023.

- [2] Fabien Siron, Dumitru Potop-Butucaru, Robert De Simone, Damien Chabrol, and Amira Methni. The synchronous Logical Execution Time paradigm. In ERTS 2022 - Embedded Real Time Systems, Toulouse, France, June 2022.

[3] Fabien Siron, Dumitru Potop-Butucaru, Robert de Simone, Damien Chabrol, and Amira Methni. (wip: )programming and verifying real-time design using logical time. In FDL 2021-Forum on specification & Design Languages, 2021. https://hal.inria.fr/hal-03545758/.

#### **National Conferences and Workshops**

[4] Fabien Siron, Dumitru Potop-Butucaru, Robert de Simone, Damien Chabrol, and Amira Methni. Vérification d'applications temps-réel basées sur le paradigme de logical execution time (let). In École d'Été Temps Réel 2021, 2021. https://hal.inria.fr/hal-03545758/.

#### **Research Report**

[5] Fabien Siron, Dumitru Potop-Butucaru, Robert De Simone, Damien Chabrol, and Amira Methni. Formal Semantics of the PsyC language. Research report, INRIA Sophia Antipolis - Méditerranée (France), 2023.

#### **Communication without proceedings**

[6] Fabien Siron, Dumitru Potop-Butucaru, Robert De Simone, Damien Chabrol, and Amira Methni. Synchronous Logical Execution Time: Towards formal verification. In Synchron 2021, 28th International Open Workshop on Synchronous Programming, La Rochette, France, November 2021.

#### **Unpublished articles**

[7] Fabien Siron, Dumitru Potop-Butucaru, Robert De Simone, Damien Chabrol, and Amira Methni. Formally verifying timing requirements on applications based on synchronous Logical Execution Time. 2023.

### FIRST PART

### Background

Learning never exhausts the mind.

— Leonardo da Vinci, (1452-1519).

# Chapter 2

## Safety-Critical Real-Time Systems

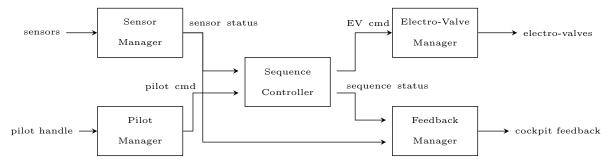

Today, in fields such as avionics and automotive, software plays an increasingly important role. Among the significant trends in these fields are automation and electrification. Examples include automatic landing systems [Air23] and electrification of aircraft landing gears [Saf23]. This results in increasingly complex systems, and, due to strong economic constraints, also results in harder integration process and bigger function concentration. For all these reasons, software reliability is becoming a major challenge in those fields. This thesis falls within this context. The following sections give global definitions characterizing the overall context.

**Critical Systems** In this work, we focus on systems that are qualified as *critical* due to the consequences a system failure could have. We give below the definition from the IEEE \* glossary [iee90]:

« Software whose failure could have an impact on safety, or could cause large financial or social loss. » (IEEE)

Depending on these consequences, critical systems can be classified into two main classes:

- Safety-critical: A system whose failure could endanger people's safety. Examples include control systems of nuclear plants or control systems in civil aircraft;

- Mission-critical: A system whose failure could endanger its mission and, thus, business

operations. Examples include navigational systems of unmanned spacecrafts or bank management systems.

In this work, we focus mostly on safety-critical systems; the targeted fields of the company KRONO-SAFE include mainly avionics and automotive industries. However, most techniques described in this work could be applied to both classes.

**Real-time and reactive software** In safety-critical real-time systems, timing is part of the system's functionnality; those systems have to respect a set of strict timing constraints to guarantee the overall safety. [KS22] defines real-time systems as follows:

<sup>\*.</sup> Institute of Electical and Electronics Engineers

A real-time computer system is a computer system where the correctness of the system behavior depends not only on the logical results of the computations, but also on the physical time when these results are produced. »

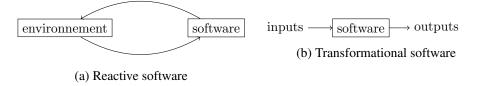

However, real-time systems are not traditional sequential software programs. A typical traditional program computes output value from inputs values, and then stop as shown in 2.1b; they are often called *Transformational* [HP84]. However, real-time systems — and more generally *reactive* systems — continuously react to the environment by a sequence of reactions similar to Figure 2.1b as shown in Figure 2.1a; reactive systems, thus, react at a pace dictated by their environment [HP84]. Reactive systems call for *concurrency*; they are often composed of various communicating parallel components that react with their environment at different rate. Additionally, as reactive systems are often used in a critical context, they should be highly predictable, and thus call for *determinism*. A system is said to be deterministic if the same sequence of inputs always produces the same sequence of outputs [Ber02]. Hence, as advocated in [Lee09], real-time and reactive software should consider time throughout the software cycle as functionality constraints rather than quality of service measurements. To do that, one should consider languages and formalisms with time as a first class citizen ensuring system's predictability.

The control system of an aircraft engine (called FADEC) is an example in which the control accuracy — and thus the whole system's safety — directly depends on temporal requirements dictated by the environment. Not respecting those requirements can lead to an engine failure, which could in turn jeopardize the system's integrity (here, the aircraft) and therefore the passengers safety. A FADEC is a very classical safety-critical real-time system and is one of the use-cases of the ASTERIOS technology, developed by KRONO-SAFE.

Figure 2.1 – Software class

**Formal Design for Real-Time Reactive Systems** As systems are becoming increasingly complex, traditional techniques face their limit: manual coding of functional source code may insert bugs, and test-based verification could fail to detect bugs due to the incompleteness of testing. Moreover, the later the bugs are detected the more expensive are the consequences. To overcome those issues, *formal methods* provide mathematically rigorous techniques for various activities of the software life cycle. We give below the definition of Clarke [CW96]:

Formal methods are mathematically based languages, techniques, and tools for specifying and verifying systems. »

(Clarke)

In real-time systems, the *Multiform Logical Time* concept [AMDS07] (sharing a lot of similarities with the Tagged signal model [LSV98]) mandates to deal with a formal abstraction of time through *logical* timing constraints dictated by high-level requirements and thus, independent from • Flow requirements (e.g., freshness, end-to-end latency).

• Schedulability analysis.

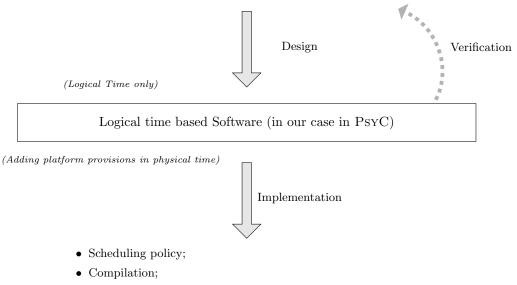

Figure 2.2 – Logical time application design methodology

a specific embedded platform. It's then the role of the implementation to map those logical timing constraints to physical time. Hence, software development is often divided into two main steps as shown in Figure 2.2, similarly to the V cycle or the avionic safety standard software process (DO-178C):

- The design phase allows for the design of logical timing constraints providing a deterministic timing behavior to be respected by the implementation.

- Then, the *implementation phase* allows logical timing constraints to be mapped to physical time based on platform timing provisions (e.g., estimation of worst case execution time) and real-time scheduling.

Logical timing constraints rely on *logical clocks* to express time; they denote sequence of instants either based on external events or on specific instants of physical time. Similarly to [Lam78], logical clocks are used to replace physical dates by logical sequencing. Real-time systems often rely on multiple logical clocks to express system components reacting on different pace. They are two cases of multi-clock systems:

- All *logical clocks* are derived (e.g., via periodic refinement) from a unique global *logical clock*, often mapped to a hardware timer during implementation;

- Logical clocks rely on multiple sources of logical time which could be independent or partially controlled.

In practice, most industrial systems fall in the first category due to safety considerations. Nonetheless, some examples still need multiple source clocks. For example, an automotive powertrain control is a typical system which relies on two time bases: a source clock based on the crankshaft position to trigger computations on specific physical state of the engine and a source clock based on a hardware timer to define timing constraints such as initialization time or deadlines [ $CDO^{+}14$ ].

In this thesis, we focus only on the *design* phase as the *implementation* phase has been heavily covered by previous work from the CEA [LDAVN10]. The *design phase* can be a particularly challenging task due to the number of requirements to satisfy. In this work, we particularly focus on *temporal requirements* specifying either constraints among the rates of multiple components (e.g., synchronizations) or among the propagation of some data across multiple components (e.g., end-to-end latency). Multiple techniques could be used then to ensure that logical timing constraints are compliant with high-level requirements. Among them, formal verification — and more precisely model-checking — is a generic and automatic technique to provide formal guarantees for the verification process. It has been heavily studied and used in formalisms based on logical time in academy [HLR94a] and industry [BVWW09].

**Industrial Considerations** Formal methods are becoming a trend for safety-critical systems in various industrial domains. In railway, the Meteor project has been designed using the B method, a formal specification language based on proven refinements [AHC96]. In avionics, synchronous reactive formalisms such as SCADE [CPP17] have been used successively in large scale avionics systems and provide formal verification techniques — mainly model-checking — that have been studied for realistic avionics systems [BVWW09].

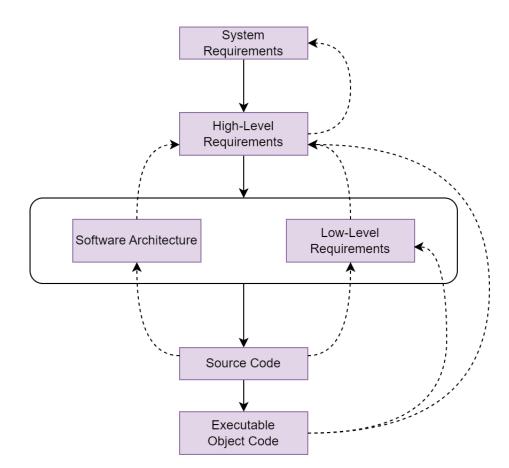

Safety-critical systems are usually subject to safety standards defining legal and regulatory requirements to specify, design, develop and verify systems at various stages. For example, DO-178C [RDE11] focuses on avionics software, ISO-26262 [Org18] on automotive systems and IEC-62304 [Com06] on medical software. As an illustration, Figure 2.3 shows the typical software process imposed by the DO-178C: the specification process typically produces a set of high-level requirements, then the design process produces both the software architecture and a set of low-level requirements, and finally the implementation and integration process produce respectively the source code and the executable object code. Verification activities are performed at each level, ensuring compliance with upper levels; this is often done with code inspections and test campaigns using strict coverage criteria.

Nonetheless, safety standards are being adapted to the use of formal methods techniques and languages:

- 1. In the avionics domain, DO-178C has an appendix, named DO-333, defining guidelines to adapt DO-178C objectives to the use of formal methods techniques and tools;

- 2. In the automotive domain, ISO-26262, advocates for the use of formal methods for the verification process of the most critical systems (ASIL-C and D);

- 3. In the industrial domain, IEC-61056, highly recommends the use of formal methods for the most critical systems (SIL-4).

In the particular case of the avionics domain – which is our main focus in this thesis due to its industrial context – NASA have worked on a detailed case study providing guidance on how to apply formal methods at various steps of the software process using the DO-333 [CM14]. In this thesis, we focus on model-checking based techniques applied to formalisms based on logical

Figure 2.3 – DO-178 Software Process

time to help the design process and its verification. The following chapter details some of these formalisms.

# Chapter 3

## Languages and Models for Real-Time Systems

| 3.1 | Real-t | ime scheduling models                         | 15 |

|-----|--------|-----------------------------------------------|----|

|     | 3.1.1  | Task models                                   | 16 |

|     | 3.1.2  | Scheduling policy and schedulability analysis | 16 |

| 3.2 | Real-t | ime languages and programming models          | 17 |

|     | 3.2.1  | Process algebra                               | 18 |

|     | 3.2.2  | Synchronous-Reactive languages                | 18 |

|     | 3.2.3  | Logical Execution Time languages              | 22 |

|     | 3.2.4  | Other languages based on logical time         | 22 |

| 3.3 | Tempo  | oral Requirements Formalisms                  | 26 |

|     | 3.3.1  | Temporal logic                                | 27 |

|     | 3.3.2  | Clock Constraint Specification Language       | 28 |

|     | 3.3.3  | Synchronous observers                         | 29 |

In this chapter, we give an overview of different languages and models used for the modelisation of real-time systems at various stages of the software life cycle. We first describe in real-time scheduling models that are typically used during the integration process and in real-time operating systems. We then give an overview of various languages and programming models dedicated to the modelisation of real-time constraints and typically used during the design process. We finally describe formalisms used to formally define high-level temporal requirements that are often used in a formal verification process.

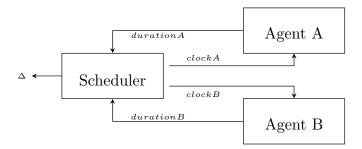

#### 3.1 Real-time scheduling models

A traditional way to model real-time systems is to consider a finite set of concurrent *tasks* (usually periodic), whose execution is dictated by a *scheduler* which decides which task is executed next at each invocation. In real-time systems, tasks are subject to strict real-time constraints

coming from high-level requirements. However, in embedded real-time systems, tasks also have time provisions dictated by the platform's computing capabilities. The real-time scheduling field is therefore interested in tasks models, and the choice of scheduling policies as well as schedulability (or feasibility) analyses to ensure that platform's provisions could not invalidate real-time task constraints. The reader might want to read [LS16] which gives a good introduction to real-time scheduling models.

#### 3.1.1 Task models

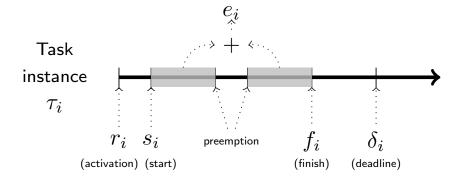

**Task constraints** We usually consider a finite set of tasks  $\mathcal{T}$  in which each task  $\tau \in \mathcal{T}$  is executed by a sequence of task instance  $\tau_1, \tau_2, \ldots$  Tasks are usually defined to be either *periodic* or *sporadic* depending on the regularity of task instances. Formally, we define  $r_i$  as being the *activation instant* of a task instance  $\tau_i$ .

In general, we define a periodic task by the activation function  $r_i = O + (i-1) \times T$  where O and T are respectively the offset and the period of the task. Sporadic tasks do not have a specific activation function for  $r_i$ , however, activation should usually satisfy  $r_{i+1} \ge r_i + T_{min}$  where  $T_{min}$  is the minimal interval between two successive task activations.

The second typical temporal constraint of a task is the *deadline* of a task written  $\delta_i$ . It corresponds to the instant on which the task instance  $\tau_i$  has to be terminated. In a real-time system with hard critical constraints, a task instance  $\tau_i$  should fit between  $r_i$  and  $\delta_i$ , otherwise it is considered as an error. Considering that  $s_i$  and  $f_i$  are respectively the execution start and termination of  $\tau_i$ , then  $\tau_i$  has to satisfy  $r_i \leq s_i < f_i < \delta_i$ . All those constraints are shown in Figure 3.1.

**Task provisions** The constraints given above are induced by temporal requirements. However, to compute the instants on which computations start and terminate,  $s_i$  and  $f_i$ , dictated by a scheduling policy, it is necessary to give an estimate of the task execution time, which we write  $e_i$ . In a preemptive model,  $e_i$  is not necessarily equal to  $f_i - s_i$ ; execution can be broken down into several sub-windows in which the sum of the execution time should be  $e_i$ . In traditional scheduling models,  $e_i$  is often considered to be constant. Today, however, it is commonly accepted that this time is variable due to multiple factors: program control-flow, cache management ... It is usually defined by a *Best* and *Worst Case Execution Time* (respectively BCET and WCET).  $e_i$  is thus often an estimation of the WCET.

#### 3.1.2 Scheduling policy and schedulability analysis

A scheduling policy elects which task should run at each invocation according to a desired objective. However, a scheduling policy may fail to satisfy some of the time constraints — typically the deadline — du to an incompatibility between real-time constraints and target provisions. In order to avoid this issue, the use of so-called schedulability analysis is needed to ensure that time provisions tasify task constraints. This analysis depends directly on the scheduling policy used, and is usually defined as a criterion demonstrating that  $f_i < \delta_i$  for any execution.

Figure 3.1 – Task model for real-time scheduling

To illustrate the concept of schedulability analysis, let's take the EDF scheduling algorithm (i.e., for *Earliest Deadline First*). At each scheduling decision (e.g., at the end of task's execution), the next task to be executed is the one with the earliest deadline. In the case of a set of periodic task and with deadline  $\delta = T$ , the schedulability analysis is defined as follows for a set of task  $\mathcal{T} = \{\tau^1, \tau^2, \dots, \tau^n\}$ :

$$\sum_{j=1}^{n} \frac{e^j}{T^j} \le 1 \tag{3.1}$$

This criterion, introduced in [XP90], ensures that the computational load is less than 100%. Hence, if the condition is met, real-time constraints are guaranteed to hold.

In practice, real-time scheduling models are rather low-lever, and do not allow reasoning from a programmatic point of view on a real-time software. This is because a scheduling model is not a programming model: there is neither communication model nor structured control. Additionally, response times are difficult to predict  $(f_i - r_i)$  is variable at runtime) and can be a cause of non-determinism. Nonetheless, those models are very useful to study the capacity of a hardware platform to satisfy real-time task constraints. In this work, we focus on real-time constraints, that we will call *logical constraints*. We make the assumption that WCET estimation and schedulability analysis exist for the various languages described in this work.

#### **3.2 Real-time languages and programming models**

One of the greatest of the mid-20th century in computer science is the Church-Turing thesis, which shows the equivalence of several models of computation, such as the lambda-calculus or the Turing machine. However, those models are *sequential*. As discussed in the previous chapter, reactive real-time systems need model of computations relying on both *concurrency* and *timing constraints*. This section gives an overview of the main languages and programming models highlighting those aspects that are all based on logical abstraction of time. For each, we also discuss the notion of *determinism*, which is often mandatory in the context of safety-critical systems.

#### 3.2.1 Process algebra

Process algebras are specific languages defined in the context of concurrency theory defined by Milner [Mil82]. These languages enable us to describe formally interactions, synchronizations and communications between process - or agents. Most algebras define the following elements [Mil82] [Hoa78]:

- Inter-process communication mechanisms;

- Sequential composition;

- Parallel composition which is generally asynchronous;

- And finally, replication mechanisms such as loops or recursion.

One of the most famous examples of process algebra is the modelisation of a Coffee Machine (CM). We give here its behavior using a simplified syntax of CCS:

$$CM = coin.(coffee + tea).brewing.CM$$

This machine is defined by a recursive sequence of action. We use two operators "+" which defines choice and "." which defines sequential composition. The behavior then the following: first the machine waits for a coin, then it proceeds to either brewing coffee or tea depending on the one selected before returning to its initial state. Let's now define the typical behavior of users who either try to get a coffee for free if it's possible or gives a coin before talking.

$$USER = (coffee + coin.coffee).talk.USER$$

Using the parallel composition " $\parallel$ ", we can now define the interactions between the two process, **USER** and **CM**. This illustrates the mechanism of handshaking which synchronizes corresponding actions.

$$(\mathbf{CM} \parallel \mathbf{USER}) = coin.coffee.(brewing \parallel talking).(\mathbf{CM} \parallel \mathbf{USER})$$

However, generally, process algebras allow defining concurrency but at the price of determinism. Due to the asynchronous composition of process, the algebras cannot guarantee that the resulting process is deterministic. Furthermore, process algebras are not adequate to specify temporally predictable requirements. Nonetheless, multiple approaches extend process algebras to support determinism or predictable temporality: SCCS [Mil83], Meije [AB84] or CoReA [Bon94] to name a few.

#### **3.2.2** Synchronous-Reactive languages

To combine concurrency and determinism, dedicated languages based on the Synchronous-Reactive (SR) programming model have been introduced [BB91]. In a SR language, time is abstracted by a sequence of instants on which computations (often called *reactions*) are triggered. Those sequences of instants are called *logical clocks* and this time abstraction, *logical time*. Multiple logical clocks can exist in SR programs; however, the semantics of SR languages usually impose to expand each behavior on a unique base clock. The SR programming model is based on two main principles:

- Synchrony: the output of a computation is available to all other computations triggered on the same instant; hence, communications are synchronous. The synchronous hypothesis states that all computations triggered on some instant should terminate before the next one.

- *Causality*: the output of a computation must be available *before* any other computations could use it on the same instant; hence, communications are *causal*.

Based on both synchrony and causality properties, SR languages provide support for modeling complex concurrent programs while ensuring determinism. SR programs focuses on temporal constraints – based on logical time – while physical time mapping is left to the implementation. Figure 3.2 shows a typical execution of a synchronous-reactive program

Figure 3.2 – Typical execution of a synchronous-reactive program in logical and physical time

#### **Imperative approach: ESTEREL**

ESTEREL [Ber02] is an imperative synchronous-reactive language. Contrary to data-flow languages described in the next section, ESTEREL code is control-flow oriented. Communications in ESTEREL are carried out using broadcasted signals. Those signals are logically instantaneous – they are available on the same instant on which they are produced – and a broadcasted to all the program. Signals can be in inputs, outputs of a component as well as internal. They are defined by a *status* indicating the presence or absence of the signal on each instant and by an optional *value*. ESTEREL provides two main mechanisms: imperative concurrency allowing multiple instruction pointers in a same program; and synchronous preemption aborting an execution. Statements are divided in two classes:

- Statements that don't take time, which are *logically instantaneous* like send s which sends a signal s or present s then P else Q which execute P or Q depending on the presence of signal s (note that even if reacting to s does not take time, P or Q may take time);

- And statements that take time one or multiple instants like pause which waits for the next instant or await S which awaits an instant in which signal s is present.

The example in Listing 3.1 illustrates the main features of ESTEREL. This program awaits signals A and B on its inputs — in any order — and emits O when both signals are received. Signal R allows the reset of the program. A detailed description of the language is given in Chapter 5 in the semantics definitions of PSYC.

```

1

module ABRO:

2

input A, B, R;

3

output 0;

4

loop

5

[ await A || await B ];

6

emit 0

7

each R

8

end module

9

```

#### Listing 3.1 – ESTEREL ABRO example

#### **Dataflow approach: LUSTRE, SIGNAL**

Imperative SR languages are however not adapted for control systems. In this domain, computations are usually described by block-diagrams in which blocks corresponds to operators and transitions to dataflow dependencies.

**Lustre** LUSTRE [CPHP87] is a declarative dataflow SR language used to model such control systems. It defines a set of mutually recursive equations operating on data streams. A stream is a sequence of values based on a (logical) clock, which specifies the presence or absence of values on each instant of a global base clock. LUSTRE defines two types of equation operators:

- Traditional operators which depend on the value's type; arithmetic operators for integers or boolean operators for boolean values.

- Synchronous operators which allow the manipulation of stream history; pre(X) defines delayed values of X by one instant and X -> Y defines X on the first instant, then Y. LUSTRE also defines sampling/merging operators that we omit here.

```

1 node Edge(X : bool);

2 returns (Y : bool);

3 let

4 Y = False -> X and not (pre X);

5 tel

6

```

#### Listing 3.2 – LUSTRE raising edge example

Listing 3.2 shows the most classical LUSTRE example which defines a raising edge detector. Y is set to true when X is true on the current instant but was not on the previous instant. Listing 3.3 shows how the raising edge detector can be used to define a similar program to the ABRO ESTEREL example. Basically, O is the raising edge of the conjunction of A and B which are held while R is not present. Table 3.3 gives a possible execution of the ABRO program.

**Signal** SIGNAL [BLGJ91] is also a dataflow SR language, really similar to LUSTRE. However, contrary to LUSTRE, SIGNAL can deal with the clocks of its streams. Those clocks are typically

```

node Abro(A, B, R : bool);

1

2

returns (0 : bool);

3

var seenA, seenB : bool;

4

let

5

O = Edge(seenA and seenB);

6

seenA = Hold(A, R);

7

seenB = Hold(B, R);

8

tel

9

```

Listing 3.3 – LUSTRE ABRO example

| А          | False | True  | False | False | False | False | True  | False |

|------------|-------|-------|-------|-------|-------|-------|-------|-------|

| В          | False | False | False | False | False | True  | False | False |

| R          | False | False | False | True  | False | False | False | False |

| seenA      | False | True  | True  | False | False | False | True  | True  |

| seenB      | False | False | False | False | False | True  | True  | True  |

| pre(seenA) | nil   | False | True  | True  | False | False | False | True  |

| pre(seenB) | nil   | False | False | False | False | False | True  | True  |

| 0          | False | False | False | False | False | False | True  | False |

Figure 3.3 – Possible execution of the ABRO example in LUSTRE

only partially defined by relations (instead of deterministic operators). Then, it is the job of the compiler to synthesize those clocks while respecting various relation constraints. Hence, SIGNAL allows the design of programs containing multiple – partially-related – clocks; hence, it is often considered as a *polychronous* language.

However, while SR languages allow mixing both concurrency and determinism, their semantics usually impose to expand reactions on a common global base clock. Consequently, even "long" computations (i.e., which physical duration lasts multiple instants of the base clock) are semantically projected on the base clock and have to terminate before the next instant (i.e., synchronous hypothesis). Hence, programs composed of various components with multiple time scale (both logically and physically) are often impossible to compile using traditional SR compilation techniques.

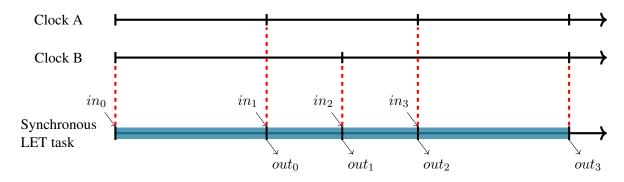

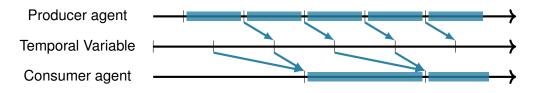

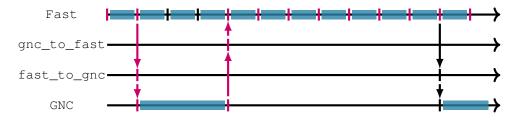

#### 3.2.3 Logical Execution Time languages

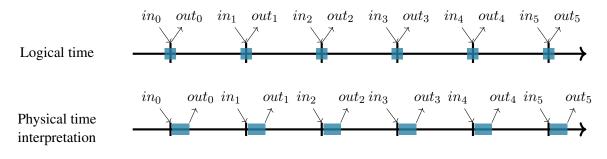

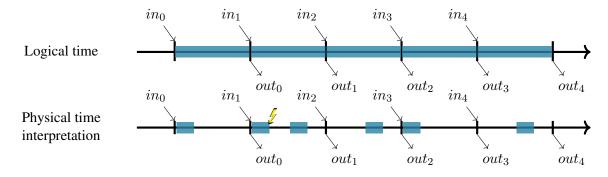

The *Logical Execution Time* (LET) [KS12] paradigm takes a different approach to specify temporal constraints; instead of specifying the computations by a reaction triggered on a clock tick, the execution time of those computations is abstracted such that a computation always behaves as if it lasts exactly a constant and fixed logical execution time. This defines an abstract time windows which contains the actual computation. However, to guarantee determinism, communication are done only on the boundaries of the LET time interval; inputs are read automatically on the start of the interval and outputs are produced automatically on the end of the interval. Figure 3.4 illustrates how LET abstracts computations: the upper part is the logical view interpreted by the model and the lower part is the physical view of a typical real-time implementation. The yellow symbol shows that in LET, execution can be typically preempted by other concurrent tasks while maintaining the communication behavior. Hence, contrary to SR, the semantics of LET allow more execution time variability for computations as (logical) computation durations are part of the semantics. This allows classical scheduling algorithms – such as EDF – to be used in the implementation.

Figure 3.4 – Typical execution of a logical execution time program in logical and physical time

GIOTTO is a time-triggered language implementing the logical execution time paradigm. It allows the definition of multiple modules parametrized by their periods which are, in turn, composed of tasks defined by their frequency. Tasks also have deterministic communication channels implementing LET communication to communicate together. Even if GIOTTO permits to describe mode and mode transition, tasks are basically strictly periodic which limits considerably its expressivity. Additionally, all constraints are expressed respectively to physical time; there is no clear distinction between logical time and physical time, nor discrete time basis as logical clocks. TIM-ING DEFINITION LANGUAGE (TDL) is an other language implementing LET extending GIOTTO concepts with a more advanced module and mode system. However, TDL suffers from the same issues as GIOTTO.

#### 3.2.4 Other languages based on logical time

Traditional Logical Execution Time languages suffer from expressivity limitations; they are often limited to multi-periodic behaviors with limited mode handling, but more importantly, timing durations are based on a unique chronometrical time base. This section describes languages

mixing aspects from both synchronous-reactive and logical execution time languages; they all rely on multiform logical time while also allowing logical durations of computations to be expressed.

#### The xGIOTTO language

XGIOTTO is a language implementing LET (as GIOTTO) but supporting events to specify synchronizations (i.e., to specify LET boundaries) [GHKS04]. In its principle, this language is closer to SR languages as logical time could express both timing or events. However, inter-arrival time assumption of events has to be encoded implicitly in the program using a rather complex mechanism called *event scoping* [KS12]. Event scopes define the computation to be taken in a given time span — specified by chronometrical time or events — and can be nested. Hence, the logical duration of a computation has to be refined to a chronometrical time basis for inter-arrival time to be considered. Hence, in this thesis, we consider that XGIOTTO computations can be triggered by events, but their deadlines are still specified by a chronometrical time basis, as in traditional LET.

The example below shows part of an automotive engine controller inspired by [GJSH05] based on two time bases: crankshaft and milliseconds. The controller is started on event *start* and immediately stopped — due to the ASAP policy — on event *stop*. Two concurrent tasks are shown: time which is triggered each millisecond and lasts one millisecond, and cycle which is triggered each crankshaft event and lasts two milliseconds.

```

1

react time() {

2

whenever [ms] react R1 until [ms];

3

}

4

react cycle() {

5

whenever [crank] react R2 until [2ms];

6

7

{

8

when [start]

9

react time() until asap [stop] ||

10

react cycle() until asap [stop] ||

11

12

}

```

Listing 3.4 – XGIOTTO controller example

#### The LINGUA FRANCA language

LINGUA FRANCA (or LF) [Loh20] is a coordination language based on a logical time framework called the Tagged Signal Model [LSV98]. The components of the language are called *reactors* and are essentially composed of *input port*, *output port*, and *reactions* that reacts to input events - called *tags* - coming from *input ports*. An application is defined by multiple *reactors* composed concurrently and by their port connections. We show in Listing 3.5 a very simple pipeline example using LINGUA FRANCA taken from [LL22]. The *reactors* are composed of a sensor task, two computing tasks and an actuator task connected in this order. The rate of the reactors are given by a logical clock (called *timer* in LF) triggering the sensor reaction each period, by default 10 milliseconds. In the semantics, by default, connected tasks are synchronous; when some reaction receives a message on a logical instant t, then it can produce an output message on the same logical instant t.

```

1

reactor Sensor(period:time(10 ms)) {

2

output out:int;

3

timer t(0, period);

4

reaction(t) -> out {=

5

6

= \}

7

}

8

reactor Task1 {

9

input in:int;

10

output out:int;

11

reaction(in) -> out {=

12

. . .

13

= \}

14

}

15

. . .

16

main reactor(period:time(10 ms)) {

17

/* we omit instantiation part */

sensor.in -> task1.in;

18

19

task1.out -> task2.in;

20

task2.out -> actuator.out;

21

}

22

```

Listing 3.5 – LINGUA FRANCA pipeline example

As explained in [LL22], LF can model LET behaviors using delayed connections between ports as shown in Listing 3.6 below; reactors task1 and task2 are assigned a LET duration of 10 milliseconds using the after construction. Note that, unlike traditional LET of GIOTTO or TDL, the semantics of LF is fully compatible with the synchronous-reactive one. Hence, reactors can be triggered by any event, or more generally, logical clocks. It is not clear however if the after construction allows the LET duration to be defined similarly, using a clock or event synchronization.

```

1 ...

2 main reactor(period:time(10 ms)) {

3 ...

4 task1.out -> task2.in after period;

5 task2.out -> actuator.out after period;

6 }

7

```

#### Listing 3.6 – LINGUA FRANCA LET pipeline example

#### The PSYC language

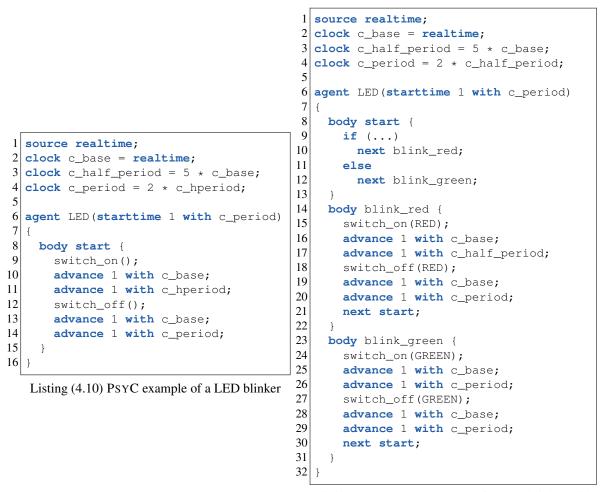

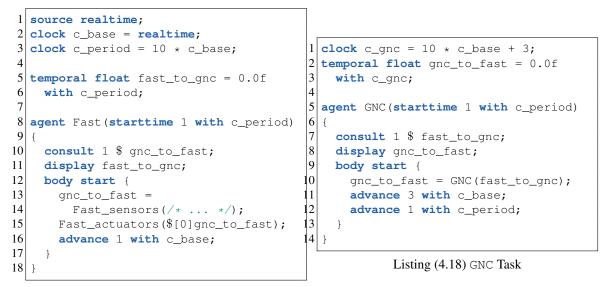

PSYC is an industrial language developed by Krono-Safe [KS23]. It is a language inspired by process algebras, synchronous-reactive languages, and with a principle very similar to Logical Execution Time. PSYC actually stands for *Parallel SYnchronous C*, thus highlighting the two main principles of the language: synchronous and parallelism (both in the model and in the implementation). In this thesis, we define PSYC based on an intermediate formalism that inherits from both synchronous-reactive and logical execution time approaches, called synchronous Logical Execution Time (sLET). In sLET, both the triggering instants and the duration of the computations are expressed using logical clocks. Hence, whereas in traditional LET a timing window is specified by a triggering instant and a chronometrical duration, in sLET, a timing window is specified by two successive synchronous instants that we call *synchronization points* (or *instants*).

Thus, comparing to ESTEREL, sLET (and PSYC) can specify the logical duration of computations, but inherit the delayed communication model from LET. Comparing to traditional LET languages such as GIOTTO, sLET uses logical clocks instants to specify interval boundaries instead of a unique chronometrical time basis. Both XGIOTTO and LINGUA FRANCA can rely on logical clock instants (respectively *events* and *tags*) to specify triggering instants and can specify the logical durations of the computations. However, logical durations are expressed by a chronometrical time basis in both cases; XGIOTTO rely on event scoping to encode implicitly inter-arrival times [KS12] and LINGUA FRANCA uses chronometrical time to express delays between reactors. The table 3.5 gives an overview of the main differences.

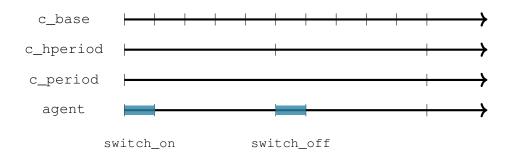

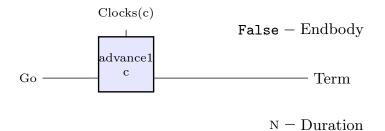

A PSYC application is composed of a set of concurrent *agents* (or processes) communicating through data-flow channels, called temporal variables. Agents are composed of C code and a dedicated temporal synchronization primitive: the advance instruction. This instruction is used to set a synchronization instant, acting as a time barrier, between *elementary actions*, which are timing intervals between two successive synchronizations. According to LET communication semantics, communications only take place atomically on these synchronisation instants. On the other hand, unlike LET, those instants are modeled relatively to logical clocks. In the following example, the end of the first *elementary action* containing f, corresponds to a synchronization of 2 ticks of the clock C. At this point, y is made visible to the other agents, and g can begin execution with the x input captured at this same instant.

#### y = f(); advance 2 with C; g(x);

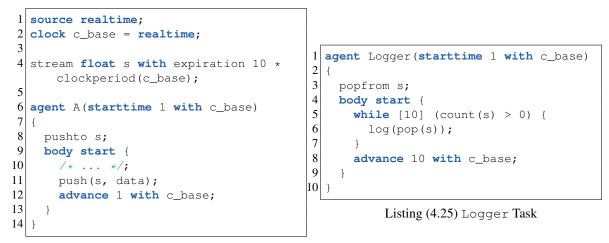

We give an illustration of a PSYC task in Listing 3.7 describing an agent performing conditional filtering (i.e., typically according to a system mode). First, the agent starts on the first tick of clock c1s, hence, 1000 milliseconds. Then, when the condition is true, the function filter has a logical duration of 3 ticks of clock c100ms, which is equivalent to 300 milliseconds in that case. It is then followed by an empty *elementary action* terminating on the next c1s tick; this is used to resynchronize on the task period. Indeed, when the condition is false, the task only performs an empty *elementary action* terminating on the next c1s tick.

```

1

clock c100ms = 100 * ms;

2

clock cls = 1000 * ms;

3

4

agent Filter(starttime 1 with cls) {

5

consult raw_data, mode /* inputs */;

6

display filtered_data /* outputs */;

7

body start {

8

if (mode == FILTER) {

9

filtered_data = Filter(raw_data);

10

advance 3 with c100ms;

11

}

12

advance 1 with cls;

13

}

14

}

15

```

Listing 3.7 – PSYC filter example

As in LINGUA FRANCA, PSYC is a language based on logical time which inherit both from LET and Synchronous-Reactive languages. As in LF, it generalizes LET using a semantics based on the synchronous-reactive approach. However, while LINGUA FRANCA is a general purpose coordination language, PSYC is an industrial language dedicated to safety-critical real-time systems. Hence, in this thesis, we focus on PSYC for various reasons. First, the PSYC language is developed by the company KRONO-SAFE who is funding this work. But most importantly, PSYC allow us to focus on a language that inherit from multiple logical time approaches while having major industrial projects using it (e.g., from the SAFRAN group). A detailed description of PSYC is given in chapter 4.

| Language      | Triggering instants     | Logical duration               | Communication model |

|---------------|-------------------------|--------------------------------|---------------------|

| ESTEREL       | logical clocks          | synchronous                    | synchronous         |

| GIOTTO        | chronometrical          | chronometrical                 | delayed             |

| XGIOTTO       | logical clocks (events) | chronometrical (event-scoping) | delayed             |

| LINGUA FRANCA | logical clocks (tags)   | chronometrical                 | both                |

| PSYC          | logical clocks          | logical clocks                 | delayed             |

Figure 3.5 – Comparative of some languages based on logical time

#### **3.3 Temporal Requirements Formalisms**

To define temporal requirements — also called *properties* — on the languages defined in the previous sections, we also need specific specification languages — actually closer to logics — allowing for a specific set of temporal behaviors. Ultimately, those specification languages are often used in formal verification to model-check the requirements on the program.

#### 3.3.1 Temporal logic

Formally reasoning about time goes back to Aristotle to interpret sentences such as "Tomorrow, there will be a sea fight" for philosophical purposes [Var08]. In the 19th century, Pierce described the need to extend classical logic with temporal operators:

« Time has usually been considered by logicians to be what is called "extra-logical" matter. I have never shared this opinion. But I have thought that logic had not yet reached the state of development at which the introduction of temporal modifications of its forms would not result in great confusion; and I am much of that way of thinking yet. Pierce » (C.S. Pierce)

However, it wasn't until the work of Pnueli in the late 1970s that a logic with temporal operators — called *temporal logic* — had been introduced. In particular, he exposes a *linear* temporal logic with future operator, called *LTL*, which can be defined by 4 main operators extending the traditional propositional logic [BK08]:

- $\bigcirc p$  (or *Next* p), holds if p holds on the next instant;

- U p q (or Until p q), holds if p holds on all instants until an instant on which q holds;

- $\Box p$  (or *Always p*), holds if *p* holds on all the following instants;

- $\diamond p$  (or *Eventually p*), holds if there exists a future instant on which p holds.

Additionnally, properties are often classified into two main classes:

- Safety properties state that "something bad should not happen". Typically, we want to prevent a bad condition to happen often modeled as an invariant that should hold on all reachable states of the program.

- *Liveness* properties state that "something good will happen". Contrary to safety properties, liveness properties guarantee that a good condition will hold sometimes in the future.

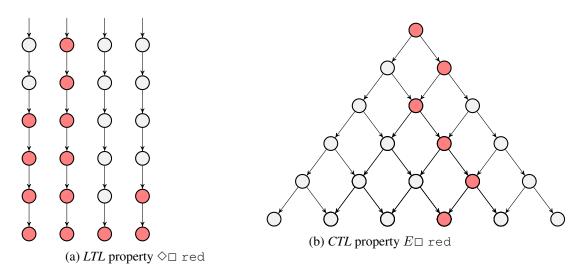

The vision of time described by LTL is, by definition, linear; to satisfy an LTL property, a program has to satisfy the property on each of its execution path. Another approach is to consider path quantification as in the Computational Tree Logic (CTL) [BK08]. CTL has two operators dedicated to path quantification: A p and E p to consider respectively universal and existential quantification for property p on execution paths of the program. Examples of LTL and CTL properties are shown in Figure 3.6. Additionnally, MTL is an other classical variations of LTL dedicated to *quantitative* temporal properties [Koy90]; classical LTL operators are extended with intervals that specify when the operator applies. As an example,  $\diamondsuit_{[0;10]} p$  specify that p should be reachable in the next 10 instants.

In our case, we want to focus on safety and linear properties as we want them to hold for all execution paths and mainly to prevent "bad things to happen" due to the safety-critical context. We also consider *bounded liveness* properties for latencies, but this is actually a special case of *safety*. However, in practice, programs based on logical time often rely on different timelines due to the use of multiple external clocks or tasks with different timing constraints. Temporal logic does not capture well properties that rely on multiple time scales — or multiple logical clocks.

Figure 3.6 – LTL and CTL property examples

#### 3.3.2 Clock Constraint Specification Language

CCSL is a specification language dedicated to the modelisation of temporal requirements defined as a set of constraints between logical clocks [And09]. Those logical clocks can be any sequence of events, similarly to the one considered in temporal logic. In this work, we choose CCSL to capture requirements as relations between the timing of multiple tasks because in PSYC, agent have usually different rates or time scales.

CCSL defines the four main following constraints:

- $c_1 \subseteq c_2$  which denotes that  $c_1$  should be a subclock of  $c_2$ ; thus, on each instant, if  $c_1$  holds then  $c_2$  should hold.

- $c_1 \prec c_2$  which denotes that  $c_1$  strictly precedes  $c_2$ ; thus, the  $n^{th}$  tick of  $c_1$  strictly precedes the  $n^{th}$  tick of  $c_2$ .

- $c_1 \leq c_2$  which denotes that  $c_1$  precedes  $c_2$ ; thus, the behavior is similar to the constraint above except that tick coincidence is allowed.

- $c_1 \# c_2$  which denotes exclusion between  $c_1$  and  $c_2$ ; thus,  $c_1$  cannot tick on the same instants as  $c_2$ .

Additionnally, each clock can be refined using CCSL expressions. We omit them here as an extensive description of CCSL is given in chapter 6.

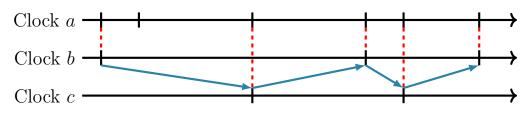

As a tiny illustration, consider the following set of constraints:  $b \ \ a, c \ \ a, b \ \ c, c \ \ c \ \ c, c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \ \ c \$

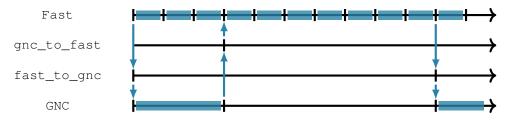

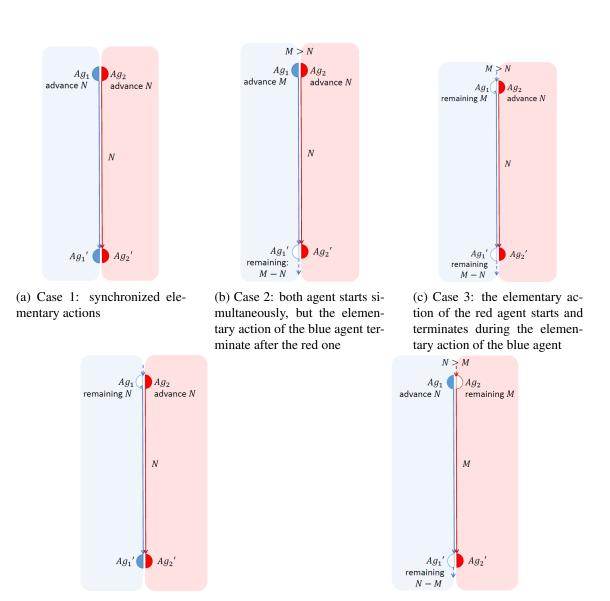

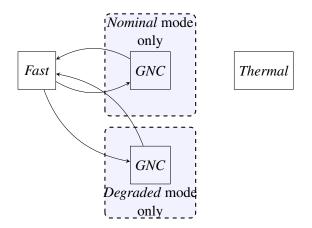

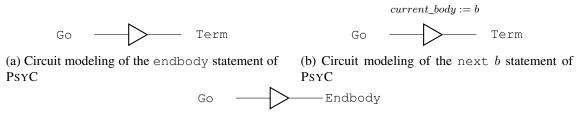

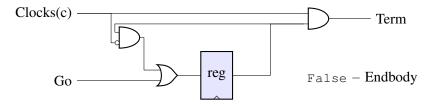

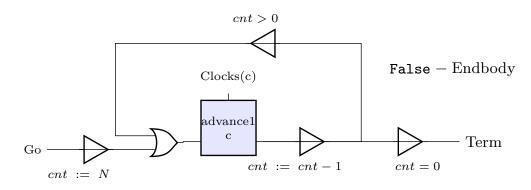

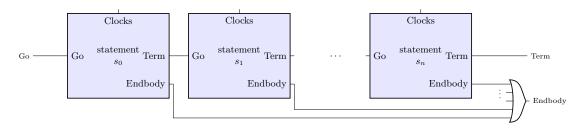

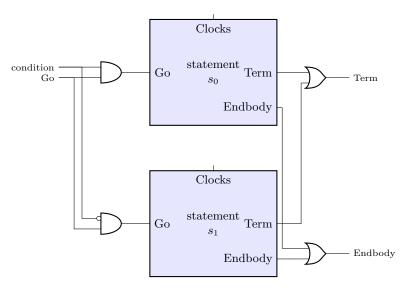

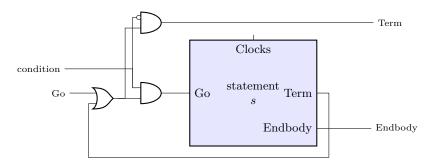

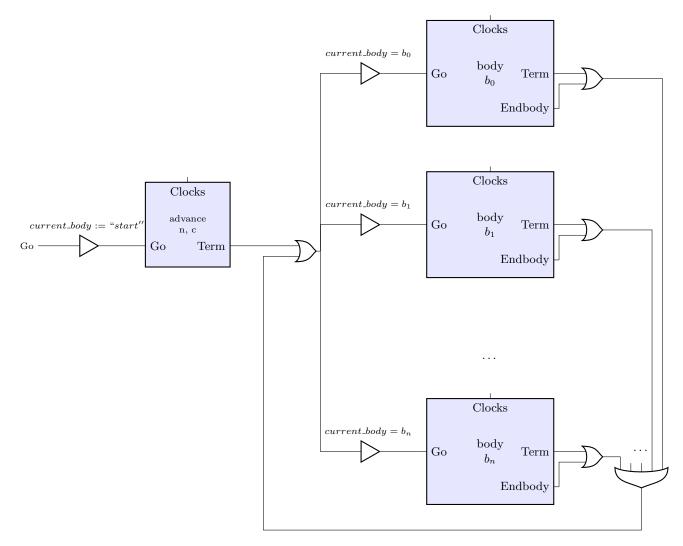

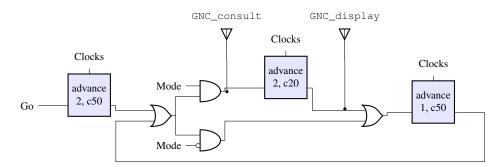

Figure 3.7 - Chronogram of a possible scheduling of the CCSL example