# Security enhancement in embedded hard real-time systems

Nicolas Bellec

### ▶ To cite this version:

Nicolas Bellec. Security enhancement in embedded hard real-time systems. Computer Science [cs]. Université rennes 1, 2023. English. NNT: . tel-04219240v1

# HAL Id: tel-04219240 https://inria.hal.science/tel-04219240v1

Submitted on 27 Sep 2023 (v1), last revised 13 Oct 2023 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

# THÈSE DE DOCTORAT DE

# L'UNIVERSITÉ DE RENNES 1

ÉCOLE DOCTORALE Nº 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Informatique

# Par Nicolas BELLEC

## Security enhancement in embedded hard real-time systems

Thèse présentée et soutenue à Rennes, le 23/05/2023 Unité de recherche : IRISA, Equipe PACAP

### Direction de thèse :

| Dirigée par :  | Isabelle PUAUT  | Professeur des Universités, IRISA Rennes |

|----------------|-----------------|------------------------------------------|

| Encadrée par : | Guillaume HIET  | Professeur, CentraleSupélec, Rennes      |

| -              | Frédéric TRONEL | Professeur, CentraleSupélec, Rennes      |

|                | Simon ROKICKI   | Maître de Conférence, ENS Rennes         |

### **Rapporteurs avant soutenance :**

Vincent NICOMETTE Professeur des Universités, INSA Toulouse Karine HEYDEMANN Maître de Conférence HDR, Sorbonne Université & Senior Expert Architecte, Thales

### **Composition du Jury :**

| Président :           | Gildas AVOINE     | Professeur des Universités, INSA Rennes       |

|-----------------------|-------------------|-----------------------------------------------|

| Examinateurs :        | Vincent NICOMETTE | Professeur des Universités, INSA Toulouse     |

|                       | Karine HEYDEMANN  | Maître de Conférence HDR, Sorbonne Université |

|                       |                   | & Senior Expert Architecte, Thales            |

|                       | Thomas CARLE      | Maître de Conférence, Université Toulouse III |

| Dir. de thèse :       | Isabelle PUAUT    | Professeur des Universités, IRISA Rennes      |

| Encadrants de thèse : | Guillaume HIET    | Professeur, CentraleSupélec, Rennes           |

# REMERCIEMENTS

Écrire cette thèse ne fut pas chose aisée. Je tiens donc à remercier en préambule toutes les personnes qui m'ont aidée tout au long de cette thèse.

Les premières personnes que je souhaite remercier sont mes encadrants de thèse, Isabelle Puaut, Frédéric Tronel, Guillaume Hiet et Simon Rokicki, qui m'ont épaulé durant ces (presque) quatre années de thèse. Un grand merci pour votre soutien et votre grande humanité, en particulier durant la période de rédaction.

Je remercie également Karine Heydemann et Vincent Nicomette pour avoir accepté de rapporter cette thèse ainsi que les autres membres du jury, Thomas Carle et Gildas Avoine.

Un remerciement particulier va à Gildas Avoine pour avoir accepté de présider mon jury de thèse et de m'avoir prodigué d'excellents conseils avec Hai Nam Tran durant le comité de suivi individuel. Merci aussi à Zoltan pour avoir pris le temps de me tutorer, ses conseils autour d'une pause-café à l'IRISA ont été très utiles.

J'ai eu la chance d'être très bien entouré durant ma thèse. J'ai pu en effet effectuer mes trois premières années de thèse dans un cadre accueillant qu'est l'IRISA au sein de l'équipe PACAP. Merci beaucoup aux membres de cette équipe pour leur accueil chaleureux, merci aux permanents, Erven, Pierre M., Isabelle, Pierre-Yves, André, Caroline et Damien, et aux non-permanents, Nassim, Lily, Camille, Antoine, Sara, Anis, Aurore, Hugo R., Nicolas, Pierre, Stefanos, Daniel et Niloofar, la "Team Gouter", qui ont animés les pauses-café avec une bonne humeur indétrônable. J'ai fini ma thèse avec un A.T.E.R à CentraleSupelec, dans l'équipe CIDRE, qui m'a très gentiment accueilli et je tiens à les remercier pour cet accueil des plus chaleureux, alors que je terminais mon manuscrit. Merci à l'équipe pédagogique et aux permanents, Jean-François, Frédéric, Guillaume, Pierre, Valérie, Pierre-François, Kévin, Michel, Emmanuelle, Ludovic, Yufei, Christophe, Gilles, et les non-permanents que j'ai pu rencontrer : Jérémy, Romain, Pierre-Victor, Nathan, Hélène, Racim, Maxime, Lionel, Jean-Marie, Lucas et Manuel. Un grand merci à Virginie, Lydie et Myriam, pour leur aide incroyable qu'elles m'ont apportée lors d'obscures démarches administratives.

Enfin, cette thèse n'aurait pas été possible sans le soutien d'Absint qui nous a fourni

gracieusement AiT, un logiciel propriétaire, qui m'a permis de faire tourner mes expériences. Pour cela, je les remercie.

Il y a aussi les membres des autres équipes de l'IRISA qui m'ont fait découvrir des sujets très intéressants. Pour cela, j'ai une pensée pour Benoit, merci pour tous ces cafés pris ensemble. Merci également à Nicolas et Mathias pour m'avoir invité à leurs séminaires "ELSE" de non-permanents, et plus généralement aux doctorants et post-doctorants de Sumo et Hycomes, Léo, Abdul, Bastien, Emily, Nicolas W., Hugo B., Aline, Adrian, et Joan, pour les pauses-café et fous rires partagés. Un grand merci à François Schwarzentruber et Sophie Pinchinat pour leur dynamisme et bienveillance.

Faire une thèse n'aurait pas été possible sans certains professeurs que j'ai pu rencontrer tout au long de ma scolarité, qui m'ont poussé à faire des sciences. En particulier, je remercie Mme Billerai qui m'a poussé à être plus rigoureux dans mes raisonnements, Mme Aulanier, pour m'avoir fait découvrir la recherche grâce à son atelier scientifique, et enfin à David Pichardie et Martin Quinson pour m'avoir donné ma chance en m'accueillant à l'ENS Rennes en informatique.

Merci à Nicolas L., Charles, Vincent, Nathan, Corentin, Pierre-Malo, Pierre-Louis, Jean-Pierre et Diego, mes amis de longue date, pour m'avoir fait découvrir les jeux de rôles et pour réussir à maintenir des séances hebdomadaires malgré la distance qui nous séparait durant la thèse. Merci pour cette bouffée d'oxygène.

Merci aussi à Clément, Rémi, Santiago, Léo, Solène, Hugo B., Hugo R., Lily et Joan pour toutes les soirées jeux autour d'une tasse de thé, et à Riwan pour tous ces moments de détente apportés.

Merci également aux amis avec qui je partage ma passion pour la danse. Merci à Filam, Guillaume De Longuemar, Léa, Guillaume Lefeuvre (encore un), Guillaume Bury (encore un !), Camille, Marie-Morgane et Marie-Audrey. Merci pour toutes les soirées de danse.

Merci à Pierre et Hadrien pour être d'aussi bons amis depuis aussi longtemps, j'ai toujours grand plaisir à vous revoir et à discuter avec vous.

Je remercie toutes les personnes de ma famille pour m'avoir supporté et soutenu pendant mes (longues) études, en particulier sur la dernière ligne droite qu'est cette thèse. J'ai une pensée émue pour mon père, avec une tristesse qu'il n'ait pas pu me voir commencer cette thèse. Merci de m'avoir transmis sa passion pour la technique dès mon enfance, d'avoir toujours été fier de moi. Merci également à ma mère d'être là pour moi et de m'avoir encouragé durant ma thèse.

Un autre type de soutien, plus original, m'a beaucoup apporté durant ma thèse : mon

chien, Plume. Merci de me forcer à sortir de nez de la recherche, et en fait de l'appartement, en particulier pendant les périodes de confinement.

Merci également à ma belle-famille, Sylvie, Frédéric, Mathilde, Barbara et Adrien, pour m'avoir accueilli aussi chaleureusement. Une pensée affectueuse aux deux derniers arrivants, Adélie et Orion.

Enfin, et c'est la plus importante, je remercie Emily, avec qui je partage ma vie. Elle a toujours été là, dans les meilleurs moments comme dans les pires, et pour cela, je la remercie du plus profond de mon cœur.

| 1 | Inti | roduct             | ion                                                   | 17 |

|---|------|--------------------|-------------------------------------------------------|----|

|   | 1.1  | Real-7             | Fime System characteristics impacting the security    | 18 |

|   | 1.2  | Attacl             | ker model                                             | 18 |

|   | 1.3  | Thesis             | 3                                                     | 19 |

| 2 | Bac  | kgrou              | nd & State of the Art                                 | 21 |

|   | 2.1  | Real-7             | Γime Systems                                          | 21 |

|   |      | 2.1.1              | WCET                                                  | 22 |

|   |      | 2.1.2              | Static estimation of WCET                             | 25 |

|   |      | 2.1.3              | Scheduling                                            | 28 |

|   | 2.2  | Securi             | ity of the memory                                     | 31 |

|   |      | 2.2.1              | Basic memory corruption attacks and first protections | 31 |

|   |      | 2.2.2              | Code reuse attacks and protections                    | 32 |

|   |      | 2.2.3              | Data-flow attacks and protections                     | 35 |

|   | 2.3  | Securi             | ty of real-time systems                               | 36 |

|   |      | 2.3.1              | Real-time system specific vulnerabilities             | 37 |

|   |      | 2.3.2              | Protecting the schedule                               | 37 |

|   |      | 2.3.3              | Adapting existing protection to real-time systems     | 38 |

| 3 | Ana  | alyzing            | 3 Data-Flow Integrity costs on Real-Time Systems      | 41 |

|   | 3.1  | Princi             | ple of software-implemented DFI                       | 42 |

|   |      | 3.1.1              | DFI static analysis                                   | 43 |

|   |      | 3.1.2              | DFI instrumentation                                   | 45 |

|   |      | 3.1.3              | DFI optimizations                                     | 47 |

|   | 3.2  | DFI Implementation |                                                       | 52 |

|   |      | 3.2.1              | Absence of virtual memory                             | 52 |

|   |      | 3.2.2              | Using RISCV architecture instead of x86               | 53 |

|   | 3.3  | Cost a             | analysis                                              | 56 |

|   |      | 3.3.1              | Experimental setup                                    | 57 |

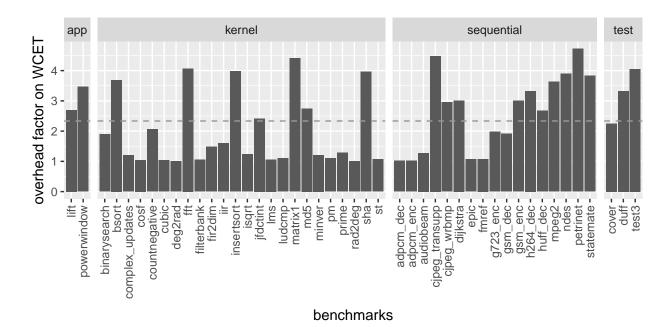

|    |        | 3.3.2   | Overhead of DFI on the WCET                                       | 58  |

|----|--------|---------|-------------------------------------------------------------------|-----|

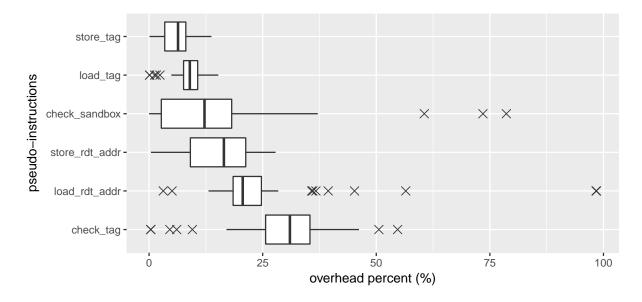

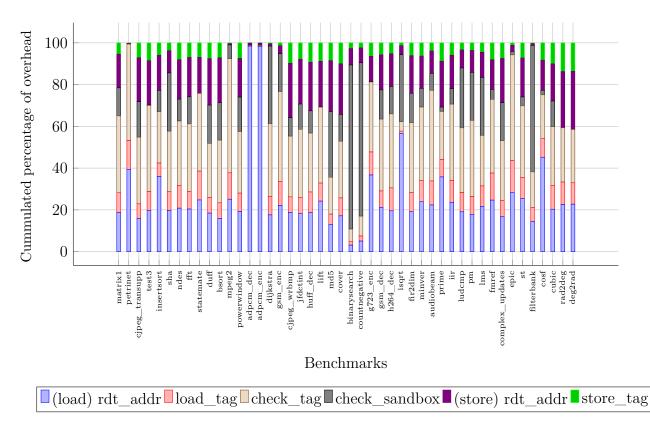

|    |        | 3.3.3   | Overhead per pseudo-instruction                                   | 60  |

|    | 3.4    | Conclu  | usion                                                             | 63  |

| 4  | Rec    | lucing  | load check costs with RT-DFI                                      | 65  |

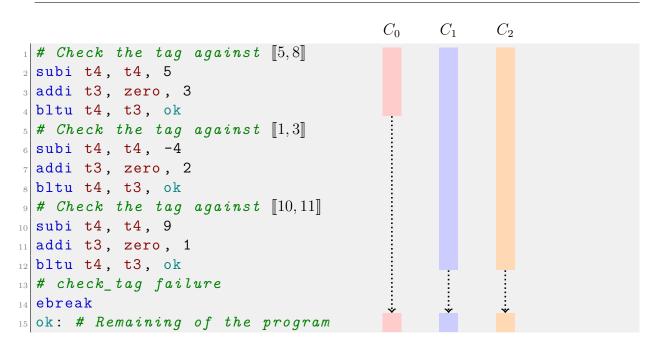

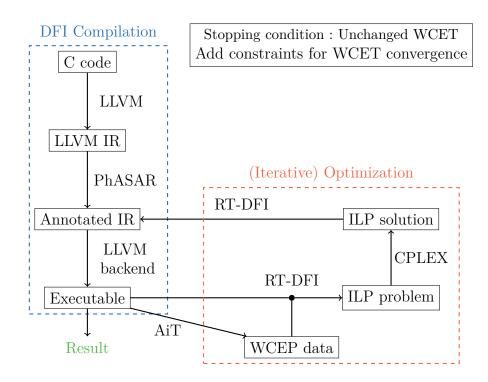

|    | 4.1    | Optim   | nizing the DFI impact on WCET                                     | 66  |

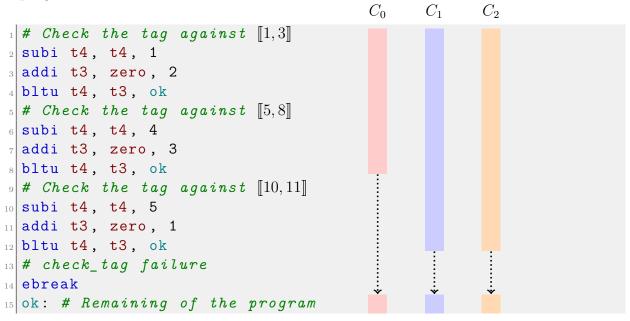

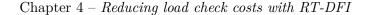

|    |        | 4.1.1   | Using WCEP information to optimize tag checks                     | 66  |

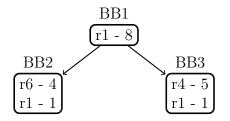

|    |        | 4.1.2   | Principle of the ILP                                              | 71  |

|    | 4.2    | Forma   | al definition of the ILP for WCET-oriented tag check optimization | 73  |

|    |        | 4.2.1   | Notation table and problem formal definition                      | 73  |

|    |        | 4.2.2   | Computing the number of checks                                    | 74  |

|    |        | 4.2.3   | Transformation into an ILP problem                                | 76  |

|    |        | 4.2.4   | Handling WCEP changes                                             | 79  |

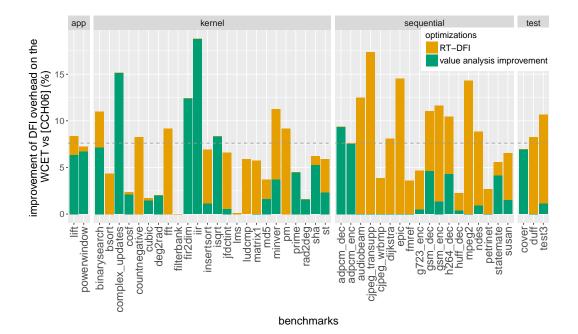

|    | 4.3    | Exper   | imental results                                                   | 80  |

|    |        | 4.3.1   | Experimental setup                                                | 80  |

|    |        | 4.3.2   | Results                                                           | 82  |

|    |        | 4.3.3   | Notes on iterative optimization                                   | 83  |

|    | 4.4    | Conclu  | usion                                                             | 84  |

| 5  | Rec    | lucing  | address computation redundancies                                  | 85  |

|    | 5.1    | Motiva  | ating example                                                     | 86  |

|    | 5.2    | Load S  | Store Chains construction and use                                 | 88  |

|    |        | 5.2.1   | Constructing LSChains                                             | 89  |

|    |        | 5.2.2   | Exploiting LSChains to remove redundant RDT address computation   | 91  |

|    |        | 5.2.3   | Beyond RDT address computation redundancy                         | 93  |

|    | 5.3    | Exper   | imental results                                                   | 94  |

|    | 5.4    | Discus  | ssion                                                             | 96  |

|    | 5.5    | Conclu  | usion                                                             | 99  |

| 6  | Cor    | nclusio | n & Future Work                                                   | 100 |

|    | 6.1    | Summ    | ary of the contributions                                          | 100 |

|    | 6.2    | Limita  | ations & Future Works                                             | 101 |

| Bi | ibliog | graphy  |                                                                   | 103 |

| A Experimental setups |       |                             |    |  |  |

|-----------------------|-------|-----------------------------|----|--|--|

|                       | A.1   | Benchmarks                  | 13 |  |  |

|                       |       | A.1.1 Notes on the security | 14 |  |  |

|                       | A.2   | Software                    | 14 |  |  |

|                       | A.3   | Hardware                    | 15 |  |  |

| Lis                   | st of | tables 1                    | 17 |  |  |

| Lis                   | st of | figures 1                   | 19 |  |  |

# **RÉSUMÉ EN FRANÇAIS**

De nombreux systèmes doivent réagir à des événements avant une date limite stricte afin de garantir leurs bon fonctionnement. Les avions et les voitures sont des exemples classiques de systèmes répondant à ces exigences. Ces systèmes sont aujourd'hui équipés de nombreux capteurs et doivent être capables de répondre suffisamment rapidement aux commandes qu'ils reçoivent afin d'assurer la sûreté de leurs utilisateurs ainsi que des personnes qui les entourent. Ces systèmes sont appelés **Systèmes temps réel** (*Real Time Systems* ou RTS en anglais), car ils doivent être conçus de manière à réagir assez rapidement aux événements à venir en toutes circonstances.

Historiquement, les systèmes temps réel ont utilisé des canaux de communication isolés (typiquement un bus de donnée CAN) car ils sont plus prévisibles. Cependant, on assiste à l'émergence de nouveaux systèmes temps réel utilisant des communications sans fil pour recevoir des commandes, transmettre des données et communiquer avec d'autres systèmes. Les drones volants sont un bon exemple de ce nouveaux type de systèmes. Un drone volant est intrinsèquement un système temps réel car il doit toujours adapter sa propulsion en fonction de son environnement. Il peut être contrôlé à distance, utilisé pour capturer des images qui doivent être envoyées à l'utilisateur et enfin, il y a une tendance à l'utilisation de flottes de drones capables de s'organiser pour accomplir une mission. Dans ces situations, la communication sans fil est essentielle pour communiquer avec l'utilisateur (soit pour recevoir des commandes, soit pour envoyer des données) et entre les drones.

Ces nouveaux canaux de communication sont également une excellente occasion d'attaquer ces systèmes. Avec les systèmes temps réel classiques, comme les communications ne se faisaient que dans un environnement fermé et contrôlé, attaquer un système signifiait déjà pouvoir communiquer avec lui, ce qui était suffisamment difficile pour empêcher de nombreuses attaques. Avec ces nouveaux systèmes, il suffit à un attaquant d'être suffisamment proche (typiquement à portée du wifi ou du bluetooth du système) pour lancer une communication et potentiellement attaquer le système. Ainsi, la sécurité des systèmes temps réel devient de plus en plus importante au fur et à mesure du déploiement de ces systèmes.

### Caractéristiques des systèmes en temps réel

Tout d'abord, décrivons certaines caractéristiques des systèmes temps réel qui ont un impact sur leur sécurité. Ces systèmes sont souvent écrits dans des **langages bas niveau** (typiquement du C) qui obligent les développeurs à gérer manuellement la mémoire. Ces langages sont sujets à des erreurs de gestion de la mémoire qui peuvent être exploitées pour attaquer les programmes. En utilisant ces erreurs, un attaquant peut briser les garanties du système en modifiant des parties de la mémoire qu'il ne devrait pas pouvoir changer. Cela peut conduire à un large éventail de problèmes affectant le système. Par exemple, un attaquant pourrait empêcher le système de répondre ou y exécuter son propre code, empêchant le système de fonctionner correctement.

Les systèmes temps réel sont également souvent **difficiles à mettre à jour**, car la modification du système nécessite de s'assurer à nouveau que toutes les échéances seront respectées par le système. De plus, les correctifs sont souvent plus difficiles à transmettre au système car ils ne disposent pas d'une connexion internet et doivent être en pause pour éviter de manquer des dates limites. Cela signifie que le délai entre la découverte d'une vulnérabilité et l'application d'un éventuel correctif peut être très long et que le système doit rester sûr pendant ce temps.

Enfin, les systèmes temps réel doivent être **prévisibles** afin de garantir les délais du système. Cela signifie que toute défense déployée pour protéger le système doit également être prévisible, en particulier dans l'estimation de son temps d'exécution, afin de s'assurer que le système peut toujours respecter ces garanties. En particulier, cela empêche le déploiement de nombreuses défenses modernes qui utilisent des sources d'aléatoire pour rendre plus difficile la tâche de l'attaquant qui doit trouver des informations cruciales pour monter son attaque<sup>1</sup>.

### Modèle de l'attaquant

De nombreuses attaques existent à différents niveaux d'un système. Certaines attaques se concentrent sur le réseau et les protocoles pour extraire des informations confidentielles, contourner les authentifications ou rendre le système indisponible. À l'inverse, certaines attaques se concentrent sur le matériel utilisé par le système, faisant fuir des informations par des canaux auxiliaires (utilisant des différences temporelles ou les émissions électro-

<sup>&</sup>lt;sup>1</sup>tel que les protections PIE et ASLR

magnétiques) ou même en injectant des fautes pour modifier le comportement du système.

Dans cette thèse, nous concentrons notre attention sur les attaques logicielles qui utilisent une vulnérabilité sur la gestion de la mémoire. Nous supposons que l'attaquant a trouvé une erreur logicielle lui permettant de corrompre la mémoire, c'est-à-dire d'écrire dans une partie inattendue de cette dernière. Cette erreur peut alors être utilisée par l'attaquant pour modifier un point arbitraire de la mémoire. À titre d'exemple, l'attaquant pourrait avoir trouvé un dépassement de tampon qui lui permet d'écrire en dépassant les limites d'un tableau et de modifier d'autres variables sur la pile. Il pourrait alors utiliser cette vulnérabilité pour changer des variables importantes dans la pile et modifier le comportement du programme.

Nous nous concentrons sur ce modèle d'attaquant pour deux raisons. Premièrement, ces vulnérabilités sont courantes dans le code des langages bas niveau. Rien qu'en 2022, le MITRE a répertorié 331 enregistrements CVE<sup>2</sup> basés sur des corruptions de la mémoire. La deuxième raison est due à la connectivité accrue des RTS. La gestion de nouvelles interfaces réseau nécessite des piles réseau complexes, également écrites dans des langages bas niveau, qui peuvent aussi être vulnérables aux corruptions de mémoire<sup>3</sup>. Comme ces piles sont utilisées par de nombreux systèmes, la moindre vulnérabilité dans l'une d'entre elles pourrait mettre en péril de nombreux systèmes, ce qui en fait des cibles très intéressantes pour un attaquant.

## Thèse

Dans cette thèse, nous présentons nos travaux concernant la sécurité des systèmes temps réel. Plus précisément, nous avons étudié une protection appelée Intégrité du flux de donnée (*Data-Flow Integrity* ou DFI en anglais) qui existait déjà pour les programmes génériques et nous l'avons adaptée pour prendre en compte les contraintes et caractéristiques des systèmes temps réel. Cette thèse est composée de cinq chapitres : un chapitre qui introduit le contexte, trois chapitres contenant nos contributions, et une conclusion. Le chapitre 2 présente une vue d'ensemble sur les systèmes temps réel, les attaques et les protections contre les corruptions de mémoire ainsi qu'un état de l'art sur la sécurité des systèmes temps réel. Le chapitre 3 présente notre implémentation et l'analyse du surcoût

$<sup>^2 {\</sup>rm Common}$ Vulnerability Exposure, une base de données qui répertorie les vulnérabilités présentes dans les programmes couramment utilisés

$<sup>^3 {\</sup>rm comme}$  la série de vulnérabilités URGENT/11 sur la pile TCP/IP de VxWorks, un système d'exploitation temps réel

de la protection DFI. Le chapitre 4 présente notre première contribution qui optimise certaines parties de la protection DFI pour réduire son surcoût le long du Chemin de Pire Temps d'Exécution. Le chapitre 5 présente une deuxième contribution qui optimise également le DFI en supprimant des redondances dans les instrumentations de la protection. Enfin, le chapitre 6 conclut cette thèse en résumant nos contributions et en proposant des travaux futurs pour poursuivre ces recherches.

# PUBLICATIONS

This thesis is based on the following paper:

Nicolas Bellec, Guillaume Hiet, Simon Rokicki, Frédéric Tronel, Isabelle Puaut. *RT-DFI: Optimizing Data-Flow Integrity for Real-Time Systems*, in ECRTS 2022 - 34th Euromicro Conference on Real-Time Systems.

During the beginning of this thesis, we also published another paper based on a work done during the master internship. This paper is not discussed in the rest of this thesis:

Nicolas Bellec, Simon Rokicki, Isabelle Puaut. Attack Detection Through Monitoring of Timing Deviations in Embedded Real-Time Systems, in ECRTS 2020 - 32th Euromicro Conference on Real-Time Systems.

#### Chapter 1

# INTRODUCTION

Many systems need to respond to specific events before a strict deadline to ensure their correct behavior. Planes and cars are examples of systems with these requisites. These systems are now equipped with many sensors and must be able to respond fast enough to the commands they receive in order to ensure the safety of their users as well as other people around them. Such systems are labeled **Real-Time Systems** (RTS) as they must be designed to ensure that they react before their deadlines to the coming events in all circumstances. To guarantee that no deadline can be missed by the system, RTS are validated before being deployed.

To ease this validation, RTS have historically used isolated communication channels (typically a Controlled Area Network bus) as it is easier to analyze the latencies of such channels, making them more predictable. However, there is an emergence of new RTS using wireless communications to receive commands, transmit data and communicate with other systems. A good representative of these new systems are flying drones. A flying drone is intrinsically a RTS as it must always adapt its propulsion in function of its environment. It can be controlled at a distance, used to capture images that must be sent back to the user and finally, there is a trend in using fleets of drones capable of organizing themselves to complete a mission. In these situations, wireless communications are essential to communicate with the user (either to receive commands or send data) and between the drones.

These new communication channels are also a great opportunity to attack these systems. With classical RTS, as the communications only happen in a closed and controlled environment, attacking a system already meant being able to communicate with it, which was hard enough to prevent many attacks. With these new RTS, an attacker just has to be close enough (e.g. at the range of the Wi-Fi or Bluetooth of the system) to start a communication and potentially attack the system. Thus, the security of RTS is becoming more and more important as these systems are massively being deployed.

# 1.1 Real-Time System characteristics impacting the security

Let's describe some characteristics of RTS that impacts their security. First, RTS are often written in **low-level languages** (typically C) that require the developers to manually manage the memory. These languages are prone to memory errors that can be exploited to attack the programs. By using memory errors, an attacker can break the guarantees of the system by modifying parts of the memory he/she should not be able to. This can lead to a wide range of issues impacting the system. For example, an attacker could crash the system or execute its own code on it, preventing the system from functioning correctly.

RTS are also often **hard to update** as modifying the system requires to re-validate that no deadline can be missed by the system. Furthermore, patches are often harder to deploy onto the system as RTS can operate for long periods of time during which they can not be updated. This means that the window of time between the discovery of a vulnerability and the application of an eventual patch can be very long. The system must remain safe during that period of time.

Finally, RTS requires to be **predictable** in order to guarantee the deadlines of the system. This means that any defense deployed to protect the system must also be predictable to ensure that we can still provide these guarantees. In particular, it prevents the deployment of many modern defenses that use randomness to prevent the attacker from finding crucial information to mount his/her attack<sup>1</sup>.

### 1.2 Attacker model

The manual management of the memory combined with the predictability of RTS makes them very vulnerable against a common class of vulnerabilities called **memory corruption vulnerabilities**. The vulnerabilities in this class uses an error the memory management to writes and read at unexpected places in memory, modifying the behavior of the program or corrupting important data. Such vulnerabilities are already very common as shown by MITRE that listed 331 CVE records<sup>2</sup> based on memory corruption in 2022

<sup>&</sup>lt;sup>1</sup>Such as the Position Independent Executable (PIE) combined with Address Space Layout Randomization (ASLR) that requires a high entropy to effectively protect a program [SPP<sup>+</sup>04], which makes cache analyses very pessimistic [FGG18]

$<sup>^2\</sup>mathrm{Common}$  Vulnerability Exposure, a database that lists vulnerabilities found in commonly used programs

alone. Furthermore, the increased connectivity of RTS requires complex network stacks that are also written in low-level languages and can also be vulnerable to memory corruption<sup>3</sup>. As these stacks are used by many systems, any vulnerability in one of these could endanger many RTS, making them very interesting targets for an attacker.

In this thesis, we wish to improve the security of real-time systems against memory corruption vulnerabilities. We focus our work on memory corruption based on a software attack (i.e. without the attacker physically attacking the system) as these attacks are the most likely to affect many RTS. Thus, we suppose that the attacker found a software error allowing him to corrupt the memory, i.e. that he/she is able to write in an unexpected part of the memory. The attacker can then use this error to modify an arbitrary point in memory.

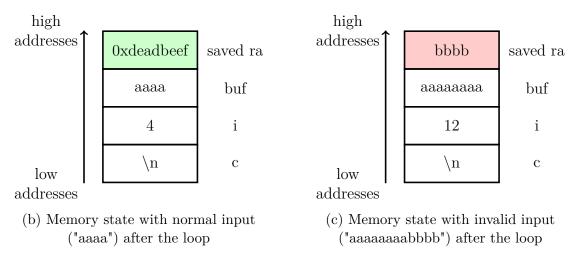

As an example, the attacker could have found a buffer overflow that allows him to write paste the bounds of a buffer and modify other variables on the stack. The attacker could then use this vulnerability to modify important variables in the stack and modify the program behavior.

### 1.3 Thesis

In this thesis, we present our work regarding the security of real-time systems. More specifically, we studied a protection called Data-Flow Integrity (DFI) that already existed for general programs [CCH06] and we adapted it for real-time systems.

We first analyze the overhead of this protection on the Worst-Case Execution Time (WCET) to establish where we should focus our optimizations. This analysis shows that three parts of the DFI are responsible for most of the overhead of this protection. The first responsible part verifies that the data loaded by the program is not corrupted at runtime. The second part computes addresses to a special table containing metadata used by the first part. Finally, the third part ensures that this table and the program code can not be modified by the protected program.

Knowing which part of the DFI are the most important sources of overhead, we first focus our effort to reduce the overhead of the first part on the WCET. To do so, we combine an Integer Linear Programming solver with data retrieved when estimating the WCET, reducing the overhead of DFI by a mean 7.6% in our experiments. This contribution was

$<sup>^3 \</sup>rm Such$  as the URGENT/11 set of vulnerabilities on the real-time operating system VxWorks' TCP/IP stack

#### Introduction

published in the 34th Euromicro Conference on Real-Time Systems.

We then tackle the overhead of the two other parts by detecting redundant computations in consecutive uses of these parts. We present a method that reduces these redundancies at the basic-block level using available registers. This method presents a mean 14.4% improvement in our experiments.

This thesis is composed of five chapters: one chapter that introduces some background, three chapters containing our contributions, and a conclusion. Chapter 2 presents an overview regarding real-time systems, memory corruptions attacks and defenses as well as a state-of-the-art about security of real-time systems. Chapter 3 presents our analysis of the overhead of Data-Flow Integrity. Chapter 4 presents our first contribution that optimizes one part of the DFI to reduce its overhead along the Worst-Case Execution Path. Chapter 5 presents a second contribution that also optimizes the DFI by removing redundancies in the protection instrumentation. Finally, Chapter 6 concludes this thesis by summarizing our contributions and providing future works to continue this research.

#### Chapter 2

# **BACKGROUND & STATE OF THE ART**

#### Chapter overview

In this chapter, we present some background on real-time systems and security against memory corruption attacks. We first present real-time systems and how their properties are guaranteed. We then present memory corruption attacks and the protections developed against these attacks. Finally, we present a state of the art of the security for real-time systems.

### 2.1 Real-Time Systems

Real-time systems (RTS) are systems composed of multiple **tasks** with constraints on the execution time of each task. A **deadline** is associated to each task and represents how much time the task has to finish. Such systems are present in many parts of our daily life, from a simple controller on a washing machine to the system controlling a satellite or a power plant. Ensuring that every task in the system respects its deadline is thus very important as any deadline miss could compromise the safety of the system (e.g. a satellite missing a deadline on its navigation task could end up colliding with debris or another satellite). To guarantee the respect of every deadline, RTS are subject to a temporal evaluation. First, the maximum execution time, called the **Worst-Case Execution Time** (WCET), of each task is estimated in isolation. The WCETs are then used to verify that, given a specific scheduling policy, the system will meet all its deadlines.

In this section, we first present the different methods to establish the WCET of the tasks in a system in Subsection 2.1.1. We then dive deeper into the static analysis method in Subsection 2.1.2, as this is the one we use in the rest of this thesis. Finally, we present how the WCETs are used to verify the schedulability of the system in Subsection 2.1.3.

### 2.1.1 WCET

To ensure that a task has enough time to finish before its deadline, its WCET is estimated first. The WCET of a task is the maximum time it takes for that task to execute on the system (in particular, on the system's hardware) when running in isolation (i.e. without the interference of other tasks).

Knowing the exact WCET of a given task is often impossible as it requires to analyze all the possible executions of the program on the system's hardware. As the number of states of the program and of the hardware increases exponentially with the size of the program, such analysis is almost never possible, especially with the extremely complex hardware architectures that we use nowadays. Thus, the WCET analysis aims at estimating an upper bound of the WCET that is as tight as possible to the real WCET (that we do not know). We search for an upper bound of the WCET to ensure that a task cannot run more than its estimated WCET in any circumstance. This property ensures that we can use the estimated WCET to verify the schedulability of the system.

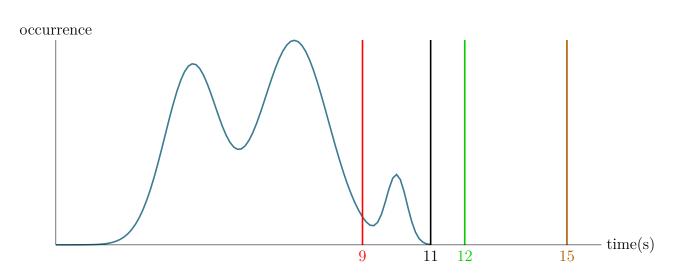

In Figure 2.1, we show an example of the distribution of the execution time of a task. A first point of observation is that the execution time may vary greatly between two executions. We also see that the distribution is bounded by an upper value, 11s in this example. This value is the real WCET. However, as we do not know this distribution perfectly when analyzing a task, we have to estimate this value. In our example, we show three possible estimations. The first one (9s) is not an upper bound of the real WCET and is thus an unsafe estimation of the WCET. Such estimation, can lead to false guarantees that the system meets all its deadlines. The second (12s) and third (15s) values are upper bounds of the real WCET and are thus safe estimations of the WCET. These values can both be used to ensure that the system meets its deadlines. However, the 15s value is more pessimistic than the 12s value, which can lead to pessimism in the schedulability analysis. In particular, the analysis may respond that the system is not schedulable with the 15s value while it would be with the 12s value. Thus, we also want the WCET analysis to return an as tight as possible estimation of the WCET (i.e. an estimation that is close to the real value).

Numerous tools have been proposed to estimate the WCET using different methods. The survey [WEE<sup>+</sup>08] presents many such tools. We can split the methods in three categories: measure based estimation, static analysis based estimation and hybrid estimation.

Figure 2.1 – Illustration of the real and three estimated WCETs for a given execution time distribution of a task

### 2.1.1.1 Measure based estimation

Measure based estimation uses measurement of the execution time of a task on the system to estimate the WCET of the task. By measuring numerous execution times (with many distinct inputs), these methods try to retrieve the execution time distribution of the task. In particular, such methods do not need to be given a hardware model of the system to estimate the WCET of the task. However, as these methods only have access to an estimation of the distribution, they are not sure to capture the real WCET in their measures. A common way to compensate this risk of under-approximation is to use Extreme Value Theory (EVT). This theory estimates the risk that a rare event happens based on previous events. For example, EVT can be used to estimate the risk of an earthquake of magnitude higher than a given threshold happening in a region, knowing the history of seismic activity of the region. This theory is based on a given number of hypotheses that must be verified to use it. Reghenzani et al. [RMF<sup>+</sup>19] worked on verifying that the hypotheses of EVT are experimentally valid. The tightness of the estimated WCET is also important to guarantee the schedulability of the systems. To this regard, Vilardell et al. [VSM<sup>+</sup>22] presented a method using Markov's inequality and power-of-k functions (functions of the form  $x^k$ ) to reduce the pessimism of methods using EVT.

#### 2.1.1.2 Static analysis based estimation

To the opposite of measure based estimation, static analysis based estimation uses a model of the system's hardware and a static analysis of the task to estimate an upper-bound of the WCET. The main downside of these techniques is the necessity to provide a model of the system's hardware, which can be very complex for modern hardware architectures. This can lead to a more pessimistic WCET estimate which can later hurt the schedulability analysis. On the other hand, if the hardware model and the analysis are correct and provide an over-estimation of the behavior of the real system, static analysis ensures that the estimated WCET is an upper-bound of the real WCET. This is in particular very important for critical systems (such as in power plants or in avionics) in which failing to meet a deadline could cause a catastrophe.

Many tools have been developed to statically estimate the WCET. AiT [FH04] is an industrial close-source estimator with many hardware models. However, as the tool is closed-source, researchers cannot implement new methods or hardware models for it. To test new analyzes, other estimators such as Heptane [HRP17] and OTAWA [CS06] exist. These estimators are open-source and with a particular focus on some specific analyzes used to estimate the WCET.

#### 2.1.1.3 Hybrid estimation

Hybrid estimation associates static analysis based estimation and measure based estimation to estimate the WCET. The main idea is to measure many program executions and to derive the probability distribution of the execution time for blocks of code. These data are then fed to a static analysis method that searches for the path with the highest execution time. This provides better guarantees than measure-only estimation while not requiring to provide a hardware model.

Bernat et al. [BCP03] proposed a probabilistic framework for hybrid estimation based on measurement of the execution time of the basic-blocks<sup>1</sup>. This led to multiple works that have been summarized in a survey by Cazorla et al. [CKM<sup>+</sup>19].

Bonenfant et al. [BCD<sup>+</sup>17] proposed to use machine learning to derive an early estimation of the WCET of a piece C source code. Machine learning have also been used by Amalou et al. [APM21] to estimate the WCET of basic-blocks at the binary level and

<sup>&</sup>lt;sup>1</sup>Basic-blocks are sequences of instructions such that the only way to branch in the sequence is at the entry and the only way to branch out of the sequence is at the exit.

then to combine these estimations into a WCET estimation of the whole task using static techniques.

### 2.1.2 Static estimation of WCET

In the rest of this thesis, we focus on static estimation of the WCET as this method also provides very useful information about the task under estimation. These data can typically be used to optimize the task in order to reduce its WCET. In this part, we present the different analyses that are often used when statically estimating the WCET. By abuse of notation, as we almost never have access to the real WCET, we use the term WCET to refer to the estimated WCET in the rest of this document.

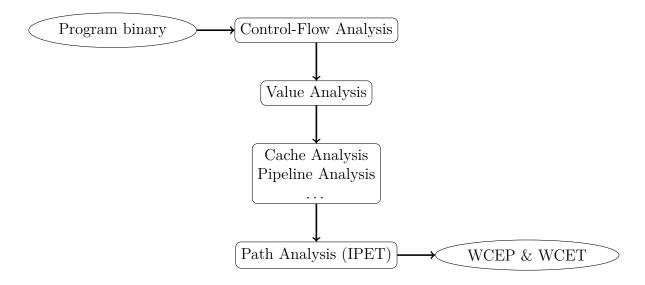

We present in Figure 2.2 a common sequence of analyzes performed by a WCET estimator. The WCET estimation is performed on the binary of a program rather than its source code to ensure that we know precisely which instructions are executed as well as the memory layout of the program under analysis. This is particularly useful to obtain a tight result as the WCET analysis depends on the micro-architecture.

Figure 2.2 – Pipeline of analyzes for WCET estimation

A common approach for static WCET estimation is to estimate the WCET of each basic-block and then find the longest path in the program with the WCET of each basic-block as weight. This requires to first perform a **Control-Flow analysis**. This analysis retrieves the structure of the program from its binary representation and determines a

superset of the possible paths in the program. In particular, this analysis retrieves the functions, the basic-blocks and the edges between the basic-blocks as well as the function calls and loops.

Another important analysis to estimate the WCET and whose results can be used to optimize the task is the **Value analysis**. This analysis estimates the value in each memory cell and each register used by the task. This is a particularly important analysis to detect infeasible paths in the program, loop bounds and is further used by other analyzes such as cache analysis. For example, if the value analysis is able to detect that a given register is equal to five for a conditional jump and the jump is only taken if the value of the register is less than three, then we can ensure that the jump cannot be taken, removing a path for the other analyzes (in particular, the search of the longest path). To improve their precision, value analyzes often provide multiple results on the same part of the code in different contexts when this part can be reached multiple times [TSH<sup>+</sup>03]. For example, in a loop, there might be a context for the first iteration of the loop and another for subsequent iterations, allowing the analysis to have more precise results on the first iteration and collapsing the results of all other iterations in the second context results. This is particularly useful to obtain a good trade-off between the analysis cost (in terms of time and memory) and its precision.

Finally, another family of analyzes that is crucial for the static estimation of the WCET is the micro-architectural analysis family. By using abstract timing models of the system's architecture, the analyses of this family deduce the possible set of states of the architecture when executing the basic-blocks of the program, to deduce the WCET of each basic-block in the different contexts. This family typically regroups the **Cache Analysis** and the **Pipeline Analysis**. The cache analysis aims at determining the state of the caches and, in particular, at detecting the cache misses and cache hits that could occur and impact the execution time of the task [FW99]. The pipeline analysis [LTH02] tries to establish the pipeline behavior. In particular, we are interested in knowing the number of cycles required to execute a basic-block, taking into account the latencies induced by memory accesses or conflicts of resources inside the processor. Other analyses can be needed with complex processors containing features such as branch prediction. In this case, specific analyses that estimate the impact of such features on the estimated WCET of a basic-block are required to obtain a tight upper-bound on the WCET for each basic-block.

Once the WCET of each basic-block is estimated, these estimations are combined to estimate the overall WCET of the task. This last analysis, called **Path Analysis**, searches

(a) CFG for the IPET

(b) IPET formulation

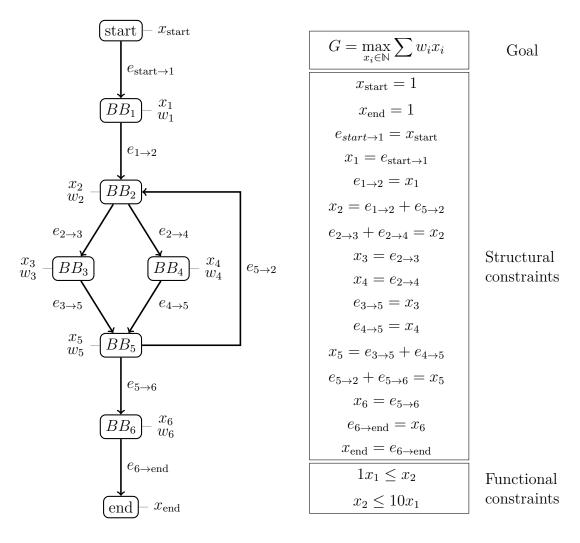

Figure 2.3 – IPET example based on [LM95]

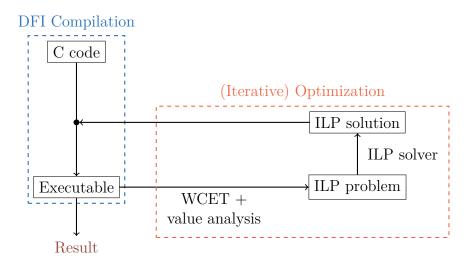

a path in the **Control-Flow Graph** (CFG) of the task with the highest estimated execution time, the so-called **Worst-Case Execution Path** (WCEP). The classical method to do so is with the **Implicit Path Enumeration Technique** (IPET). The IPET encodes the problem of finding the path with the highest execution time as an **Integer Linear Programming** (ILP) problem [LM95]. As an example of this method, we show in Figure 2.3 the CFG (2.3a) of a simple program and the resulting ILP (2.3b). For each basic-block  $BB_i$ , we note  $w_i$  its WCET and  $x_i$  an ILP variable that represents the number of time this basic-block is executed in the WCEP. For each edge between  $BB_i$  and  $BB_j$ , we note  $e_{i \rightarrow j}$  an ILP variable that represents the number of time the edge is taken in the WCEP. The goal of the ILP is to maximize  $\sum w_i x_i$ , that represents the maximal execution time of the path selected by the ILP.

A first set of **structural constraints** are used to encode in the ILP the limits due to the structure of the program. In particular, we encode that each basic-block is executed as many times as an edge enters it in the path and that each execution of a basic-block leads to an execution of one of its successor in the CFG. This is expressed by the following formula:  $\sum_{i \in \text{pred}(BB_j)} e_{i \to j} = x_j = \sum_{k \in \text{succ}(BB_j)} e_{j \to k}$ . In this set of constraints, we also find limits such as  $x_{\text{start}} = 1$  and  $x_{\text{end}} = 1$  that express that the task only start and end once (to estimate its WCET).

A second set of constraints, called **functional constraints**, encodes information about the functionality of the program. In the example, we can find constraints about the loop bounds of the loop that can only have between 1 and 10 iterations. Encoding loop bounds typically prevents an unbounded ILP problem. This is in this set that we can also find constraints that encode program specific behaviors which can improve the precision of the WCET estimation. For example, if  $BB_4$  could only be executed once in the loop, a constraint  $x_4 \leq 1$  would be added, potentially reducing the estimated WCET if  $w_4 > w_3$ .

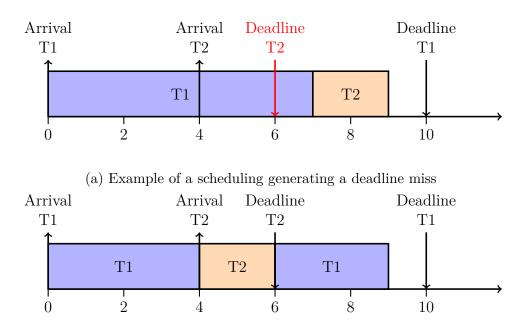

### 2.1.3 Scheduling

Verifying that the system always respects its timing constraints requires the estimation of the WCET of each task in the system. However, WCETs alone are not enough to ensure that multiple tasks running in parallel won't miss their deadlines. Interferences between the tasks may prevent a task from running, generating a missed deadline. For example, in Figure 2.4, we present two scenarios with the same set of tasks (T1 and T2) but with two different scheduling policies. We suppose that T1 requires seven units of time to execute while T2 only requires two units of time. With the first policy (Figure 2.4a), the system never preempts a running task, which leads to a deadline miss for the task T2 as this task arrives while T1 is already running. On the other hand, with the second policy (Figure 2.4b), the system preempts a running task when another task has less time to complete, preventing the deadline miss in our example.

These considerations led to many researches on the impact of the schedule and how to ensure the absence of deadline miss for different systems and schedulers. In this section, we only provide a light overview of the existing works as a context for the thesis.

(b) Example of a correct scheduling

Figure 2.4 – Example of scheduling policies with two tasks T1 (WCET=7) and T2 (WCET=2)

Depending on the characteristics of the system and of the set of tasks, many methods have been proposed to ensure the schedulability of the system. A first class of methods is to find sufficient schedulability conditions that, when verified, ensure that the system is schedulable with a given scheduling policy. Jie et al. [JRZ10] provide a survey on many such conditions, in particular for uniprocessor scheduling.

For example, let  $S = \{\tau_1, \tau_2, ..., \tau_n\}$  be a task set with  $(T_i, W_i)$  the couple (period, WCET) of  $\tau_i$ . We suppose that the deadline of a task, i.e. the maximum time allowed for the task to execute, is equal to its period. The **Earliest Deadline First** (EDF) scheduling policy

always executes the task with the earliest deadline. It supposes that the system can preempt running tasks and that the system uses a uniprocessor. In the absence of inversion of priority, typically caused by a task of higher priority (according to EDF) accessing a shared variable reserved by a task of lower priority, the EDF scheduling policy has the following sufficient condition: if  $\sum_{i=1}^{n} (W_i/T_i) \leq 1$ , then S is schedulable.

Another method to ensure the schedulability of the system is to perform a **Response Time Analysis** (RTA) [JP86]. The RTA consists in estimating the response time of every task in the system, i.e. the time between the arrival of the task (the moment the task is ready to be scheduled) and the time the task finishes its execution, considering the interferences of the other tasks. If, for every task in the system, its response time is lower than its deadline, then the system is schedulable. However, obtaining a safe and tight upper bound of the interferences between the tasks can become very complicated, especially with multiple, heterogeneous cores. This can make the analysis too pessimistic from some schedulable systems.

Finally, the schedulability of the system can be estimated by exploring the space of possible schedules to ensures the absence of deadline misses. This is in particular useful when dealing with multiprocessor systems where the previous methods fail. Guan et al. [GGD<sup>+</sup>07] proposed to use timed automata to search the schedule space of sets of tasks with static-priority on a multiprocessor system. By transforming the schedulability problem into a reachability problem in a timed automaton, Guan et al. can use well known reachability algorithms to exhaustively search the schedule space and ensure that the system is schedulable. Yalcinkaya et al. [YNB19] extended this idea to non-preemptive self-suspending sets of tasks.

The main problem with these methods are the resources required to execute them (in terms of time and memory). Reachability algorithms for timed automata are known to be PSPACE, which often makes them intractable on large schedulability problems.

Thus, a new method has emerged since 2017 [NB17] to search the scheduling space without relying on timed automata. This method uses **Schedule Abstract Graphs** (SAG) that abstract all the possible execution orders of the tasks. By using such a graph, one can prove (or disprove) that the system may not cause a deadline miss. The main advantage of this method is its computation time. By abstracting and merging some scheduler states (e.g., when the order of scheduling of a subset of tasks does not modify the arriving state), evaluating the schedulability with this method can be much faster than with timed automata, even if the problem remains exponentially complex [RNN22].

### 2.2 Security of the memory

The apparition in 1988 of the Morris' worm [ano21] has shown the importance of protecting the memory against corruption attacks. These considerations have also started appearing for RTS as memory corruption can break the guarantees on the system. In this section, we present the evolution of software-based memory corruption attacks and protections without considering the real-time properties of a system.

### 2.2.1 Basic memory corruption attacks and first protections

The most classic memory corruption attack consists in writing data past the bounds of a buffer. This attack, called **buffer overflow**, has been described in [One96]. In Figure 2.5, we present an example of a program vulnerable to this attack. This program receives a password and stores it in a buffer of eight characters. In a normal use-case, the memory of the program is presented in Figure 2.5b. The password ("aaaa") is contained in the variable **buf** and the other parts of the stack are not affected. However, when an attacker provides a password longer than 8 characters, the program continues to write past the buffer limits into other variables on the stack. In Figure 2.5c, we present the case of the input "aaaaaaaabbbb" (eight 'a' followed by four 'b'). In this case, we can see in memory that the value of the **saved ra** has been written over by the attacker. As the **saved pc** value is the address to which the program returns when finishing the execution of the function, this means that the attacker can control which instructions the program will execute after this function.

The first method to exploit such a vulnerability is to write the binary code of a small program (typically called a **shellcode** as it is often used to launch a shell) into the buffer. Then, by writing past the buffer, we overwrite the saved instruction pointer (i.e. **saved ra**) with the address of the buffer. When the function returns, the saved instruction pointer is restored and the program jumps to the written code and executes it.

To protect against such attacks, a first protection that appeared was to prevent writable parts of a program from being executable. This protection is often referred as  $\mathbf{W} \oplus \mathbf{X}$ (write xor execute) and prevents directly writing the code you want to execute into the buffer before jumping on it. Another common protection is to randomize where parts of the program are loaded. This protection, called **Address Space Layout Randomization** (ASLR), was first used to randomize the start address of the stack and the libraries and thus prevent the attacker from finding where he/she should return to execute its

```

void get_password() {

char buf[8];

char c = recv();

for (int i = 0; c != '\n'; ++i ) {

buf[i] = c;

c = recv();

}

...

}

```

Figure 2.5 – Example of a buffer overflow vulnerability

shellcode. However, other techniques appeared to bypass these protections.

### 2.2.2 Code reuse attacks and protections

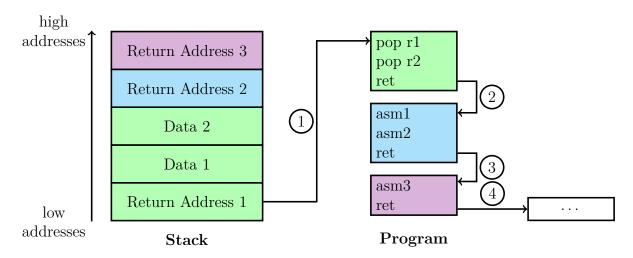

Instead of writing the code to execute into the memory and then execute it, we can use code that already exists in the program. In practice, most programs loads a standard library (typically the *libc*) which contains functions to launch new processus (e.g. *execve*). By jumping to one of these functions, we can easily obtain an arbitrary execution of code (by launching a shell for example). A generalization of this method is to use small snippets of code that finish by a return instruction (called **gadgets**) and to link them together to execute arbitrary code. As there are many such gadgets in most binaries, finding the right gadgets to execute an arbitrary sequence of instructions is often possible. This generalization is called **Return-Oriented Programming** (ROP) and remains one of the main methods to use a memory corruption vulnerability inside a program [CW14] [vdVAS<sup>+</sup>17].

Figure 2.6 – Example of Return-Oriented Programming

In Figure 2.6, we present an example of ROP. The attacker overwrites the stack such that a first return address ("Return Address 1" in our example) overwrites the return address of the function with the rest of the stack setup by the attacker as in the figure. When the program returns, it first jumps to the return address placed on the stack to a first gadget. In the example, this gadget loads some data placed by the attacker onto the stack into registers. The program then returns again, this time jumping to the gadget pointed by "Return Address 2". It then executes a few instructions and returns again, this time to the address pointed by "Return Address 3". As we see here, the attacker can ultimately link as many gadgets as he/she needs to create its own program inside the program.

A first protection against such attacks is to prevent the attacker from knowing the addresses of the gadgets in memory. This protection, called **Position Independent Code** (PIE), extends the ASLR protection to the program code and not just the libraries. However, it requires to re-compile the program such that the whole program can run whatever the address at which it is loaded. Each time the program is launched, this protection loads the program in a randomized part of the virtual memory such that the attacker can not predict the addresses of the gadgets. The main problem of this protection is that any data leak about the address of a function (inside the code) can allow the attacker to retrieve the address at which the program has been loaded, which breaks the

protection (note that ASLR has the same issue).

To further increase the difficulty for the attacker to find gadgets, finer grain randomization have been proposed such as **Selfrando**<sup>2</sup>. This protection randomizes the addresses of the functions in the program at each execution. As with PIE and ASLR, this prevents the attacker from predicting the addresses of gadgets. However, as each function address is randomized separately, the attacker needs to leak much more addresses to find enough gadgets to mount its attack.

Another protection against memory corruption, especially buffer overflows, is the use of a **stack canary**. This protection inserts a value, randomized at each program execution, at each function call between the stack frame (containing the local variables) and the saved registers. Just before the function returns, this value is checked to ensure it has not changed. If the value has changed, then the value of the stored registers cannot be trusted and an exception is raised. However, an attacker can easily bypass this protection either by leaking the value of the canary to overwrite the canary with the correct value, or by overwriting directly the registers without modifying the canary (with a well modified pointer for example).

To provide a stronger protection against ROP, Abadi et al. [ABE<sup>+</sup>05] presented the Control-Flow Integrity (CFI) and the shadow stack protections. The shadow stack protection stores the return addresses of called functions in a so-called *shadow stack*. When the function returns, the return address in the stack is compared with the return address in the shadow stack to verify that they are the same. If it is not the case, a memory corruption is detected and an exception triggered. This protects against ROP but still allows attacks that modify function pointers (e.g. to call *execve*). On the other hand, CFI ensures that when calling a function, the program does not deviate from a control-flow graph that have been extracted at compile time. In particular, this means that an attacker that modifies a function pointer cannot redirect the control-flow wherever he wants but is forced to choose among a restricted set of functions. By using both CFI and a shadow stack, the goal is to prevent an attacker from exploiting a memory corruption vulnerability in the program by preventing any illegal jump.

CFI has two main weaknesses that can be exploited to bypass it. First, as Evans et al. showed  $[ELO^+15]$ , the precision of the control-flow graph is extremely important to obtain a good protection. The control-flow graph often contains imprecision, containing paths that do not exist in the real program (especially due to the precision of pointer/alias

<sup>&</sup>lt;sup>2</sup>https://github.com/runsafesecurity/selfrando

```

1 char buffer[12];

2 char c = 255;

3 int height = getHeight();

4 for(int i = 0; c != 0; i++) {

5 c = recv();

6 buffer[i] = c;

7 }

8 if (height >= 10000)

9 crash plane()

```

Figure 2.7 – Example of program vulnerable to a Data-only attack

analyzes). An attacker can use these paths to bend the control-flow and carry its attack while remaining undetected by the CFI. The second weakness of CFI is the apparition of new attacks that exploit memory corruption vulnerabilities without modifying the control-flow [CXS<sup>+</sup>05]. These attacks target the data-flow of the program instead of the control-flow and can thus remain undetected even with the best CFI.

### 2.2.3 Data-flow attacks and protections

Data-flow attacks modify values in the memory of the program that are later used by the program to take a decision. For example, the attacker could modify a loop counter such that the loop iterates more time than it is supposed to. This can then lead the program to read a cryptographic key that the attacker can later use to break into the system.

A more concrete example is present in Figure 2.7. In this example, supposedly placed in an airplane, the program receives a number of characters that are placed on a buffer of size 12. As the size of the received data is not checked, it is easy for an attacker to overflow past the buffer and to overwrite the saved instruction pointer. However, if a protection such as CFI protects the program, overwriting the instruction pointer would be easily detected. On the other hand, the attacker could also just modify the **height** variable with its buffer overflow, remaining undetected by the protection while forcing the program into the nefarious function **crash\_plane**.

To protect the systems against data-flow attacks, new protections that ensure the integrity of the data-flow have been proposed. Castro et al. [CCH06] proposed the **Data-Flow Integrity** (DFI) protection that instruments store and load instructions in the program to verify at each load instruction that the loaded data has been written by a

store instruction that is supposed to write it (based on a statically analyzed data-flow graph of the program). In the rest of this document, we use the term DFI instead of DFI protection for simplification purpose. Akritidis et al. [ACR<sup>+</sup>08] proposed **Write Integrity Testing** (WIT). This protection computes for each store instruction in the program a set of objects that the instruction can write into. The protection then instruments the program to ensure that each store instruction writes in one of the object in its set and adds guards between the objects to detect overflows from one object to another. Compared to DFI, WIT trades off the protection for better performances. Indeed, while DFI can detect a large class of attacks including data-only attacks and some information leaks, WIT can only defend against data-only attacks. However, WIT has a time overhead up to 25% while DFI can go up to 150% on some benchmarks. Furthermore, as they are both based on a static analysis of the program to produce their data-flow graph, they can both have an imprecise data-flow graph which could let an attack slip through [DS16] even if this is far more complicated than with CFI.

Other protections have also been developed to obtain memory safety (i.e. a protection that stops all memory corruption exploits) such as CCured [NCH<sup>+</sup>05], Cyclone [JMG<sup>+</sup>02] or Softbound [NZM<sup>+</sup>09]. These protections use *fat-pointers* which are pointers with metadata attached to them to store the bounds of the pointers. However, such pointers tend to prevent binary compatibility and to have a large overhead [SPW<sup>+</sup>13]. Another notable work in this domain has been the development of CHERI [WWN<sup>+</sup>15] that aims at using hardware implemented fat-pointers to improve the security of programs without too much overhead.

## 2.3 Security of real-time systems

With the increase in complexity and the addition of new communication channels (e.g. Bluetooth, Wi-Fi), RTS have become the target of new attacks. Such attacks negatively impact the safety of these systems as each attack potentially breaks the timing and safety properties of the system. As these systems are more and more integrated in our daily life, the risk of attacks on these systems impacts the safety of more and more people. As an example, Millers et al. [MV15] were able to take the control of the brakes of an unmodified car using wireless communication while Carsten et al. [CAY<sup>+</sup>15] presented multiple vulnerabilities in car systems due to the complexity of these systems. This led to an increased focus on the security of these systems. In this section, we present security

issues and proposed solutions specific to real-time systems.

#### 2.3.1 Real-time system specific vulnerabilities

Real-time systems require to be predictable to obtain a tight estimation of the WCET and to perform the schedulability analysis. However, this increased predictability can be exploited by the attackers to trigger new vulnerabilities.

A first security issue for RTS is the predictability of the scheduling. As the set of tasks running on a RTS is easier to predict than on a general system, it is also easier for an attacker to detect the arrival of specific tasks that he/she wants to target. Chen et al. [CMP<sup>+</sup>19] presented such an attack as a side-channel in preemptive fixed-priority schedulers that can reveal the arrival time of future jobs. Such a side-channel can be used to launch advanced attacks such as cache side-channel attacks to recover a cryptokey by targeting a specific task. Kwak et al. [KL18] presented a covert timing channel that allows two conspiring tasks in a uniprocessor real-time system to communicate using timing variations. For example, this could be used to extract data (e.g. a cryptokey) from a specific task into another task, although these tasks are isolated in terms of memory.

Many RTS also use sensors to estimate the state of their environment and decide the next step of operation. For example, an autonomous car uses cameras and radars to detect obstacles, signalization and other cars in order to safely move in its environment. An attacker could disrupt the sensors of one such system in order to feed false-data to the system. For example, Cao et al. [CXC<sup>+</sup>19] presented an attack on cars with lidar-based perception where they could modify the car perception and make the car crash.

Finally, real-time systems are often written in low-level languages such as C or C++ that are known to be vulnerable to memory corruption attacks. The tendency of RTS to not use non-deterministic hardware mechanisms (e.g. virtual memory and MMU) and protections (e.g. ASLR) to improve the predictability of the system tends to ease the work of attackers. For example, the absence of ASLR in a system often means for an attacker that he can brute-force the address space to find interesting addresses that he can use.

#### 2.3.2 Protecting the schedule

To protect real-time systems against attacks using predictable schedule, a first method has been to randomize the schedule. However, as the RTA of the system depends on the schedule, the randomization of the schedule must still ensure the schedulability of the system. Yoon et al. [YMC<sup>+</sup>16] presented a protection, called *TaskShuffler*, that randomizes the scheduler while maintaining the schedulability of the system. To ensure the schedulability, the randomizer bounds, for each task  $\tau_i$ , the maximum time other lower priority tasks can execute instead of  $\tau_i$ . Vreman et al. [VPK<sup>+</sup>19] presented an upper-bound on the number of random schedules that can be obtained for a system while maintaining its schedulability. This upper-bounds can be used to evaluate whether randomizing the schedule improves the security or if the configurations can be deduced by the attacker. However, Nasri et al. [NCB<sup>+</sup>19] showed that schedule randomization can sometime make the system more vulnerable to attacks rather than improving the security by transforming an inherently safe schedule into a schedule where sensitive tasks could appear in a vulnerable order.

Another method, presented by Völp et al. [VHH08], is to modify the scheduler to prevent timing side-channels. By estimating if a blocking thread could leak information and using the idle thread (a thread that does nothing), this protection is able to prevent the leakage of information using timing side-channels. However, it requires a higher budget for the scheduling and is limited to fixed-priority schedulers.

#### 2.3.3 Adapting existing protection to real-time systems

Real-time systems must be predictable to guarantee their timing constraints. This leads to many constraints that prevent the use of general protections against memory corruption attacks as many of these protections either worsen the predictability of the system (such as ASLR or CFI) or require specific hardware (e.g. a MMU). Furthermore, real-time OSes tend to be simplified to ease their timing verification and improve their predictability. In particular, that means that protections often provided by the kernel on general computers are not present in a real-time OS, which further ease the exploitation by the attackers.

Thus, there is a gap between existing protections for general computers and protections fit for RTS. A first method to bridge this gap is to adapt the analyses used to estimate the WCET. Fellmuth et al. [FGG18] proposed to modify the instruction cache analysis to reduce the pessimism of this analysis in presence of artificially diversified software at different levels. Their study focused on three levels of artificial diversity: segment-level (typically ASLR), function-level (the order of the functions in the executable is randomized at runtime, similar to *Selfrando*) and block-level (each basic-block of each function is randomized). By modifying the instruction cache analysis to handle artificial diversity, they try to obtain a more precise analysis while providing an important protection for the program. Another method to use general purpose protections in RTS is to adapt them to the system at hand. For example, Abad et al. [AvdWL<sup>+</sup>13] proposed a hardware-implemented CFI with a predictable overhead such that it can be used by RTS while Walls et al. [WBB<sup>+</sup>19] proposed RECFISH, a CFI specialized for ARM Cortex-R devices that does not rely on process isolation provided by the operating system. Both these approaches modify existing protections (in both these cases: CFI) and adapt them to real-time systems that have different features and requirements. Mishra et al. [MCG21] presented a survey on CFI methods specialized for real-time systems. In this survey, in additions to the CFI techniques already presented, we can also find new methods that rely on using specific characteristics of RTS. For example, Wolf et al. [WFU<sup>+</sup>12] and Bellec et al. [BRP20] use information on the WCET coupled with the CFG to detect anomalies in the control-flow at runtime via timing anomalies.

Fellmuth et al. [FHP<sup>+</sup>17] proposed to use information on the WCEP to guide the artificial diversification of real-time tasks. By knowing the WCEP, the protection can diversify the program on this path up to a given budget such that the maximum overhead on the WCET is fixed by the developer. Furthermore, the program can also diversify the basic-blocks outside the WCEP without impacting the WCET by computing a metric called **criticality** [BHJ12] that acts as a timing distance between a basic-block and the WCEP.

Finally, Yoon et al. [YMC<sup>+</sup>17] and Kadar et al. [KTF19] used the predictability of RTS to protect them. They both learned predictable patterns of how system calls are used by the system. Then, when the system is deployed, they monitor the system calls. If they detect an abnormal pattern, they consider it indicates the presence of an attack.

In conclusion, real-time systems' security is still in its infancy. Almost all the works presented in this section are still very recent (almost all have been presented after 2017) and new vulnerabilities are discovered every year in these systems. It is thus important to provide new protections adapted to RTS that are able to resist against attackers that use more and more sophisticated attacks. This is precisely what we do in this thesis by adapting DFI to real-time systems and by optimizing it to reduce its impact on the WCET.

#### Chapter 3

# ANALYZING DATA-FLOW INTEGRITY COSTS ON REAL-TIME SYSTEMS

#### Chapter overview

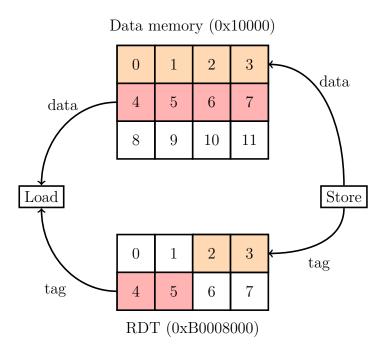

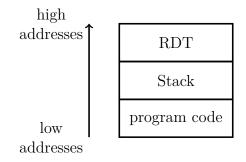

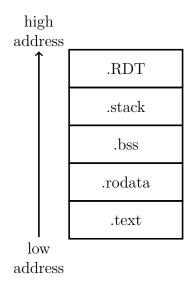

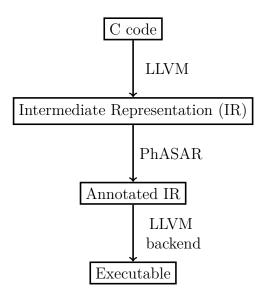

The goal of this chapter is to analyze the impact of **Data-Flow Integrity** (DFI) on the Worst-Case Execution Time in order to target our optimizations presented in the next chapters. We first present how DFI works and which optimizations already exist for it in the literature. We then present our implementation of DFI as no reference implementation exists and we focus our work on real-time systems. Using our implementation, we empirically analyze the cost of this protection on the Worst-Case Execution Time, and we determine which parts of DFI are the most likely to drive this cost. We show that the timing overhead of DFI is mainly concentrated in 3 parts which are the tag check at each load, the computation of the addresses in the **Runtime Definition Table** (RDT) and preventing store instructions from modifying the RDT.

**Data-Flow Integrity** (DFI) is a protection against memory corruption attacks introduced in 2006 by Castro et al. [CCH06]. DFI attempts to detect when a loaded value has been written by an instruction that should not have written it. Before the protected program loads a value from memory, DFI first loads a metadata (called a **tag**) associated to that value. That metadata represents which instruction stored that value in memory. DFI then checks that this metadata belongs to the set of valid tags for that load. If it does, the value can be loaded by the program. If not, a memory corruption is detected and an exception is raised.

As DFI protects the whole memory, it can tackle advanced attack schemes such as Non-Control Data Attacks [DS17] that use corrupted data without affecting the program's control-flow. This means that DFI can detect a wide range of memory corruption attacks, including the most recent software-only attacks, and help the system react accordingly to survive these attacks. Furthermore, software-implemented DFI only adds a few instructions before each load and store instruction in the program and does not require help from the system itself. As these instructions are simple instructions (mostly arithmetic instructions and fixed target jumps), a WCET estimator should be able to analyze a program protected with DFI and estimate a coherent WCET without the need for manually provided information. Thus, the main issue to use DFI for real-time systems is its memory and time overhead. Indeed, the time overhead of DFI on the average runtime is known to be important (up to 150% in some experiments [CCH06]). It would not be surprising to have a similar or higher overhead on the estimated WCET which would inevitably prevent the use of DFI.

To establish the overhead of DFI on the estimated WCET and find real-time specific optimizations, we first need an implementation of DFI. However, there is no off-the-shelf implementation available. Thus, we developed our own version based on the description presented in [CCH06].

In this chapter, we start by presenting how DFI works in Section 3.1. In Section 3.2, we explain the implementation choices we made when developing our version of DFI. Finally, we present a cost analysis of our DFI implementation in Section 3.3 where we detect three main sources of overhead for DFI. We use this cost analysis to motivate our contributions presented in the next two chapters.

## 3.1 Principle of software-implemented DFI

To protect a program, DFI first analyzes and instruments the program at compile time. The instrumentation of the program then dynamically checks that the program behaves correctly based on the performed analysis. If at any time the program does not behave correctly, the instrumentation raises an exception to be handled by the system on which the program is executing. For example, to ensure that the system still respects its schedule, one way to handle such an exception could be to have a deteriorated state where the system only ensures the most critical tasks.

In this section, we present how DFI protects a program and the optimizations proposed in the original paper [CCH06]. We first introduce the static analysis part of DFI in Subsection 3.1.1. We then present the instrumentation part DFI that handles the protection at runtime in Subsection 3.1.2. Finally, we present in Subsection 3.1.3 the existing optimizations for DFI as proposed by Castro et al. [CCH06].

#### 3.1.1 DFI static analysis

**Remark.** In this thesis, we often use **load** and **load instruction** indifferently as well as **store and store instruction** indifferently.

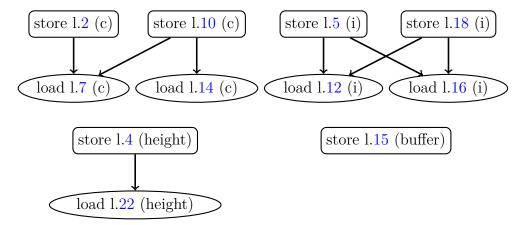

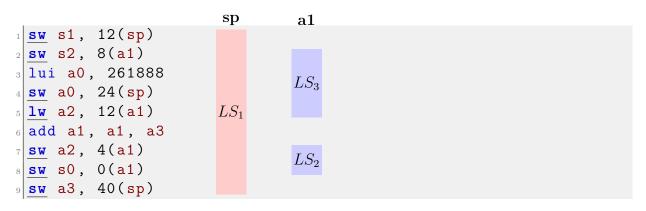

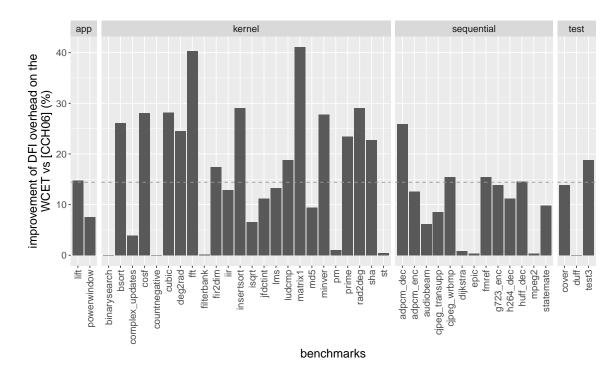

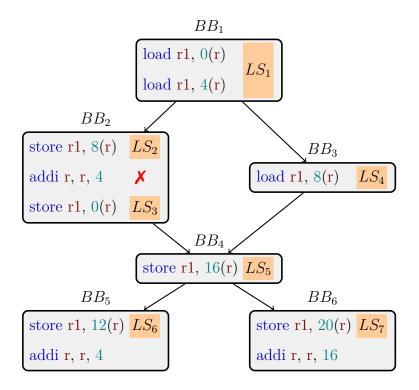

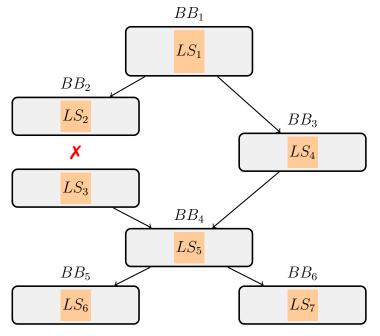

The static analysis used by DFI is based on determining, for each load instruction in the program, which store instructions may have legitimately written the loaded data. To do this, we construct, at compile time, a **Data-Flow Graph** (DFG) which is a bipartite graph where nodes are load/store instructions and an edge between a store and a load represents the fact that this load can read data written by this store. A program example is shown in Figure 3.1 with its DFG presented in Figure 3.2. This example contains the C code of the program (Figure 3.1a), to understand the goal of this code snippet, and a RISCV assembly version of the program (Figure 3.1b) on which the DFG is constructed. In this example, we have some variables and a simple loop that writes received characters into a buffer. In the DFG, we identify each instruction by its type (store or load) and its line number. We also add the variable name on which the instruction operates.