# A full stack simulator for HPC: multi-level modelling of the BXI interconnect to predict the performance of MPI applications

Julien Emmanuel

### ▶ To cite this version:

Julien Emmanuel. A full stack simulator for HPC: multi-level modelling of the BXI interconnect to predict the performance of MPI applications. Modeling and Simulation. Université Claude Bernard - Lyon I, 2023. English. NNT: 2023LYO10029. tel-04211680v2

## HAL Id: tel-04211680 https://inria.hal.science/tel-04211680v2

Submitted on 22 Apr 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THESE de DOCTORAT DE L'UNIVERSITE CLAUDE BERNARD LYON 1

# **Ecole Doctorale** N°512 **InfoMaths**

**Discipline**: Informatique

Soutenue publiquement le 08/03/2023, par :

# Julien EMMANUEL

# Un simulateur pour le calcul haute performance : modélisation multi-niveau de l'interconnect BXI pour prédire les performances d'applications MPI

### Devant le jury composé de :

Legrand, Arnaud Coti, Camille Quinson, Martin Guérin-Lassous, Isabelle Perache, Marc Moy, Matthieu

Henrio, Ludovic Pichon, Grégoire Directeur de Recherche Professeure Professeur des Universités

Professeure des Universités Directeur de Recherche

Maître de Conférences

Chargé de Recherche Ingénieur CNRS Grenoble ÉTS Montréal ENS Rennes Université Claude Bernard

Lyon 1 CEA Arpajon

Université Claude Bernard Lvon 1

Lyon 1 CNRS Lyon Atos – Echirolles Président du Jury Rapporteuse Rapporteur Examinatrice

Examinateur Directeur de thèse

Invité Invité

# S Résumé

Pour obtenir les meilleures performances possibles dans les supercalculateurs, il est aujourd'hui nécessaire d'utiliser des réseaux d'interconnexion de plus en plus sophistiqués. C'est pour répondre à ce besoin qu'Atos produit le réseau BXI, composé de cartes réseau (NIC) et de commutateurs (switches). Le paramétrage optimal de ce matériel est une problématique complexe, en particulier parce que l'espace de paramètres que l'on souhaite explorer est grand, et qu'il n'est pas possible de faire des expériences réelles permettant d'explorer cet espace. Ainsi, on souhaite utiliser un simulateur pour évaluer les performances d'une application donnée pour un ensemble de paramètres.

La principale difficulté rencontrée lors du développement de tels simulateurs provient de la complexité de la pile logicielle utilisée sur les grappes de calcul que l'on souhaite simuler : les applications scientifiques sont souvent programmées à un haut niveau d'abstraction et leurs communications traversent plusieurs couches logicielles avant d'être exécutées par le matériel. Il faut donc choisir laquelle de ces couches logicielle intercepter en simulation, afin de garantir une bonne précision tout en conservant des performances acceptables.

Notre contribution prend la forme d'un simulateur du réseau BXI, qui propose un modèle simplifié du matériel, tout en permettant l'exécution d'applications complètes sur plusieurs machines simulées. Ce simulateur permet de prendre en compte les spécificités de toutes les couches logicielles intermédiaires entre le NIC et l'application simulée, moyennant des modifications mineures dans celles-ci. Nous validons ce modèle expérimentalement en comparant l'exécution de benchmarks sur une grappe de calcul équipée de matériel BXI et la simulation de ces benchmarks dans notre simulateur. Ce modèle bas niveau ayant un coût en performance non négligeable, nous présentons également une méthodologie pour alterner dynamiquement entre plusieurs modèles de précision différente au cours de l'exécution d'une simulation, afin de permettre à l'utilisateur de paramétrer au mieux quelles parties de l'application doivent être simulées avec le plus de précision.

# **S** Abstract

In order to obtain the best possible performance in supercomputers, it is necessary to use interconnection networks of ever-increasing complexity. In order to provide such networks, Atos designs the BXI interconnect, which is composed of network controllers (NIC) and switches. Optimal configuration of this hardware is a complex task, in particular because the parameter space to explore is very large, and it is not practically possible to run real-world experiments to explore this parameter space. For this reason, we wish to use a simulator to evaluate the performance of a given application for a set of parameters.

The main difficulty that arises when developing such simulators comes from the complexity of the software stack that is used on the clusters that we wish to model: scientific applications are often programmed at a high level of abstraction, and their communications go through several layers of software before they are executed by the hardware. Therefore, it is important to choose which software layer to intercept in simulation, in order to get a good accuracy of the model while keeping acceptable performance of the simulation.

Our contribution is a simulator of the BXI interconnect, which provides a simplified model of the hardware, while allowing the execution of complete applications of several simulated machines. This simulator accounts for the properties of all layers of the software stack between the NIC and the simulated application, thanks to minor modifications in these software libraries. We validate this model experimentally by comparing the execution of benchmarks on a cluster equipped with BXI hardware and the simulation of these benchmarks in our simulator. Because our low-level model has a significant cost in terms of performance, we also present a methodology to switch dynamically between several models of different accuracy during the execution of a simulation, in order to allow users to tune as well as possible which parts of the application should be modeled with the best accuracy.

# **Solution** Remerciements

Bien qu'il me semble impossible de remercier toutes les personnes qui m'ont aidé dans la réalisation de cette thèse, et qui m'ont soutenu durant ces trois années, je tiens à mentionner le rôle important de quelques personnes sans qui ces travaux n'auraient pas pu exister.

En premier lieu, je souhaite remercier Matthieu MOY et Ludovic HENRIO, qui ont dirigé ma thèse au LIP, ansi que Grégoire PICHON, qui a encadré mes travaux chez Atos, pour leurs précieux conseils tout au long de cette thèse, leur patience face aux montagnes de courbes qui montent et qui descendent, ainsi que leur aide dans la relecture de ce manuscrit. Je remercie également toute l'équipe CASH du LIP: passer ces trois ans ensemble malgré la distance due au télétravail a été un plaisir, vous allez enfin arrêter d'entendre parler des fameuses cartes BXI. Merci également à toutes les personnes qui m'ont fourni une aide précieuse chez Atos, pour leur patience et leur sympathie, en particulier tous les membres de l'équipe BXI-LL, ansi que les équipes hardware et MPI, sans qui ce travail n'aurait pas été possible.

De même, merci à toute l'équipe de développement de SimGrid pour leur aide précieuse et leurs conseils avisés, en particulier Martin QUINSON, Arnaud LEGRAND, Arnaud GIERSCH, Augustin DEGOMME, Frédéric SUTER, Millian POQUET, Bruno DONASSOLO et Tom CORNEBIZE.

Je remercie également Isabelle Guerin-Lassous pour avoir accepté de participer au jury de soutenance, Marc Perache pour l'intérêt qu'il a porté à mon travail tout au long de cette thèse, Arnaud Legrand pour ses conseils lors des comités de suivi individuels, ainsi que Martin Quinson et Camille Coti pour avoir accepté d'endosser le rôle de rapporteur et rapporteuse de ce manuscrit.

Enfin, je tiens bien sûr à remercier ma famille, en particulier mes parents, ma soeur et mes grand-parents, ainsi que Célestine qui partage ma vie, pour leur soutien infaillible, y compris dans les moments les plus difficiles. Je remercie également mes amis du LIP et d'ailleurs, en particulier Benjamin sans qui cette thèse n'aurait probablement pas eu lieu, mais aussi Paul-Louis, Thomas, mes co-bureaux au LIP Amaury et Pauline, Thaïs, Nicolas, Hugo, Yannick et Gabriel.

Finally, I would like to thank my friends Fabio, Sev and Cerp for their continued support throughout the second half of this PhD, may we continue to complain about RNG for many years to come. Thanks to Webhead as well, it has been a pleasure working with you, and I hope it continues in the future.

# Sesumé détaillé

Pour obtenir les meilleures performances possibles dans les supercalculateurs, il est aujourd'hui nécessaire d'utiliser des réseaux d'interconnexion de plus en plus sophistiqués. C'est pour répondre à ce besoin qu'Atos produit le réseau BXI, composé de cartes réseau (NIC) et de commutateurs (switches). Le paramétrage optimal de ce matériel est une problématique complexe, en particulier parce que l'espace de paramètres que l'on souhaite explorer est grand, et qu'il n'est pas possible de faire des expériences réelles permettant d'explorer cet espace. Ainsi, on souhaite utiliser un simulateur pour évaluer les performances d'une application donnée pour un ensemble de paramètres.

La principale difficulté rencontrée lors du développement de tels simulateurs provient de la complexité de la pile logicielle utilisée sur les grappes de calcul que l'on souhaite simuler : les applications scientifiques sont souvent programmées à un haut niveau d'abstraction et leurs communications traversent plusieurs couches logicielles avant d'être exécutées par le matériel. Il faut donc choisir laquelle de ces couches logicielle intercepter en simulation, afin de garantir une bonne précision tout en conservant des performances acceptables.

Notre contribution prend la forme d'un simulateur du réseau BXI, qui propose un modèle simplifié du matériel, tout en permettant l'exécution d'applications complètes sur plusieurs machines simulées. Ce simulateur permet de prendre en compte les spécificités de toutes les couches logicielles intermédiaires entre le NIC et l'application simulée, moyennant des modifications mineures dans celles-ci. Nous validons ce modèle expérimentalement en comparant l'exécution de benchmarks sur une grappe de calcul équipée de matériel BXI et la simulation de ces benchmarks dans notre simulateur. Ce modèle bas niveau ayant un coût en performance non négligeable, nous présentons également une méthodologie pour alterner dynamiquement entre plusieurs modèles de précision différente au cours de l'exécution d'une simulation, afin de permettre à l'utilisateur de paramétrer au mieux quelles parties de l'application doivent être simulées avec le plus de précision.

### Chapitre 1

Ce chapitre introduit le contexte de nos travaux (décrit ci-dessus). Nous y présentons quelques informations sur le processus de développement qu'utilisent les équipes d'Atos pour créer le matériel BXI, qui sert de cas d'étude à nos travaux. Ce premier chapitre termine par une annonce nos contribution et du plan du document.

### Chapitre 2

Le deuxième chapitre précise le contexte de nos travaux en présentant le domaine du calcul haute performance. Y sont présentées l'architecture d'une grappe de calcul (sujet

Ben

d'étude de nos expériences) ainsi que les caractéristiques du matériel réseau développé par Atos, que nous cherchons à modéliser. En particulier, nous présentons l'API Portals, qui est implémentée de manière matérielle par l'interconnect BXI d'Atos. Le chapitre se termine par une présentation des programmes informatiques que nous tâcherons de simuler par la suite, afin d'expliquer leur intérêt dans le cadre de la validation de notre simulateur.

### **Chapitre 3**

Le troisième chapitre présente l'état de l'art existant dans le domaine de la simulation de systèmes HPC. Nous y présentons la principale difficulté auxquels tous les simulateurs font face : le compromis entre précision du modèle et performance de la simulation. Nous détaillons plus amplement les caractéristiques de quelques simulateurs qui se prêtent au type de travaux que nous entreprenons, en particulier SimGrid que nous avons choisi d'utiliser.

### **Chapitre 4**

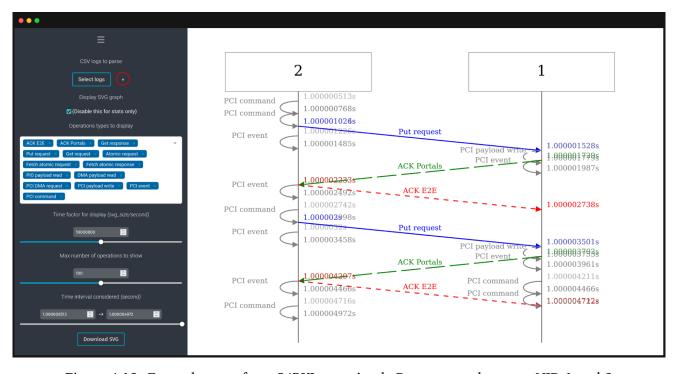

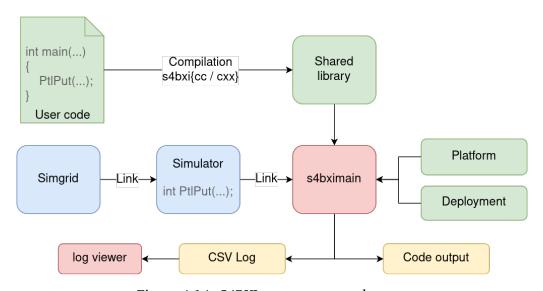

Le quatrième chapitre présente notre première contribution : un simulateur de l'API Portals, optimisé pour modéliser l'interconnect BXI d'Atos. Nous détaillons en particulier notre description de platforme, qui modélise les différents composants matériels présents dans une grappe de calcul réelle, ansi que notre implémentation de l'API Portals dans le monde simulé, en utilisant les briques de base offertes par SimGrid.

Nous présentons les outils qui ont été développés pour assiter l'utilisateur du simulateur, et nous terminons avec des expériences de validation, qui comparent nos résultats de simulations avec des exécutions de benchmarks sur une grappe de calcul réelle (équipée de matériel BXI).

### **Chapitre 5**

Le cinquième chapitre explique comment des bibliothèques logicielles abstraites peuvent être adaptées pour fonctionner au dessus de notre modèle bas niveau. Nous étudions en particulier l'API MPI, car c'est la plus couramment utilisée dans le domaine du calcul haute performance. Nous montrons que notre approche permet d'exécuter MPI en simulation avec très peu de modifications, ce qui nous permet de faire des simulations avec une pile logicielle beaucoup plus fidèle au fonctionnement réel par rapport aux modèles fluides pré-existant dans l'état de l'art.

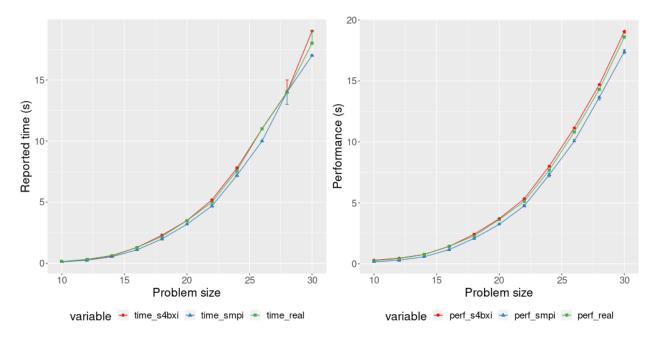

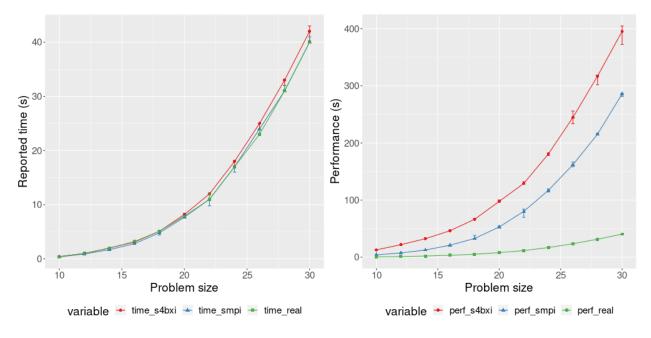

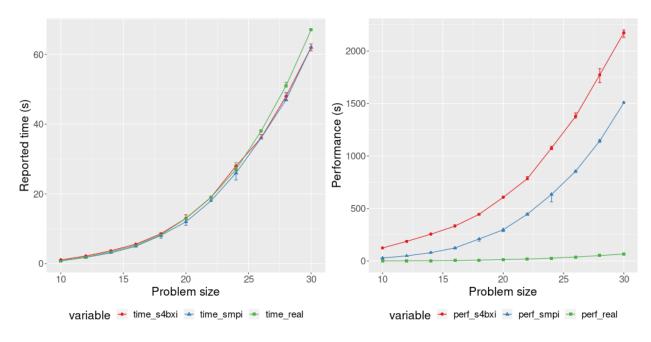

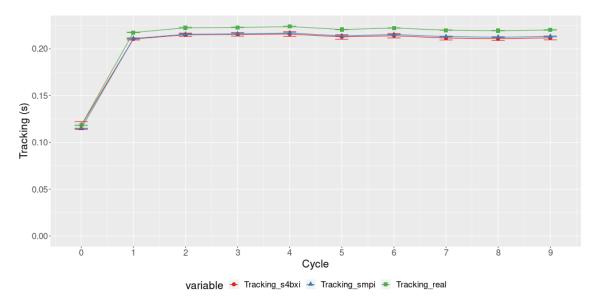

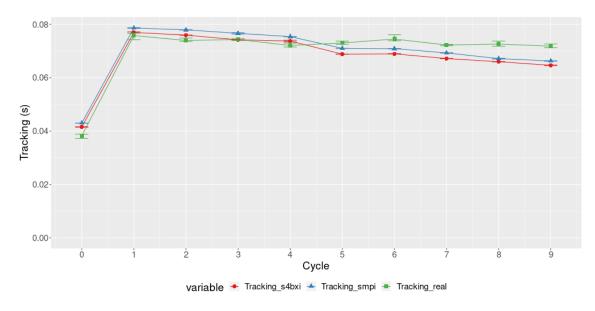

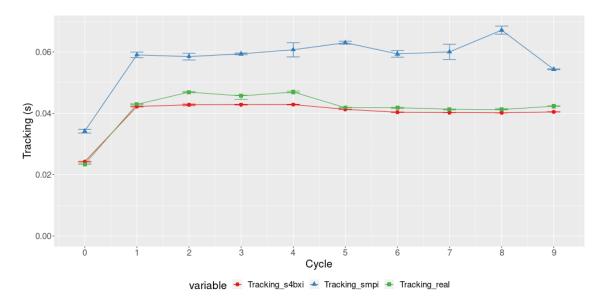

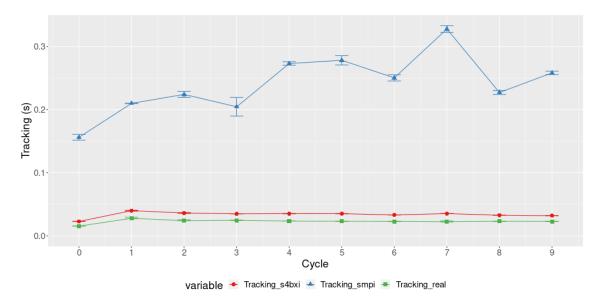

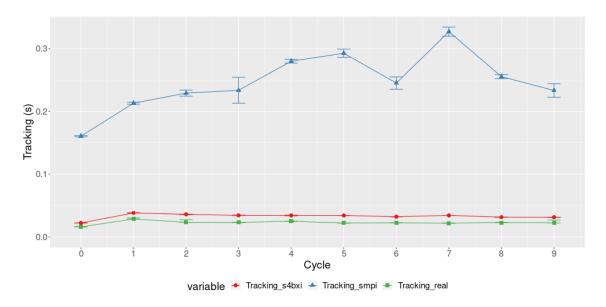

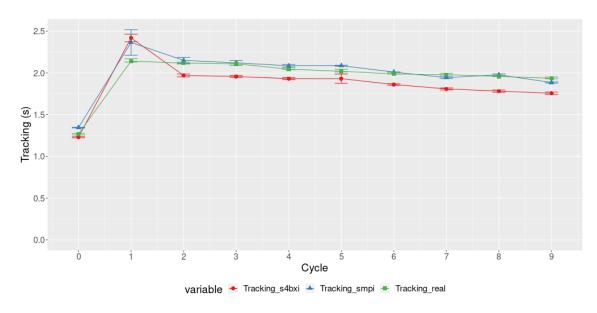

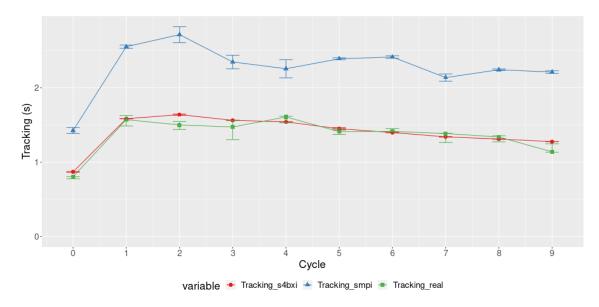

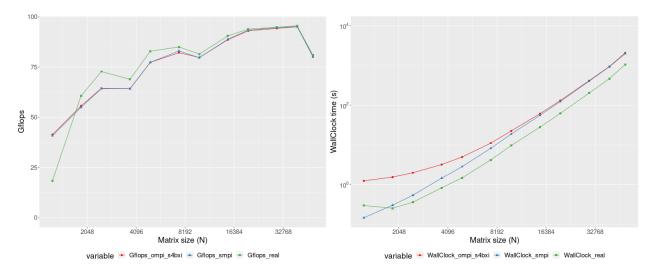

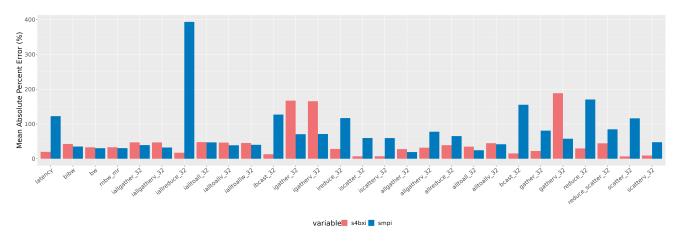

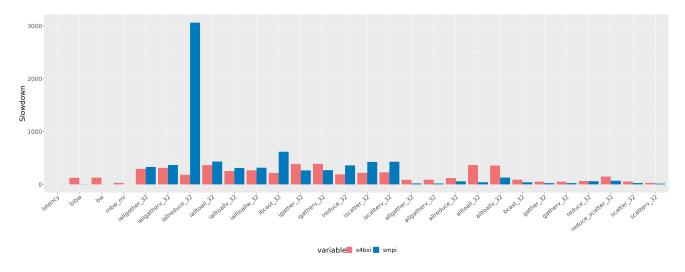

Nous présentons une validation expérimentales, utilisant les programmes décrit dans le Chapitre 2. Nous comparons nos résultat à SMPI, simulateur pré-existant le plus proche de notre modèle. Nous en concluons que les deux modèles ont des forces et faiblesses complémentaires : là où notre approche (basée sur notre simulateur, S4BXI) offre un modèle plus précis, SMPI offre un modèle plus rapide d'exécution.

Après avoir étudié MPI, nous présentons des travaux préliminaires sur la simulation de l'API OpenSHMEM. Nous détaillons comment adapter cette bibliothèque à notre simulateur, et présentons des résultats expérimentaux.

**100**

### Chapitre 6

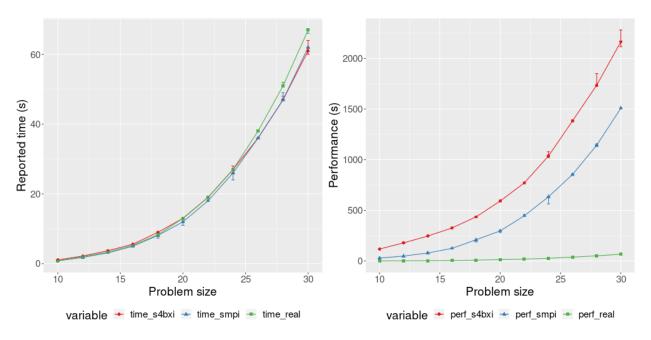

Ce chapitre présente une nouvelle contribution : en se basant sur les forces et les faiblesses des deux simulateurs que nous avons étudiés, S4BXI et SMPI, nous développons une méthodologie de simulation permettant de coupler les deux modèles au sein d'une même simulation. Ainsi, les utilisateurs de notre simulateurs peuvent changer de modèle réseau dynamiquement, durant l'exécution de la simulation.

Nous présentons des résultats expérimentaux utilisant cette approche, sur deux programmes simulés. Nous proposons une conclusion qui met en avant les forces et les faiblesses de cette méthodologie de simulation.

### Chapitre 7

Nous dédions un chapitre complet à la présentation des études futures qui pourraient être réalisées à partir de nos travaux. Nous présentons des exemples d'expériences sur lesquelles nous avons commencé à travailler, mais qui nécessiteraient plus de temps de travail. Nous détaillons en particulier une étude s'intéressant à la notion de contrôle de flux, dans le but de simplifer le processus de développement des prochaines générations de matériel BXI.

### Chapitre 8

Dans ce dernier chapitre, nous présentons la conclusion de nos travaux : nous résumons nos contributions principales, ainsi que les portes que nos travaux ouvrent pour des études futures.

À mon grand-père, qui n'aurait pas compris un mot de ce qui va suivre, mais qui aurait été très fier

W.

# **Sontents**

| Ré | ésum   | é                                         | iii |

|----|--------|-------------------------------------------|-----|

| Ał | ostrac | ct                                        | iv  |

| Re | emero  | ciements                                  | v   |

| Ré | ésum   | é détaillé                                | vii |

| 1  | Intr   | roduction                                 | 1   |

|    | 1.1    | HPC for simulation and simulation for HPC | 1   |

|    | 1.2    | Design process of a NIC for HPC at Atos   | 3   |

|    |        | Contributions                             | 6   |

|    | 1.4    | Structure of this thesis                  | 6   |

| 2  | Con    | text: High Performance Computing          | 9   |

|    | 2.1    | HPC clusters' architecture                | 9   |

|    |        | 2.1.1 General overview                    | 9   |

|    |        | 2.1.2 Networking hardware                 | 11  |

|    |        | 2.1.3 Networking Software Stack           | 12  |

|    | 2.2    | The Portals API                           | 14  |

|    |        | 2.2.1 Portals data structures             |     |

|    |        | 2.2.2 Communication primitives            |     |

|    |        | 2.2.3 Portals's implementation in BXI     | 17  |

|    | 2.3    | Benchmarks of interest                    | 18  |

|    |        | 2.3.1 Network benchmarks                  |     |

|    |        | 2.3.2 Realistic (proxy) applications      | 20  |

| 3  | Rela   | ated work around simulation               | 23  |

|    | 3.1    | Tradeoff between performance and accuracy | 23  |

|    | 3.2    | Use cases and input formats               |     |

|    | 3.3    | A few notable simulators                  |     |

|    |        | 3.3.1 Structural Simulation Toolkit       |     |

|    |        | 3.3.2 Shadow                              | 25  |

|    | 3.4    |                                           |     |

|    |        | 3.4.1 Architecture                        |     |

|    |        | 3.4.2 Usage                               |     |

|    |        | 3.4.3 Performance and isolation concerns  |     |

|    | 3.5    | High-level models                         | 31  |

|   | 3.6 | Multi-level modeling                                            | 32 |

|---|-----|-----------------------------------------------------------------|----|

| 4 |     | XI, a low-level Portals model                                   | 33 |

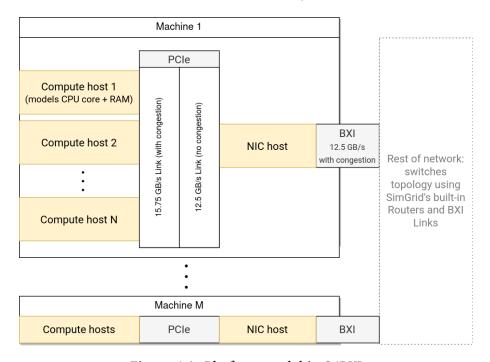

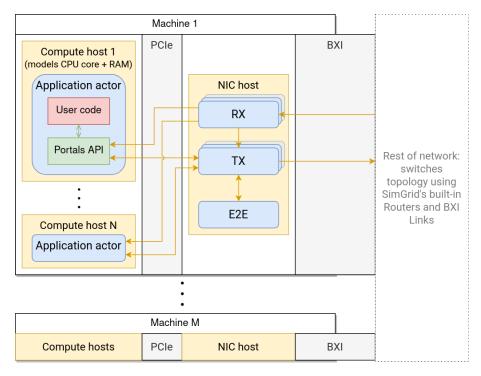

|   | 4.1 | Platform model                                                  | 33 |

|   | 4.2 | Actor placement                                                 | 35 |

|   |     | 4.2.1 On-NIC Actors                                             |    |

|   |     | 4.2.2 Actors on CPU cores                                       | 38 |

|   | 4.3 | Portals model                                                   |    |

|   |     | 4.3.1 Representation in S4BXI                                   |    |

|   |     | 4.3.2 Tuning for the BXI interconnect                           |    |

|   |     | 4.3.3 Streaming data from memory to memory across BXI           |    |

|   |     | 4.3.4 Performance options                                       |    |

|   | 4.4 |                                                                 |    |

|   | 4.5 |                                                                 |    |

|   | 1.0 | 4.5.1 Practical usage of S4BXI, and simulated process isolation |    |

|   |     | 4.5.2 Platform implementation in S4BXI                          |    |

|   |     | 4.5.3 Portals's implementation in C/C++                         |    |

|   |     | -                                                               |    |

|   |     | 4.5.4 Capturing function calls                                  |    |

|   | 1.0 | 4.5.5 Completeness                                              |    |

|   | 4.6 |                                                                 |    |

|   |     | 4.6.1 Custom made benchmarks                                    |    |

|   |     | 4.6.2 PtlPerf                                                   | 59 |

| 5 |     | ge with high-level APIs                                         | 65 |

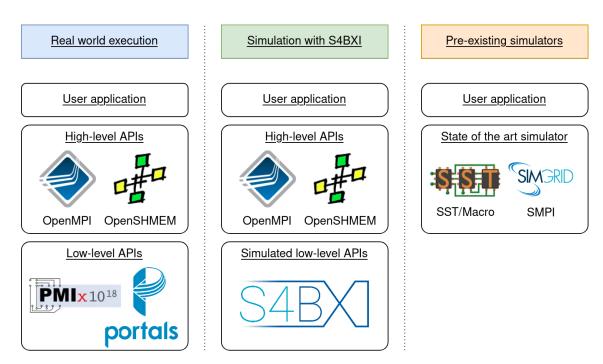

|   |     | HPC software stack overview                                     |    |

|   | 5.2 | Atos's version of OpenMPI                                       |    |

|   | 5.3 | Adapting OpenMPI for the simulated world                        | 68 |

|   |     | 5.3.1 Simulation of out-of-band communications without PMIx     | 68 |

|   |     | 5.3.2 Adapting OpenMPI's initialization for S4BXI               | 69 |

|   |     | 5.3.3 Shared memory support                                     | 70 |

|   |     | 5.3.4 Handling copies of MPI libraries in S4BXI                 |    |

|   |     | 5.3.5 A word on performance regarding polling                   | 72 |

|   | 5.4 | Compatibility with SMPI sampling                                | 74 |

|   |     | Experimental validation                                         |    |

|   |     | 5.5.1 OSU micro-benchmarks                                      |    |

|   |     | 5.5.2 LULESH                                                    |    |

|   |     | 5.5.3 Quicksilver                                               |    |

|   |     | 5.5.4 High-Performance Linpack (HPL)                            |    |

|   | 5.6 |                                                                 |    |

|   | 3.0 | 5.6.1 Running OpenSHMEM in S4BXI                                | 90 |

|   |     | 5.6.2 Experimental validation                                   |    |

|   | 5.7 |                                                                 |    |

|   | 5./ | Summary                                                         | 93 |

| 6 |     | ore flexible accuracy/performance tradeoff                      | 95 |

|   | 6.1 | Design choices                                                  | 95 |

|   |     | 6.1.1 Two network models over SimGrid                           |    |

|   |     | 6.1.2 Different ideas to share the network loads                |    |

|   | 6.2 |                                                                 |    |

|   | 6.3 | Redirecting MPI calls using S4BXI's middleware                  | 98 |

xiv rr Contents

|              | 6.4                 | Maintaining MPI's internal coherency | 100        |

|--------------|---------------------|--------------------------------------|------------|

|              | 6.5                 | Making model changes more lenient    | 102        |

|              | 6.6                 | Experimental results                 | 105        |

|              |                     | 6.6.1 OSU micro-benchmarks           |            |

|              |                     | 6.6.2 Quicksilver                    | 109        |

|              | 6.7                 | Concluding remarks                   | 114        |

| 7            | Ong                 | oing and future work                 | 115        |

|              | 7.1                 | Flow control in BXI                  | 115        |

|              | 7.2                 | Future work                          | 121        |

|              |                     |                                      |            |

| 8            | Con                 | clusion                              | 125        |

|              |                     | clusion raphy                        | 125<br>129 |

| Bi           | bliog               |                                      |            |

| Bi<br>A      | bliog<br>S4B        | raphy                                | 129        |

| Bi<br>A<br>B | bliog<br>S4B<br>Ope | raphy<br>XI class hierarchy          | 129<br>137 |

Contents xv

# Strapter 1

## Introduction

### 48 1.1 HPC for simulation and simulation for HPC

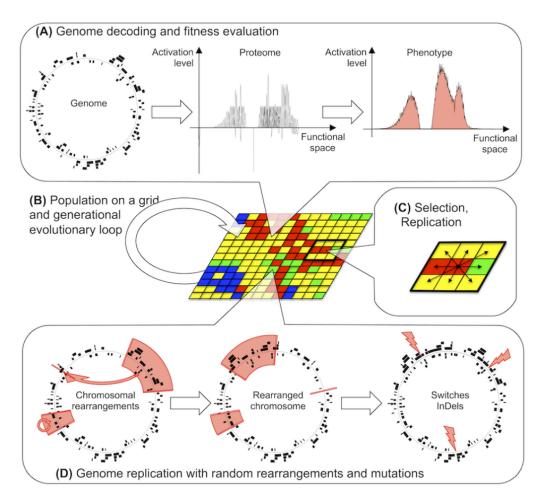

Nowadays, many scientific domains rely on simulation in order to better understand the world around us, or to design systems that are difficult to prototype and test in the real world. There are many examples of such models, as can be seen on Figure 1.1 which shows an application of Computational Fluid Dynamics to model the airflow around a BAE-HAWK plane, or on Figure 1.2, which illustrates the Aevol model, a digital genetics platform designed to study the evolutionary process [LPRCB18].

Figure 1.1: Fluid dynamics on a BAE-HAWK plane<sup>1</sup>

As scientific models get more and more accurate, they also become increasingly complex, and they require an increasing amount of computing power to run. As a result, most scientific domains today require the use of High Performance Computing (HPC): clusters of an ever-growing number of machines which work together towards the same goal. HPC is such a powerful tool that it is used in most research fields, but also most industries, with applications as varied as healthcare, weather forecast, geology, every vehicle's design, etc. An example of such computing cluster is displayed on Figure 1.3, where we can see the supercomputing facility of the European Centre for Medium-Range Weather Forecasts (ECMWF) in Bologna, which is made up of Atos BullSequana XH2000 clusters and is used to run a global Earth system model, in order to get weather reports as accurate as possible. Additionally, as artificial intelligence takes an increasing space in our lives, through a huge diversity of algorithms, the amount of data that we need to process is growing at a very high rate, and the computing power required to train algorithms increases proportionally.

<sup>&</sup>lt;sup>1</sup>Image from https://cfd2012.com/aircraft-design.html

Figure 1.2: The Aevol model. Image from [LPRCB18].

Figure 1.3: HPC facility at ECMWF, made up of four Atos BullSequana XH2000 clusters<sup>2</sup>

https://www.ecmwf.int/en/about/media-centre/focus/2022/fact-sheet-supercomputing-ecmwf

<sup>&</sup>lt;sup>2</sup>Image from

As clusters get larger and larger, interconnection networks that connect the machines together need to handle huge quantities of communications, with the highest performance possible, in order not to slow down the scientific applications running on the cluster. In this context, Atos develops its own interconnection network, the Bull eXascale Interconnect (BXI), which is used in some of the most powerful European supercomputers, such as Tera-1000-2 [TOP17] which was the most powerful supercomputer in Europe at the time of its installation.

Because of the growing complexity of the hardware that is used to power supercomputers (CPUs, accelerators, interconnection network, etc.), predicting the execution time of a scientific application on a given cluster is a difficult task, although it is important for several reasons: for example to dimension new clusters, or to tune the parameters of the software stack and of the hardware to optimize performance. Additionally, designing next-generation hardware is increasingly hard, as we constantly aim for better performance, therefore conducting studies in simulation is a good tool to facilitate this design process. This is where simulation can help, by providing a model of the cluster which can be used to estimate its performance in various scenarios, even hypothetical ones that cannot be reproduced with the hardware currently available. This typically happens in the context of the co-design of next-generation hardware.

It is important to note that, since the application being run is usually itself a physical simulation, the word "simulation" can be used in this context to refer to two different objects: the simulation of a supercomputer, which uses the cluster as the object of its study, and the simulation that might run inside the cluster, which models a completely different system (as presented previously). In the context of our work, our contribution is the design of a simulator of HPC clusters (with a focus on the simulation of BXI), but in order to validate our model we will also manipulate physics models (presented in Chapter 2), which we will run in a virtual cluster in the simulated world. In order to differentiate both types of simulators, in this document we will refer to physics models as "scientific applications" or "user applications", to avoid potential confusion with our model of BXI.

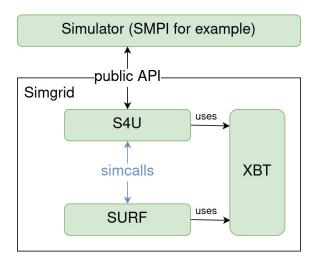

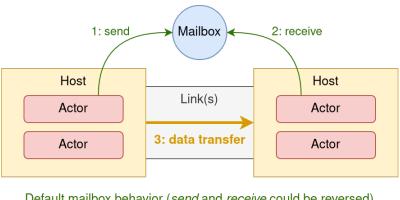

In the field of cluster simulation, many types of models are available, which are used to simulate various parts of a cluster with a high accuracy, or model the whole cluster, but with a more simplistic model. Our work is a collaboration between the "Laboratoire de l'Informatique du Parallélisme" (LIP) and Atos<sup>3</sup>. In this context, we focus on the communication aspect of supercomputers, and in particular on the BXI Interconnect made by Atos. Our model of this hardware is based on the SimGrid framework, which allows us to design a simulator modeling communications at message-level by leveraging SimGrid's actor-based flow-model.

In the next section, we will present how BXI is designed at Atos, using our hands-on experience with this interconnect, the knowledge that we gained from working inside the low-level software team of this company, and our interactions with the hardware and high-level software teams. In particular, we will present the existing uses of simulation in this context, and illustrate the potential benefits of a more abstract simulator.

### → 1.2 Design process of a NIC for HPC at Atos

The process of creating an Application Specific Integrated Circuit (ASIC), such as a Network Interface Controller (NIC) in the context of High Performance Computing, is very

<sup>&</sup>lt;sup>3</sup>This PhD is funded by a "Convention industrielle de formation par la recherche" (Cifre)

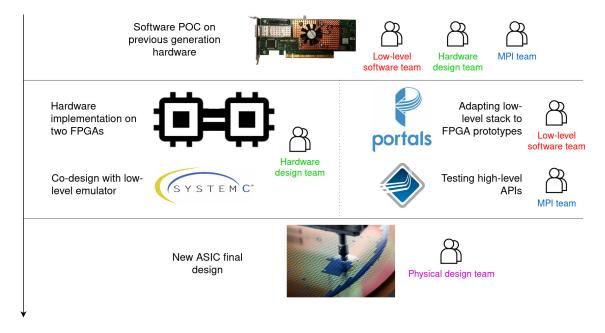

costly: the full design and manufacturing process can cost millions of Euros. Every step of the process is complex, very time-consuming and expensive, from the design by an R&D team, to the prototyping, and then the actual production of the finished product. This is why this creation process (depicted in Figure 1.4) follows many steps that aim to facilitate and speed up the design, in order for manufacturers to remain competitive.

Figure 1.4: Design process of the BXI NIC at Atos

There are mainly four teams that are involved in the process: the hardware design is made by two teams, which are responsible for the prototyping on Field-Programmable Gate Arrays (FPGA) and the firmware development on one side, and the physical layout on the final ASIC on the other side. From the point of view of the software, there are also two different teams: one of them is specifically responsible for the tuning of Atos's version of the Message Passing Interface (MPI), since this high-level API is the most commonly used in the field of HPC, therefore its maintenance and optimization are very important. The second team, BXI-LL, is responsible for the lower-levels of the software stack, which involves developing the driver for BXI NICs, as well as the user-level library for Portals, which is the network API implemented by the NIC. This API offers connectionless, reliable point-to-point communications, and since it is entirely implemented in hardware by the NIC, the user-level software library is a very thing wrapper that mainly formats commands and sends them to the NIC. Additionally, the BXI-LL team is responsible for the other high-level services that are supported by BXI, such as the Lustre distributed Filesystem, OpenSHMEM, etc.

As we can see on Figure 1.4, the design process of BXI NICs starts with an exploration of the possible features that could be implemented, either by emulating these features on hardware that is as similar as possible to the currently developed ASIC (for example by using old generation hardware to design the new generation), or using a high-level simulator to get a rough estimate of the functionality and performance of each option. Once this step is done and the least promising features have been abandoned, the remaining ones can be implemented in a first prototype. Because making a physical prototype would be extremely time-consuming and costly, this step is always done either on reconfigurable

hardware such as an FPGA, or in a very low-level simulation framework. Sometimes both are made, for example at Atos there is a SystemC model of the BXI switch, as well as an FPGA implementation. Additionally, in order to develop the driver and user library for the first generation of BXI, an emulator of the NIC was made using QEMU [Bel05], but it was not maintained for the later generation of BXI hardware. When the first prototype of the hardware is complete, software developers can start using it to design the driver that is going to power the hardware. Hardware and software developers then iterate over the prototype to improve both the circuit and the software stack, until both are ready for production use, which is assessed with manual tests, as well as the execution of a test suite designed by the BXI-LL team in order to test most use-cases of the hardware that need to be supported. At this point, the design on FPGA is passed to a dedicated team responsible for the layout of the different circuits on the final chip. Finally, the ASIC is ready to be manufactured at scale.

The issue with this workflow is that a prototype on an FPGA can be around two orders of magnitude slower than the final product, especially for large circuits where "artificial" bottlenecks can exist on FPGA but not on the final product: for example the BXI NIC made by Atos does not fit on a single FPGA, and therefore it is distributed across two FPGAs connected together. Even with this design, the NIC must be simplified to fit on two FPGAs: only two List Matching Engines (LMEs) can be implemented instead of four on the real ASIC for example. These engines are Application-Specific Instruction set Processors (ASIP), which implement most of the processing of incoming messages, with instructions optimized to sustain a message rate as high as possible (more details about the process of receiving messages will be presented in Section 4.2.1), therefore having only two on the FPGA platform instead of four on the final ASIC is a change that has a significant impact on the behavior of the NIC. With prototypes this slow, it is also impossible to generate enough traffic to cause meaningful congestion on the network, which is problematic because congestion is an important phenomenon to study, as it impacts greatly the performance of networks with real ASICs. Low-level simulators are even slower than FPGA prototypes, with speeds that are often several orders of magnitude slower than the final product. This means that during this development process, software teams can only test their code on very small scale tests (usually involving two machines at most in the case of NIC development). This is a problem because it makes it very difficult to evaluate the performance of the new hardware on a realistic application, which can exhibit unexpected behavior and performance because of the complex interaction between all the components of a modern cluster. For example, at a small scale an application might be CPU-bound, but at a larger scale communications might become more important and stress the memory, which could become the bottleneck since it is a shared resource between the CPUs and NICs. This problem becomes even more complex if a storage system or an accelerator uses the memory at the same time, or if the data that needs to be sent on the network is on the storage. All of these scenarios create interdependencies between the different resources, and their impact on performance at different scales can be unexpected.

This is why it would be beneficial for the different development teams to have a model of the new hardware at an intermediate level: more accurate than the initial rough approximations, but faster than low-level emulators, in order to study more realistic workloads. The hardware and low-level software team at Atos could use it to perform studies on specific properties of the hardware, for example evaluating the impact of different protocol design choices. The teams responsible for the development of Atos's version of MPI could use it for higher-level studies, such as tuning the algorithms used by MPI to perform

complex operations between many machines, or testing their developments. Finally, Atos's clients could use our simulator to evaluate the performance of their applications, and tune the configuration of their code before performing real-world executions. In particular, the main client of the BXI Interconnect, the "Commissariat à l'Énergie Atomique et aux Énergies Alternatives" (CEA) showed interest in our work, and could be a potential user of our simulator.

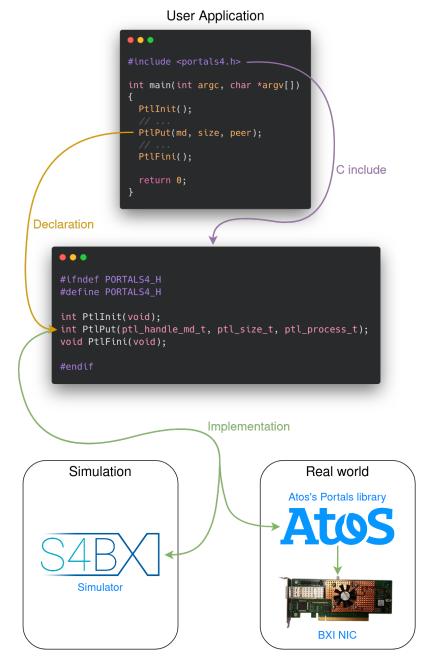

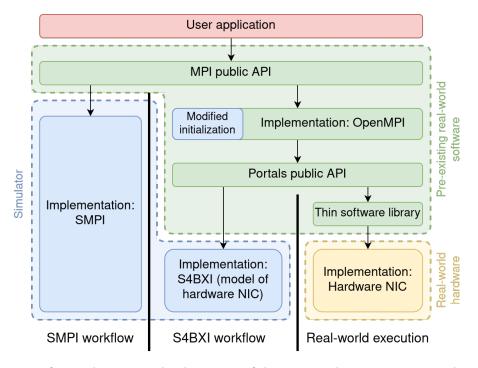

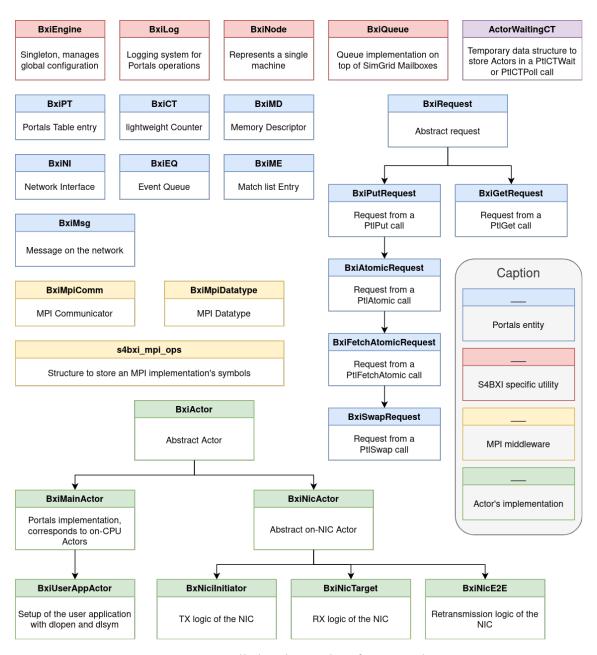

### **3** 1.3 Contributions

In our work, we design a simulator of HPC clusters, that is focused on the simulation of the BXI interconnect made by Atos. As BXI NICs implement the Portals API in hardware, we propose an implementation of this API in simulation. To this end, we rely on the SimGrid framework, which provides a flow-model of communication, and allows us to implement a Discrete Event Simulator (DES) using cooperative Actors. Even though flow-models are typically used to simulate communication at message level, we use a novel approach that models transfer at a lower level of granularity than most state-of-the art simulators. This design choice allows us to create a more accurate model of the hardware, without modeling each packet individually. To the best of our knowledge, this is the first time that a model of Portals has been made publicly available. We validate our model, using low-level experiments which rely on the Portals API.

We show that our simulation method is versatile, by running high-level network APIs on top of our low-level model. In this context, we study in detail the execution of Atos's implementation of MPI in our simulator, and we also show preliminary work with OpenSHMEM. To validate our model in this context, and to compare it with the closest state-of-the-art MPI simulator, SMPI, we run unmodified scientific applications that are commonly used to assess the performance of HPC clusters. These experiments confirm our expectations, as we observe that our simulation method is more accurate than SMPI, but also slower, as our model is more detailed. Therefore, we explore a new method to tune the ratio between performance and accuracy of our simulation method, by combining our network model and SMPI's, and enabling users to switch between them at runtime.

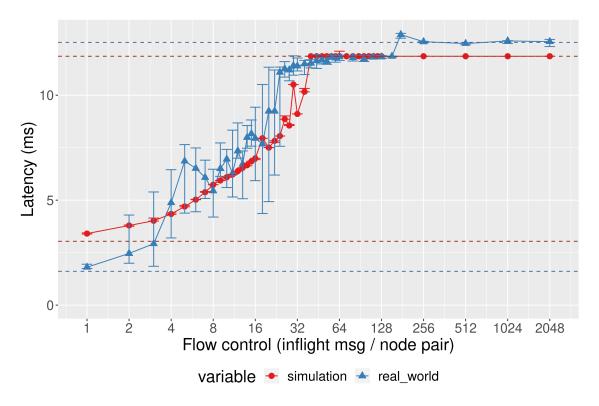

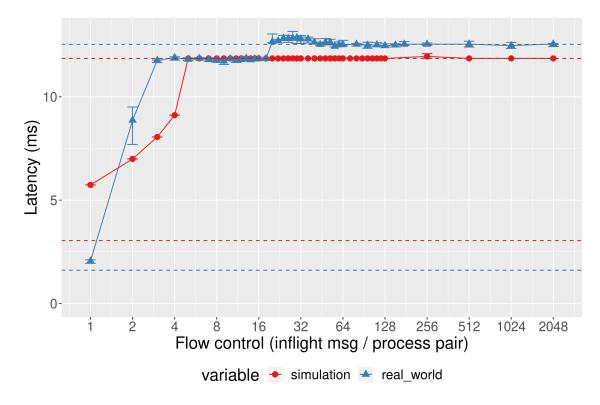

We conduct a study in order to assess the usefulness of potential evolutions of BXI NICs, by implementing flow-control mechanisms in simulation and testing this feature in different scenarios. This study shows the versatility of our simulator, as it demonstrates how low-level features of the hardware can be evaluated using high-level benchmarks, and we present a few other studies which could be conducted using a similar methodology (but which are left as future work).

### 48 1.4 Structure of this thesis

Our contributions are organized in seven chapters: Chapter 2 gives context regarding the field of HPC, by presenting the architecture of a typical HPC cluster and the most significant interconnection networks. It also details properties of the Portals API which will be important for the rest of our work, and describes a few scientific applications which will be used in our experiments.

Chapter 3 presents pre-existing simulators of HPC clusters, with a focus on SimGrid in order to illustrate the most important features which we leverage in our simulator.

Chapter 4 then focuses on our low-level model, by explaining how Portals is implemented in simulation, and which properties of the hardware are modeled by our approach.

It also shows validation results by relying on point-to-point benchmarks of Portals. Even though this work was published in [EMHP20], in this thesis we also present several features of our simulator which were added after the initial publication.

Chapter 5 explains how this model can be used to run high-level APIs, and in particular MPI. To this end, it details the modifications that need to be performed on the real-world implementations of MPI and OpenSHMEM in use at Atos, in order to make them compatible with our simulator. Part of this work was published in [EMHP21], but significant work has been added since: in particular, this publication does not mention our study on OpenSHMEM, and our benchmarks are now more complete.

Chapter 6 shows how we can combine two network models, and allow users to switch between them at runtime.

Chapter 7 discusses some ideas that are more experimental, in particular it details our study on flow-control in BXI (a very early version of this work was published in [EMHP21]), and it lists ideas that are left as future work.

Finally, Chapter 8 concludes this document by summarizing our work.

# Suppose Chapter 2

# **Context: High Performance Computing**

This chapter presents the context of our work. We will start with an overview of the architecture of a modern HPC cluster, and then showcase several benchmarks commonly used in HPC, which we will refer to later in this thesis (in the context of the validation of our simulator).

### **3.1** HPC clusters' architecture

Our work focuses on the network aspect of High Performance Computing. We will start with some context regarding HPC clusters, and then focus on the challenges that interconnection network face, both at the hardware and software level.

### → 2.1.1 General overview

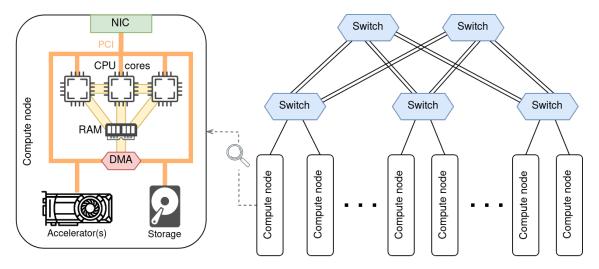

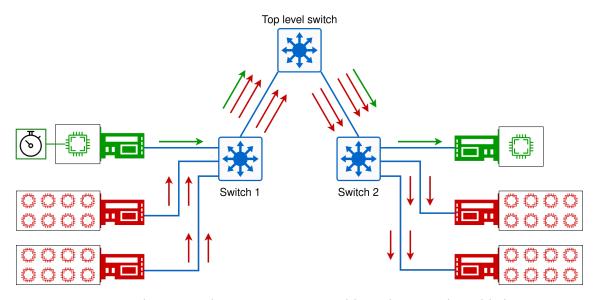

Because of the physical limitations that CPUs face, High Performance Computing (HPC) clusters use very specific hardware to get the most computing power possible from each machine that composes the cluster, and they also have an increasing number of machines connected together. This means that a typical machine (referred to as "node" in this document) is usually composed not only of one or more CPUs, but also one or more Network Interface Controller (NIC) and possibly one or more accelerator for fast parallel computation. These nodes are interconnected using switches of low-latency and usually high radix (i.e. a large number of ports allows connecting many nodes or other switches), which enables various topologies to be used. For example Figure 2.1 depicts a simple fattree, with wider links (higher bandwidth) closer to the "root" of the tree. On this example, we can see that the distance between two nodes is variable: two machines connected to the same switch will be able to communicate by traversing only two cables and one switch, whereas nodes on opposite sides of the tree will need to traverse four links and three switches to communicate, increasing the latency of network transfers.

While the diversity of hardware and increasing number of nodes makes clusters more performant, it also makes it more difficult to predict the performance of a cluster executing a given application, because of complex interactions between each type of hardware on each node. A second side effect is that clusters become increasingly more costly to build and run, which makes real-world experiments very costly. The increase of the number of nodes also makes the topology of the cluster more and more important: routers and cables

Figure 2.1: Simplified cluster representation, with a zoom on a compute node

are an expensive part of the cluster, but it is crucial that they have a good performance, so connecting all this hardware efficiently is very important. On Figure 2.1 we can see that while nodes are usually very similar to each other (a typical cluster will have many identical compute nodes, and a few service nodes for login, storage, management, etc.), the allocation of tasks on the cluster still matters, because of communications: nodes that are on different switches will have to go through more links and switches in order to exchange data, whereas nodes on the same switch will benefit from a very low latency. We can also see that messages can take several paths through the network when going from one node to another, which makes efficient routing important.

There has been many studies in the field of interconnection networks and routing algorithms, from which many topologies have emerged. To cite only the most commonly used, the Flattened Butterfly [KDA07] focuses on cost-efficiency, by relying on path diversity, which shows the best result when the routing algorithm used leverages adaptive routing, which means that switches can decide which path to choose on a message-per-message or packet-per-packet basis, instead of having a strict static route for each source-destination pair (which improves the load-balancing abilities of the network). Dragonfly [KDSA08] networks operate on the same idea, but they use groups of switches to emulate a "virtual router" of even higher radix than the underlying switches, which further reduces the cost of building the network, while still showing good performance. Torus [ASS09] topologies are more original since they do not use a traditional architecture with NICs on compute nodes and switches to connect them together: instead every node has an "interconnect controller", which acts both as a NIC (with several "communication engines" to communicate with CPUs) and a small switch (with a dozen of ports typically). This allows nodes to be connected in small groups, and groups to be connected together along a variable number of dimension (up to 6D for the Tofu interconnect for example). Finally, the most common topology is probably the Fat-Tree [Lei85], which has been extensively studied, in order to improve routing [GGG<sup>+</sup>07], make accurate simulations [LHSJ15], etc. It relies on a hierarchy of switches, with compute nodes connected at the lowest level, and cables of increasing bandwidth as we get closer to the root of the tree, as depicted earlier in Figure 2.1. Several routing algorithms have been proposed on this topology, which rely on either static or adaptive routing [GGG<sup>+</sup>07], and which try to balance the load as well as possible between the different paths that are available in the tree. The most common

is D-Mod-K [Zah10] but others exist, such as node-type-based load-balancing [GQG18] which was proposed by Atos.

While our work could theoretically be used to study different topologies and compare their performance, it will not be discussed in detail in this thesis because the interconnect that we work on, BXI, is mostly used with Fat-Trees in production, therefore all our experiments will use this topology.

### - 2.1.2 Networking hardware

In the world of High Performance Computing, there are several competitors when it comes to production interconnection networks: the most notable are Cray (acquired by HPE during this PhD), Mellanox (acquired by Nvidia during this PhD), Fujitsu and Atos. Another noteworthy interconnection network is OmniPath: while it has first been discontinued by Intel, it has since been bought by Cornelis Networks, and there are several interesting studies on its performance and modeling [RGI17].

Cray's interconnects support a wide range of topologies: from Dragonfly network in their latest Slingshot interconnect, to 3D-Torus in the Seastar interconnect [BPU05]. Torus networks have been shown to work in higher dimensions, for example in 6D with the Tofu interconnect [ASS09] made by Fujistu, which is used in the Fugaku supercomputer (number two on the Top500 list as of the writing of this PhD). While early versions of Cray's interconnect were known to use Portals 3 as their lower-level network API, Slingshot is based on the Ethernet protocol [DDM+20]. On older generations of interconnect (as the Gemini and Aries which are still used in several clusters) the lowest software layer that is exposed to user code is composed of two APIs: uGNI and DMAPP [Cra10]. Cray's NICs typically support bandwidths up to 200Gbits/s.

Mellanox's interconnects are the most popular option for new clusters. They implement the standard Infiniband architecture [Pfi01], which is supported by most (if not all) higher-level APIs. They also feature a variety of hardware of different performance and price, such as the EDR and HDR series, which explains their popularity for clusters of all sizes. At the lowest level, users call the IB-verbs interface which is used to communicate with the NIC. High-end NICs from Mellanox typically support bandwidths up to 200GBits/s, with the upcoming generation expected to support 400Gbits/s.

Atos's interconnect, BXI, will be our case study for this PhD. It implements in hardware the Portals 4 network API, and is used in some of the fastest European supercomputers. It is one of the youngest interconnect of the market, with NICs supporting bandwidths up to 100Gbits/s, but it has showed very good results so far, equipping supercomputers with a very good rank in the Top500 list: Tera-1000-2 was at the 14<sup>th</sup> place worldwide and n°1 in Europe at the time of its installation [TOP17], and currently Exa1-HF holds the 20<sup>th</sup> place worldwide [TOP21] (it was also 14<sup>th</sup> at the time of its installation in 2021).

All these interconnects share a few similarities: their main goal is to offload as much network processing from the CPU as possible. This is made possible using a few properties that differ from traditional networking hardware: first, OS-bypass allows user code to send commands to a NIC without any system call, which speeds up communications significantly. Most NICs also provide zero-copy processing, which implies that incoming messages can be processed fast enough so that the incoming data is routed to the correct location in memory without being copied in intermediate buffers. This is made possible either by pinning memory pages used for network communications (as Mellanox's hardware does), or by having a full Virtual-to-Physical (V2P) circuit on the NIC (as does Atos's BXI hardware).

While the simulation of other interconnects and network APIs have been studied in depth, for example the congestion on Infiniband networks by [Vie10][GR12], Intel OmniPath with OpaSim [CFAS18], or Cray's interconnect [MCRC17], very few studies have been conducted on BXI, and the existing ones focus on very specific problems, such as the update of routing tables when the topology changes [VQ16]. In this thesis we will propose a model for Portals 4 and tune the simulator for accurate simulations of the BXI interconnect.

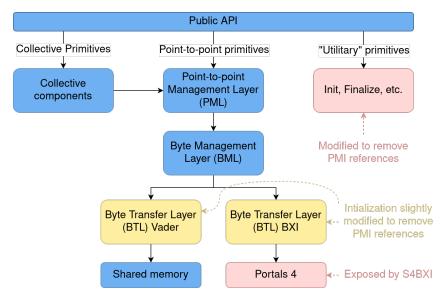

### → 2.1.3 Networking Software Stack

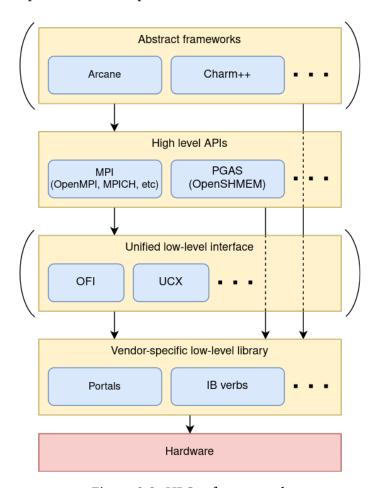

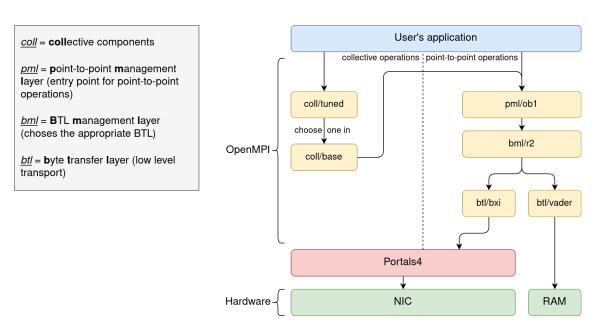

While the typical software stack for HPC communications is very different from the traditional OSI layers, it features similar levels of abstraction (depicted on Figure 2.2). We will start by giving a global overview of these layers, before presenting Portals in more details in the next section, since it is the lowest-level software layer used at Atos, and it will be the most important from the point of view of our simulator.

Figure 2.2: HPC software stack

At the lowest level, there is usually a very thin software library (potentially coupled with a kernel module), that directly interacts with the hardware, and exposes a few primitives with a very low level of abstraction to user code. It usually only performs point-to-point operations between two machines, and does not have any notion of collective operations involving several machines. For Infiniband this layer is called IB-verbs, and for Atos's

BXI interconnect it is the Portals 4 API directly, as it is fully implemented by the NIC in hardware. It is this Portals 4 layer that our simulator will model, as it will provide a model of the behavior of the NIC.

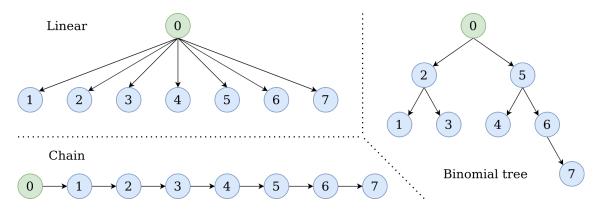

Above this layer, high-level APIs provide more abstract features that allow programmers to write efficient code, focusing on the algorithmic aspects and abstracting away the implementation details of communications. In this category, several programming models exist: for example Partitioned global address space (PGAS), with implementations such as OpenSHMEM [CCP $^+$ 10], allow user code to have a transparent representation of memory that is distributed on several machines. The most popular of these programming models is without a doubt the Message Passing Interface (MPI) [GWS06], which offers many ways of communicating: onesided, where a target machine exposes memory regions that other machines can query; regular point-to-point operations where both machines are actively involved (using send and receive primitives); and finally collective operations which provide abstract communication primitives such as all-to-all pattern, gather (N to 1 communication), scatter (1 to N), and even simple data processing with reduce, allreduce, etc. primitives. These collective operations usually have several implementations, which can be chosen dynamically depending on the message sizes and the number of machines involved in the operation. There are many MPI implementations, such as OpenMPI, MPICH, IntelMPI, etc. We will study OpenMPI in particular, as it is the MPI implementation that is officially supported by our case study interconnect, BXI. It is worth noting that our version of OpenMPI is a fork optimized by Atos for BXI, which we will explain in more detail in Chapter 5. These high-level APIs are sometimes criticized for their cost in terms of performance, in particular MPI [RAO+17], but their compromise between ease of use and performance makes them the standard to write HPC applications. Some projects even try to replicate this type of programming model in hardware, as [MdFLBH19] does on Field Programmable Gate Arrays (FPGAs).

These two layers are the most important and will usually exist in any HPC software stack, but there can also be additional ones: in particular some APIs try to provide a unified interface between the low-level transport and the high-level abstract API. The goal of this added layer is to limit the number of implementations that need to be made in high-level APIs to accommodate for any possible low-level transport. This is similar to the intermediate representation compilers use, which allows them to have only N frontends and M backends to be able to compile N languages into M machine codes, instead of having  $N \times M$  complete toolchains. These interfaces include the Open Fabric Interface (OFI) [GHS<sup>+</sup>15], of which Atos made an implementation built with Portals (in order to support BXI), as well as Unified Communication X (UCX) [SVL<sup>+</sup>15] or Nemesis [PGB11] for example.

Finally, while high-level APIs are already more user-friendly than low-level transports, they are still very general purpose and offer much control, which is why some frameworks can be used on top of them for even more abstraction. They can be domain-specific, as Arcane [GL09] for example, which is a tool made by the CEA to build physics simulators on top of MPI. Some libraries like SkePU [EK10] provide complete data-processing algorithms on distributed data, for example MapReduce, Stencils, etc. Some frameworks expose a unified API to execute algorithms on heterogeneous architectures (for example by exploiting local parallelism with OpenMP¹, inter-machine parallelism with MPI, etc.) like StarPU [ATNW11]. Some approaches even go as far as designing a full programming language for parallel processing, such as Chapel [PBCP+21], which implements a PGAS model

<sup>&</sup>lt;sup>1</sup>OpenMP is an API for parallel processing across CPU cores, which relies on compiler directives and a library

and uses low-level transports directly, or Charm++ [KK93], which provides automated load balancing and supports MPI as its transport mechanism.

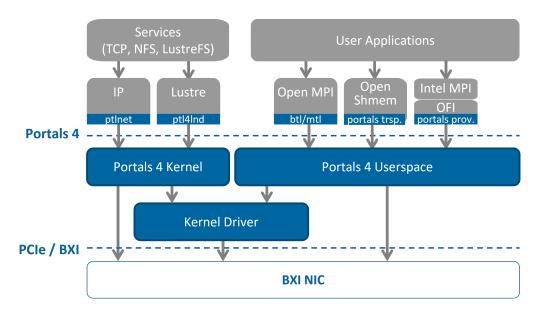

Figure 2.3: Atos's software stack on top of BXI NICs

The software stack used at Atos, which is going to serve as a case study for this thesis, is depicted on Figure 2.3. It is based on Portals, which we will describe in more detail in the next section, and supports a wide range of higher level APIs and services: it can emulate the Ethernet protocol using a layer called Ptlnet, supports the Lustre distributed Filesystem, provides different APIs for fast computation such as OpenMPI, OpenSHMEM, and IntelMPI (on top of OFI), etc. In this thesis we will study in detail OpenMPI in particular, and we will discuss OpenSHMEM support.

### **№ 2.2** The Portals API

Portals is a standard HPC API specified by Sandia National Laboratories [BSP<sup>+</sup>22]. It has been used in supercomputers for decades, with a few success stories like the ASCI Red supercomputer [MH98], which was the first to break the Teraflop barrier in 1996 using an early version of Portals. Since then Portals has been used mainly by Cray, and nowadays its main implementation is in the BXI interconnect made by Atos. This API provides connectionless, reliable communications using Remote Direct Memory Accesses (RDMA). While many details about the underlying protocol are left to the implementation, Portals is designed with OS-bypass in mind, and it should enable a "natural" implementation of MPI two-sided primitives, as well as PGAS one-sided operations.

#### → 2.2.1 Portals data structures

Portals features several data structures to interact with the hardware, which are defined in the Portals's specification [BSP<sup>+</sup>22]. This section presents the most important ones in the context of our work.

### General purpose structures

**Network Interfaces (NI)** act as an "entry" point, which represents the interface with the hardware. In Portals the addressing is analogue to IP addressing, since each physical NIC has a **Node Identifier (NID)**, which is the equivalent of IP addresses (although it is a simple number instead of a full address), and each NI (which usually corresponds to a single application process) has a unique **Process Identifier (PID)**. In those NIs, one or more **Portal Table (PT)** stores the data structures that will be used for the reception of messages. The pair  $\{PID; PT\}$  is similar to ports in an IP-based stack.

### Reception data structure

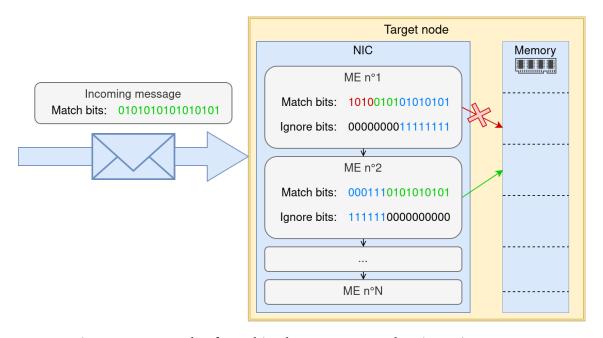

Matching Entries (ME) are used to configure the reception of incoming messages. A matching entry stores the address and length of the memory space where incoming messages' data should be written, as well as match bits and ignore bits. Match bits are a set of 64 bits which allows an efficient routing of data at the receiver side: when an initiator sends a request, it includes match bits in the message, and the target uses these bits to identify which ME should be used to process the request, by testing each ME against the incoming message using the following criterion:

$((incoming\_bits \land match\_bits) \& \sim ignore\_bits) == 0$

Figure 2.4: Example of matching between MEs and an incoming request

The first ME to match the incoming request is then used to determine on which memory region the requested operation needs to be performed. An example is shown on Figure 2.4, where we can see that nodes can have several MEs, which map to different locations in memory. To determine which ME needs to be used when processing an incoming request, Portals loops through the available MEs, and looks at match bits, using the opposite of the ignore bits as a mask (so the only match bits that are relevant are the positions where there is a 0 in the ignore bits). If those bits are the same as in the incoming message, the

ME is used to process the message (in order to determine the memory location where the incoming payload should be written). In the example, the first ME does not match, because the first bits are not ignored and they are different from the first bits of the incoming message, whereas the second ME matches because even though the first bits are different, they are ignored, and all the ending bits are identical to the bits of the incoming message. Therefore, the payload from the incoming message is stored in the memory location referenced by ME  $\rm n^{\circ}2$ .

MEs feature a variety of options that affect their behavior: they can have one or several uses, as well as locally manage the offset at which messages are written after each operation (by default this offset is specified on the sender side), etc. Portals also features more simple **List Entries (LE)**, which function exactly as MEs, but do not use match bits or ignore bits, which means that every incoming message will match the first LE posted in the Portal Table.

#### Transmission data structures

The data structure for transmission is more simple than the structures for reception: **Memory Descriptors (MD)** are simply used to represent the start and length of the memory zone that needs to be sent on the network. They also feature a few options, but which do not change drastically their behavior: these options mostly impact which events need to be emitted or not.

### **Event systems**

Portals feature two distinct event systems, which allow users to be notified of the activity on the network by attaching data structures to a PT, an MD or an ME.

The first, more complete system involves **Event Queues (EQ)**, which record full events with detailed information on the corresponding operation, such as the type of event, an error code, and a variable number of fields depending on the type of the event (for example the NID of the remote peer who caused the event, or the amount of data that was impacted, etc.). EQs can be associated with PTs and MDs.

The second system is more lightweight: instead of EQs, it uses **Counting Events (CT)**, which do not record any information about the operations that is in progress. Instead, each CT features two counters that track successful operations and failed operations. CTs can either count by incrementing by one each time, or incrementing by the number of bytes that was manipulated in the corresponding operation (based on a flag at their creation). CTs can be associated with MEs and MDs.

Both systems can be queried through a variety of function, which can search for events (or a certain value in CTs) in a way that is either asynchronous or blocking, while looking at either one or several EQ/CT.

### **2.2.2** Communication primitives

Portals features several operation types to exchange and manipulate data. All these operations are strictly point-to-point, as Portals does not have a concept of collective operation.

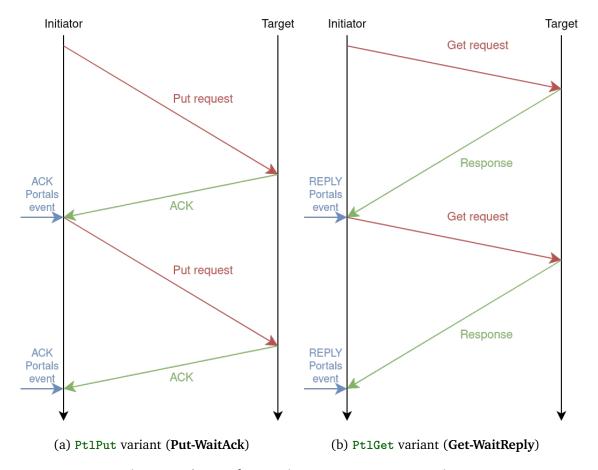

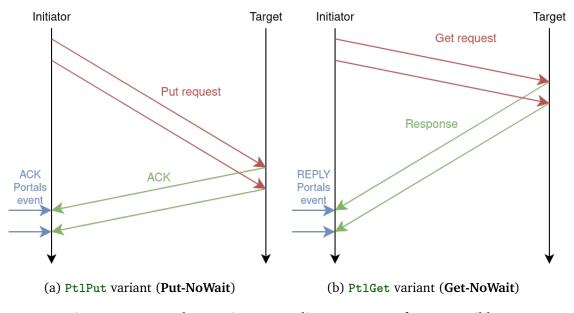

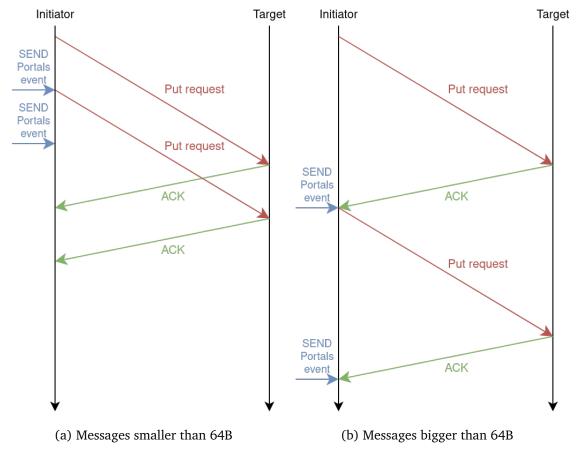

### **PtlPut**

Put operations are a very basic "send" operation, which corresponds to an RDMA write. As most operations, it can have match bits or not, and it will trigger various events that users can listen to: in particular a "SEND" event when the user buffer (which contains the data to be sent) can be safely re-used and an "ACK" event when an acknowledgement has been received from the remote node that was targeted. At the target, Put operations trigger a "PUT" event.

#### PtlGet

Get operations correspond to an RDMA read: making a Get request only sends a small message to ask the remote machine for a piece of memory, at which point the remote NIC will send back the requested data in a response. Unlike Put operations this means that the request is very lightweight (only a few bytes of metadata) and the payload which can have an arbitrary size is in the response instead. From a user perspective, the completion of the operation can be tracked by listening to a "REPLY" event. At the target, Get operations trigger a "GET" event.

#### **PtlAtomic**

Atomic operations operate in a way that is very similar to a Put, but the NIC also performs an arithmetic operation using two operands: the incoming payload and the data already present at the specified address in the remote node's memory (which is also used to store the result). These operations can be a sum, product, etc. on various data types (integers, floating point numbers, etc.).

### PtlFetchAtomic

FetchAtomic operations work in the same way as Atomics, but they also send a full response which contains the piece of data before it was modified by the Atomic operation. This means that FetchAtomic behaves as an Atomic and a Get at the same time: the request contains data to be used by the Atomic operation, but the response also contains data to be written at the initiator side as in a traditional Get. This also means that the operation involves two MDs at initiator side: one to describe the data to be sent and one to store the incoming response.

This operation has a variant, called PtlSwap, which operates very similarly to PtlFetchAtomic except that the permitted operation types are not arithmetic operations but different variations of swaps (conditional, with a mask, etc.).

### → 2.2.3 Portals's implementation in BXI

While Portals is a good specification for the API that should be exposed to users, at the lowest level significant freedom is left to the implementation. In this section we will present a few properties of BXI's implementation of Portals which will be of interest when modeling Portals in our simulator.

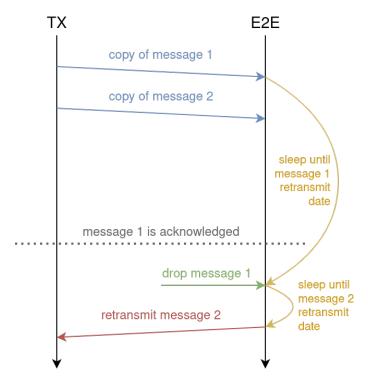

### End-to-End (E2E) Reliability

Since Portals is a reliable network API, it is the responsibility of BXI NICs to ensure that messages are delivered without errors. At packet-level the integrity of the data is enforced

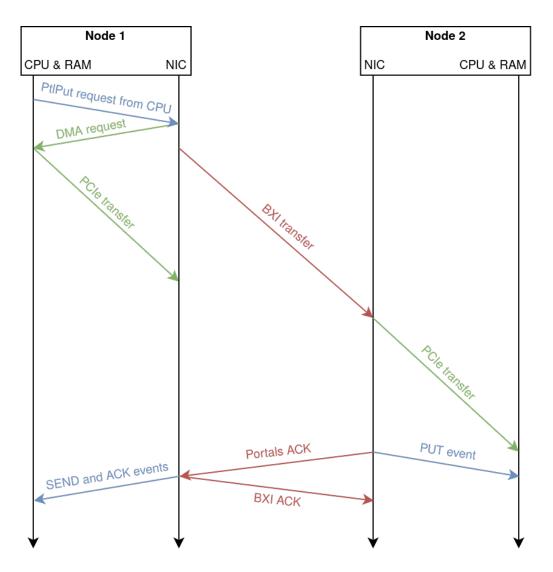

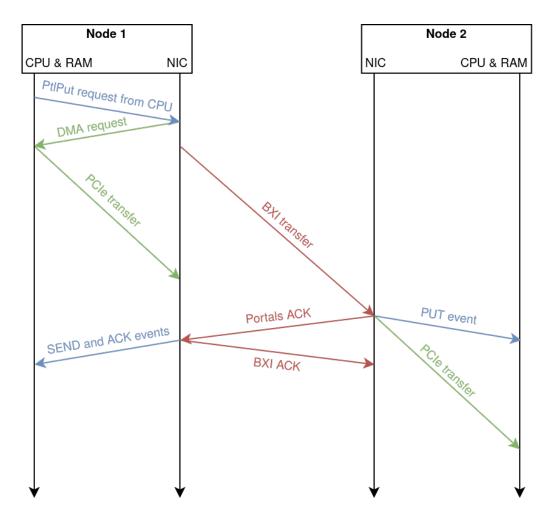

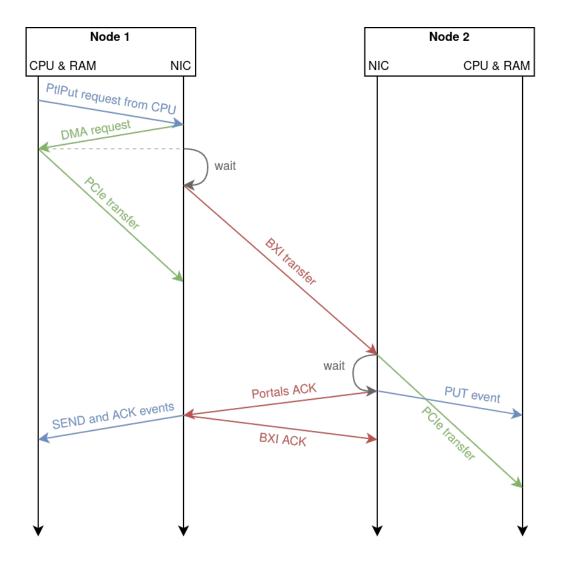

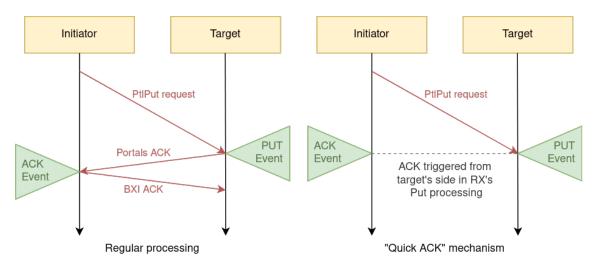

using a Cyclic Redundancy Check (CRC): each network packet features a field in its header for CRC data, which allows the receiver of messages to check the integrity of the payload, and send an acknowledgement (ACK) with an error code if any packet was corrupted, which will trigger a retransmission of the message by the sender. At message-level, a system of timeouts and retries is implemented using a dedicated "E2E" circuit. This part of the NIC keeps track of all outgoing messages, and if no acknowledgement is received within a configurable delay, the NIC will retransmit it. This happens a tunable number of times until the message is eventually given up on. An interesting property to note is that since ACKs are important messages that need to be reliably transmitted to ensure all events are properly generated, BXI implements two levels of ACKs. We will call "Portals ACK" the messages that acknowledge the reception of a Put or Atomic operation (which can cause the emission of an ACK event for the user application), and "BXI ACK" the messages that acknowledge the reception of a Portals ACK (which is only used internally by the E2E logic to know that a Portals ACK message does not need to be retransmitted, in a way that is entirely transparent to the user application).

### Virtual Networks (VN)

According to the Portals specification, it is required for messages to be ordered. This means that commands issued to the NIC by the user should result in messages being sent on the network in the same order, and also that this order should match the order of receptions at the target (in case all messages target the same machine). This causes a practical issue in real-world scenarios, which can lead to a complete deadlock of a NIC in the worst case: for example if fetching the data that needs to be sent by a request triggers a page fault which can only be resolved with another Portals request (if this data is located on a Network File System for example). Such dependencies between requests are solved by allowing different VNs to progress independently: BXI supports a total of four VNs: a "COMPUTE" VN for requests, a "COMPUTE" VN for responses, a "SERVICE" VN for requests and a "SERVICE" VN for responses. In our previous example, the problem would be solved by starting the NFS in "SERVICE" mode while having the main application in "COMPUTE" mode.

This system also allows requests and responses to progress independently: for example a small ACK can progress even if a large request is in progress. This last property is to be taken with a grain of salt: even though the vast majority of the processing in the NIC allows all four VNs to progress independently, at the very end (writing the packets physically on the network cable) messages are once again sequential, and packets from different messages cannot be interleaved.

### **3.3** Benchmarks of interest

In HPC, there is a wide variety of benchmarks that are used to assess the performance of a cluster. The diversity of these applications comes from the need to evaluate performance at different scales, for example with low-level utilities to evaluate the speed of communications between a pair of machines, or at the opposite full scale applications which exhibit more complex behavior but which are also a more realistic use-case of an HPC cluster. Benchmarks can also have different goals in terms of workload: some are more network-intensive, others will focus on CPU usage, etc. The original use-case of most benchmarks is to evaluate the performance of real clusters. In contrast, this thesis focuses on simulation, and we will use the same benchmarks to assess the accuracy of our models.

We will therefore run these benchmarks both on real-life clusters and in simulation to compare the results.

Additionally, the applications in which execution flow does not depend on the manipulated data can be adapted in skeleton versions, where the execution flow and communication patterns are preserved but most of the expensive computation phases are removed. Skeleton versions of applications are especially useful to study the network's performance, in particular in simulation where the computational phases can be replaced by an increase of the simulated time, as we will see in more detail in Chapter 5.

This section will present the benchmarks we chose to use in this thesis, from the most simplistic low-level utilities to the most complete applications.

### → 2.3.1 Network benchmarks

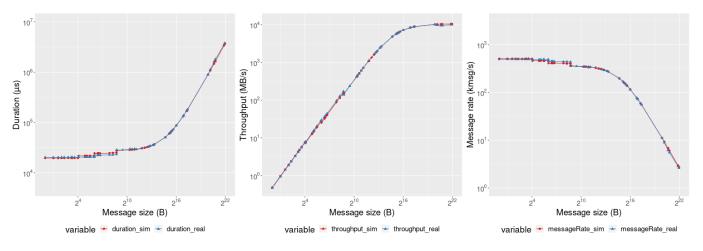

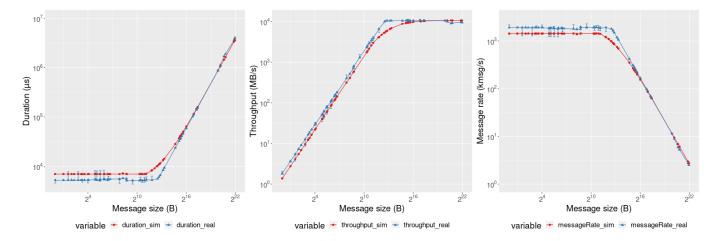

### **Ptlperf**

Ptlperf (short for "Portals performance") is a tool developed at Atos, whose goal is to measure the network speed between two NICs using the Portals 4 API. It has various modes, which replicate more or less realistic scenarios:

- Fast mode sends as many messages on the network as possible without caring for acknowledgements or any other Portals event. It makes the resulting workload unrealistic, but it showcases the theoretical maximum transmission speed of the hardware.

- ACK mode counts completed requests by keeping track of acknowledgements from the target, a new message is sent each time the ACK event from the previous request is received.

- CT mode works in similarly, but it uses lightweight counters instead of full events to keep track of completed transfers, sending one message at a time.

- Reply mode implements a ping-pong instead of sending messages in one direction only.

- Match mode mimics a more realistic use case with several messages inflight, and a more realistic use of resources at the target side (MEs).

### **OSU Micro Benchmarks**

Ohio State University (OSU) benchmarks are a set of dozens of "unit test" style benchmarks, made by the creators of the MPI implementation MVAPICH, targeted at MPI and OpenSHMEM: each benchmark calls a specific primitive in a short warm up loop and then a measurement loop, in order to determine its performance on increasingly large messages. While this creates highly artificial workloads, that do not correspond to a real-life scenario, it is an efficient and standard way to measure the performance of a specific primitive in a cluster. In essence, they are similar to Ptlperf in that they benchmark a specific primitive, even though the methodology is slightly different, since OSU benchmarks time a fixed number of calls, whereas Ptlperf tries to fit as many calls as possible in a fixed amount of time.

#### → 2.3.2 Realistic (proxy) applications

While low-level network benchmarks are a good entry point to evaluate the performance of an interconnection network, or the accuracy of a network simulator, they do not represent realistic workloads. Using more realistic applications is then important to evaluate the interactions between network operations, computations, I/O operations, etc., and we will use the following ones in our study.

#### **LULESH**

Figure 2.5: Visual representation of LULESH results<sup>2</sup>

Livermore Unstructured Lagrangian Explicit Shock Hydrodynamics (LULESH) is a very popular C++ proxy application that is commonly used to benchmark HPC clusters [KBK+13]. The underlying physics problem that it solves is a specific instance of a hydrodynamics problem, more specifically a Sedov blast wave problem, which studies the deformation of materials in 3D, as explained in [HKG11]. A graphical representation of an example result is displayed on Figure 2.5. As this application is very popular, implementations of LULESH exist for most parallel programming frameworks and hardware.

LULESH mainly uses point-to-point operations for its communications, along with more occasional Reduce and AllReduce calls. The execution flow of the application depends on the numerical results from computation, which is why it is difficult (if at all possible) to make a skeleton version of this application. It also has a constraint on the number of processes that need to be used to run it: because of the way work is distributed on the MPI ranks, the total number of process must be the cube of an integer (so 1, 8, 27 are valid numbers of ranks for example).

### Quicksilver

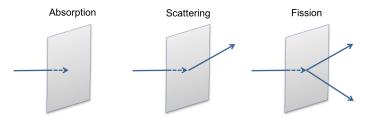

Quicksilver is a C++ proxy application that uses a Monte Carlo algorithm [CC75] to solve a particle transport problem: it models a configurable number of particles, and their interactions in 3 dimensions with a predefined mesh. The possible interaction types are represented on Figure 2.6. Quicksilver has implementations both on CPU, with OpenMP and MPI, and on GPU with CUDA.

<sup>&</sup>lt;sup>2</sup>Image from https://asc.llnl.gov/codes/proxy-apps/lulesh

<sup>&</sup>lt;sup>3</sup>Image from https://asc.llnl.gov/codes/proxy-apps/quicksilver

Figure 2.6: 3 possible interactions that a particle can have in the Quicksilver model<sup>3</sup>

It features a variety of point-to-point and collective operations, as well as custom datatypes, which makes it an interesting app to study. However, similarly to LULESH it is very hard to make a skeleton version for it as execution flow depends on the correctness of calculations.

#### **HPL**

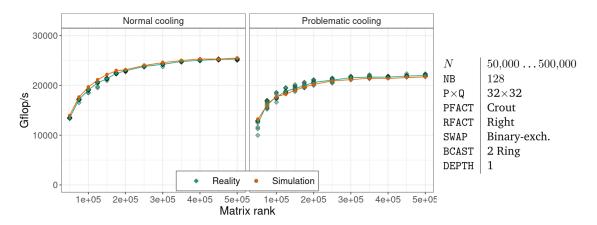

Figure 2.7: Results of HPL simulation in SMPI in two scenarios. Image from [Cor21]

High-Performance Linpack (HPL) is a very popular benchmark, famous for being used to rank supercomputers in the Top500 list [TOP22]. It solves a mathematical problem, more specifically a randomly generated dense linear system. The algorithm that is implemented is a lower-upper (LU) decomposition.

It relies on MPI for its communication, and on the Basic Linear Algebra Subprograms (BLAS) [LHKK79] for computation, which is a library that has many implementations, some generic and some vendor specific. For example, AMD provides its own version of BLIS [VvdG15], a framework that provides a fast BLAS implementation, which is optimized for AMD CPUs (in particular the Epyc and Ryzen architectures), and which is the version we will use in our experiments.

HPL does not use any collective operation from MPI directly, instead the application reimplements all collective primitives itself (using combinations of point-to-point operations), and allows users to tune the algorithm used for each type of operation in the input file that drives the execution.

What makes it an interesting application to study is that it has already been the subject of many studies, and therefore it already has existing skeleton versions: in this thesis we will be able to reuse a skeleton made for SMPI with no modifications. Simulation results obtained with SMPI in two scenarios (with or without a cooling incident on the cluster) are

shown on Figure 2.7. It also makes heavy use of user-made datatypes and communicators (by splitting the global "MPI\_COMM\_WORLD"), which is not very common, so it is a good way to test these features in simulation.

# Strangter 3

## Related work around simulation

As discussed in the previous section, an HPC software stack can be complex, and the hardware features many of optimizations and offloads that can have unpredictable effect on the performance on real-life applications. Because of this, it is very challenging to predict the execution time of an application on a given cluster, although it is an important problem to solve, in order to improve applications' code, optimize libraries, and design more performant hardware for the next generation. It is also important to be able to model the behavior of hardware before making physical prototypes, because it accelerates the development and reduces the costs of hardware design by orders of magnitude. For software developers, testing on real-life clusters, or hardware that is not available yet, can be difficult and costly (since clusters require a huge amount of power, and often have many users which need to share the resources). This is why simulators are a crucial tool for both hardware designers and software developers in HPC.

## **⊗** 3.1 Tradeoff between performance and accuracy

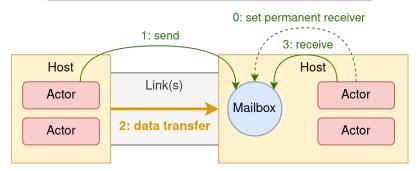

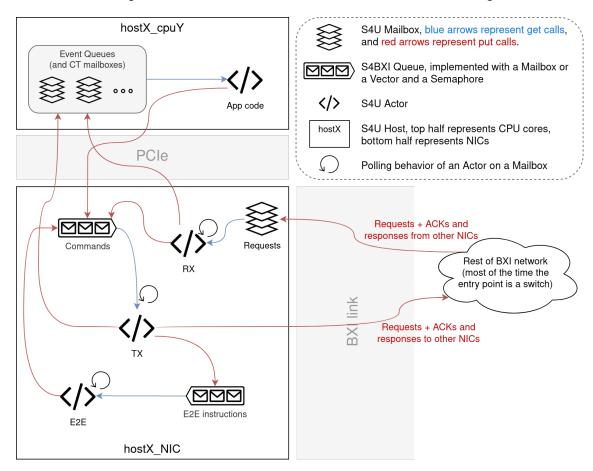

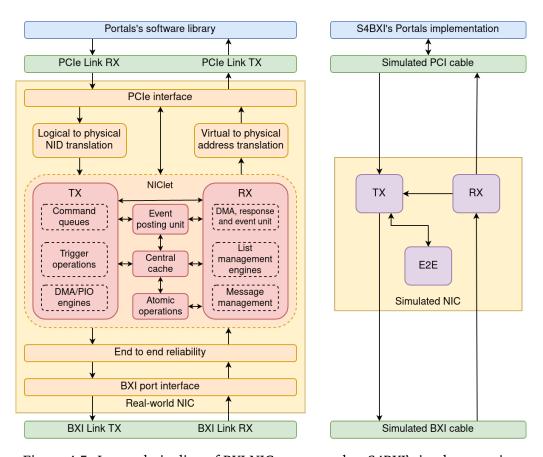

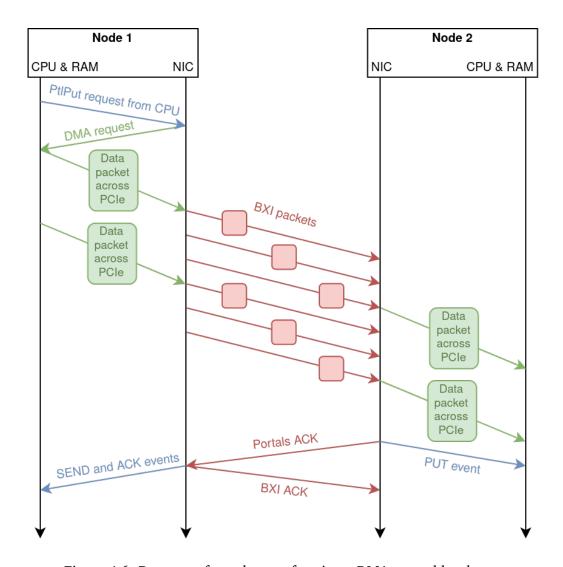

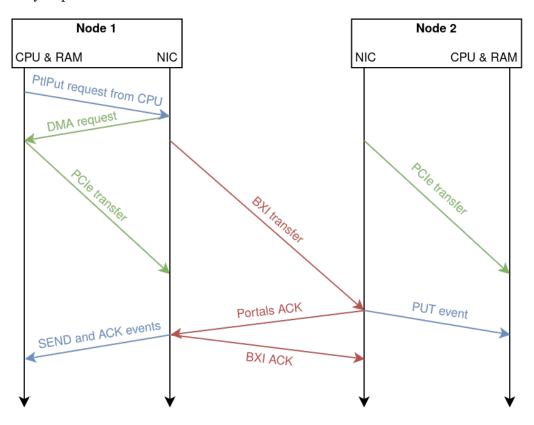

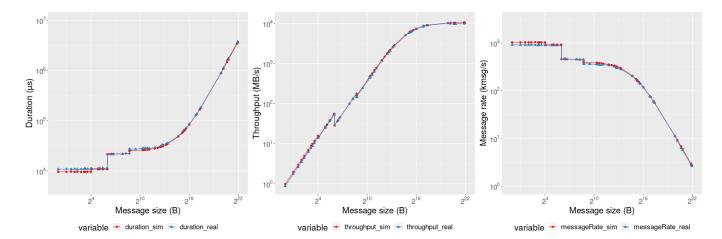

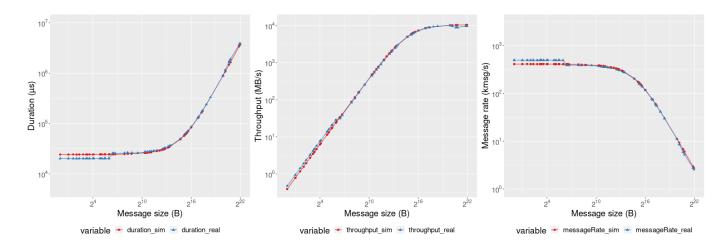

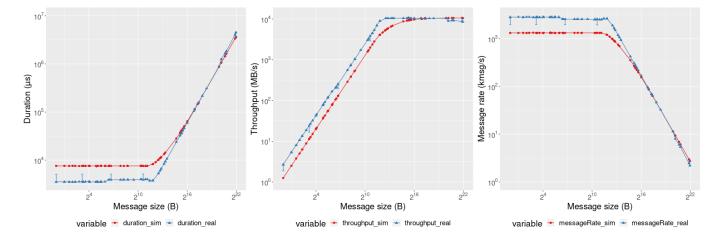

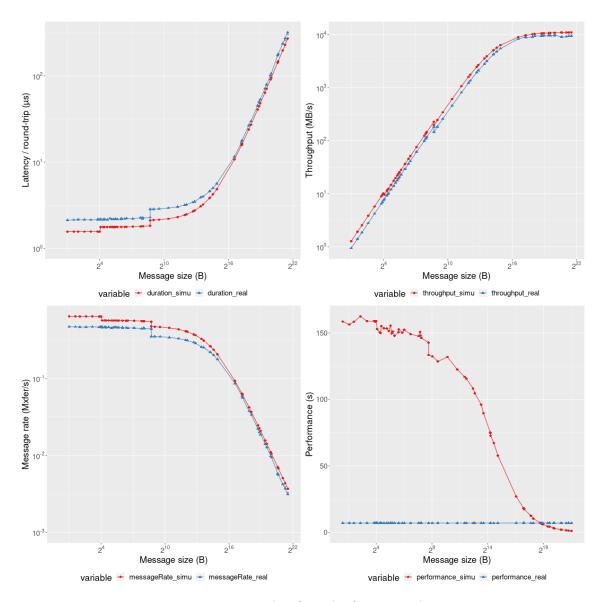

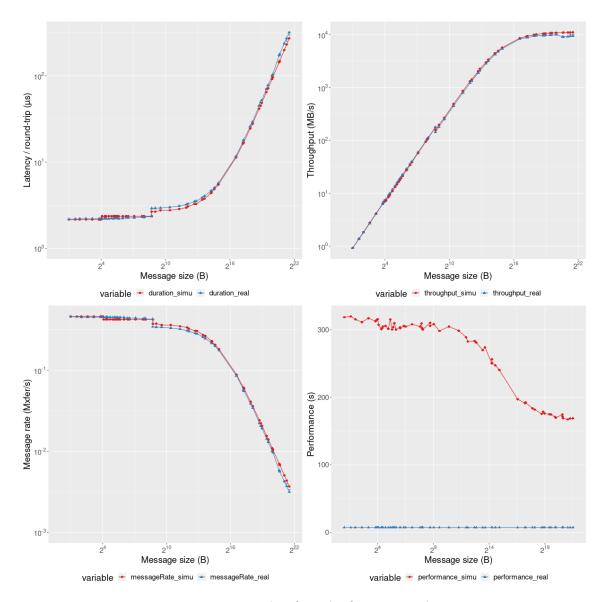

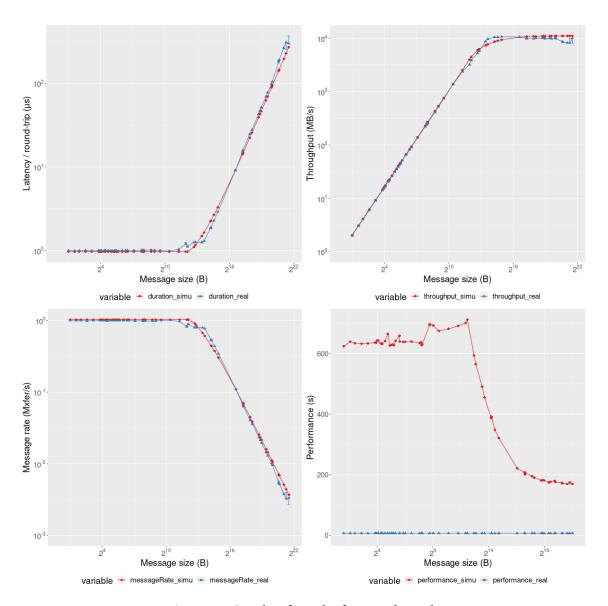

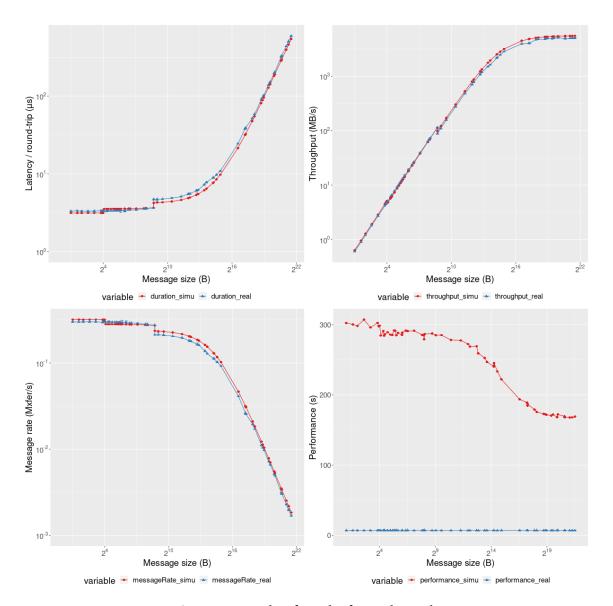

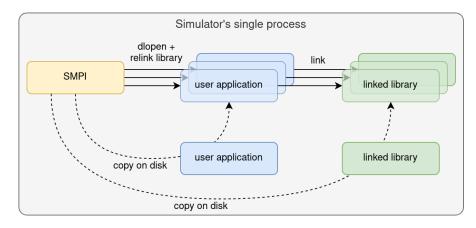

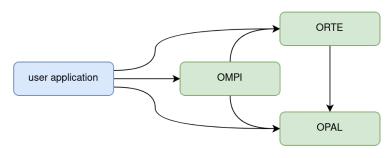

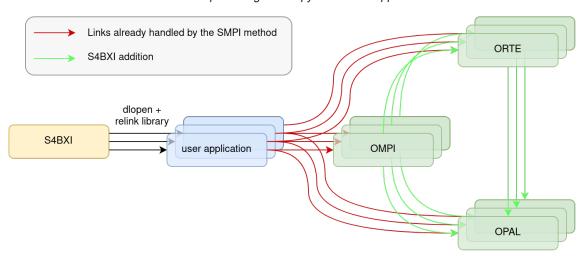

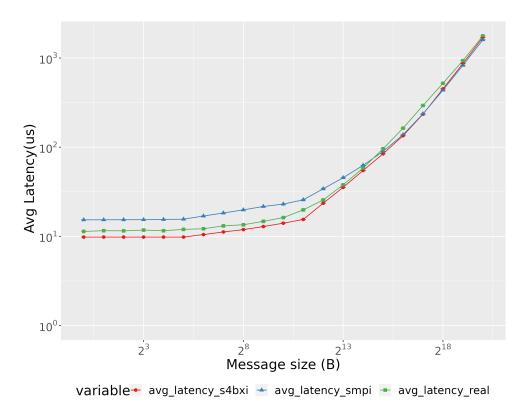

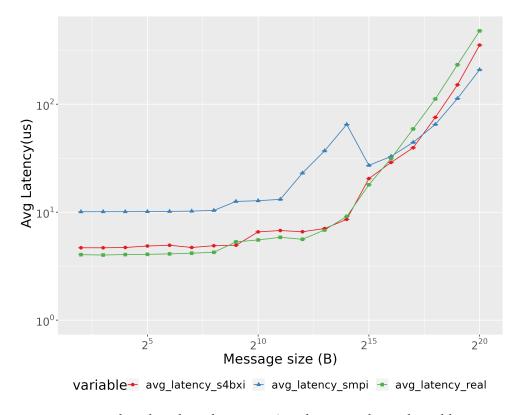

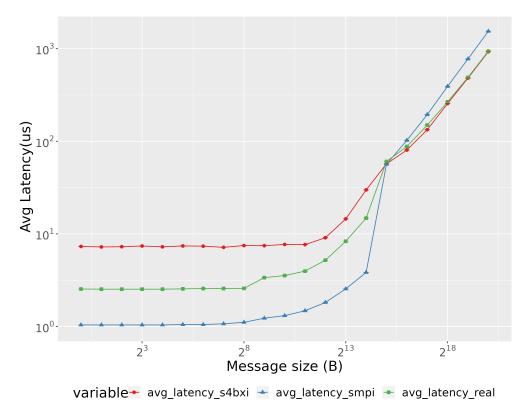

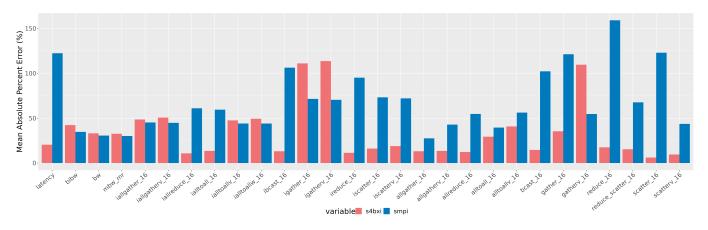

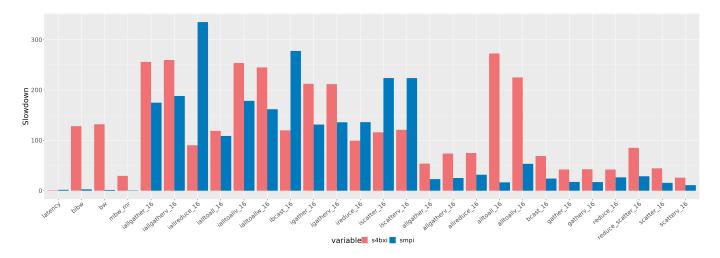

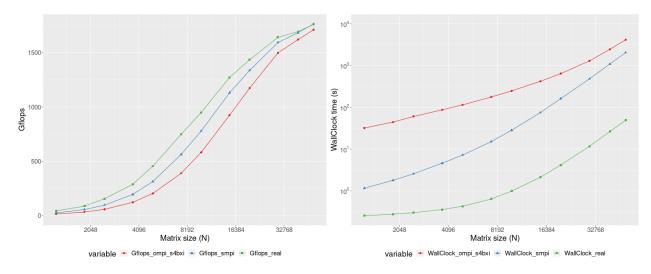

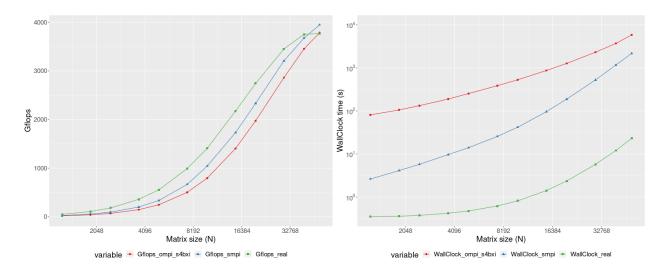

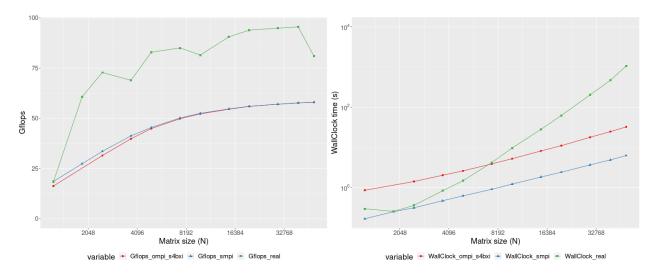

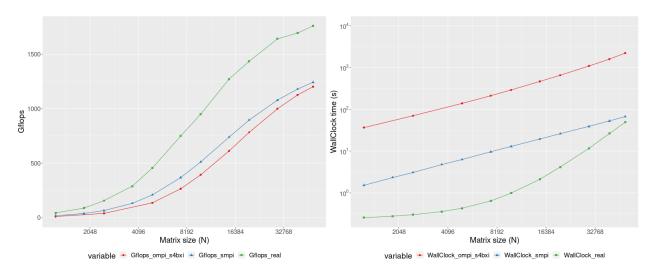

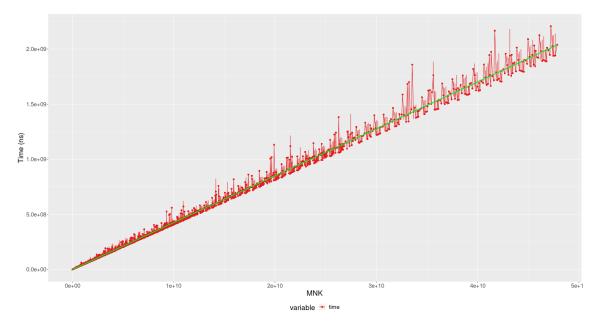

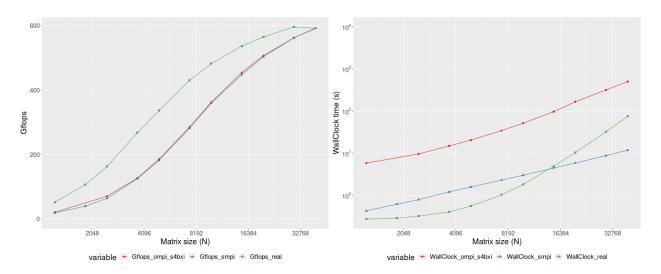

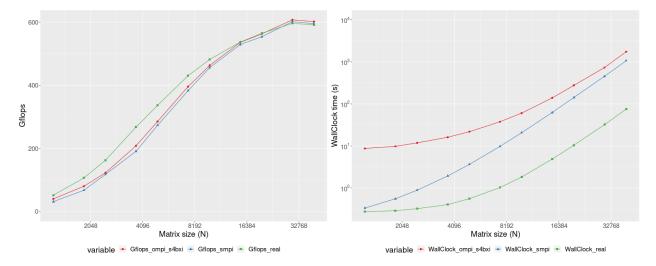

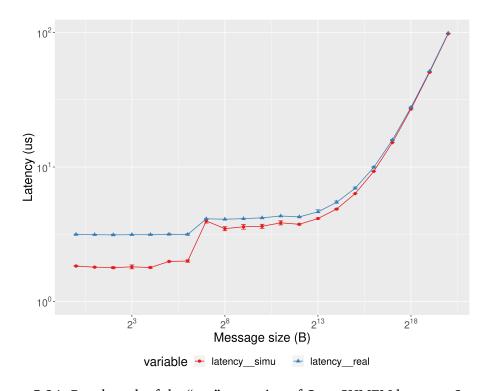

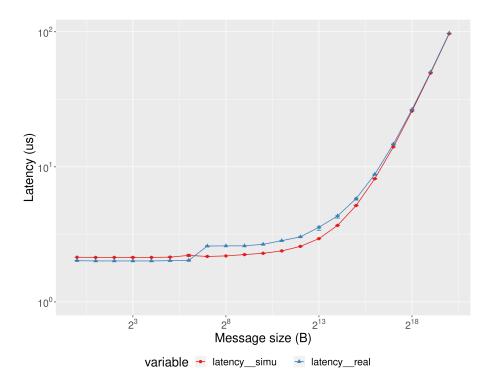

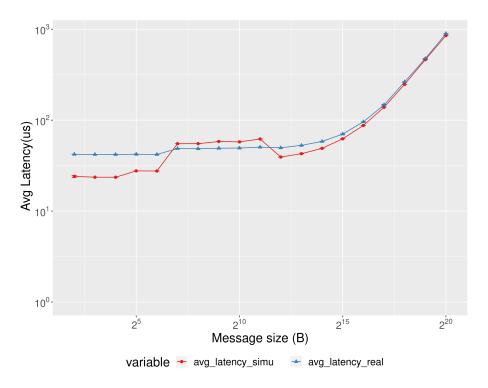

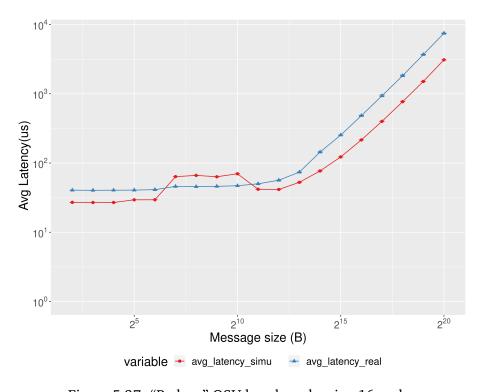

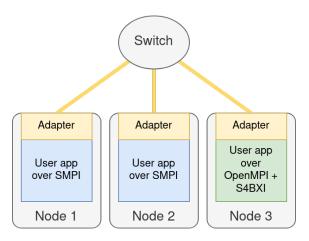

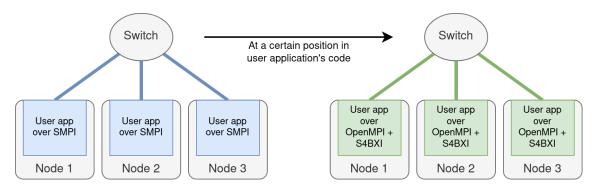

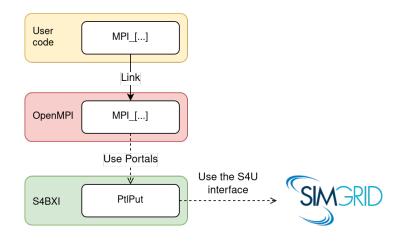

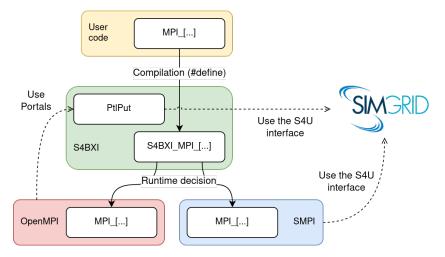

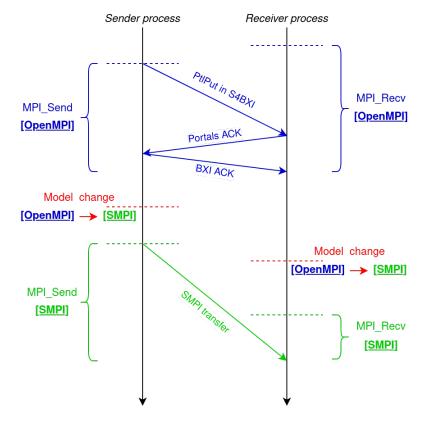

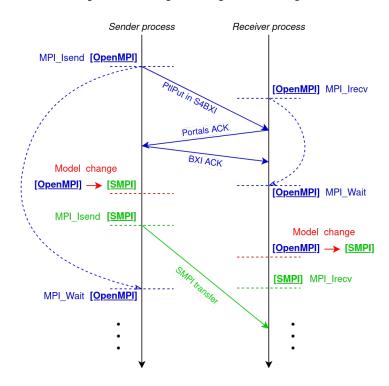

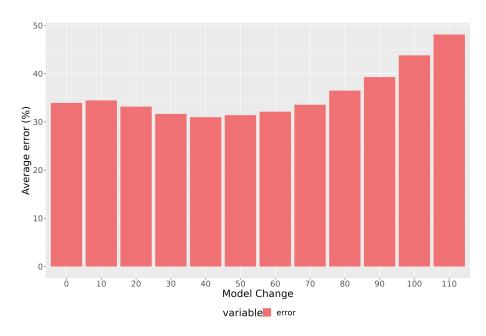

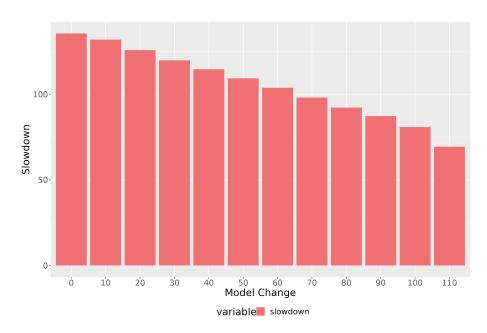

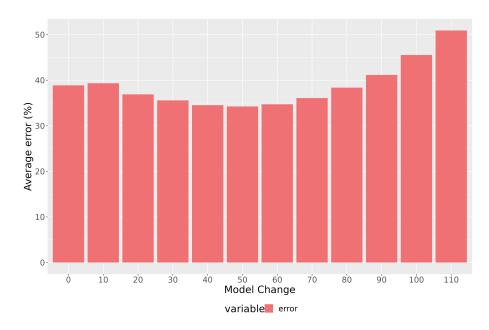

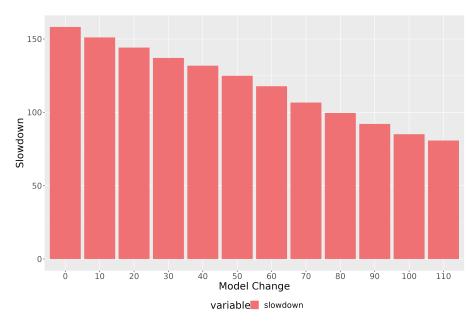

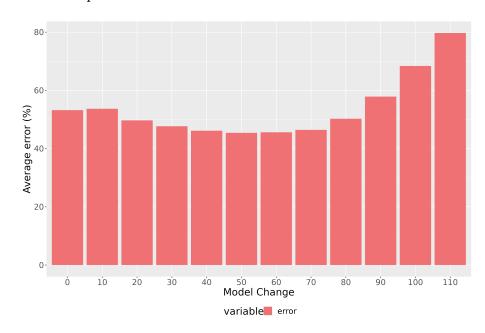

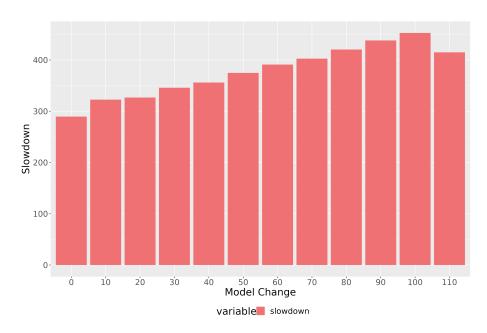

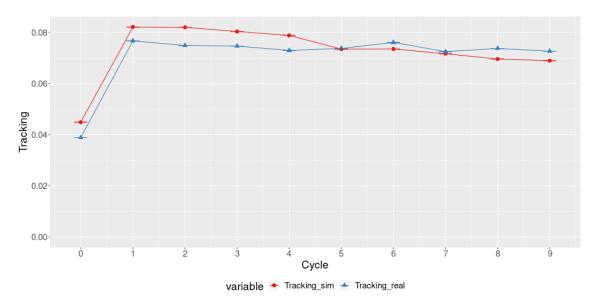

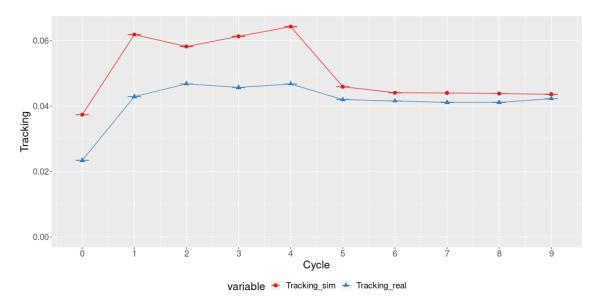

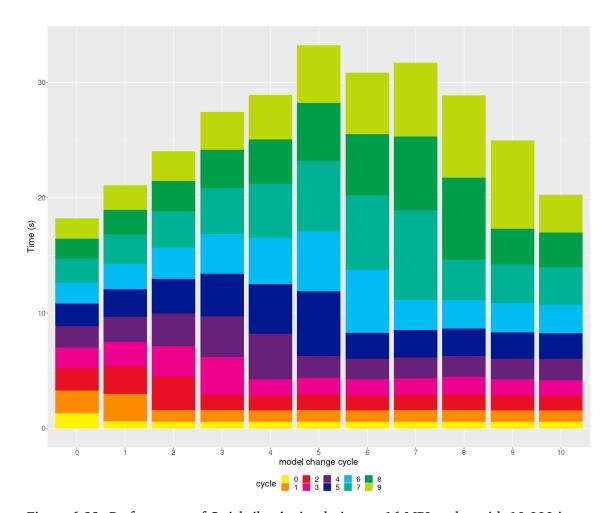

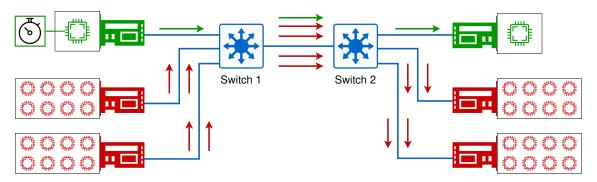

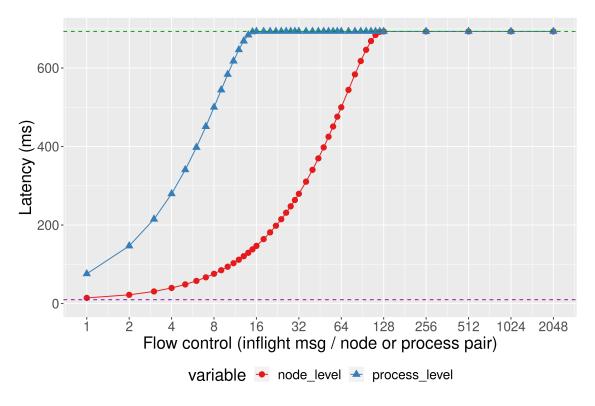

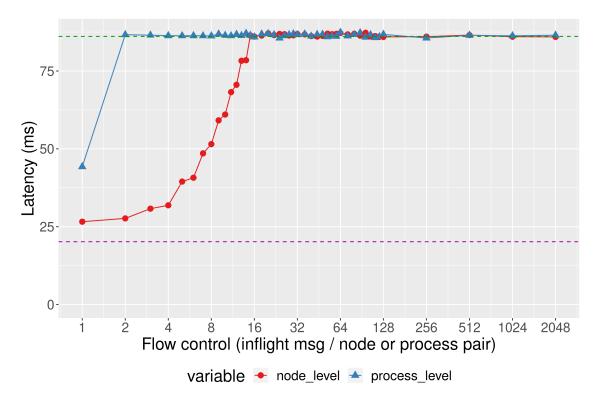

We can categorize simulators in a few groups, depending on their use case: for hardware designers, most of the time simulators need to be a faithful emulator of real-world hardware, to be able to fine tune the behavior of the circuit to get the desired output. This type of simulation is called Cycle Accurate, Bit Accurate (CABA) when modeling processing units (like CPUs), and are often built with frameworks like SystemC [CMMC08] or gem5 [MCJW17] (sometimes both). When modeling networking hardware, this type of simulation is called packet-level (or flit-level), and is typically built with frameworks such as ns-3 [RH10], Omnet++ [Var01] or CODES [JBH+17]. The biggest advantage of this type of simulators is that they are very accurate and faithful to real-world hardware, but the downside is they are often very expensive to run in terms of performance, as the simulations are orders of magnitude slower than real-world executions.