# Micro-architectural side channels: Studying the attack surface from hardware to browsers

Clémentine Maurice

# ▶ To cite this version:

Clémentine Maurice. Micro-architectural side channels: Studying the attack surface from hardware to browsers. Cryptography and Security [cs.CR]. Université de Lille, 2023. tel-04180074

# HAL Id: tel-04180074 https://inria.hal.science/tel-04180074

Submitted on 11 Aug 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Micro-architectural Side Channels: Studying the attack surface From hardware to browsers

présentée et soutenue publiquement le 24 mai 2023 par

# Clémentine Maurice

Chargée de Recherche au CNRS

pour obtenir le

Diplôme d'Habilitation à Diriger des Recherches de l'Université de Lille

Spécialité Informatique

# Composition du Jury

Rapporteurs Davide Balzarotti Professeur, EURECOM

Lejla Batina Professeure, Radboud University Tamara Rezk Directrice de Recherche, Inria

Examinateurs Herbert Bos Professeur, VU Amsterdam

Gilles Grimaud Professeur, Université de Lille

Garant Romain Rouvoy Professeur, Université de Lille

# **Abstract**

Hardware is often represented as an abstract layer that behaves correctly, executes instructions and produces a result. However, side effects due to the execution of computations on actual computers can lead to *information leakage*. *Fault attacks* also threaten security, by generating errors in the physical system and thus bypassing security mechanisms. Typically, information leakage from *side-channel attacks* includes power consumption or electromagnetic emissions, and fault attacks include altering the system's power supply or clock. All of these attacks require physical access to the device. In contrast, my research activities since October 2015 have focused on side-channel and fault attacks that do not require physical access, and instead use the micro-architecture components of the processors. These attacks are software-based, and, therefore, remotely executable.

The main research challenge in micro-architectural attacks is to build secure systems and hardware that are immune to these vulnerabilities. In this manuscript, I give a partial view of my contributions in this domain, focusing on the attack surface, one of the main issues we face. In the first part, we cover the hardware attack surface, *i.e.*, the discovery of new side channels in unsuspected micro-architectural components. In the second part, we focus on a particular delivery method for side-channel attacks: web browsers.

# Résumé

Le matériel est souvent représenté comme une couche abstraite qui se comporte de manière correcte, exécutant des instructions et produisant un résultat. Cependant, des effets de bords dus à l'exécution des calculs sur une machine peuvent créer des *fuites d'informations* sensibles. Les *attaques par fautes* menacent également la sécurité, en générant des erreurs sur le système physique et donc en contournant les mécanismes logiciels de sécurité. Typiquement, les fuites d'informations qui découlent d'*attaques par canaux auxiliaires* incluent la consommation de courant ou les émanations électromagnétiques, et les attaques par fautes incluent la modification de l'alimentation électrique ou de l'horloge du système. Toutes ces attaques requièrent un accès physique à l'appareil. Au contraire, ma recherche depuis octobre 2015 s'intéresse aux fuites d'informations et attaques par fautes qui ne requièrent aucun accès physique, et qui utilisent les composants de micro-architecture des processeurs. Ces attaques sont réalisables par logiciel, et donc exécutables à distance.

L'enjeu principal de la recherche sur les attaques liées à la micro-architecture est de construire des systèmes et du matériel sûrs et résistants à ces vulnérabilités. Dans ce manuscrit, je donne une vue partielle de mes contributions dans ce domaine, en me concentrant sur la surface d'attaque, l'un des principaux problèmes auxquels nous sommes confrontés. Dans la première partie, nous couvrirons la surface d'attaque matérielle, c'est-à-dire la découverte de nouveaux canaux auxiliaires dans des composants micro-architecturaux insoupçonnés. Dans la seconde partie, nous nous concentrerons sur une méthode particulière de diffusion des attaques par canaux auxiliaires : les navigateurs web.

# **Contents**

| 1  | Intr  | Introduction                                            |    |  |  |  |  |

|----|-------|---------------------------------------------------------|----|--|--|--|--|

|    | 1.1   | Micro-architectural security                            | 4  |  |  |  |  |

|    | 1.2   | Challenges                                              | 5  |  |  |  |  |

|    | 1.3   | My contributions                                        | 6  |  |  |  |  |

|    | 1.4   | Organization of the manuscript                          | 7  |  |  |  |  |

| 2  | Side  | e channels, side channels everywhere                    | 9  |  |  |  |  |

|    | 2.1   | DRAM addressing                                         | 10 |  |  |  |  |

|    |       | 2.1.1 Acquiring measurements                            | 11 |  |  |  |  |

|    |       | 2.1.2 Modeling DRAM addressing                          | 13 |  |  |  |  |

|    |       | 2.1.3 Security impact                                   | 13 |  |  |  |  |

|    | 2.2   | AMD cache way predictors                                | 16 |  |  |  |  |

|    |       | 2.2.1 Acquiring measurements                            | 17 |  |  |  |  |

|    |       | 2.2.2 Modeling the cache way predictor                  | 17 |  |  |  |  |

|    |       | 2.2.3 Security impact                                   | 18 |  |  |  |  |

|    | 2.3   | Intel CPU interconnect                                  | 21 |  |  |  |  |

|    |       | 2.3.1 Acquiring measurements                            | 21 |  |  |  |  |

|    |       | 2.3.2 Modeling the CPU interconnect                     | 22 |  |  |  |  |

|    |       | 2.3.3 Security impact                                   | 24 |  |  |  |  |

|    | 2.4   | Discussion                                              | 26 |  |  |  |  |

| 3  | Тис   | quoque, my browser                                      | 27 |  |  |  |  |

|    | 3.1   | Timing is everything                                    | 27 |  |  |  |  |

|    |       | 3.1.1 (In)security of resolution clamping               | 28 |  |  |  |  |

|    |       |                                                         | 30 |  |  |  |  |

|    | 3.2   |                                                         | 32 |  |  |  |  |

|    |       | 3.2.1 Porting port contention side channels in browsers | 33 |  |  |  |  |

|    |       | 3.2.2 Security impact                                   | 34 |  |  |  |  |

|    | 3.3   | Discussion                                              | 35 |  |  |  |  |

| 4  | Con   | iclusions and perspectives                              | 36 |  |  |  |  |

|    | 4.1   |                                                         | 36 |  |  |  |  |

|    | 4.2   | Perspectives                                            | 37 |  |  |  |  |

| Bi | bliog | graphy                                                  | 40 |  |  |  |  |

| Publications from October 2015 to January 2023                    | 51 |

|-------------------------------------------------------------------|----|

| Software related to my research from October 2015 to January 2023 | 54 |

| Appendices                                                        | 55 |

# Chapter 1

# Introduction

The following document is a synthesis of my research activity since my PhD defense in October 2015. After a postdoc at IAIK, Graz University of Technology, Austria, I joined the EMSEC team at the IRISA lab, in Rennes, France, in October 2017. I then joined the Spirals team at the CRIStAL lab, in Lille, France, in February 2021. In the last seven years, my research activities have addressed a variety of topics, however, all related to micro-architectural security. During this time, I have had the pleasure to see the domain growing, from a few papers per year (and a domain admittedly not very bustling, if not a bit comatose, according to my own PhD supervisors) to dedicated sessions in every international toptier security, micro-architecture, and system conferences. I have been, arguably, the main co-advisor of two successful doctorates, Thomas Rokicki (defended on November 29, 2022) and Guillaume Didier (defended January 20, 2023). I currently co-advise a third-year doctoral student, Pierre Ayoub (since 2020, co-advised with Aurélien Francillon), and a first-year doctoral student, Antoine Geimer (since 2022, main co-advisor).

# 1.1 Micro-architectural security

Hardware is often represented as an abstract layer that behaves correctly, executing instructions and producing a result. However, side effects due to the execution of computations on actual computers can create *information leakage*. Fault attacks also threaten security, by generating errors on the physical system and thus bypassing security mechanisms. Typically, information leakage from side-channel attacks includes power consumption or electromagnetic emissions, and fault attacks include altering the system's power supply or clock. All these attacks require physical access to the device and are referred to as physical attacks. In contrast, I am interested in attacks that do not require physical access, and that use micro-architectural components of processors, hereafter referred to as *micro-architectural attacks*. These attacks are all software-based, and, therefore, remotely executable. Let us depict a brief overview of the different classes of micro-architectural attacks.

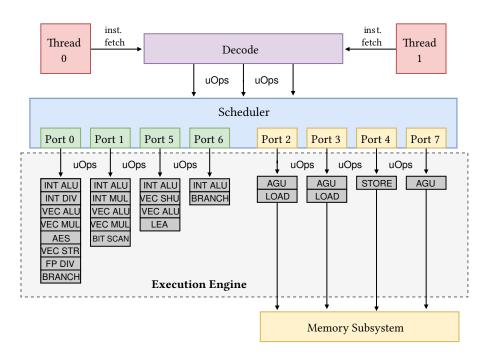

In 1996, Kocher published his seminal work on *side-channel attacks* [91] by describing the first timing attacks against various cryptosystems: just by measuring the execution time of private key operations, an attacker can derive secret keys. In the following decade, the cache has been used to obtain more fine-grained information [23, 27, 119, 120, 117, 154]. Side-channel attacks are mainly due to optimizations in modern processors and operating systems, and in particular to shared microarchitectural components. The attacks use components such as the CPU cache [33, 82, 104, 117, 120, 178, 181, 179], the branch prediction unit [6, 9, 57, 58, 60], the memory management unit [67, 68,

137], floating point units [17], the ring interconnect [118], or even CPU ports [8, 10]. Indeed, these optimizations create differences in the execution time of programs, thus revealing secret information.

In contrast, *fault attacks* exploit physics and are more active attacks. While hardware operates correctly within some physical boundaries, the goal for an attacker is to push the components outside of these boundaries, using software only. Today, the most studied fault-based attack without physical access concerns DRAM and is called Rowhammer [30, 45, 46, 63, 71, 73, 78, 88, 89, 93, 99, 111, 116, 125, 128, 145, 150, 158, 177]. Internally, each DRAM cell consists of a capacitor and a transistor, which electrically implement a 0 or a 1. By repeatedly accessing cells, the charge of these cells leaks out and interacts electrically with the charge of neighboring cells. Thus, it is possible to change the value of cells in memory without ever having accessed them.

Finally, a novel class of attacks appeared in 2018, transient execution attacks [40, 90, 103]. They exploit transient instructions, i.e., instructions that are not committed to the architectural state, due to a misprediction in speculative execution, or a fault. Functional correctness is ensured by pipeline flushes, which discard any architectural effects of pending instructions. Nevertheless, these instructions leave traces in micro-architecture — traces that we have spent a solid decade perfecting the art of retrieving through side channels. Transient execution attacks have much more severe outcomes than side-channel and fault attacks, having been shown to be able to leak, e.g., kernel memory and passwords.

My research has spanned mostly side-channel attacks, moderately fault attacks (and in particular, Rowhammer attacks), and very sparingly transient execution attacks. This manuscript focuses solely on side-channel attacks.

# 1.2 Challenges

The main challenge of research on micro-architectural security is to build secure systems and hardware that are immune to these vulnerabilities. Faced with this challenge, I distinguish two main issues: 1) the attack surface is not well known today, both at the hardware and software level, 2) current countermeasures suffer from an adoption problem, due to performance, cost, and scaling reasons. While I do have contributions related to countermeasures [70, 139, 140], most of my work pertains to the attack surface, this is thus the focus of this *Habilitation à Diriger des Recherches*. I believe that studying the attack surface is a necessary and preliminary step in designing efficient countermeasures. Indeed, a system that would be, e.g., entirely protected against cache attacks, even with the most exquisite and efficient cache design, would not fare well, with the *same attacker model*, regarding any attack on any other component. Of course, the task of a defender is, in essence, asymmetric compared to the one of an attacker. Much like the Rebels attacking the Death Star in Star Wars, an attacker only has to find a *single* entry point, whereas a defender has to make sure that *all* entry points are secured.

The attack surface itself is, however, not a small matter. We aim at finding vulnerabilities — which, let us remember, exist whether we find them or not — to defend against them. From a defensive perspective, the task is, therefore, immense: we need to find all vulnerabilities an attacker could exploit! Furthermore, micro-architecture sits between the hardware and software interface. This means that part of the attack surface is tied to hardware, leading to a first research question "What are the vulnerable components, and how to use them to leak secret data?", and part of the attack surface is tied to software, leading to a second research question "What are the vulnerable pieces of software, and what are the different attack deliveries?".

# 1.3 My contributions

In this section, I give an overview of my various contributions, even though I will not detail all of them in this manuscript.

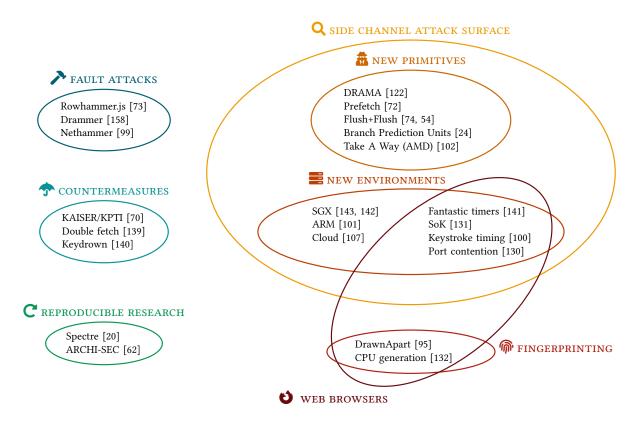

My main contributions concern the **side-channel attack surface**, at the hardware level. The first body of work I focused on is the creation of **new primitives**, to further understand the attack surface. Indeed, it is not possible to build efficient countermeasures without understanding precisely which components leak information, and how to manipulate the state of these components to leak information. As information usually leaks from the execution time of some instructions, we discovered timing leakage in novel instructions such as x86 prefetch [72] and clflush [74]. On some occasions, the creation of new primitives required some reverse-engineering work. This was the case when we investigated the first DRAM side-channel attack [122], the branch prediction unit [24], the AMD cache way predictor [102], and the CPU Interconnect [54].

Another body of work I focused on is investigating side-channel attacks in **new environments**. Indeed, typically, side-channel attacks are developed in native x86 environments, using native code such as C and assembly, as it makes it easier to manipulate components at a low level. Some primitives require specific instructions, e.g., the clflush instruction, which are only available in x86. It can therefore be challenging to port these attacks to new environments that either are not native, or with a different instruction set architecture. We demonstrated side-channel attacks from ARM devices [101], SGX enclaves [142, 143], covert channels in the cloud [107], as well as side-channel attacks in **web browsers** [100, 130, 131, 141]. Closely related to side-channel attacks in the browser is **finger-printing**. We explored hardware fingerprinting, a novel field of research, and in particular, machine

fingerprinting leveraging GPUs with WebGL [95], and CPU generation fingerprinting leveraging port contention [132].

Different from side-channel attacks, I also focused on **software-based fault attacks**, and in particular the Rowhammer attack [89]. Here, my objective has also been to study the different environments in which Rowhammer was feasible. Indeed, much like side-channel attacks, the first attack was carried out in a native environment, using specific x86 instructions such as clflush. We demonstrated that, even though the attack requires surgical precision to access the right DRAM rows and to evict lines from the cache, this fault attack can be performed from JavaScript [73]. We later demonstrated that the attack can also be performed on ARM devices [158], and even remotely through network requests, given some conditions on the system [99].

While micro-architectural attacks are complicated to protect against, I strive to propose **countermeasures** in each attack paper (even though their adoption can be difficult due to performance overhead). Some work was, however, focused on countermeasures alone. We proposed a mitigation called Keydrown against software-based keystroke timing side-channel attacks [140]. We also built a countermeasure dubbed KAISER [70] that provides practical kernel address isolation and protects against side-channel attacks that bypass KASLR (and in particular our previous work [72]). Interestingly, KAISER ended up being a countermeasure for the Meltdown attack by Lipp et al. [103] and was deployed in all major operating systems as kernel page-table isolation (KPTI). Finally, we also used side channels as a countermeasure – when they are overwhelmingly used as an attack – to detect and exploit double-fetch bugs in the kernel, eliminating them with hardware transactional memory instructions [139].

Finally, I am interested in **reproducible research** on micro-architectural security. Through the ANR ARCHI-SEC project, we are building a platform using the gem5 simulator to facilitate the reproducibility of micro-architectural attacks [62]. This is a completely new direction in this field where simulators are only used to model new hardware countermeasures. The use of a simulator for these attacks is not trivial because the processor model must be faithful to reality, and the complexity and lack of documentation can be a hindrance. We showed that visualization techniques for CPU pipeline could help the reproducibility of Spectre attacks by Kocher et al. [90], and ran data collection from gem5 and an ARM Cortex-A72 CPU to analyze the simulation accuracy. Our conclusions are optimistic about the role simulators can play in the future of micro-architectural security research [20], but much work remains.

# 1.4 Organization of the manuscript

This manuscript highlights some selected results of my research since my PhD defense in October 2015. Detailed experiments and algorithms can be found in the original papers. I have chosen to highlight two research directions: first, new side-channel primitives, and second, side channels in browsers. They seem to have little in common: the first is very close to the hardware components and will involve a fair amount of reverse-engineering, and the second is at the very top of the abstraction layers, in web browsers; yet, they complement each other.

► Chapter 2 dives into the micro-architectural level, and focuses on the components used to build new side-channel primitives. We will explore the DRAM (Section 2.1), the AMD cache way predictor (Section 2.2), and the Intel CPU interconnect (Section 2.3). It answers our first question "What are the vulnerable components, and how to use them to leak secret data?".

- ▶ Chapter 3, at a higher level, provides an overview of my work on side channels in web browsers. It shows that, even though side-channel attacks require fine-grained control over hardware components, these attacks are possible in web browsers. We will delve into the security of timers in browsers (Section 3.1), and detail a novel side channel based on CPU port contention (Section 3.2). It answers our second question "What are the vulnerable pieces of software, and what are the different attack deliveries?", focusing on the delivery aspect.

- ▶ Chapter 4 provides some conclusions and research perspectives that I would like to pursue.

# **Chapter 2**

# Side channels, side channels everywhere

In which we show that no micro-architectural component is spared by side channels

A large part of my work has focused on finding new side channels in micro-architectural components. Indeed, when I finished my PhD thesis, the two main components that were studied in terms of side-channel attack surface were the cache [1, 2, 4, 5, 7, 23, 27, 75, 76, 83, 85, 104, 112, 117, 119, 120, 148, 151, 152, 154, 168, 171, 176, 179] and the branch prediction unit [3, 6, 9] – except for the arithmetic logic unit of the Intel Pentium 4 that had also been studied by Aciicmez et al. [8] and the floating point unit that had been studied by Andrysco et al. [17].

However, the cache and the branch predictor were just the tip of the iceberg of the attack surface of a modern CPU. While caches [14, 33, 51, 56, 69, 80, 82, 109, 110, 123, 136, 153, 178, 181] and branch prediction units [58, 57, 60] have still been heavily studied in the last years, including in my own work [24, 54, 74, 101, 102, 107, 143], other components started being brought to light such as the TLB [67], the MMU [68], CPU ports [10, 66], the CPU ring interconnect [118], and the random number generator [59]. A practical axiom is that every micro-architectural component shared across processes has been, or will be, attacked.

As I explained in the introduction, our goal is to get a better, and, as much as possible, comprehensive view of the hardware attack surface. Indeed, securing one component is not enough if other components are leaking — in the same way as patching a hole on a leaking pipe that has a dozen other holes is futile. Another aspect to consider is that the scope of attack may be different from one component to another. For example, branch predictors restrict the attacker to same-core attacks (*i.e.*, the victim has to reside on the same core), the cache allows cross-core attacks but is still limited to same-CPU attacks, while DRAM attacks can be carried across CPUs too.

**Reverse-engineering.** Today, a major obstacle to a refined and complete analysis of the hardware attack surface is the lack of documentation of micro-architectural components by manufacturers. Indeed, in side-channel attack experiments, we never directly observe what we want to measure: our observations are always indirect, e.g., knowing whether a line is present in the cache through timing alone. It is, therefore, crucial to have as much knowledge as possible about the environment of our

experiments, *i.e.*, the micro-architectural components, to reduce the number of uncontrolled variables. Another matter is that, as attacks are getting more sophisticated and reaching more (undocumented) components, the need for reverse-engineering increased as well. One interesting aspect is that the lack of documentation, while hindering security research, is in fact not linked to security, but rather to performance. Indeed, these components are at the heart of performance improvements from one generation to another, and are therefore intellectual property, giving a competitive advantage that is better left undocumented.

Related work in reverse-engineering focused on last-level cache addressing [84, 180], cache replacement policies [161], cache directories [178], hardware prefetchers [129, 159], the CPU Ring Interconnect [118], page table caches [138], branch predictors [155], and GPUs [174]. The measurement acquisition is usually performed in two different ways: either through timing [84, 180] or through hardware performance counters [106, 155, 161]. While hardware performance counters give more precise information as they count given events (e.g., mispredicted branches at decoding, mispredicted branches at execution), they can suffer from non-determinism [53, 169]. Moreover, not all events can be monitored on all platforms, as non-architectural events change across generations. Timing measurements have a very high resolution (usually one CPU cycle) on native environments, using the x86 rdtsc instruction [178], a thread counter [101, 138], or dedicated performance counters [159].

Reverse engineering micro-architectural components is a research direction that I started during my PhD with the reverse-engineering of the last-level cache addressing functions [106]. It was a major axis of my research project application for CNRS, and I have continued to develop it, including with the Ph.D. of Guillaume Didier and through the ANR JCJC MIAOUS project of which I am the PI.

# Outline

Section 2.1 presents the reverse-engineering of DRAM addressing functions and subsequent novel side channel based on DRAM. Section 2.2 presents the reverse-engineering of the AMD L1 cache way predictor, and two novel side channels based on it. Section 2.3 presents a model of the CPU Interconnect that allowed us to refine Flush+Flush cache attacks. Throughout these three examples, I will outline the general method for acquiring measurements required for reverse-engineering and modeling the different components, as well as the security implications of this reverse engineering. Section 2.4 discusses these results.

# 2.1 DRAM addressing

During my postdoc, we were interested in the Rowhammer attack [89] and we quickly discovered differences in timing due to the row buffer in DRAM. We decided to investigate this, and developed DRAMA, short for DRAM Addressing attacks. The work presented hereafter has been published in:

Peter Pessl, Daniel Gruss, Clémentine Maurice, Michael Schwarz, and Stefan Mangard. "DRAMA: Exploiting DRAM Addressing for Cross-CPU Attacks". In: *USENIX Security Symposium*. 2016

Every physical memory location maps to a memory location in one out of many rows in one out of several banks in the DRAM. Considering a single access to a row i in a bank, there are two cases:

**Row hit** The row i is already *cached* in the row buffer. The reason for a *row hit* can be that unrelated code just opened row i in this bank recently or that since our last access to row i in this bank, no other access went to another row in the same bank.

**Row conflict** The row i is *not cached* in the row buffer. A *row conflict* occurs if any other row  $j \neq i$  in the same bank has been opened since the last access to row i.

Considering frequent accesses to two (or more) addresses, we distinguish three cases:

- 1. The addresses map to different banks. In this case, the accesses are independent and whether the addresses have the same row indices has no influence on the timing. Row hits are likely to occur for the accesses, *i.e.*, a low access time.

- 2. The addresses map to the same row i in the same bank. In this case, the accesses are not independent. The accesses are likely to keep the row i open. Thus, row hits are likely to occur for the accesses, i.e., a low access time.

- 3. The addresses map to the different rows  $i \neq j$  in the same bank. In this case, the accesses are again not independent. Each access to an address in row i will close row j and vice versa. Thus, row conflicts occur for the accesses, *i.e.*, a high access time.

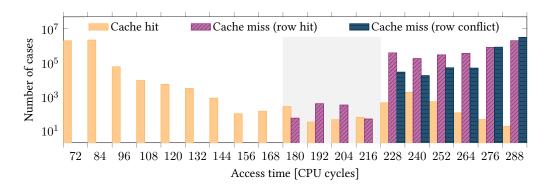

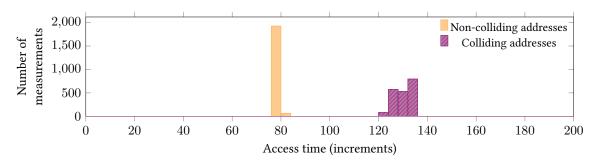

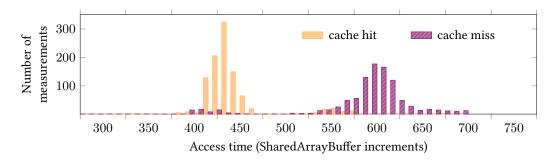

Figure 2.1: Histogram for cache hits and cache misses divided into row hits and row conflicts on an Intel i5-3230M (Ivy Bridge) CPU.

Figure 2.1 shows a comparison of standard histograms of access times for cache hits and cache misses. Cache misses are further divided into row hits and row conflicts. In the remainder, we build different attacks that are based on this timing difference between row hits and row conflicts.

## 2.1.1 Acquiring measurements

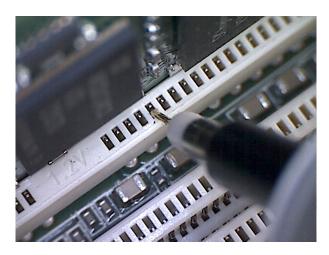

# 2.1.1.1 Physical probing

Our first approach is to physically probe the memory bus and to directly read the control signals. As shown in Figure 2.2, we use the tip of a standard passive probe to establish contact with the pin at the DIMM slot. We then use a high-bandwidth oscilloscope to measure the voltage and deduce the pins logic value. We contact all pins of interest, namely the bank-address bits (BA0, BA1, BA2 for DDR3 and BG0, BG1, BA0, BA1 for DDR4) and the chip select CS. We then record the logic levels on these pins for many randomly selected physical addresses.

This reverse-engineering approach has some drawbacks: 1) Expensive measurement equipment is needed. 2) It requires physical access to the internals of the tested machine. However, its main advantage is that the address mapping can be reconstructed for each signal individually and exactly, *i.e.*, we can determine the exact individual functions for the bus pins.

Figure 2.2: Physical probing of the DIMM slot with a standard passive probe.

# 2.1.1.2 Using row conflicts

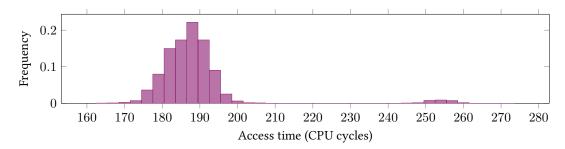

For our second approach, we exploit the fact that row conflicts lead to higher memory access times. We use the resulting timing differences to find sets of addresses that map to the same bank but to a different row. The entire process is fully automated in software and runs without privileges.

We aim to find same-bank addresses in a large array mapped into the attacker's address space. For this purpose, we perform repeated alternating accesses to two addresses and measure the average access time. We use clflush to ensure that each access is served from DRAM and not from the CPU cache. As shown in Figure 2.3, for some address pairs the access time is significantly higher than for most others. These pairs belong to the same bank but to different rows. The alternating accesses cause frequent row conflicts and consequently a high latency. The addresses are subsequently grouped into sets having the same channel, DIMM, rank, and bank.

Figure 2.3: Histogram of average memory access times for random address pairs on an Intel i7-4700 (Haswell) CPU. A clear gap separates the majority of address pairs causing no row conflict (lower access times), because they map to different banks, from the few address pairs causing a row conflict (higher access times), because they map to different rows in the same bank.

# 2.1.2 Modeling DRAM addressing

# 2.1.2.1 Recovering the hash function

The reconstruction of DRAM addressing functions differs depending on the method used for acquiring measurements. In the first case where we acquired measurements with physical probing, for each DRAM addressing bit, we create an over-defined system of linear equations in the physical address bits and then solve this system using linear algebra. The solution is the addressing function for the corresponding DRAM addressing bit.

In the second case where we acquired timing measurements, we use the identified address sets to reconstruct the addressing functions. This reconstruction can either be based on 2 MB, 1 GB pages, or privileged information such as the virtual-to-physical address translation that can be obtained through /proc/pid/pagemap. In the case of 2 MB pages we can recover the partial functions up to bit  $a_{20}$ , as the lowest 21 bit of virtual and physical address are identical. In the case of 1 GB pages we can recover all partial functions up to bit  $a_{30}$ . This is sufficient to recover the full DRAM addressing functions on all our test systems without any privileges.

Similarly to the solving phase of the probing approach, we presume the linearity of the DRAM addressing functions. Bits  $(a_0..a_5)$  are used for addressing within a cache line. Bits  $a_{30}$  and upwards are not used. The search space is then small enough to perform a brute-force search of linear functions within seconds. For this, we generate all linear functions that use exactly n bits as coefficients and then apply them to all addresses in one randomly selected set. We verify the correctness either by comparing it to the results from the physical probing, or by performing a software-based test, *i.e.*, verifying the timing differences on a larger set of addresses.

## 2.1.2.2 **Results**

Table 4.2 in the Appendix shows a comprehensive overview of all platforms and memory configurations we analyzed (Table 4.1 in the Appendix). As all found functions are linear, we simply list the index of the physical address bits that are XORed together.

We can observe that the detailed mapping differs with the memory setup, such as the number of DIMMs (single channel or dual channel) or CPUs. Additionally, changes can appear between different generations of CPUs, e.g., the rank and channel selection functions which are composed of a single bit on Sandy Bridge, and multiple bits from Ivy Bridge and onward. Due to DDR4's introduction of bank grouping and the doubling of the available banks (now 16), the addressing function necessarily changed again. Finally, the mapping used on the mobile platforms we analyzed is much simpler.

## 2.1.3 Security impact

This reverse-engineering work has led to a covert channel and a side-channel attack that leverage row conflicts, dubbed DRAMA (DRAM Attacks). Both these attacks do not require any shared memory, as opposed to the cache attack Flush+Reload. Unlike all cache attacks (except for [82]), their only prerequisite is that the two communicating processes (in the case of the covert channel), or the victim and the attacker (in the case of the side-channel attack), have access to the same memory module, including scenarios where these processes do not share a CPU.

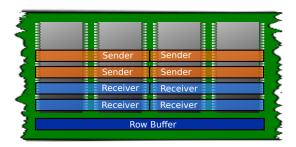

(a) Covert channel scenario. The sender occupies rows in a bank to trigger row conflicts. The receiver occupies rows in the same bank to observe these row conflicts.

(b) Side-channel attack scenario. Victim and spy have memory allocated in the same DRAM row. By accessing this memory, the spy can determine whether the victim just accessed it.

Figure 2.4: Row placement in the cases of covert channel and side-channel attack scenarios.

## 2.1.3.1 Covert channel

We present a first DRAMA attack, namely a high-speed cross-CPU covert channel that does not require shared memory and can operate across CPUs.

**Protocol.** Our covert channel exploits timing differences caused by row conflicts. Figure 2.4a illustrates how rows are occupied by sender and receiver. The receiver process continuously accesses a chosen physical address in the DRAM and measures the average access time over a few accesses. If the sender process now continuously accesses a different address in the same bank but in a different row, a row conflict occurs. This leads to higher average access times in the receiver process. Bits can be transmitted by switching the activity of the sender process in the targeted bank on and off. The receiver process distinguishes the two values based on the mean access time. We assign a logic value of 0 to low access times (inactive sender) and a value of 1 to high access times (active sender).

Each (CPU, channel, DIMM, rank, bank) tuple can be used as a separate transmission channel. However, a high number of parallel channels leads to increased noise. Note that transmission channels are unidirectional, but the direction can be chosen for each one independently, thus, two-way communication is possible.

**Performance Evaluation.** We evaluate the performance of our covert-channel implementation on two systems: 1) a standard desktop PC with an Intel i7-4790 CPU (Haswell) with 2 DDR4 DIMMs, 2) a server system with two Intel Xeon E5-2630 v3 CPUs (Haswell-EP), equipped with 4 DDR4 DIMMs.

In our proof-of-concept implementation, we transmit 8 bits per block using 8 (CPU, channel, DIMM, rank, bank) tuples, and each block is sent and measured for a fixed period. The error rate varies depending on the raw bitrate, which depends on measurement intervals. On our desktop setup, the error probability stays below 1% for bitrates of up to 2 Mbps. The channel capacity reaches up to 2.1 Mbps (raw bitrate of 2.4 Mbps, 1.8% error rate). On our server setup, the maximum capacity is 1.6 Mbps (raw 2.6 Mbps, 8.7% error rate).

We also implemented a transmission in a cross-CPU and cross-VM setup on the server system. We obtain a transmission rate of 596 Kbps at an error rate of 0.4%, without a cross-VM synchronization mechanism. These results are thus far from what can be achieved in practice with synchronization.

#### 2.1.3.2 Side-channel attack

We now present a second DRAMA attack, a side-channel attack that again exploits the row buffer, where the spy and the victim can run on separate CPUs and do not share memory. This side channel achieves a temporal resolution comparable to Flush+Reload and a higher spatial resolution than Prime+Probe. In this side-channel attack, an attacker infers the activity of a victim process by detecting *row hits* and *row conflicts*. The spy and victim need to have access to the same row (Figure 2.4b).

The spy and the victim can share a row without shared memory due to the DRAM addressing functions. The size of a row is typically 8 KB and memory is organized in 4 KB pages. Thus, the physical memory of a row contains the memory of 2 or more pages depending on the DRAM addressing functions. If no DRAM addressing functions use low address bits ( $a_0 - a_{11}$ ), the spatial resolution is 4 KB, which is the worst case. However, if DRAM addressing functions (channel, BG0, CPU, etc.) use low address bits, rows with the same row index in different banks are interleaved in the same memory region. For example, on our Haswell-EP test system, the spatial resolution of our attack is 512 B.

To run the side-channel attack on a private memory address t in a victim process, the attacker allocates a memory address p that maps to the same bank and the same row as the target address t. The attacker also allocates a row conflict address  $\bar{p}$  that maps to the same bank but to a different row. The side-channel attack then works in three steps: 1) Access the row conflict address  $\bar{p}$ , 2) Wait for the victim to compute, 3) Measure the access time on the targeted address p. If the measured timing is below a row-hit threshold (cf. the highlighted "row hit" region in Figure 2.1), the victim has just accessed t or another address in the target row. Thus, we can accurately determine when a specific non-shared memory location is accessed by a process running on another core or CPU.

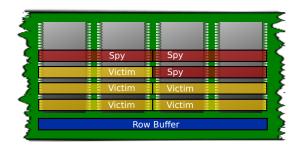

Figure 2.5: Exploitation phase on non-shared memory in a DRAMA template attack on an Intel i5-3230M (Ivy Bridge) CPU with DDR3. A low access time is measured when the user presses a key in the Firefox address bar.

Based on this attack principle, we build a fully automated DRAMA template attack (similarly to [75]). Figure 2.5 shows an access time trace for an address found in this template attack while typing in the Firefox address bar. A low access time is measured for every key the user presses.

# 2.2 AMD cache way predictors

After some investigation of AMD manuals, we decided to study AMD cache way predictors, a component that does not exist in Intel processors and that had not been studied by the security community before. The work presented hereafter has been published in:

Moritz Lipp, Vedad Hadžić, Michael Schwarz, Arthur Perais, Clémentine Maurice, and Daniel Gruss. "Take A Way: Exploring the Security Implications of AMD's Cache Way Predictors". In: *ASIACCS*. 2020

To look up a cache line in a set-associative cache, bits in the address determine in which set the cache line is located. With an n-way cache, n possible entries need to be checked for a tag match. To avoid wasting power for n comparisons leading to a single match, Inoue et al. [81] presented way prediction for set-associative caches. Instead of checking all ways of the cache, a way is predicted, and only this entry is checked for a tag match. If the prediction is correct, the access has been completed, and access times similar to a direct-mapped cache are achieved. If the prediction is incorrect, a normal associative check has to be performed, which increases the latency.

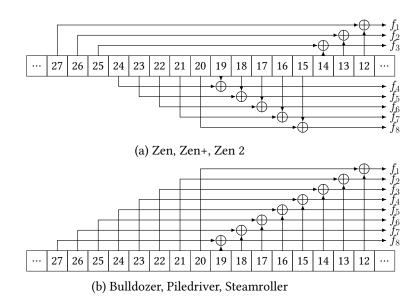

Every cache line in the L1D cache is tagged with a linear-address-based  $\mu$ Tag [16, 64]. This  $\mu$ Tag is computed using an undocumented hash function, which takes the virtual address as input. For every memory load, the way predictor predicts the cache way of every memory load based on this  $\mu$ Tag. As the virtual address, and thus the  $\mu$ Tag, is known before the physical address, the CPU does not have to wait for the TLB lookup. If there is no match for the calculated  $\mu$ Tag, an early miss is detected, and a request to L2 is issued. Figure 2.6 illustrates AMD's way predictor.

Figure 2.6: Simplified illustration of AMD's way predictor.

The AMD's way predictor incurs some timing differences considering the access of two addresses. We distinguish two cases:

- 1. The two addresses yield a conflict in the  $\mu$ Tag table, *i.e.*, they are virtual addresses that yield the same  $\mu$ Tag.

- 2. The two addresses are aliased, *i.e.*, the two different *virtual* addresses map to the same *physical* location.

In both cases, the second load sees an L1D cache miss and thus loads the data from the L2D cache [16].

# 2.2.1 Acquiring measurements

**High-resolution timing.** The attacker requires a method to measure timing differences in the range of a few CPU cycles. The unprivileged rdtsc instruction returning the current cycle count is commonly used for cache attacks on Intel CPUs. Using this instruction, an attacker can get timestamps with a resolution between 1 and 3 cycles. On AMD CPUs, this register has a cycle-accurate resolution until the Zen micro-architecture. Since then, it has a significantly lower resolution as it is only updated every 20 to 35 cycles.

The AMD Ryzen micro-architecture provides the *Actual Performance Frequency Clock Counter* (APERF counter) [15] which can be used to improve the accuracy of the timestamp counter. However, it can only be accessed in kernel mode. Although other timing primitives provided by the kernel, such as get\_monotonic\_time, provide nanosecond resolution, they can be noisier and still not sufficiently accurate to observe timing differences, which are only a few CPU cycles.

Hence, on more recent AMD CPUs, it is necessary to resort to a different method for timing measurements. In an earlier work on ARM-based cache attacks [101], we showed that *counting threads* can be used where unprivileged high-resolution timers are unavailable. A counting thread constantly increments a global variable used as a timestamp without relying on micro-architectural specifics. This is the method that we use throughout this section unless otherwise specified.

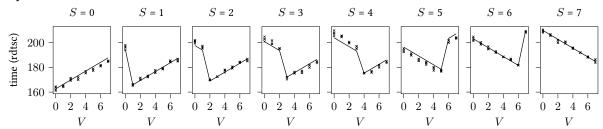

Figure 2.7: Measured duration of 250 alternating accesses to addresses with and without the same  $\mu$ Tag.

$\mu$ Tag collisions. We rely on  $\mu$ Tag collisions to reverse-engineer the hash function. We pick two random virtual addresses that map to the same cache set. If the two addresses have the same  $\mu$ Tag, repeatedly accessing them one after the other results in conflicts. As the data is then loaded from the L2 cache, we can measure an increased access time, as illustrated in Figure 2.7. Another method would be to measure the performance counter for L1 misses.

# 2.2.2 Modeling the cache way predictor

# 2.2.2.1 Recovering the hash function

With the ability to detect conflicts, we can build N sets representing the number of entries in the  $\mu$ Tag table. First, we create a pool v of virtual addresses, which all map to the same cache set, *i.e.*, where bits 6 to 11 of the virtual address are the same. We start with one set  $S_0$  containing one random virtual address out of the pool v. For each other randomly-picked address  $v_x$ , we measure the access time while alternatively accessing  $v_x$  and an address from each set  $S_{0...n}$ . If we encounter a high access

time, we measure conflicts and add  $v_x$  to that set. If  $v_x$  does not conflict with any existing set, we create a new set  $S_{n+1}$  containing  $v_x$ . In our experiments, we recovered 256 sets.

Every virtual address that is in the same set produces the same hash. We assume that this undocumented hash function is linear based on the knowledge of other such hash functions we previously reverse-engineered [106, 122]. Moreover, we expect the size of the  $\mu$ Tag to be a power of 2, resulting in a linear function. To recover the hash function, we need to find which bits in the virtual address are used for the 8 output bits that map to the 256 sets. Due to its linearity, each output bit of the hash function can be expressed as a series of XORs of bits in the virtual address. Hence, we can express the virtual addresses as an over-determined linear equation system. The solutions of the equation system are then linear functions that produce the  $\mu$ Tag from the virtual address.

While the least-significant bits 0-5 define the cache line offset, note that bits 6-11 determine the cache set and are not used for the  $\mu$ Tag computation [16]. To solve the equation system, we used the Z3 SMT solver. Every solution vector represents a function that XORs the virtual-address bits that correspond to '1'-bits in the solution vector. The hash function is the set of linearly independent functions, *i.e.*, every linearly independent function yields one bit of the hash function. The order of the bits cannot be recovered. However, this is not relevant for using the hash function, as we are only interested in whether addresses collide, not in their numeric  $\mu$ Tag value.

#### 2.2.2.2 **Results**

Figure 4.1 in the Appendix illustrates the recovered  $\mu$ Tag hash functions on the AMD Zen, Zen+, Zen 2, Bulldozer, Piledriver, and Steamroller micro-architectures listed in Table 4.3 in the Appendix. The function illustrated in Figure 4.1a for Zen, Zen+, and Zen 2 micro-architectures uses bits 12 to 27 to produce an 8-bit value mapping to one of the 256 sets. For the Bulldozer, Piledriver, and Steamroller micro-architectures, the hash function uses the same bits but in a different combination as illustrated in Figure 4.1b.

## 2.2.3 Security impact

This reverse-engineering work has led to two novel side channels that leverage AMD's L1D cache way predictor. With Collide+Probe, we monitor memory accesses of a victim's process without requiring the knowledge of physical addresses. With Load+Reload, while relying on shared memory similarly to Flush+Reload, we can monitor memory accesses of a victim's process running on the sibling hardware thread without invalidating the targeted cache line from the entire cache hierarchy.

## 2.2.3.1 Collide+Probe

Collide+Probe exploits  $\mu$ Tag collisions in AMD's L1D cache way predictor, *i.e.*, addresses that have the same  $\mu$ Tag. As we described previously, the way predictor uses virtual-address-based  $\mu$ Tags to predict the L1D cache way. If an address is accessed, the  $\mu$ Tag is computed, and the way-predictor entry for this  $\mu$ Tag is updated. If a subsequent access to a different address with the same  $\mu$ Tag is performed, a  $\mu$ Tag collision occurs, and the data has to be loaded from the L2D cache, increasing the access time. We exploit this timing difference to monitor accesses to such colliding addresses.

**Threat model.** For this attack, we assume that the attacker has unprivileged native code execution on the target machine and runs on the same logical CPU core as the victim. Furthermore, the attacker can force the execution of the victim's code, e.g., via a function call in a library or a system call.

**Attack.** The attacker first chooses a virtual address v of the victim that should be monitored for access. To mount a Collide+Probe attack, the attacker selects a virtual address v' in its own address space that yields the same  $\mu$ Tag  $\mu_{v'}$  as the target address v, i.e.,  $\mu_v = \mu_{v'}$ . Moreover, both v and v' have to be in the same cache set. The attack consists of three phases performed repeatedly:

**Phase 1: Collide.** The attacker accesses the pre-computed address v' and, thus, updates the way predictor. The way predictor associates the cache line of v' with its  $\mu \text{Tag } \mu_{v'}$  and subsequent memory accesses with the same  $\mu \text{Tag}$  are predicted to be in the same cache way. Since the victim's address v has the same  $\mu \text{Tag}$  ( $\mu_v = \mu_{v'}$ ), the  $\mu \text{Tag}$  of that cache line is marked invalid and the data is effectively inaccessible from the L1D cache.

**Phase 2: Scheduling the victim.** The victim is scheduled to perform its operations.

**Phase 3: Probe.** The attacker measures the access time to the pre-computed address v'. If the victim has not accessed the monitored address v, the data of the pre-computed address v' is still accessible from the L1D cache and the way prediction is correct. Thus, the measured access time is fast. If the victim has accessed the monitored address v and thus changed the state of the way predictor, the attacker suffers an L1D cache miss when accessing v', as the prediction is now incorrect. The data of the pre-computed address v' is loaded from the L2 cache and, thus, the measured access time is slow. By distinguishing between these cases, the attacker can deduce whether the victim has accessed the targeted data.

## 2.2.3.2 Load+Reload

Load+Reload exploits the way predictor's behavior for aliased addresses, *i.e.*, virtual addresses mapping to the same physical address. When accessing data through a virtual address alias, the data is always requested from the L2 cache instead of the L1D cache [16]. Consequently, this allows one thread to evict shared data used by the sibling thread with a single load. Although the requested data is stored in the L1D cache, it remains inaccessible for the other thread and, thus, introduces a timing difference when it is accessed.

**Threat model.** For this attack, we assume that the attacker has unprivileged native code execution on the target machine. The attacker and victim run simultaneously on the same physical but different logical CPU thread. The attack target is a memory location with a virtual address v shared between the attacker and victim, e.g., a shared library.

**Attack.** Load+Reload exploits the timing difference when accessing a virtual-address alias v' to build a cross-thread attack on shared memory. The attack consists of 3 phases:

**Phase 1: Load.** In contrast to Flush+Reload, where the targeted address v is flushed from the cache hierarchy, Load+Reload loads an address v' with the same physical tag as v in the first phase. Thereby, it renders the cache line containing v inaccessible from the L1D cache for the sibling thread.

**Phase 2: Scheduling the victim.** The victim process is scheduled. If the victim process accesses the targeted cache line with address v, it sees an L1D cache miss. As a result, it loads the data from the L2 cache, invalidating the attacker's cache line with address v' in the process.

**Phase 3: Reload.** The attacker measures the access time to the address v'. If the victim process has accessed the cache line with address v, the attacker observes an L1D cache miss and loads the data from the L2 cache, resulting in a higher access time. Otherwise, if the victim has not accessed the cache line with address v, it is still accessible in the L1D cache for the attacker and, thus, a lower access time

is measured. By distinguishing between both cases, the attacker can deduce whether the victim has accessed the address v.

## 2.2.3.3 Case study: covert channel

As many other cache side channels, Collide+Probe and Load+Reload can be used in different attack scenarios: 1) a covert channel between two processes to leak arbitrary data, and to leak secret data from the kernel in a Spectre attack; 2) reducing the entropy of kernel ASLR, user space ASLR, and hypervisor ALSR in a virtual machine setting; 3) a side-channel attack on a weak cryptographic implementation, e.g., the AES T-tables implementation. In this manuscript, we only detail the covert channel which uses Collide+Probe, and refer to the paper [102] for the other attack scenarios.

**Protocol.** For the most simplistic form of the covert channel, two processes agree on a  $\mu$ Tag and a cache set. These two processes must reside in the same logical core. In the initialization phase, both parties allocate their own page. The sender chooses a virtual address  $v_S$ , and the receiver chooses a virtual address  $v_S$  such that  $v_S$  and  $v_R$  are in the same cache set and yield the same  $\mu$ Tag.

To encode a 1-bit to transmit, the sender accesses address  $v_S$ . To transmit a 0-bit, the sender does not access address  $v_S$ . The receiving end decodes the transmitted information by measuring the access time when loading address  $v_R$ . If the sender has accessed address  $v_S$  to transmit a 1, the collision caused by the same  $\mu$ Tag of  $v_S$  and  $v_R$  results in a slow access time for the receiver. If the sender has not accessed address  $v_S$ , no collision caused the address  $v_R$  to be evicted from L1D and, thus, the access time is fast. This timing difference allows the receiver to decode the transmitted bit.

We extend this simple covert channel to transmit multiple bits in parallel by utilizing multiple cache sets. Instead of decoding the transmitted bit based on the timing difference of one address, we use two addresses in two cache sets for every bit we transmit: one to represent a 1-bit and the other to represent the 0-bit. As the L1D has 64 cache sets, we can transmit up to 32 bits in parallel without reusing cache sets.

**Performance evaluation.** We evaluate the transmission and error rate of our covert channel in a local setting and a cloud setting. We achieve a maximum transmission rate of 588.9 kBps using 80 channels in parallel on the AMD Ryzen Threadripper 1920X. On the AMD EPYC 7571 in the Amazon EC2 cloud, we achieve a maximum transmission rate of 544.0 kBps also using 80 channels. In contrast, L1 Prime+Probe achieves a transmission rate of 400 kBps [120] and Flush+Flush 496 kB/s [74]. The mean transmission rate increases with the number of bits sent in parallel. However, the error rate increases drastically when transmitting more than 64 bits in parallel.

As accesses to unrelated addresses with the same  $\mu$ Tag as our covert channel introduce noise in our measurements, we use error correction to achieve better transmission. We evaluate different hamming codes on an AMD Ryzen Threadripper 1920X. While the H(7,4) code is slightly more robust [77], the H(15,11) code achieves a better transmission rate of 452.2 kBps.

## 2.3 Intel CPU interconnect

Our work on the Intel CPU interconnect started serendipitously while trying to reverse-engineer another component: the hardware prefetcher. This work is part of Guillaume Didier's PhD, and has been published in:

Guillaume Didier and Clémentine Maurice. "Calibration Done Right: Noiseless Flush+Flush Attacks". In: *DIMVA*. 2021

Several cache attack primitives exist with different requirements and trade-offs. Flush+Flush [73], on which I worked during my postdoc, is a stealthy and fast one using the timing of the clflush instruction which depends on whether a line is cached. However, one aspect that has been overlooked for this attack is the choice of the threshold to distinguish between a flush hit (slower) and a flush miss (faster). This threshold is crucial to avoid noise. When looking at the timings for a single address and on a single run, it appears that there is a good separation between the hits and the misses. However, from one run to another, the exact threshold may change, even with a fixed frequency. The threshold also different addresses.

We hypothesize that the variability is due to the complex topology of sliced caches, and that accounting for these sources of variability improves significantly the quality of the channel, especially as the number of cores grows. Our experiments show that ignoring CPU topology can result in very poor error rates, e.g., in some cases up to 45% error rate. In the remainder of the section, we show that taking into account the topology and slices to compute tailored thresholds allows us to build a side channel with an error rate well under 0.01%. Flush+Flush is, therefore, contrary to what was thought before, not a noisy attack when crafted carefully.

# 2.3.1 Acquiring measurements

**Setup.** We run experiments on two single-socket systems: 1) *4-core machine*: a machine with an Intel Core i5-8365U CPU (Whiskey Lake, 4 cores, 8 threads), 2) *8-core machine*: a machine with an Intel Core i9-9900 CPU (Coffee Lake, 8 cores, 16 threads).

We enable hyper-threading, but disable turbo boost on those machines. The intel\_pstate driver is set to performance mode on all cores, to stabilize the core frequencies.

**Measurements.** We investigate the factors that influence the execution time of clflush to improve the Flush+Flush attack, and propose a mathematical model with an associated ring topology. The only information we have from the Intel documentation is that the interconnect is a "bidirectional ring".

A clflush miss occurs when a cache line is not validly cached, which corresponds to a line in the I state. A line that has just been flushed is in the I state — the cache may have an entry in the I state or no entry at all, but it is equivalent at the cache coherency protocol level. A clflush hit occurs when the line is in any valid state. In practice, in a Flush+Flush attack, the cache line of interest transitions from an I to an E state when the single victim core loads the line that has just been flushed. Therefore, the two relevant timings are clflush of a line in the E state for a hit, and in the I state for a miss. We study these timings depending on three parameters:

- 1. A: the attacker core that executes clflush on an address,

- 2. *V*: the victim core that accesses the address and caches it in its L1 or L2,

- 3. S: the core that contains the last-level cache slice that this address maps to.

# 2.3.2 Modeling the CPU interconnect

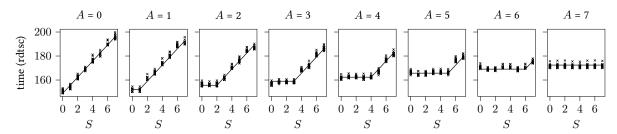

(a) For a cache line in the I state, depending on its slice S for each attacker core A. Victim logic core has no impact on a miss.

(b) For a cache line in the E state, depending on the victim core V for each slice S, using a fixed attacker core (A=0).

Figure 2.8: Median timings of clflush on the 8-core machine depending on the victim core V, the slice S, and the attacker A, along with the fitted model according to our proposed topology.

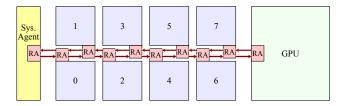

**Topology.** For each attacker core, Figure 2.8a shows the time it takes to execute a clflush instruction on a cache line in the I state, depending on the slice. The first finding is that all 8 cores have a distinct timing pattern, which implies that the ring has no symmetry. For each attacker, we notice that slices with a lower core number than the attacker all have the same timing, while for slices with a higher number the time increases with the distance between the attacker and the slice. Such a pattern only makes sense if the nodes are aligned linearly, and if the attacker sends a message to the slice, which then sends a message to the system agent, and then back to the slice, and finally to the attacker. Consequently, the miss time is more variable for attackers closer to the system agent than for one further away.

Figure 2.8b shows the time it takes to execute a clflush instruction on a cache line in the E state. Here, we notice an asymmetry in the core, which can be explained if the recall request is always sent by the slice in the same direction without knowing in which core the line is cached.

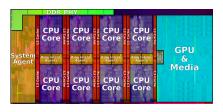

Given that the topology is described as a ring, given the die shot in Figure 2.9a and our results, we propose the topology in Figure 2.9b, with 8 cores aligned in a linear graph with forward and backward links. For a 4-core machine, similar measurements lead to a similar topology with only cores 0-3.

**Mathematical model.** The above timing measurements can be interpreted within the proposed topology as follows, leading to a mathematical model that can be fitted and compared with the measurements. Misses result in a request to be sent on the ring from the core requesting the flush to the slice, which then sends a message to the memory, and then answers the same path in reverse, using

- (a) Intel Coffee Lake 8-core die shot.

- (b) Proposed i9-9900/8-core topology.

Figure 2.9: Core i9-9900 die shot and topology.

each time the shortest path. The eviction time in state I,  $t_I(A, S)$  is thus:

$$t_I(A, S) = C + h \times |A - S| + h \times |S - M|,$$

in which:

- ► *C* is a constant base timing,

- $\blacktriangleright$  h is a constant corresponding to the time a round-trip hop on the ring takes,

- $\blacktriangleright$  M corresponds to the system agent location, which is -1.

Upon receipt of a request to flush a line in the E state, the slice sends a single message along the ring, in one privileged direction. For core numbered from 0 to  $\frac{n_{core}}{2}$  included, this is towards the higher numbered cores (and the GPU), otherwise, it is towards the lower numbered cores. This message is passed around the ring until the victim core V that has the line cached in its lower level cache (L1/L2) receives it. If the core is not in the initial direction, the message will follow the ring back in the other direction until it reaches the victim core. The victim core then discards the line, which is clean, and sends a reply to the slice, along the shortest path. The eviction time in state E,  $t_E(A,S,V)$  is thus:

$$t_E(A,V,S) = \begin{cases} C' + h \times |A-S| + h \times |R-(V-M)| & \text{if } S \leqslant \frac{N}{2} \text{ and } V < S \\ C' + h \times |A-S| + h \times |S-V| & \text{if } S \leqslant \frac{N}{2} \text{ and } V \geqslant S \\ C' + h \times |A-S| + h \times |S-V| & \text{if } S > \frac{N}{2} \text{ and } V \leqslant S \\ C' + h \times |A-S| + h \times |M-V| & \text{if } S > \frac{N}{2} \text{ and } V \leqslant S, \end{cases}$$

where:

- ightharpoonup C' is a different base time constant,

- $\blacktriangleright$  h is a constant corresponding to the time a round-trip hop on the ring takes,

- $\triangleright$  N is the number of cores,

- ▶ R is the ring diameter in hops, corresponding to how many hops there are between the system agent and the GPU, and thus, in our case, R = N + 1.

In addition to our measurements, Figure 2.8a and Figure 2.8b present the fitted model for the 8-core machine, which appears to explain the behavior consistently.

**Summary.** We have uncovered that while CPUs appeared to be arranged symmetrically in Intel's bidirectional ring, they are in fact aligned one after the other in a linear graph, with the system agent at an end and the GPU at the other end. First, the clflush instruction timing is always influenced by the distance between the core requesting the flush and the slice where the address lives in the last-level

cache. Second, in the I state the timing will depend on the distance between the slice and the system agent, whereas in the E state, it will depend on how long a message sent along the ring will need to reach the core that currently has the line, and then go back to the slice. These findings are consistent with the concurrent work of Paccagnella et al. [118].

# 2.3.3 Security impact

This reverse-engineering work leads to the improvement of the error rate in the Flush+Flush [74] side channel. The attack setup is therefore the same as with Flush+Flush: the attacker needs to be co-located to the same CPU as the victim to share the last-level cache, and relies on shared memory with the victim (e.g., a shared library or memory deduplication). The attacker can then carry on a side-channel attack on a vulnerable implementation, or a covert channel between two parties they control.

**Attacker model.** We define different attacker models depending on attacker capabilities.

- ▶ Global Threshold (GT): The simplest model, using a single threshold that minimizes the average error rate over all triples of attacker, victim, and slice. This is a topology-oblivious attacker, as in the initial Flush+Flush attack.

- ▶ Best A, Known V: The attacker knows on which core the victim is running and chooses the attacker core it runs on. The attacker computes a single threshold for all addresses, therefore ignoring the impact of cache slices.

- $\blacktriangleright$  Best AV: The attacker can pick the cores both the victim and the attacker are running on, e.g., in the case of a covert channel or a side-channel attack in which the attacker launches the victim process. It ignores the impact of slices.

- ▶  $Known \ \ddot{S}$ : The attacker does not know on which core they or their victim runs, but takes into account the slices, using per-slice thresholds. We use this model for comparison with the GT model.

- ▶ Best A,  $Known \, \tilde{S}V$ : The attacker pins their process to the best core, knows the victim core and takes into account the slices. This is a realistic attacker model. To be compared with Best A,  $Known \, V$  model.

- ▶ Best AV,  $Known \tilde{S}$ : This is the most powerful side-channel attacker, that can pin both the attacker and victim.

- ▶ Best  $AV\tilde{S}$ : This is the best covert channel attack model, where the attacker chooses the cores and an address in a slice that yields the best results.

**Experimental results on error rate.** We measure the error rate that can be achieved for each triple consisting of an attacker core, a victim core, and a slice. For each  $(A,V,\tilde{S})$  we make  $2^{20}$  measurements,  $2^{19}$  hits (in E state), and  $2^{19}$  misses (in I state). From these distributions, we evaluate the number of hits and misses that would be correctly or incorrectly classified using a threshold, and determine thresholds that minimize the average error rate for each model, along with the corresponding average error rate.

Table 2.1 shows the error rates for the 4-core and 8-core machines, indicating for A,V and  $\tilde{S}$  whether they are unknown, known, or chosen in each case. For the 8-core machine, we observe a staggering difference between the 25% error rate of the GT attacker model, to the close to 0% error rate of the  $Best~AV\tilde{S}$  model.

|                               | 4-core ma             | 4-core machine |   |                     |                 | 8-core machine |   |                       |  |

|-------------------------------|-----------------------|----------------|---|---------------------|-----------------|----------------|---|-----------------------|--|

|                               | Error rate            | $\overline{A}$ | V | $\tilde{\tilde{S}}$ | Error rate      | $\overline{A}$ | V | $\overline{	ilde{S}}$ |  |

| GT                            | 14.0%                 | U              | U | U                   | 25.1%           | U              | U | U                     |  |

| Best $A$ , Known $V$          | 6.07%                 | 3              | K | U                   | 10.5%           | 7              | K | U                     |  |

| Best $AV$                     | 0.176%                | 7              | 0 | U                   | 0.115%          | 7              | 8 | U                     |  |

| Known $\tilde{S}$             | 11.6%                 | U              | U | K                   | 22.8%           | U              | U | K                     |  |

| Best $A$ , Known $\tilde{S}V$ | 3.16%                 | 5              | K | K                   | 7.18%           | 7              | K | K                     |  |

| Best $AV$ , Known $\tilde{S}$ | 0.103%                | 7              | 0 | K                   | 0.0174%         | 1              | 0 | K                     |  |

| Best $AV\tilde{S}$            | $4.96\times10^{-3}\%$ | 3              | 3 | 3                   | $0 (< 2^{-20})$ | 2              | 7 | 14                    |  |

Table 2.1: Results for each attacker model. "U" means Unknown, and "K" Known.

**Covert channel.** We implement a framework to benchmark covert channel ideal bandwidth with different primitives. Table 2.2 shows that our carefully calibrated Flush+Flush yields a threefold increase in bandwidth on both machines compared to the naive Flush+Flush, and provides a bandwidth higher than Flush+Reload by 3 to 4 %.

Table 2.2: Covert channel benchmarking.

|                       | 4-core machine |             |           | 8-core machine |             |           |  |

|-----------------------|----------------|-------------|-----------|----------------|-------------|-----------|--|

| Channel               | Capacity       | Bit rate    | Err. rate | Capacity       | Bit rate    | Err. rate |  |

| Naive Flush+Flush     | 1.01 Mbitps    | 2.96 Mbitps | 20%       | 1.88 Mbitps    | 5.89 Mbitps | 23%       |  |

| Optimized Flush+Flush | 2.99 Mbitps    | 3.03 Mbitps | 0.1%      | 5.81 Mbitps    | 5.81 Mbitps | 0.005%    |  |

| Flush+Reload          | 2.88 Mbitps    | 2.91 Mbitps | 0.1%      | 5.57 Mbitps    | 5.57 Mbitps | 0.0005%   |  |

**Side-channel attack on AES.** As the AES T-tables implementation is well-known to be vulnerable to side-channel attacks, we use it as a benchmark to compare our Flush+Flush implementation to the naive version of Flush+Flush and to the Flush+Reload attack.

A naive Flush+Flush attack will show some lines with all hits or all misses, due to the threshold depending on the slice. Using a per-slice threshold allows us to achieve an accuracy similar to Flush+Reload. Again, accounting for the contribution of slices and CPU interconnect to clflush timing variations makes an optimized Flush+Flush channel competitive with Flush+Reload, and improves the reliability over naive Flush+Flush. We refer to the paper [54] for more details about the side-channel attack on AES T-tables implementation.

**Summary.** Choosing the attacker and victim locations significantly improves the accuracy over the very unreliable global threshold. On top of that, using a per-slice threshold provides a further boost. However, when the victim cannot be chosen, accounting for slices gives a much greater boost. Lastly, choosing the best combination of attacker, victim, and slice gives close-to-perfect error rates. We conclude that Flush+Flush with careful calibration is a compelling alternative to Flush+Reload.

## 2.4 Discussion

These works were focused on uncovering the hidden part of the iceberg that is the side-channel attack surface of modern CPUs – beyond caches and branch predictors. In all cases, we required a first phase of reverse engineering to fully understand how a particular micro-architectural component works before being able to attack it. While some people find it ingrate work, as manufacturers indeed possess the blueprints for these components that are just undocumented to the public, I believe that this is important work. Indeed, much like software obfuscation does not resist a sufficiently motivated attacker in most cases, these works (and their associated related work) show that a sufficiently motivated researcher is indeed able to reverse-engineer components — if not always precisely, at least adequately to obtain a model that allows novel or improved attacks.

## **X** Limitations

A striking limitation of these works, also applicable to most — if not all — related work, is that the reverse-engineering phase relies on a lot of manual work. While we strive to automate the process as much as possible, the very first parts of the research process, *i.e.*, how to choose the component to study, and how to acquire measurements, require expertise and manual intervention. A related concern is that, as CPUs become more and more efficient, either new components emerge, or known components are modified by manufacturers. These changes occur at a very fast pace, as new CPU generations are devised every year. This means that the attack surface may change every year as well, with the risk of rendering obsolete the research done on older components. A research direction that is orthogonal to this is the automated discovery of side channels [160, 170].

A second limitation, also applicable to related work, is that we establish covert channels to evaluate the reverse-engineering: they are a proof-of-concept that, by design, corroborates the correctness of the reverse-engineering. The main limitation concerns comparisons between covert channels from one paper to another. As they are mainly proofs-of-concept, the protocols are always ad-hoc and change from one paper to another. The creation of a standard benchmark for covert channels would help establish a fair comparison.

# Chapter 3

# Tu quoque, my browser

In which we show that web browsers are not spared by side channels.

Micro-architectural attacks are usually demonstrated in native environments, and written in low-level languages like C (often helped with inline assembly), considering that they require great control of micro-architectural components. Porting such attacks to browsers is not trivial, as several layers of abstraction separate scripts running on browsers from hardware components.

However, fundamentally, side-channel attacks only require benign actions. Indeed, all of them require a timer, and cache attacks, for example, require accessing precise regions of memory. While JavaScript executes in a strict sandbox and hides the notion of addresses and pointers, these two pre-requisites can be fulfilled, therefore allowing side-channel attacks in browsers. The first microarchitectural attack in JavaScript was shown by Oren et al. [115] in 2015, where they demonstrated a cache attack in JavaScript.

Since then, the landscape of browsers changed a lot, including in reaction to micro-architectural attacks. In this chapter, we delve into these changes and their consequences in terms of security.

# Outline

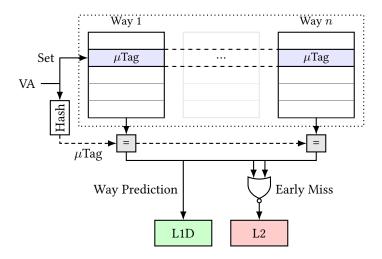

Section 3.1 presents our results on browser timers. We first investigate the (in)security of resolution clamping. We show that it is, in practice, possible to retrieve a nano-second resolution from browser vendors that clamped their timers to 5  $\mu$ s (e.g., Chrome and Firefox) or even 100 ms (e.g., Tor Browser). We then study the evolution of JavaScript's timers in browsers and their multiple changes in the last few years, and seek to evaluate their security. Section 3.2 presents a novel side-channel attack in browsers, using port contention. Section 3.3 discusses these results.

# 3.1 Timing is everything

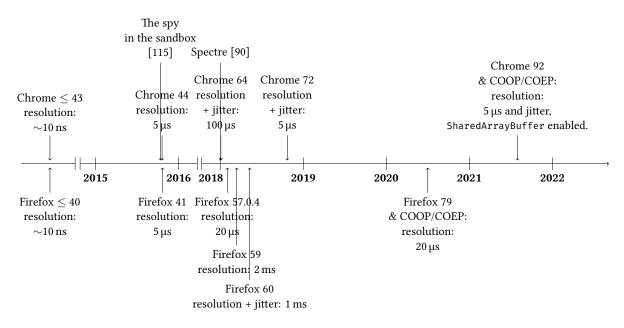

In response to Oren et al. cache attack, the W3C [162] and browser vendors [43, 13, 28] have clamped the performance.now() method to a resolution of  $5\,\mu s$ . The timestamps in the Tor browser had been even more coarse-grained, at  $100\,m s$  [108]. The rationale is simple: a timer that is clamped to  $5\,\mu s$  will output 0 to any measurement below  $5\,\mu s$ , and, in effect, does not allow differentiating between cache

hits and cache misses, which would require a resolution of 10-100 ns<sup>1</sup>.

Timers are the main, if not the only, variable over which browser vendors have some control when it comes to side-channel mitigation. It is therefore unsurprising that most countermeasures were developed from this angle.

# 3.1.1 (In)security of resolution clamping

During my postdoc, we sought to evaluate the security of resolution clamping and its impact on sidechannel attacks in browsers. The work presented hereafter has been published in:

Michael Schwarz, Clémentine Maurice, Daniel Gruss, and Stefan Mangard. "Fantastic timers and where to find them: High-resolution microarchitectural attacks in javascript". In: *International Conference on Financial Cryptography and Data Security (FC)*. 2017

We demonstrate that reducing the resolution of timing information or even removing these interfaces is completely insufficient as an attack mitigation. We propose several new mechanisms to obtain absolute and relative timestamps. We evaluated 10 different mechanisms on the most recent versions, at the time of writing, of 4 different browsers: Chrome, Firefox, Edge, as well as the Tor browser, which took even more drastic measures. We show that all browsers leak highly accurate timing information that exceeds the resolution of official timing sources by 3 to 4 orders of magnitude on all browsers, and by 8 on the Tor browser. In all cases, the resolution is sufficient to revive the attacks that were thought mitigated.

Our main insight is that there are two ways of recovering a high-resolution timer on a browser that clamped timer resolution:

- 1. Recovering a high resolution from the provided High Resolution Time API, *i.e.*, performance. now().

- 2. Creating alternative timing primitives, *implicit* timers, from scratch, using the browser API.

## 3.1.1.1 Recovering a high resolution from performance.now()

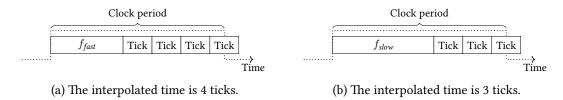

It has already been observed that it is possible to recover a high resolution by observing the clock edges [105, 144, 157, 92]. We systematize these observations and derive two methods to recover a high resolution from performance.now().

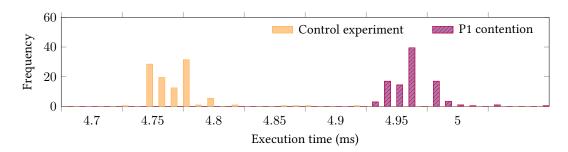

Figure 3.1: Clock interpolation: Counting the number of ticks between the end of the function to measure and the end of the clock period.