## Microarchitectures for Robust and Efficient Incremental Backup in Intermittently-Powered Systems

Davide Pala

#### ▶ To cite this version:

Davide Pala. Microarchitectures for Robust and Efficient Incremental Backup in Intermittently-Powered Systems. Embedded Systems. Université de Rennes 1, 2022. English. NNT: . tel-03885206

## HAL Id: tel-03885206 https://inria.hal.science/tel-03885206

Submitted on 5 Dec 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE

## L'UNIVERSITÉ DE RENNES 1

ÉCOLE DOCTORALE Nº 601

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: Informatique

Par

## **Davide PALA**

# Microarchitectures for Robust and Efficient Incremental Backup in Intermittently Powered Systems

Thèse présentée et soutenue à Rennes, le 10 novembre 2022 Unité de recherche : Inria/IRISA

#### Rapporteurs avant soutenance:

Abdoulaye Gamatié Directeur de Recherche, CNRS, LIRMM, Montpellier

Tanguy Risset Professeur, INSA Lyon, CITI

#### **Composition du Jury:**

Président : Daniel Etiemble Professeur, Université Paris-Saclay, LRI

Examinateurs : Abdoulaye Gamatié Directeur de Recherche, CNRS, LIRMM, Montpellier

Tanguy Risset Professeur, INSA Lyon, CITI

Maria Méndez Real Maitre de Conférences, Polytech Université de Nantes, IETR

Daniel Etiemble Professeur, Université Paris-Saclay, LRI

Dir. de thèse : Olivier Sentieys Professeur, Université de Rennes, Inria, IRISA Co-dir. de thèse : Ivan Miro-Panades Ingénieur-Chercheur, CEA-List, Grenoble

#### Invité:

Erven Rohou Directeur de Recherche, Inria, IRISA, Rennes

## RÉSUMÉ DE LA THÈSE

L'explosion de l'Internet des objets (IoT), des nœuds de capteurs sans fil et des appareils portables a suscité un intérêt accru pour la récupération d'énergie en tant que source d'alimentation de ces appareils. Beaucoup de ces systèmes ne peuvent pas se permettre la présence d'une batterie pour alimenter l'application. Cela peut être dû à des exigences strictes en matière de coût, de taille et/ou de poids du système. De plus, l'utilisation d'une batterie pour les appareils dont la durée de vie est longue peut être difficile car les batteries ont généralement une courte durée de vie et doivent être remplacées fréquemment, ce qui rend l'entretien et la maintenance de l'appareil coûteux, en particulier lorsque ces systèmes sont utilisés dans des endroits éloignés. Dans ces cas, la récupération de l'énergie de l'environnement peut être une alternative viable pour alimenter ces systèmes.

L'inconvénient fondamental de l'utilisation de l'énergie extraite de l'environnement pour alimenter un système est que l'énergie est souvent limitée et sporadique. Cela implique que les appareils connaîtront des pannes de courant imprévisibles pendant qu'ils remplissent leur fonction. Le désir de continuer à calculer tout en utilisant une alimentation intermittente a accru l'intérêt pour les ordinateurs non volatils, en particulier les processeurs non volatils (NVP). Les ordinateurs non volatils peuvent être définis comme suit :

#### ordinateurs non volatils ou Non-Volatile Computers

"systèmes qui peuvent presque instantanément sauvegarder leur état de manière non volatile afin que le fonctionnement puisse continuer même en cas d'interruption de courant imprévue" [Yu+11]

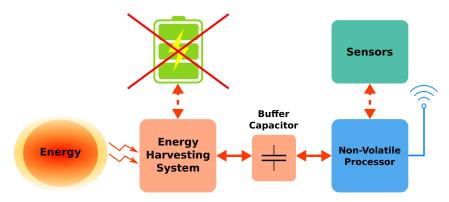

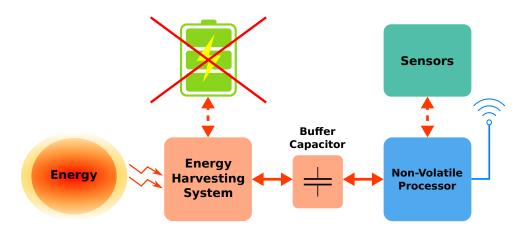

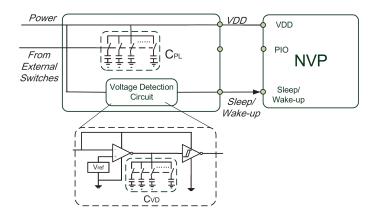

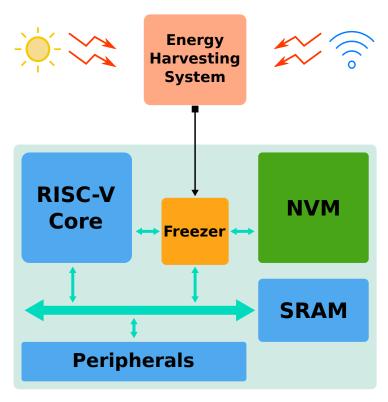

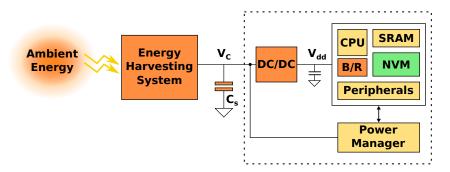

La Figure 1 montre l'architecture système d'un appareil typique alimenté par intermittence et sans batterie. Comme le montre la Figure 1, ces systèmes sont généralement construits autour des éléments de base ci-dessous : 1) Le système de récupération d'énergie, qui puise l'énergie de l'environnement et la fournit aux autres composants du système.

2) Un condensateur tampon est utilisé pour stocker une petite quantité d'énergie, afin de permettre au système de continuer à fonctionner et de sauvegarder son état, lorsque le

FIGURE 1 – Architecture de haut niveau d'un dispositif sans batterie, alimenté par intermittence.

système de récupération est incapable de fournir de l'énergie. La tension aux bornes du condensateur tampon est fréquemment utilisée pour évaluer la « disponibilité » de l'énergie et pour identifier le moment où une perte de puissance est sur le point de se produire. La perte de puissance est généralement identifiée par la tension aux bornes du condensateur tampon tombant en dessous d'un seuil prédéterminé. 3) Le processeur non volatil (NVP), qui est le système informatique principal, généralement connecté à certains capteurs et à une connectivité réseau via des appareils radio à faible puissance.

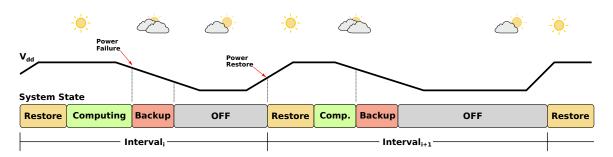

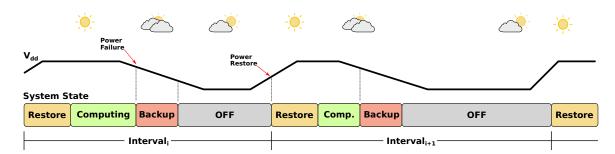

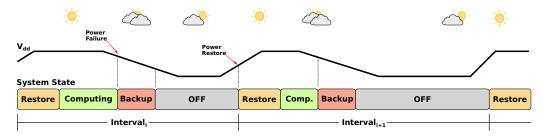

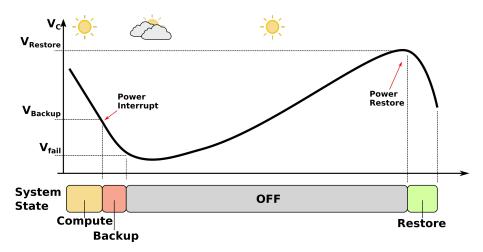

La figure 2 montre un exemple d'exécution intermittente, où l'exécution est interrompue par des coupures de courant, représentées par des chutes de tension et divisées en intervalles. Le calcul intermittent est donc une séquence de quatre états d'un appareil : éteint (power-off), restauration (restore), calcul (compute) et sauvegarde (backup). Afin de préserver la progression de l'exécution du système en cas de panne de courant et d'éviter de redémarrer depuis le début (ou de rebooter le système), le NVP doit effectuer une sauvegarde de l'état du système avant que l'alimentation ne soit complètement coupée et que l'appareil soit éteint. Lorsqu'il y a assez d'énergie pour continuer l'exécution, l'état précédent est restauré.

Un autre problème des appareils alimentés par intermittence est de maintenir l'état non volatil cohérent. Des problèmes de cohérence surviennent lorsque, après une sauvegarde, la mémoire non volatile (NVM) est modifiée et que l'alimentation est coupée avant qu'une nouvelle sauvegarde ne soit exécutée. Ce type d'erreur inclut également les erreurs dues à une interruption soudaine pendant le processus de sauvegarde, qui laissent l'état de sauvegarde dans la NVM inachevé. De nombreuses solutions dans l'état de l'art, et en

FIGURE 2 – Exemple de calcul en présence d'alimentation intermittente.

particulier de nombreux processeurs entièrement non volatils, n'offrent aucune détection ou protection contre les erreurs de sauvegarde ou les erreurs d'incohérence. Certaines solutions sont capables de détecter ces erreurs, mais ne peuvent pas récupérer et nécessitent un redémarrage de l'application.

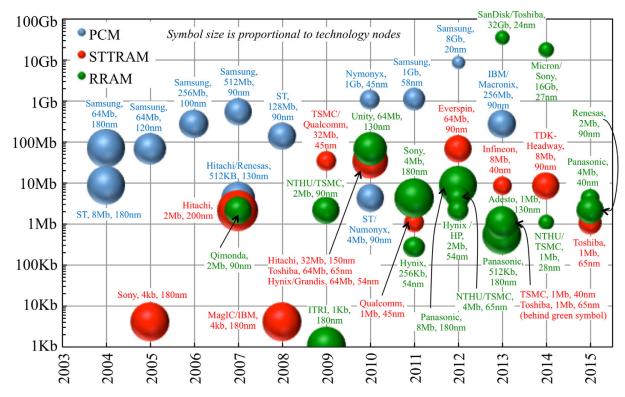

Ce travail introduit d'abord les technologies de mémoire non volatile (NVM). Le fonctionnement de base de ces NVM est décrit en général, et les avantages et les limites de chaque technologie sont mis en évidence. Ensuite, en utilisant les informations recueillies à partir de diverses revues de la littérature, nous donnons une comparaison entre les différentes types et technologies de NVM et d'autres technologies de mémoire comme SRAM, DRAM et FLASH.

Dans cette thèse, nous décrivons des méthodes qui s'appuient sur un contrôleur matériel dédié pour permettre une informatique alimentée de manière transitoire avec des sauvegardes à la demande rapides et efficaces sur une plate-forme SRAM avec NVM pour les sauvegardes. En utilisant une conception basée sur SRAM + NVM, il est montré qu'il est possible de conserver les avantages de l'exécution rapide et économe en énergie de SRAM tout en limitant les inconvénients des NVM, tels que leur faible endurance, leur énergie active élevée et leur temps d'accès plus lent.

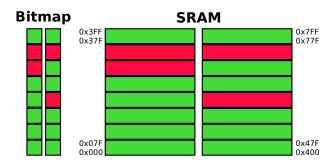

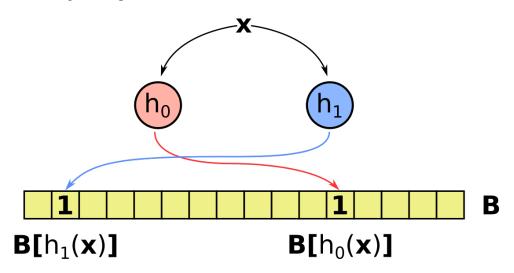

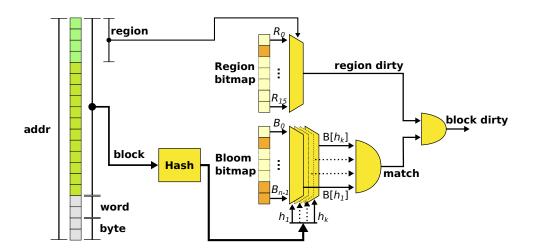

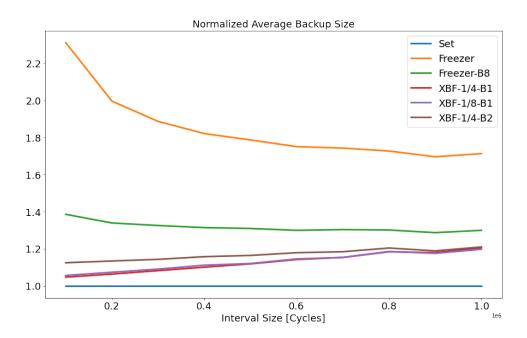

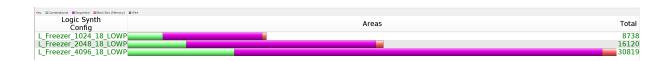

Dans cette thèse, nous présentons *Freezer*, un contrôleur spécialisé pour la sauvegarde et la restauration qui surveille dynamiquement les accès mémoire tout au long de l'exécution du programme. Lorsqu'une coupure de courant est détectée, le contrôleur valide les modifications sur une copie dans une mémoire non volatile (NVM). Notre procédé peut être mis en œuvre en utilisant des standards et ne fait pas appel à des mémoires hybrides sophistiquées. Freezer utilise un tableau de bits comme bitmap, pour marquer

les sections de la mémoire qui sont modifiées. L'espace d'adressage est divisé en blocs consécutifs, chaque bloc est constitué de N mots de 32 bits (par exemple, un espace d'adressage de 32 Ko peut être divisé en 1024 blocs de 8 mots). En fonctionnement normal, lorsque le CPU écrit à une adresse, Freezer identifie le bloc qui contient l'adresse et met à 1 le bit correspondant dans le bitmap. Lorsqu'une coupure de courant est détectée, Freezer lit le bitmap et copie uniquement les blocs modifiés depuis la SRAM vers la NVM.

Les résultats sur un ensemble de benchmarks montrent une réduction moyenne de  $8\times$  de la taille de la sauvegarde. Grâce à notre contrôleur dédié, le temps de sauvegarde est encore réduit de plus de  $100\times$ , avec un ajout de surface et de puissance de seulement 0,4% et 0,8%, respectivement, par rapport à système sans Freezer.

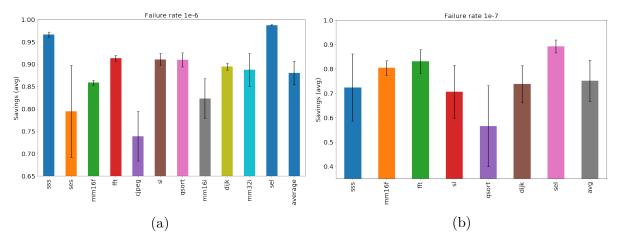

Les sauvegardes et restaurations d'état sont des opérations cruciales dont l'interruption pourrait compromettre la progression ou éventuellement entraîner la corruption de l'état de l'application. Pour résoudre ce problème, nous présentons deux algorithmes de sauvegarde et de restauration qui, à chaque étape, peuvent garantir l'existence d'un état cohérent du système vers lequel se replier en cas d'erreur lors de la sauvegarde. De plus, nous montrons que cette garantie nous permet d'améliorer encore l'efficacité énergétique du système en permettant des temps d'exécution plus longs avec la même valeur de condensateur. Par rapport à une approche double-buffering conventionnelle, les deux algorithmes que nous proposons permettent d'économiser au total plus de 23% d'énergie et de temps d'exécution.

L'approche bitmap est efficace pour suivre les modifications dans un espace d'adressage relativement petit, mais cette approche est difficile à mettre à l'échelle pour des mémoires plus grandes, car elle nécessite soit d'utiliser plus de bits, ce qui entraîne une surcharge de zone, soit de suivre de plus grandes sections de mémoire avec le même nombre de bits. Le suivi d'une grande section de mémoire réduit la précision de la sauvegarde différentielle (c'est-à-dire que davantage de mots non modifiés sont enregistrés), augmentant ainsi sa taille.

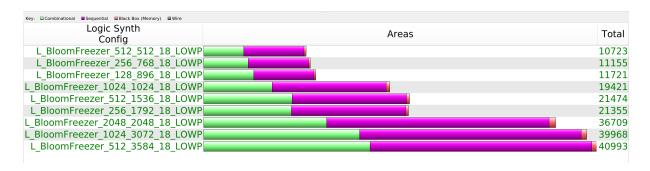

Pour améliorer l'évolutivité des systèmes de sauvegarde incrémentale tels que Freezer, sans augmenter la taille des sauvegardes, une nouvelle méthode pour suivre les régions de mémoire modifiées est proposée. Pour cela, nous définissons et étudions des structures de données abstraites et probabilistes telles que les *filtres Bloom*, en combinaison avec notre approche Freezer. Cette combinaison Bloom+Freezer permet de suivre des espaces d'adressage beaucoup plus grands, tout en améliorant la taille de la sauvegarde, même par rapport à une version évolutive et beaucoup plus chère de Freezer.

La thèse est organisée comme suit. Le chapitre 1 présente un aperçu de l'état de l'art, en analysant les forces et les faiblesses des approches trouvées dans la littérature. Le chapitre 2 présente une revue des technologies émergentes de mémoire non volatile. Dans le chapitre 3, Freezer, un contrôleur de sauvegarde implémentant la sauvegarde incrémentale à la demande, est proposé, conçu et validé. Le chapitre 4 présente deux algorithmes de sauvegarde incrémentale qui garantissent la cohérence de l'état du système. Le chapitre 5 étudie l'utilisation de filtres Bloom pour améliorer et étendre le suivi de la mémoire, pour un schéma de sauvegarde incrémentielle. Enfin, le chapitre 5.6 résume ce travail, et présente une discussion sur certaines perspectives futures intéressantes.

## **TABLE OF CONTENTS**

| In       | trod | uction               |                                                                 | 13 |  |

|----------|------|----------------------|-----------------------------------------------------------------|----|--|

| 1        | Stat | te of tl             | he Art                                                          | 19 |  |

|          | 1.1  | Non-V                | Volatile Computers and Energy Harvesting                        | 19 |  |

|          |      | 1.1.1                | Scarce and Intermittent Energy Sources                          | 19 |  |

|          |      | 1.1.2                | Non-Volatile System Design Objectives                           | 21 |  |

|          | 1.2  | Soluti               | ons for Backup Robustness and Consistency                       | 23 |  |

|          | 1.3  | Softwa               | are Solutions                                                   | 25 |  |

|          |      | 1.3.1                | Programming Languages and Task-Based Approaches                 | 25 |  |

|          |      | 1.3.2                | Static Techniques                                               | 26 |  |

|          |      | 1.3.3                | Run-Time Techniques                                             | 28 |  |

|          |      | 1.3.4                | Sytare                                                          | 33 |  |

|          | 1.4  | Archit               | sectural (Hardware) Solutions                                   | 34 |  |

|          |      | 1.4.1                | NVM Integration                                                 | 34 |  |

|          |      | 1.4.2                | Brainshift Architecture                                         | 36 |  |

|          | 1.5  | Non-V                | Volatile Processors                                             | 38 |  |

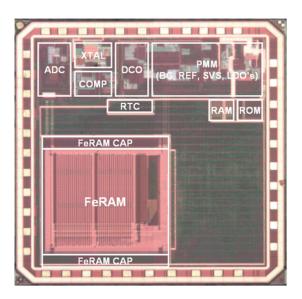

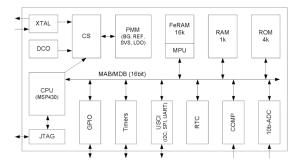

|          |      | 1.5.1                | MSP430F : an MCU with Embedded FeRAM $\ldots \ldots \ldots$     | 38 |  |

|          |      | 1.5.2                | THU1010N: a Non-Volatile-Processor based on FeFFs               | 40 |  |

|          |      | 1.5.3                | Non-Volatile logic Cortex-M0 with distributed FeRAM mini arrays | 41 |  |

|          |      | 1.5.4                | A 90nm 20MHz nvMCU based on STT-RAM                             | 43 |  |

|          |      | 1.5.5                | A 65 nm ReRAM-Enabled NVP                                       | 44 |  |

|          |      | 1.5.6                | RRAM Non-Volatile Intelligent Processor                         | 46 |  |

|          |      | 1.5.7                | FeRAM Parallel Recovery SoC                                     | 47 |  |

|          | 1.6  | Concl                | usion                                                           | 48 |  |

| <b>2</b> | Nor  | on-Volatile Memories |                                                                 |    |  |

|          | 2.1  | Introd               | luction                                                         | 53 |  |

|          | 2.2  | Phase                | Change Memory                                                   | 53 |  |

|          |      | 2.2.1                | SET and RESET write operations                                  | 54 |  |

### TABLE OF CONTENTS

|   |               | 2.2.2  | PCM Cell                                       |

|---|---------------|--------|------------------------------------------------|

|   |               | 2.2.3  | Characteristics                                |

|   | 2.3           | Magne  | etic RAM                                       |

|   |               | 2.3.1  | Magnetic Tunnel Junction                       |

|   |               | 2.3.2  | Field Induced Magnetic Switching MRAM          |

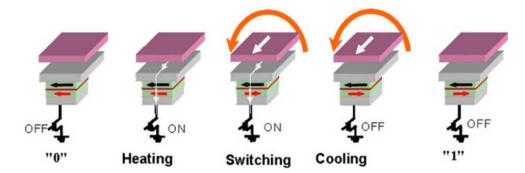

|   |               | 2.3.3  | Thermally Assisted Switching MRAM              |

|   |               | 2.3.4  | Spin-Transfer Torque MRAM                      |

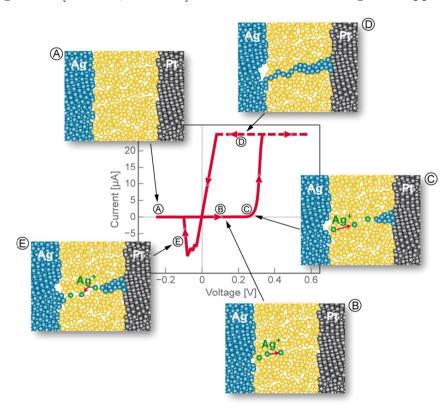

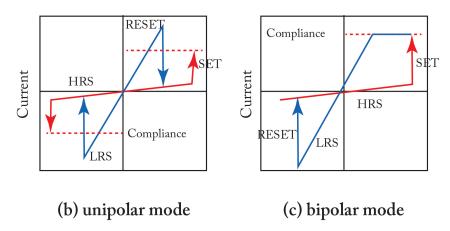

|   | 2.4           | Resist | ive Memories and Memristors                    |

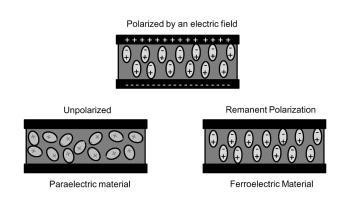

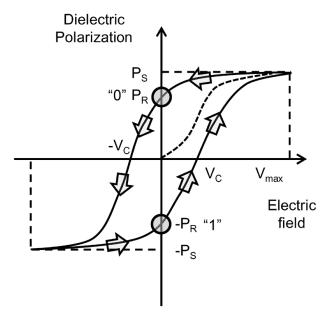

|   | 2.5           | Ferroe | electric RAM                                   |

|   | 2.6           | Comp   | arison                                         |

| 3 | $\mathbf{FR}$ | EEZEI  | R a Dedicated Backup and Restore Controller 71 |

|   | 3.1           | Introd | luction                                        |

|   | 3.2           | Backg  | round and Related Work 73                      |

|   | 3.3           | Syster | m Modelling                                    |

|   |               | 3.3.1  | Considered System Model                        |

|   |               | 3.3.2  | System Architecture                            |

|   |               | 3.3.3  | Modelling Memory Access Energy                 |

|   | 3.4           | Model  | ling of the Backup Strategies                  |

|   |               | 3.4.1  | Full Memory Backup                             |

|   |               | 3.4.2  | Used Address Backup                            |

|   |               | 3.4.3  | Modified Address Backup                        |

|   |               | 3.4.4  | Oracle                                         |

|   |               | 3.4.5  | Block-Based Strategies                         |

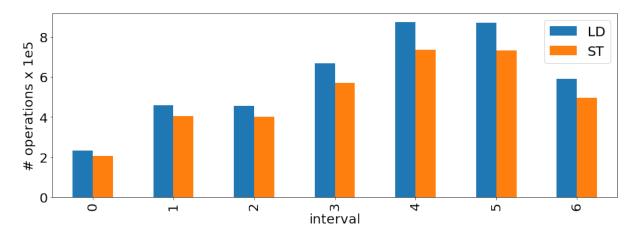

|   | 3.5           | Trace  | Analysis and Improvement in Backup Size        |

|   | 3.6           | Freeze | er                                             |

|   |               | 3.6.1  | Freezer Architecture                           |

|   |               | 3.6.2  | Area and Power Results                         |

|   |               | 3.6.3  | Impact of Block Size                           |

|   | 3.7           | Result | ss                                             |

|   |               | 3.7.1  | Backup Size                                    |

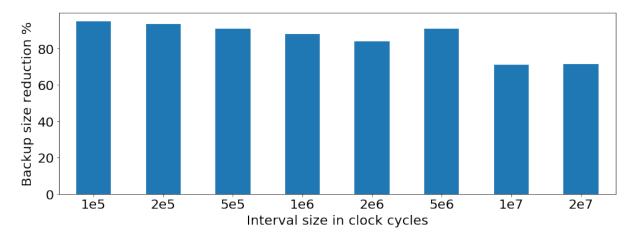

|   |               | 3.7.2  | Impact of Interval Size                        |

|   |               | 3.7.3  | Backup Time                                    |

|   |               | 3.7.4  | Energy Comparison with other Memory Models     |

|   |     | 3.7.5 Impact of Leakage Power                                     | 101 |

|---|-----|-------------------------------------------------------------------|-----|

|   |     | 3.7.6 Energy and Area Overhead Considerations                     | 102 |

|   | 3.8 | Discussion About The Approach                                     | 104 |

|   | 3.9 | Conclusion                                                        | 105 |

| 4 | Rob | oust and Consistent Incremental Backup for Intermittently Powered |     |

|   |     | <u>-</u>                                                          | 107 |

|   | 4.1 | Introduction                                                      | 107 |

|   | 4.2 | Architecture Model                                                | 111 |

|   | 4.3 | Related Work                                                      | 114 |

|   | 4.4 | Robust and Consistent Backup                                      |     |

|   |     | 4.4.1 Full Backup with Double Buffering                           | 116 |

|   |     | 4.4.2 Restore & Update Strategy                                   |     |

|   |     | 4.4.3 Cumulative Updates Strategy                                 |     |

|   | 4.5 | Robustness Against Power Failures                                 |     |

|   |     | 4.5.1 Robust Backup and Restore Algorithms                        | 122 |

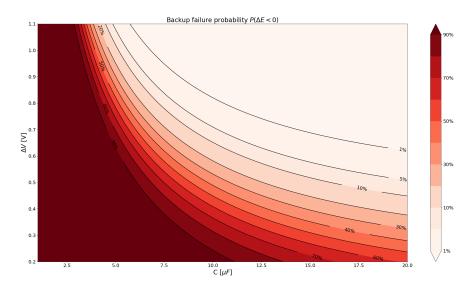

|   |     | 4.5.2 Probabilistic Failure Model                                 | 123 |

|   | 4.6 | Results                                                           | 127 |

|   |     | 4.6.1 Experimental Setup and Simulation Procedure                 | 127 |

|   |     | 4.6.2 Probability of backup interruption                          | 129 |

|   |     | 4.6.3 Analysis of Memory and Backup Data Size                     | 130 |

|   |     | 4.6.4 Overhead Analysis                                           | 133 |

|   | 4.7 | Exploiting Robust Backup to Rise System Efficiency                | 134 |

|   | 4.8 | Conclusion                                                        | 138 |

| 5 | Blo | om-Filter Based Memory Write Tracking for Differential Backup 1   | 41  |

|   | 5.1 | Introduction                                                      |     |

|   | 5.2 | Background and Related Work                                       |     |

|   |     | 5.2.1 Incremental Backup                                          |     |

|   |     | 5.2.2 Hashing and Bloom Filters                                   |     |

|   | 5.3 | System Model                                                      |     |

|   | 5.4 | Filter-Based Memory Write Tracking                                |     |

|   |     | 5.4.1 Plain Bloom Filters                                         |     |

|   |     | 5.4.2 Parallel Bloom Filters                                      |     |

|   |     | 5.4.3 Hybrid Hierarchical Bloom-Freezer                           | 149 |

### TABLE OF CONTENTS

| 5.5          | Result | ts                                                                                                                         | 151 |

|--------------|--------|----------------------------------------------------------------------------------------------------------------------------|-----|

|              | 5.5.1  | Simulation Setup                                                                                                           | 151 |

|              | 5.5.2  | Simulation Results                                                                                                         | 152 |

|              | 5.5.3  | Hardware Model                                                                                                             | 153 |

| 5.6          | Concl  | $lusion \dots \dots$ | 157 |

| Conclu       | ısion  |                                                                                                                            | 159 |

| Bibliography |        |                                                                                                                            |     |

## INTRODUCTION

The explosion of Internet-of-Things (IoT), wireless sensor nodes and wearable devices, has lead to an increasing interest in energy harvesting as a source for powering these devices. Many of these systems cannot afford the presence of a battery to power the application. This can be due to strict requirements with respect to cost, size and/or weight of the system. Moreover, the use of a battery can be difficult for devices with an expected long lifetime, as batteries usually have low endurance and require frequent replacements, making the device expensive to service and maintain, especially when such devices are deployed in remote locations. In these cases, environmental energy harvesting can be a viable alternative to power these devices.

The main drawback of powering a device with energy harvested from the environment, is that the available energy is usually scarce and intermittent. This means that the device, while executing its task, will suffer from unpredictable power interruptions. The idea of sustaining computation under intermittent power has pushed forward the interest towards  $Non-Volatile\ Computers$  and in particular  $Non-Volatile\ Processors\ (NVP)$ . Non-volatile computers can be defined as in [Yu+11]:

#### Non-Volatile Computer

"systems that can almost instantly save their state in a non-volatile fashion so that operation can continue even across an unanticipated power interruption" [Yu+11]

In recent years, the emergence of faster *Non-Volatile Memories* has enabled the development and research of NVPs for intermittent computing devices powered with environmental energy harvesting.

Figure 3 shows the block-level architecture of a typical battery-less, intermittently-powered device. These systems are usually based around the following basic components, as shown in Figure 3:1) The *Energy Harvesting System*, which extracts some form of environmental energy and feeds it to the rest of the system. 2) A *Buffer Capacitor* that is

FIGURE 3 – High level architecture of a battery-less, intermittently-powered device.

used to store a small amount of energy, to allow for the system to continue its execution or to save its state when the harvester is not able to provide power. The voltage across the buffer capacitor is commonly used to measure the "availability" of the energy and to detect an imminent power loss, which is usually detected when the voltage across the buffer capacitor falls below a certain threshold. 3) The *Non-Volatile Processor*, which is the main computing device and is usually connected to some sensors and some kind of network connectivity, usually through low-power radio devices.

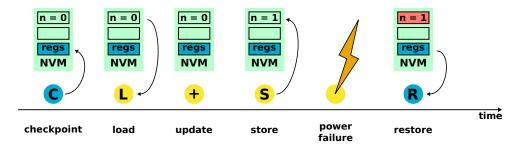

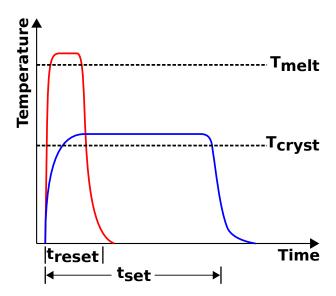

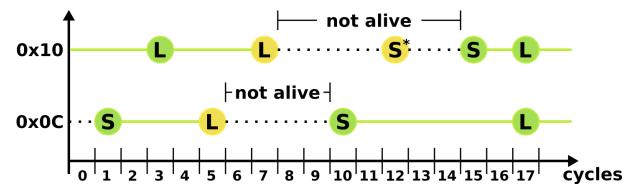

Figure 4 shows an example of intermittent computing, with the execution interrupted and divided into intervals by power failures, which are shown as drops in the voltage. Intermittent computing is therefore a sequence of four states of a device : power-off, restore, compute, and backup. In order to preserve progress of the system execution across power failures and to avoid restarting from the very beginning (or to reboot the system), the NVP has to perform a backup of the system state before the power is completely lost and the device is off. Then, when there is again enough energy to continue execution, the previous state is restored.

Many solutions have been proposed to implement efficient non-volatile computing systems, that can carry computation across unpredictable power interruptions. One of the main characteristics of these systems is the backup (or check-pointing) strategy, which can either be: On-demand, meaning that the backup operation is triggered by an event signaling an imminent power failure, or Static/Periodic, in which case the check-points are placed in predetermined locations in the code of the application.

Static check-pointing strategies use compile-time techniques to optimize aspect of the

FIGURE 4 – Example of computation under intermittent power.

backup such as the size (*i.e.*, the amount of data that needs to be saved), and the number and placement of the check-points. The main drawback with this approach is that the check-points are executed even when the energy is available and, in the event of a power failure, the whole progress made from the last check-point is lost.

On-demand check-pointing on the other hand tries to execute the backup only when necessary (i.e., just before the power fails). With this kind of strategies, the system responds to an event such as the voltage across the buffer capacitor falling below a predetermined threshold. In this case, the backup could be executed at any moment during the execution of the application. It is therefore difficult to optimize in advance the size of the backup. For this reason, most on-demand check-pointing strategies usually have to save the whole memory every time.

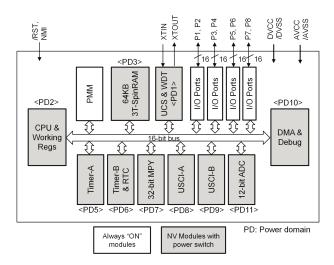

We can also categorize non-volatile computing systems by whether they are based on software-level or hardware-level solutions. Software-based approaches are usually implemented on platforms with both SRAM and an addressable Non-Volatile Memory (NVM), e.g., like the commercially available msp430F [Ins21]. These solutions are usually easier to implement and to apply to existing applications, but tend to be much slower and less efficient than the hardware-based approaches.

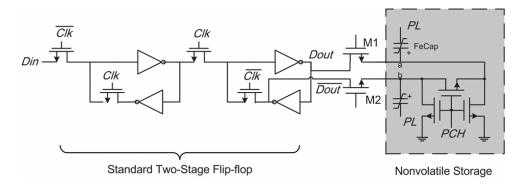

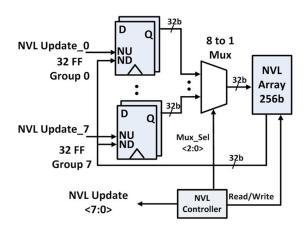

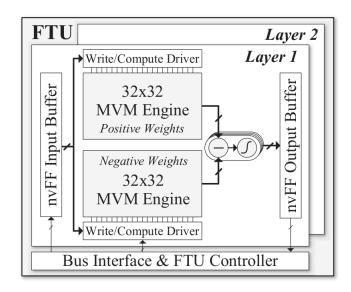

Hardware-level solutions on the other hand exploit NVM integration, usually to implement fully non-volatile processors, where every memory element, including the internal registers, are made non-volatile. This is usually achieved by using an NVM as the only system memory, and using hybrid non-volatile flip-flops (nvFFs) (*i.e.*, flip-flops paired with a non-volatile element) for the internal registers. The aim with this kind of solutions is to minimize the backup and restore time, achieving a system that is able to respond almost instantly to power failures, and to resume as quickly as possible the execution when the power is back. These systems also come with several disadvantages, as they are difficult

to implement and adopt, due to the use of exotic technologies and need for intrusive and extensive modifications of the processor architecture, which cannot be applied to existing licence IPs and hard IPs. Moreover, these solutions usually come with great overheads in terms of area of the chip, due to nvFFs being much larger than regular FFs and much more difficult and expensive to manufacture.

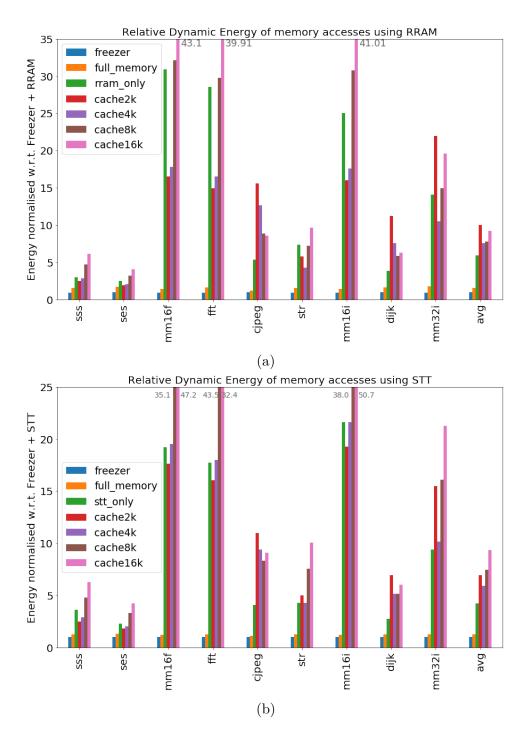

Systems based only on NVM, both hardware and software based ones, also face additional problems due to the limitations of current NVM technologies, which are explored more in depth in Chapter 2. In particular, NVMs offer slower read and write access speed and increased read and write energy consumption with respect to volatile, static random-access memory (SRAM). This translates into worse performance and increased power consumption during the active times (*i.e.*, computing phases in Figure 4), resulting in slower progress and more interruptions. Additionally, NVMs currently suffer from limited endurance, as the NVM cells can wear out and stop working in a limited number of write cycles.

Another problem of intermittently-powered devices is to keep the non-volatile state consistent (*i.e.*, safe). Consistency problems arise when, after a backup, the NVM is modified, and power is lost before a new backup is executed. This type of error also includes errors due to sudden interruption during the backup process, which leave the backup state in the NVM uncompleted. Many solutions in the state of the art, and in particular many fully non-volatile-processors, do not offer any detection or protection against backup errors or inconsistency errors. Some solutions are able to detect these errors, but cannot recover and require a restart of the application.

This work was part of the <u>ZE</u>ro <u>P</u>ower (ZEP) computing systems project. The ZEP project gathers four INRIA teams that have a scientific background in architecture, compilation, operating system and low power, together with the CEA Lialp and Lisan laboratories of CEA LETI & LIST. The ZEP project addresses the issues related to designing small, battery-less computing nodes, in the context of IoT and ubiquitous computing, by combining non-volatile memory, energy harvesting, micro-architecture innovations, compiler optimizations, and static analysis. In the context of the ZEP project, this work has focused mainly on the micro-architectural enhancements for battery-less, intermittently powered systems.

In this work, we start from the idea of implementing an on-demand backup solution on a platform equipped with both SRAM and NVM, that uses primarily the SRAM for normal computations and the NVM for backups. Using an SRAM+NVM based architecture allows to keep the advantages of fast and energy efficient execution on SRAM, while minimizing the drawbacks of NVMs such as the low endurance. Results in Chapter 3 provide some insights about the benefits of such SRAM+NVM based architectures.

First, we propose Freezer in Chapter 3, a hardware controller to implement an efficient incremental backup technique for on-demand check-pointing. The choice of an on-demand approach guarantees a more reactive system, that does not execute unnecessary backups, and minimizes the need for rollbacks after restore. Moreover, thanks to our proposed incremental backup approach, our method optimizes the backup size by saving only the modified blocks, and achieves an 87% average reduction in backup size with respect to full memory backups.

Moreover, to address the possibility of consistency errors, due to sudden interruption during backup, we further improve on our approach, and we present two algorithms that provide robust and consistent on-demand incremental backups, while always guaranteeing the existence of a consistent state, to which the system can revert to, in case of errors.

Finally, we look at extending our Freezer approach to more capable systems, i.e., with main memory capacity greater than 64KB. 64KB is already much larger than what is commonly used in intermittently-powered devices. But, in the future, bigger devices are likely to be used for these tasks. However, to allow more capable devices to enter the intermittently-powered domain, more scalable approaches are required. To improve the scalability of incremental backup systems such as Freezer, without increasing the size of the backups, a new method to track modified memory regions is proposed. For this, we define and study approximate membership data structures such as  $Bloom\ filters$ , in combination with our Freezer approach. This allows to track much larger address spaces, while also improving the backup size, even when compared with a scaled and much more expensive version of Freezer.

To summarize, in this work, we present a summary and comparison of the different NVM technologies, with data end results collected from many works in the literature. We present an on-demand incremental backup scheme, that can reduce backup size by more than 87% with respect to full-memory backup. We propose two algorithms for robust and consistent incremental backup, that guarantee the existence of a consistent state to revert

to in case of errors. And, finally, we investigate extending incremental backup to larger address spaces, by using Bloom filters to track modified memory regions.

The rest of the thesis is organized as follows. Chapter 1 presents an overview of the State of the Art, analyzing the strength and weaknesses of the approaches found in the literature. Chapter 2, presents a review of the emerging Non-Volatile Memory technologies. In Chapter 3, Freezer, a backup controller implementing on-demand incremental backup, is proposed, designed and validated. Chapter 4 presents two incremental backup algorithms that guarantee the consistency of the system state. Chapter 5 investigates the use of Bloom filters to improve and extend memory tracking, for an incremental backup scheme. Finally, Chapter 5.6 sums up this work, and presents a discussion about some interesting future perspectives.

## STATE OF THE ART

In recent years, intermittently-powered systems have been the object of research and studies from both industry and academia. Non-Volatile Processors (NVP) and, more in general Non-Volatile Computers, are at the core of these systems, and allow them to be powered by intermittent energy sources harvested from the environment. In this chapter, the concept of Non-Volatile Computer and energy harvesting for intermittently powered systems are introduced. A brief description of the fields of application for these devices is given, then the key concept, the challenges and design objectives for non-volatile system design are outlined. The chapter then gives an overview of some solutions, both at the software and hardware levels, that have been proposed in the literature to implement and optimize these systems. Then, some hardware based non-volatile processors that have been proposed in the literature are briefly presented. Finally, we compare these different solutions from the state of the art, outlining their strengths and weaknesses.

## 1.1 Non-Volatile Computers and Energy Harvesting

## 1.1.1 Scarce and Intermittent Energy Sources

Energy scavenging from the environment can be achieved through many sources with different types of devices. The main types of environmental energy sources are:

- Light (solar or indoor),

- Vibration or Motion,

- Thermal,

- Radio Waves, and

- Wind.

Common characteristics of these types of energy sources are the low amount of power, and their unpredictability on the availability of such power. In fact, many of these sources do not exceed few  $\mu W/cm^2$  as reported in Table 1.1 from [Vul+10], and the availability is also

limited and subject to variations due to changes in the environmental conditions. Because

Table 1.1 – Harvested power of different energy sources (from [Vul+10])

| Source           | Harvested Power    |

|------------------|--------------------|

| Ambient Light    |                    |

| Indoor           | $10 \ \mu W/cm^2$  |

| Outdoor          | $10 \ mW/cm^2$     |

| Vibration/Motion |                    |

| Human            | $4 \ \mu W/cm^2$   |

| Industrial       | $100 \ \mu W/cm^2$ |

| Thermal          |                    |

| Human            | $30 \ \mu W/cm^2$  |

| Industrial       | $1-10 \ mW/cm^2$   |

| RF               |                    |

| GSM Base Station | $0.1 \ \mu W/cm^2$ |

the power levels involved are so low, these types of systems usually rely on capacitors or small batteries to buffer the harvested energy and smooth out variations in the supply voltage, as shown in Figure 3. Additionally, to enable long running computations on energy harvesting platforms, the device must be able to maintain progress in the event of an unexpected power failure, because of the unpredictability and intrinsic variability of environmental energy harvesting.

To cope with these issues of scarce and intermittent energy sources, researchers have been focusing on a new class of devices called Non-Volatile Processors (NVPs) or, more in general Non-Volatile Computers or Non-Volatile Systems. One of the early attempts to address these issues was presented by Yu et al. in [Yu+11], where a non-volatile microcontroller, based on floating gate transistors, is proposed. In this work, the authors identified two main types of applications that a non-volatile processor would enable: running computations under unstable power sources, and allow idle power reduction while maintaining fast response times [Yu+11]. According to this definition a Non-Volatile Computer needs to guarantee forward-progress across unexpected power failures. This requires two fundamentals operations: NV Store and NV Restore. NV Store means saving the state of the system in a non-volatile fashion, while NV Restore indicates the operation of retrieving a previously saved state. To support these operations, non-volatile memories are used, to quickly save the state of the system before a power failure occurs, and to restore the state when the power is newly available.

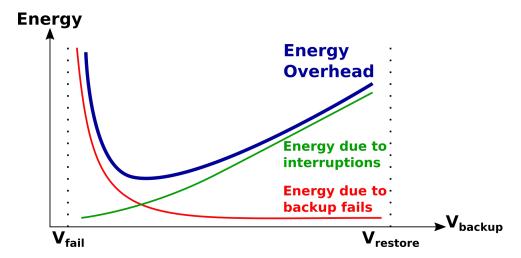

### 1.1.2 Non-Volatile System Design Objectives

The design of Non-Volatile Computer system for intermittently-powered and ambient energy harvesting scenarios poses a new set of challenges and objectives with respect to the normal low-power design. In fact, while low-power or ultra-low-power design techniques are necessary to allow operation under extremely low energy sources, they are not sufficient to enable efficient computing in an intermittent system. In particular there are other important targets that need optimization in these types of systems, such as the backup and restore time and energy. Backup time and restore time need to be minimized to improve the efficiency of the system. Achieving fast backup and restore phases allows to have a responsive system, while minimizing the backup and restore energy is important so that more of the available energy can be used to further the computation during the execution phase.

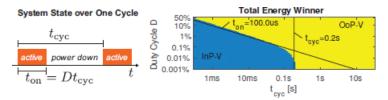

Forward progress maximization is, in general, one of the main objectives, and one of the main design goals for transiently-powered systems. To this end, there are many different decisions that a designer can take when engineering these kind of NV systems. As an example, in [Ma+16], several processor architectures are explored, with different energy sources. Contrary to normal low-power systems, the paper shows how, in some situations, even a more power hungry architecture, such as an Out-of-Order processor (OoO), can yield improvement in the forward progress of the application. This is because when the environmental energy is plenty, an OoO processor can better exploit the abundance of energy, while a non-pipelined in-order processor would lag behind, without fully utilizing the incoming energy.

Another important design decision concerns the type of check-pointing strategy, which can be categorized as either *On-Demand* or *Static/Periodic*. With static check-pointing, the backups are performed when the application reaches a check-point, which is usually a predetermined place in the code of the program. In particular, some strategies define check-points in the code at compile time, in places such as at the beginning of loops or before function calls [RSF11]. To avoid always taking backups, when a check-point is reached, the voltage across the storage capacitor (see Figure 3) is measured, and the backup is taken only if the voltage is below a threshold [RSF11]. On the other hand, systems using on-demand checkpoints trigger backups in response of some events, that normally signifies that a power failure is imminent. Usually, such triggering event is given by the voltage across the buffer capacitor falling below a defined threshold. This normally requires some

dedicated circuit such as voltage comparators or analog-to-digital converters to measure the value of the voltage of the storage capacitor. On-demand check-pointing works when the platform is capable to rapidly save the volatile state in response to the trigger events.

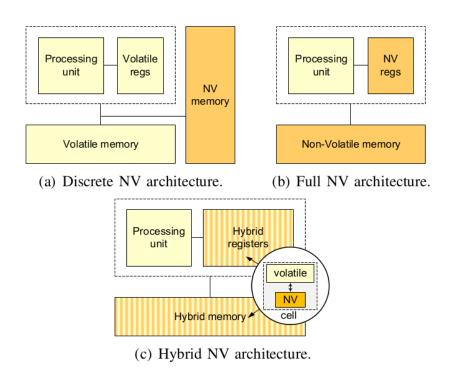

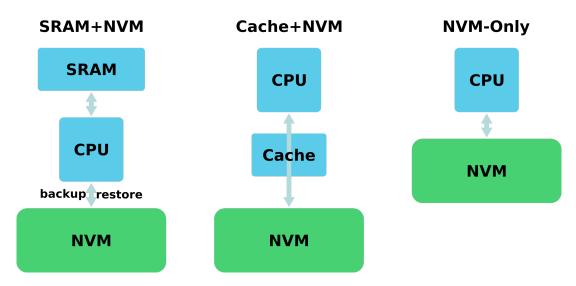

Another design decision concerns the architecture of the non volatile memory, which can be distributed or centralized. Additionally, the non-volatile memory can be integrated in the system in different ways, Figure 1.1 from [Yu+11] depicts three possible architectural choices for NVM integration.

FIGURE 1.1 – NVM integration techniques for non-volatile computers (from [Yu+11])

- The *Discrete NV* approach couples a normal SRAM memory with a discrete NVM, which allows simpler integration and has the advantage of using standard memory arrays. However, the backup and restore operations are slower as they need to be performed with sequential transfers.

- The Full NV approach tries to solve this issue by getting rid of the volatile memories, and only using NVMs. Additionally, if also the internal registers are made non-volatile, it means that no backup operation is necessary as the main memory is already non-volatile. In practice, while it is possible to replace the main SRAM

memory with an NVM, this introduces several drawbacks as NVMs are not as fast and require more energy per operation than SRAMs. Moreover, the current NVM technologies do not allow yet the same level of endurance of SRAM, meaning that the platform could experience a much shorter life-time due to the wearing of the NVM.

— To achieve the performance and endurance of SRAM with almost instantaneous backup and restore operations, a *Hybrid NV* approach can be taken. This technique relies on using hybrid SRAM memories that are enhanced with the integration of non volatile devices for each SRAM cell [Lee+15; Liu+16]. Such hybrid memories can perform like SRAM during normal operations, but they can very quickly transfer the content from the SRAM cells to the non-volatile elements and vice versa. This gives the possibility of executing the backup (and restore) simultaneously on many memory cells at once. In principle, it is possible to backup the whole memory array in parallel, however some work avoid a full parallel backup, in order to limit the peak current that this operation would require [Liu+16]. This approach is also far from being mature from the technology point of view and therefore cannot be used yet as a concrete technique.

## 1.2 Solutions for Backup Robustness and Consistency

While the use of emerging NVMs can open the possibility for efficient intermittently powered devices, their use can also bring inconsistencies when they are paired with volatile state. According to Ransford *et al.* [RL14], two types of inconsistencies can arise when NVMs are used in an intermittent-power scenario:

- NV-internal, and

- NV-external.

Both types of inconsistencies can occur after a power failure. Internal inconsistencies are due to data stored in the NVM being only partially updated before a power failure. As an example, this can happen if the backup is not completed before the system runs out of energy. This would leave the backup in an inconsistent state and, unless protection mechanisms are applied, lead to the complete loss of progress, as it would happen in [Bal+15]. External inconsistencies instead arise when the NVM is used both for backup and to store run-time variables. They can appear after a successful backup, if a variable in the NVM is updated and a power failure happens before the next checkpoint is reached. This means

that after the restore, the volatile state is rolled-back to the previous backup, while the NVM variable remains unchanged. To address these inconsistencies, Xie et al. [Xie+15] propose a consistency-aware check-pointing algorithm, which eliminates consistency errors in a system using NVM as its main memory, and also tries to minimize the number of check-points.

Figure 1.2 shows how a consistency error can arise in systems using NVM as the main memory, when the following sequence of events happen: 1) a check-point is executed, 2) a variable is read from the NVM, 3) the variable is used for some computation, 4) the result is stored in the NVM, and 5) a power failure happens. The state (*i.e.*, the registers) is then restored from NVM, but because the power failure happened before reaching a new check-point, the state will resume from before the variable is loaded (step 2), which means that the incorrect value will be read (n = 1 in the example in Figure 1.2) and used. In [Xie+15],

FIGURE 1.2 – Sources of consistency errors in systems using NVM as the main memory.

the authors propose to avoid these consistency errors by changing the position of the check-points, inserting a check-point in between the load/store error pair. The paper then presents an algorithm to identify these error pairs, and proposes an heuristic algorithm to minimize the number of required check-points. While the technique proposed in [Xie+15] addresses the inconsistency issue with NVM based systems, the approach presents some disadvantages mainly due to two main factors: the drawbacks of a system using NVM as the only system memory, the use of a static check-pointing technique. NVMs are still slower and consume more energy for read and write operation with respect to traditional SRAM. Moreover, because this is a static check-pointing scheme, the system does not respond to a power-failure events, but waits to reach a predetermined location before executing the check-point. This can result in wasted energy, due to unnecessary backup executions when the energy is available. Additionally, because the check-points are in fixed locations, additional energy needs to be spent to roll-back the state after a restore.

## 1.3 Software Solutions

In this section, we give a brief overview of some software-level solutions that are meant to enable or optimize intermittent computing platforms. Software-level solutions and techniques have been explored in several works, and they generally do not require major modifications of the hardware or any exotic hardware feature. In particular, many software-level techniques are targeted for commercially available platform, s such as the MSP430FE series of micro-controller that feature a byte addressable non-volatile Ferroe-lectric RAM (FRAM).

These minimal hardware requirements makes the software-level solutions compelling for their low cost and because they might be easier to deploy. However, they do come with major drawbacks in terms of speed and consumed energy when compared with dedicated hardware solutions. This is especially true for run-time systems that need to carry out backup and restore task.

In this brief overview, we identify three major types of software-level techniques:

- dedicated and domain-specific programming languages,

- compiler and static techniques, and

- runtime/Operating-System level frameworks.

## 1.3.1 Programming Languages and Task-Based Approaches

An interesting approach proposed in the literature to enable non-volatile computing on energy harvesting devices, is to use dedicated or domain-specific programming languages or frameworks.

One of these dedicated framework is *Chain*, proposed in [CL16] as a programming language and run-time framework "for programming intermittent devices". Chain is a *task*- and *channel*-based programming language and framework, implemented in C, which guarantees to be intermittent safe at the task granularity [CL16]. In particular with Chain, the program needs to be divided into tasks by the programmer, which can perform both I/O and computations. These tasks communicate with other tasks, or with future instances of themselves, through channels which are implemented on the non-volatile memory. Each task can have their own private volatile variables, and have separate channels for input and output. However, tasks cannot directly access the NVM. Each task views its inputs as if they were immutable (*i.e.*, cannot be modified by the receiving task) constants and

always available in their channel. Moreover, every volatile variable must be task local. Because of this memory access model, each task is both atomic and idempotent, meaning that they can be interrupted and re-executed any number of times without changing the final result [CL16].

The main advantage of this approach is that it does not need check-points. In fact, once the inputs for the next task are written into the non-volatile channel, and the next task is scheduled to run, it is effectively like the program has reached a new check-point. However, this approach has some disadvantages. First of all, a user needs to learn a new programming language and framework and must adapt its application, converting it into a task based design. This means that existing code cannot be easily used with this approach without some important changes. Additionally, the framework only guarantees to be intermittent safe at the task level. This means that the programmer must guarantee that each task is able to run to completion, and must take care that the computation of each task is not too energy expensive and can fit within the energy budget. Otherwise, the whole application could be blocked by a single task that is always interrupted before completing. And correctly sizing each task could be difficult. Moreover, changes in the environmental conditions, such as increase in temperature, ageing and wear could reduce the effective capacitance and increase leakage 1, thus changing the effective energy storage.

Another programming language and run-time system for "perpetual systems" is Eon, presented in [Sor+07]. Contrary to Chain, Eon does not deal with the problem of backup/recovery in an intermittent computing scenario. While Chain addresses the problem of backup/recovery in intermittent systems, Eon is intended to be a "coordination language", that is built to be "energy aware" [Sor+07]. In particular with Eon, the programmer can define how the system responds to external events depending on the energy state.

### 1.3.2 Static Techniques

Static Techniques are a category of software-level solution that exploit some static information, usually at compile time, to optimize the backup and restore operations. As an example, in [Zha+15], the authors propose a static analysis of a program that is able to determine an efficient position for the backups, such that the required size for the non-

<sup>1.</sup> TDK, C2012X5R0G476M125AB: Detailed Information | Capacitors - Multilayer Ceramic Chip Capacitors, en, URL: https://product.tdk.com/en/search/capacitor/ceramic/mlcc/info?part\_no=C2012X5R0G476M125AB (visité le 09/07/2022).

volatile space is reduced. In particular, the technique proposed in [Zha+15] analyzes the program at a basic block granularity. The idea is that, instead of executing the backup as soon as the energy warning arrives, the backup can be deferred and executed n basic blocks later, when the size of the state (the stack frame) is smaller. This means that more instructions are executed, and the size of the resulting backup is reduced. To enable this, an offline analysis of the program is executed using the following information: the available energy when receiving the energy warning, the energy model for both instruction execution and backup, and the control flow graph (CFG) at the basic block level for the application [Zha+15]. Given these, for each basic block, the feasible set of backup position is computed, as well as the optimal position, that tells for each basic block bb to execute the backup after B(bb) basic blocks.

A similar approach is proposed also in [Zha+17], where the authors demonstrate a method to reduce the NVM size. The method is based on stack analysis techniques to determine the required size of the NVM, and on the identification of efficient backup positions. The backup positions are inserted in the code as *labels*. The idea is that instead of executing the backup immediately, at run-time when a power failure is signaled, the program continues the execution until it reaches the first *label*, and then it backups the volatile state and the stack. These labels are positioned in order to minimize the amount of data to store in the NVM in a static optimization task. However, the proposed technique also relies on a modified version of the Intel 8051 core, where a reserved instruction is used as a backup label in the code. This special processor is equipped with a dedicated backup-controller and non-volatile controller to execute the backup. This reliance on a dedicated processor, makes the backup process more optimized, at the expense of reducing the applicability of this solution.

Another category of static techniques is concerned with the estimation and evaluation of system energy and power requirements, that are useful in phase of development of a intermittently-powered device and its application. To this end, in [Che+17], a technique for determining application specific peak power and energy for an ultra-low power processor is presented. This technique can allow to better size the harvester and/or energy storage of the platform. The proposed technique uses the gate-level netlist of the processor to perform a symbolic simulation of the program. In this simulation, unknown logic values (Xs) are propagated through the gates as the application inputs. This simulation

allows to perform an "input-independent gate activity analysis", where the activity of gates is recorded, and gates that are not exercised can be identified [Che+17]. This allows to limit the peak power and energy consumption of the processor during the execution of the application. The author show that the application-specific peak power and energy bounds computed with the proposed approach, are normally much lower (27%, 26% and 15%) than those based on design specifications, stress-mark and profiling [Che+17].

One drawback of this approach, is that it requires access to the gate-level netlist of the processor, which is often not available. Although, as pointed out by the authors, the vendors of the processor could offer this evaluation as a cloud-based service, without releasing the netlist of the processor.

### 1.3.3 Run-Time Techniques

Software-based run-time techniques can be viewed like small OS-like software layers that manage the backup and restore functionalities.

#### Mementos

One of the first examples of such software strategies is presented in [RSF11]. In the paper, the authors present *Mementos*, a software system that provides general-purpose programs with support for running in intermittent computing scenarios, by providing protection from power losses [RSF11]. *Mementos* comprises both a run-time system library and a set of compile-time techniques for optimizing the placement of energy checks in the program [RSF11]. The compile-time optimization wraps the program with the code for restoring the state from previous checkpoints, as well as instruments the code of the program, inserting calls to a Mementos library function, which estimates the available energy.

Mementos provides three types of instrumentation for placing the trigger points:

- loop-latch mode,

- function return mode, and

- timer aided mode.

The first two strategies, *loop-latch* and *function return*, place trigger points at the loop back-edges and after call instructions respectively. The third strategy, *timer aided mode*, uses a timer interrupt that is added either at function returns or at loop latches, to raise a flag. Each trigger point only checks the flag, and proceeds with the the energy check

only if the flag is raised, after each energy check the flag is lowered again.

The run-time energy estimation is done by measuring the voltage level at the capacitor with the analog-to-digital converter (ADC), (which needs to be available in the target platform). If the measured voltage is above the *checkpoint threshold voltage* ( $V_{thresh}$ ), then no snapshot is performed. Otherwise, Mementos assumes that a failure is imminent and begins check-pointing the state. The check-pointed state includes the registers, the stack, whose depth is computed using the stack pointer, and the global variables, which are captured at compile time.

Mementos also takes care to protect against check-point corruption due to power losses during a check-pointing operation. In particular, the first checkpoint word it writes is an header used to detect incomplete checkpoints and reconstruct complete ones, while the last word is a magic number that ends every valid checkpoint. Thus incomplete checkpoints are detected, and can be erased after boot when the energy is available [RSF11].

While this system allows application to run under intermittent power, it does so by introducing significant overhead. Because it uses statically placed check-points, unnecessary and expensive checks could be executed. Moreover, unnecessary state check-points can also be taken if the threshold is not set properly, which incurs in an even greater cost in terms of energy and execution time. Moreover, the system does not take a snapshot until a checkpoint is reached. This means that power failures can happen relatively far from the previous checkpoint, resulting in a higher restore and roll-back cost. In the paper, the authors report an overhead ranging between 65.4% and 360% of the CPU cycles with respect to the uninstrumented program.

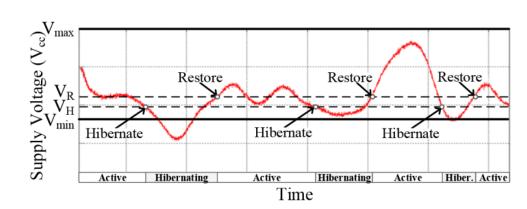

#### Hibernus and Hibernus++

In response to some of the shortcomings of Mementos and other periodic/static checkpointing systems, Balsamo et al. present Hibernus, a software-based approach to sustain computation under intermittent power supply [Bal+15]. Instead of placing checkpoints at compile time, Hibernus saves a snapshot only once immediately before a power failure, and then goes to sleep. The idea is to remove unnecessary checks and thus to minimize the number of backup operations, and also to minimize or remove the overhead of rollbacks. As shown in Figure 1.3, Hibernus compares the supply voltage  $(V_{CC})$  with a given hibernate threshold  $(V_H)$  voltage. If the supply voltage is lower than the threshold  $(V_{CC} \leq V_H)$ , an interrupt is generated, and the system moves from the active to the hibernating state. In the hibernating state, the system immediately saves a snapshot of the full system memory

FIGURE 1.3 – Example of Hibernus execution, from [Bal+15]

and of the registers, and then goes into deep sleep. Another interrupt is used to trigger the restore operation, when the supply voltage raises above the restore threshold  $V_R$  [Bal+15].

The main advantage of Hibernus's approach over Mementos is that the backup is executed on-demand, only when a power failure is deemed to occur. This minimizes run-time overhead, as no checks are executed. However, Hibernus does require full memory backup, as no compile time optimizations are applied. This means that the backup and restore threshold must be selected pessimistically, to have enough energy for a full memory backup. Another issue with Hibernus is that the backup and restore thresholds are statically selected based on an off-line characterization of the platform [Bal+16].

To address this issue, Balsamo et al. propose Hibernus++, an evolution of Hibernus that dynamically adapts the hibernate and restore thresholds based on the system power consumption, the size of the capacitor, and the behaviour of the harvested energy [Bal+16]. When power is harvested, Hibernus++ checks if the system is calibrated, and if not it runs the calibration to set the threshold voltages. Then, the supply is checked to ensure that the system can run. If not, the system sleeps until the energy is sufficient. When the supply test is successful, the system checks if there is a snapshot to be restored. Hibernus++ also detects if the previous snapshot failed and, if so, it increases  $V_H$ . If there is a valid snapshot, Hibernus++ restores the system state and resumes operation, otherwise the computation is started from the beginning. The calibration routine is therefore an iterative process where the platform waits to reach a calibration voltage  $V_{cal}$ , and then disconnect the supply and takes a snapshot. After the snapshot, the voltage level is measured and used to compute the hibernation voltage  $V_H$ . If the calibration attempt fails,  $V_{cal}$  is increased and the calibration retried [Bal+16].

Hibernus++ also tunes the restore strategy based on the characteristics of the harves-

ted energy source. The energy source is characterized as High-Power if the power supplied by the harvester is sufficient to drive the platform. Otherwise, the energy harvester is characterized as Low-Power [Bal+16]. For High-Power sources, the restore can start as soon as the voltage raises above  $V_{min}$ . On the other hand, for Low-power sources, the voltage needs to reach a higher value. Otherwise, the platform pulling more power than the source can immediately drop the voltage, triggering the hibernation procedure and not allowing any progress to be made.

#### Quick-Recall

In [Jay+15], Jayakumar et al. present Quick-Recall, an hardware-software approach for transiently-powered computing. The approach relies on the use of FeRAM, as a superior alternative to Flash memory. Quick-Recall defines the system context to be preserved across power failures, as the program state, the processor state, and the peripheral state [Jay+15]. Quick-Recall uses the FeRAM as its main memory, thus there is no overhead for retaining the program state. The processor state includes all the microprocessor ISA registers, such as the program-counter (PC), stack-pointer (SP), status-registers (SR) and the general purpose registers (GPRs), Quick-Recall saves the values of all this registers to FeRAM in case of a checkpoint. The problem of retaining the peripheral state is delegated to the programmer, as Quick-Recall will use a programmer-defined initialization routine during the restore phase [Jay+15].

The main advantage of Quick-Recall is that it allows to easily adapt an existing program to run in a transiently powered scenario. Moreover, because the system uses FeRAM as its main memory, only the processor registers need to be saved, which means that the overhead of check-points and restores is much reduced. However, the drawback of this approach is that FeRAM requires more energy during the active state and it is slower, with respect to SRAM. This results in slower operation frequency, and the additional power consumption can drain the capacitor faster, resulting in an increased power failure rate. Another drawback of this approach is that is partially susceptible to a broken time machine problem [RL14], as an incomplete check-point would leave the NVM in an inconsistent state. To avoid this problem, QuickRecal writes a flag after each check-point, which is checked and then cleared after the restore. This means that, if a check-point is interrupted, the flag is never set and, at the next restore, the system will restart the application from the beginning, loosing all the progress.

#### eM-map

In [Jay+17], the authors start from the observation that approaches that rely only on NVMs as unified memory for transiently-powered systems (like Quick-Recall [Jay+15]), achieve reliability at the price of energy and performance inefficiencies when compared to SRAM-based systems. On the other hand, SRAM does offer better latency and energy efficiency but is exposed against power losses [Jay+17]. To address these issues, the authors propose eM-map, a energy-aware memory mapping technique, for hybrid FeRAM and SRAM systems [Jay+17]. eM-map treats Functions as the basic units, that can have their text, data and stack sections mapped to either FeRAM or SRAM, while, for simplicity reasons, the heap is unique and mapped exclusively to FeRAM. The best memory mapping for each function, is the one that can complete in one power cycle these three steps: 1) migration, sections mapped to SRAM are moved from FRAM to SRAM, 2) execution of the function, and 3) check-point (moving back data from SRAM to FeRAM), with minimum energy [Jay+17].

At the beginning, all functions are configured to have the three sections mapped on FeRAM (FFF), for which no migration and almost no check-pointing are necessary. To determine the best mapping for each function, a one-time characterization of the functions is run. The test picks a configuration (e.g., FFS), meaning text and data in FeRAM, stack in SRAM), measures the initial voltage, performs the three steps (migration, execution and checkpoint), and then measures the final voltage and energy consumption for the current configuration, updating if necessary the preferred configuration [Jay+17]. To further improve the efficiency of the system, the authors also propose an "Energy-Align" function, that ensures that the three steps (for mappings different than FFF) are executed only if enough energy is available, otherwise shutting-down the platform.

While eM-map provides an optimization of the backup, by finding the best way to map a function in a hybrid NVM-SRAM system, it does so by relying on the assumption that the execution flow of the device is deterministic. As an example, a device might always collect the same amount of data, and performs computation on this data that takes a deterministic amount of clock cycles [Jay+17]. This assumption is necessary to ensure a correct evaluation of migration execution and check-pointing energy cost. This means that this approach is not easily applicable to more general computing task, that might have some non-deterministic or data dependent behaviour. Moreover, the guarantees of consistency against "broken time machine" errors [RL14], are based on the assumption that there is enough energy to complete the function atomically, this is explicitly checked

by the energy-align function. However, if the estimation of the energy consumption for a function is wrong or, for some reason, like aging or other environmental conditions, the system has less energy than what is estimated, the function could still be interrupted, which could result in an inconsistent state.

#### 1.3.4 Sytare

In [Ber+19], Sytare, a lightweight kernel for managing check-pointing and peripheral state on transiently powered systems is presented. While many run-time techniques focus manly on check-pointing the content of main-memory, with Sytare, the authors, also address the issues of persisting the peripheral state in a transiently powered systems. The authors identify three main aspects in dealing with peripheral state persistence: peripheral state volatility, peripheral access atomicity, and interrupt handling. The peripheral state is assumed to be entirely volatile, as complex peripherals, such as a radio chip, would require a new configuration after a power failure. The access to the peripheral should be atomic, which means that if a power loss interrupts the hardware access (such as a radio transmission), the process must be restarted from scratch after the reboot. Finally, the interrupts could modify the data memory or the state of peripherals, causing consistency errors.

To address these issues the authors propose a separation between the application code and the driver code controlling the hardware, with the addition of a thin kernel code layer (Sytare) that works as the interface between the application code and the drivers. This kernel code manages the initialization, check-pointing and restore of the platform. Moreover the driver calls are made accessible through system-calls that wrap the driver code, dealing with guaranteeing the peripheral access atomicity as well as the initialization, save and restore of the peripheral context. Because the system call needs to be repeated in case of a power failure, the system call stack is not saved, instead the system call address, its arguments and a flag that signals that a system call was in progress are saved. This allows the system to replay the system call on reboot, after the state of the platform and the context of the drivers has been restored.

This approach makes it possible to adapt an existing application, to run in a transiently powered scenario with relatively low modifications. However, the system still requires some effort on the part of both the application programmer, as well as the driver developer which needs to write the functions for the actual low level access of the peripheral devices.

For the check-pointing of the application state, Sytare uses a double buffering backup scheme, to be able to restore in case of a power failure during the backup. Similarly to other run-time solutions, the proposed check-pointing method saves the whole volatile state of the application. This makes the backup process slower and more expensive in terms of energy consumption. An improvement on the backup process is proposed in [Ber+20], where the memory protection unit is used to implement a differential backup, so that only the regions of memory that have changed are saved during a check-point.

## 1.4 Architectural (Hardware) Solutions

In recent years, many ways of achieving non-volatility for intermittent platforms have been explored in both industry and academia. Many of the proposed solutions are hardware-based, involving the integration of NVMs in the architecture, which are detailed in this section. Among the hardware-based solutions, many works have presented the implementation of fully non-volatile processor, by exploiting emerging NVMs and implementing non-volatile flip-flops based on different types of NVM devices. Later, in Section 1.5, a brief description of some fully non-volatile processor solutions presented in different papers is given.

## 1.4.1 NVM Integration

The integration of NVMs in the different levels of the memory hierarchy has been explored by many works. NVMs can be integrated both to achieve non-volatility, as well as for other advantages, such as the reduction of leakage energy and the increased density. These characteristics can bring improvements even in domains other than intermittent computing. As an example, both in [Sen+16a] and in [Xue+11], the integration of STT-RAM in the last level cache is explored.

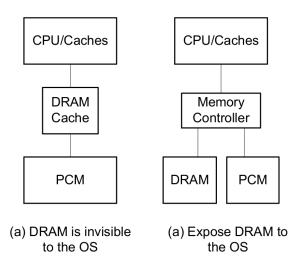

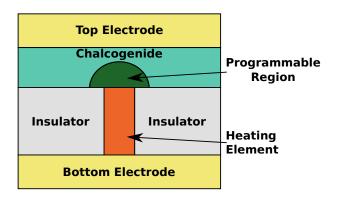

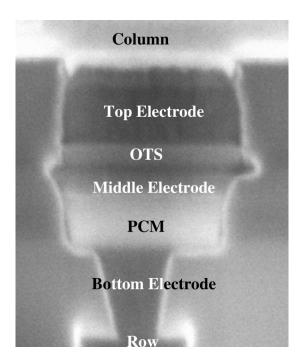

In [Xue+11], an introduction to three NVM technologies: PCM, STT-RAM and RRAM is given. The three technologies are presented with some possible applications especially for PCM and STT-RAM. In particular, PCM is presented both as a possible replacement for Flash, as well as a memory to replace or complement DRAM as the system memory. Figure 1.4 from [Xue+11] shows two possible organizations for a hybrid PCM/DRAM main memory system. The first possibility illustrated by Figure 1.4(a) is

to have a PCM main memory with a DRAM cache in front, to help mitigate the write latency and extend the lifetime of the PCM. This configuration is reported to achieve  $3\times$

FIGURE 1.4 – Hybrid DRAM/PCM main memory organization from [Xue+11].

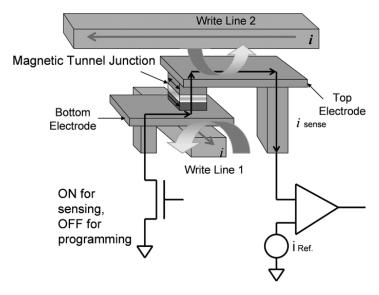

speedup and 3× increase of lifetime, by having a DRAM cache with a capacity of 3% of the PCM storage, while introducing a limited 13% area overhead [Xue+11]. The other organization shown in Figure 1.4(b), exposes both the DRAM and PCM to the operating system (OS). This allows various OS level optimizations to be implemented, to both increase performance and extend the life time of the PCM [Xue+11]. While this approach can be interesting for other domains (e.g., in high-performance computing), it can be difficult to apply in the embedded systems domain, and especially to intermittently-powered systems, which are usually very constrained in terms of power, area and cost. The paper [Xue+11] also presents STT-RAM as a possible candidate for implementing L2/L3 caches taking advantage of 3D integration. In particular, different strategies are analyzed for the implementation of L2/L3 caches with STT-RAM considering many cases such as a full SRAM to STT-MRAM replacement for both L2 and L3 caches, SRAM for the L2 and STT-RAM for the L3, with the possibility of moving the error correction code (ECC) bits of the L2 cache into the STT-RAM based L3 cache.

The use of STT-RAM for the last levels of cache can introduce several advantages. As STT-RAM is much more dense than SRAM, a much larger L2 and L3 cache can be included w.r.t. SRAM with the same area. The presence of an SRAM based L1 can partly hide the speed and energy penalty introduced due to STT-RAM write operations. Moreover, because STT is non-volatile, having an STT-based L3 cache eliminates the

high static power consumption with respect to a standard SRAM-based cache. The main drawbacks of this approaches is cost, as it requires complex packaging (or manufacturing) techniques. Moreover, while some applications can benefit from a larger cache, others can see a performance degradation due to the STT being slower than a traditional SRAM cache.

In [Sen+16a], the impact of the integration of MRAM in the hierarchy is analyzed. In particular, the paper focuses on the L2 cache, though L1 cache is also analyzed. The analysis uses the gem5 processor simulator together with the circuit-level characteristics of the MRAM. Then, the output of gem5 simulation is extracted and the energy consumption of the memory hierarchy is computed. The analysis concluded that replacing SRAM with MRAM in the L2 cache can bring significant advantages, such as reducing the energy consumption thanks to the lower leakage of MRAM. Moreover, because the considered MRAM has a faster read time than the compared SRAM (both in 45nm), there is no more a performance penalty due to the longer write times of MRAM. However, the paper also reports that MRAM is not yet a good substitute for SRAM in the L1 cache, due to its current characteristics, in particular the high write latency.

#### 1.4.2 Brainshift Architecture

In [Hag+17], Brainshift is presented, a method that exploits the scan-chains for the backup and restore operations. Contrary to approaches such as non-volatile flip-flops used in many NVPs [Bar+13; Sak+14; Liu+16], the proposed method tries to avoid introducing modifications and additional hardware to the processor architecture. Instead this work relies on the existing scan-chain circuits, normally used in digital designs for testing purposes, to perform the backup and restore of the internal state of the processor. The micro-controller is divided into two domains: the non-volatile domain (NVD) and the volatile domain (VD), this two domains defines the registers that will be saved and those that will not. Additionally, some non relevant registers inside the NVD do not need to be saved. As an example, the pipeline registers can be excluded from the backup operation. Before executing the backup the processor is put to sleep mode, this ensures that all transactions in the bus are completed. Then, the relevant state in the NVD can be shifted into an Out-of-Place Memory (OoPMem).

Another major difference with other NVPs is that the OoPMem being used in this work, is not a proper non-volatile memory. In fact, this paper proposes the use of a ultra-

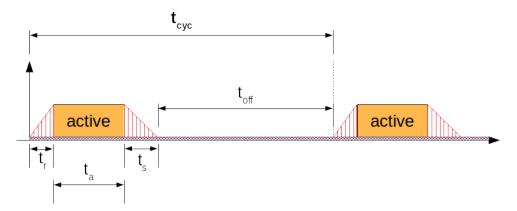

low-power SRAM memory, capable of low-power retention, combined with the use of an auxiliary retention battery. According to the reported numbers, this type of memory, when paired with a small  $50\mu Ah$  battery, is capable of retaining 10kbits for over 2 years. The paper also presents the analysis of two possible approaches for the backup and restore operations: In-Place and Out-of-Place backup. In particular, the total energy consumed during one power cycle  $E_{cuc}$  is considered, and is defined as

$$E_{cyc} = E_{S+R} + t_{cyc}((P_{on} + P_{oh})D + P_{ret}(1 - D))$$

(1.1)

where  $E_{S+R}$  is the energy for saving and restoring the state,  $t_{cyc}$  the total time for a power cycle, D the duty cycle, or the fraction of  $t_{cyc}$  spent in the ON state,  $P_{on}$  the power consumed during the on state,  $P_{oh}$  the power overhead due to the adopted strategy, and  $P_{ret}$  the power necessary to retain the backup information during the OFF time, which can be zero for strategies using non-volatile memories. Figure 1.5 compares the total energy

FIGURE 1.5 – In-Place vs Out-of-Place energy consumption with varying  $t_{cyc}$ .

of In-Place and Out-of-Place strategies, given the parameters reported in Table 1.2. As

Table 1.2 – Parameters for In-Place vs Out-of-Place comparison

|                              | In-Place                                                                 | Out-of-Place            |

|------------------------------|--------------------------------------------------------------------------|-------------------------|

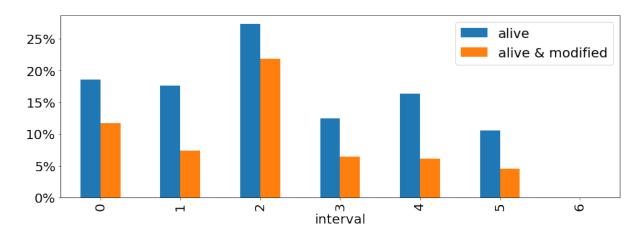

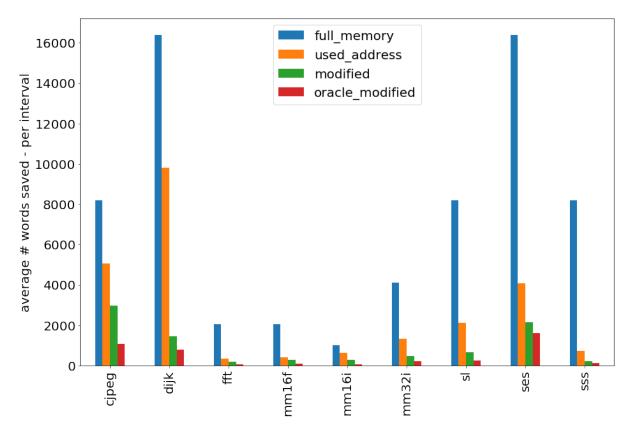

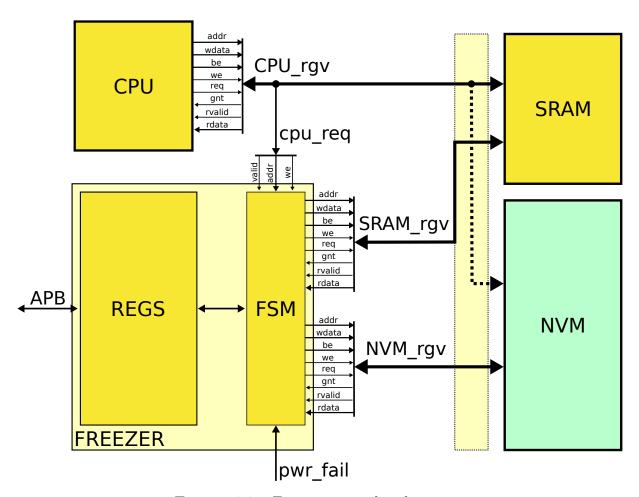

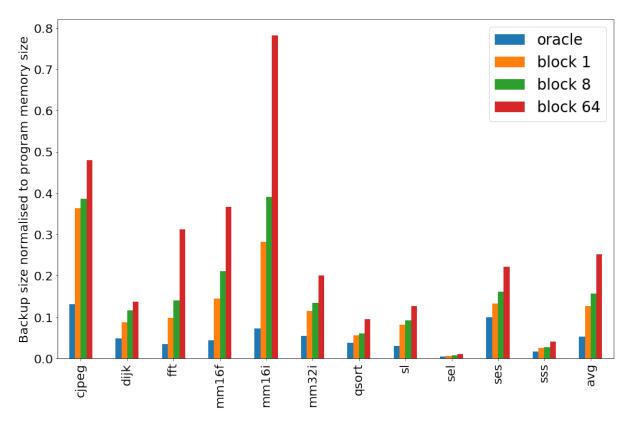

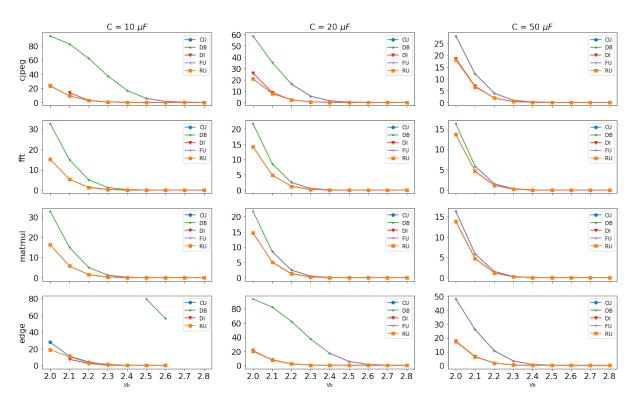

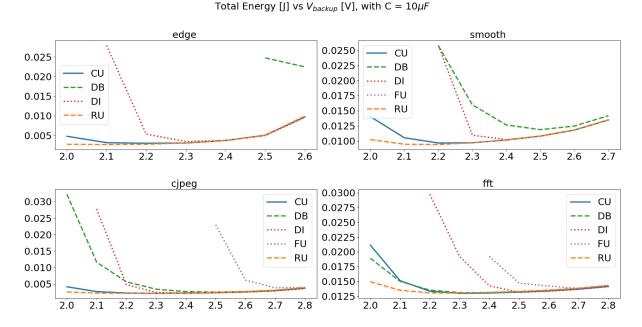

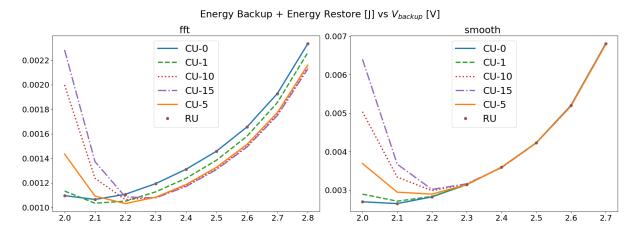

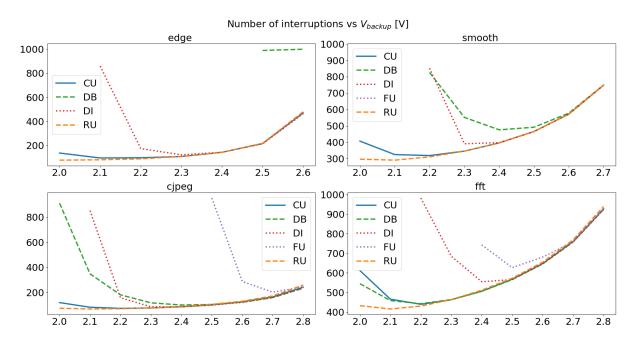

| $E_{S+R}$ $P_{ret}$ $P_{oh}$ | $\begin{array}{c c} 0 \text{ pJ/b} \\ 1 \text{ pW/b} \\ 2\% \end{array}$ | 6 pJ/b<br>30 pW/b<br>0% |