# THÈSE DE DOCTORAT DE

L'UNIVERSITÉ DE RENNES 1 Comue Université Bretagne Loire

ÉCOLE DOCTORALE Nº 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Informatique

#### Par

## « Bahram YARAHMADI »

« Static and dynamic compiler support for intermittently powered computer systems »

Thèse présentée et soutenue à Rennes, le 1er juillet, 2021 Unité de recherche : Institut National de Recherche en Informatique et Automatique (Inria) Thèse N° :

#### **Rapporteurs avant soutenance :**

Abdoulaye GAMATIÉ Directeur de Recherche, CNRS, LIRMM Fabrice RASTELLO Directeur de Recherche, INRIA

#### **Composition du Jury :**

Attention, en cas d'absence d'un des membres du Jury le jour de la soutenance, la composition du jury doit être revue pour s'assurer qu'elle est conforme et devra être répercutée sur la couverture de thèse

| Président :     | Prénom Nom           | Fonction et établissement d'exercice (à préciser après la soutenance) |

|-----------------|----------------------|-----------------------------------------------------------------------|

| Examinateurs :  | Olivier SENTIEYS     | Professeur, Université de Rennes 1                                    |

|                 | Henri-Pierre CHARLES | Directeur de Recherche, CEA                                           |

|                 | Maria MENDEZ REAL    | Maître de conférence, Polytech Université de Nantes                   |

| Dir. de thèse : | Erven ROHOU          | Directeur de recherche INRIA                                          |

#### Invité(s) :

Prénom Nom Fonction et établissement d'exercice

## ACKNOWLEDGEMENT

I would like to express my sincere gratitude to my advisor Dr. Erven ROHOU for giving me the chance to work under his supervision. I would like to thank him for his incredible patience and guidance. He has served as an excellent mentor and advisor with his continuous support and encouragement.

I would like to thank the members of the jury for having agreed to examine my work.

I am extremely thankful to the members of the PACAP team at INRIA for their help, support and kindness. I consider myself truly lucky to have worked with them.

Finally, a special thanks to my parents, family, and friends for their support and for everything they have done for me.

# TABLE OF CONTENTS

| A        | Abstract 9                          |                                                           |                 |  |  |  |

|----------|-------------------------------------|-----------------------------------------------------------|-----------------|--|--|--|

| 1        | Rés                                 | Résumé                                                    |                 |  |  |  |

|          | 1.1                                 | Objectifs                                                 | 12              |  |  |  |

|          | 1.2                                 | Solutions proposées                                       | 13              |  |  |  |

| <b>2</b> | Intr                                | roduction                                                 | 19              |  |  |  |

|          | 2.1                                 | Context                                                   | 19              |  |  |  |

|          | 2.2                                 |                                                           | 21              |  |  |  |

|          |                                     |                                                           | 22              |  |  |  |

|          |                                     | 1 0                                                       | 22              |  |  |  |

|          | 2.3                                 |                                                           | 23              |  |  |  |

|          |                                     |                                                           | $\frac{-3}{23}$ |  |  |  |

|          |                                     |                                                           | 24              |  |  |  |

|          | 2.4                                 | <b>-</b>                                                  | 25              |  |  |  |

|          |                                     |                                                           | _0              |  |  |  |

| 3        | Bac                                 | ekground                                                  | 27              |  |  |  |

|          | 3.1                                 | Introduction                                              | 27              |  |  |  |

|          | 3.2                                 | Intermittent execution                                    | 28              |  |  |  |

|          |                                     | 3.2.1 Persistent memory technologies                      | 28              |  |  |  |

|          |                                     | 3.2.2 Architecture models                                 | 29              |  |  |  |

|          | 3.3                                 | Energy consumption estimation                             | 29              |  |  |  |

|          | 3.4                                 | Worst-case execution time and Heptane                     | 32              |  |  |  |

|          | 3.5                                 | Checkpointing and program resumption strategies           | 34              |  |  |  |

| 4        | WC                                  | CEC-based Checkpoint Placement and Compiler Optimizations | 39              |  |  |  |

|          | 4.1                                 | Introduction                                              | 39              |  |  |  |

|          | 4.2 WCEC-Aware checkpoint placement |                                                           | 39              |  |  |  |

|          |                                     | 4.2.1 Technical background                                | 39              |  |  |  |

|          |                                     | 4.2.2 Approach                                            | 41              |  |  |  |

#### TABLE OF CONTENTS

|          |     | 4.2.3  | WCEC estimation                                       | . 43 |

|----------|-----|--------|-------------------------------------------------------|------|

|          |     | 4.2.4  | Mapping between Heptane and LLVM IR                   | . 45 |

|          |     | 4.2.5  | Coping with non-termination                           | . 45 |

|          |     | 4.2.6  | WCEC-Aware compiler transformations and optimizations | . 46 |

|          | 4.3 | Evalua | ation                                                 | . 48 |

|          |     | 4.3.1  | Settings                                              | . 48 |

|          |     | 4.3.2  | Benchmarks                                            | . 48 |

|          |     | 4.3.3  | Experiments                                           | . 49 |

|          | 4.4 | Conclu | usion                                                 | . 53 |

| <b>5</b> | Dyr | namic  | Checkpoint Placement based on self-modifying code     | 55   |

|          | 5.1 | Introd | luction                                               | . 55 |

|          | 5.2 | Motiva | $\operatorname{ation}$                                | . 56 |

|          | 5.3 | Overv  | iew of SFSG                                           | . 56 |

|          | 5.4 | Static | program preparation                                   | . 59 |

|          | 5.5 | Trace  | management                                            | . 61 |

|          |     | 5.5.1  | Trace collection                                      | . 61 |

|          |     | 5.5.2  | Ephemeral tracing                                     | . 62 |

|          | 5.6 | Runtii | me checkpoint management                              | . 63 |

|          |     | 5.6.1  | Determining checkpoint locations                      | . 63 |

|          |     | 5.6.2  | Specialized checkpoints                               | . 65 |

|          |     | 5.6.3  | Coping with non-termination                           | . 66 |

|          | 5.7 | Evalua | ation                                                 | . 67 |

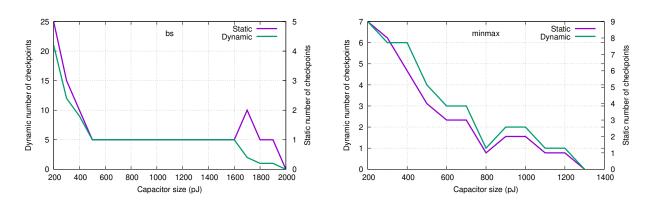

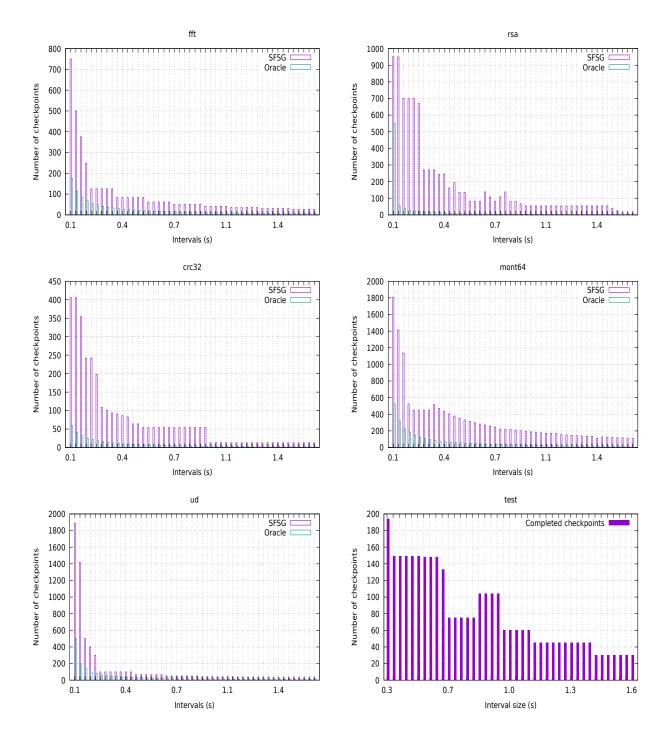

|          |     | 5.7.1  | Number of checkpoints                                 | . 68 |

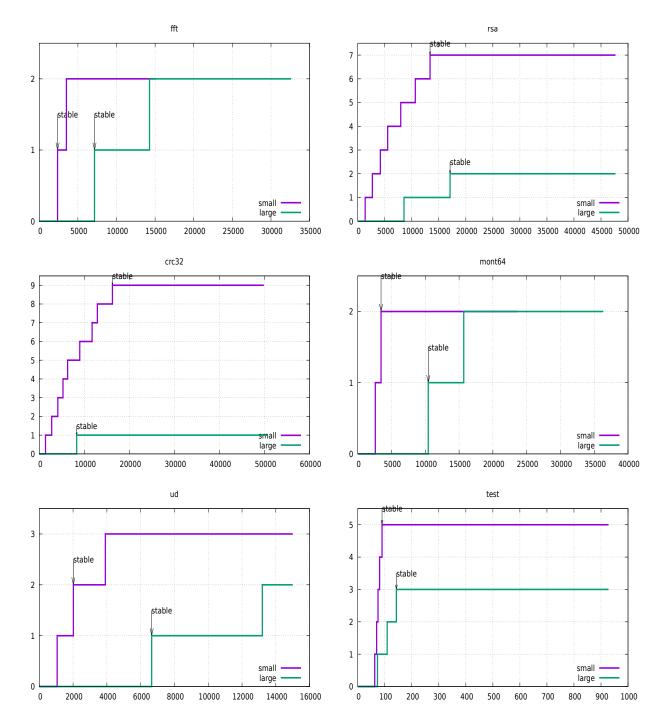

|          |     | 5.7.2  | Stabilization of checkpoint insertion                 | . 70 |

|          |     | 5.7.3  | Tracing overhead                                      | . 70 |

|          |     | 5.7.4  | Code size                                             | . 72 |

|          | 5.8 | Discus | ssion and future extensions                           | . 72 |

|          |     | 5.8.1  | Memory protection unit                                | . 72 |

|          |     | 5.8.2  | Dealing with closed-source                            | . 73 |

|          |     | 5.8.3  | NVM and memory consistency issue                      | . 73 |

|          | 5.9 | Conclu | usion                                                 | . 73 |

|          |     |        |                                                       |      |

## Conclusion

| Appendix A   | 81 |

|--------------|----|

| Bibliography | 87 |

## ABSTRACT

With the advent of Internet of Things (IoT), there is a need to provide energy for a massive number of tiny smart devices without using large, heavy, and high-maintenance batteries. One promising way is to harvest energy from the environment and store it into an energy buffer such as a capacitor which is in charge of supplying energy to the device. However, harvested energy sources are all unstable making the execution of programs intermittent. That is, the program is executed as long as there is available energy in the capacitor, and crashes when it exhausts. As a result, programs with long-running processing time cannot be completed with a single charge of the capacitor. Recently, different software and hardware-based checkpointing strategies have been proposed to make forward progress toward execution for energy harvesting IoT devices. This thesis introduces two different software solutions based on the static and dynamic compilation. The proposed static compiler inserts checkpoints based on statically-computed worst-case energy consumption of code sections. Moreover, it applies classical compiler optimizations in order to decrease the required number of checkpoints at runtime. The proposed dynamic compilation technique shifts checkpoint placement and specialization to the runtime and takes decisions based on the past power failures and execution paths taken before each power failure. Both proposed solutions guarantee making forward progress as well as keeping the memory consistent. Furthermore, they aim to increase portability by not using any hardware feature of the IoT device. In addition, the proposed dynamic compiler approach is transparent to programmers and the proposed static compiler approach limits the burden on programmers to a negligible additional effort.

# Résumé

Nous vivons à l'ère de l'Internet des objets (IoT), où le monde qui nous entoure est composé d'un grand nombre de minuscules objets qui détectent, communiquent et traitent des données dans notre environnement. Pour ces minuscules objets, l'approvisionnement et la consommation d'énergie sont un défi : il n'est pas économiquement viable, ni même physiquement possible de les configurer avec des batteries de grande taille, lourdes et nécessitant beaucoup d'entretien. Récemment, il a été proposé d'utiliser des techniques de collecte d'énergie comme moyen alternatif de fournir de l'énergie sans avoir recours à des batteries. Dans ces techniques, l'énergie est extraite de différentes sources dans l'environnement (par exemple, la lumière du soleil ou le vent) [60, 75] et stockées dans un tampon tel qu'un condensateur. Cependant, l'un des problèmes des sources d'énergie récoltées est qu'elles sont toutes instables. Cette instabilité des sources d'énergie et la faible quantité d'énergie qu'un condensateur peut stocker font que l'exécution des programmes est interrompue par des pannes de courant. Par conséquent, les tâches dont le temps de traitement est long ne peuvent pas être réalisées avec une seule charge du condensateur. Une façon de garantir la progression vers l'achèvement des tâches est de tirer parti de l'idée de prendre des points de contrôle. C'est-à-dire en stockant toutes les données volatiles nécessaires telles que l'état du processeur, la pile de programmes et le tas dans une mémoire persistante avant l'épuisement de l'énergie. Lorsque l'énergie redevient disponible, tout l'état volatil est recopié et le programme peut continuer son exécution.

D'une part, le pointage de l'état volatil du programme dans la mémoire non volatile disponible dans les systèmes embarqués semble prometteur, car un programme peut avoir une exécution intermittente jusqu'à son terme. D'autre part, la prise imprudente de points de contrôle fait soit que le système ne progresse pas, soit qu'il souffre d'une dégradation des performances et de l'énergie. Par exemple, un nombre de points de contrôle inférieur à ce qui est nécessaire, appelé nombre optimal de points de contrôle, fait qu'au moins une partie du code consomme plus d'énergie que la quantité maximale d'énergie dans le condensateur. Par conséquent, la section est exécutée de manière répétée sans aucune progression. Au contraire, en prenant plus de points de contrôle que le nombre optimal, on gaspille l'énergie du système pour effectuer des travaux inutiles, car prendre un point de contrôle n'est pas sans coût. De plus, Ransford et Lucia [61] ont mis en évidence que le fait de prendre des points de contrôle et de reprendre l'exécution peut entraîner des violations de la correction du programme lorsque celui-ci a des effets de bord, comme la modification des données non volatiles. Par exemple, considérons le cas où un point de contrôle est pris et où le programme lit et modifie certaines données en mémoire non volatile. Si une panne de courant se produit avant d'atteindre le point de contrôle suivant, le système doit revenir au point de contrôle précédent et exécuter à nouveau les mêmes instructions. Cependant, la deuxième fois, les données en mémoire non volatile ne sont pas correctes. Pour faire face au problème de performance et au bogue susmentionné, les chercheurs ont proposé différentes approches de solutions entièrement logicielles [51, 23, 52, 69, 8] à des solutions matérielles/logicielles communes [62, 37, 10, 9, 33] ainsi que des solutions uniquement matérielles [81, 73].

Les solutions matérielles et logicielles communes peuvent prendre des points de contrôle au prix de l'ajout de fonctionnalités matérielles supplémentaires ou de l'utilisation des fonctionnalités matérielles des microcontrôleurs du commerce qui sont conçues à l'origine pour être utilisées par le programmeur (par exemple, les minuteries, les CAN) et non par le logiciel système d'un tiers. Toutefois, les solutions au niveau logiciel peuvent résoudre les problèmes d'exécution intermittente sans utiliser de caractéristiques matérielles spéciales ou dédiées. En conséquence, les solutions logicielles sont plus portables. Dans cette recherche, nous abordons les problèmes susmentionnés au niveau du logiciel.

## 1.1 Objectifs

Les objectifs de cette thèse sont :

- permettre d'éviter la non-terminaison du programme et avoir une mémoire cohérente ;

- faciliter la programmation du système de collecte d'énergie, soit en fournissant des solutions transparentes, soit en limitant la charge des programmeurs à un effort supplémentaire négligeable;

- fournir une solution portable ne nécessitant aucun matériel supplémentaire, ni utilisant une fonction matérielle dédiée.

### 1.2 Solutions proposées

Un compilateur statique peut analyser statiquement la consommation d'énergie d'un programme sur un matériel particulier et placer des points de contrôle dans le graphe de flot de contrôle du programme en conséquence. De plus, inspiré de l'idée utilisée dans les compilateurs dynamiques, un compilateur peut suivre l'exécution du programme pour trouver le point où se produit la panne de courant et placer le point de contrôle au moment de l'exécution en conséquence. Cette thèse propose deux solutions indépendantes de compilateurs statiques et dynamiques.

#### WCEC : placement des points de contrôle et optimisation du compilateur

Dans ce travail, nous proposons de définir l'emplacement de ces points de contrôle sur la base de la consommation d'énergie des sections de code, calculée statiquement dans le pire des cas. Nous appliquons également des optimisations classiques des compilateurs afin de réduire le nombre de points de contrôle requis au moment de l'exécution. Comme notre méthode est basée sur la consommation d'énergie dans le pire des cas, nous pouvons garantir la cohérence de la mémoire et l'avancement des calculs.

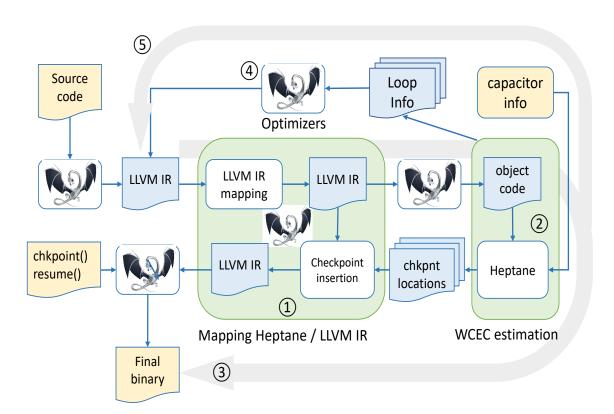

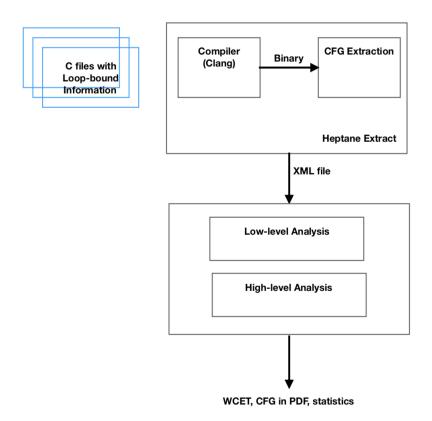

La détermination de l'emplacement des points de contrôle est basée sur le graphe de flot de contrôle (CFG) du programme. Il est similaire au calcul des estimations du pire temps d'exécution (WCET) dans le domaine des systèmes temps réel. L'estimation statique de la consommation d'énergie dans le pire des cas (WCEC) nécessite d'avoir une représentation du programme ainsi qu'un modèle énergétique qui reflète la consommation d'énergie du système. Pour le premier, le CFG du programme représente des structures complexes telles que les boucles, les conditions et les appels de fonction. Pour le second, les modèles énergétiques aux niveaux inférieurs du logiciel tels que l'architecture du jeu d'instructions (ISA) sont plus précis car ils sont plus proches du matériel [28]. Notre mise en œuvre consiste en un composant d'estimation de WCEC fonctionnant au-dessus d'un outil appelé Heptane. Heptane est un outil conçu à l'origine pour calculer le WCET. Il s'agit également d'un algorithme de localisation de points de contrôle. La figure 1.1 montre l'aperçu de notre flux. De plus, comme Heptane ne fonctionne que sur des fichiers binaires exécutables et que notre placement final de point de contrôle se fait au niveau LLVM IR [44], nous avons adopté une cartographie entre Heptane et LLVM IR.

Comme indiqué, l'entrée de la chaîne d'outils proposée est la taille du condensateur et le code C de haut niveau annoté avec des informations liées à la boucle. Il convient de

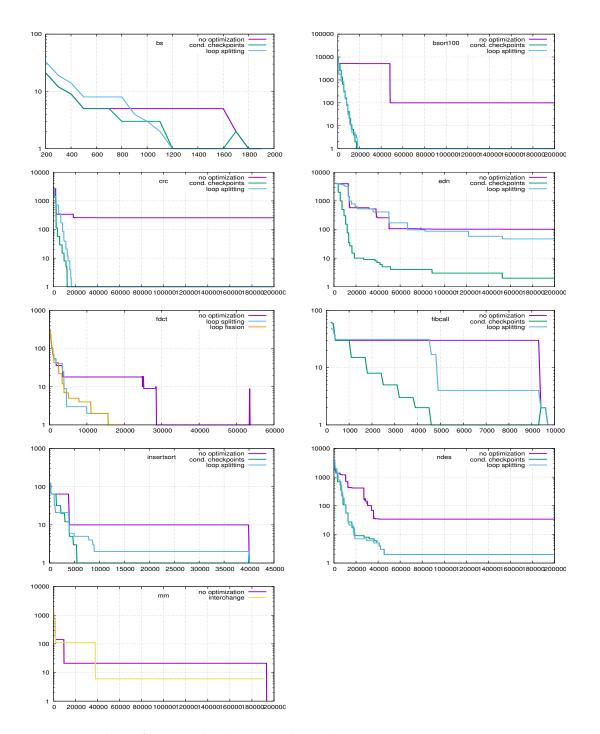

Figure 1.1: Aperçu de notre flux

noter que la spécification des informations liées à la boucle est le seul effort supplémentaire demandé au programmeur. La sortie de notre chaîne d'outils est un code binaire enrichi d'appels de déclenchement de points de contrôle. Chaque déclencheur de point de contrôle est un appel à une bibliothèque d'exécution qui est responsable de la copie de l'état volatile du programme dans la mémoire non volatile. L'overhead et le coût énergétique du contrôle lui-même dépendent fortement de l'architecture sous-jacente. Pour une architecture avec une mémoire non volatile comme mémoire unifiée, le coût du checkpointing est presque constant puisque seuls les registres du CPU doivent être copiés. Cependant, pour les systèmes configurés avec une mémoire volatile comme la SRAM ainsi qu'un type de mémoire non volatile, le coût du contrôle est variable et dépend de l'état du programme comme la taille de la pile et du tas, ainsi que de la quantité de données actives au moment du contrôle. Dans ce dernier cas, nous devons garantir que nous avons suffisamment d'énergie pour effectuer le contrôle dans le pire des cas, et l'emplacement du point de contrôle est important. Dans le pire des cas, le système doit avoir suffisamment d'énergie pour contrôler toute la mémoire volatile du point de contrôle. Notre travail peut fonctionner avec les deux types d'architecture. Cependant, dans ce travail, nous partons du principe qu'il y a toujours assez d'énergie disponible pour contrôler un nombre constant de registres CPU dans le premier cas ou toute la mémoire volatile dans le second cas, et nous nous concentrons sur le placement des points de contrôle qui garantit l'exactitude et la progression. Nous avons appliqué des optimisations du compilateur pour réduire le nombre de contrôles à l'exécution. Notre objectif ici n'est pas de fournir une étude exhaustive de l'impact de chaque optimisation, mais plutôt de démontrer l'avantage de certaines optimisations pour la gestion énergétique des systèmes à alimentation intermittente. Comme les boucles sont la partie des programmes la plus consommatrice de temps et d'énergie, nous avons choisi des optimisations sur les boucles. De plus, le placement de points de contrôle dans les boucles peut augmenter la consommation d'énergie de l'exécution, ce qui rend essentiel de traiter les boucles avec soin. Il est clair que toutes les optimisations ne peuvent pas être appliquées à toutes les boucles, car les dépendances des données doivent être vérifiées pour garantir la préservation de la sémantique du programme. Dans ce travail, nous avons choisi des points de contrôle conditionnels, le fractionnement de boucle, la fission de boucle et l'échange de boucle. Nos résultats montrent que les optimisations ont la capacité de réduire le nombre de points de contrôle nécessaires, ce qui montre que les optimisations classiques des compilateurs peuvent être exploitées pour réduire le nombre de points de contrôle.

#### Placement dynamique des points de contrôle basé sur un code auto-modifiant

Dans ce travail, inspiré par l'idée utilisée dans les compilateurs dynamiques, nous avons adopté un cadre comprenant plusieurs passes d'analyse et de transformation du compilateur ainsi qu'un système d'exécution. Notre travail reporte au runtime les décisions finales concernant l'emplacement des points de contrôle. Les décisions qu'il prend au moment de l'exécution sont basées sur le chemin d'exécution que le programme avait pris avant la panne de courant. De cette façon, le système d'exécution apprend des pannes de courant afin de placer les points de contrôle. Notre travail s'appelle SFSG (So Far So Good). Intuitivement, SFSG est basé sur l'observation qu'un programme IoT exécute une série de tâches en continu pendant une longue période de temps et que les flots de contrôle se répètent pendant l'exécution. Par exemple, les petits dispositifs IoT consistent souvent en une boucle infinie qui détecte certaines données de l'environnement, les calcule, les chiffre éventuellement et transmet le résultat. Mais la répétition du flux de contrôle s'applique - à des degrés divers - également à la plupart des applications. C'est la raison d'être des optimisations guidées par profiling, mais aussi des caches d'instructions et des

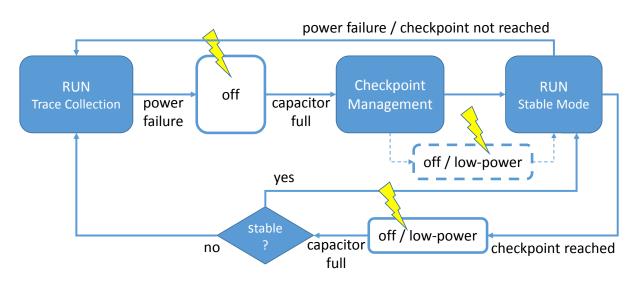

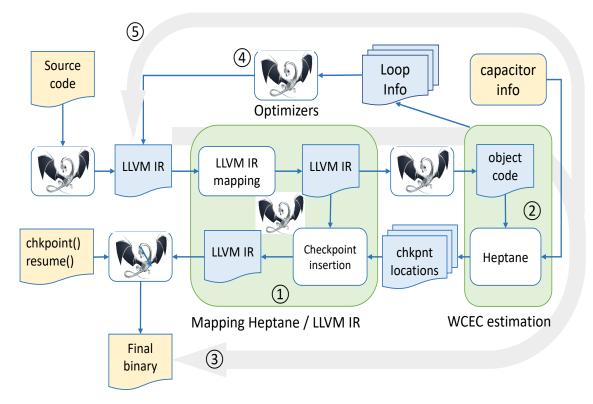

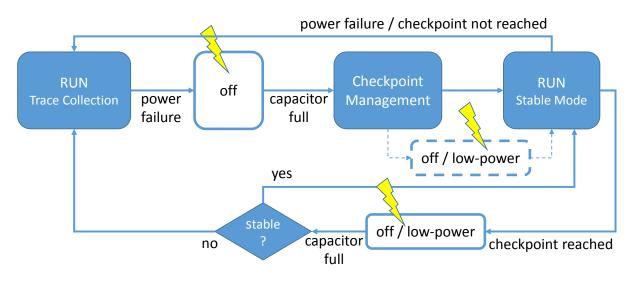

Figure 1.2: Flux des états d'exécution

prédicteurs de branchements. En bref, nous laissons le programme s'exécuter, légèrement modifié pour générer une trace d'exécution en mémoire non volatile, jusqu'à épuisement de l'énergie. Lorsque l'énergie reprend, et que le système redémarre, nous savons, grâce à la trace, où il s'est arrêté. Nous insérons un point de contrôle un peu avant, et nous relançons l'exécution depuis le début. Avec un peu de chance, l'exécution atteint le point de contrôle. La ré-exécution reprendra à partir de ce nouveau point, garantissant ainsi une progression vers l'avant. Si le point de contrôle n'est pas atteint, nous l'insérons un peu plus tôt dans le CFG et reprenons l'exécution. Au point de contrôle, nous attendons que le condensateur soit complètement rechargé. Notre système paie une pénalité lorsqu'un chemin de code est vu pour la première fois. Un prix plus élevé est payé si les chemins de contrôle changent souvent. Cependant, même dans ce dernier cas, notre système reste correct et progresse dans son exécution : nous ne sommes pas limités à une classe particulière de programmes.

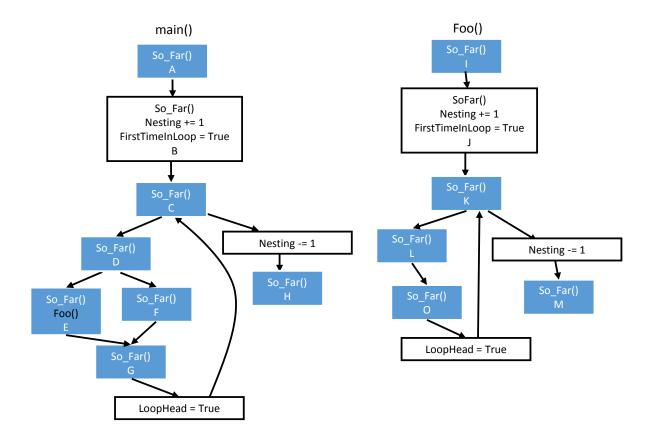

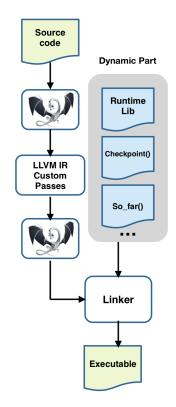

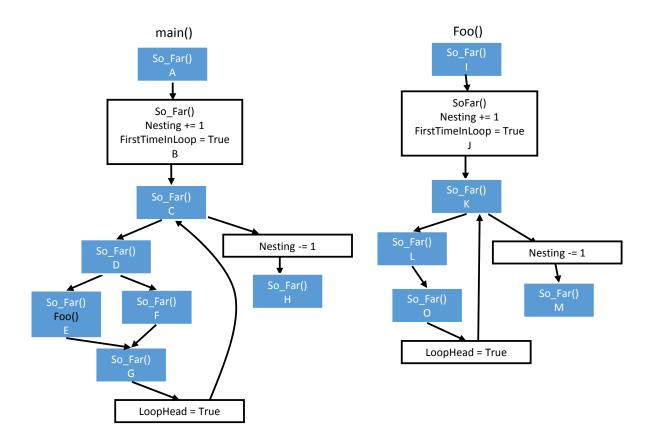

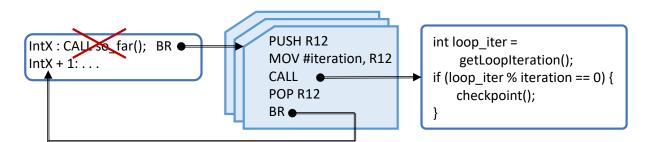

Le système d'exécution (la partie dynamique) est responsable de l'orchestration globale des différentes étapes en jeu. Il est illustré par une machine à états finis dans la figure 1.2. La phase statique transforme les CFG, extrait les propriétés du programme. Elle permet également au programme d'ajouter des points de contrôle à différents endroits. La figure 1.3 montre comment main() et Foo() Les CFGs sont transformés. La combinaison de la partie statique et de la partie dynamique peut fournir un mécanisme permettant de collecter des traces d'exécution lorsque le programme est en cours d'exécution. La trace peut fournir des informations sur le moment où la défaillance s'est produite. Le système d'exécution peut placer un point de contrôle dans le code sur la base des informations de

Figure 1.3: Transformations statiques des CFGs

la trace. En outre, SFSG découvre automatiquement les parties du code qui consomment plus d'énergie que le condensateur du microcontrôleur ne peut en fournir et insère des points de contrôle pour garantir la terminaison. Nous avons évalué SFSG sur un système à base de TI MSP430, avec différents types de bechmarks ainsi que différents intervalles d'interruptions pour simuler des pannes de courant. Dans tous les cas, SFSG pourrait permettre de progresser sans devoir s'interrompre.

## INTRODUCTION

### 2.1 Context

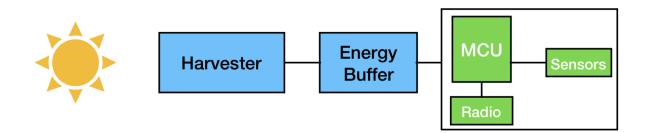

A new kind of computing systems has recently emerged, loosely referred to as Internet of Things (IoT) devices. While these devices broadly differ in purposes and form factors, many are tiny and meant to be deployed in hard-to-reach locations to monitor various properties (temperature of remote places, solidity of bridges...). For this reason, they are not equipped with batteries. Instead, they harvest energy from their environment to fill an energy buffer. They run until the energy buffer depletes and stop. The energy buffer is responsible for providing the energy of the device. When it runs out of energy, the device stops executing tasks and waits until the energy level of the energy buffer reaches a threshold. Figure 2.1 shows the schematic of an energy harvesting device. It contains a microcontroller (MCU) having peripherals such as sensors and radio to interact with the world. Also, it includes a capacitor acting like an energy buffer for the device. The harvester is another entity of an energy harvesting device that is in charge of extracting energy from the environment and storing it in the energy buffer.

There are various energy harvesting sources. Radio frequency (RF) [84], solar [60], thermal [50], kinetic [11] and vibration [74] are examples of energy harvesting sources that are accessible depending on the environment. However, one problem with these sources of energy is that they are all unstable. This instability of energy sources and the small amount of energy a capacitor can store make the execution of programs interrupted by power failures. As a result, tasks with long running processing time cannot be completed with a single charge of the capacitor, because, after each power failure, the execution starts from the beginning. One way to guarantee forward progress to the completion of tasks is by leveraging the idea of taking checkpoints used in distributed systems. In a distributed system checkpointing is a highly used technique to provide fault tolerance and rollback recovery by saving a snapshot of necessary information periodically. These information are stored in a stable storage such as a disk. Therefore, when a system crashes due to a

Figure 2.1: The schematic of an energy harvesting system

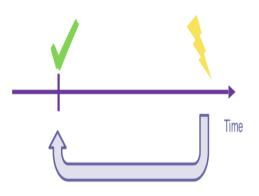

Figure 2.2: Rollback to a checkpoint location

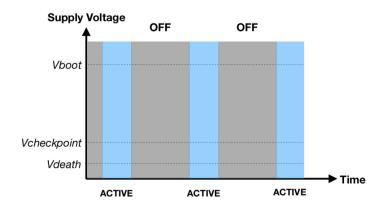

failure, it can be re-stared and roll back to the point that the checkpoint had been taken and resume its execution [42]. This technique can be used in an energy harvesting device that is subjected to power failures because of energy depletion. Herein, a checkpoint can be taken by storing all necessary volatile data such as processor state, program stack, and global variables into a persistent memory before energy depletion. In this way, when the energy becomes available again after the power failure, all the volatile state will be copied back and the program can continue its execution. Figure 2.2 shows rolling back to a location where a checkpoint has been taken when a power failure happens during the execution time. It is worth noting that the MCU of the energy harvesting device includes a type of persistent memory to store non-volatile data such as the text (code segment) of the program that can be used to store checkpoint data as well. As a result of checkpointing and the abundant power failures, programs running on an energy harvesting device are executed intermittently. That is, a program is executed as long as there is available energy in the capacitor, and crashes when it exhausts. It waits until the energy will be available again to resume the execution. Figure 2.3 shows that an energy harvesting device is switching between two cycles during its lifetime. When the voltage is at Vdeath, the

Figure 2.3: Various starges and cycles of an energy harvesting device

device is off or it does not have energy to proceed with the execution of the program. In this stage, the device is extracting the energy from the environment. When the voltage of the capacitor reaches a specific threshold (Vboot), the device starts a new life-cycle and resumes the execution of the program that had been interrupted. Taking checkpoints also consumes energy and the cycles of the system that must be taken into consideration. For that, in some energy harvesting devices, a new voltage threshold for specifying the point of checkpoint must be set. For instance, in Figure 2.3, when the voltage is at Vcheckpoint, the system still has the energy to take a checkpoint.

There are some issues related to this model of execution which we discuss in this Chapter.

### 2.2 Problem definition

Writing programs that are executed intermittently is challenging as the program execution might be interrupted frequently because of the unpredictable nature of energy sources. Even with the existence of the checkpointing mechanism, it is not always guaranteed that the program will make forward progress to the completion. The programmer must be sure that the program will complete its task when it is running in the deployment environment. In addition, another unique bug of energy harvesting devices that use checkpointing techniques is related to the consistency issue of persistent memories which may lead to program correctness violation. In this thesis, we define the former problem as Lack of forward progress and the latter as Inconsistent memory.

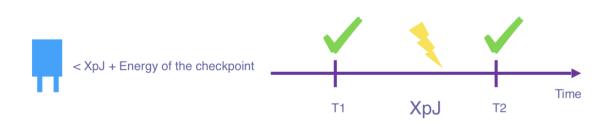

Figure 2.4: Lack of forward progress

#### 2.2.1 Lack of forward progress

As checkpoints have overhead, they can affect the overall performance of the system in terms of execution time and energy consumption. Taking checkpoints too early wastes the energy and cycles of the system for useless work. On the other hand, taking checkpoints too late, may put the system at risk of unhandled power failure. In the worst case, the program faces non-termination when the code between two checkpoints requires more energy than the capacitor can provide. Consequently, the program cannot reach the next checkpoint and will face power failure each time it tries to re-execute the code from the first checkpoint location. This is one of the novel bugs introduced by intermittent execution. Figure 2.4 shows that there are two checkpoints in the program (in times T1 and T2). For reaching the second checkpoint from the first checkpoint, XpJ of energy is needed. Plus, the energy consumption of the checkpoint itself must be taken into account. However, the capacitor cannot provide this amount of energy.

#### 2.2.2 Inconsistent memory

A program under intermittent execution may face a memory inconsistency issue when it uses both volatile and non-volatile memory of the system for allocating variables and data, and they are involved in an instruction sequence that performs Write-After-Read (WAR) [69]. In this scenario, re-executing instructions due to the checkpointing and resuming may lead to program correctness violations. For example, consider a case that a checkpoint is taken and then the program reads and modifies some data in non-volatile memory. If a power failure happens before reaching the following checkpoint, the system must roll back to the previous checkpoint and re-execute the same instructions. However, the second time, the data in non-volatile memory are not correct. Figure 2.5 illustrates an example with two pieces of code containing checkpoint trigger calls. In this example, the variable X is allocated in non-volatile memory by the programmer. The value of variable

```

NV int X; NV int X;

X = 0; __checkpoint();

__checkpoint(); X = 0;

X++; X++;

// Power failure // Power failure

send(X); send(X);

(a) (b)

```

Figure 2.5: Memory inconsistency problem

X at the end of the continuous execution (execution without power failure) of these code sections will be 1. However, if after statement X++ a power failure happens, in (a), the system rollbacks to the last checkpoint location which is a line just before the statement and re-execute the statement again. As a result, the value of variable X that is going to be sent at the end will be 2. The reason behind this is that the statement X++ is WAR to the non-volatile variable X. In (b), the value at the end will be still 1 as the checkpoint trigger call is before the statement X = 0 and the sequence of statements X = 0 and X++ is *idempotent*. A piece of code is *idempotent* if repeated subsequent invocations do not modify the state of the machine. In (b), the aforementioned sequence performs WARAW and the write before the first read makes the sequence idempotent.

## 2.3 Contribution

To cope with the aforementioned performance issues and bugs, researchers have proposed different approaches from fully software solutions [51, 23, 52, 79, 69, 8] to joint hardware/software solutions [62, 37, 10, 9, 33] as well as hardware-only solutions [81, 73]. Hardware based and joint hardware/software solutions can take checkpoints at the cost of adding additional hardware features or using hardware features of the commercial MCUs which are originally designed to be utilized by the programmer (e.g., timers, analog-todigital converters) and not by the third-party system software. However, software level solutions can cope with the problems of intermittent execution without using any special or dedicated hardware feature. As a result, software solutions are more portable. In this research, we address the aforementioned problems in software level.

#### 2.3.1 Objectives

The objectives of this thesis are :

— to provide forward progress without facing non-termination as well as to have a

consistent memory;

- to ease programming of energy harvesting system either by providing transparent solutions or by limiting the burden on programmers to a negligible additional effort;

- to provide a portable solution by not requiring any extra hardware or using any dedicated hardware feature.

#### 2.3.2 Proposed solutions

A static compiler can statically analyze the energy consumption of a program on a particular hardware and place checkpoints trigger calls into the control flow graph (CFG) of the program accordingly. Also, inspired by the idea used in dynamic compilers, a compiler can track the execution of the program at runtime to find the point that power failure happens and place the checkpoint at runtime accordingly. This thesis proposes two independent static and dynamic compiler solutions :

#### Static Checkpoint Placement

In this static compiler approach, we propose to define these checkpoint locations based on statically-computed worst-case energy consumption of code sections. We also apply classical compiler optimizations in order to decrease the required number of checkpoints at runtime. This work was presented in **International Conference on Embedded Computer Systems: Architectures, MOdeling and Simulation (SAMOS 2020)** and will be explained in detail in Chapter 4.

#### **Dynamic Checkpoint Placement**

In this work, inspired by the idea used in dynamic compilers, we propose SFSG: a dynamic checkpoint placement and specialization strategy which delays checkpoint placement and specialization to the runtime and takes decisions based on the past power failures and execution paths taken before each power failure. The goal of SFSG is to provide forward progress and to avoid facing non-termination without using hardware features or programmer intervention. This work was presented in **International Workshop on Software and Compilers for Embedded Systems (SCOPES 2021)** and will be presented in Chapter 5.

## 2.4 Organization of thesis

The reminder of this thesis is organized as follows. Chapter 3 reviews the state of the art in intermittent execution. It also provides background information needed for better understanding this thesis work. Chapter 4 presents our static checkpoint placement strategy for intermittent execution. Chapter 5 presents our dynamic checkpoint placement strategy. Finally, Chapter 6 presents the conclusion of this thesis as well as possible future work.

## BACKGROUND

## 3.1 Introduction

We live in the era of Internet of Things (IoT) where the world around us is surrounded with a large number of tiny objects sensing, communicating and processing data in our environment. For these tiny objects, energy provision and consumption are challenging: it is not economically viable, or even physically possible to configure them with large, heavy, and high maintenance batteries. Recently, using energy harvesting techniques as an alternative way to supply energy without resorting to batteries has been proposed. In these techniques, energy is extracted from different sources in the environment (e.g., sun light or wind) [60, 75] and stored in a buffer such as a capacitor. However, one problem with harvested energy sources is that they are all unstable [40, 83]. This instability of energy sources and the small amount of energy a capacitor can store make the execution of programs interrupted by power failures. As a result, tasks with long running processing time cannot be completed with a single charge of the capacitor. One way to guarantee forward progress to completion of tasks is by leveraging the idea of taking checkpoints. That is, storing all necessary volatile data such as processor state, program stack and global variables into a persistent memory before energy depletion. When the energy becomes available again, all the volatile state will be copied back and the program can continue its execution. On one hand, checkpointing volatile state of the program into the non-volatile memory available in embedded systems seems to be promising, as a program can have intermittent execution to completion. On the other hand, incautious taking of checkpoints either makes the system not to have forward progress or to suffer from performance and energy degradation. For instance, fewer checkpoints than what is needed, called the optimal number of checkpoints, causes at least a section of code to consume more energy than the maximum amount of energy in the capacitor. As a result, it makes the section to be executed repeatedly without any forward progress. This is a unique bug in intermittent computation jargon which is also called facing non-termination. On the contrary, taking

more checkpoints that the optimal number, wastes the system energy for doing unnecessary work, since taking checkpoint is not without cost. Also, Ransford and Lucia [61] pinpointed that checkpointing and resuming execution may lead to program correctness violations when the program performs side-effects, such as changing non-volatile data. For example, consider a case that a checkpoint is taken and then the program reads and modifies some data in non-volatile memory. If a power failure happens before reaching the following checkpoint, the system must rollback to the previous checkpoint and re-execute the same instructions. However, the second time, the data in non-volatile memory are not correct.

This chapter overviews the technologies and solutions around energy harvesting systems as well as fundamental methods that are used in this thesis. Section 3.2 outlines technologies used in energy harvesting systems including memory technologies and architecture models. Section 3.3 briefly overviews the techniques for estimating the energy consumption of programs and discusses the advantages and discusses advantages and disadvantages of each work. Section 3.4 briefly introduces the tool the we extensively used to prototype the proposed static checkpoint placer. Section 3.5 reviews some of the existing solutions to cope with the problems related to intermittent execution of programs.

### **3.2** Intermittent execution

As mentioned earlier, with the help of checkpoints, a program can survive power failures and resume its execution. The checkpoint overhead and the amount of checkpoint data are highly dependent on the architecture model and the type of persistent memory used in the device. Also, depending on the architecture of the device and how checkpoint data are stored, the system may suffer aforementioned memory inconsistency problem. In this Section, we briefly introduce persistent memory technologies that can be used in an energy harvesting device. Also, we discuss two architecture models previously presented for energy harvesting systems.

#### 3.2.1 Persistent memory technologies

Persistent memories can preserve data when the device is off. One of the most known types of persistent memories is Flash. This non-volatile memory can store checkpoint data in an energy harvesting device. However, a Flash write operation can only switch a memory cell from 1 to 0. Switching a memory cell from 0 to 1 requires erasing a large block of memory. As a result, the process of writing to Flash consumes a significant amount of energy and power resulting in the performance degradation of the whole system. Recently, with the advent of new byte-addressable non-volatile memory technologies (e.g., FRAM<sup>1</sup>, MRAM<sup>2</sup>), the process of writing has been enhanced. These memories are superior to Flash memory in terms of power consumption and latency [15]. As a result, the process of taking checkpoints in intermittent computation is more efficient with these memories and outperforms systems configured with Flash memories [35]. Non-volatile memory technologies are different in terms of endurance, capacity, read/write asymmetry, energy consumption and latency. The proposed solutions in this thesis are expected to be compatible with any type of non-volatile memory.

#### 3.2.2 Architecture models

The de facto standard architecture model for intermittent computation is a hybrid model where SRAM is used as volatile memory and a type of non-volatile memory such as FRAM [25] or Flash as the persistent memory. In this model, the NVM is used for program text and backup data. At the time of checkpoint, the volatile state of the program in SRAM such as program stack and global variables as well as CPU registers must be copied to NVM. In this model, the overhead of checkpoint is variable and dependent on, such as the size of stack, as well as the amount of live data at the time of checkpointing. The alternative model for hybrid model is an architecture with fully non-volatile memories. In this model, NVM is used as a unified memory which means that the program's data and stack are also stored in NVM. This can decrease the amount of data that is needed to be backed up at the time of taking checkpoint as only CPU registers are needed to be backed up. However, the performance of the whole execution of a program may suffer because of the NVM's higher access latency and energy consumption in comparison to SRAM [36].

### **3.3** Energy consumption estimation

Estimating energy consumption of energy harvesting systems is necessary, as one way to provide solutions to problems related to intermittent computation is by having a good

<sup>1.</sup> Ferroelectric RAM

<sup>2.</sup> Magnetoresistive RAM

understanding of the energy consumption of the micro-controller (MCU). As we will see in the next chapter, our static checkpoint placement strategy is based on energy consumption estimation. Moreover, to estimate the energy consumption, an energy model is needed. This section reviews previous work on energy consumption.

There are two main approaches to determine the energy consumption of a program on a particular hardware: measurement based techniques and solutions based on static analysis and estimation. Although approaches based on physically measuring the energy consumption of the device are likely to determine the most accurate energy consumption, they require having knowledge and expertise of using sophisticated equipment which for software people is hard and painful. This process can be worst when some MCUs do not provide hardware components for energy measurement [27]. Also, as we will see, measurement based techniques cannot guarantee a safe upper bound estimation of the energy consumption. On the other hand, energy estimation techniques based on static analysis requires to have an energy model defining the energy costs. These energy costs or models can be provided by the hardware manufacturer. However, for most commercial processors these models are not available. As a result, people resort to measurement techniques to construct the energy model.

Estimating energy consumption and constructing energy model have been explored in various levels of the computer system stack. For instance, energy consumption can be estimated in the instruction level architecture (ISA) level by estimating the energy consumption of each instruction. The first instruction level power analysis was proposed based on current drawn of the processor while it executes certain instructions repeatedly for measuring the base energy cost of each instruction together with inter-instruction effects such as circuit state overhead [67, 68]. Inspired by Tiwari work [67], people proposed an energy model for a simple deterministic multi-threaded architecture [41]. Also, Chakrabarti et al. [20] present an instruction level power analysis technique based on gate level power estimation requiring access to the gate level or at least RTL level description.

Above the ISA level, researchers have shown the feasibility of the energy estimation in compiler intermediate representation (IR) level. Grech et al. [29] have developed a static analyzer working on the LLVM IR [44]. It estimates the energy consumption based on the extracted cost relations from the program. These cost relations are recursive equations that are extracted from a program, representing the cost of running the program in terms of its input [29, 6].

A few researchers based on the idea from classical worst-case execution time analy-

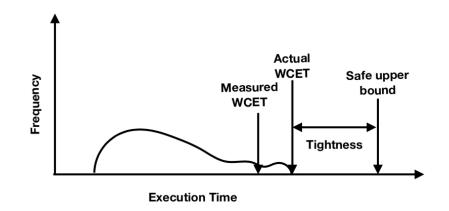

Figure 3.1: Safety and tightness

sis (WCET) [76] have proposed worst-case energy consumption (WCEC) analysis. They tried to benefit from the considerable research on WCET to compute WCEC, as the terminologies used in WCET, can also be applied to WCEC analysis (see Section 3.4). To the best of our knowledge, the work proposed by Jayaseela et al. [38] was the first work to compute worst-case energy consumption. It is stated in the paper that because of the dynamic energy due to switching activity in the circuit, the path corresponding to the WCET of a program may not coincide with the path consuming maximum energy [38]. As a result, using WCET to compute WCEC is not always appropriate. However, they broadly used similar methodologies used in WCET estimation in their work to estimate WCEC.  $\theta q$  [71] is another tool for estimating WCEC. If an accurate energy model for the target architecture is available, it computes an upper bound for WCEC by statically analysing the program code. Otherwise, it uses techniques such as genetic algorithm besides measurement techniques to construct an energy model for the target architecture. Moreover, as the energy model may not be available for commercial off-the-shelf hardware platforms and it is an important property for both WCEC and WCET, people have proposed [65, 64] automatic benchmark generators along with measurement techniques to find an appropriate input that can result to WCEC or WCET. There are some issues which are specific to the energy consumption and cannot be inspired by execution time approaches. For instance, external features of a device significantly contribute to the energy consumption. Unlike  $\theta q$  and other WCEC tools, sys WCEC[70] takes into account the energy consumption of peripherals. Pallister et al. [59] explored the contribution of the operand data on energy consumption. They have showed that unlike execution time, energy is data dependent. Morse et al. [57] proved that determining exact worst-case energy

Figure 3.2: The schematic of a WCET tool

consumption with the high level of accuracy in terms of tightness is NP-hard. Therefore, providing a safe upper-bound comes with over estimation proportional to data-dependent energy.

## **3.4** Worst-case execution time and Heptane

In static WCET analysis the goal is to have a **safe** as well as a **tight** estimation on execution time of a program executing on a hardware. **Safety** means that the actual execution time must be less than, or equal to, the estimated upper-bound, regardless of program input. **Tightness** means that the estimation must be as close as possible to actual WCET. Figure 3.1 illustrates these two important properties of the WCET. Thanks to the extensive research in the WCET analysis, there are commercial and open source static WCET tools [1, 2, 31, 3, 4, 63]. Figure 3.2 shows the schematic of a WCET analysis tool called Heptane [31]. Heptane's functionality is divided into two separated

```

#include "annot.h"

int i;

for (i = 0; i < 10; i++) {

ANNOT_MAXITER (10)

. . .

}</pre>

```

Figure 3.3: A loop annotated with loop-bound information

#### components: Heptane Extract and Heptane Analysis.

Heptane Extract generates control flow graphs (CFGs) from source code files written in C or assembly. First, it calls the compiler and linker to generate the binary code. Then, it splits the binary code into basic blocks. A basic block is a sequence of instructions with a single entry and a single exit point. A CFG is a directed graph where each node is a basic block and each edge represent a possible control transfer between two basic blocks. The generated CFG is stored in an XML file inorder to be used by Heptane Analysis. Finally, Heptane Extract identifies loops and adds loop-bound information provided in the source code into the same XML file. The loop-bound information is one of the constraints of Heptane and the programmer is responsible to provide it for each loop via annotations. Figure 3.3 shows a simple loop that is annotated with loop-bound information. It is worth mentioning that Heptane does not also have support for indirect jumps, jump tables, and pointers to function.

Heptane Analysis generally applies several types of analysis on a program. These analyses extract information require to compute WCET from the program. They are applied on various levels of program representation such as object code or source code. The two major analyses are known as high-level analysis or path analysis and low-level analysis. The low-level analysis accounts for low-level features of the processor based on the cost model. Heptane Analysis also supports cache analysis, data address analysis, and pipeline analysis. The high-level analysis determines the longest execution paths among all possible flows in a program. It uses the most prevalent technique for high level analysis to compute WCET called Implicit Path Enumeration Technique (IPET) [48]. It is based on Integer Linear Programming (ILP) formulation of the WCET calculation problem. The output of Heptane Analysis is one scalar number considered as WCET of the whole program. Also, Heptane Analysis can produce statistics about cache as well the CFG of the program in pdf format.

## 3.5 Checkpointing and program resumption strategies

As mentioned earlier, as a result of unstable energy sources providing the energy of the MCU, a program execution may suffer from abundant power failures. These frequent power failures are unexceptional and unavoidable. Therefore, providing a program resumption strategy is obligatory to make the program continue its execution to completion. Check-poiting program state into the non-volatile memory is a resumption strategy to make programs survive from failures. However, as it is mentioned before, injudicious check-pointing may rise performance and correctness issues. In this section we review proposed checkpointing solutions and other program resumption strategies used in intermittently powered system.

Researchers have proposed software-only, joint hardware/software as well as fully hardware solutions for making forward progress as well as program correctness in energy harvesting systems. In this section, we will discuss them briefly. Software-only approaches resort to pure software such as a compiler and they do not use any special or dedicated hardware feature of the MCU. Joint hardware/software solutions make use of both hardware features of the MCU (e.g., peripherals of the MCU such as a timer or the ADC of the system ) and system software (e.g., compilers, linkers). Hardware solutions try to overcome the problems by modifying the hardware or in the extreme case they come up with a new hardware. It should be noted that this categorization is not strict and depends on the definition of the proposed solution and the context.

#### Joint hardware/software solutions

To the best of our knowledge, Mementos [62] was the first solution that brought the old concept of checkpointing in large scale and high-performance computing (HPC) to energy harvesting MCUs and made the programs continue their execution across power failures. At compile-time, it instruments trigger points at different program locations such as loop-latches (aka tails of back-edges), and function returns. These trigger points are calls to a function that estimates the available energy at run-time by comparing the capacitor's voltage with a predefined threshold with the help of an analog-to-digital converter (ADC). If the voltage is below the threshold, Mementos checkpoints volatile state of the system onto non-volatile memory. Otherwise, the system continues its normal execution. A driving principle of Mementos was to "reason minimally about energy at compile time, maximally at run time", because even expert programmers are not reliable when reasoning about energy. However, reading the capacitor voltage with ADC regularly consumes a significant amount of energy. The first version of Mementos uses Flash as the persistent memory which has high write energy overhead.

A few work such as QuickRecall [37], Hibernus [10] and Hibernus++[9] prefer to do on-demand checkpointing (aka Just-In-Time checkpointing [54]) as well as using FRAM as the persistent memory. They monitor the voltage of the capacitor of the system by using hardware support and like Mementos when the voltage is below a threshold, they backup the volatile state. By specifying a proper threshold, they perform efficiently. However, the threshold for each program is different as each program has its own data-size and memory footprints. As a result, finding the threshold is challenging. One of these works [37] uses FRAM as a unified memory which means that programs data and stack are also stored in FRAM. This can decrease the amount of data that is needed to be backed up at the time of checkpointing as only CPU registers are needed to be backed up. However, the performance of the whole execution of a program may suffer because of the FRAM's higher access latency in comparison to SRAM. Jayakumar et al. [36] proposed a mapping technique that maps different program sections in a hybrid FRAM-SRAM MCU aiming to minimize the overall energy consumption. Flexicheck [66] is another software/hardware solution trying to predict future energy profiles based on specific knowledge of the unit that excites the harvester. There are a few works supporting the idea of runtime checkpointing adaptivity by utilizing the timer of the MCU and relying on the timing [53, 21].

#### Software solutions

Software solutions rely on compilers and/or programmers. A type of software solution that includes modification in the programming language as well as additional responsibilities for the programmer is known as task-based programming models [51, 23, 52]. In a task-based programming model, the programmer is responsible for dividing the code into atomic sections called tasks. These tasks can be re-executed without having side effects on the non-volatile memory. Therefore, the main goal of these models is to cope with the memory consistency issue when the program is being executed intermittently and has allocated data in non-volatile memory. These models apply different methods to take checkpoints and guarantee memory consistency. Dino [51] ensures about non-volatile data consistency with a mechanism called data versioning. That is, making a volatile copy of non-volatile data that are potentially inconsistent. Chain [23] uses a channel-based memory model. In this model data are send and receive per each pair of tasks. Task's inputs and outputs are stored in distinct memory locations ensuring memory consistency. Alpaca [52] uses automatic privatization. It detects shared variables between tasks and copies them into a private buffer of each task. At the end of the task, modified variables are committed to the main memory. However, in these models, the programmer must be sure that a task's energy consumption does not exceed the maximum available energy in capacitor. Otherwise, the system would face the forward progress problem known as non-termination and would execute the same task repeatedly. To make sure that the application have forward progress, the programmer can act conservatively and place more task boundaries into the code results in wasting more time and energy. Coala [55] is another task based programming model trying to eliminate the forward progress problem in a more efficient way by resorting to the timer of the system.

Ratchet [69] inserts checkpoints at compile-time. It exploits the notion of idempotency for creating restartable code sections. It places checkpoints at idempotent region boundaries. However, because of limitations in alias analysis, the number of checkpoints might be more than needed. Ratchet only works with systems with one unified non-volatile memory. For ensuring forward progress without facing non-termination, it resorts to the programmer and the watchdog timer of the system<sup>3</sup>.

A few prior work [13, 24] also consider checkpoint placement by estimating energy. However, at some point in their work, they estimate energy by profiling or measurement techniques or they did not insert checkpoints based on WCEC. As a result, in both cases, their approaches are not safe.

Baghsorkhi et al. [8] proposed undo/redo logs [56, 77] to record non-volatile/volatile data during the execution of the program. They also partitioned the program into regions. At the end of each region, there is a commit point where all recorded redo logs become permanent and undo logs are discarded. However, if a power failure happens during the execution, undo logs are used to recover the old values of non-volatile data and redo logs are discarded. They used dynamic instruction counts as the specifier of boundaries between aforementioned regions which is not safe and the system might face non-termination. Wägemann et al. [72] proposed checkpointing based on WCEC that is very similar to the static compiler presented by this thesis. The work is a runtime kernel which schedules tasks based on the estimated WCEC.

<sup>3.</sup> In this research we consider Ratchet and Coala as software approaches.

#### Hardware solutions

To facilitate the process of checkpointing, the community has proposed non-volatile processors (NVP) [81, 73] which are considered as fully hardware approaches. In these architectures all memories in the MCU from main memory to register files are non-volatile. Researchers have proposed software techniques to improve the performance and to ensure the correctness of these specialized processors. For instance, a loop tiling technique has been proposed to reduce the overhead of checkpoints [45]. Also, another software technique has been proposed by Zhao et al. [82] to determine efficient backup positions in these processors. A consistency-aware checkpointing algorithm has been designed to ensure correctness by eliminating the memory inconsistency issue [78].

There are also other hardware approaches [33, 49] trying to cope with the problems in intermittent execution of the programs by modifying hardware. Freezer [58] is a specialized backup/restore controller trying to reduce the overhead of taking checkpoints.

#### Discussion

It is empirically proved that on demand checkpointing techniques such as QuickRecall, regardless of the difficulty of finding a proper threshold, are efficient in terms of the number of checkpoints as they checkpoint just before power failures [54]. However, they excessively utilize the hardware features of the the device. Generally both hardware based and joint hardware/software solutions can take checkpoints at the cost of adding additional hardware features or using hardware features of the commercial MCUs which are originally designed to be utilized by the programmer (e.g., timers, ADCs) and not by the third party system software. In conclusion to the fully hardware and joint hardware and software solution, using additional hardware features or existing not only increases the energy consumption of the system, but also decreases the portability.

On the other hand, task based software solutions are not transparent to the programmer. The programmer must be aware of the new programming paradigms as well as new libraries and keywords added to the programming language. Also, reasoning about the number and the size of tasks is painful and error-prone for programmers. The burden will be worst when it comes to changing the code or some features of the hardware such as capacitors as the programmer must reconstruct the whole process again.

The proposed work in this thesis are considered as fully software solutions. Both static and dynamic techniques presented in this thesis aim not to use any hardware features of the MCU and be transparent to the programmer as much as possible. Moreover, they guarantee making forward progress toward execution without facing non-termination as well as keeping the memory consistent.

Our static checkpoint placer is based on WCEC. It guarantees both forward progress and memory consistency. As it is mentioned before, the only checkpoint placer based on WCEC is proposed by Wägemann et al. [72]. Our work differs from it in a way that it is based on the WCEC of program sections and the control-flow graph of the program. Also, our work applies classical compiler optimization in order to decrease the number of checkpoints. To the best of our knowledge, our proposed dynamic compiler approach is the first to bring dynamic compilation to intermittent computation.

Chapter 4

# WCEC-BASED CHECKPOINT PLACEMENT AND COMPILER OPTIMIZATIONS

## 4.1 Introduction

This chapter presents the first proposed approach by this thesis to guarantee forward progress without non-termination and to keep memory consistent in energy harvesting systems. The contribution of this work is the following:

- we propose a static, automatic, compiler-based technique for insertion of checkpoints that guarantees correctness and termination of a program on an intermittently powered system;

- we leverage compiler optimizations to reduce the number of checkpoints;

- we limit the burden on programmers to a negligible additional effort;

- we provide a portable solution without requiring any extra hardware support.

The organization of this chapter is as follows. Section 4.2 presents our proposed method with the required background used to adopt it. Section 4.3 evaluates the proposed method. And finally, Section 4.4 concludes the work.

# 4.2 WCEC-Aware checkpoint placement

## 4.2.1 Technical background

Determining checkpoint locations is based on the control flow graph (CFG) of the program. It is similar to the computation of worst-case execution time (WCET) estimates in the real-time domain [76].

The goal is to have a safe as well as tight estimation of the energy consumption of

a program executing on the hardware. Safety means that the actual consumption must be less than, or equal to, the estimate, regardless of program input and dynamic events. Tightness means that the estimation must be as close as possible to actual WCEC. Herein, the safety property of WCEC guarantees forward progress and program correctness.

For the forward progress, safety guarantees that the energy consumption for reaching the next checkpoint is less than or equal to the energy a capacitor can provide, since checkpoints are placed based on WCEC with the distance of capacitor's maximum energy. We restrict the system to resume execution after a checkpoint only when the capacitor is full (it may enter a low-power mode for better efficiency). This way, we ensure that when the system wakes up from a checkpoint, it reaches the next one, where it waits for the capacitor the recharge. This property also helps coping with the aforementioned memory consistency issue: as re-execution do not occur, we avoid problems related to memory inconsistency or replaying side effects [61]. With the exception of the checkpoints and resuming code, the application follows its normal control flow.

Also, herein, the tightness of WCEC relates to the number of checkpoints relative to the optimal number. The tighter the WCEC, the lower the number of unnecessary checkpoints.

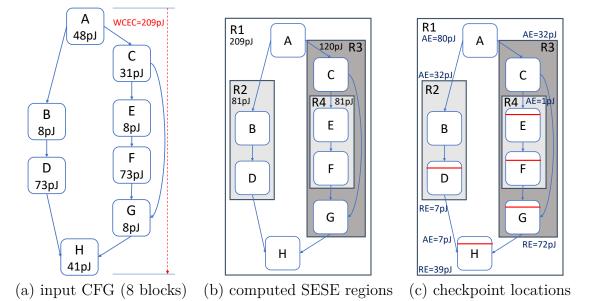

Estimating WCEC statically necessitates to have a representation of the program as well as an energy model which reflects the energy consumption of the system. For the former, the CFG of the program represents complex structures such as loops, conditions and function calls. For the latter, energy models at the lower levels of the software such as ISA are more accurate as they are closer to the hardware [28]. Figure 4.2 (a) shows a sub CFG of a program generated from the binary representation of the program. It contains eight basic blocks. The number besides each block indicates the worst-case amount of energy that the basic block consumes, computed based on the energy model (e.g. for simple architectures, by adding the amount of energy each instruction of the block consumes). In this CFG, the estimated worst-case consumption is 209 pJ.

For real-life applications, CFGs are large and the overall estimated WCEC is always much larger than the maximum energy a capacitor can provide. Also, due to the branches and loops, the number of paths from the start node to the end node is large. For instance, in the above mentioned simple CFG, the number of paths from node A to node H is three. This number increases as the CFG gets larger and more complex with branches and loops.

As typical in the real-time domain, interrupts and preemption cannot be handled at

Figure 4.1: Overview of our flow

this level. If present, they should be handled in a distinct part of the system runtime.

## 4.2.2 Approach

**Problem Statement.** For any given capacitor size (i.e. energy amount), our approach consists in inserting checkpoints at various places in the program such that, from any checkpoint, another checkpoint can be reached, regardless of the dynamic path taken by the application.

**Solution.** To make the problem tractable, we adopted an algorithm based on Single-Entry-Single-Exit (SESE) regions [39]. SESE regions may be complex, but they have a single well-defined entry as well as a single well-defined exit node. As such, they provide convenient placeholders for checkpoints. Also, these regions can be nested, sequentially composed or disjoint (see Figure 4.2 (b)). The largest SESE region is the CFG itself as it has one start node and one end node<sup>1</sup>. The smallest SESE regions are basic blocks and

<sup>1.</sup> Even in the presence of multiple return statements in a function, a compiler can easily create a new block and add edges to it to guarantee a single exit node.

instructions. In our work, since our granularity for checkpoint placement is basic blocks, we chose the basic block as the smallest SESE region.

The input of the algorithm (see Algorithm 1) is the CFG of the program with its corresponding SESE regions, and the capacitor size. The algorithm starts by estimating the WCEC of the outermost region and if the estimated WCEC is bigger than the available energy, it recursively analyzes the nested regions.

| Algorithm 1 Checkpoint Locating Algorithm                                          |

|------------------------------------------------------------------------------------|

| Data: CFG with Identified SESE Regions                                             |

| <b>Result:</b> Checkpoint Locations                                                |

| C is the energy of capacitor                                                       |

| CheckpointLocations is a vector of LLVM IR line numbers                            |

| r is the outermost region                                                          |

| Identify ChKLocations(r, C)                                                        |

| function IdentifyChKLocations( $SESERegion R$ , $AvailableEnergy E$ )              |

| $e \leftarrow \delta$ -WCEC(Entry node of R, Exit node of R)                       |

| if $e > E$ then                                                                    |

| if $R$ has nesting regions then                                                    |

| $E \leftarrow E$ - (Energy consumption of Entry node of R)                         |

| for All Region $N_i$ Nested in R do                                                |

| $  remainingEnergy \leftarrow min_i(IDENTIFYCHKLOCATIONS(N_i, E))$                 |

| end                                                                                |

| else                                                                               |

| $ $ remaining Energy $\leftarrow$ C - e, Add this Location to Checkpoint Locations |

| end                                                                                |

| else                                                                               |

| $remainingEnergy \leftarrow E - e$                                                 |

| end                                                                                |

| return remainingEnergy                                                             |

| end function                                                                       |

|                                                                                    |

For estimating the energy of a region, we rely on partial WCET estimation ( $\delta$ -WCET) proposed by Bouziane et al. [17, 16]. However, for the sake of clarity in Algorithm 1, we used energy consumption in lieu of execution time wherever relevant. For instance, consider the CFG of Figure 4.2 (b), and assume the capacitor can store 80 pJ. The algorithm first estimates the energy of region R1. Since the estimated value exceeds 80 pJ, it recur-

sively estimates the energy of R2 and R3 after subtracting the cost of block A (remaining energy of 32 pJ = 80 pJ - 48 pJ). It continues until it reaches the innermost SESE regions (basic block) and it places a checkpoint at the beginning of that basic block. The algorithm returns the amount of remaining energy. When it places a checkpoint, the return value will be the maximum amount of energy in the capacitor subtracted by the energy consumption of the basic block. Figure 4.2 (c) shows the CFG with inserted checkpoints.

As shown, the input of the proposed toolchain is the capacitor size and high-level C code annotated with maximum loop bound information. It is worth noting that specifying this information is the only supplementary effort requested from the programmer, and it is typical of embedded real-time systems. The output of our tool-chain is a binary code enriched with checkpoint trigger calls. Each checkpoint trigger is a call to a run-time library which is responsible for checkpointing the volatile state of the program into the non-volatile memory. The overhead and the energy cost of checkpointing itself is highly dependent on the underlying architecture. For architecture with non-volatile memory as unified memory, the cost of checkpointing is almost constant since only CPU registers must be copied. However, for systems configured with a volatile memory such as SRAM as well as a type of non-volatile memory, the cost of checkpointing is variable and dependent on program state such as the size of stack and heap, as well as the amount of live data at the time of checkpointing. In the latter case, we need to guarantee we have enough energy to perform the checkpointing in the worst case, and the location of the checkpoint matters. In the worst case the system must have enough energy to checkpoint all volatile memory. Our solution can deal with both types of architectures. However, in this work, we assume that there is always enough energy available for checkpointing a constant number of CPU registers in the former case or all volatile memory in the latter case, and we focus on the placement of checkpoints that guarantees correctness, and forward progress.

#### 4.2.3 WCEC estimation

Our implementation consists of a component for estimating the WCEC (Heptane [31]), augmented with a checkpoint insertion algorithm.

Figure 4.1 shows the overview of our flow. The first component (box ① in the figure) is LLVM augmented by a few passes. It first builds a mapping between LLVM IR and binary code (see Section 4.2.4), compiles the code and invokes our WCEC estimation tool. This tool, called Heptane (box ② in the figure) determines where checkpoints should be located based on information about the capacitor and a power model of the architecture. This

Figure 4.2: Input CFG, computed Single-Entry Single-Exit regions, and selected checkpoint locations (red lines, AE=available energy, RE=remaining energy)

information is fed back to LLVM for actual insertion of the checkpoints and production of the binary. This process is highlighted by the arrow designated as ③. We also explored how loop optimizations can be leveraged to decrease the cost of checkpoints (Section 4.2.6). In this case, Heptane selects appropriate loop optimizations that are forwarded to LLVM (box ④). This results in a new version of the program in LLVM IR (arrow designated as ⑤). The process of arrow ③ is repeated.

In addition, since Heptane works in binary code and our final checkpoint placement is in LLVM IR [44], we added a mapping between Heptane and LLVM IR described in Section 4.2.4.

Heptane [31] is a tool originally developed for estimating worst-case execution time (WCET) [76]. Heptane's functionality is divided into two separated components: Heptane Extract and Heptane Analysis. The former is for generating control-flow graph (CFG) of the program from the object code. The latter performs two types of analysis on the generated CFG: high-level analysis and low-level analysis. The low-level analysis compute an upper-bound for each basic block in CFG by considering the cost of instructions as well as features related to micro-architecture such as cache and pipeline. Then, the high-level analysis can compute the whole program's WCET by performing Implicit Path Enumeration Technique (IPET) [48] which is based on Integer Linear Programming (ILP) formulation of the WCET calculation problem.

In this work, since our concern is energy, inspired by Wägemann et al. [71], an energy cost for each instruction is specified instead of cycle cost that Heptane normally considers. Due to the simplicity of the processors in the domain, that is processors without caches and branch prediction, applying complex analysis in Heptane is not necessary. However, our approach is general and can include more complex architectures as long as an accurate (and safe) energy model is provided by manufacturer. Also, herein, the goal of work is not the WCEC of the whole program; instead we want to fragment the program into code sections which can be executed in one life cycle when the capacitor is fully charged. These code sections are bounded by checkpoint trigger calls. As a result, the location of these checkpoint trigger calls in the program must be identified.

## 4.2.4 Mapping between Heptane and LLVM IR

Since the analysis part is performed on binary code, and placing checkpoint trigger calls is applied at LLVM IR level, we need a mapping between the two. To achieve this, inspired from Grech et al. [29], we "hijacked" the debug information mechanism that propagates source-location information into a binary: at LLVM-level, we replace source location by the line number in the LLVM IR representation. The regular toolchain processes it as usual, carrying our information instead of traditional source line numbers.

We created two LLVM passes. Source Line to LLVM IR traverses the LLVM IR and replaces source location information with LLVM IR location information. After this pass, the binary code is generated and given to Heptane. As mentioned, the output of Heptane is a series of line numbers which specify where to place checkpoint triggers in LLVM IR. The *Checkpoint placement* is responsible to place checkpoint triggers based on the line numbers that Heptane produces. After this pass, the final binary code is generated and the program is ready to be executed on energy harvesting device.

## 4.2.5 Coping with non-termination