# Contributions to the safe and efficient parallelisation of hard real-time systems

Keryan Didier

## ▶ To cite this version:

Keryan Didier. Contributions to the safe and efficient parallelisation of hard real-time systems. Embedded Systems. EDITE de Paris, 2019. English. NNT: . tel-02456172v1

# HAL Id: tel-02456172 https://inria.hal.science/tel-02456172v1

Submitted on 27 Jan 2020 (v1), last revised 31 Aug 2020 (v2)

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE l'UNIVERSITÉ PIERRE ET MARIE CURIE

# Spécialité Informatique

École doctorale Informatique, Télécommunications et Électronique (EDITE)

Présentée par

# Keryan Didier

# Pour obtenir le grade de DOCTEUR de l'UNIVERSITÉ PIERRE ET MARIE CURIE

Sujet de la thèse:

# Contributions to the safe and efficient parallelisation of hard real-time systems

soutenue le 19 septembre 2019

devant le jury composé de :

Prof. Christine ROCHANGE

Prof. Reinhard VON HAXLEDEN

M. Philipe BAUFRETON

Dr. Albert COHEN

Prof. Alix MUNIER

Dr. Dumitru POTOP-BUTUCARU

Examinateur

Directeur de thèse

# Abstract

We propose an automatic parallelization method for applications featuring fine-grain internal parallelism. Our method adds the needed overheads to the WCET values, ensuring safety by construction without the need for subsequent schedulability analysis. It is aimed at applications with fine-grain parallelism where excessive per-task overheads would result in poor parallelization gains. To keep overheads under control, we make strong hypotheses on the target execution platform, on the form of generated code, and on the integration of the various tools of the back-end. These hypotheses allow our tool-flow to perform a full-fledged timing and schedulability analysis incrementally during allocation and scheduling. Allocation and scheduling are performed jointly, using scalable compilation-like heuristics. The resulting schedule and code are correct by construction. By covering all aspects of resource allocation and code generation, our work belongs to the compilation realm. What fundamentally differentiates it from previous compilation work is the choice of performing a safe, worst-case timing analysis incrementally during compilation around which are integrated parallelization, real-time scheduling, and memory allocation. This method is suitable for very large-scale applications, as it uses low-complexity mapping heuristics, which quarantees scalability.

We also propose a language, named InteLus, for the description of parallel multithreaded implementations of dataflow specifications. It is a sub-set of Lustre extended with annotations representing mapping and code generation choices. While such extensions are common in literature, our language and modeling approach go further in one fundamental way: implementation models specified in InteLus are strictly richer than the multi-threaded C code we want to generate. InteLus allows the representation of all mapping decisions needed for multi-threaded code generation in our context. InteLus's representation of threads and thread synchronization is a sub-case of the C11/pthread concurrency model. Therefore, C code can be obtained by selectively putting elements of the InteLus program into C and linker script syntax without making any further mapping decision. Annotations are covered by the operational semantics of InteLus. This allows us to formally define the correctness of implementation models. To facilitate the definition of the correctness properties, implementation models are endowed with not one, but two semantics: the synchronous semantics of Lustre (which simply discards mapping annotations) and the machine semantics, which interprets the program and its annotations as a multi-threaded imperative program. This dual semantic nature of our implementation models enables us to envision an original approach to proving implementation correctness.

# Contents

| 1        | 1.1<br>1.2<br>1.3<br>1.4                       | Motiva     |                                                       | 9<br>11<br>15<br>20 |  |  |  |  |  |  |

|----------|------------------------------------------------|------------|-------------------------------------------------------|---------------------|--|--|--|--|--|--|

| Ι        | Effi                                           | cient p    | parallelization of real-time applications             | 23                  |  |  |  |  |  |  |

| <b>2</b> | Platform-independent specification in Heptagon |            |                                                       |                     |  |  |  |  |  |  |

|          | 2.1                                            | Functi     | ional specification and code generation with Heptagon | 25                  |  |  |  |  |  |  |

|          |                                                | 2.1.1      | Synchronous programming                               | 25                  |  |  |  |  |  |  |

|          |                                                | 2.1.2      | Syntax and intuitive semantics of Heptagon            | 28                  |  |  |  |  |  |  |

|          |                                                | 2.1.3      | Code generation API                                   | 36                  |  |  |  |  |  |  |

|          |                                                | 2.1.4      | Non-functional annotations                            | 39                  |  |  |  |  |  |  |

|          | 2.2                                            | Extens     | sions and integration specification                   | 40                  |  |  |  |  |  |  |

|          |                                                | 2.2.1      | Exposing parallelism                                  | 41                  |  |  |  |  |  |  |

|          |                                                | 2.2.2      | Real-time requirements                                | 43                  |  |  |  |  |  |  |

|          |                                                | 2.2.3      | Integration specification                             | 44                  |  |  |  |  |  |  |

|          | 2.3                                            | Specifi    | ication normalization                                 | 44                  |  |  |  |  |  |  |

|          |                                                | 2.3.1      | Exposing node states                                  | 44                  |  |  |  |  |  |  |

|          |                                                | 2.3.2      | Hyper-period expansion                                | 45                  |  |  |  |  |  |  |

|          |                                                | 2.3.3      | Normalized integration specification                  | 48                  |  |  |  |  |  |  |

| 3        |                                                |            | and software architecture                             | 49                  |  |  |  |  |  |  |

|          | 3.1                                            |            | vare architecture                                     | 50                  |  |  |  |  |  |  |

|          | 3.2                                            | m software | 52                                                    |                     |  |  |  |  |  |  |

|          |                                                | 3.2.1      | Synchronization with real-time                        | 54                  |  |  |  |  |  |  |

|          |                                                | 3.2.2      | Event-driven synchronization                          | 54                  |  |  |  |  |  |  |

|          |                                                | 3.2.3      | Memory coherency                                      | 55                  |  |  |  |  |  |  |

|          |                                                | 3.2.4      | Requirements on compilation tools                     | 55                  |  |  |  |  |  |  |

|          | 3.3                                            |            | cure of an implementation                             | 56                  |  |  |  |  |  |  |

|          |                                                | 3.3.1      | Threads running in lockstep                           | 56                  |  |  |  |  |  |  |

|          |                                                | 3.3.2      | Explicit memory mapping                               | 59                  |  |  |  |  |  |  |

6 CONTENTS

|    |                               | 3.3.3   | The case for resource sharing                 |  |  |  |  |  |  |  |  |  |  |

|----|-------------------------------|---------|-----------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| 4  | Timing model 6                |         |                                               |  |  |  |  |  |  |  |  |  |  |

|    | 4.1                           | Datafl  | ow function analysis                          |  |  |  |  |  |  |  |  |  |  |

|    |                               | 4.1.1   | Function characterization                     |  |  |  |  |  |  |  |  |  |  |

|    |                               | 4.1.2   | Compilation                                   |  |  |  |  |  |  |  |  |  |  |

|    |                               | 4.1.3   | Static analysis                               |  |  |  |  |  |  |  |  |  |  |

|    | 4.2                           | Analys  | sis of thread code fragments before synthesis |  |  |  |  |  |  |  |  |  |  |

|    | 4.3                           |         | ry access interferences                       |  |  |  |  |  |  |  |  |  |  |

|    | 4.4                           | Paralle | el WCET computation                           |  |  |  |  |  |  |  |  |  |  |

|    | 4.5                           |         | rm description format                         |  |  |  |  |  |  |  |  |  |  |

| 5  | Mapping and code generation 7 |         |                                               |  |  |  |  |  |  |  |  |  |  |

|    | 5.1                           |         | ime systems compilation                       |  |  |  |  |  |  |  |  |  |  |

|    | 5.2                           |         | vation tables                                 |  |  |  |  |  |  |  |  |  |  |

|    |                               | 5.2.1   | Safe abstraction issues                       |  |  |  |  |  |  |  |  |  |  |

|    | 5.3                           | Incren  | nental timing analysis                        |  |  |  |  |  |  |  |  |  |  |

|    |                               | 5.3.1   | Memory coherency protocol                     |  |  |  |  |  |  |  |  |  |  |

|    |                               | 5.3.2   | Synchronization protocol                      |  |  |  |  |  |  |  |  |  |  |

|    |                               | 5.3.3   | Interferences                                 |  |  |  |  |  |  |  |  |  |  |

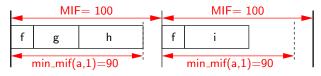

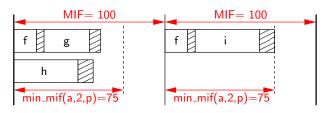

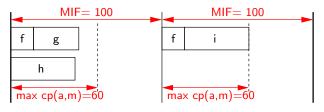

|    |                               | 5.3.4   | Reservation size                              |  |  |  |  |  |  |  |  |  |  |

|    | 5.4                           | Schedi  | uling algorithm                               |  |  |  |  |  |  |  |  |  |  |

|    |                               | 5.4.1   | Incremental resource allocation               |  |  |  |  |  |  |  |  |  |  |

|    |                               | 5.4.2   | Implementation of fby equations               |  |  |  |  |  |  |  |  |  |  |

|    |                               | 5.4.3   | Reservation and schedulability test           |  |  |  |  |  |  |  |  |  |  |

|    | 5.5                           | Synch   | ronization synthesis                          |  |  |  |  |  |  |  |  |  |  |

|    |                               | 5.5.1   | Potential trade-offs                          |  |  |  |  |  |  |  |  |  |  |

| 6  | Exp                           | erime   | ntal evaluation                               |  |  |  |  |  |  |  |  |  |  |

|    | 6.1                           | Indust  | rial use-case definition                      |  |  |  |  |  |  |  |  |  |  |

|    |                               | 6.1.1   | Use case UCA                                  |  |  |  |  |  |  |  |  |  |  |

|    |                               | 6.1.2   | Use-case UCS                                  |  |  |  |  |  |  |  |  |  |  |

|    |                               | 6.1.3   | General considerations                        |  |  |  |  |  |  |  |  |  |  |

|    | 6.2                           | Exper   | imental results                               |  |  |  |  |  |  |  |  |  |  |

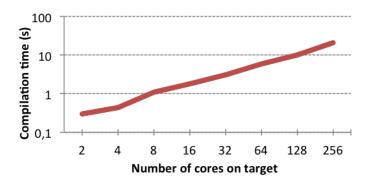

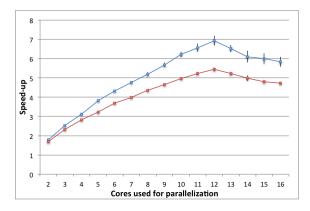

|    |                               | 6.2.1   | Scalability                                   |  |  |  |  |  |  |  |  |  |  |

|    |                               | 6.2.2   | Parallelization efficiency                    |  |  |  |  |  |  |  |  |  |  |

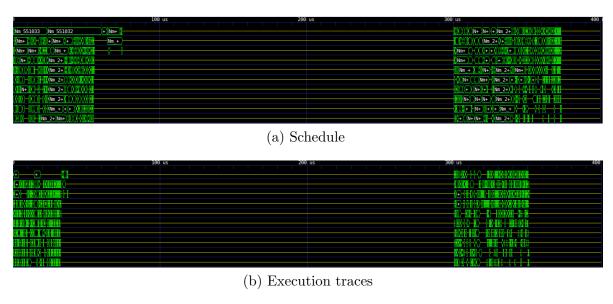

|    |                               | 6.2.3   | Correctness                                   |  |  |  |  |  |  |  |  |  |  |

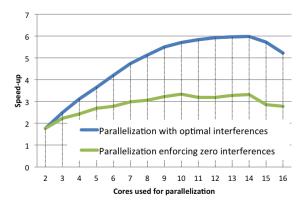

|    |                               | 6.2.4   | The cost of isolation                         |  |  |  |  |  |  |  |  |  |  |

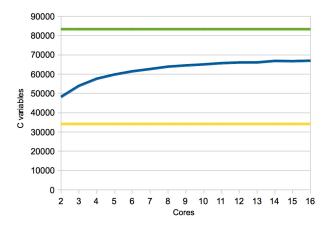

|    |                               | 6.2.5   | Memory use and synchronization optimizations  |  |  |  |  |  |  |  |  |  |  |

|    |                               |         |                                               |  |  |  |  |  |  |  |  |  |  |

| ΙΙ | Ba                            | ck-end  | l correctness formalization 11                |  |  |  |  |  |  |  |  |  |  |

| 7  | The                           | Intelu  | is language 11                                |  |  |  |  |  |  |  |  |  |  |

|    | 7.1                           | Lustre  | e/Heptagon sub-set                            |  |  |  |  |  |  |  |  |  |  |

CONTENTS 7

|     | 7.2<br>7.3                         | Non-functional extensions17.3.1 Thread structure17.3.2 Location allocation17.3.3 Machine semantics of API call equations1 | .21<br>.23<br>.24<br>.24<br>.25 |  |  |  |  |  |  |  |  |

|-----|------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|--|--|--|

| 8   | Platform independent semantics 127 |                                                                                                                           |                                 |  |  |  |  |  |  |  |  |

| Ü   | 8.1                                | -                                                                                                                         |                                 |  |  |  |  |  |  |  |  |

|     | 0.1                                | v                                                                                                                         | .27<br>.28                      |  |  |  |  |  |  |  |  |

|     |                                    |                                                                                                                           | 29                              |  |  |  |  |  |  |  |  |

|     |                                    |                                                                                                                           | 29                              |  |  |  |  |  |  |  |  |

|     |                                    |                                                                                                                           | .31                             |  |  |  |  |  |  |  |  |

|     |                                    | ,                                                                                                                         | 32                              |  |  |  |  |  |  |  |  |

|     | 8.2                                |                                                                                                                           | .33                             |  |  |  |  |  |  |  |  |

|     | 0.2                                | v                                                                                                                         | .34                             |  |  |  |  |  |  |  |  |

|     |                                    |                                                                                                                           | .34                             |  |  |  |  |  |  |  |  |

|     |                                    |                                                                                                                           | 35                              |  |  |  |  |  |  |  |  |

|     | 8.3                                | 1                                                                                                                         | 36                              |  |  |  |  |  |  |  |  |

|     | 0.0                                |                                                                                                                           | 36                              |  |  |  |  |  |  |  |  |

|     |                                    |                                                                                                                           | 37                              |  |  |  |  |  |  |  |  |

|     |                                    | - · · · · · · · · · · · · · · · · · · ·                                                                                   | .37                             |  |  |  |  |  |  |  |  |

|     |                                    | -                                                                                                                         |                                 |  |  |  |  |  |  |  |  |

| 9   |                                    |                                                                                                                           | 39                              |  |  |  |  |  |  |  |  |

|     | 9.1                                | 1                                                                                                                         | .39                             |  |  |  |  |  |  |  |  |

|     |                                    |                                                                                                                           | 40                              |  |  |  |  |  |  |  |  |

|     |                                    |                                                                                                                           | .41                             |  |  |  |  |  |  |  |  |

|     |                                    |                                                                                                                           | 42                              |  |  |  |  |  |  |  |  |

|     | 9.2                                |                                                                                                                           | 42                              |  |  |  |  |  |  |  |  |

|     | 9.3                                |                                                                                                                           | 42                              |  |  |  |  |  |  |  |  |

|     |                                    | 8                                                                                                                         | 45                              |  |  |  |  |  |  |  |  |

|     |                                    | 9.3.2 Mapping                                                                                                             | 47                              |  |  |  |  |  |  |  |  |

|     |                                    |                                                                                                                           |                                 |  |  |  |  |  |  |  |  |

| 10  |                                    | r r r r r r r r r r r r r r r r r r r                                                                                     | 49                              |  |  |  |  |  |  |  |  |

|     | 10.1                               |                                                                                                                           | .49                             |  |  |  |  |  |  |  |  |

|     |                                    | 1                                                                                                                         | 49                              |  |  |  |  |  |  |  |  |

|     |                                    |                                                                                                                           | .50                             |  |  |  |  |  |  |  |  |

|     | 10.2                               | Challenges and perspectives                                                                                               | .51                             |  |  |  |  |  |  |  |  |

| Bil | bliog                              | graphy 1                                                                                                                  | 53                              |  |  |  |  |  |  |  |  |

8 CONTENTS

# Chapter 1

# Introduction

# 1.1 Context

Full automation is possible and needed in real-time scheduling. The implementation of complex embedded software relies on two fundamental and complementary engineering disciplines: real-time scheduling and compilation. Real-time scheduling covers<sup>1</sup> the upper abstraction levels of the implementation process, which determine how a functional specification is transformed into a set of tasks and how the tasks are mapped and scheduled onto the resources of the execution platform in a way that ensures functional correctness while respecting non-functional requirements. By comparison, compilation covers the low-level code generation process, where each task (usually a piece of sequential code written in C, Ada, etc.) is transformed into machine code, allowing actual execution.

In the early days of embedded systems design, both high-level and low-level implementation activities were largely manual. However, two factors led to rapid automation at low-level: the increasing amount and complexity of software, and the standardization of both general-purpose programming languages and instruction set architectures (ISAs) of execution platforms.

At the high level, many activities remained largely manual for a long time. Such is the case for the partitioning of the application into sequential tasks, the production of *glue code* ensuring task orchestration, communication and synchronization, or even timing analysis, where adding experience-based margins to computed worst-case execution time (WCET) estimates is still commonplace. This lack of automation can be attributed to two factors:

- The lack of standardization in execution platforms and in functional and nonfunctional modeling languages made the construction of (qualified) tools expensive and inefficient.

- Penalties associated with the lack of automation were acceptable on low-complexity systems featuring few processors and tasks, and often featuring tasks that require little synchronization [1].

$<sup>^{1}</sup>$ Along with other disciplines such as operating systems, software engineering, etc.

Both factors are now gone:

- Languages for functional modeling of control applications such as Simulink [2], Scade [3], or LabView [4], and languages for non-functional specification such as SysML [5] or UML/MARTE [6] are today standard practice in industry. There are also well-established official standards like those describing execution platforms in fields such as avionics—ARINC 653 [7]—and automotive industries—Autosar [8].

- The rapidly increasing complexity of execution platforms and software leads to prohibitive development costs for manual processes when efficiency is desired.

Note that efficiency is a key property in real-time systems design. While the *mathe-matical modeling* of schedulability problems is in the form of constraint systems (there is a solution or not), in *practice*, efficiency of the implementation method will determine how much software can be executed, therefore how many functions can be performed and with which precision.

Fully automating the mapping process is difficult. The key difficulty of real-time scheduling is that timing analysis and resource allocation depend on each other. This difficulty is particularly acute in the case of safety-critical control systems where certification regulations do not tolerate the weakening of timing characterizations in multiprocessor environments; this is the context of my work.

An exhaustive search for the optimal solution not being possible for complexity reasons, heuristic approaches are used to break this dependency cycle. Two such approaches are typical in real-time systems design.

The most common is to first build the system, and then check the respect of real-time requirements through a global analysis. Building the system uses here unsafe timing information such as measures, WCETs in isolation plus arbitrary margins, etc. This is similar to classical compilation, where the timing models used for software pipelining or VLIW instruction scheduling are not meant to provide worst-case timing bounds, but average-case optimization figures on chosen benchmarks. The second approach is to ensure by construction the respect of requirements. In this case, system construction uses task timing characterizations that are safe for all possible resource allocations (worst-case bounds).

The drawback of the first approach is the lack of traceability between resource allocation decisions and timing analysis results. If the system does not respect its real-time requirements, mapping changes are needed, but these changes may also change the timing analysis, and so on without guarantee of convergence to a solution. The second approach is much more appealing from an automation perspective and considering the fine-grained control it offers to platform engineers. Its drawback is pessimism, as all resource allocations are made for the worst case.

So far, the practicality of the second approach has never been established. Automated real-time parallelization flows still rely on simplified hypotheses ignoring much of the timing behavior of concurrent tasks, communication and synchronization code. And even with such unsafe hypotheses, few studies and tools considered the harmonic

multiperiodic task graphs of real-world control applications, and the problem of statically managing all their computational, memory, synchronization, and communication resources.

Ensuring the safety of the generated code is difficult. Regardless of the chosen approach (using unsafe timing information or using safe timing information), automatic mapping methods and tools follow a "correct-by-construction" paradigm. However, like for C compilers, this is not sufficient to provide the levels of confidence required by the most critical embedded software. Supplementary arguments are needed, based on both engineering experience (e.g. extensive test) and formal arguments (e.g. proof of correctness of the tool). In both cases, formalizing the correctness of the mapping tools is essential, and one key step in doing this is defining the formal semantics of parallel implementations.

As hardware design resolutely moves towards massive parallelism based on the use of chip-multiprocessors, mastering concurrency, and thus exploiting the full potential of such hardware, becomes increasingly difficult. Threads are one of the major programming paradigms for such multi- and many-core systems. They arguably provide the best portability and the finest control over resource allocation, which are both essential in the design of embedded applications that need to get the best guaranteed performance out of resource-constrained hardware.

However, the expressiveness of threads comes at a price. As a model of computation, threads are wildly non-deterministic and non-compositional [9], making programming, formal analysis, and implementation difficult [10, 11]. This explains why multi-threaded software is often bug-ridden even in the context of critical systems [12].

But there are also good news: in many industrial contexts (avionics, automotive, etc.) the use of threads is tightly controlled, and the threaded code implements a functionality specified in a high-level concurrent formalism.

We consider in our work the particular case where the functional specification of the system is done in a dataflow synchronous language such as Lustre/Scade [13] or a sub-set of Simulink [2]. In this case, multi-threaded implementations, possibly obtained using automatic mapping tools, have particular structure and properties: The number of threads is fixed, each one implementing a recurrent task obtained by sequencing a fixed set of dataflow blocks (or parts thereof, obtained by parallelization).

When taken individually, such properties already facilitate the formal analysis of multi-threaded systems. But in many cases, the multi-threaded implementation preserves a fundamentally dataflow structure, with specific rules on the way platform resources (shared memory, semaphores) are used. Such implementations are not only data race free (DRF) in the restricted sense of [11], but also deterministic.

## 1.2 Related work and contribution

In this context, my thesis is concerned with the *safe and efficient parallelization of hard real-time systems*. This string of keywords hints at several topics in computer science and engineering.

Hard real-time systems. My work concerns the implementation of real-time systems [1]. These are systems whose execution is subject to real-time requirements, such as worst-case bounds on the latency between arrival of an event and appropriate reaction to it. These systems exist in a large spectrum ranging from multimedia applications such as music player to cyber-physical systems found in transportation, medicine, or robotics.

Hard real-time systems are those where requirements must always be respected. This is not the case in a set-top box, where losing a video frame should not happen too often, but is ultimately largely innocuous. However, this is usually the case in *critical cyber-physical systems*. In such systems, the non-respect of the real-time requirements can lead to life- or mission-threatening situations, either because the requirement is part of the very description of the system function (as in an airbag, which must be inflated in at most 80 ms after the crash) or because the real-time requirements are meant to ensure the controllability of the system (as in avionics flight control software).

Much of the classical work on real-time systems implementation (in both research and industry) relies on a two-phase process which clearly separates the construction of the implementation from its verification and validation (V&V) [14]. Verification activities, including determining whether the system satisfies its non-functional requirements (a process known as schedulability analysis) are performed on the completed implementation. The construction of the implementation uses incomplete/unsafe/unformalized versions of the timing analysis algorithms to guide its mapping decisions and code transformations. For instance, the construction of tasks and memory allocation are often guided by potentially unsafe WCET and/or memory footprint estimations, derived from previous experience and partial code analysis. Furthermore, significant parts of the implementation process remain to this day manual or unformalized in many industrial settings.

Automatic parallelization The problem we consider is the automatic parallelization of hard real-time applications. More specifically, we target shared memory multi-core processors, and our objective is the fully automatic construction of the executable implementation code in an approach similar to classical compilation. In our hard real-time context, this amounts to not only performing the allocation and scheduling of computations onto the various cores, but also synthesizing the control and synchronization code, choosing the memory allocation, and finally ensuring that the non-functional requirements are satisfied given these allocation and code generation choices.

Our work is by no means the first to contribute to this bold objective.

Recent advances have largely automated the construction of task code and the generation of real-time implementations on specific sequential or multi-core targets. Industrial solutions include here Simulink Real-Time from MathWorks, and Scade KCG6 Parallel from ANSYS/Esterel Technologies [3]. Academic results in this direction include [15, 16, 17, 18]. However, none of these tools provide strong schedulability guarantees when integrating multiple synthesized tasks: separate timing and schedulability analysis must be performed after synthesis. Several methods have been proposed [19, 20, 21] but they come with the shortcomings of the first approach sketched in the in-

troduction. In particular, in the event of a global non-schedulability diagnosis, it is difficult to pinpoint its source so as to guide subsequent re-engineering efforts.

A few approaches have gone further, by letting timing analysis results guide mapping and code generation under simplifying hypotheses common in real-time scheduling, e.g., assuming that task WCET values include overheads related to parallel/concurrent execution. Among these approaches we cite the industrial tool Asterios Developer from KronoSafe, based on the  $\Psi$ C language [22], as well as the academic tools and toolboxes SynDEx [23], BIP [24], SchedMCore [25], Prelude [26], Lopht [27, 28], SigmaC [29, 30], the work on the time-triggered mapping of Lustre [31], Xoncrete [32], or the work of Baruah et al. on the synthesis of multi-core cyclic executives [33]. We defer the reader to [27] for a longer description.

While these methods guarantee correctness and have the potential of providing more feedback in case of non-schedulability diagnostics, the simplifying hypotheses are seldom (if ever) satisfied in practice. To our knowledge, they are satisfied only when using prototype hardware designed for predictability, e.g. by ensuring the absence of memory access interferences [34, 35]. But the hypotheses are never satisfied on modern off-the-shelf multi- and many-cores, where the overheads due to concurrent execution include contributions that may be difficult to estimate, depending on the hardware or software architecture of the system: memory access and bus access interferences, cache-related delays, synchronization costs, scheduler execution time, etc.

A step further is taken in [36, 37], where the tool itself adds the needed overheads to the WCET values. In [36], overheads are large (several hundred cycles per task), to account for the time-triggered execution mechanism where so-called monitors are used to dynamically update triggering dates. In [37], overheads are not even discussed, and no comparison with the sequential case without communication costs is given. More important, in both cases the objective of the method is optimization, not implementation under constraints, as it is in our case.

Contribution 1: Real-time systems compilation We propose an automatic parallelization method for applications featuring fine-grain internal parallelism. Like in [36, 37], our method adds the needed overheads to the WCET values, ensuring safety by construction without the need for subsequent schedulability analysis. However, unlike these methods, it is aimed at applications with fine-grain parallelism where excessive per-task overheads would result in significantly reduced parallelization potential. To keep overheads under control, we make strong hypotheses on the target execution platform, on the form of generated code, and on the integration of the various tools of the back-end. These hypotheses allow our tool-flow to perform a full-fledged timing and schedulability analysis incrementally during allocation and scheduling. Allocation and scheduling are performed jointly, using scalable compilation-like heuristics. The resulting schedule and code are correct by construction. If construction of the schedule is impossible, the partial mapping and schedulability analysis allow the engineer to pinpoint the immediate causes of the scheduling failure.

By covering all aspects of resource allocation and code generation, our work is clearly related to previous work on compilation. In previous work [38], we already noted and

exploited the formal and algorithmic proximity between off-line real-time scheduling and various results on software pipelining for super-scalar and VLIW processors, where the scheduling burden is mostly supported by the compilers [39, 40]. What fundamentally differentiates our current work from previous compilation work is the choice of performing a safe, worst-case timing analysis incrementally during compilation.

My thesis does *not* provide advances on the complexity of real-time scheduling algorithms. Recent papers provided conflicting evidence—pro [41, 42] and contra [43]—on the ability of methods based on constraint solving to find solutions to large-scale real-time scheduling problems. Like most others, the scheduling problem we address can be encoded as an ILP, SMT, or constraint program. However, we consider parallelization, real-time scheduling, memory allocation, and safe and precise timing analysis for very large-scale applications going much beyond the most complex constraint programming and complexity studies. Furthermore, we consider the use of low-complexity mapping heuristics a positive point, as it *quarantees* scalability.

### Contribution 2: An implementation model for dataflow multi-threaded software.

We propose a language, named InteLus, for the description of parallel multi-threaded implementations of dataflow specifications. It is a sub-set of Lustre extended with annotations representing mapping and code generation choices. Such extensions are common in existing literature, but our language and modeling approach go beyond previous work in one fundamental way: implementation models specified in InteLus are strictly richer than the multi-threaded C code we want to generate. InteLus allows the representation of all mapping decisions needed for multi-threaded code generation in our context—sequencing of dataflow blocks into threads executed by processors; code, stack, data variables to memory locations; synchronizations to hardware locks, etc. InteLus's representation of threads and thread synchronization is a sub-case of the C11/pthread concurrency model [44]. Therefore, C code can be obtained by selectively putting elements of the InteLus program into C and linker script syntax without making any further mapping decision—a process we call pretty-printing, exemplified in Section 1.3.

Annotations are covered by the InteLus operational semantics. This allows us to formally define (but not yet prove) the correctness of implementation models. To facilitate the definition of the correctness properties, implementation models are endowed with not one, but two semantics: the *synchronous semantics* of Lustre (which simply discards mapping annotations) and the *machine semantics*, which interprets the program and its annotations as a multi-threaded imperative program. This dual semantic nature of our implementation models enables us to envision an original approach to proving implementation correctness, based on 3 proof obligations:

- 1. Refinement Under synchronous semantics the Lustre specification and the InteLus implementation model are equivalent modulo a pipelining transformation.

- 2. Mapping Executing the implementation model under machine semantics produces the same sequences of values as those produced by the same model under synchronous semantics.

3. Code generation The machine semantics of the implementation model faithfully describes the behavior of the multi-threaded C code produced by pretty printing.

Previous work on implementation modeling. Much work exists on parallel application mapping (e.g. [23, 25, 45]), but it always involves a non-trivial code generation phase that escapes formal modeling and analysis, covering at least some of the aspects we consider here: thread construction, synthesis of synchronization and memory consistency protocols, etc. The language we propose allows formal reasoning on the correctness of all these mapping and code generation decisions. The only step not covered by our correctness formalization is pretty printing, which moves to a C syntax while preserving unchanged the thread structure and the allocation.

Our modeling language and method currently do not cover timing aspects, due to the limited time we had in the context of this thesis. Thus, it does not allow reasoning about real-time correctness. For time-triggered systems [45] this also means that we cannot reason about functional correctness. However, having such a framework to define the functional correctness of multi-threaded implementations of dataflow systems has its merits in its own right, even outside of the real-time domain. Furthermore, timing aspects can be considered in the future and built on top of this current work.

Our results are closely related to previous work on providing (operational) semantics to synchronous languages and to concurrent C. Our machine semantics is close in form to the operational C11 semantics of [11], most notably to the variant without the "promise" rule, which is adapted to DRF programs like the ones we synthesize. Main differences are that we consider a very restricted concurrency model, and that we consider a particular type of shared memory architecture and the associated memory allocation problem (which previous semantics [11, 44] do not cover). From a dataflow language perspective, my thesis includes novel operational semantics for Lustre covering the language extensions (triggers and synchronization-only variables) and the machine semantics that formalizes execution on platform at the dataflow level.

Beyond defining the formal semantics of implementation models, we formalize the proof obligations ensuring implementation correctness. This is the first step towards formal proof of correctness for the multi-threaded implementation of Lustre programs. In this sense our work is related to previous results on the formally verified compilation of dataflow synchronous languages [46, 47]. By comparison, our work extends dataflow modeling to cover multi-processor implementation issues (mutex synchronization, memory consistency), but we have not yet proved the correctness of the method.

# 1.3 Motivating example

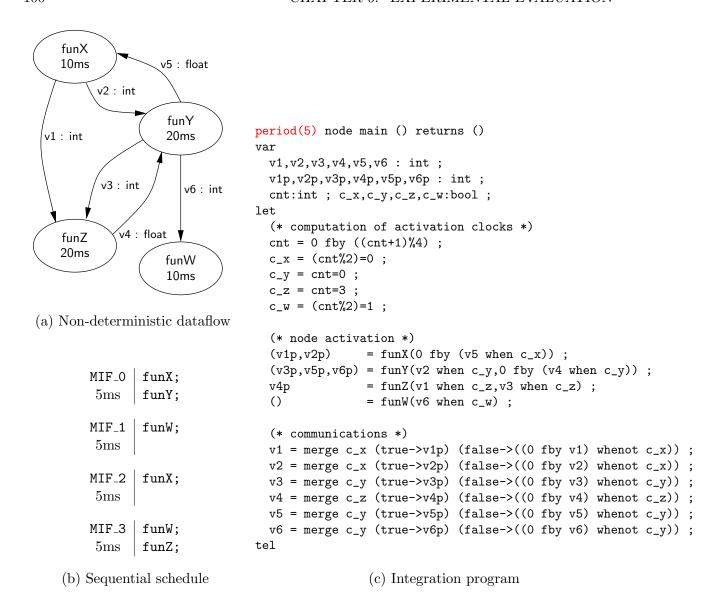

Our compilation problem is similar to that solved by a compiler and linker flow for a sequential imperative language: to produce *correct executable code* that statically orchestrates the machine resources, in a *fully automatic* and *scalable* way. But there are also important differences. Following long-standing practice in the avionics industry [48], the input program—also known as the *functional specification*—is provided in a dataflow synchronous language with a *cyclic execution scheme*. As exemplified in

Figure 1.1, we use for functional specification the Heptagon language [49, 50]. The second major difference is that the functional specification—the Heptagon program—is annotated with *non-functional requirements* the implementation must respect. In our example, annotations specify *real-time* requirements (period and deadline). The third difference is that the target low-level semantics is multithreaded with explicit resource allocation and mapping for communication and synchronization.

```

open Io (* declarations of platform-dependent I/O functions read_int, write_int *)

open Func (* declarations of externally-defined functions f, g, h *)

node simple (i:int) returns (z:int)

var y,d : int; x : float;

5

read int

write int

deadline(1500) x = f(i);

6

y = g(d);

7

8

z = h(x,y);

d = 0 \text{ fby } z;

9

tel

10

Z

11

period(3000) node main () returns ()

12

var i,o : int;

init:0

13

let.

14

3000

i = read_int();

inline o = simple (i);

16

() = write_int(o);

17

18

tel

19

20

```

Figure 1.1: On the left, functional specification provided as a Heptagon program (in black) with non-functional requirements specified through annotations (in red). On the right, a graphical representation of the dataflow of node main, after inlining of node simple.

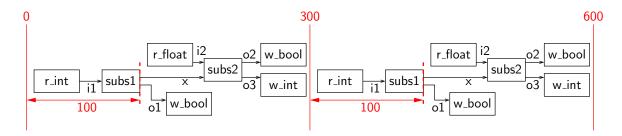

We target shared memory multiprocessors with uniform memory access. To facilitate timing analysis, hardware and low-level libraries must satisfy a number of properties detailed in Chapter 3. For such hardware, we generate statically scheduled, statically allocated, bare metal code whose structure facilitates timing analysis, along the guidelines of [20]. The threads generated from our example for a dual-core target are presented in Figure 1.2. To allow compilation and execution, they must be accompanied by the boot code launching the threads, by the sequential code of the functions implementing the dataflow blocks f, g, and h, by the communication and synchronization library, and by a linker script enforcing memory allocation of all code and data.

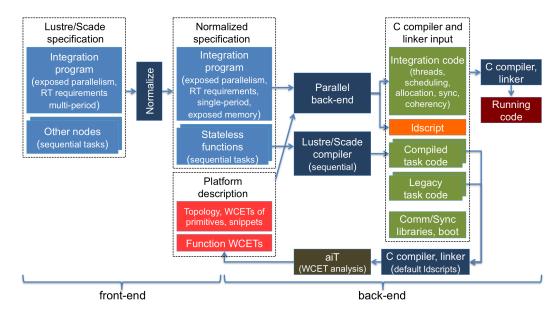

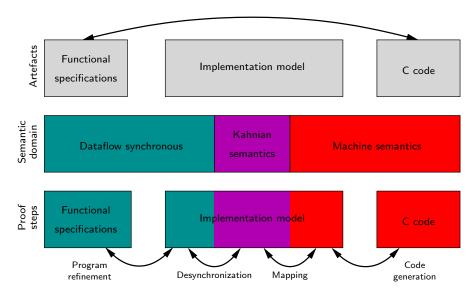

To ensure that generated code is not only functionally correct, but also satisfies by construction the real-time requirements, we rely on the compilation flow of Figure 1.3. The front-end normalizes and simplifies the input program, bringing it to a form that satisfies the requirements of static single assignment (SSA) form [51]. In the backend, the sequential code of the basic dataflow blocks (f, g, h in our example<sup>2</sup>) is

<sup>&</sup>lt;sup>2</sup>I/O is performed through shared variables, so read\_int and write\_int require no code in Figure 1.2.

```

void* thread cpu1(void*){

void* thread cpu0(void*){

1

lock init pe(0); init();

2

lock init pe(1);

for(;;){

3

for(;;){

4

time_wait(3000);

5

barrier_notify(0,2);

barrier_notify(1,2);

barrier wait(0);

6

barrier sync(1);

dcache_inval();

dcache_inval();

f(i,&x);

8

g(z,&y);

9

dcache flush();

dcache_flush();

unlock(1);-

lock(1,1);

lock(0,0); <

unlock(0);

dcache_inval();

12

13

h(x,y,&z);

dcache_flush();

14

}}

15

}}

```

Figure 1.2: Parallel C code generated from the Heptagon program in Figure 1.1 for a two-core implementation

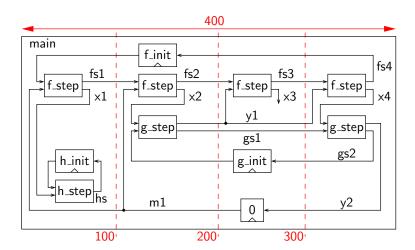

separately compiled and analyzed to determine their WCET, worst-case number of accesses to shared communication resources (memory banks), and memory footprint. This information is used in the parallel back-end, which performs real-time resource allocation and code generation, building the parallel threads of Figure 1.2 and the linker script of Figure 1.4.

Of this compilation flow, several components have been extensively studied in previous work: the compilation of dataflow synchronous programs to sequential code [52], C compilation [53], and WCET analysis[54]. My thesis focuses on the remaining topics: the front-end normalization phase in Chapter 2, the parallel back-end in Chapter 3, and the integration of all back-end tools around the timing model of Chapter 4 which guarantees by construction the respect of real-time requirements.

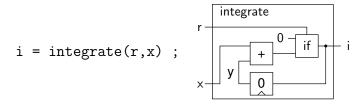

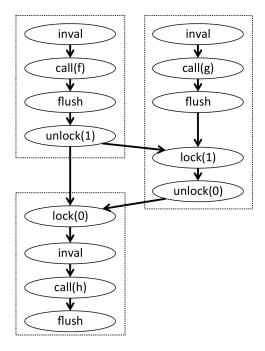

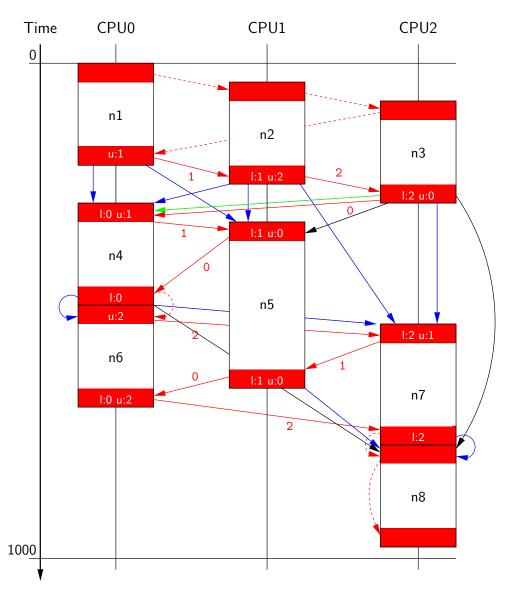

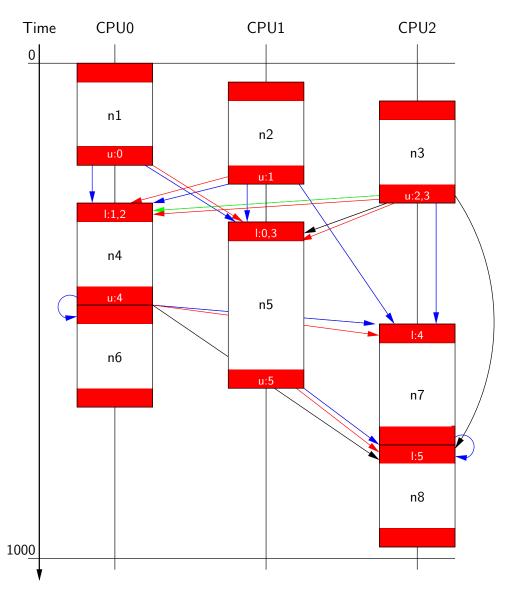

Formal implementation modeling The multi-threaded code of Figure 1.2 preserves a fundamentally dataflow structure, which can be represented with an extended Lustre syntax as pictured in Figure 1.4(left). Note that, even for this trivial example, the parallel C implementation and its implementation model is already quite complex. To ensure correct operation sequencing and communication on the multi-core, calls to f, g, and h are surrounded by:

- Mutex operations (lock and unlock API calls) ensuring that production happens before consumption, and that consumption is completed when a communication variable is reused for production. Barrier synchronization operations are also used to ensure that execution is performed in lockstep. However, we shall not insist on these, as they can be decomposed into mutex operations.

- Data cache operations (dflush and dinval API calls) implementing the memory coherency protocol ensuring that the consumer uses the correct data. Explicit cache operations are only needed on platforms without hardware cache coherency

Figure 1.3: Proposed implementation flow—tools and artifacts

such as our test platform. On more classical POWER or ARM multi-cores, they can be simply discarded, as the semantics of lock and unlock (of either the pthread or C11 mutexes) ensures the needed coherency.

On the right of the implementation model, we have pictured the C code. Note that our modeling does not (yet) cover real-time behavior. For this reason, the time\_wait API call of Figure 1.2 has been discarded here.

As mentioned above, the multi-threaded implementation consists not only of C code, but also comprises GCC annotations and the linker script defining memory allocation. Such tightly-controlled mapping is common in critical embedded systems. In avionics applications like our case study, the worst case execution time must be demonstrated for normal conditions, but the application must also be robust to "external factors". The choice of a mutex-synchronized implementation improves robustness by guaranteeing the respect of the functional semantics regardless of timing aspects. Providing execution time guarantees can then be done through tight control of memory allocation and synchronization, and through the use of hardware with good support for timing predictability. These design choices, covered elsewhere [55], reduce timing variability and facilitate timing analysis [20].

The implementation model of Figure 1.4 (left) consists of a dataflow program (in black and blue) extended with annotations defining all the aspects of its mapping (in red). The dataflow program uses some extensions to Lustre (in blue) allowing the description of synchronization. These extensions include the synchronization data type event and the wait and done constructs that allow the definition of sequencing constraints not implied by data dependencies. The dataflow implementation program provides a precise functional model of the execution on platform. For instance, specifi-

```

fun f:(int)\rightarrow(int) at 0x20100

ldscript fragment:

1

x=0x22000; y=0x32000; z=0x22004; i=0x220064;

fun g:(int)->(float) at 0x30200

fun h:(float,int)->(int) at 0x20500

stack0=0x30000; stack1=0x40000;

.=0x20000; .bank2:{*(.text.cpu0);

var input i:int at 0x22064 i_cpu0:int at i on cpu0

.=0x100 ; *(.text.f) ;

x:int at 0x22000 x_cpu0:int at x on cpu0

.=0x500 ; *(.text.h) ;

y:float at 0x32000

6

y_cpu0:float at y on cpu0 y_cpu1:float at y on cpu1

7

z:int at 0x22004 z_cpu0:int at z on cpu0

.=0x30000; .bank3:{*(.text.cpu1);

8

.=0x200 ; *(.text.g) ;

d:int at z d_cpu1:int at z on cpu1

9

u:event at 1 v:event at 0

10

s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,t1,t2,t3,t4,t5,t6,b:event

11

12

// memory, C code in the initO function

13 extern void f(int,int*);

d = 0 \text{ fbv } z

b = barrier(b0,b1) // HW barrier semantics, no C code

14 extern void g(int,float*);

15 extern void h(int,float,int*);

s9 = top fby s8 // thread 0 self-activation, no C code

t6 = top fby t5 // thread 1 self-activation, no C code

16 extern int i,x,z; extern float y;

__attribute__((section(.text.cpu0)))

17

thread on cpu0 at 0x20000 stack 0x30000

18 void thread_cpu0(){ init0(); for(;;){

[br_notify:0,2]

b0 = top

19 barrier_notify(0,2);

barrier_wait(0) ;

s9

done(s0) [br_wait:0]

_ = b

20

s9 wait(s0) done(s1) [inval:0x22064] i_cpu0 = i

21

dcache_inval();

x_cpu0 = f(i_cpu0)

22

f(i,&x);

s9 wait(s1) done(s2)

dcache_flush();

s9 wait(s3) done(s4) [unlock:1]

u = top

24

unlock(1):

s9 wait(s4) done(s5) [lock:0]

_ = v

25

lock(0);

s9 wait(s5) done(s6) [inval:0x32000] y_cpu0 = y

26

dcache_inval();

s9 \text{ wait}(s7) \text{ done}(s8)  [flush:0x22004] z = z_cpu0 28

dcache_flush();

29 }}

__attribute__((section(.text.cpu1)))

30

thread on cpu1 at 0x30000 stack 0x40000

31

void thread_cpu1() { init1(); for(;;){

b1 = top

32

barrier_notify(1,2);

[br notify:1.2]

_ = b

done(t0) [br_wait:1]

33

barrier_wait(1) ;

34

t6 wait(t0) done(t1) [inval:0x22004] d_cpu1 = d

dcache_inval();

g(z,&y);

dcache_flush() ;

t6 wait(t3) done(t4) [lock:1]

_ = u1

37

lock(1):

t6 wait(t4) done(t5) [unlock:0]

v = top

38

unlock(0);

39 }}

tel

```

Figure 1.4: Implementation model corresponding to the example of Figure 1.2 (real-time excluded)

cation variable y is replaced here with three variables y, y\_cpu0, and y\_cpu1 allowing the representation of the various states of the memory system where the value produced on processor cpu0 has not yet been propagated to the RAM or to the cache of processor cpu1. The implementation model provides dataflow interpretations for the various API calls. For instance, in line 36 the dataflow interpretation of flush ensures that the local value of y\_cpu0 has been propagated onto its RAM counterpart y, and in line 38 the dataflow interpretation of unlock produces a token (the special literal top) that can be consumed later by the lock call in line 25. The equations in lines 13-16 are not part of threads. They perform the initialization of state variables, represent the self-reactivation of the thread bodies, and provide the semantics of the platform HW barrier.

Under the application-specific code structuring hypotheses detailed in Chapter 3,

the mapping information of Figure 1.4(left) is exhaustive. It allows the generation of all the C code, GCC annotations, and linker script of Figure 1.4(right) by simple pretty-printing, as no new mapping decisions are needed. For instance, the list of equations of a thread is transformed line-by-line into the sequence of function calls forming the body of the infinite loop of the corresponding C thread.

Such implementations and implementation models can be automatically synthesized, using our automatic mapping method or other existing tools [34, 56]. They can also be manually written.

# 1.4 Thesis plan

This thesis is organized in two distinct parts corresponding to the two main contributions identified above.

Efficient parallelization of real-time applications We start in Chapter 2 with a presentation of the specifications we handle, namely, dataflow synchronous programs. There, we present functional specification with Heptagon[49] as it exists today through an intuitive semantics of the main components of its language and the structure of the code generated by its compiler. We then propose some extensions to the language to specify real-time requirements, thus allowing the encoding of all the *platform-independent* aspects of the specification to be parallelized (both functional and non-functional). We also present in this chapter the transformations we apply to our specifications to obtain a normalized form that our back-end can process efficiently.

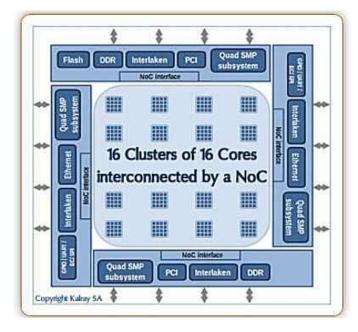

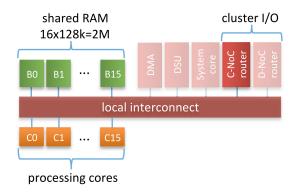

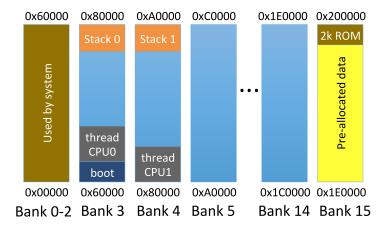

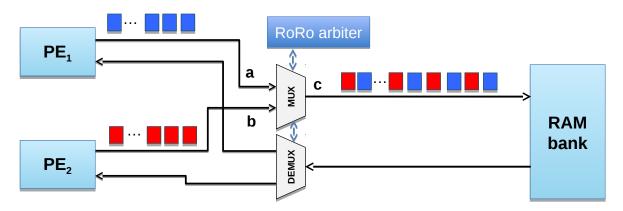

In Chapter 3, we focus on the hardware and software architecture. We start by identifying and discussing predictability properties required to allow the efficient parallel implementation of our applications. We describe the simple application programming interface (API) we rely on to synthesize our code, and explain how it can be implemented on some existing multi-cores, most notably on the platform we use for experimental evaluations—the Kalray MPPA 256 Bostan many-core. We also present in this chapter the structure of the implementation we generate: code organization, how the primitives are used, and how the memory is organized.

In Chapter 4, we present the timing model and the timing analysis methodology. First, we discuss the way a worst-case execution time (WCET) analysis tool for sequential code is used to perform the analysis of the sequential functions of the functional specification. This analysis must ensure that computed WCET values are independent of function code and data mapping. We then propose an interference model for the target architecture. This model precisely accounts for memory access interferences due to parallel execution. Finally, we derive a global timing analysis method for parallel software satisfying the code structuring hypotheses of Chapter 3.

In Chapter 5, we present our automatic mapping method and algorithms. We first discuss the difference between our approach, traditional compilation, and traditional real-time implementation processes. We then present the real-time scheduling algorithms, which also perform memory allocation and the allocation of computations to

1.4. THESIS PLAN 21

the various cores in a way that incrementally ensures the respect of non-functional requirements. This is only possible by incrementally performing, at scheduling time, the timing interference analysis. We also present here the code generation method ensuring, and in particular the original synchronization synthesis method.

We conclude this part with the experimental results, presented in Chapter 6. After presenting our two industrial use-cases, we propose a method for quantifying the efficiency of parallelization algorithms for real-time applications, and then we present our results.

Formal implementation modeling We start in Chapter 7 with the presentation of a new language called InteLus. This language is a stripped-down version of Lustre extended with dataflow constructs allowing the representation of pure synchronization and operation sequencing, and with non-functional annotations defining the mapping of the data, computations, and communications onto the hardware resources (RAM, CPUs, mutexes, etc.).

Chapter 8 defines the dataflow semantics of Intelus. Two distinct semantics are defined. The first one is a synchronous semantics, whose only particularity is that it follows a structural operational semantics (SOS) paradigm. The second one interprets Intelus programs as asynchronous Kahn process networks (KPN). A strong semantics preservation property links the two semantics. We also introduce in this chapter a series of necessary properties all correct implementation models must satisfy.

Chapter 9 introduces the machine semantics of Intelus, which takes into account the non-functional annotations of the language. This semantics, which defines the state of the execution platform and state transitions, is necessarily platform-dependent. We formalize the correctness of implementation models with respect to functional specifications. Correctness properties cover two aspects: the absence of run-time errors during execution on the platform, and the semantics preservation between the functional specification and the implementation model.

We conclude this thesis and present the perspectives offered by this work in Chapter 10.

# Part I

# Efficient parallelization of real-time applications

# Chapter 2

# Platform-independent specification in Heptagon

To provide the functional specification of a real-time system, we use Heptagon [49], a dataflow synchronous language close in form and semantics to Lustre [13] and its industrial dialect Scade [3]. We also extend Heptagon with non-functional annotations allowing the representation of platform-independent non-functional requirements. Heptagon, extended with these annotations, allows us to define all aspects of our system that are independent from details of the execution platform. We call this the *platform-independent specification* of the system.

We start this chapter by presenting the core concepts of the Heptagon language, starting with the principles of the synchronous paradigm. Then, we introduce the language annotations that allow the specification of non-functional requirements. Finally, we explain how platform-independent specifications are normalized before being given to our parallelization and code generation algorithms.

# 2.1 Functional specification and code generation with Heptagon

Heptagon is both a language and a research compiler. In this thesis we shall extensively discuss both – the language as the support of our specifications, and the compiler as a key tool in our code generation flow.

In this section, we provide a brief introduction to synchronous programming, an overview of the subset of Heptagon we use, and a brief presentation of the code generation conventions we use.

## 2.1.1 Synchronous programming

Synchronous programming originated in the real-time community [57, 58]. It was designed as a way to non-ambiguously specify the functional part of complex real-time embedded control systems. These systems have very particular specification needs.

Reactive and real-time systems. First of all, they are reactive systems [59], whose role is to respond, in a timely and continuous manner, to events produced by their environment at the pace set by the environment. In the description of a reactive system, the focus is less on the description of the computation to be performed, but on the description of the interaction between system and its environment, and by extension between sub-systems. A key property of most reactive systems is concurrency. Concurrency occurs at both specification and implementation level. At specification level, various sub-systems may require interaction with the environment (or with other sub-systems) possibly at different paces. At implementation level, software reactive systems often have multi-task implementations.

Concurrency complicates both the design and the analysis of systems. As subsystems/tasks compete for access to resources, undesired phenomena such as deadlocks, starvation, or data races can occur. More generally, concurrent execution can lead to functional non-determinism. This is bad news, as in the industrial engineering of real-time embedded control systems, determinism is a highly desirable property, at it can largely facilitate activities at all steps of the design cycle – specification, implementation, verification and validation (V&V).

Real-time systems are reactive systems where the system/environment interaction or the interaction between sub-systems must satisfy precise timing requirements. Typical requirements are:

- An airbag must be deployed at most 80ms after a shock event has been detected.

- The cyclic computation and interaction of a flight controller must happen on a period of 50ms, to ensure the controllability of the plane.

Real-time systems are often described and implemented as a set of elementary behaviors without internal concurrency, usually called *tasks*, which are activated (or interrupted, disabled) following specific rules depending on environment input, task interaction, a timed pattern, or a combination thereof. Specifying a real-time system mainly consists in specifying the set of tasks and their (concurrent) activation pattern.

The synchronous programming paradigm [60] and the synchronous languages are one of the solutions proposed for the programming of reactive and real-time systems. In this paradigm, system execution is semantically divided into a sequence of completely ordered execution instants. Concurrency is confined inside execution instants, and each instant must involve a statically bounded number of computations<sup>1</sup>. Furthermore, the concurrency inside an instant satisfies the requirements of the static single assignment form [51], which enforces<sup>2</sup> a causal ordering between the computations: inside each instant, a variable is assigned at most once, and no variable is assigned a value after being read inside the same instant. Causality implies the determinism of the computations

<sup>&</sup>lt;sup>1</sup>Some languages have been introduced that do not have this restriction [61], but they are rather exceptions from the common use (at least in the industry).

<sup>&</sup>lt;sup>2</sup>In conjunction (as in virtually all work in compilation) with the property of dominance of variables definitions over their uses.

inside an instant, which in turn implies the global determinism of correct synchronous programs. Data races and deadlocks are not possible.

Synchronous languages provide constructs allowing the natural description of elementary computations and their hierarchic composition involving relations of (data and control) dependency, concurrency, priority, and (conditional) activation.

To represent activation, the synchronous paradigm proposes the notion of *logical clocks*. A logical clock represents the sequence of execution instants where some computation or communication is performed, or where a variable is assigned a value. Every operation and variable of a system has exactly one clock, describing its (deterministic) activation/communication pattern. The *base clock* of a system represents the set of all execution instants of the system. All other clocks are derived from the base clock through subsampling.

From its beginning, synchronous reactive programming has been declined in several languages, the three best known being:

- Esterel [62], an imperative programming language with explicit expression of concurrency and hierarchic control. Its emphasis on control flow is particularly suited for control-dominated applications in robotics or hardware design.

- Lustre [13], a declarative dataflow programming language. Scade [63] is a industrial dialect of Lustre used in the engineering of critical systems, e.g. in avionics.

- Signal [64], another dataflow language which facilitates the definition of systems with multiple, unrelated logical clocks.

Throughout this thesis, we will see the synchronous paradigm through the lens of Lustre. In particular, the next section will illustrate the concepts of the dataflow synchronous paradigm through the description of the Heptagon dialect of Lustre.

**Related formalisms.** Synchronous languages are not the only class of formalisms used to describe (reactive) real-time systems.

Synchronous data-flow (SDF) [65] and derived formalisms (such as CSDF [66], BDF [67]) also feature a deterministic and cyclic execution model. However, while in synchronous languages all computations and communications are synchronized with respect to the global base clock, the SDF execution model is fundamentally asynchronous and decentralized. An SDF block can be executed as soon as enough input is available, and execution is not constrained with respect to global events.

Traditionally used in real-time scheduling, task models [68, 69] focus on the coarse-grain organization of the application—the partitioning of its code into tasks, and the real-time properties of the tasks (durations, periods, deadlines, etc.). The functional behavior of the tasks is abstracted away, as task models are not designed as full-fledged programming languages.

While synchronous languages are not concerned with the *duration* of computations, time-triggered languages such as Giotto [70] (with its current LET [71] dialect) or PsyC [22] introduce duration as a first-class language construct, to allow its explicit specification and analysis.

Heavily used in industry, Simulink[72] is a language and tool for design and simulation of control systems, in discrete or continuous time. Its syntax is similar to that of dataflow synchronous languages like Lustre. However, the semantics of Simulink is defined by the simulation engine, and it varies depending on numerous simulation parameters, some of which trade semantic determinism and consistency for simulation speed. Thus, while certain sub-sets of Simulink can be considered synchronous, the whole language (in all its simulation configurations) is not. The situation is similar for LabView [4].

### 2.1.2 Syntax and intuitive semantics of Heptagon

A Heptagon program is a textual representation of a dataflow graph with dedicated constructs specifying activation. The language syntax allows to express dependence or concurrency of operations, conditional activation and communication, and hierarchical program composition.

This section will present the subset of Heptagon we need in our work using simple examples to illustrate the intuitive semantics of the constructs.

### Equation

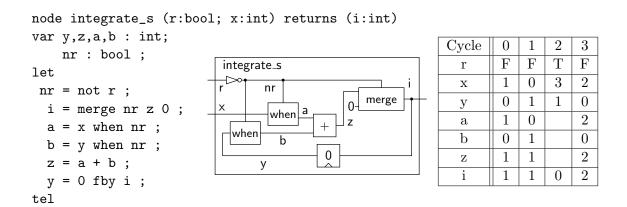

In Heptagon, vertices of the dataflow graph are called *equations*. The simplest kind of equation is the *function call*, of which an example is provided in Figure 2.1(left), along with its informal graphical representation (middle) and an execution trace (right). This

|             |           |              | Cycle  |   |   |         |   |        |  |

|-------------|-----------|--------------|--------|---|---|---------|---|--------|--|

|             | X → f → Z |              | 0      | 1 | 2 | 3       | 4 | 5      |  |

| x = f(x,y); |           | X            | 1      |   |   | 3       |   | 0      |  |

|             | •         | у            | 1      |   |   | -1      |   | 3      |  |

|             |           | $\mathbf{Z}$ | f(1,1) |   |   | f(3,-1) |   | f(0,3) |  |

Figure 2.1: Function call equation in Heptagon. Syntax (left), graphical representation (middle), six cycles long example trace (left).

function takes two inputs and produces one output. The execution of the equation is cyclic. At each execution cycle where it is activated, the equation reads one input from each of x and y and produces f(x,y) on the variable z. The function call equation synchronizes its inputs and outputs. If at least one input is present in an execution cycle, then all inputs are present and all outputs are produced. Formally, all input and output variables have the same clock. We call this a *clock constraint*.

To facilitate the use of common mathematical operators, Heptagon allows their use with natural infix syntax. Thus, if a function call equation must compute the addition of two integers, we will write:

$$z = x + y;$$

While the function in our example has one output, Heptagon functions can have any fixed number of outputs. Such functions are called using the following syntax:

```

() = output0(x,y,z); (* Function with no output and three inputs *) (a,b) = output2(x); (* Function with two outputs and one input *)

```

Note the OCaML-style comments, which can be nested (unlike in C/C++).

#### **Dataflow**

Equations can be connected through variables to form a dataflow allowing the computation of more complex functions.

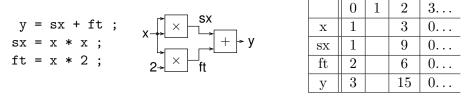

Figure 2.2: Dataflow computing  $y = x^2 + 2x$

We provide in Figure 2.2 the dataflow encoding the computation of the mathematical function  $y = x^2 + 2x$ . In this dataflow, the input variable x is used thrice. Variables sx and ft are internal to our dataflow. They are outputs of multiplication equations and input to the addition equation. Variables can be inputs of any number of dataflow nodes (or none), but each variable that is not an input of the dataflow must be produced by exactly one dataflow node.

This example also shows a constant value 2 in the second equation. Constants can be seen as functions without inputs that produce the same value at each execution cycle where the output is needed.

Recall from Section 2.1.1 that the dataflow must satisfy the structuring requirements of the SSA form, and in particular the causality requirement. In the textual representation of the dataflow, equations need not be ordered to satisfy causal dependencies. The causality analysis and the ordering of equations for code generation is the task of the compiler. In our example, the equations are in reverse topological order, which would produce an incorrect result should the fragment be interpreted as a C program (but the fragment is correct and will produce the correct C code with Heptagon). More generally, the semantics of a Heptagon program do not depend on the order of its equations.<sup>3</sup>

The following program is incorrect due to a violation of the causality requirement:

$$x = f(y);$$

$y = g(x);$

Function f depends on the execution of g through the variable y, while g depends on f through x. Execution is therefore not possible, and the program is rejected by the compiler. Similarly, a function cannot have as both input and output the same variable.

<sup>&</sup>lt;sup>3</sup>The form of the C code generated by the Heptagon compiler may depend on the equation order, but without changing the computed function.

Function equations that are not causally ordered in the dataflow are concurrent. They can be executed in any order or in parallel. In Figure 2.2, the two multiplication equations are concurrent.

## State

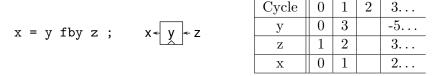

In the example of Figure 2.2, the computation of a cycle only depends on the value of the input x. Heptagon also gives the programmer the ability to specify stateful behaviors by storing *state* values from one execution cycle to the next. This is done using the operator fby (followed-by).

Figure 2.3: The fby (followed-by) statement of Heptagon

The fby statement has two inputs (denoted y and z in Figure 2.3) and one output (denoted x in our figure). The input and output variables of the construct are present in the same cycles (they have the same clock). In the first cycle where it is present, x takes the same value as y. In all other cycles where it is present, x takes the previous value of z. Operationally, the execution of fby takes place in two phases: it produces the value of x at the beginning of a cycle, allowing execution to proceed, and then stores the value of z for the next cycle, at the cycle end.

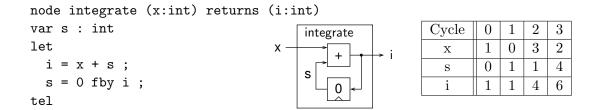

| X <i>→</i>           | ¬ i | Cycle | 0 | 1 | 2 | 3 | 4        |

|----------------------|-----|-------|---|---|---|---|----------|

| i = x + s;           |     | X     | 1 | 0 |   | 3 | $2\dots$ |

| s = 0 fby i; $s = 0$ |     | s     | 0 | 1 |   | 1 | 4        |

| LA                   |     | i     | 1 | 1 |   | 4 | 6        |

Figure 2.4: State in Heptagon

As pictured in Figure 2.4, the fby allows the specification of feedback loops without breaking the causality requirements. This example implements an integrator— $\mathbf{i}$  is the sum of all previous values of  $\mathbf{x}$ .

### Expressions. Syntax restrictions.

The syntax of Heptagon allows grouping dataflow equations into expressions. For instance, instead of:

```

y = 0 \text{ fby } z;

x = f(y);

```

one can simply write x = f(0 fby z). It is always possible to expand a complex expression into a set of dataflow equations containing each exactly one dataflow operator.

### 2.1. FUNCTIONAL SPECIFICATION AND CODE GENERATION WITH HEPTAGON31

Grouping operators into expressions or expanding expressions into simpler equations does not change the semantics of a program, which remains subject to the same causality requirements and clock constraints.

To simplify the definition of the semantics and to reduce the complexity of code generation, we simplify throughout this thesis the syntax of the language. We focus on the dataflow core of the language, and do not cover Heptagon constructs such as the modular reset or the automata [49]. Furthermore:

- We assume that each equation contains at most one dataflow operator.<sup>4</sup>

- We assume that the first argument of a fby operator is a constant.

The last two constraints can be removed with light to moderate effort. We did not do it, because the language sub-set we consider covers the needs of our industrial use cases. Covering modular reset and automata poses no theoretical problem—as they can always be translated into pure dataflow—but providing an efficient practical solution may require more work (and use cases).

# Modularity

Once built, a dataflow—i.e. its equations and variables—can be encapsulated under the form of a dataflow node. The node is the programming unit of Heptagon. A node definition provides:

Name An identifier, similar to a function name, which must uniquely identify the node in its namespace.

**Signature** The set of input and output variables along with their types and possibly clocks.

Local variables They are grouped in the var section of the node definition. Local variables are invisible from outside the node.

**Dataflow** A set of dataflow equations using only the input, output, and local variables of the node. These equations must provide a value to all local and output variables.