## Static Analysis and Dynamic Adaptation of Parallelism. Pierre Huchant

### ▶ To cite this version:

Pierre Huchant. Static Analysis and Dynamic Adaptation of Parallelism.. Computer Science [cs]. Université de Bordeaux, 2019. English. NNT: . tel-02429785

## HAL Id: tel-02429785 https://inria.hal.science/tel-02429785v1

Submitted on 6 Jan 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Thèse présentée pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE BORDEAUX

École doctorale de Mathématique et Informatique de Bordeaux Spécialité : **Informatique**

Par Pierre HUCHANT

## Analyse statique et adaptation dynamique du parallélisme

Après avis de :

Cédric Bastoul William Jalby Professeur, Université de Strasbourg Professeur, UVSQ Rapporteur Rapporteur

Soutenue le 29 mars 2019 devant la commission d'examen composée de :

| Martin Quinson          | Professeur, ENS Rennes                       | Président du jury  |

|-------------------------|----------------------------------------------|--------------------|

| Denis Barthou           | Professeur, Bordeaux INP                     | Directeur de thèse |

| Marie-Christine COUNILH | Maître de conférence, Université de Bordeaux | Examinatrice       |

| Cédric Bastoul          | Professeur, Université de Strasbourg         | Rapporteur         |

| WILLIAM JALBY           | Professeur, UVSQ                             | Rapporteur         |

| Cédric Bastoul          | Professeur, Université de Strasbourg         | Rapporteur         |

## Résumé

Les applications de calcul scientifique ont besoin de ressources de calcul de plus en plus importantes et beaucoup de grands challenges scientifiques exigent des capacités de calcul Exascale (10 puissance 18 calculs par seconde) pour être relevés. L'un des principaux obstacles pour atteindre l'Exascale est la difficulté de programmer les architectures parallèles actuelles. De nouvelles méthodes automatiques sont nécessaires pour combler l'écart entre les développeurs d'applications scientifiques et les experts en calcul haute performance. De plus, les applications scientifiques devenant de plus en plus complexes et étant supposées s'exécuter à très large échelle, de nouveaux outils sont nécessaires pour aider les développeurs lors de la phase de débogage des programmes. Cette thèse explore la combinaison de méthodes statiques et dynamiques pour faciliter la programmation des applications de calcul haute performance. Deux enjeux majeurs sont étudiés : faciliter la programmes parallèles.

La première partie de cette thèse s'intéresse à l'adaptation automatique des tâches de calcul aux architectures hétérogènes. Nous proposons une nouvelle méthode pour faciliter la programmation des architectures hétérogènes composées de plusieurs unités de calcul (CPUs et GPUs). Le programmeur exprime le parallélisme de son application sous forme de tâches OpenCL sans se soucier des problèmatiques liées à l'architecture sur laquelle son code sera exécuté. Ensuite notre méthode partitionne automatiquement chaque tâche en sous-tâches et équilibre la charge de travail entre les unités de calcul afin de tirer pleinement avantage de toutes les ressources de calcul de la machine.

La deuxième partie de cette thèse porte sur la détection automatique des interblocages dans les programmes parallèles. Nous proposons une nouvelle analyse statique permettant de détecter précisement les chemins d'exécution menant à des interblocages dans les programmes parallèles. Cette analyse statique est ensuite combinée à une instrumentation dynamique du code afin de prévenir les interblocages à l'exécution.

Les solutions proposées dans cette thèse ont été testée et validées sur des cas réels d'applications parallèles.

**Mots clés:** calcul haute performance, architectures hétérogènes, débogage, analyse statique, analyse dynamique, OpenCL, équilibrage de charge

## Abstract

Scientific applications have an increasing need of resources and many grand scientific challenges require exascale compute capabilities to be addressed. One major concern to achieve exascale is programmability. New automatic methods are required to fill the gap between developers of scientific applications and HPC experts. In addition, as scientific applications are becoming more and more complex and are supposed to run at extreme scale, new tools are required to assist developers in the debugging phase of application development. This thesis explores the combination of static and dynamic methods to improve programmability of HPC applications. Two major issues are investigated: the complexity of programming heterogeneous architectures and the prevention of deadlocks in parallel programs.

The first part of this thesis investigates the automatic task adaptation for heterogeneous architectures. More precisely, we propose a new method to improve programmability of heterogeneous architectures. The programmer expresses the parallelism of his application through a sequence of OpenCL tasks without considering issues related to the underlying architecture where its code will be executed. Then our method automatically partitions the tasks into sub-tasks executed by each device and handles load balancing between the devices to take full advantage of the machine capabilities.

The second part of this thesis investigates the automatic detection and prevention of deadlocks in parallel programs. We propose a novel static analysis to precisely detect execution paths in parallel programs potentially leading to deadlocks. This static analysis is then combined with a dynamic instrumentation of the code to automatically prevent deadlocks at runtime.

The solutions proposed in this thesis have been tested and validated on real parallel applications.

**Key words:** High Performance Computing, Heterogeneous Architectures, Debugging, Static Analysis, Dynamic Analysis, OpenCL, Load Balancing

# Contents

| 1      | Intro           | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9                                                                           |

|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

|        | 1.1             | Introduction to High Performance Computing                                                                                                                                                                                                                                                                                                                                                                                                                           | 9                                                                           |

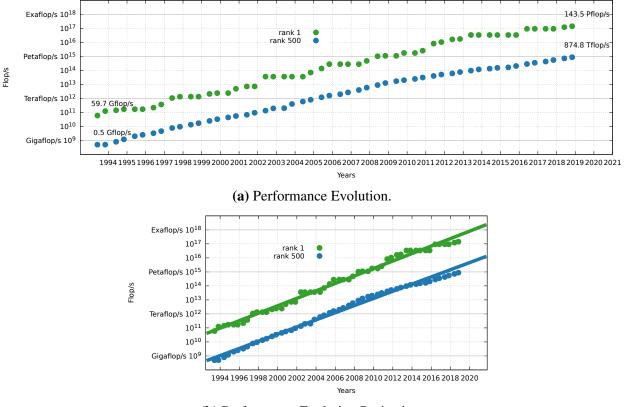

|        |                 | 1.1.1 Parallel Architectures Evolution                                                                                                                                                                                                                                                                                                                                                                                                                               | 9                                                                           |

|        |                 | 1.1.2 Towards Exascale                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10                                                                          |

|        |                 | 1.1.3 Challenges for Programmability                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11                                                                          |

|        | 1.2             | Expressing Parallelism                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12                                                                          |

|        |                 | 1.2.1 OpenMP                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13                                                                          |

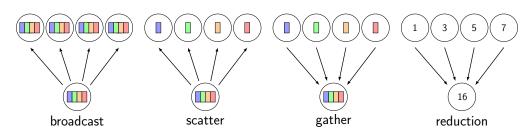

|        |                 | 1.2.2 MPI                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13                                                                          |

|        |                 | 1.2.3 Partitioned Global Address Space                                                                                                                                                                                                                                                                                                                                                                                                                               | 14                                                                          |

|        |                 | 1.2.4 Programming Many-Core                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14                                                                          |

|        |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16                                                                          |

|        | 1.3             | Debugging HPC Applications                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16                                                                          |

|        |                 | 1.3.1 Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16                                                                          |

|        |                 | 1.3.2 Parallel Debugging                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                                          |

|        |                 | 1.3.3 Bug Detection Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                                          |

|        |                 | 1.3.4 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                                          |

|        | 1.4             | Outline and Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                                                                          |

| -      |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                             |

| I      |                 | L O                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23                                                                          |

| I<br>2 | Auto            | omatic Adaptation for Iterated Sequences of Irregular Kernels                                                                                                                                                                                                                                                                                                                                                                                                        | 25                                                                          |

|        |                 | omatic Adaptation for Iterated Sequences of Irregular Kernels       2         Context and Parallelization Model       2                                                                                                                                                                                                                                                                                                                                              | <b>25</b><br>26                                                             |

|        | Auto            | omatic Adaptation for Iterated Sequences of Irregular Kernels       2         Context and Parallelization Model       2         2.1.1       Context                                                                                                                                                                                                                                                                                                                  | <b>25</b><br>26<br>26                                                       |

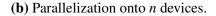

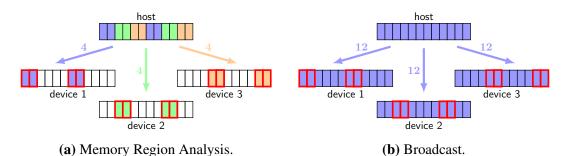

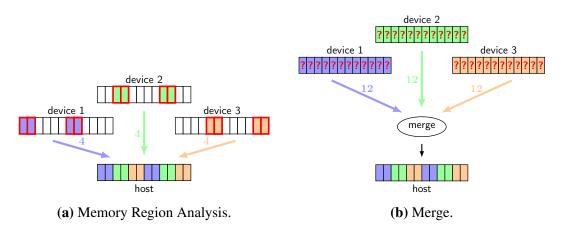

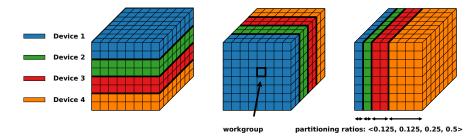

|        | Auto            | omatic Adaptation for Iterated Sequences of Irregular Kernels       2         Context and Parallelization Model       2         2.1.1       Context         2.1.2       Parallelization Model                                                                                                                                                                                                                                                                        | <b>25</b><br>26<br>26<br>29                                                 |

|        | <b>Auto</b> 2.1 | omatic Adaptation for Iterated Sequences of Irregular Kernels       2         Context and Parallelization Model       2         2.1.1       Context         2.1.2       Parallelization Model         2.1.3       Partitioning Strategies                                                                                                                                                                                                                            | <b>25</b><br>26<br>26<br>29<br>31                                           |

|        | Auto            | omatic Adaptation for Iterated Sequences of Irregular Kernels       2         Context and Parallelization Model       2         2.1.1       Context         2.1.2       Parallelization Model         2.1.3       Partitioning Strategies         Challenges       3                                                                                                                                                                                                 | <b>25</b><br>26<br>26<br>29<br>31<br>33                                     |

|        | <b>Auto</b> 2.1 | omatic Adaptation for Iterated Sequences of Irregular Kernels       2         Context and Parallelization Model       2         2.1.1       Context         2.1.2       Parallelization Model         2.1.3       Partitioning Strategies         Challenges       3         2.2.1       Data Partitioning                                                                                                                                                           | <b>25</b><br>26<br>29<br>31<br>33<br>34                                     |

|        | <b>Auto</b> 2.1 | omatic Adaptation for Iterated Sequences of Irregular Kernels       2         Context and Parallelization Model       2         2.1.1       Context         2.1.2       Parallelization Model         2.1.3       Partitioning Strategies         Challenges       2         2.2.1       Data Partitioning         2.2.2       Load Balancing                                                                                                                        | <b>25</b><br>26<br>29<br>31<br>                                             |

|        | <b>Auto</b> 2.1 | omatic Adaptation for Iterated Sequences of Irregular Kernels       2         Context and Parallelization Model       2         2.1.1       Context         2.1.2       Parallelization Model       2         2.1.3       Partitioning Strategies       3         Challenges       3         2.2.1       Data Partitioning       3         2.2.3       Summary       4                                                                                               | <b>25</b><br>26<br>29<br>31<br>33<br>34<br>38<br>42                         |

|        | <b>Auto</b> 2.1 | omatic Adaptation for Iterated Sequences of Irregular Kernels       2         Context and Parallelization Model       2         2.1.1       Context         2.1.2       Parallelization Model       2         2.1.3       Partitioning Strategies       2         Challenges       3         2.2.1       Data Partitioning       3         2.2.2       Load Balancing       3         2.2.3       Summary       4         Principle of Adaptive Partitioning       4 | <b>25</b><br>26<br>29<br>31<br>33<br>34<br>38<br>42<br>42                   |

|        | <b>Auto</b> 2.1 | omatic Adaptation for Iterated Sequences of Irregular Kernels2Context and Parallelization Model22.1.1Context2.1.2Parallelization Model22.1.3Partitioning Strategies3Challenges32.2.1Data Partitioning32.2.2Load Balancing32.2.3Summary4Principle of Adaptive Partitioning42.3.1Static Analysis and Transformation4                                                                                                                                                   | <b>25</b><br>26<br>29<br>31<br>33<br>34<br>38<br>42<br>42<br>44             |

|        | <b>Auto</b> 2.1 | omatic Adaptation for Iterated Sequences of Irregular Kernels2Context and Parallelization Model22.1.1Context2.1.2Parallelization Model22.1.3Partitioning Strategies22.1.3Partitioning Strategies3Challenges32.2.1Data Partitioning32.2.2Load Balancing32.2.3Summary4Principle of Adaptive Partitioning42.3.1Static Analysis and Transformation42.3.2Dynamic Adaptation4                                                                                              | <b>25</b><br>26<br>29<br>31<br>33<br>34<br>38<br>42<br>42<br>44<br>45       |

|        | <b>Auto</b> 2.1 | omatic Adaptation for Iterated Sequences of Irregular Kernels2Context and Parallelization Model22.1.1 Context22.1.2 Parallelization Model22.1.3 Partitioning Strategies22.1.3 Partitioning Strategies3Challenges32.2.1 Data Partitioning32.2.2 Load Balancing32.2.3 Summary4Principle of Adaptive Partitioning42.3.1 Static Analysis and Transformation42.3.2 Dynamic Adaptation442.3.3 Buffer Management                                                            | <b>25</b><br>26<br>29<br>31<br>33<br>34<br>38<br>42<br>42<br>44<br>45<br>45 |

|        | <b>Auto</b> 2.1 | omatic Adaptation for Iterated Sequences of Irregular Kernels2Context and Parallelization Model22.1.1Context2.1.2Parallelization Model2.1.3Partitioning Strategies2.1.3Partitioning Strategies2.1.1Data Partitioning2.2.2Load Balancing2.2.3Summary2.3.1Static Analysis and Transformation2.3.2Dynamic Adaptation2.3.3Buffer Management2.3.4General Algorithm                                                                                                        | <b>25</b><br>26<br>29<br>31<br>33<br>34<br>38<br>42<br>42<br>44<br>45       |

| 4.1       Load Balancing Computation       76         4.1.1       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       78         4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       81         4.2.2       Evaluation       85         4.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       90         4.3.3       Fine-grained Partitioning       90         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         II       Detection of Collective Errors Origin in Parallel Applications       97         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experime                                                                 | 3 | Auto | omatic Data Partitioning 49                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|-------------------------------------------------------------------------------|

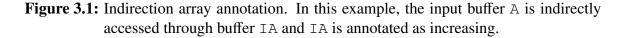

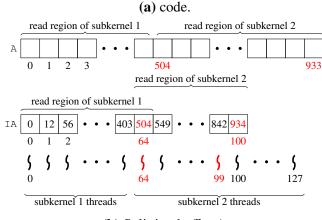

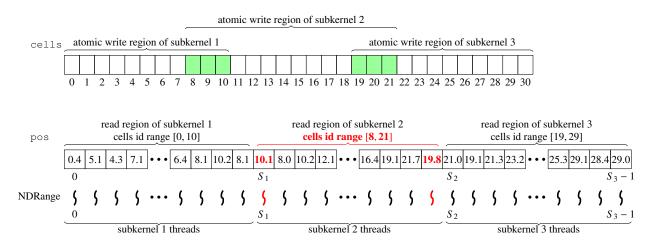

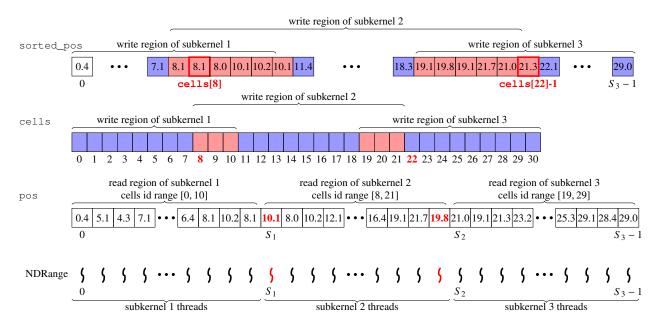

| 3.1.2       Parametric Region Construction and Instantiation       52         3.1.3       Overlapping Write Regions       55         3.1.4       Atomics       57         3.1.5       Limits       57         3.1.6       Atomics       57         3.1.5       Limits       57         3.2       Case Study: SOTL       58         3.2.1       Algorithm and Data Structures       59         3.2.2       Kernels Analysis       62         3.2.3       Evaluation       69         3.3       Related Work       70         3.4       Summary       72         4       Dynamic Load Balancing of Iterated Sequences of Irregular Kernels       75         4.1       Load Balancing Computation       76         4.1.1       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       81         4.2.1       Formalization       81         4.2.2       Evaluation                                                                                                                                                                    |   | 3.1  | Memory Region Analysis                                                        |

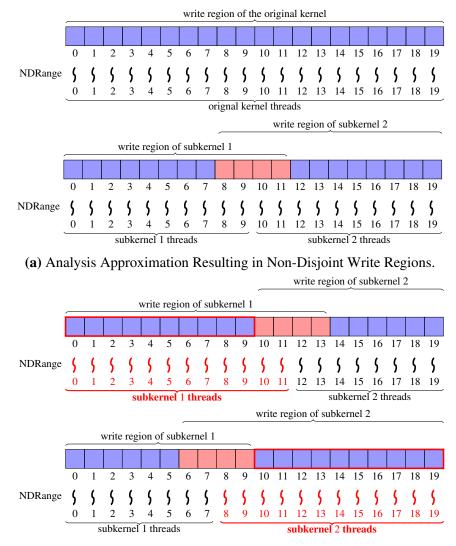

| 3.1.3       Overlapping Write Regions       55         3.1.4       Atomics       57         3.1.5       Limits       57         3.1.5       Limits       57         3.1.6       Case Study: SOTL       58         3.2.1       Algorithm and Data Structures       59         3.2.2       Kernels Analysis       62         3.2.3       Evaluation       69         3.3       Related Work       70         3.4       Summary       72         4       Dynamic Load Balancing of Iterated Sequences of Irregular Kernels       75         4.1       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       76         4.2.1       Formalization       76         4.2.2       Evaluation       78         4.3.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grained Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95 <th></th> <th></th> <th>3.1.1 Objectives and Principles</th>                                                                       |   |      | 3.1.1 Objectives and Principles                                               |

| 3.1.4       Atomics       57         3.1.5       Limits       57         3.2       Case Study: SOTL       58         3.2.1       Algorithm and Data Structures       59         3.2.2       Kernels Analysis       62         3.2.3       Evaluation       69         3.3       Related Work       70         3.4       Summary       72         4       Dynamic Load Balancing of Iterated Sequences of Irregular Kernels       75         4.1       Load Balancing Computation       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       76         4.1.4       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       78         4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       81         4.2.2       Evaluation       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grained Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91 </th <th></th> <th></th> <th>3.1.2 Parametric Region Construction and Instantiation</th>                                         |   |      | 3.1.2 Parametric Region Construction and Instantiation                        |

| 3.1.5       Limits       57         3.2       Case Study: SOTL       58         3.2.1       Algorithm and Data Structures       59         3.2.2       Kenels Analysis       62         3.2.3       Evaluation       69         3.3       Related Work       70         3.4       Summary       72         4       Dynamic Load Balancing of Iterated Sequences of Irregular Kernels       75         4.1       Load Balancing Computation       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       76         4.1.4       Resolution Method       77         4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       78         4.2.2       Consuccation-Aware Load Balancing       81         4.2.1       Formalization       81         4.3.2       Dynamic Coarse-grained Partitioning       90         4.3.3       Static Coarse-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       97<                                                                           |   |      | 3.1.3 Overlapping Write Regions                                               |

| 3.2       Case Study: SOTL       58         3.2.1       Algorithm and Data Structures       59         3.2.2       Kernels Analysis       62         3.2.3       Evaluation       69         3.3       Related Work       70         3.4       Summary       72         4       Dynamic Load Balancing of Iterated Sequences of Irregular Kernels       75         4.1       Load Balancing Computation       76         4.1.1       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       78         4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       81         4.2.2       Evaluation       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grain Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         9       S.1       Objective ef our Full-Interprocedural Collectives Verification       97         5.1       Dylactive of our Full-Interproced                                                                          |   |      | 3.1.4 Atomics                                                                 |

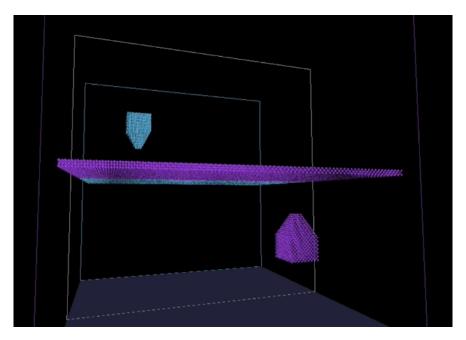

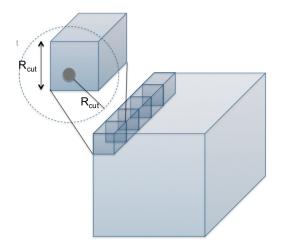

| 3.2.1       Agorithm and Data Structures       59         3.2.2       Kernels Analysis       62         3.2.3       Evaluation       69         3.3       Related Work       70         3.4       Summary       72         4       Dynamic Load Balancing of Iterated Sequences of Irregular Kernels       75         4.1       Load Balancing Computation       76         4.1.1       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       76         4.1.4       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       81         4.2.1       Formalization       81         4.2.2       Evaluation       85         4.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         9       5.1       Detection of Collective Errors Origin in Parallel Applications         97 <t< th=""><th></th><th></th><th>3.1.5 Limits</th></t<>                                                           |   |      | 3.1.5 Limits                                                                  |

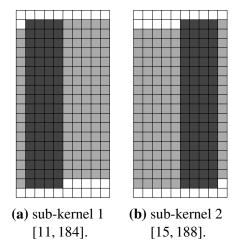

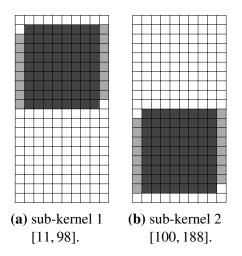

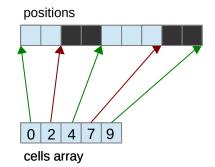

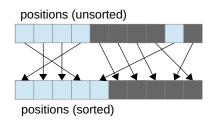

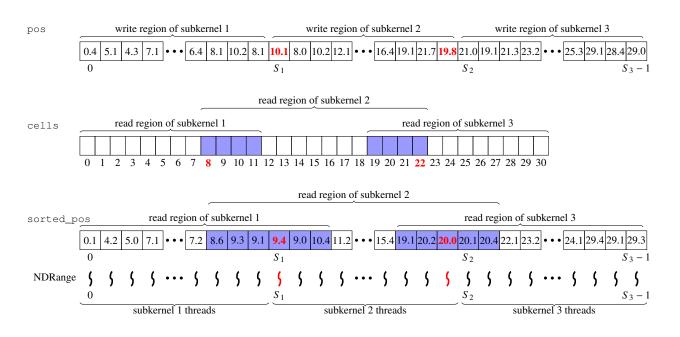

| 3.2.2       Kernels Analysis       62         3.2.3       Evaluation       69         3.3       Related Work       70         3.4       Summary       72         4       Dynamic Load Balancing of Iterated Sequences of Irregular Kernels       75         4.1       Load Balancing Computation       76         4.1.1       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       78         4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       81         4.2.2       Evaluation       85         4.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grained Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         7       Detection of Collective Errors Origin in Parallel Applications       97         5.1       Detection of collective Error Detection       99         5.1.1       PARCOACH       100       5                                                                                   |   | 3.2  | Case Study: SOTL                                                              |

| 3.2.3       Evaluation       69         3.3       Related Work       70         3.4       Summary       72         4       Dynamic Load Balancing of Iterated Sequences of Irregular Kernels       75         4.1       Load Balancing Computation       76         4.1.1       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       78         4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       81         4.2.2       Evaluation       81         4.2.1       Formalization       81         4.2.2       Evaluation       81         4.2.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grain Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         97       Summary and conclusion of the first part       95         98       5.1       Objectives and Principles       100                                                                                                                      |   |      | 3.2.1 Algorithm and Data Structures                                           |

| 3.3       Related Work       70         3.4       Summary       72         4       Dynamic Load Balancing of Iterated Sequences of Irregular Kernels       75         4.1       Load Balancing Computation       76         4.1.1       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       78         4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       81         4.2.2       Evaluation       81         4.2.1       Formalization       81         4.2.2       Evaluation       81         4.2.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grain Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         97       S1.1       Objectives and Principles       100         5.1.1       PARCOACH       100       100         5.1.2       Objective of our Full-Interprocedural Analysis       107                                                                                                  |   |      | 3.2.2 Kernels Analysis                                                        |

| 3.4       Summary       72         4       Dynamic Load Balancing of Iterated Sequences of Irregular Kernels       75         4.1       Load Balancing Computation       76         4.1.1       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       78         4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       81         4.2.2       Evaluation       85         4.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grained Partitioning       90         4.3.3       Fine-grained Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         7       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2       Full-I                                                                 |   |      | 3.2.3 Evaluation                                                              |

| 4       Dynamic Load Balancing of Iterated Sequences of Irregular Kernels       75         4.1       Load Balancing Computation       76         4.1.1       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       78         4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       81         4.2.2       Evaluation       85         4.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       90         4.3.2       Dynamic Coarse-grained Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         9       5.1       Objectives and Principles       100         5.1.1       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objective of our Full-Interprocedural Analysis       107         5.2       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108                                             |   | 3.3  | Related Work                                                                  |

| 4.1       Load Balancing Computation       76         4.1.1       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       78         4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       81         4.2.2       Evaluation       85         4.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grain Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         II       Detection of Collective Errors Origin in Parallel Applications       97         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3                                                                  |   | 3.4  | Summary                                                                       |

| 4.1.1       Formalization       76         4.1.2       Resolution Method       77         4.1.3       Evaluation       78         4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       81         4.2.2       Evaluation       85         4.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grained Partitioning       90         4.3.3       Fine-grained Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         II       Detection of Collective Errors Origin in Parallel Applications       97         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       PARCOACH Extension for a Full-Interprocedural Analysis       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108                                              | 4 | Dyn  | amic Load Balancing of Iterated Sequences of Irregular Kernels 75             |

| 4.1.2       Resolution Method       77         4.1.3       Evaluation       78         4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       81         4.2.2       Evaluation       85         4.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grain Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95 <b>II</b> Detection of Collective Errors Origin in Parallel Applications       97 <b>5</b> PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111                                                                        |   | 4.1  | Load Balancing Computation                                                    |

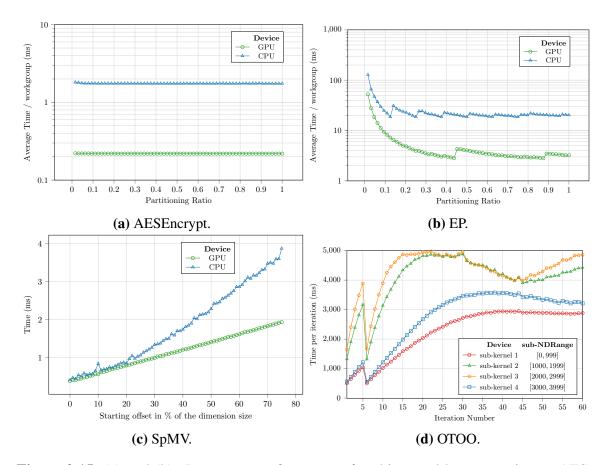

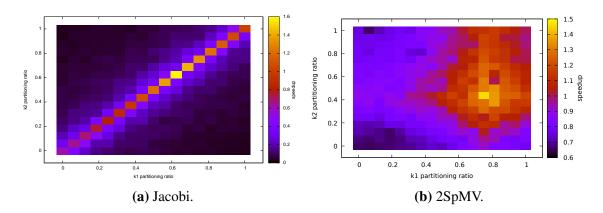

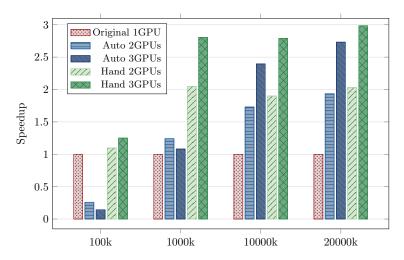

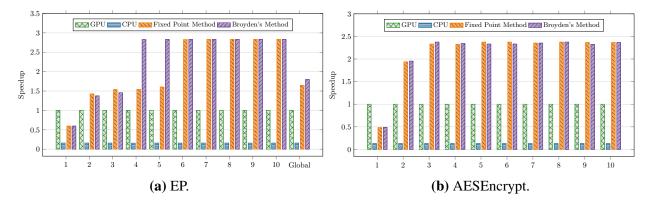

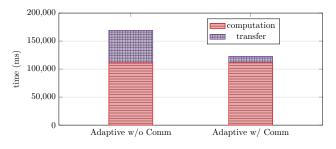

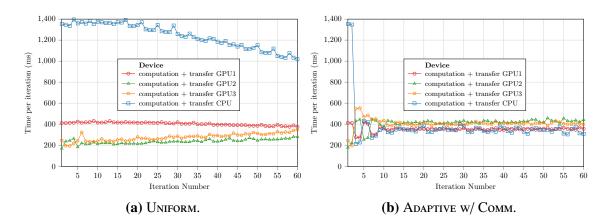

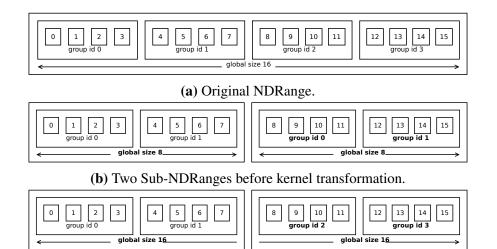

| 4.1.3       Evaluation       78         4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       81         4.2.2       Evaluation       81         4.2.2       Evaluation       85         4.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grain Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         II       Detection of Collective Errors Origin in Parallel Applications       97         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2.4       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111 <t< th=""><th></th><th></th><th>4.1.1 Formalization</th></t<> |   |      | 4.1.1 Formalization                                                           |

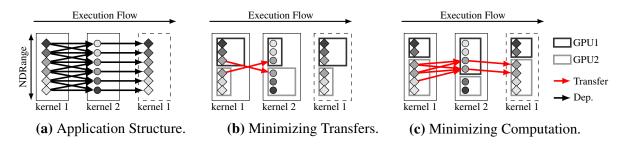

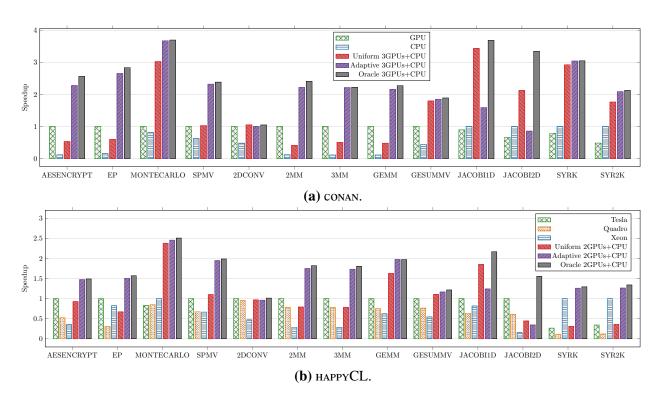

| 4.2       Communication-Aware Load Balancing       81         4.2.1       Formalization       81         4.2.2       Evaluation       85         4.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grain Partitioning       90         4.3.3       Fine-grained Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95 <b>II</b> Detection of Collective Errors Origin in Parallel Applications       97         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2.4       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111 </th <th></th> <th></th> <th>4.1.2 Resolution Method</th> |   |      | 4.1.2 Resolution Method                                                       |

| 4.2.1       Formalization       81         4.2.2       Evaluation       85         4.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grain Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         II       Detection of Collective Errors Origin in Parallel Applications       97         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       108         5.3       Code Instrumentation       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                 |   |      | 4.1.3 Evaluation                                                              |

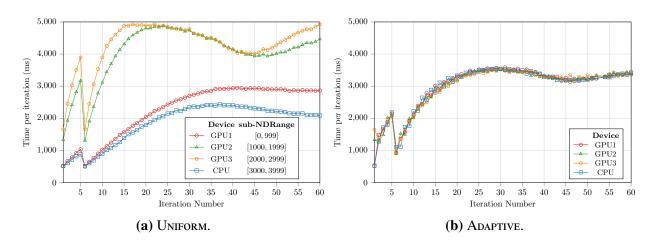

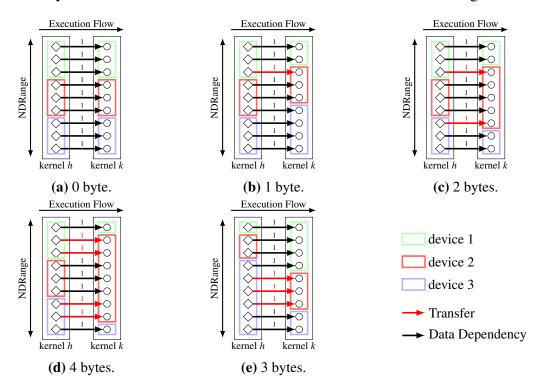

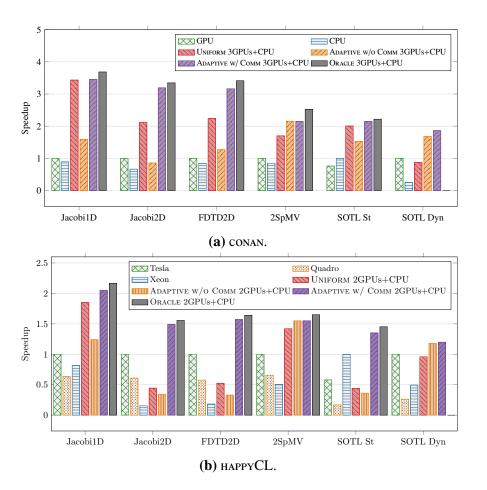

| 4.2.2       Evaluation       85         4.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grain Partitioning       90         4.3.3       Fine-grained Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95 <b>II</b> Detection of Collective Errors Origin in Parallel Applications       97         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                                                              |   | 4.2  | Communication-Aware Load Balancing                                            |

| 4.3       Related Work       88         4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grain Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         II       Detection of Collective Errors Origin in Parallel Applications       97         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                                                                                                                                                     |   |      | 4.2.1 Formalization                                                           |

| 4.3.1       Static Coarse-grained Partitioning       88         4.3.2       Dynamic Coarse-grain Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         II       Detection of Collective Errors Origin in Parallel Applications       97         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2       Full-Interprocedural Analysis       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                                                                                                                                              |   |      | 4.2.2 Evaluation                                                              |

| 4.3.2       Dynamic Coarse-grain Partitioning       90         4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       91         4.5       Summary and conclusion of the first part       95 <b>II</b> Detection of Collective Errors Origin in Parallel Applications       97         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                                                                                                |   | 4.3  | Related Work                                                                  |

| 4.3.3       Fine-grained Partitioning       91         4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         II       Detection of Collective Errors Origin in Parallel Applications       97         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      | 4.3.1 Static Coarse-grained Partitioning                                      |

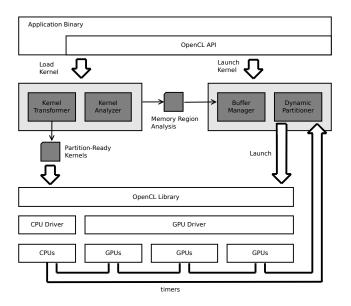

| 4.4       Implementation       91         4.5       Summary and conclusion of the first part       95         II       Detection of Collective Errors Origin in Parallel Applications       97         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |      | 4.3.2 Dynamic Coarse-grain Partitioning                                       |

| 4.5       Summary and conclusion of the first part       95         II       Detection of Collective Errors Origin in Parallel Applications       97         5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      | 4.3.3 Fine-grained Partitioning                                               |

| II Detection of Collective Errors Origin in Parallel Applications       97         5 PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1 Objectives and Principles       100         5.1.1 PARCOACH       100         5.1.2 Objective of our Full-Interprocedural Analysis       107         5.2 Full-Interprocedural Analysis       107         5.2.1 PPCFG Construction       107         5.2.2 Collective Error Detection       108         5.3 Code Instrumentation       109         5.4 Experimental Results       111         5.4.1 Static Analysis Results       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 4.4  | Implementation                                                                |

| 5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 4.5  | Summary and conclusion of the first part                                      |

| 5       PARCOACH Extension for a Full-Interprocedural Collectives Verification       99         5.1       Objectives and Principles       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      |                                                                               |

| 5.1       Objectives and Principles       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Π | De   | etection of Collective Errors Origin in Parallel Applications 97              |

| 5.1       Objectives and Principles       100         5.1.1       PARCOACH       100         5.1.2       Objective of our Full-Interprocedural Analysis       107         5.2       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5 | PAR  | <b>COACH Extension for a Full-Interprocedural Collectives Verification</b> 99 |

| 5.1.2Objective of our Full-Interprocedural Analysis1075.2Full-Interprocedural Analysis1075.2.1PPCFG Construction1075.2.2Collective Error Detection1085.3Code Instrumentation1095.4Experimental Results1115.4.1Static Analysis Results111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      | •                                                                             |

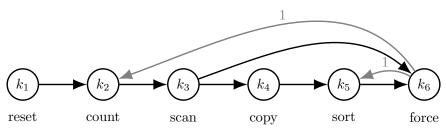

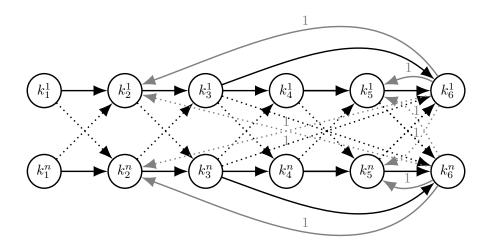

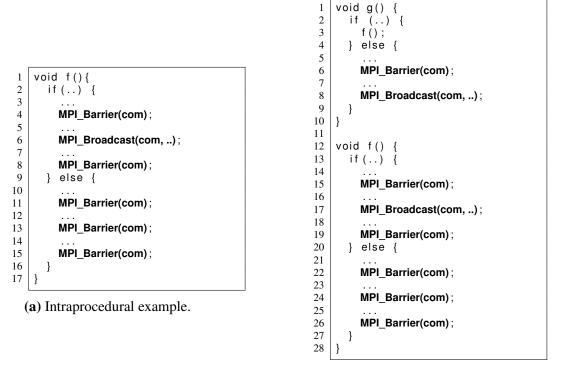

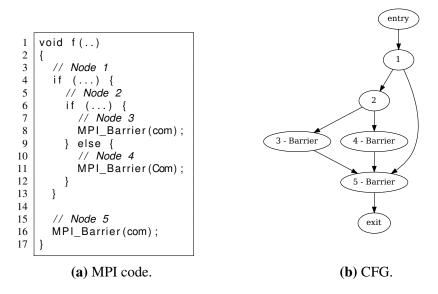

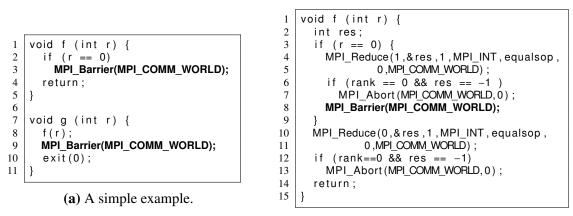

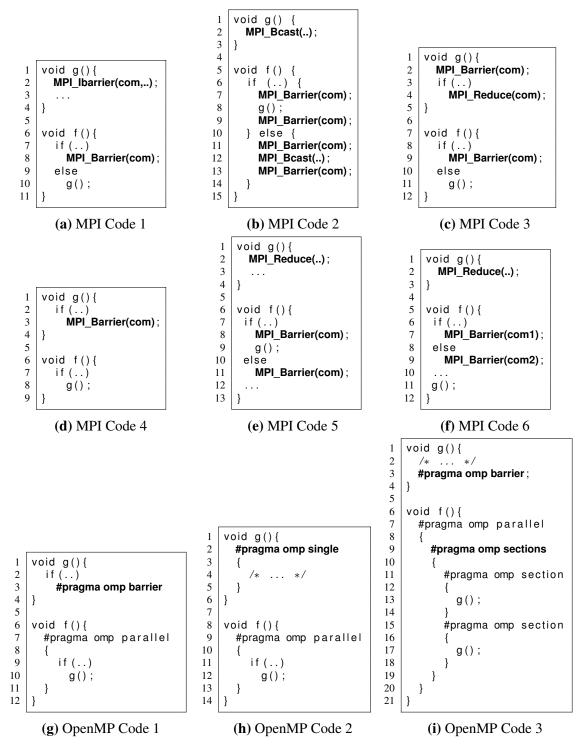

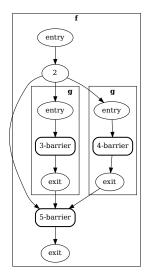

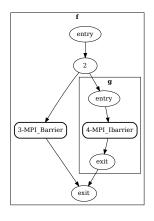

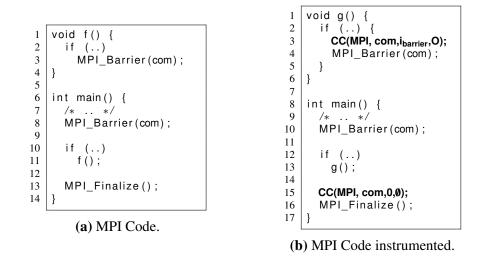

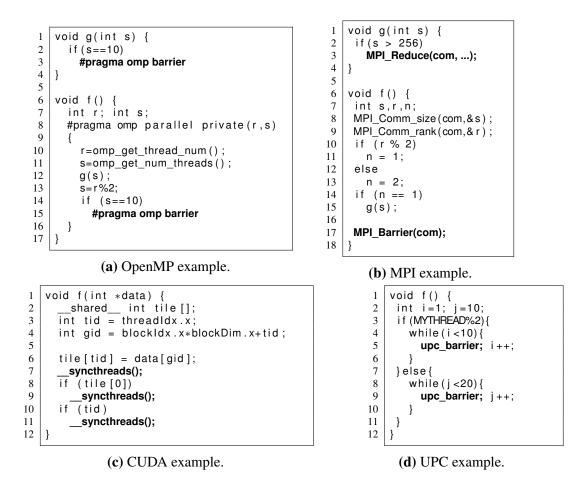

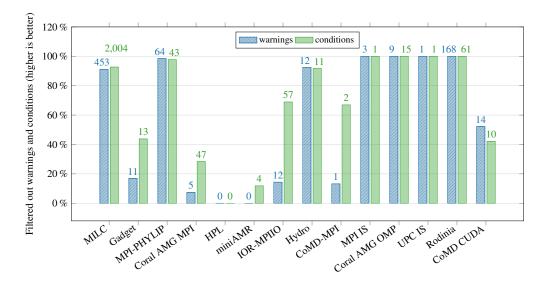

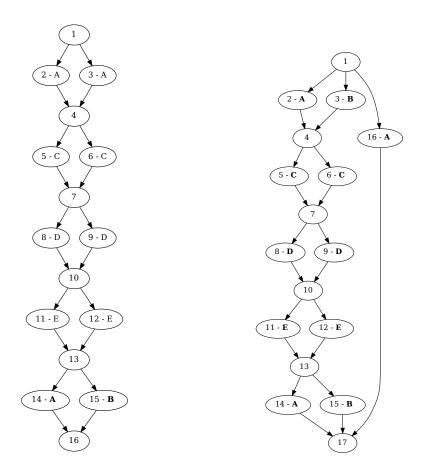

| 5.2       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 5.1.1 PARCOACH                                                                |

| 5.2       Full-Interprocedural Analysis       107         5.2.1       PPCFG Construction       107         5.2.2       Collective Error Detection       108         5.3       Code Instrumentation       109         5.4       Experimental Results       111         5.4.1       Static Analysis Results       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 5.1.2 Objective of our Full-Interprocedural Analysis                          |

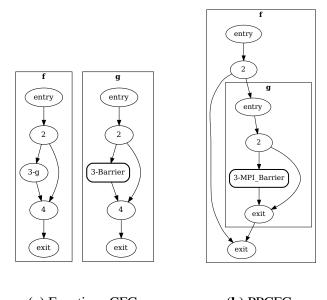

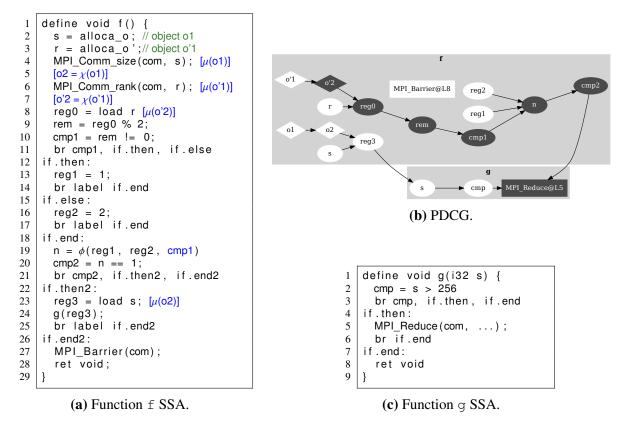

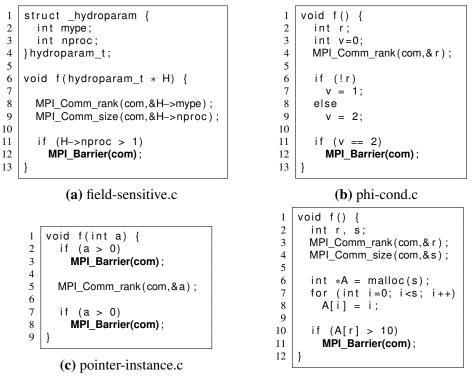

| 5.2.1PPCFG Construction1075.2.2Collective Error Detection1085.3Code Instrumentation1095.4Experimental Results1115.4.1Static Analysis Results111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 5.2  |                                                                               |

| 5.2.2Collective Error Detection1085.3Code Instrumentation1095.4Experimental Results1115.4.1Static Analysis Results111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |      | · ·                                                                           |

| <ul> <li>5.3 Code Instrumentation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      |                                                                               |

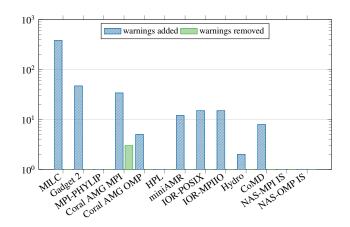

| 5.4 Experimental Results         111           5.4.1 Static Analysis Results         111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 5.3  |                                                                               |

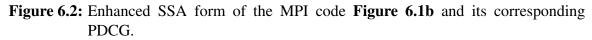

| 5.4.1 Static Analysis Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      |                                                                               |

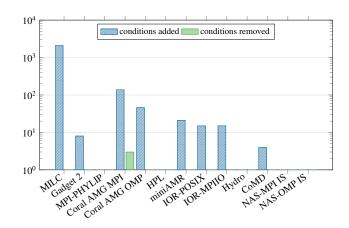

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      | •                                                                             |

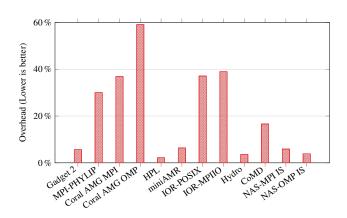

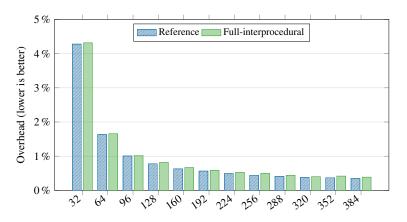

| J.4.2 Execution results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      | 5.4.2 Execution Results                                                       |

| 5.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 5.5  |                                                                               |