## Polyhedral Compilation for Domain Specific Languages Chandan Reddy

## ▶ To cite this version:

Chandan Reddy. Polyhedral Compilation for Domain Specific Languages. Computer Science [cs]. Ecole normale supérieure, 2019. English. NNT: . tel-02385670

## HAL Id: tel-02385670 https://inria.hal.science/tel-02385670v1

Submitted on 28 Nov 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT

DE L'UNIVERSITÉ PSL

Préparée à École Normale Supérieure

# **Polyhedral Compilation for Domain Specific Languages**

## Soutenue par Chanadan Reddy Le 31 Mars 2019

#### Ecole doctorale n° 386

SCIENCS MATHÉMATIQUES DE PARIS CENTRE

Spécialité INFORMATIQUE

## Composition du jury :

| M. Cédric Bastoul<br>Professor, University of Strasbourg                    | Rapporteur         |

|-----------------------------------------------------------------------------|--------------------|

| M. Saman Amarasinghe<br>Professor, Massachusetts Institute of<br>Technology | Rapporteur         |

| Mme Corinne Ancourt<br>Directeur de recherche, MINES ParisTech              | Examinateur        |

| Mme Christine Eisenbeis<br>Directeur de recherche, INRIA Saclay             | Examinateur        |

| M. Grigori Fursin<br>Ingénieur de recherche, Dividiti                       | Examinateur        |

| M. Albert Cohen<br>Directeur de recherche, Google and ENS                   | Directeur de thèse |

# Abstract

In the recent years, the complexity of optimizing compilers has increased significantly due to increasing diversity of programming languages and heterogeneity of target architectures. Even though there has been a lot of progress with the general purpose compilers, they are not been able to extract peak level performance provided by the specialized libraries. To bridge this performance gap domain specific compilers(DSLs) are proposed, by restricting input to a specialized domain it can perform more aggressive transformations needed to achieve peak performance while being more flexible than standard libraries. One of the major optimization needed to obtain high performance on modern heterogeneous architectures is loop transformations to exploiting locality and automatic parallelization. The polyhedral model has evolved as a highly efficient, reusable generic framework for loop optimizations especially for regular static control affine programs. In this thesis we explore the suitability of polyhedral loop transformation framework in context of compiling Image processing and Deep learning pipelines. We study the challenges of adapting a generic polyhedral scheduler for DSLs. We propose various extensions to the scheduler to find optimal schedule by modeling various hardware and application characteristics.

We present method to handle reductions in polyhedral model. In the state-of-the-art polyhedral compilers there was no support for reductions. The reduction loop was treated as a serial loop and this may be a major bottleneck for several applications especially on GPUs. We propose languages extensions in PENCIL to express arbitrary user-defined reductions. We encode this reduction information in polyhedral model using reduction dependences. We show how to use this dependences in polyhedral scheduler to exploit parallelization of reduction loops. We also propose a template based code generation for emitting highly efficient reduction code for GPUs. We validate our approach through experiments by comparing automatically generated code with the highly tuned library.

Exploiting locality is a key factor in achieving high performance on the complex processors with complex memory/computation hierarchies. The cost function used in the Pluto algorithm optimizes only temporal locality. Exploiting spatial locality is as important as temporal locality and it has implications on vectorization and coalesced memory accesses. we propose a new unified algorithm for optimizing parallelism and locality in loop nests, that is capable of modeling temporal and spatial effects of multiprocessors and accelerators with deep memory hierarchies and multiple levels of parallelism. It orchestrates a collection of parametrizable optimization problems for locality and parallelism objectives over a polyhedral space of semantics-preserving transformations. We discuss the rationale for this unified algorithm, and validate it on a collection of representative computational kernels/benchmarks.

We study the challenges of using polyhedral compilation techniques for a complex, real-world, end-to-end image processing application called SLAMBench. The SLAMBench has several non-affine kernels that not readily amendable for polyhedral compilation. We show the usefulness of summary functions to compile such non-affine parts of the program thus extending the reach of polyhedral compilation. We also present prl runtime library needed to avoid redundant data transfers between device and host. We validate our high-level compilation approach through experiments comparing the performance of the generated code with the highly optimized manual version of the SLAMBench.

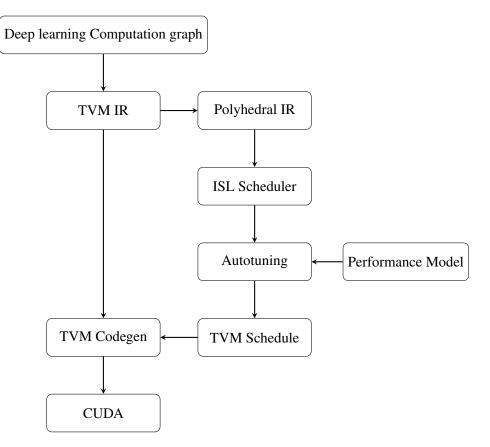

We also study the applicability of polyhedral compilation for optimizing deep learning pipelines. Most of the operations in the deep learning pipelines are affine hence are suitability for polyhedral compilation. Our framework is build on TVM an end-to-end deep learning compilation framework with support for multiple front ends such as MXNet, Tensorflow etc. and supports multiple different architectures. We extract the polyhedral representation from TVM IR and use polyhedral scheduler along with performance model based autotuning to automatically find the schedules for TVM operators. In this context we extend the polyhedral scheduler to find optimal schedules for different sizes and shapes of the tensor. We model the amount of data reuse for the case when all the parameter values are known, and formulate the constraints to ILP to maximize data reuse. We also present a performance model based autotuning technique that can cut down the tuning time from hours to minutes. We conduct experiments on the common deep learning benchmarks validating the effectiveness and general applicability of our technique in providing portable performance.

Finally, we summarize our work and present concluding remarks as well as future research directions. We believe with the improvements proposed in this dissertation improves the effectiveness of polyhedral framework as a loop transformation framework for compiling DSLs.

# Résumé

Au cours des dernières années, la complexité de l'optimisation du compilateur a considérablement augmenté en raison de la diversité croissante des langages de programmation et de l'hétérogénéité des cibles architectures. Même si les compilateurs à usage général ont beaucoup progressé, ils ne sont pas en mesure d'extraire les performances de pointe fournies par les bibliothèques spécialisées. Pour remédier à cette situation, des compilateurs spécifiques au domaine (DSL) sont proposés, en limitant la saisie à un domaine spécialisé, il peut effectuer des transformations plus agressives nécessaires pour atteindre le pic performances tout en étant plus flexible que les bibliothèques standard. Une des optimisations majeures des transformations de boucle sont nécessaires pour obtenir des performances élevées sur les architectures hétérogènes modernes à exploiter la localité et la parallélisation automatique. Le modèle polyédrique a évolué comme un cadre générique hautement efficace et réutilisable pour l'optimisation des boucles, en particulier pour programmes affines de contrôle statique réguliers. Dans cette thèse, nous explorons la pertinence de cadre de transformation de boucle polvédrique dans le contexte de la compilation Traitement de l'image et Pipelines d'apprentissage en profondeur. Nous étudions les défis de l'adaptation d'un générique ordonnanceur polyédrique pour DSL. Nous proposons diverses extensions à le planificateur pour trouver la planification optimale en modélisant divers matériels et caractéristiques d'application.

Nous présentons une méthode pour gérer les réductions dans un modèle polyédrique. Dans l'état de l'art compilateurs polyédriques, il n'ya pas eu de soutien aux réductions. La réduction boucle a été traitée comme une boucle série et cela peut être un goulot d'étranglement majeur pour plusieurs applications notamment sur les GPU. Nous proposons des extensions de langues dans PENCIL pour exprimer des réductions arbitraires définies par l'utilisateur. Nous encodons ceci informations de réduction dans un modèle polyédrique utilisant des dépendances de réduction. Nous montrons comment utiliser ces dépendances dans un planificateur polyédrique exploiter la parallélisation des boucles de réduction. Nous proposons également un génération de code basée sur des modèles pour une réduction très efficace de l'émission code pour les GPU. Nous validons notre approche par des expériences de comparer le code généré automatiquement avec le très optimisé bibliothèque.

L'exploitation de la localité est un facteur clé pour atteindre de hautes performances sur le processeurs complexes avec des hiérarchies complexes de mémoire / calcul. Le coût fonction utilisée dans l'algorithme de Pluton n'optimise que la localité temporelle. L'exploitation de la localité spatiale est aussi importante que la localité temporelle et a des implications sur la vectorisation et les accès mémoire coalescés. nous proposons un nouvel algorithme unifié pour optimiser le parallélisme et localité dans des nids de boucles, capable de modéliser temporellement et effets spatiaux des multiprocesseurs et des accélérateurs à mémoire profonde les hiérarchies et les multiples niveaux de parallélisme. Il orchestre un collection de problèmes d'optimisation paramétrables pour la localité et objectifs de parallélisme sur un espace polyédrique de préservation de la sémantique transformations. Nous discutons de la raison de cet algorithme unifié, et valider sur une collection de calcul représentatif noyaux / points de repère.

Nous étudions les défis de l'utilisation de techniques de compilation polyédriques pour SLAM-Bench, une application de traitement d'image complexe et réaliste, de bout en bout. La SLAM-Bench a plusieurs noyaux non affines qui ne peuvent pas être facilement modifiés compilation polyédrique.Nous montrons l'utilité des fonctions de synthèse pour compiler de telles parties non affines du programme étendant ainsi la portée de la compilation polyédrique. Nous présentons également la bibliothèque d'exécution prl nécessaire pour éviter les redondances. transferts de données entre l'appareil et l'hôte. Nous validons notre haut niveau approche de compilation par des expériences comparant les performances du code généré avec la version manuelle hautement optimisée de SLAMBench.

Nous étudions également l'applicabilité de la compilation polyédrique à l'optimisation pipelines d'apprentissage en profondeur. La plupart des opérations dans l'apprentissage en profondeur les pipelines sont affines et conviennent donc à la compilation polyédrique. Notre cadre repose sur TVM, une compilation d'apprentissage en profondeur de bout en bout framework avec support de plusieurs interfaces telles que MXNet, Tensorflow etc. et prend en charge plusieurs architectures différentes. Nous extrayons la représentation polyédrique de TVM IR et utilisons planificateur polyédrique avec autotuning basé sur un modèle de performance pour trouver automatiquement les horaires des opérateurs TVM. Dans ce contexte, nous étendons l'ordonnanceur polyédrique pour trouver horaires optimaux pour différentes tailles et formes du tenseur. Nous modélisons la quantité de données réutilisées pour le cas où tous les les valeurs des paramètres sont connues et formulent les contraintes à ILP maximiser la réutilisation des données. Nous présentons également un modèle de performance basé sur technique de réglage automatique qui peut réduire le temps de réglage de quelques heures à quelques minutes. Nous menons des expériences sur les critères communs d'apprentissage en profondeur qui valident la l'efficacité et l'applicabilité générale de notre technique dans fournir des performances portables.

Enfin, nous résumons nos travaux et présentons les conclusions finales ainsi que les recherches futures. directions. Nous croyons aux améliorations proposées dans cette thèse améliore l'efficacité du cadre polyédrique en tant que transformation de boucle cadre pour la compilation de DSL.

# Acknowledgements

Undertaking this Ph.D has been a truly challenging experience for me and it would not have been possible to do it without the support and guidance from many people.

Firstly, I would like to express my sincere gratitude to my advisor Albert Cohen for the continuos support my research, for his patience, motivation and immense knowledge. I highly appreciate the freedom he gave me in choosing my topics of research. I am grateful for his patience and encouragement during the difficult phase of my thesis. I would also like to thank him for funding all travel for conferences and workshops. Without his guidance and constant feedback this thesis would not have been achievable.

Besides my advisor, I would like to thank the rest of my thesis committee: Prof Cédric Bastoul, Prof Saman Amarasinghe, Mme Corinne Ancourt, Mme Christine Eisenbeis and M. Grigori Fursin. Special thanks to Prof Cédric Bastoul and Prof Saman Amarasinghe for taking time from their busy schedule to review my thesis.

I thanks my fellow team mates of Parkas lab for all the stimulating discussions and all the fun we had we had in the last four years. Thank you Tobias, Riyad, Ulysee, Alex, Jie, Guillaume, Lelio, Andy, Basile, Tim and all others. It was great sharing lab with all of you during last four years.

I am grateful to my mum, dad and sister Geetha, Gopal and Chaithra, for their moral and emotional support throughout my life. A very special gratitude to Linda for all support and encouragement during my Ph.D, very well appreciated, Thank you.

Chandan

# Contents

| Ac | know    | ledgem  | ients                                   | vii    |

|----|---------|---------|-----------------------------------------|--------|

| Li | st of f | ìgures  |                                         | xi     |

| Li | st of t | ables   |                                         | xiv    |

| In | trodu   | ction   |                                         | 1      |

| 1  | Intr    | oductio | n                                       | 1      |

|    | 1.1     | Toward  | ds Domain-specific Languages            | <br>2  |

|    | 1.2     | Handli  | ing spatial locality                    | <br>3  |

|    | 1.3     | Reduc   | tions in polyhedral model               | <br>4  |

|    | 1.4     | SLAM    | IBench compilation                      | <br>6  |

|    | 1.5     | Deep l  | earning pipeline compilation            | <br>6  |

| 2  | Bacl    | kground | d                                       | 9      |

|    | 2.1     | Polyhe  | edral framework                         |        |

|    |         | 2.1.1   | Finding Affine Schedules                | <br>10 |

|    |         | 2.1.2   | Feautrier's Algorithm                   | <br>11 |

|    |         | 2.1.3   | Pluto Algorithm                         | <br>12 |

|    | 2.2     | Polyhe  | edral Scheduling in isl                 | <br>15 |

|    |         | 2.2.1   | Scheduling Problem Specification in isl | <br>15 |

|    |         | 2.2.2   | Affine Transformations                  | <br>16 |

|    |         | 2.2.3   | Linear Independence                     | <br>17 |

|    |         | 2.2.4   | Clustering                              | <br>18 |

|    |         | 2.2.5   | Additional Transformations              | <br>19 |

| 3  | Red     | uctions | in PENCIL                               | 21     |

|    | 3.1     | Overvi  | iew of PENCIL                           | <br>21 |

|    |         | 3.1.1   | Summary Functions                       | <br>23 |

|    |         | 3.1.2   | Assume Builtin                          |        |

|    |         | 3.1.3   | Independent Directive                   | <br>24 |

|    |         | 3.1.4   | PencilKill                              | <br>25 |

|    | 3.2     | Reduct  | tion built-ins                          | <br>26 |

#### Contents

|   |      | 3.2.1   | Reduction Initialization Builtin                    | 26 |

|---|------|---------|-----------------------------------------------------|----|

|   |      | 3.2.2   | Reduction Builtin                                   | 27 |

|   |      | 3.2.3   | Related work                                        | 27 |

|   | 3.3  | Modeli  | ing Reductions in Polyhedral Model                  | 30 |

|   |      | 3.3.1   | Reduction Domain                                    | 30 |

|   |      | 3.3.2   | Reduction Dependences                               | 31 |

|   |      | 3.3.3   | Reduction-Enabled Scheduling                        | 31 |

|   |      | 3.3.4   | Related work                                        | 32 |

|   | 3.4  | Code C  | Generation                                          | 34 |

|   |      | 3.4.1   | Optimizations for Reduction code on GPUs            | 34 |

|   |      | 3.4.2   | Template Specialization for User-defined Reductions | 35 |

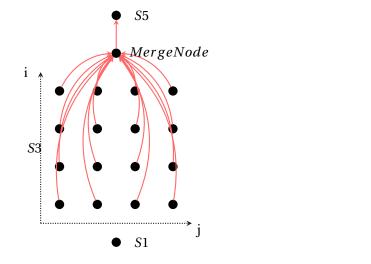

|   | 3.5  | Experie | mental Evaluation                                   | 37 |

|   |      | 3.5.1   | Single Reduction Kernel                             | 37 |

|   |      | 3.5.2   | Srand Reduction kernel                              | 38 |

|   |      | 3.5.3   | SLAMBench reduction kernel                          | 38 |

| 4 | SL A | MBenc   | h                                                   | 41 |

| - | 4.1  |         | Bench Kernels                                       |    |

|   | 4.2  |         | zing SLAMBench Kernels                              | -  |

|   | 4.3  |         | ary functions                                       |    |

|   | 4.4  |         | ng Reductions                                       |    |

|   | 4.5  |         | intime                                              |    |

|   |      |         |                                                     |    |

| 5 |      |         | lel for Spatial Locality and Coalescing             | 51 |

|   | 5.1  |         | ing Line-Based Access                               |    |

|   | 5.2  | -       | Proximity Relations                                 |    |

|   | 5.3  | -       | ral Proximity Relations                             |    |

|   | 5.4  |         | ng as Few Spatial Proximity Relations as Possible   |    |

|   | 5.5  | -       | ng and Prioritizing Spatial Proximity Constraints   |    |

|   | 5.6  |         | oblem to Carry Many Spatial Proximity Relations     |    |

|   | 5.7  |         | lling for CPU Targets                               |    |

|   | 5.8  |         | lling for GPU Targets                               |    |

|   | 5.9  | -       | mental Evaluation                                   |    |

|   |      | 5.9.1   | Implementation Details                              | 60 |

|   |      | 5.9.2   | Experimental Protocol                               | 61 |

|   |      | 5.9.3   | Sequential Code Performance                         |    |

|   |      | 5.9.4   | Parallel CPU Code Performance                       | 63 |

|   |      | 5.9.5   | Comparison with Hybrid Affine/Syntactic Approach    | 64 |

|   |      | 5.9.6   | Parallel GPU Code Performance                       | 65 |

|   | 5.10 |         | nces in Schedules: Case Study Discussions           |    |

|   |      | 5.10.1  | Two Matrix Multiplications                          |    |

|   |      |         | LU Decomposition                                    |    |

|   |      | 5.10.3  | Triangular Matrix Multiplication                    | 69 |

| 6  | Auto   | ) schedu | lling Deep learning pipelines             | 71  |

|----|--------|----------|-------------------------------------------|-----|

|    | 6.1    | TVM .    |                                           | 71  |

|    |        | 6.1.1    | TVM schedule primitives                   | 73  |

|    | 6.2    | Problem  | m specialization                          | 77  |

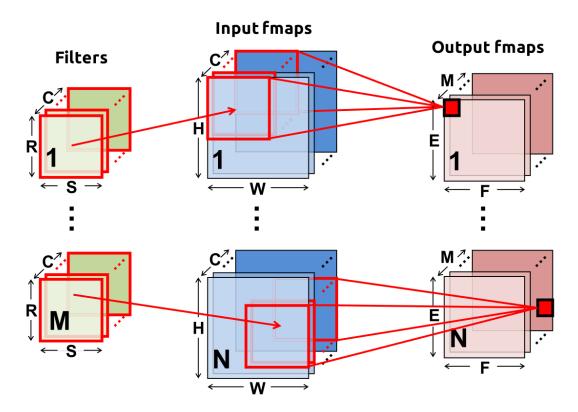

|    |        | 6.2.1    | Convolutions                              | 77  |

|    |        | 6.2.2    | Data reuse in Convolutions                | 78  |

|    |        | 6.2.3    | Parameter specific cost function          | 79  |

|    | 6.3    | Auto ti  | uning                                     | 83  |

|    |        | 6.3.1    | Performance model from data               | 84  |

|    |        | 6.3.2    | Operator specific model                   | 84  |

|    |        | 6.3.3    | Transfer learning across architectures    | 85  |

|    |        | 6.3.4    | Transfer learning across operators        | 86  |

|    | 6.4    | Experi   | mental results                            | 88  |

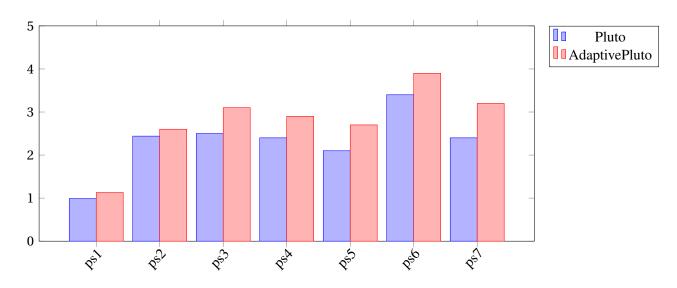

|    |        | 6.4.1    | Adaptive schedule                         | 88  |

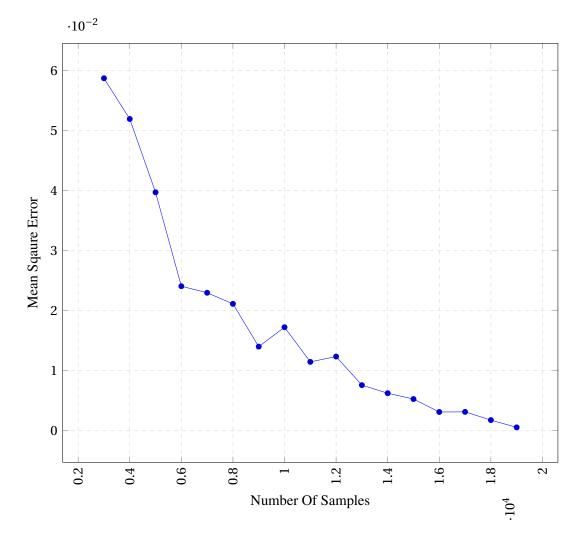

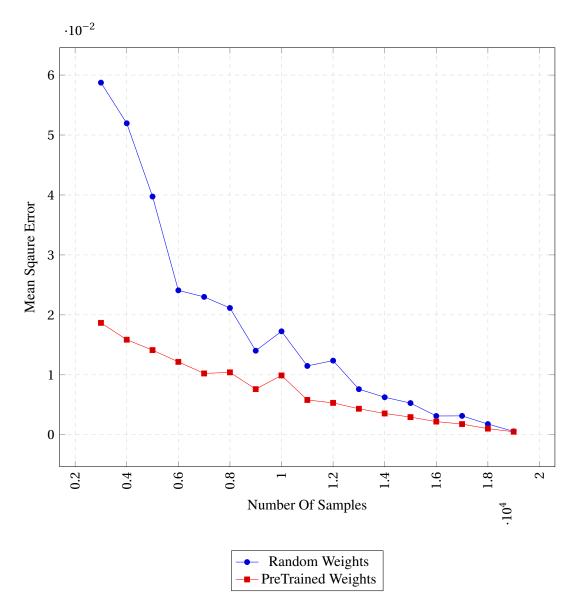

|    |        | 6.4.2    | Model accuracy                            | 89  |

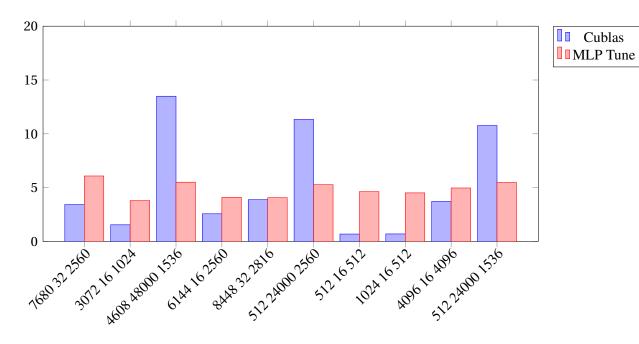

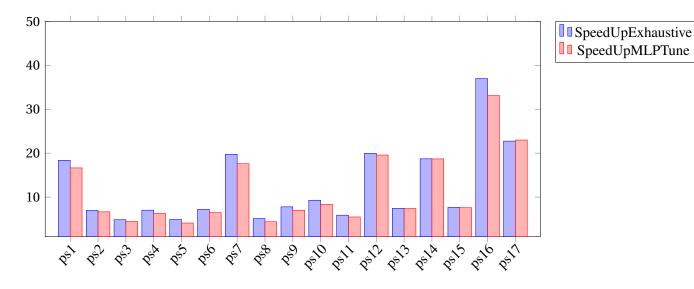

|    |        | 6.4.3    | MLP tuning vs Exhaustive                  | 90  |

|    |        | 6.4.4    | Performance of Generated kernels          | 91  |

|    |        | 6.4.5    | Tuning Convolution kernels                | 91  |

|    |        | 6.4.6    | MLP Tune vs other search techniques       |     |

|    |        | 6.4.7    | Transfer Learning                         | 93  |

| 7  | Con    | clusion  | and Perspectives                          | 97  |

|    | 7.1    | Conclu   | sion                                      | 97  |

|    |        | 7.1.1    | Handling reductions                       | 97  |

|    |        | 7.1.2    | Spatial locality                          | 98  |

|    |        | 7.1.3    | SLAMBench                                 | 98  |

|    |        | 7.1.4    | DeepLearning pipelines                    | 98  |

|    | 7.2    | Future   | Work                                      | 99  |

|    |        | 7.2.1    | Learning hardware specific cost functions | 99  |

|    |        | 7.2.2    | Fusion heuristics                         | 99  |

| A  | An a   | ppendi   | X                                         | 101 |

| Bi | bliogı | aphy     |                                           | 111 |

# List of Figures

| 2.1  | Naive implementation.of matrix multiplication                                      | 9  |

|------|------------------------------------------------------------------------------------|----|

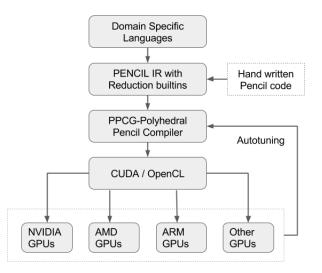

| 3.1  | A high level overview of the PENCILcompilation flow                                | 22 |

| 3.2  | Example code illustrating the use of summary functions                             | 24 |

| 3.3  | Complex number multiplication                                                      | 27 |

| 3.4  | Reduction from Rodinia's Srand benchmark                                           | 28 |

| 3.5  | Example from Rodinia's Srand reduction in PENCIL                                   | 29 |

| 3.6  | Example from PolyBench's correlation benchmark                                     | 29 |

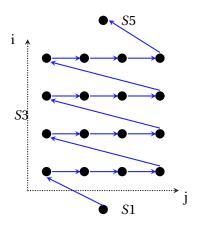

| 3.7  | Original reduction domain and dependences                                          | 30 |

| 3.8  | Modified reduction dependences                                                     | 30 |

| 3.9  | Performance on NVIDIA GeForce GTX 470                                              | 39 |

| 3.10 | Performance on NVIDIA Quadro K4000                                                 | 39 |

| 3.11 | Performance on NVIDIA TK1                                                          | 39 |

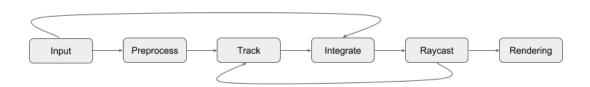

| 4.1  | A high level overview of the SLAMBench pipeline                                    | 42 |

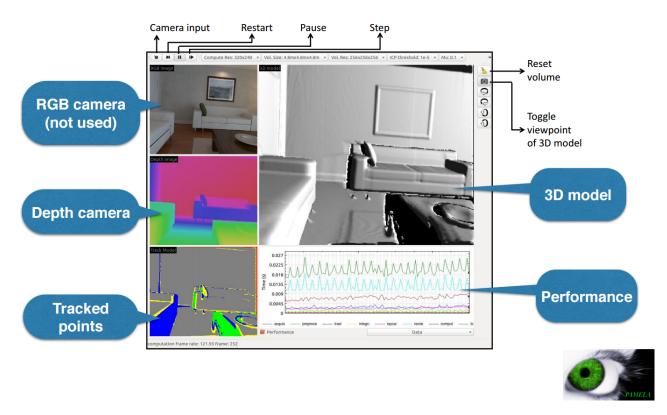

| 4.2  | SLAMBench GUI                                                                      | 42 |

| 4.3  | Pencilized mm2meters kernel                                                        | 45 |

| 4.4  | Integrate kernel with Summary function                                             | 46 |

| 4.5  | PRL memory flags                                                                   | 48 |

| 4.6  | PRL allocation calls                                                               | 49 |

| 5.1  | Non-identical (S1) and non-uniform (S2) accesses to an array.                      | 53 |

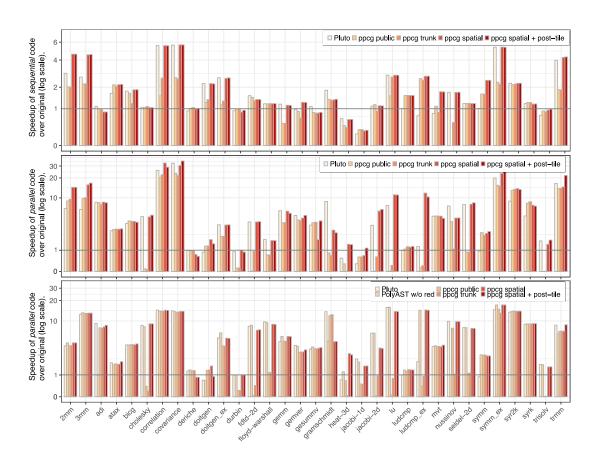

| 5.2  | Speedup of the optimized tiled code over the original code with different schedul- |    |

|      | ing algorithms; top: sequential code on skylake, middle: parallel code on ivy;     |    |

|      | bottom: parallel code on <b>westmere</b>                                           | 64 |

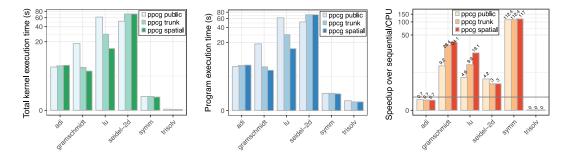

| 5.3  | Left and center graphs show total kernel execution time and program execution      |    |

|      | time (lower is better). Right graph shows speedup over CPU sequential version      |    |

|      | (higher is better)                                                                 | 66 |

| 5.4  | Parameter values, number of kernels generated by public and spatial versions of    |    |

|      | ppcg and cumulative number of invocations of those kernels for each benchmark      |    |

|      | (lower is better).                                                                 | 66 |

| 5.5  | Code of the $2mm$ (left) and $lu$ (right) benchmarks with labeled statements       | 68 |

| 6.1  | TVM auto scheduling overview                                                       | 72 |

| 6.2  | Convolution computation                                | 77 |

|------|--------------------------------------------------------|----|

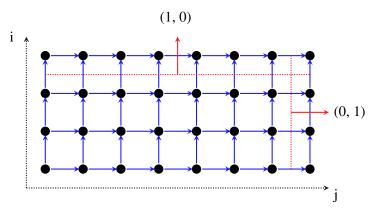

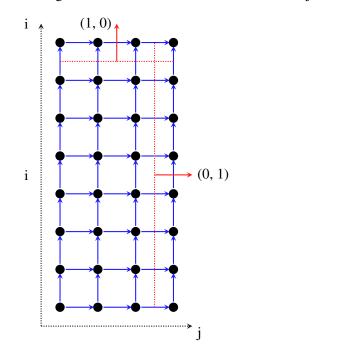

| 6.3  | Problem instance with $i < 5$ and $j < 9$              | 80 |

| 6.4  | Problem instance with $i < 9$ and $j < 5$              | 80 |

| 6.5  | Synthetic example                                      | 80 |

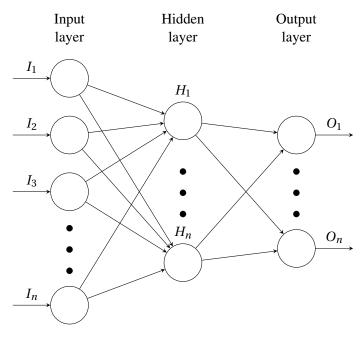

| 6.6  | Multi Layered Perceptron(MLP)                          | 85 |

| 6.7  | SpeedUp of Convolution kernel with Resnet-50 workloads | 88 |

| 6.8  | Reduction in Mean square error with number of samples  | 89 |

| 6.9  | Speedup MLP Tune vs. Cublas                            | 91 |

| 6.10 | Speedup MLP Tune vs. Exhaustive for Convolution HWCN   | 92 |

| 6.11 | Reduction in Mean square error with pre existing model | 95 |

# List of Tables

| 3.1 | Optimal parameter values for the number of thread blocks and for the thread     |    |

|-----|---------------------------------------------------------------------------------|----|

|     | block size                                                                      | 38 |

| 3.2 | Speedup of the SLAMBench reduction kernel relative to the manual implementation | 40 |

| 4.1 | SLAMBench Kernels                                                               | 43 |

| 4.2 | Pencilizing First attempt, Manual : 68 FPS, PPCG : 0.1 FPS                      | 45 |

| 4.3 | With Summary functions, Manual : 68 FPS, PPCG : 1 FPS                           | 47 |

| 4.4 | With Parallel reductions, Manual : 68 FPS, PPCG : 50 FPS                        | 47 |

| 6.1 | Resnet Problem Sizes                                                            | 79 |

| 6.2 | SpeedUp of Convolution kernel in Resnet-50 with NCHW layout                     | 88 |

| 6.3 | Matrix multiplication kernel MLP tune vs Exhaustive search                      | 90 |

| 6.4 | SpeedUp MLP Tune and Exhaustive Search over TVM Manual schedule                 | 92 |

| 6.5 | Search techniques comparison                                                    | 94 |

|     |                                                                                 |    |

# **1** Introduction

Computer architectures continue to grow in complexity, stacking levels of parallelism and deepening their memory hierarchies to mitigate physical bandwidth and latency limitations. Harnessing more than a small fraction of the performance offered by such systems is a task of ever growing difficulty. Optimizing compilers transform a high-level, portable, easy-to-read program into more complex but efficient, target-specific implementation. Achieving performance portability is even more challenging: multiple architectural effects come into play that are not accurately modeled as convex optimization problems, and some may require mutually conflicting program transformations. In this context, systematic exploration of the space of semantics-preserving, parallelizing and optimizing transformations remains a primary challenge in compiler construction.

Loop nest optimization holds a particular place in optimizing compilers as, for computational programs such as those for scientific simulation, image processing, or machine learning, a large part of the execution time is spent inside nested loops. Research on loop nest transformations has a long history [Wol95, KA02]. Much of the past work focused on specific transformations, such as fusion [KM93], interchange [AK84] or tiling [Wol89, IT88], or specific objectives, such as parallelization [Wol86] or vectorization [AK87].

The *polyhedral framework* of compilation introduced a rigorous formalism to represent and operate on the control flow, data flow, and storage mapping of a growing class of loop-based programs [FL11]. It provides a unified approach to loop nest optimization, offering precise relational analyses, formal correctness guarantees and the ability to perform complex sequences of loop transformations in a single optimization step by using powerful code generation/synthesis algorithms. It has been a major force driving research on loop transformations in the past decade thanks to the availability of more generally applicable algorithms, robust and scalable implementations, and embedding into general or domain-specific compiler frameworks [PCB<sup>+</sup>06, GGL12a]. Loop transformations in polyhedral frameworks are generally abstracted by means of a *schedule*, a multidimensional relation from iterative instances of program statements to logical time. Computing the most profitable legal schedule is the primary goal of a polyhedral optimizer.

#### **Chapter 1. Introduction**

Feautrier's algorithm computes minimum delay schedules [Fea92b] for arbitrary nested loops with affine bounds and array subscripts. The Pluto algorithm revisits the method to expose coarse-grain parallelism while improving temporal data locality [BHRS08a, BAC16]. However, modern complex processor architectures have made it imperative to model more diverse sources of performance; deep memory hierarchies that favor consecutive accesses—cache lines on CPUs, memory coalescing on GPUs—are examples of hardware capabilities which must be exploited to match the performance of hand-optimized loop transformations.

### **1.1 Towards Domain-specific Languages**

There exist a large number of mature polyhedral compilation frameworks and loop optimizers, including both research projects [BHRS08b, CCH08, VCJC<sup>+</sup>13a], and commercial productions [TCE<sup>+</sup>10, GGL12b, SLLM06]. Such compilers usually take a general-purpose high-level or intermediate language as input, extract the polyhedral representation for static affine parts of it, perform loop optimizations in polyhedral IR and then transform optimizes polyhedral representation to input high-level or intermediate language. Unlike the traditional compiler where there are multiple compilation stages for each individual loop transformations, in polyhedral model all the loop transformations are combined into a single compilation stage. This greatly simplifies the loop transformation stages as we do not have to worry about ordering of individual loop transformation stages. Despite the success over traditional compilers, the optimality of the code generated by such polyhedral compilers still remains elusive, falling behind the performance of heavily hand-tuned codes written by an expert.

One of the reason of performance gap between the generated codes of optimizing compilers and hand-written programs is due to the conservativeness of general combination stages. An expert programmer makes use of domain specific and problem specific information to produce highly optimized library functions for a given architecture whose performance is close to machine peaks. The general purpose compiler does not have all the relevant domain specific information and it cannot perform aggressive transformations needed achieve peak performance. It is very difficult to prove the correctness of such aggressive transformations in a general context hence a very conservative heuristics are chosen. It is not possible for the programmer to convey this domain specific knowledge to the compiler in general purpose languages.

Domain-specific languages (DSLs) are proposed to bridge this performance gap and are becoming prevalent in many application domains. A high-level language that is specific to a given domain improves the programmer productivity since there are high level abstractions specific to a given domain can be used as building blocks. It also allows the DSL compiler to take advantage of the domain specific knowledge while compiling such high level abstractions. It can perform aggressive transformations since input domain is restricted. This makes it much easier to reason about correctness of such transformations and can use aggressive heuristics to obtain high performance. To summaries general purpose compilation is a evolutionary while domain specific compilation is revolutionary. The polyhedral model was successfully integrated with DSLs, such as those for optimizing DSLs for graphical dataflow language [BB13, SSPS15], stencil computations [HVF<sup>+</sup>13], image processing applications Halide [RKBA<sup>+</sup>13] PolyMage [MVB15] etc. Recently, due to the revolution in the field of deep learning there are several DSL compilation frameworks such as XLA in Tensorflow [AIM17], JIT compiler in Pytorch [PCC<sup>+</sup>], TensorComprehensions [VZT<sup>+</sup>18] and TVM compiler stack [tvm] are gaining popularity. The loop transformations play very a important role in achieving high performance in these domains. The polyhedral model is highly suited as intermediate representation for performing loop transformations in these DSL compilation framework.

## 1.2 Handling spatial locality

There has been some past work on incorporating knowledge about consecutive accesses into a polyhedral optimizer, mostly as a part of transforming programs for efficient vectorization [TNC<sup>+</sup>09, VMBL12, KVS<sup>+</sup>13]. However, these techniques restrict the space of schedules that can be produced; we show that these restrictions miss potentially profitable opportunities involving schedules with linearly dependent dimensions or decoupling the locality optimization of individual fused clusters of statements. In addition, these techniques model non-convex optimization problems through the introduction of additional discrete (integer, boolean) variables and introducing bounds on coefficients. These ad-hoc bounds do not practically impact the quality of the results, but remain slightly unsatisfying from a mathematical modeling perspective. Finer architectural modeling such as the introduction of spatial effects also pushes for more discrete variables, requiring extra algorithmic effort to keep the dimensional growth under control. A different class of approaches relies on a combination of polyhedral and traditional, syntactic-level loop transformations. A polyhedral optimizer is set up for one objective, while a subsequent syntactic loop transformation addresses another objective. For example, PolyAST uses a polyhedral optimizer to improve locality through affine scheduling and loop tiling. After that, it applies syntactic transformations to expose different forms of parallelism [SPS14]. Prior to PolyAST, the pioneering Pluto compiler itself relied on a heuristic loop permutation to improve spatial locality after the main polyhedral optimization aiming for parallelism and temporal locality [BHRS08a]. Operating in isolation, the two optimization steps may end up undoing each other's work, hitting a classical compiler phase ordering problem.

We propose a polyhedral scheduling algorithm that accounts for multiple levels of parallelism and deep memory hierarchies, and does so without imposing unnecessary limits on the space of possible transformations. Ten years ago, the Pluto algorithm made a significant contribution to the theory and practice of affine scheduling for locality and parallelism. Our work extends this frontier by revisiting the models and objectives in light of concrete architectural and microarchitectural features, leveraging positive memory effects (e.g., locality) and avoiding the negative ones (e.g., false sharing). We fundamentally extend the reach of affine scheduling, seeing it as a collection of parameterizable optimization problems, with configurable constraints and objectives, allowing for schedules with linearly dependent dimensions, and dealing with non-convex spaces. In particular, we contribute a "clustering" technique for loop fusion (an essential locality-enhancing transformation) which allows to precisely intertwine the iterations of different statements while maintaining the execution order within each loop, and we extend the loop sinking options when aligning imperfectly nested loops to the same depth. We address spatial effects by extending the optimization objective and allowing for linearly dependent dimensions in affine schedules that are out of reach of a typical polyhedral optimizer. We also provide an original approach to non-convex optimization problems where negative schedule coefficients are necessary to tile loop iteration spaces while aligning them with the direction of consecutive memory accesses.

We design our algorithm as a template with multiple configuration dimensions. Its flexibility stems from a parameterizable scheduling problem and a pair of optimization objectives that can be interchanged during the scheduling process. As a result, our approach is able to produce in one polyhedral optimization pass schedules that previously required a combination of polyhedral and syntactic transformations. Since it remains within the polyhedral model, it can benefit from its transformation expressiveness and analysis power, e.g., to apply optimizations that a purely syntactic approach might not consider, or to automatically generate parallelized code for different accelerators from a single source.

## 1.3 Reductions in polyhedral model

A reduction is an associative and commutative computation that operates on a set of data reducing its dimensionality. Reductions can be found in many scientific application domains such as image processing, liner-algebra, partial differential equations, computational geometry etc. They often found in the codes that test the convergence of iterative algorithms and are executed over and over again. Reductions are also found extensively in Monte Carlo simulations where averages and variances of a vast number of random simulations need to be computed. An unoptimized or poorly optimized reduction will become the bottleneck for whole program performance. In reductions, a binary operator is applied successively to all elements of the input set. This introduces dependences between loop iterations and forces them to execute sequentially. This binary operator is usually associative and commutative. These properties allow us to ignore the sequential dependence and parallelize reductions. Since the reduction operator is associative, we can perform multiple reduction operator can further be used to optimize the reduction on parallel architectures such as GPUs.

To optimize reductions, we first need to identify them. Automatic detection of simple reductions with commonly used reduction operators such as addition, multiplication, min, max is quite trivial. There are some techniques proposed in the literature to detect them. However, when the reduction is performed on a user-defined data type or with a more complex operator it is very challenging to detect them and none of existing compiler can do this automatically. It is quite clear to the programmer identify reduction operations. Hence, we propose two extensions that allow the programmer to convey reduction information to the compiler. For a compiler to optimize reductions, it requires the identity value of reduction operator, reduction domain and the

actual reduction operator. The programmer can convey all these information using the proposed extensions with very little modifications to input code.

Even after the reduction is identified, it is not trivial to optimize them on massively parallel architectures such as GPUs. Reduction operations typically, have very low arithmetic intensity, performing one operation per load. Hence, they are bandwidth bound and require many extensive optimizations to achieve peak performance. There are many libraries like CUB, THRUST that provide a highly efficient implementation of reductions. They can achieve more than 90 percent of peak performance by performing various optimizations including using architecture-specific instruction to perform reduction and tuning parameters for a given architecture. Programmer can customize reduction by providing a reduction operator and an identity value. It is easy to map a single reduction into a library call but, when you have multiple reductions on same input data, or if you want to perform the reduction on selective elements of the input, then it is not efficient to use these libraries as they require multiple reduction calls or preprocessing of input data. For example, consider a program to find min and max elements of an array. We need two library calls, once to find the min and another one to find the max. This inefficient as one could use a single scan of the array to find both max and min. SLAMBench has a reduction kernel that performs 32 different reductions. MG benchmark of the NAS benchmark suite has a reduction kernel to find 10 largest and 10 smallest elements of an array. Using library calls in these cases will be highly inefficient. Although library APIs are highly efficient, they are not flexible enough to adapt to input program requirements.

Reductions are bound by the maximum available bandwidth of the device. We can improve the arithmetic intensity of reductions by performing certain loop transformations such as loop fusion. Performing two reductions at once is twice as fast as two separate reductions. In the latter case, input data is scanned twice, whereas in former input data is scanned only once and two reductions are performed per single load. In order to enable such transformations, we model reductions in polyhedral model. We propose a dependence based abstraction for modeling reductions in polyhedral model. This abstraction fits well into the existing polyhedral compilation toolchain while enabling loop optimizations for reductions.

We propose template based code generation for reductions. We have selected a reduction template that does have all the optimizations required to achieve peak performance. We adapt this template to match the reductions defined by the programmer. Since, we have complete information regarding reductions in the input program, we can precisely modify the template code even after we performed optimizations on reductions. We also auto-tune the template for a given GPU architecture to find optimal values for parameters such as block size, grid size and number reduction elements per threads. Thus, with our approach, we are able to generate highly efficient code for sequences of user-defined reductions that is portable across different architectures.

#### 1.4 SLAMBench compilation

SLAM [NIH<sup>+</sup>11] is the main algorithm to perform real-time localization and dense mapping using depth information. SLAMBench [NBZ<sup>+</sup>14] is open-source benchmark for real-time dense SLAM algorithm. This is a large end-to-end benchmark with 14 different kernels that constructs a 3D model from the input depth images. There are several challenges for applying polyhedral computation techniques to such a large benchmark. We port the entire SLAMBench kernel to PENCIL intermediate language and use PPCG to automatically produce CUDA and OpenCL version of kernels. Several of these kernels are non-affine and hence cannot be directly expressed in polyhedral model. We use summary functions to wrap the non-affine core kernel parts while exposing the affine loops to polyhedral model. We also show the need of runtime in avoiding redundant data copies between device and host. We propose prl runtime library that can be used to express the array access information in non pencil regions. This information is used during the program execution to decide the need to transfer data between device and the host. This approach of writing kernels in high level intermediate language (PENCIL) rather than low level device specific languages such as CUDA or OpenCL enhances the programmer productivity while providing portable performance across different GPU devices and architectures. We show the adaptability of polyhedral compilation techniques for large benchmarks.

## **1.5** Deep learning pipeline compilation

In recent years there is been an exponential growth in deep learning techniques. Deep learning pipeline has all the computations that are affine and are amendable for polyhedral compilation. Typically, in deep learning pipeline consists executing a DAG of tensor computations millions of time during training phase. This computation DAG has many layers of same computation repeated multiple time with different sizes and shapes of tensors. We study advantages and challenges of using polyhedral compilation techniques for deep learning tensor computations. We extract polyhedral intermediate representation from TVM [CMJ<sup>+</sup>18], an end-to-end compiler stack that has support for many popular deep learning frameworks such as Tensorflow, MXNet, Keras etc. We identify two key challenges with using existing polyhedral compilation techniques with deep learning computations. First, the current state-of-the-art polyhedral scheduler is agnostic to the values of program parameters such as tensor sizes. Hence, it will produce the same schedule for all the different layers with drastically different tensor sizes and shapes. We propose new additions to the Pluto algorithm that models the actual data reuse. We show how to formulate data reuse into linear constraints for the ILP so that we find the schedule that maximizes data reuse. This additional constraints ensure that we find optimal schedule for any given problem sizes. The second problem that we address is improving the autotuning time.

The ILP based polyhedral scheduler automatically finds the best loop transformations. In order to map such computations to GPUs, we need to choose the value of various parameters such as tile sizes, block sizes, grid sizes, unroll factors etc.. Typically, we use an autotuner to find the optimal values of these parameters. The autotuner does an exhaustive search on the entire exponential search space to find the optimal values. The optimal values of these parameters depends on the particular GPU architecture and problem size. We need to repeat the expensive exhaustive search for different problem sizes and GPU architectures. We propose a performance model based autotuning that drastically reduces time for autotuning from hours to minutes. We propose a performance model based approach to filter the worst candidates from the search space. We automatically build a performance model for each operator on a given architecture. The performance model will predict the execution time of kernel for any given size and parameter values. The performance model a MLP (Multi-layered-perceptron) model that is built from data collected by uniform sampling of the search space. We built an accurate performance model with this approach. We use this model on all the valid candidates on the search space and pick only a few hundred best candidates. Only these candidates are evaluated on the hardware to find the optimal parameter values.

In summary, these are the main contributions of the thesis:

- First class support for reductions in polyhedral model using reduction dependences, extend scheduler to support reductions and template based code generation for GPUs.

- Modeling spatial locality and extending ILP scheduler to handle multiple conflicting objectives.

- Polyhedral compilation of end-to-end real world 3D imaging SLAMBench benchmark.

- Data reuse volume extensions to ILP scheduler to adapt the schedule with problem sizes in the context of compiling deep learning pipeline in polyhedral framework.

# **2** Background

#### 2.1 Polyhedral framework

The polyhedral framework is a linear algebraic representation of the program parts that are "sufficiently regular". It may represent arithmetic expressions surrounded by loops and branches whose conditions are affine functions of outer loop iterators and runtime constants [FL11]. These constants, referred to as *parameters*, may be unknown at compilation time and are treated symbolically. Expressions may read and write to multidimensional arrays with the same restrictions on the subscripts as on control flow. It has been the main drive for research on loop optimization and parallelization in the last two decades [Fea92b, Bas04, BHRS08a, GGL12a].

The polyhedral framework operates on individual executions of statements inside loops, or *statement instances*, which are identified by a named multidimensional vector, where the name identifies the statement and the coordinates correspond to iteration variables of the surrounding loops. The set of all named vectors is called the *iteration domain* of the statement. Iteration domains can be expressed as multidimensional sets constrained by Presburger formulas [PW94a]. For example, the code fragment in Figure 2.1 contains two statements, S and R with iteration domains  $\mathcal{D}_{S}(N) = \{S(i, j) \mid 0 \le i, j < N\}$  and  $\mathcal{D}_{R}(N) = \{R(i, j, k) \mid 0 \le i, j, k < N\}$  respectively. In this paper, we use parametric named relations as proposed in *iscc* [Ver11]; note that set vectors in  $\mathcal{D}_{S}$  and  $\mathcal{D}_{R}$  are prefixed with the statement name. Unless otherwise specified, we assume all values to be integer,  $i, j, \dots \in \mathbb{Z}$ .

Polyhedral modeling of the control flow maps every statement instance to a multidimensional logical execution date [Fea92b]. The instances are executed following the lexicographic order of

```

for (i = 0; i < N; ++i)

for (j = 0; j < N; ++j)

S: C[i][j] = 0.0;

for (i = 0; i < N; ++i)

for (j = 0; j < N; ++j)

for (k = 0; k < N; ++k)

R: C[i][j] = A[i][k] * B[k][j];

Figure 2.1 – Naive implementation of matrix multiplication.

```

their execution dates. This mapping is called a *schedule*, typically defined by piecewise(quasi-) affine functions over the iteration domain  $\mathcal{T}_{S}(p) = \{i \rightarrow t \mid \{t_j = \phi_{S,j}(i, p)\} \land i \in \mathcal{D}_{S}\}$ , which are disjoint unions of affine functions defined on a finite partition of the iteration domain, allowing integer division by constants. They allow arbitrarily complex loop traversals and interleavings of statement instances. In this paper, x denotes a row vector and  $\vec{x}$  denotes a column vector. Code motion transformations may be expressed either by introducing *auxiliary dimensions* [KP95] in the schedule or by using a *schedule tree* structure that directly encodes enclosure and statement-level ordering [VGGC14]. For example, the schedule that preserves the original execution order in Figure 2.1 can be expressed as  $\mathcal{T}_{S}(N) = \{S(i, j) \rightarrow (t_1, t_2, t_3, t_4) \mid t_1 = 0 \land t_2 = i \land t_3 = j \land t_4 = 0\}$ ,  $\mathcal{T}_{R}(N) = \{R(i, j, k) \rightarrow (t_1, t_2, t_3, t_4) \mid t_1 = 1 \land t_2 = i \land t_3 = j \land t_4 = k\}$ . The first dimension is independent of the iteration domain and ensures that all instances of S are executed before any instance of R.

To preserve the program semantics during transformation, it is sufficient to ensure that the order of writes and reads of the same memory cell remains the same [KA02]. First, accesses to array elements (a scalar being a zero-dimensional array) are expressed as multidimensional relations between iteration domain points and named cells. For example, the statement S has one write access relation  $\mathscr{A}_{S \to C}^{write} = \{S(i, j) \to C(a_1, a_2) \mid a_1 = i \land a_2 = j\}$ . Second, pairs of statement instances accessing the same array element where at least one access is a write are combined to define a *dependence relation*. For example, the dependence between statements S and R is defined by a binary relation  $\mathscr{P}_{S \to R} = \{S(i, j) \to R(i', j', k) \mid i = i' \land j = j' \land (i, j) \in \mathscr{D}_S \land (i', j', k) \in \mathscr{D}_R\}$ . This approach relates all statement instances accessing the same memory cell and is referred to as *memory-based* dependence analysis. It is possible to compute exact *data flow* given a schedule using the *value-based* dependence analysis [Fea91]. In this case, the exact statement instance that wrote the value before a given read is identified. For example, instances of R with  $k \neq 0$  no longer depend on S:  $\mathscr{P}_{S \to R} = \{S(i, j) \to R(i', j', k) \mid i = i' \land j = j' \land k = 0 \land (i, j) \in \mathscr{D}_S \land (i', j', k) \in \mathscr{D}_R\}$ .

A dependence is *satisfied* by a schedule if all the statement instances in the domain of its relation are scheduled before their counterparts in the range of its relation, i.e., dependence sources are executed before respective sinks. A program transformation is *valid*, i.e., preserves original program semantics, if all dependences are satisfied.

#### 2.1.1 Finding Affine Schedules

Numerous optimization algorithms in the polyhedral framework define a closed form of all valid schedules and solve an optimization problem in that space. As they usually rely on integer programming, objective functions and constraints should be expressed as affine functions of iteration domain dimensions and parameters. Objectives may include: minimum latency [Fea92b], parallelism [BHRS08a], locality [BBK<sup>+</sup>08] and others.

Multidimensional affine scheduling aims to determine sequences of statement schedule functions of the form  $\phi_{S_i} = \mathbf{i} \mathbf{c}_j + \mathbf{p} \mathbf{d}_j + D$  where  $\mathbf{c}_j$ ,  $\mathbf{d}_j$ , D are (vectors of) unknown integer values. Each

such affine function defines one dimension of a multidimensional schedule.

**Dependence Distances, Dependence Satisfaction and Violation** Consider the affine form  $(\phi_{R,j}(i, p) - \phi_{S,j}(i, p))$ , defined for a dependence between S and R. This form represents the *distance* between dependent statement instances. If the distance is positive, the dependence is *strongly satisfied*, or *carried*, by per-statement scheduling functions  $\phi$ . If it is zero, the dependence is *weakly satisfied*. The dependence with a negative distance that was not *carried* by any previous scheduling function is *violated* and the corresponding program transformation is invalid. For a schedule to be valid, i.e., to preserve the original program semantics, it is sufficient that it carries all dependences [KA02].

**Farkas' Lemma** Note that the target form of the schedule function contains multiplication between unknown coefficients  $c_j$ ,  $d_j$ , D and loop iterator variables **i** that may take any value within the *iteration domain*. This relation cannot be encoded in a *linear* programming problem. Polyhedral schedulers usually rely on the affine form of Farkas' lemma, a fundamental result in linear algebra that states that an affine form  $c\vec{x} + d$  is nonnegative everywhere in the (non-empty) set defined by  $A\vec{x} + \vec{b} \ge 0$  iff it is a linear combination  $c\vec{x} + d \equiv \lambda_0 + \lambda(A\vec{x} + \vec{b})$ , where  $\lambda_0, \lambda \ge 0$ . Applying Farkas' lemma to the dependence distance relations and equating coefficients on the left and right hand side of the equivalence gives us constraints on schedule coefficients  $c_j$  for the dependence to have non-negative distance, i.e., to be weakly satisfied by the schedule function, in the iteration domains.

**Permutable Bands** A sequence of schedule functions is referred to as *schedule band*. If all of these functions weakly satisfy the same set of dependences, they can be freely interchanged with each other without violating the original program semantics. Hence the band is *permutable*. Such bands satisfy the sufficient condition for loop tiling [IT88] and are also referred to as *tilable bands*.

#### 2.1.2 Feautrier's Algorithm

Feautrier's algorithm is one of the first to systematically compute a (quasi-)affine schedule if there exists exits one [Fea92a, Fea92b]. It produces *minimal latency* schedules. The general idea of the algorithm is to find the minimal number of affine scheduling functions by ensuring that each of them carries as many dependences as possible. Once all dependence have been carried by the outer loops, the statement instances inside each individual iteration can be computed in any order, including in parallel. Hence Feautrier's algorithm exposes inner, fine-graph parallelism.

**Encoding Dependence Satisfaction** Let us introduce an extra variable  $e_k$  for each dependence in the program. This variable is constrained by  $0 \le e_k \le 1$  and by  $e_k \le \phi_{\mathsf{R}_k,j}(\mathbf{i}, \mathbf{p}) - \phi_{\mathsf{S}_k,j}(\mathbf{i}, \mathbf{p})$ ,

where  $S_k$  and  $R_k$  identify the source and the sink of the  $k^{th}$  dependence, respectively.  $e_k = 1$  iff the dependence is carried by the given schedule function.

**Affine Transformations** Feautrier's scheduler proceeds by solving linear programming (LP) problems using a special lexmin objective. This objective was introduced in the PIP tool and results in the lexicographically smallest vector of the search space [Fea88]. Intuitively, lexmin first minimizes the foremost component of the vector and only then moves on to the next component. Thus it can optimize multiple criteria and establish preference among them.

The algorithm computes schedule functions that carry as many dependences as possible by introducing a penalty for each non-carried dependence and by minimizing it. The secondary criterion is to generate small schedule coefficients, typically decomposed into minimizing sums of parameter and schedule coefficients separately. These criteria are encoded in the LP problem as

$$\operatorname{lexmin}\sum_{k}(1-e_{k}), \sum_{j=1}^{n_{s}}\sum_{i=1}^{n_{p}}d_{j,i}, \sum_{j=1}^{n_{s}}\sum_{i=1}^{\dim \mathscr{D}_{S_{j}}}c_{j,i}, e_{1}, e_{2} \dots e_{k} \dots$$

(2.1)

where individual  $d_{j,i}$  and  $c_{j,i}$  for each statement are included in the trailing positions of the vector in no particular order,  $n_p = \dim \vec{p}$  and  $n_s$  is the number of statements. The search space is constrained, using the Farkas lemma, to the values  $d_{j,i}$ ,  $c_{j,i}$  that weakly satisfy the dependences. Dependences that are carried by the newly computed schedule function are removed from further consideration. The algorithm terminates when all dependences have been carried.

#### 2.1.3 Pluto Algorithm

The Pluto algorithm is one of the core automatic parallelization and optimization algorithms [BHRS08a]. Multiple extensions have been proposed, including different search spaces [VMBL12], specializations and cost functions for GPU [VCJC<sup>+</sup>13b] and generalizations with guarantees of the existence of a solution [BAC16].

**Data Dependence Graph Level** On a higher level, Pluto operates on the data dependence graph (DDG), where nodes correspond to statements and edges together with associated relations define dependences between them. Strongly connected components (SCC) of the DDG correspond to the loops that should be preserved in the program after transformation [KA02]. Note that one loop of the original program containing multiple statements may correspond to multiple SCCs, in which case loop distribution is allowed. For each component, Pluto computes a sequence of permutable bands of maximal depth. To form each band, it iteratively computes affine functions linearly independent from the already computed ones. Linear independence ensures the algorithm makes progress towards a complete schedule on each step. Carried dependences are removed only when it is no longer possible to find a new function that weakly satisfies all of them, which

delimits the end of the permutable band. After removing some dependences, Pluto recomputes the SCC on the updated DDG and iterates until at least as many scheduling functions as nested loops are found and all dependences are carried. Components are separated by introducing an *auxiliary* dimension and scheduled by topological sorting.

Affine Transformation Level Affine transformation in Pluto is based on the observation that dependence distance  $(\phi_{R,j}(i, p) - \phi_{S,j}(i, p))$  is equal to the reuse distance, i.e. the number of iterations of the given loop between successive accesses to the same data. Minimizing this distance will improve locality. Furthermore, zero distance implies that the dependence is not carried by the loop (all accesses are made within the same iteration) and thus does not prevent its parallelization. Pluto uses Farkas' lemma to define a parametric upper bound on the distance  $(\phi_{R,j}(i, p) - \phi_{S,j}(i, p)) \le u\vec{p} + w$ , which can be minimized in an ILP problem as

lexmin  $u_1, u_2, ..., u_{n_n}, w, ..., c_{S,1}, ...$

where  $n_p = \dim \vec{p}$ , and  $c_{S,k}$  are the coefficients of  $\phi_{S,j}$ . The  $c_{S,k}$  coefficients are constrained to be represent a *valid* schedule, i.e. not violate dependences, using Farkas' lemma. They are also restricted to have at least one strictly positive component along a basis vector of the null space of the current partial schedule, which guarantees linear independence. Note that it is sufficient to have a non-zero component rather than a strictly positive one, but avoiding a trivial solution with all components being zero may be computationally expensive [BAC16].

**Fusion** Auxiliary dimensions can be used not only to separate components, but also to group them together by assigning identical constant values to these dimensions. This corresponds to a *loop fusion*. By default, Pluto sets up an integer programming problem to find such constants that optimize the *smart fusion* heuristic. This heuristic tries to maximize fusion between components while keeping the number of required prefetching streams limited [BGDR10]. Pluto also features the *maximum fusion* heuristic, which computes weakly connected components of the DDG and keeps statements together unless it is necessary to respect the dependence.

**Tiling** For each *permutable band* with at least two members, Pluto performs loop tiling after the full schedule was computed. It is applied by introducing additional schedule dimensions after the band and relating them to those of the band through linear inequalities. New dimensions correspond to *point loops* and original ones correspond to *tile loops*. Various tile shapes are supported through user-selected options. For the sake of simplicity, we hereinafter focus on rectangular tiles.

**Differentiating Tile and Point Schedule** The default tile construction uses identical schedules for *tile* and *point loops*. Pluto allows to construct different schedules using the following two

post-affine modifications. First, a *wavefront* schedule allows to expose parallelism at the tile loop level. If the outermost schedule function of the band carries dependences, i.e., the corresponding loop is not parallel, then it may be replaced by a sum of itself with the following function, performing a *loop skewing* transformation. It makes the dependences previously carried by the second-outermost function to be carried by the outermost one instead, rendering the second one parallel. Such wavefronts can be constructed for one or all remaining dimensions of the band exposing different degrees of parallelism. Second, loop *sinking* allows to leverage locality and vectorizability of point loops. Pluto chooses the point loop j that features the most locality using the heuristic based on scheduled access relations  $\mathcal{A} \circ \mathcal{T}$

$$j: L_j = n_{\rm S} \cdot \sum_i (2s_i + 4l_i + 8\nu - 16o_i) \to \max,$$

(2.2)

where  $n_S$  is the number of statements in the loop,  $s_i = 1$  if the scheduled access  $\mathcal{A}_i \circ \mathcal{T}$  features spatial locality  $a_{n_a} = kt_j + f(\mathbf{u}) + w$ ,  $1 \le k \le 4$ ,  $n_a = \dim(\text{Dom }\mathcal{A})$  and  $s_i = 0$  otherwise;  $l_i = 1$  if it yields temporal locality  $a_{n_a} = f(\mathbf{u}) + w$  and  $l_i = 0$  otherwise;  $o_i = 1$  if it does not yield either temporal or spatial locality  $s_i = l_i = 0$  and  $o_i = 0$  otherwise; and v = 1 if  $o_i = 0 \forall i$ . The loop jwith the largest  $L_j$  value is put innermost in the band, corresponding to the *loop permutation*. The validity of skewing and permutation is guaranteed by permutability of the band.

**Pluto+** Recent work on Pluto+ extends the Pluto algorithm to prove its completeness and termination as well as to enable negative schedule coefficients [BAC16]. It imposes limits on the absolute values of the coefficients to simplify of the linear independence check and zero solution avoidance.

## 2.2 Polyhedral Scheduling in isl

Let us now present a variant of the polyhedral scheduling algorithm, inspired by Pluto and implemented in the isl library [Ver10]. We occasionally refer to the embedding of the scheduling algorithm in a parallelizing compiler called ppcg [VCJC<sup>+</sup>13b]. We will review the key contributions and differences, highlighting their importance in the construction of a unified model for locality optimization.

The key contributions are: separated specification of relations for semantics preservation, locality and parallelism; schedule search space supporting arbitrarily large positive and negative coefficients; iterative approach simultaneously ensuring that zero solutions are avoided and that non-zero ones are linearly independent; dependence graph clustering mechanism allowing for more flexibility in fusion; and the instantiation of these features for different scheduling scenarios including GPU code generation [VCJC<sup>+</sup>13b].<sup>1</sup> A technical report is available for the most detailed information about the algorithm and implementation [VJ17].

#### 2.2.1 Scheduling Problem Specification in isl

The scheduler we propose offers more control by through different groups of relations suitable for specific optimization purposes:

- *validity relations* impose a partial execution order on statement instances, i.e., they are dependences sufficient to preserve program semantics;

- *proximity relations* connect statement instances that should be executed as close to each other as possible in time;

- *coincidence relations* connect statement instances that, if not executed at the same time (i.e., not coincident), prevent parallel execution.

In the simplest case, all relations are the same and match exactly the dependence relations of Pluto: pairs of statement instances accessing the same element with at least one write access. Hence they are referred to as *schedule constraints* within isl. However, only *validity* relations are directly translated into the ILP *constraints*. *Proximity* relations are used to build the objective function: the distance between related instances is minimized to exploit locality. The scheduler attempts to set the distance between points in the *coincidence* relations to zero, to expose parallelism at a given dimension of the schedule. The latter relations are also useful to inform the scheduler that certain instances may safely commute (atomically), even if dependences exist, removing those dependences from the former relations; it is a basis for *live range reordering* [VC16], which

<sup>&</sup>lt;sup>1</sup>While many of these features have been available in isl since version isl-0.06-43-g1192654, the algorithm has seen multiple improvements up until the current version; we present these features as contributions specifically geared towards the construction of better schedules for locality and parallelism, for the first time.

removes *false* dependences induced by the reuse of the same variable for different values, when the live ranges of those values do not overlap.

#### 2.2.2 Affine Transformations

**Prefix Dimensions** Similarly to Pluto, isl iteratively solves integer linear programming (ILP) problems to find permutable bands of linearly independent affine scheduling functions. It uses a lexmin objective, giving priority to initial components of the solution vector. Such behavior may be undesirable when these components express schedule coefficients: a solution with a small component followed by a very large component would be selected over a solution with a slightly larger first component but much smaller second component, while large coefficients tend to yield worse performance [PBB<sup>+</sup>11]. Therefore, isl introduces several leading components as follows:

- sum of all parameter coefficients in the distance bound;

- constant term of the distance bound;

- sum of all parameter coefficients in all per-statement schedule functions;

- sum of all variable coefficients in all per-statement schedule functions.

They allow isl to compute schedules independent of the *order of appearance* of coefficients in the lexmin formulation. Without the prefix, it would have also preferred the  $(\phi_2 - \phi_1) \le 0p_1 + 100p_2$  distance bound to  $(\phi_2 - \phi_1) \le p_1 + 0p_2$  bound because (0, 100) < (1, 0), while the second should be preferred assuming no prior knowledge on the parameter values.

**Negative Coefficients** The isl scheduler introduces support for negative coefficients by substituting dimension x with its negative and positive part  $x = x^+ - x^-$ , where  $x^+ \ge 0$  and  $x^- \ge 0$  in the non-negative lexmin optimization. This decomposition is only performed for schedule coefficients c, where negative coefficients correspond to loop *reversal*, and for parameter coefficients of the bound u, connected to c through Farkas' inequalities. Schedule parameter coefficients and constants d can be kept non-negative because a polyhedral schedule only expresses a relative order. These coefficients delay the start of certain computation with respect to another. Thus a negative value for one statement can be replaced by a positive value for all the other statements.

ILP Formulation The isl scheduler minimizes the objective

$$\operatorname{lexmin}\sum_{i=1}^{n_p} (u_i^- + u_i^+), w, \sum_{i=1}^{n_p} \sum_{j=1}^{n_s} d_{j,i}, \sum_{j=1}^{n_s} \sum_{i=1}^{\dim \mathscr{D}_{s_j}} (c_{j,i}^- + c_{j,i}^+), \dots$$

(2.3)

in the space constrained by applying Farkas' lemma to *validity* relations. Coefficients  $u_i$  and w are obtained from applying Farkas' lemma to *proximity* relations. Distances along *coincidence* relations are required to be zero. If the ILP problem does not admit a solution, zero-distance requirement is relaxed. If the problem remains unsolvable, *isl* performs band splitting as described below.

Individual coefficients are included in the trailing positions and also minimized. In particular, negative parts  $u_i^-$  immediately precede respective positive parts  $u_i^+$ . Lexicographical minimization will thus prefer a solution with  $u_i^- = 0$  when possible, resulting in non-negative coefficients  $u_i$ .

**Band Splitting** If the ILP problem does not admit a solution, isl applies a variant of Feautrier's scheduler [Fea92b] using *validity* and *coincidence* relations as constraints [VJ17]. If the problem involved constraints based on *coincidence* relations and outer parallelism is not requested in configuration, it first relaxes such constraints and tries to find a solution. Otherwise, it finishes the current schedule band, removes relations that correspond to fully carried dependences and starts a new band.

#### 2.2.3 Linear Independence

**Encoding** Just like Pluto, isl also computes a subspace that is orthogonal to the rows containing coefficients of the already computed affine schedule functions, but it does so in a slightly different way [VJ17]. Let  $\mathbf{r}_k$  form a basis of this orthogonal subspace. For a solution vector to be linearly independent from previous ones, it is sufficient to have a non-zero component along at least one of these  $\mathbf{r}_k$  vectors. This requirement is enforced iteratively as described below.

**Optimistic Search** isl tries to find a solution x directly and only enforces non-triviality if an actual trivial solution (zero) was found. More specifically, it defines *non-triviality regions* in the solution vector x that correspond to schedule coefficients. Each region corresponds to a statement and is associated with a set of vectors  $\{r_k\}$  described above. A solution is trivial in the region if  $\forall k, r_k \vec{x} = 0$ . In this case, the scheduler introduces constraints on the signs of  $r_k \vec{x}$ , invalidating the current (trivial) solution and requiring the ILP solver to continue looking for a solution. Backtracking is used to handle different cases, in the order  $r_1 \vec{x} > 0$ , then  $r_1 \vec{x} < 0$ , then  $r_1 \vec{x} = 0 \land r_2 \vec{x} > 0$ , etc. When a non-trivial solution is found, the isl scheduler further constrains the prefix of the next solution,  $\sum_i u_i, w$ , to be lexicographically smaller than the current one before continuing iteration. In particular, it enforces the next solution to have an additional leading zero.

This iterative approach allows isl to support negative coefficients in schedules while avoiding the trivial zero solution. Contrary to Pluto+ [BAC16], it does not limit the absolute values of coefficients, but instead requires the isl scheduler to interact more closely with the ILP solver.

#### Chapter 2. Background

This hinders the use of an off-the-shelf ILP solver, as is (optionally) done in R-Stream [VMBL12] and Pluto+ [BAC16]. Due to the order in which sign constraints are introduced, isl prefers schedules with positive coefficients in case of equal prefix. The order of the coefficients is also reversed, making isl prefer a solution with final zero-valued schedule coefficients. This behavior allows to prefer the original loop order in absence of a good transformation.

Although, in the worst case, this iterative approach considers an exponentially large number of sign constraints, it does not often happen in practice. As the validity constraints are commonly derived from an existing loop program, ensuring non-triviality for one region usually makes other validity-related regions non-trivial as well.

**Slack for Smaller-Dimensional Statements** When computing an *n*-dimensional schedule for an *m*-dimensional domain and m < n, only *m* linearly independent schedule dimensions are required. Given a schedule with *k* linearly independent dimensions, *isl* does not enforce linear independence until the last (m-k) dimensions. Early dimensions may still be linearly independent due to validity constraints. At the same time, *isl* is able to find bands with linearly-dependent dimensions if necessary, contrary to Pluto, which enforces linear independence early.

#### 2.2.4 Clustering

Initially, each strongly-connected component of the DDG is considered as a cluster. First, isl computes per-statement schedules inside each component. Then it selects a pair of clusters that have a *proximity* edge between them, preferring pairs where schedule dimensions can be completely aligned. The selection is extended to all the clusters that form a (transitive) validity dependence between these two. Then, the isl scheduler tries to compute a global schedule, between clusters, that respects inter-cluster validity dependences using the same ILP problem as inside clusters. If such a schedule exists, isl combines clusters after checking several profitability heuristics. Cluster combination is essentially loop fusion, where per-statement schedules are *composed* with schedules between clusters. Otherwise, it marks the edge as *no-cluster* and advances to the next candidate pair. The process continues until a single cluster is formed or until all edges are marked *no-cluster*. Clustering essentially corresponds to loop fusion, except that it allows for rescheduling of individual clusters with respect to each other. The final clusters are topologically sorted using the validity edges.

**Clustering Heuristics** Clustering provides control over parallelism preservation and locality improvement during fusion. When parallelism is the objective, isl checks that the schedule between clusters contains at least as many coincident dimensions on all individual clusters. Furthermore, it estimates whether the clustering is profitable by checking whether it makes the distance along at least one proximity edge constant and sufficiently small.

#### 2.2.5 Additional Transformations