## Performance Optimization Mechanisms for Fault-Resilient VLIW Processors

Rafail Psiakis

### ▶ To cite this version:

Rafail Psiakis. Performance Optimization Mechanisms for Fault-Resilient VLIW Processors. Embedded Systems. Université de Rennes 1, 2018. English. NNT: . tel-01956233

### HAL Id: tel-01956233 https://inria.hal.science/tel-01956233v1

Submitted on 15 Dec 2018  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE DE DOCTORAT DE

L'UNIVERSITE DE RENNES 1 Comue Universite Bretagne Loire

ECOLE DOCTORALE N° 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Informatique

### Par Rafail PSIAKIS

### Performance Optimization Mechanisms for Fault-Resilient VLIW Processors

Thèse présentée et soutenue à Rennes, le 21/12/2018 Unité de recherche : INRIA Rennes – Bretagne Atlantique et IRISA UMR 6074 Thèse N° :

#### Rapporteurs avant soutenance :

Alberto BosioProfesseur à l'Ecole Centrale de Lyon - INLArnaud VirazelMaître de Conférences HDR à l'Université de Montpellier - LIRMM

#### **Composition du Jury :**

| Examinateurs :  |                     |                                                                 |

|-----------------|---------------------|-----------------------------------------------------------------|

|                 | Alberto Bosio       | Professeur à l'Ecole Centrale de Lyon - INL                     |

|                 | Arnaud Virazel      | Maître de Conférences HDR à l'Université de Montpellier - LIRMM |

|                 | Sébastien Pillement | Professeur à l'Université de Nantes - IETR                      |

|                 | Georgios Keramidas  | Chercheur à l'Université de Patras, Grèce                       |

|                 | Angeliki Kritikakou | Maître de Conférences à l'Université de Rennes 1- IRISA         |

| Directeur de th | èse :               |                                                                 |

|                 | Olivier Sentieys    | Professeur à l'Université de Rennes 1 – IRISA/INRIA             |

**Titre :** Mécanismes d'optimisation des performances des processeurs VLIW à tolérance de fautes.

Mots clés: tolérance aux fautes, VLIW processeurs, exploitation des ressources inactives, optimisation de performance, injection de fautes, analyse de la vulnérabilité.

Résumé : domaines critiques exigent une combinaison de inactives hétérogènes au moment de l'exécution, à fiabilité, de performances et de faible consommation l'intérieur et à travers des ensembles d'instructions d'énergie. Very Large Instruction Word (VLIW) consécutifs. La technique se concentre sur les processeurs améliorent les performances grâce à erreurs légères. La troisième contribution traite des l'exploitation ILP (Instruction Level Parallelism), tout défauts persistants. Un mécanisme matériel est en maintenant les coûts et la puissance à un niveau proposé, qui réplique au moment de l'exécution les bas. L'ILP étant fortement dépendant de l'application, instructions et les planifie aux emplacements inactifs les processeurs n'utilisent pas toutes leurs en tenant compte des contraintes de ressources. Afin ressources en permanence et ces ressources de réduire davantage le surcoût lié aux performances peuvent donc être utilisées pour l'exécution et de prendre en charge l'atténuation des erreurs d'instructions redondantes. Cette thèse présente une uniques et multiples sur les transitoires de longue méthodologie d'injection fautes pour les processeurs durée (LDT), une quatrième contribution est VLIW et trois mécanismes matériels pour traiter les présentée. Nous proposons un mécanisme matériel pannes légères, permanentes et à long terme qui détecte les défauts toujours actifs pendant menant à quatre contributions. La première l'exécution et réorganise les instructions pour utiliser contribution présente un schéma d'analyse du facteur non seulement les unités fonctionnelles saines, mais de vulnérabilité architecturale et du facteur de également les composants sans défaillance des vulnérabilité d'instruction pour les processeurs VLIW. unités fonctionnelles concernées.

Les processeurs intégrés dans des La deuxième contribution explore les ressources

Title: Performance Optimization Mechanisms for Fault-Resilient VLIW Processors.

**Keywords:** fault tolerance, VLIW processors, idle resource exploitation, performance optimization, fault injection, vulnerability analysis

(VLIW) processors provide and Instruction Vulnerability Factor (IVF) analysis the affected function units. schema for VLIW processors.

Abstract: Embedded processors in critical domains The second contribution explores heterogeneous idle require a combination of reliability, performance and resources at run-time both inside and across low energy consumption. Very Long Instruction Word consecutive instruction bundles. The technique performance focuses on soft errors. The third contribution deals improvements through Instruction Level Parallelism with persistent faults. A hardware mechanism is (ILP) exploitation, while keeping cost and power in proposed which replicates at run-time the instructions low levels. Since the ILP is highly application and schedules them at the idle slots considering the dependent, the processors do not use all their resource constraints. In order to further decrease the resources constantly and, thus, these resources can performance overhead and to support single and be utilized for redundant instruction execution. This multiple Long-Duration Transient (LDT) error dissertation presents a fault injection methodology for mitigation a fourth contribution is presented. We VLIW processors and three hardware mechanisms to propose a hardware mechanism, which detects the deal with soft, permanent and long-term faults faults that are still active during execution and releading to four contributions. The first contribution schedules the instructions to use not only the healthy presents an Architectural Vulnerability Factor (AVF) function units, but also the fault-free components of

To my mother and father...

# Résumé étendu en français

La conception des systèmes embarqués modernes est très complexe car ces systèmes doivent simultanément satisfaire à un certain nombre de critères qui se contredisent généralement. Les applications embarquées doivent généralement s'exécuter et fournir leur résultat dans un délai déterminé, le temps total d'exécution est donc essentiel. Une défaillance dun système embarqué peut avoir des conséquences fatales, la fiabilité est donc devenue un facteur très important. D'autre part, l'industrie des circuits intégrés s'efforce de réduire les coûts unitaires. La minimisation de la surface et de la puissance revêt donc une grande importance.

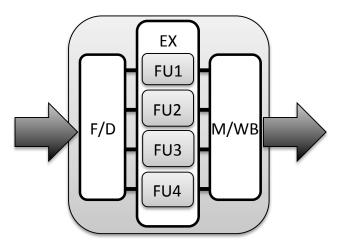

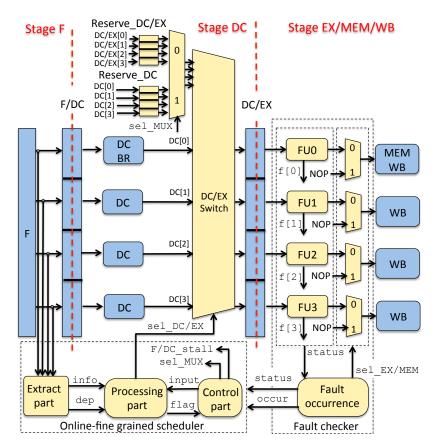

L'augmentation de la fréquence d'horloge est une pratique courante pour améliorer les performances du système et, par conséquent, le temps d'exécution de l'application. Cependant, en augmentant la fréquence d'horloge, la consommation d'énergie augmente également. Une solution à ce problème consiste à faire évoluer les architectures mono-cur classiques vers des architectures prenant en charge une sorte de parallélisme, telles que les processeurs VLIW (Very Long Instruction Word) utilisés dans cette thèse. La figure 1 présente un chemin de données VLIW simplifié pouvant exécuter jusqu'à quatre instructions simultanément, prenant ainsi en charge l'exécution en parallèle via IILP (Instruction Level Parallelism) du processeur. La phase dexécution a été amplifiée pour montrer le parallélisme inhérent à de tels systèmes.

Pour réduire la consommation électrique, une autre pratique courante consiste à réduire la tension et la fréquence de fonctionnement du système. Cependant, la réduction de la tension de fonctionnement, associée à la taille décroissante des transistors, rend les systèmes intégrés plus vulnérables aux erreurs et, par conséquent, moins fiables. Pour répondre à la demande croissante de fiabilité, les systèmes embarqués sont généralement conçus avec des capacités de détection et/ou de correction, atténuation et masquage des erreurs.

Cependant, augmenter la fiabilité implique généralement l'utilisation d'une forme de redondance, qu'elle soit spatiale ou temporelle, ayant un impact négatif sur la surface (et

Figure 1: Architecture VLIW à quatre voies. Détail de la phase d'exécution avec ses quatre unités fonctionnelles parallèles.

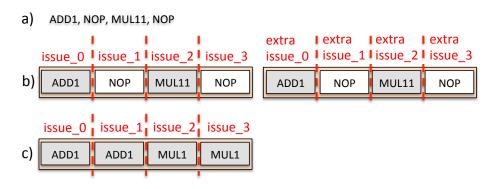

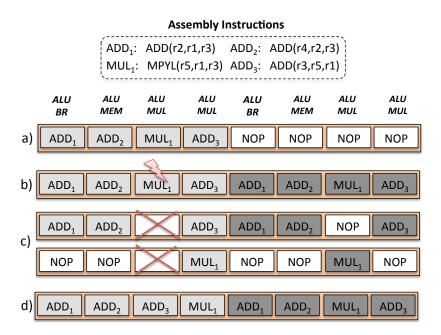

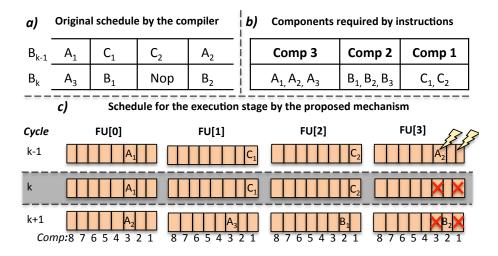

donc le coût du système) et le temps d'exécution. Des techniques ont été développées pour assurer la fiabilité du niveau du transistor jusqu'au niveau de l'application, en utilisant une redondance matérielle (HW) ou logicielle (SW). La figure 2 présente schématiquement les différences entre la redondance HW (Fig. 2.b) et SW (Fig. 2.c) dans un scénario utilisant un processeur VLIW et un ordonnancement des calculs résultant dune compilation donnée (Fig. 2.a). Les approches utilisant la redondance matérielle étendent le matériel du système non protégé à lorigine en ajoutant des ressources supplémentaires pour exécuter les instructions redondantes. D'autre part, les mécanismes de redondance logicielle réutilisent les ressources disponibles pour ordonnancer des instances redondantes des instructions sur le système d'origine.

Dans cette thèse, nous explorons des moyens efficaces pour fournir des systèmes intégrés fiables grâce à la redondance logicielle, tout en limitant les surcoûts en surface et temps d'exécution. Nous montrons que les méthodes de redondance logicielle permettent daméliorer la fiabilité à moindre coût lorsqu'elles sont combinées à des architectures à redondance inhérente, telles que les processeurs VLIW. Nous proposons trois mécanismes matériels qui explorent les ressources inactives des processeurs VLIW. Nous effectuons tout dabord une analyse sur plusieurs *benchmarks* pour obtenir leur ILP moyen. Cette analyse montre que  $1,51 \leq ILP \leq 2.85$  pour la configuration à quatre voies. Pour la configuration à 8 voies, nous observons que  $1.75 \leq ILP \leq 4.46$ . Cela implique que chaque cycle durant lexécution comporte un nombre suffisant de *slots* inactifs à exploiter. Une analyse temporelle de dépendance entre les instructions a également été effectuée pour chaque application afin de détecter les ressources inactives potentielles pouvant être exploitées pour la tolérance aux fautes. Les résultats montrent que les cas avec zéro dépendance entre deux ensembles *(bundles)* consécutifs du VLIW est supérieur à 50% et que le cas avec exactement une dépendance est également assez fréquent (40%). Cela implique que les créneaux inactifs peuvent également être exploités de façon temporelle entre séquences dinstructions.

Figure 2: Redondance SW/HW dans un scénario VLIW.

Cette thèse présente ensuite une méthodologie d'injection de fautes pour vérifier et analyser la vulnérabilité des processeurs VLIW non protégés ainsi que les trois mécanismes matériels exploitant les ressources inactives pour traiter les fautes transitoires, permanentes et à long terme, ce qui mène aux trois contributions principales de la thèse.

La première contribution présente un environnement danalyse de l*Architectural Vulnerability Factor* (AVF) et de l*Instruction Vulnerability Factor* (IVF) pour les processeurs VLIW. Ces métriques définissent le facteur de vulnérabilité architecturale et micro-architecturale d'un processeur, quelle que soit la fréquence des occurrences de fautes. Lobjet de létude AVF et IVF dans cette thèse est de mettre en évidence les capacités de masquage de fautes des processeurs VLIW de type RISC et de trouver les parties les plus critiques de la conception qui doivent être protégées contre ces fautes. Pour cela, une méthodologie dinjection de fautes au niveau de différentes structures de mémoire est proposée pour extraire les capacités de masquage aux niveaux architecture et instruction du processeur. Un schéma de classification des défaillances de haut niveau est présenté pour catégoriser la sortie du processeur.

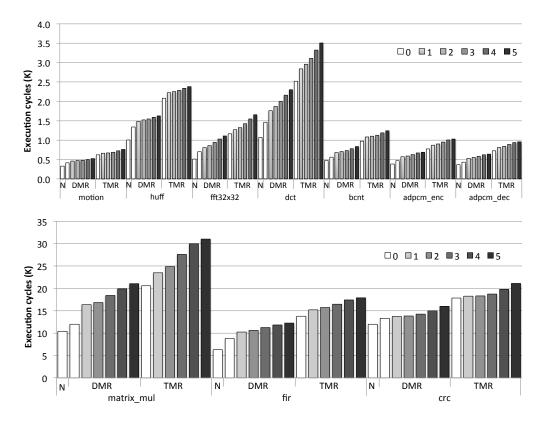

La deuxième contribution explore les ressources inactives hétérogènes au moment de l'exécution, à l'intérieur dun ensemble et entre plusieurs ensembles d'instructions consécutifs. Pour ce faire, une technique dordonnancement des instructions optimisée pour le matériel est appliquée en parallèle avec le pipeline afin de contrôler efficacement la réplication et lordonnancement des instructions. Suivant les tendances à la parallélisation croissante, une conception ciblant les architectures VLIW clustérisées est également proposée pour traiter les problèmes de passage à léchelle, tout en maintenant un surcoût en surface et puissance raisonnable. La technique proposée accélère la performance de 43,68% avec un surcoût en surface et en puissance de  $\sim 10\%$  par rapport aux approches existantes. Les analyses AVF et IVF évaluent la vulnérabilité du processeur avec le mécanisme proposé. Les résultats montrent quen raison du mécanisme proposé et de la technique de réplication appliquée, les instructions les plus vulnérables de larchitecture protégée, cest-à-dire les opérations arithmétiques et mémoire en entier, sont jusqu'à 2,2x moins vulnérables que celles de larchitecture non protégée.

La troisième contribution traite des défauts persistants. Un mécanisme matériel, qui réplique au moment de l'exécution les instructions et les planifie aux emplacements inactifs en tenant compte des contraintes de ressources, est proposé. Si une ressource devient défaillante, l'approche proposée permet de réaffecter efficacement les instructions d'origine et les instructions répliquées pendant l'exécution. Les premiers résultats dévaluation de performance montrent un gain de performance jusquà 49% par rapport aux techniques existantes.

Afin de réduire davantage le surcoût en performance et de prendre en charge latténuation des erreurs simples et multiples de type transitoires longues (Long-Duration Transients -LDT), une troisième contribution est présentée. Nous proposons un mécanisme matériel qui détecte les défauts toujours actifs pendant l'exécution et réorganise les instructions pour utiliser non seulement les unités fonctionnelles saines, mais également les composants sans défaillance des unités fonctionnelles concernées. Lorsque le défaut disparaît, les composants de l'unité fonctionnelle concernée peuvent être réutilisés. La fenêtre dordonnancement du mécanisme proposé comprend deux ensembles d'instructions pouvant explorer des solutions d'atténuation des fautes lors de l'exécution de l'ensemble dinstructions en cours et de l'ensemble d'instructions suivant. Les résultats obtenus sur l'injection de fautes montrent que l'approche proposée peut atténuer un grand nombre de fautes avec des surcoûts faibles en performance, surface et puissance.

# Contents

| 1        | Inti           | roduction and Motivations                   | 1  |

|----------|----------------|---------------------------------------------|----|

|          | 1.1            | VLIW Processors                             | 3  |

|          | 1.2            | VLIWs and Fault Tolerance                   | 5  |

|          | 1.3            | Motivations                                 | 7  |

|          | 1.4            | Dissertation Contributions                  | 8  |

|          | 1.5            | Thesis Organization                         | 10 |

| <b>2</b> | Bac            | kground and state of the art                | 11 |

|          | 2.1            | Fault Injection and Vulnerability Analysis  | 11 |

|          | 2.2            | VLIW Processors Under Soft Errors           | 14 |

|          | 2.3            | VLIW Processors Under Permanent Faults      | 16 |

|          | 2.4            | VLIW Processors Under Long-Term Faults      | 18 |

| 3        | Arc            | hitecture's Vulnerability Analysis          | 21 |

|          | 3.1            | Architectural Vulnerability Factor Analysis | 21 |

|          | 3.2            | Instruction Vulnerability Factor Analysis   | 27 |

|          | 3.3            | Conclusion                                  | 30 |

| 4        | $\mathbf{Tin}$ | ne and Space Instruction Rescheduling       | 33 |

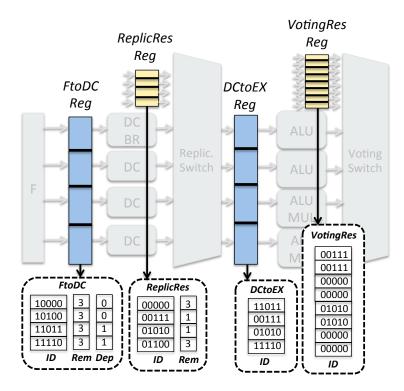

|          | 4.1            | Running example                             | 33 |

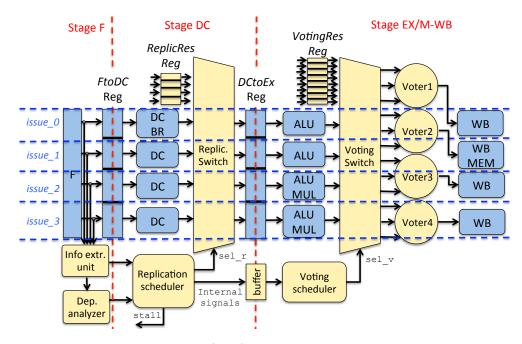

|          | 4.2            | Overview of the proposed architecture       | 36 |

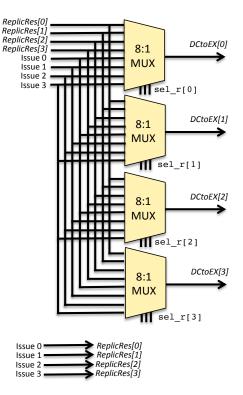

|          | 4.3            | Processing Components                       | 36 |

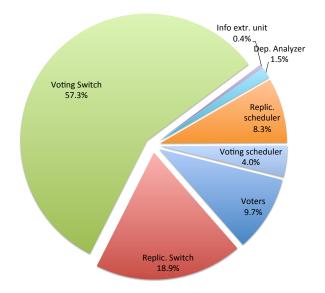

|          |                | 4.3.1 Replication Switch                    | 37 |

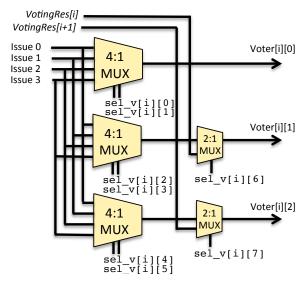

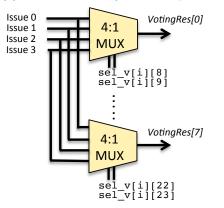

|          |                | 4.3.2 Voting Switch                         | 38 |

|          |                | 4.3.3 Voters                                | 39 |

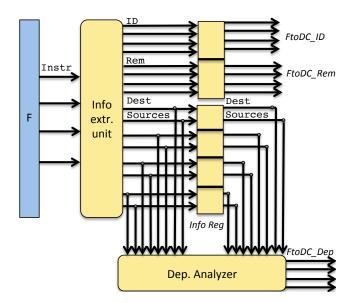

|          | 4.4            | Control Logic Components                    | 39 |

|   |      | 4.4.1                                 | Information Extraction Unit                                                                                                        |  |  |  |  |  |

|---|------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|   |      | 4.4.2                                 | Dependency Analyzer                                                                                                                |  |  |  |  |  |

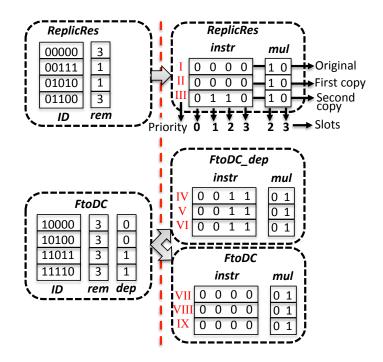

|   |      | 4.4.3                                 | Replication Scheduler                                                                                                              |  |  |  |  |  |

|   |      |                                       | $Pre-processing \dots \dots$ |  |  |  |  |  |

|   |      |                                       | Bitwise Logic                                                                                                                      |  |  |  |  |  |

|   |      | 4.4.4                                 | Voting Scheduler                                                                                                                   |  |  |  |  |  |

|   | 4.5  | Cluste                                | er-based approach                                                                                                                  |  |  |  |  |  |

|   | 4.6  | Exper                                 | imental Results                                                                                                                    |  |  |  |  |  |

|   |      | 4.6.1                                 | Performance                                                                                                                        |  |  |  |  |  |

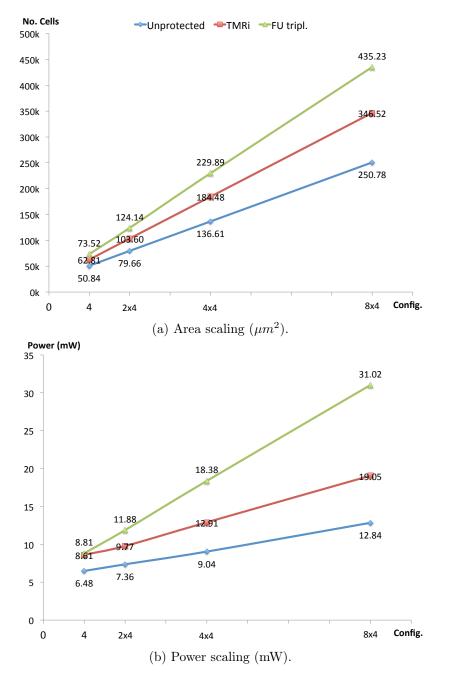

|   |      | 4.6.2                                 | Area and Power                                                                                                                     |  |  |  |  |  |

|   |      | 4.6.3                                 | AVF and IVF analysis                                                                                                               |  |  |  |  |  |

|   |      |                                       | AVF analysis:                                                                                                                      |  |  |  |  |  |

|   |      |                                       | IVF analysis: $\dots \dots \dots$  |  |  |  |  |  |

|   |      | 4.6.4                                 | Conclusion                                                                                                                         |  |  |  |  |  |

| 5 | Inst | ructio                                | n Rescheduling for persistent errors 65                                                                                            |  |  |  |  |  |

|   | 5.1  | Coarse                                | e Grained Mitigation for Permanent Errors                                                                                          |  |  |  |  |  |

|   |      | 5.1.1                                 | Motivation example and overview                                                                                                    |  |  |  |  |  |

|   |      | 5.1.2                                 | Performance Evaluation                                                                                                             |  |  |  |  |  |

|   | 5.2  | Fine-C                                | Grained Mitigation for Multiple Long-Duration Transients                                                                           |  |  |  |  |  |

|   |      | 5.2.1 Overview and Motivating Example |                                                                                                                                    |  |  |  |  |  |

|   |      | 5.2.2                                 | Fault Checker                                                                                                                      |  |  |  |  |  |

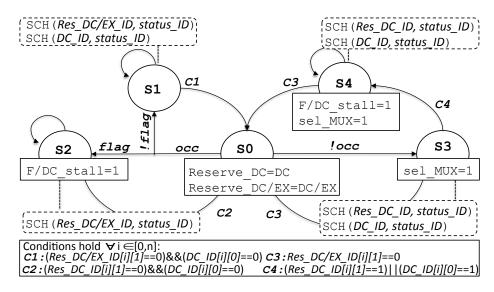

|   |      | 5.2.3                                 | Online fine-grained scheduler                                                                                                      |  |  |  |  |  |

|   |      |                                       | 5.2.3.1 Extract part                                                                                                               |  |  |  |  |  |

|   |      |                                       | 5.2.3.2 Processing part                                                                                                            |  |  |  |  |  |

|   |      |                                       | 5.2.3.3 Control part                                                                                                               |  |  |  |  |  |

|   |      | 5.2.4                                 | Evaluation results                                                                                                                 |  |  |  |  |  |

|   |      |                                       | 5.2.4.1 Performance                                                                                                                |  |  |  |  |  |

|   |      |                                       | 5.2.4.2 Area and power $\ldots \ldots $ 84                   |  |  |  |  |  |

|   | 5.3  | Conclu                                | usion                                                                                                                              |  |  |  |  |  |

| 6 | Sun  | nmary                                 | and Future Work 85                                                                                                                 |  |  |  |  |  |

|   | 6.1  | Thesis                                | Summary                                                                                                                            |  |  |  |  |  |

|   | 6.2  | Direct                                | ions for Future Work                                                                                                               |  |  |  |  |  |

| Acknowledgements      | 89  |

|-----------------------|-----|

| Publications          | 91  |

| References            | 93  |

| List of Figures       | 104 |

| List of Abbreviations | 105 |

| List of Tables        | 109 |

## Chapter 1

## Introduction and Motivations

The design of modern embedded systems is very challenging, since these systems have to simultaneously meet a number of criteria that usually contradict one another. Embedded applications usually have to react and provide their result within a fixed delay, so the total execution time is essential. A failure of an embedded system can have fatal consequences, so reliability has become a very important factor. On the other hand, the Integrated Circuit (IC) industry has been striving towards unit cost reduction, so area and power minimization is of great importance.

Increasing the clock frequency is a common practise to increase system performance, and, thus, the application execution time [86]. However, by increasing the clock frequency, the power consumption is increased as well. A solution to this issue was the evolution of the classic single-core architectures to architectures supporting a kind of parallelism. The shrinking of the transistor size enables hundreds of millions transistors to be placed on a single chip reducing manufacturing cost and increasing integration and computer processing abilities. Three levels of parallel execution exist: a) Thread Level Parallelism (TLP), where different tasks are executed in parallel on an architecture with several processing elements (e.g. Multicores, Simultaneous multithreading (SMT) processors), b) Data Level Parallelism (DLP), where parallelism arises from executing essentially the same code on a large number of data (e.g. Single Instruction Multiple Data (SIMD) processors, vector processors and Graphics Processing Units (GPUs)), and c) Instruction Level Parallelism (ILP), where parallelism is explored by executing in parallel independent instructions (e.g. Very Large Instruction Word (VLIW) processors and superscalars). Architectures exploring TLP (such as General Purpose Processors (GPP)) are used in multi-application domains where task parallelization is of critical importance and they introduce increased complexity and cost [8]. Architectures exploring DLP introduce large area and power overhead and they are useful only in case of applications with extensive data level parallelism (e.g. rendering applications [35], etc.). Architectures exploring ILP can offer parallelism with minimum complexity [68] being a very promising candidate for the domain of embedded systems striving for performance, without introducing high area overhead (e.g. Hexagon DSP [17], etc.).

To reduce power consumption, another common practise is to reduce the operating voltage and frequency of the embedded system. However, reducing the operating voltage in combination with the decreasing size of the transistors, makes the embedded systems more susceptible to reliability violations and, thus, less reliable [42], [76]. Reliability violations occur due to Process, Voltage, and Temperature (PVT) variations [74], circuit aging-wearout induced by failure mechanisms, such as Negative-Bias Temperature Instability (NBTI), Hot Carrier Injection (HCI) [49], radiation-induced Single-Event Effects (SEEs), such as Single-Event Upsets (SEUs) and Single Event Transients (SETs) [7], clock skews [58], thermal stress [79], electromagnetic interference, such as cross-talk and ground bounce [81], etc. These phenomena can cause errors that may affect the embedded system temporarily (soft errors), permanently (hard errors) or semi-permanently (intermittent errors) [13]. To satisfy the increasing demand for reliability, embedded systems are usually designed with error detection and/or error correction/mitigation capabilities.

However, to increase the reliability, it usually implies a form of redundancy, either spatial or temporal, impacting in a negative way on the area and/or the execution time. Several techniques have been developed to provide reliability from the transistor level up to the application level, using either Hardware (HW) or Software (SW) redundancy [56]. Approaches using HW redundancy extend the hardware of the original unprotected system by adding spare resources. Then, the same instructions are executed several times on the extra resources and their results are compared to provide error detection and/or correction [32]. As the instructions are executed in parallel, normally no execution time overhead is observed. However, the area overhead is significantly increased. On the other hand, SW redundancy mechanisms introduce redundancy through software modifications on the application running on the original unprotected system. They reuse the available resources to execute the fault tolerant instructions, and, thus, increasing the execution time [60].

In this dissertation, we explore efficient ways to provide reliability to the embedded systems, while keeping the area and execution time overhead low. We expect that SW redundancy methods are able to achieve reliability with less cost when they are combined with architectures that have inherent redundancy, such as VLIW processors.

Figure 1.1: VLIW architecture with 4 issues.

#### 1.1 VLIW Processors

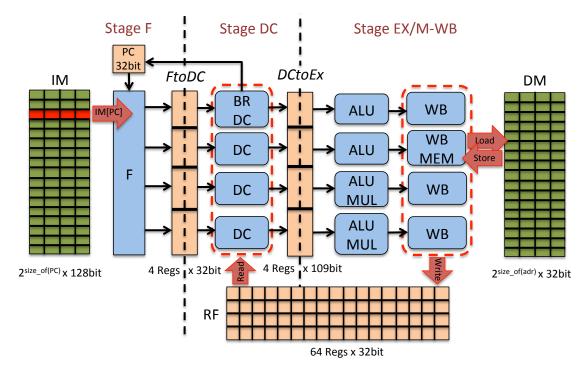

An example of a VLIW architecture (similar to VEX [20]) is presented in Fig. 1.1. The figure depicts a processor's data path with four issues. The data-path consists of a 3-stage pipeline with Fetch (F), Decode (DC) and Execute/Memory-WriteBack (EX/M-WB) and, thus, it does not require a bypass logic. The processor has one Instruction Memory (IM) port, that fetches an  $n \times 32$ -bit word each cycle according to the current value of the Program Counter (PC). Thus, it can issue up to n instructions per cycle, where n is the number of issues of the architecture. These instructions are executed on:

- Memory units (MEM) that perform load and store instructions. There are as many

memory units as data cache memory ports connected to the processor. More precisely,

there should be at least [n/4] data cache ports to interact with the Data Memory

(DM). In the presented example there is one MEM in the second issue.

- Integer and logic units that execute the common set of integer, compare, shift and

logical instructions on registers or immediate operands. More precisely, the VLIW FUs are either complex FUs, which are able to execute all types of operations and simpler FUs, which cannot execute sophisticated operations, such as multiplications and divisions. In this configuration, there are  $\lceil n/2 \rceil$  simple FUs, including only ALUs and  $\lceil n/2 \rceil$  complex FUs, including ALUs and multiplication units. These FUs commit their result in the registers of a Register File (RF) comprising of 64 general-purpose 32-bit registers.

• Single branch unit that executes control instructions based on conditional results stored in registers. The control instructions can be conditional branches, unconditional jumps, direct and indirect calls, and returns. In this configuration the BRanch (BR) unit is only available in the first issue.

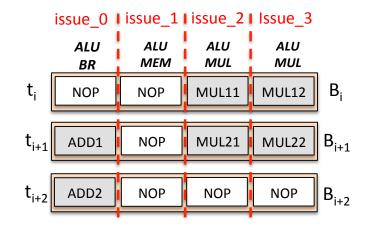

The Instruction-Set Architecture (ISA) considered in this dissertation follows the RISC ISA implementation and encoding (similar to the ISA of RISC-V processor [84]). The number of instructions executed in parallel per cycle depends on VLIW's FU parallelization capability (i.e. issue-width), the configuration of the VLIW (type of FUs used) and the intrinsic ILP available in each application. The instructions, which are issued and executed in parallel, form a bundle named *instruction bundle*. The VLIWs execute instructions in parallel, based on a fixed schedule determined when the programs are compiled.

For instance, suppose that the following matrix multiplication operation needs to be calculated:

$$\begin{pmatrix} A & B \\ C & D \end{pmatrix} \times \begin{pmatrix} E \\ G \end{pmatrix} = \begin{pmatrix} A \times E + B \times G \\ C \times E + D \times G \end{pmatrix}$$

(1.1)

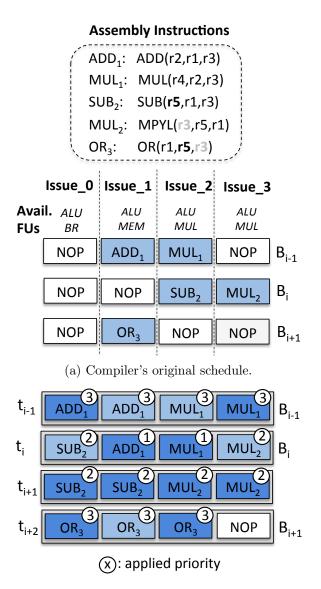

As shown, for the calculation of this equation we need to perform four independent multiplications and two independent additions afterwards. Compilers can determine this parallelization opportunity and exploit processor's resources to obtain better performance, while respecting dependencies (e.g. the addition must be executed after the calculation of the multiplications, thus it is dependent from them). Fig. 1.2 schematically presents three consecutive instruction bundles  $B_i$ ,  $B_{i+1}$  and  $B_{i+2}$  scheduled by the compiler targeting the architecture of Fig. 1.1 for the computation of the above equation. The compiler has scheduled two multiplication instructions at *issue 2* and *issue 3* for the bundle  $B_i$  in order to calculate the two multiplication instructions are scheduled also at *issue 2* and *issue 3* for the bundle  $B_{i+1}$  in order to calculate the two multiplications needed, i.e.  $C \times E$  and  $D \times G$ , for the second element of the output matrix. In addition, the compiler also schedules an addition instruction at *issue*  $\theta$  of  $B_{i+1}$  in order to calculate the AE + BG. At  $B_{i+2}$ , when the results of the two multiplications of  $B_{i+1}$  are ready, an addition instruction is scheduled to compute the last element (CE + DG) of the output matrix. In order to perform this calculation, a normal processor without ILP exploitation capabilities would require one cycle for each of these instructions, i.e. six cycles in total, while in our case the cycles needed are only three.

Figure 1.2: Three instruction bundles scheduled by the compiler for the computation of Eq. 1.1.

Since the order of execution of instruction and the decision of which operations can be executed simultaneously is handled by the compiler, any scheduling hardware (such as the instruction queue, reorder buffer, dependency-checking) that is needed when using out-oforder processors is avoided. Thus, VLIWs offer good computing power, high parallelization and performance gain with reduced hardware complexity and power consumption. For this reason VLIWs have been commercialized and used in several implementations during the past years (e.g., Intel Itanium [75], Trimedia CPU64 [83], Hexagon DSP [17], etc.).

#### **1.2 VLIWs and Fault Tolerance**

In the context of VLIW processors, the compiler is not always able to fill the entire bundle with instructions [1], because either there is no parallelism in the application or the processor configuration provides limited resources. Hence, idle slots are introduced in the form of No OPeration instructions (NOP). These idle slots can be used to execute redundant instructions. In this way, processor's reliability increases since SW redundancy is applied, while the execution time overhead, introduced by the instruction replication, decreases. The SW redundancy approach applied on VLIWs can be implemented either in software or in hardware.

Approaches following a software implementation insert redundant instructions during design-time (i.e. applying a kind of redundancy in the original code itself) and/or during compile-time (i.e. the compiler is programmed to apply a kind of redundancy during compilation). They can efficiently explore the idle slots to schedule the redundant instructions without additional hardware control. However, the code size, the storage requirements and the power consumption are increased, whereas they cannot deal with dynamically changing faulty environments. For instance, the compiler duplicates the operations and schedules them in different FUs of a VLIW processor [11] or it exploits the idle FUs for soft error mitigation by adding a new time slot, whenever the idle FU exploitation in the current time slot is not possible [29]. For the comparison of the results of the replicated instructions extra comparison instructions should be executed [10, 9]. To reduce the number of executed instructions, software-implemented approaches are combined with hardware implementations. The instruction duplication and scheduling is performed in the software by the compiler, but the comparison is performed by the hardware. In case of an error, a simple HW instruction rebinding takes place so as to re-execute the instruction at the next time slot [72].

Hardware mechanisms replicate the instructions at run-time. Existing approaches maintain the compiler's result and explore the use of idle FUs in space, i.e., only inside the current instruction bundle. For instance, in [63], the idle issue slots inside the current instruction bundle are used for the execution of the duplicated instructions. If no idle slots exist, the instructions are not duplicated, which reduces the reliability of the processor. In [64, 65] the technique is extended by adding an extra time slot, so as to duplicate the instruction bundles that have more that half of its issue-width filled with instructions. However, the execution overhead is increased.

In this dissertation, we explore hardware mechanisms for SW redundancy, as they can efficiently deal with dynamically changing faulty environments compared to software implementations. We expect that by exploring the idle FUs of VLIWs, not only in space, but also in time through rescheduling of independent instructions of subsequent bundles, the reliability will be increased, while the execution time overhead will decrease.

#### **1.3** Motivations

To motivate the benefits of the design of such mechanisms, we need to reply to two main questions:

- 1. How many of these resources are actually available to be used for fault tolerance each cycle?

- 2. How many of each application's instructions can be potentially rescheduled to enable further idle FU exploitation?

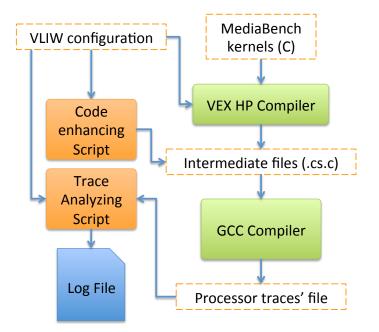

In order to answer to these fundamental questions, we analyzed ten basic media benchmarks from the MediaBench suite [36] with respect to their intrinsic parallelization capability. Similar media applications have been used by others in the literature to evaluate fault tolerant approaches [65], [10], [43]. In order to perform our analysis we utilized the VEX C compiler<sup>1</sup> provided by HP to compile our benchmarks. Initially, we perform an analysis of the binaries obtained by the VEX compiler in order to export the benchmarks' characteristics. Table 1.1 illustrates the average number of instructions per bundle, ILP, for the 4-issue and 8-issue VLIW configurations. We observe that  $1.51 \leq \text{ILP} \leq 2.85$  for the 4-issue configuration. For the 8-issue configuration, we observe that  $1.75 \leq \text{ILP} \leq 4.46$ . This implies that in several bundles, there is a sufficient number of idle slots to be exploited. By duplicating the issue width, it does not imply a duplication of the ILP, because of the limited parallelization capability of the applications. Therefore, more idle slots exist in the 8-issue configuration. ILP metric provides us relevant information for the idle FUs exploitation in space, meaning that only the idle FUs within one bundle are explored.

When idle FUs exploitation occurs also in time, meaning that the FUs exploitation is performed among several bundles, we require to explore another metric, i.e. the percentage of the dependency occurrences per application. In this way, we implicitly know how many instructions are independent and, thus, they can be postponed in time so as to explore idle FUs in upcoming bundles. We analyzed the benchmarks to identify the number of

<sup>&</sup>lt;sup>1</sup>The VEX compiler is derived from the Lx/ST200 C compiler, which is a descendant of the Multiflow C compiler. VEX compiler allows complex program compilation, custom instruction experimentation, and scalability. It targets C language and concentrates on acyclic scheduling (no software pipelining is supported). It supports partial predication and its only region shape is a trace (no superblocks nor treegions). It uses trace scheduling as its global scheduling engine. A programmable machine model determines the configuration of the target architecture. Some of the tuneable parameters that allow architecture exploration without having to recompile the compiler are for instance the number of clusters, the number of execution units, the issue width, and the latency of specific instructions.

the dependent instructions between two bundles. In Table 1.1 we present the dependency occurrence (%) for each application for zero, one, two and three or more simultaneous dependencies between consecutive bundles. As we observe, for most of the applications, the

|             | 4-issue |                  |          |      | 8-issue |                  |          |      |      |      |

|-------------|---------|------------------|----------|------|---------|------------------|----------|------|------|------|

| Benchmark   | ILP     | Dep. Occurrence% |          |      | ILP     | Dep. Occurrence% |          |      |      |      |

|             |         | 0                | 1        | 2    | 3+      | ILI              | 0        | 1    | 2    | 3+   |

| adpcm_dec   | 1,77    | 60,6             | 35,2     | 4,1  | 0       | 2,28             | $50,\!3$ | 37,7 | 9,6  | 2,3  |

| adpcm_enc   | 1,82    | 58,7             | 35,9     | 4,9  | $0,\!5$ | 2,41             | 48,6     | 39   | 9    | 3,3  |

| bent        | 2,49    | 36               | 54       | 10   | 0       | 3,62             | 27       | 43,5 | 5,1  | 24,3 |

| dct         | 2,22    | $53,\!9$         | 30,1     | 7,7  | 8,3     | 3,31             | 45,4     | 28,1 | 7,1  | 19,4 |

| fft32x32s   | 2,85    | 62,6             | 17,2     | 20,2 | 0       | 4,19             | 60,8     | 6,8  | 6,5  | 26   |

| huff_ac_dec | 1,51    | 59,9             | 36,1     | 3,6  | 0,5     | 1,75             | 40,7     | 50,7 | 7,9  | 0,7  |

| motion      | 1,94    | 57               | 29,1     | 11,6 | 2,3     | 2,39             | 47,1     | 30   | 18,6 | 4,3  |

| fir         | 2,09    | 62,3             | 29,8     | 7,9  | 0       | 2,5              | 51,6     | 36,8 | 11,6 | 0    |

| crc         | 1,76    | 29,8             | $65,\!6$ | 4,5  | 0,1     | 1,8              | 28,2     | 64,8 | 6,9  | 0,1  |

| matrix_mul  | 2,61    | $51,\!5$         | 32,2     | 16,4 | 0       | 4,46             | 21,1     | 62,7 | 16,2 | 0    |

Table 1.1: VEX Compiled Applications' Profiling

case of having zero dependencies between two consecutive bundles is more than 50%. The case with exactly one dependency is also quite frequent ( $\sim 40\%$ ), whereas the case of multiple dependencies is rather rare ( $\sim 15\%$ ). Considering the limited ILP of the applications and the limited number of dependent instructions between consecutive bundles, we assume that the idle FU exploitation in time would be beneficial in terms of execution time overhead improvement.

The need for increased reliability in combination with the above-mentioned findings regarding applications' characteristics motivate the development of efficient hardware mechanisms that exploit idle resources both in space (limited ILP of the applications) and time (independent instructions that can be postponed later). The next subsection presents an overview of the contributions of this work which are all driven by the observation of several idle resources in modern VLIW processors.

#### **1.4** Dissertation Contributions

The main contributions of this dissertation with respect to the research topic of reliable VLIW processors are the following.

- Vulnerability analysis through fault injection: A fault injection software methodology is developed to test the vulnerability of the presented VLIW architecture. Both Architectural Vulnerability Factor (AVF) and Instruction Vulnerability Factor (IVF) analyses are performed to motivate the need for increased reliability against faults occurring in VLIW data paths. A high-level failure classification scheme is presented to categorize the output of the processor.

- Time and space instruction rescheduling: We propose a hardware mechanism capable of i) replicating at run-time the original instructions to provide VLIW processors with fault tolerance and ii) dynamically scheduling these original and replicated instructions to efficiently explore the idle FUs of current and upcoming bundles to improve execution time overhead. To achieve that, a hardware-optimized scheduling technique is proposed based on bit-wise logic. A cluster-based architecture is proposed, to support larger VLIW configurations and scalability. The detailed hardware implementation of the proposed mechanisms in the VLIW data path is presented and evaluated through extensive results on performance, area and power consumption. The AVF and IVF analysis is performed to evaluate the vulnerability factor of the VLIW architecture enhanced with the proposed mechanisms. Early results of this work have been published in [Psi17a], whereas an extended version has been submitted for publication in [Psi19b].

- Instruction rescheduling for persistent errors: When errors become persistent, the number of available FUs is reduced, thus affecting the execution time of the applications. A coarse-grained mitigation mechanism is proposed, that replicates and binds the instructions at run-time in order to provide error detection and mitigation. When a permanent error is detected, the instruction execution is modified to avoid the faulty FU. Both instruction replication and binding explore the healthy FUs taking the limitations on the type and the number of resources into account. A set of evaluation performance experiments with respect to the execution time overhead are performed and show up to 49% performance gain over existing techniques. This work has been published in [Psi17b].

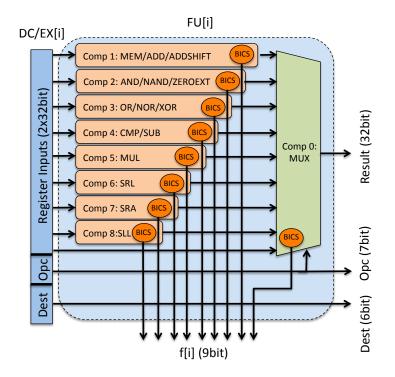

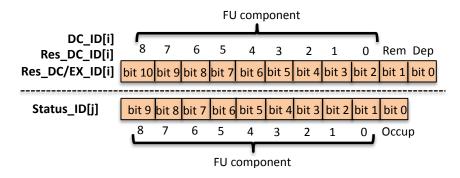

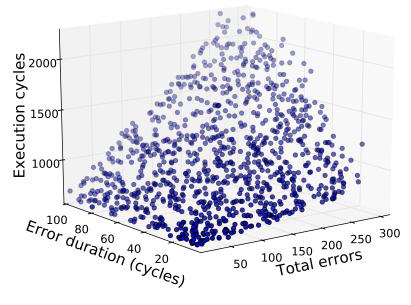

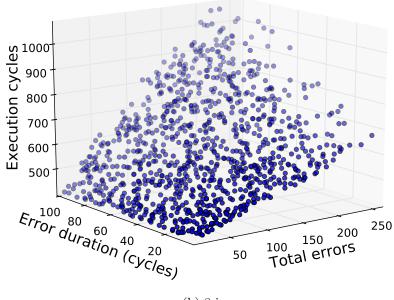

In order to further decrease the performance overhead, while supporting dynamic faulty environments including single and multiple Long-Duration Transient (LDT) faults, we propose a fine-grained mitigation mechanism that detects the active faults during execution and excludes only the faulty components of the affected FUs and for as long as it is necessary. To achieve that, a fine-grained micro-architectural solution is proposed that partitions an FU in components, where each component is an individual circuit that executes a group of instructions. Each FU component is enhanced with a Built-In Current Sensor (BICS) mechanism, so as to identify the exact location of the fault and the duration that the fault is active. An online fine-grained instruction re-scheduling mechanism is proposed that explores idle healthy FU components in the current and the next instruction execution. Finally, we perform exhaustive fault injection simulations (214K) varying the number of total faults, the number of concurrently occurring faults and the fault duration. The obtained results show a minor performance degradation ( $\sim 9\%$  for four concurrent faults) even for several occurring multiple long duration faults. This work has been accepted for publication in [Psi19a].

#### 1.5 Thesis Organization

The dissertation is organized into six chapters including this one. Chapter 2 discusses the state of the art research works w.r.t. fault resilient VLIW processors. Chapter 3 presents the details of the VLIW architecture used in this dissertation, w.r.t. the architectural and instruction vulnerability factor. In Chapter 4, we present the second contribution of this dissertation, i.e. the time and space instruction rescheduling, whereas in Chapter 5 we present our third contribution, i.e. the fine-grained instruction rescheduling. Finally, the thesis concludes with an overview of the presented work and a discussion on future research directions in Chapter 6.

## Chapter 2

# Background and state of the art

In the following sections we present the state of the art concerning fault injection and fault mitigation methods on modern embedded architectures and more specifically VLIW processors. We present the work related to the aforementioned research area split in four sections. In the first section, we discuss the latest published works on fault injection and vulnerability analysis on modern embedded processors. In the following sections, we discuss about the state of the art techniques concerning transient, permanent, and long duration fault detection and mitigation.

### 2.1 Fault Injection and Vulnerability Analysis

According to [87], the fault injection techniques can be classified as: 1) Hardware-based, 2) Software-based, 3) Emulation-based, 4) Simulation-based, and 5) Hybrid methods.

Hardware-based fault injection techniques test processors in realistic experimental conditions (e.g., radiation chambers, thermal stress experiments). In [23] an approach for SET detection and measurement is proposed. Real fault injection experiments are performed targeting a custom test chip, which is irradiated with heavy ions and pulsed lasers, while it is triggered by random inputs. FIST5 [25], developed at the Chalmers University of Technology in Sweden, uses heavy ion radiation to create transient faults at random locations inside a chip when the chip is exposed to the radiation and can thus cause single- or multiplebit-flips. Messaline [2], developed at LAAS-CNRS, in Toulouse, France, uses both active probes and sockets to conduct pin-level fault injection. Messaline can inject stuck-at, open, bridging, and complex logical faults. Although such approaches are very accurate, a drawback is that they require the physical implementation of the device under test and that the tested chip is heavily stressed, being defected after the experiment.

Software-based fault injection techniques are applied at the application level and mainly focus on applications' masking capabilities. Due to application-level fault masking (operationlevel fault masking, fault masking due to fault propagation, and algorithm-level fault masking), the manifested errors may have zero impact on the application outputs. In [26], an application-level fault modelling is proposed. The proposed method models the behaviour of the faults which have already been manifested in the application-level. In [67], softwareimplemented fault injection is studied and a pitfalls interpretation is presented. The fault probability is approximated using the Poisson distribution, which is used to inject single errors in the memory. Ways to reduce the experiment effort are also studied using fault sampling and defuse, and pruning analysis. A high-level fault injector for Intel Xeon Phi, built upon GDB (the GNU debugger), is presented in [50]. Results show that 75% of the injected faults do not generate an observable error. Software-based techniques cannot inject faults into locations that are inaccessible to software and, thus, they have limited accuracy. On the other hand, since they are applied at high level, they require minimum simulation time and they can be easily implemented.

Emulation-based fault injection has been presented as an alternative solution for reducing the time spent during simulation-based fault injection campaigns. It is based on using Field Programmable Gate Arrays (FPGAs) for speeding-up fault simulation. This technique allows the designers to study the actual behavior of the circuit in an application environment, taking real-time interactions (e.g. I/Os) into account. However, when an emulator is used, the initial architecture or algorithmic description must be synthesizable to an FPGA design.

In simulation-based fault injection, there is a simulator that simulates the hardware as well as the injected faults. For instance, in [57], the authors propose analytical equations to model the propagation of a voltage pulse to flip flops. Random errors are injected at all possible nodes of a circuit gate-level netlist in order to calculate the Soft Error Rate (SER). Verification afterwards is performed using HSPICE. A tool for automated integration of fault injection modules is presented in [78]. The gate-level netlist is enhanced with injection modules after each gate and flip-flop. These modules are parametrized by the user for various fault specifications. In [80] a gate-level fault injection methodology for logical and electrical masking effects in case of reconvergent fanouts is presented. Delayed fault glitches are generated in case of reconvergent fanouts. In [21] the authors propose a simulator implemented fault injection tool, where faults are induced by altering the logical values of the model elements during the simulation. They enhance MGSim [53] with a fault injection capability, thus the fault injection is performed at component-level. In [44] the relationship between glitches in the gates and latched errors in the flip flops is studied using mathematical models. The results of the proposed method are compared with HSPICE's results. The work in [61] introduces faulty behavior signatures that are computed after several gate-level injections. These signatures give the error occurrence probability of each output vector and are used by a saboteur that injects faults on a high level representation model of the tested design. This technique benefits from the high accuracy of the low-level injection and the simulation speed of a high-level injection. In [18], the authors measure the SER of a processor starting from a technology response model up to application masking. Only the injected errors from lower levels, which were latched by a memory element, are considered in the higher level and, thus, simulation time is reduced due to masking. In [52], a Monte-Carlo-based fault injection technique is proposed, taking into account multiple faults. In order to obtain accurate results, the injected nodes are selected according to their proximity to the error source in the place and route diagram.

AVF (Architecture Vulnerability Factor) was proposed by [47]. It concerns the probability of a soft error to result in an error of the program visible output. AVF estimation of modern microprocessors, using Statistical Fault Injection (SFI) for MBUs, is proposed in [41]. The presented method partitions the design into various hierarchical levels and systematically performs incremental fault injections to generate vulnerability estimates. Fault injection times are accelerated by 15x on average. A simulator-level fault injection framework is proposed in [82] that targets the Multi2Sim simulator. It measures the AVF of each application for a specific architecture, when single or multiple bit-flips into memory structures occur. In [4], the authors propose a new reliability metric named as Instruction Vulnerability Factor (IVF). Each instruction is tested with different operands in all the stages of a processor's pipeline under soft errors to measure the IVF. Results show that the execution stage is the most vulnerable part of the tested processor according to the average IVF of each stage. The study concludes with a technique for a fast and accurate AVF estimation using the IVFs of running instructions. Fault injection experiments at the Register Transfer Level (RTL) and Instruction Set Simulator (ISS) level are performed in [19]. The results are compared in order to find a correlation between the two approaches. Each application's instruction diversity is measured (i.e., the number of different opcodes) in order to detect which areas in the RTL are actually affected. The authors in [46] propose a multi-level simulation that switches between ISS-level and RTL at run-time. The fault injection is performed when the simulation has passed to the RT level, evaluating the impact of soft errors in the pipeline of a RISC processor. The multi-level simulation benefits from the accuracy of the RTL-level simulation and the fast simulation time of the ISS-level simulation. Finally, simulation-based techniques provide accurate enough results, because the simulation models have most of the low-level hardware information while the run-time injection concept provides an accurate enough simulation of real scenarios. Additionally, when using simulation-based fault injection techniques, there is no risk to damage the system in use. A drawback of such approaches is the significant overhead in simulation and development time.

Few hybrid techniques also exist. A method combining software-based and simulationbased fault injection is presented in [27]. It uses pin-level forcing or generates interrupts to activate software fault injection. Hybrid methods benefit from the the advantages of both categories.

In this dissertation, we developed a simulation-based fault injection methodology and we used the AVF and IVF metrics to evaluate the VLIW architecture and the proposed hardware mechanism. To the best of our knowledge, this is the first AVF, IVF study on VLIW processors with heterogeneous issues. Valuable insights are obtained from this analysis, concerning the masking capabilities and the vulnerability characteristics of VLIW processors.

#### 2.2 VLIW Processors Under Soft Errors

Software-based and hardware-based techniques have been proposed to take advantage of the additional resources in statically scheduled processors with inherent resource redundancy and to provide error detection and/or error correction. Software-based approaches replicate and schedule the instructions at design-time and additional instructions are inserted for comparison of the results. Software error detection approaches apply the duplication of the instructions after the compilation of the code and, thus, they can control where the original and replicated instructions are executed, e.g., in different function units. For instance, the approaches presented in [10, 9] apply full duplication and full comparison at the compiled code, whereas the approach of [28] reduces the number of compared instructions. CASTED [45] proposes a compiler-based technique to distribute error detection overhead across core/- clusters applicable to tightly-coupled cores and clustered VLIWs. To reduce the number of additional instructions, software-based approaches are combined with hardware-based ones. The instructions duplication and scheduling is performed by the compiler whereas the comparison is performed by the hardware [30, 29]. In [37], a hardware/software-based technique is proposed, where the compiler encodes information in the instructions and a hardware mechanism decodes the information to run-time duplicate the instructions.

However, the aforementioned approaches do not provide any correction means. In software-based techniques no additional hardware control is required, but code size, storage and power consumption are increased. The code size increase has also a negative impact on system reliability, as more bits are present in the system, leading to a higher soft error rate [59]. Additionally, software-based techniques cannot deal with dynamic fault situations, meaning that they are not able to change the schedule according the current affected unit. To avoid these limitations, hardware approaches replicate the instructions at run-time using specific hardware mechanisms.

Hardware-based approaches eliminate the need of high storage requirements and additional instructions and are either applied to homogeneous or heterogeneous VLIWs. In [66], a dynamically adaptive homogeneous processor design is proposed, which is capable of reconfiguring the processor in order to achieve the best trade-off among fault tolerance, performance, and energy consumption. The applied fault tolerance technique exploits the spatial and temporal identical idle resources of a VLIW. In [15, 16], the authors propose a common approach for short transient and permanent faults. The instructions are partitioned in groups in order to be able to be directly compared, inserting one or two idle cycles for each instruction bundle. Due to the increased performance overhead, the use of spare function units is explored. Results are provided for one spare unit and homogeneous issues with ALU FUs.

Combination of a software and a hardware approach is presented in [73]. The instruction duplication and scheduling is performed by the compiler and the comparison of the instructions is performed by the hardware. In case of an error, re-execution takes place through a simple HW operation rebinding that adds an additional slot and re-binds the operation to another FU. However, the VLIW also consists of homogeneous issue slots with FUs that can execute any type of operations.

Although hardware-based approaches that exploit the idle resources inside homogeneous

VLIWs introduce a less complex control logic, they cannot be applied for heterogeneous VLIW data paths. In addition, their scalability is argued because an N-issue implementation would require N identical FUs, with N multipliers, N memory units, etc. On top of that, homogeneity in FUs does not usually reflect to realistic VLIW processor configurations with limited resources (e.g., [75]). Especially for architectures that employ floating point units, the area and power overhead can be very high. Existing approaches for heterogeneous VLIWs do not explore dependencies and idle slots among instructions bundles, adding unnecessary performance overhead.

In [63, 64, 65], one-to-one coupling of heterogeneous VLIW pipelines is applied and, thus, the duplicated instructions can use the schedule of the original instructions given by the compiler. In [63], error detection is applied through instruction duplication. If no idle slots exist, the instructions are not duplicated. When an error is detected, instruction reexecution is applied. In [64, 65], the technique is extended with ILP reduction. When a VLIW bundle has more than half of its issue-width filled with instructions, the bundle is divided into two and an additional time slot is added.

Compared with existing approaches, in this dissertation we propose a hardwarebased approach for heterogeneous VLIW data paths, which explores at run-time the idle slots in space and time, i.e. both inside and among instruction bundles, to decrease performance overhead. Restrictions due to both the number and the type of resources and the dependencies are taken into account. The technique proposed in this thesis is applied to a VLIW with a combination of simple and complex FUs, but it can be easily extended to VLIWs supporting floating point arithmetic operations. Supporting floating point operations would require FUs with significant area/power overhead, where their replication to achieve fault tolerance is forbidden when resources are limited. Thus, the proposed technique would have a more significant impact since it provides fault tolerance without adding extra FUs.

#### 2.3 VLIW Processors Under Permanent Faults

The approaches designed for permanent errors have to modify the execution of the program to avoid the use of faulty units. As these methods focus on permanent faults, the detection of the faulty unit is usually assumed to be done upfront. These approaches can be implemented either off-line in software or on-line in hardware. Several software approaches exist. For instance, the compiler duplicates the operations and schedules them in different FUs of VLIW processors [11] or exploits the idle slots for soft errors [29]. The authors in [45] propose a compiler based technique to distribute error detection overhead to the available resources of architectures with abundant ILP, like VLIWs. The software approach of [31] stores several versions of the scheduling, where each scheduling is an alternative implementation for a given error. The permanent faults are detected offline and the program memory is modified adequately, in case of an off-line detected permanent fault. The work in [85] focuses on permanent faults in the registers of the VLIW and proposes a recompilation technique with a register pressure control to re-assign variables to fault-free registers. Concerning the software approaches, usually no additional hardware control is required, but code size, storage and power consumption are increased.

Several hardware approaches also exist. Few of them are capable of online identifying and handling the permanent errors. The following techniques add spare hardware resources for the error handling, thus the area and control overhead are increased. In [15], a spare function unit is added for error detection in VLIW, whereas single errors of one type are considered. In [16], spare function units are inserted to support Triple Modular Redundancy (TMR) and when not enough resources exist and the recovery is performed by re-execution of the faulty instruction. In [14, 51], a coarse-grained reconfiguration is proposed for a single permanent fault for each hardware class of ASICs based on the partitioning of the time and instruction bundle space. The technique has been extended for multiple faults by assuming one fault at each band and each reconfiguration of the scheduling can isolate one faulty unit. The fault detection is assumed to have been done in advance. In [77], the fault is detected by adding smaller ALUs and a reconfiguration logic is inserted in the execution stage to avoid the use of the faulty unit. Concerning the hardware approaches, usually no software modifications are required, but area and power consumption are increased due to extra hardware.

Some approaches combine software and hardware implementations. In [71], a software repair routine modifies the instructions permanently in the memory. During start-up, a self-test takes place to identify the faulty slots. This information is used to change the schedule stored in the memory. If the repair routine fails, a simple hardware binding mechanisms adds time slots and sequentially maps the instructions that cannot be assigned to other slots. In [69], the approach is extended to cover pipeline registers, the register ports and the bypass logic. In [70], the approach is combined with adaptive software-based self-test,

assuming though that the permanent errors have been already detected.

When permanent errors occur, either spare units have to be used or the executed program has to be modified through self-repair routine or through the use of several stored versions. However, these solutions introduce high area overhead for the additional resources, time overhead for the execution of the repair algorithm and storage overhead of the multi-versioning. **To address these limitations, a hardware mechanism is proposed (Chapter 5, Section 1) which at run-time replicates the instructions and schedules them at the idle FUs considering the resource constraints. If a resource becomes faulty, the proposed approach efficiently rebinds both the original and replicated instructions during execution.**

### 2.4 VLIW Processors Under Long-Term Faults

To the best of our knowledge, there is no technique targeting VLIW processors that deals with Long-Duration Transient (LDT) faults. Few approaches exist that focus on LDTs in general and they mostly focus on the error detection part at the transistor level using Built-In Current Sensors (BICS). In [5], a comparison of different BISCs can be found. Existing approaches usually stall the computation as long as the LDTs are valid or apply re-execution of the faulty instruction to single instruction processors. In [39], a BICS is proposed as a SET sensor connected directly to the bulk of transistors. In [6], a new lower area BICS scheme is propose using a single circuit to monitor at the same time both CMOS networks. When the SET is vanished, the computation restarts. In [38], a recomputing instruction mechanism is combined with BICS for transient errors on a micro-controller. In [33, 34], DMR is applied to detect any corruption of the application logic in a pipeline processor and a new micro-rollback scheme is applied to correct long duration transients, single event upsets and timing violation. Other approaches insert spare resources increasing the area overhead. For instance, a fault tolerant technique with a double-mirror BISC is proposed in [24], allowing the detection of abnormal current consumption. If a defect occurs, redundant circuits are used.

Concerning VLIW processors, as most of the existing approaches are designed for transient and/or permanent errors, they are either not applicable or too pessimistic for LDTs. As mentioned in the previous sections, several software-based and hardware-based techniques have been proposed to take advantage of the abundant resources inside the VLIW data paths in order to provide error detection and/or error correction.

Software-based approaches for transient errors apply duplication of the instructions at the compilation time and. Thus, they can control where the original and replicated instructions are executed, i.e., in different function units, to support the detection of both transient and permanent faults [10, 9, 28, 30, 29, 73]. Although these techniques could be applied for LDTs, the performance overhead introduced by the continuous re-execution of the faulty instructions because of the long duration faults is rather significant. Hardware-based approaches for transient errors replicate the instructions at run-time using specific hardware [64, 65, 54]. Since no restrictions are applied to the on-line schedule, these techniques cannot detect persistent errors and, thus, they are not applicable to LDTs.

The approaches designed for permanent errors have to modify the execution of the program to avoid the use of faulty units. Approaches based on the modification of the execution of the program can be implemented either off-line in software or on-line in hardware. Software approaches such as [31, 71, 69, 70] assume that the detection of the faulty unit is done upfront, which is not possible in the case of LDTs. Few hardware approaches are capable of online identifying the permanent errors [55, 77, 15, 16], and, thus, could be applied for LDTs. However, the exclusion of the faulty unit is permanent leading to pessimistic results for LDTs.

To eliminate the performance overhead due to the re-execution or due to the pessimistic FU exclusion for LDTs on VLIW processors, we propose a finegrained mitigation hardware mechanism combined with BISC FUs (Chapter 5, Section 2). During execution, this mechanism characterizes the components of each FU, identifies LDTs, reschedules the faulty instructions to the healthy FU components, and temporarily excludes the faulty ones. When LDTs vanish, the faulty FU components can be reused once again.

## Chapter 3

# Architecture's Vulnerability Analysis

Today's increased demand for reliable systems rises questions such as:

- 1. Given a processor's architecture with a given fault masking capability, what is the frequency of the errors a system experiences from its environment?

- 2. Is it necessary to incorporate a mitigation technique inside a given design, or the probability of a fault propagated to the user level is rather negligible (fault masking)?

- 3. Which part(s) of an architecture should be protected the most?

- 4. Which is the most suitable mitigation technique to be adopted?

Although the first question is not always easy to be answered since it depends on external to the system factors (e.g., radiation, PVT), the research community found a way to respond to the second and third questions by introducing two new metrics. These metrics define the architectural and micro-architectural vulnerability factor of a processor, regardless of the frequency of the fault occurrences. In the following sections, we explore the Architectural Vulnerability Factor (AVF) and the micro-architectural / Instruction Vulnerability Factor (IVF) of the VLIW architecture used in this dissertation, in order to point out its fault masking capabilities and find the most critical parts of the design that should be protected against faults.

#### 3.1 Architectural Vulnerability Factor Analysis

A structure's architectural vulnerability factor (AVF) is the probability that a fault in a processor will result in a visible error in the final output of a program [4, 47]. For instance,

an error in the offset part of a NOP instruction has zero impact to the executed application, it is considered as masked and, thus, it reduces the overall AVF of the processor. The AVF is measured only for the storage cells (bits) of an architecture. Adopting the classification of [4, 47] the important bits are the Architecturally Correct Execution (ACE) bits, while the remaining bits are un-ACE bits. The AVF is defined as the portion of the important bits, which are required for the correct calculation of the final output of a program, to the total number of bits and it is given by

$$AVF = \frac{ACE \ storage \ bits}{Total \ storage \ bits \ of \ the \ processor}.$$

(3.1)

Since the processor changes its state at each cycle, the ACE bits also change. Therefore, the AVF is calculated per cycle.

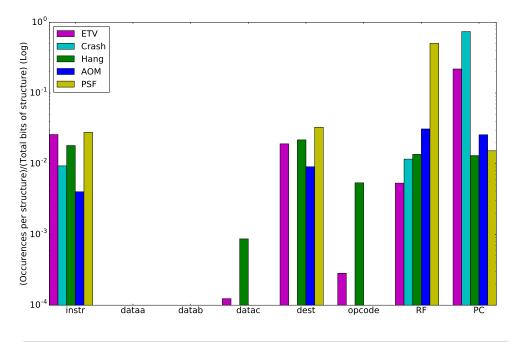

We define the following six classes that refer to the application's output and the processor's state after the complete execution of a program with one fault injected, as compared to the golden values obtained from an execution without faults:

- 1. **Correct**: The program is executed correctly. The program's output and processor's internal states (registers, stack memory, PC, etc.) match with the golden values.

- 2. Execution Time Violation (ETV): The output and processor's internal states are as expected, but the program finishes later than expected.

- 3. **Crash**: Execution finishes unexpectedly. An exception is raised and the processor crashes.

- 4. Hang: Execution enters in an infinite loop.

- 5. Application Output Mismatch (AOM): The program exits correctly, but its output does not match with the golden one.

- 6. **Processor's State Failure (PSF)**: The output of the program is correct, but there is(are) mismatch(es) in processor's internal state (registers, stack memory, PC, etc.).

When a fault occurs in the ACE bits, the result of the execution is either Crash, Hang or AOM. On the other hand, faults in the un-ACE bits result in Correct, ETV or PSF outputs.

A processor's simulator that simulates the behaviour of the VLIW architecture was developed during this thesis. The processor's model is developed in C++ and it is capable

of executing vex binaries. The simulator is enhanced with: a) a non-synthesizable fault injection function, which injects faults at user specified injection points and random timestamps, and b) a function which checks the output of the application and the state of the processor, compares them with the golden values, and categorizes the result in one of the six presented classes. The injection points can be in all the storage structures of the processor. The memory units (IM and DM) are excluded for better simulation performance under the assumption that ECC codes or similar techniques have been used for their protection.

The fault injection experiment is presented by Alg. 1. We execute once the binary file with our simulator without injecting faults to obtain the golden output values of the application and the golden state of the processor (line 1). Having the information about the cycles needed for one complete execution, we decide the number of cycles we will inject faults on  $(inj\_cycles)$ . Then, at each iteration, we choose randomly one unique cycle inside the valid range where the fault will be injected (line 3). For each of these cycles we iterate over all issues, all memory structures and all bits of each structure (lines 4,5,6).

| Algorithm 1 AVF Fault Injection Experiment Algorithm          |

|---------------------------------------------------------------|

| 1: ./vliw "binary_file" > gold_log                            |

| 2: for (i = 0, i < inj_cycles, i++) do                        |

| <pre>3: c[i] = unique_random(max_cycles, c, size_of(c))</pre> |

| 4: for each issue (\$is) do                                   |

| 5: for each struct (\$s) do                                   |

| 6: for each bit (\$b) do                                      |

| 7: ./vliw "bin" "gold_log" \$is \$s \$b \$c > inj_log         |

| 8: end for                                                    |

| 9: end for                                                    |

| 10: end for                                                   |

| 11: end for                                                   |

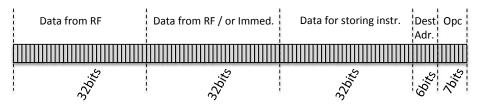

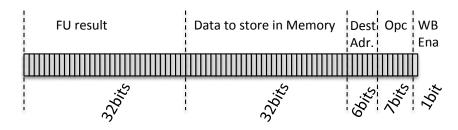

For the VLIW architecture used here we have four issues; the structures and their bits are shown in Table 3.1 (refer to Fig. 1.1). Thus, in every iteration, we inject one fault (modelled as bit-flip) to one bit of one of the FtoDC, DCtoEx, PC and RF registers. The results are compared with the golden ones from the *gold\_log* file and a report is generated and stored into the *inj\_log* file, categorizing each injection to one of the six presented categories.

Table 3.1: Bit composition for the used VLIW architecture.

|                         | FtoDC  |        |        | DCtoEx |       |        | PC | RF      |

|-------------------------|--------|--------|--------|--------|-------|--------|----|---------|

|                         | instr  | dataa  | datab  | datac  | dest  | opcode |    | IUL     |

| issues x<br>struct_bits | 4 x 32 | 4 x 32 | 4 x 32 | 4 x 32 | 4 x 6 | 4 x 7  | 32 | 64 x 32 |

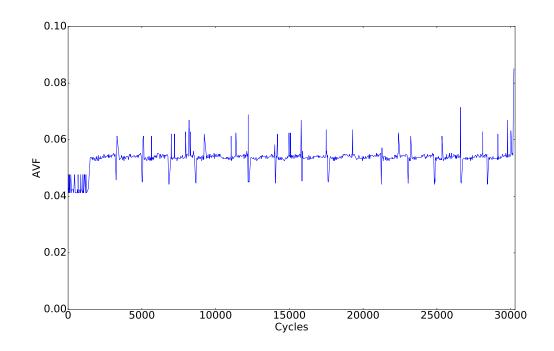

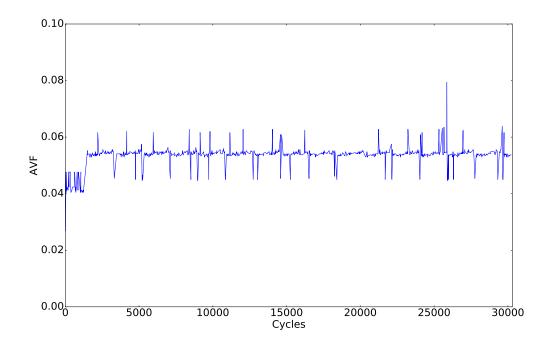

Fig. 3.1 presents the per cycle AVF of the processor when it executes a matrix multiplication application, calculated from Equation 3.1. The whole execution of the application takes 30228 cycles, thus an exhaustive fault injection simulation injecting faults at each cycle would require several days. Small intervals, such as one cycle difference, leads to a more accurate estimation with the AVF being more sensitive to the instantaneous behaviour of the application. On the other hand, when the interval length is too large, a lot of AVF variations may be lost. To tackle this issue and decrease the simulation time, we randomly choose 1000 unique cycles to inject faults at. The periodic behaviour of the AVF observed in Fig. 3.1 with instantaneous changes from max to low values shows the existence of loops in the executed code. The average AVF of the matrix multiplication application is 0.0534.

Figure 3.1: Per cycle AVF for VEX processor when executing a matrix multiplication

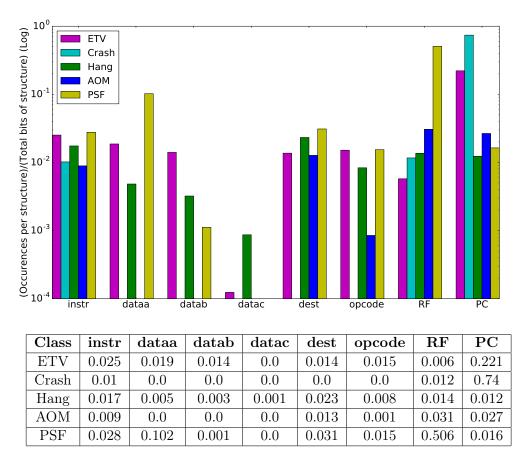

Fig. 3.2 presents the categorization of processor's AVF according to the aforementioned six classes when executing the matrix multiplication application. The results are normalized in order to be independent from the ILP and are presented in logarithmic scale. We observe that for most of the structures, the output of the application is rarely affected. This is because of:

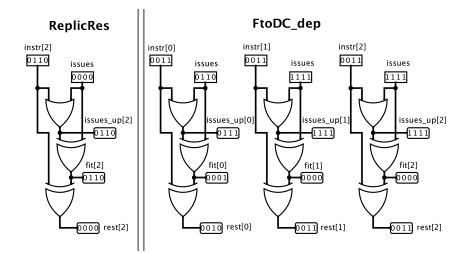

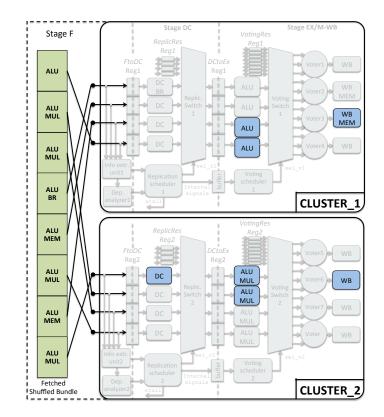

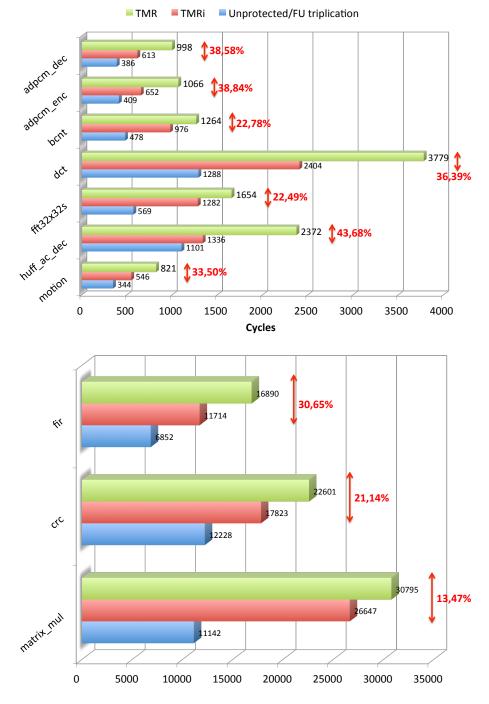

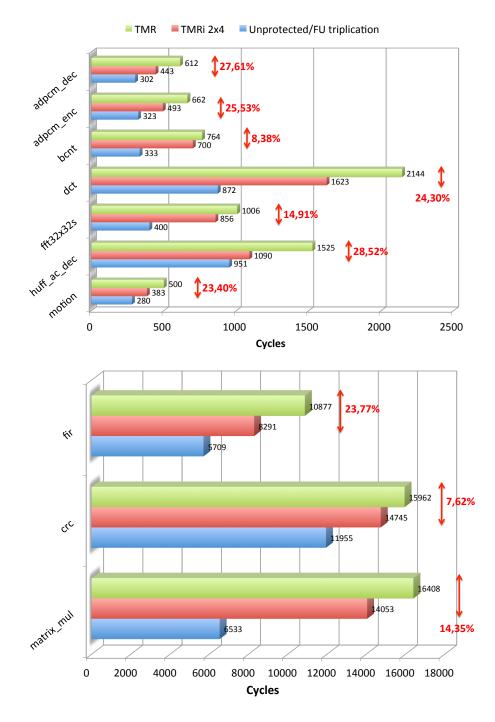

a) application masking (e.g. fault injection to a register that is not used by the application),