## Architectural Exploration of Network Interface for Energy Efficient 3D Optical Network-on-Chip

Van-Dung Pham

#### ▶ To cite this version:

Van-Dung Pham. Architectural Exploration of Network Interface for Energy Efficient 3D Optical Network-on-Chip. Embedded Systems. Université de rennes 1, 2018. English. NNT: . tel-01956229

### HAL Id: tel-01956229 https://inria.hal.science/tel-01956229

Submitted on 15 Dec 2018

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE DE DOCTORAT DE

#### L'UNIVERSITE DE RENNES 1

COMUE UNIVERSITE BRETAGNE LOIRE

**ECOLE DOCTORALE N° 601**

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: Traitement du Signal et Télécommunications

Par

### Van-Dung PHAM

# **Architectural Exploration of Network Interface for Energy Efficient 3D Optical Network-on-Chip**

Thèse présentée et soutenue à Lannion, le 13/12/2018

Unité de recherche : INRIA Rennes - Bretagne Atlantique et IRISA UMR 6074

Thèse N°:

#### Rapporteurs avant soutenance :

Virginie FRESSE Maître de conférences HDR à l'Université Jean Monnet Saint Etienne

Camel TANOUGAST Professeur des Universités à l'Université de Lorraine

#### **Composition du Jury:**

Président : Prénom Nom Fonction et établissement d'exercice (à préciser après la soutenance) Examinateurs : Virginie FRESSE Maître de conférences HDR à l'Université Jean Monnet Saint Etienne

Camel TANOUGAST Professeur des Universités à l'Université de Lorraine

Smail NIAR Professeur des Universités à l'Université de Hauts de France

Dir. de thèse : Olivier Sentieys Professeur à l'Université de Rennes 1

Co-dir. de thèse : Daniel CHILLET Professeur à l'Université de Rennes 1

Invité(s)

Sébastien LE BEUX Maître de conférences HDR à l'École Centrale de Lyon, Invité Cédric KILLIAN Maître de conférences à l'Université de Rennes 1, Invité

# Contents

| A | Abstract 1          |                                                                      |    |  |  |  |  |  |

|---|---------------------|----------------------------------------------------------------------|----|--|--|--|--|--|

| 1 | Intr                | roduction                                                            | 3  |  |  |  |  |  |

|   | 1.1                 | Context of 3D Optical Network-on-Chip                                | 4  |  |  |  |  |  |

|   |                     | 1.1.1 Optical Interconnect Technology                                | 4  |  |  |  |  |  |

|   |                     | 1.1.2 Three-Dimensional Integration                                  | 6  |  |  |  |  |  |

|   | 1.2                 | Thesis Contributions                                                 | 7  |  |  |  |  |  |

|   | 1.3                 | Dissertation Organization                                            | 9  |  |  |  |  |  |

| 2 | State-of-the-Art 10 |                                                                      |    |  |  |  |  |  |

|   | 2.1                 | Photonics Interconnect                                               | 10 |  |  |  |  |  |

|   |                     | 2.1.1 Transmitter                                                    | 11 |  |  |  |  |  |

|   |                     | 2.1.1.1 Lasers                                                       | 11 |  |  |  |  |  |

|   |                     | 2.1.1.2 Microring Resonators                                         | 13 |  |  |  |  |  |

|   |                     | 2.1.1.3 Modulators                                                   | 15 |  |  |  |  |  |

|   |                     | 2.1.2 Optical Medium                                                 | 16 |  |  |  |  |  |

|   |                     | 2.1.2.1 Waveguide                                                    | 16 |  |  |  |  |  |

|   |                     | 2.1.2.2 Through Silicon Via                                          | 18 |  |  |  |  |  |

|   |                     | 2.1.3 Receiver                                                       | 20 |  |  |  |  |  |

|   | 2.2                 | Optical Network on-Chip – Some Case Studies                          | 21 |  |  |  |  |  |

|   |                     | 2.2.1 ONoC based on Circuit Switching                                | 21 |  |  |  |  |  |

|   |                     | 2.2.2 ONoC based on Optical Crossbar                                 | 22 |  |  |  |  |  |

|   | 2.3                 | Survey of Existing ONoC Architectures Based on Communication Schemes | 23 |  |  |  |  |  |

|   |                     | 2.3.1 Single Writer Single Reader                                    | 24 |  |  |  |  |  |

|   |                     | 2.3.2 Multiple Writers Single Reader                                 | 25 |  |  |  |  |  |

|   |                     | 2.3.3 Single Writer Multiple Readers                                 | 26 |  |  |  |  |  |

|   |                     | 2.3.4 Multiple Writers Multiple Readers                              | 27 |  |  |  |  |  |

|   | 2.4                 | Error Correction Codes to Improve Energy Efficiency                  | 27 |  |  |  |  |  |

|   |                     | 2.4.1 Basic Concepts                                                 | 28 |  |  |  |  |  |

|   |                     | 2.4.2 ECC in Wireless Sensor Networks (WSN)                          | 29 |  |  |  |  |  |

|   |                     | 2.4.3 ECC in Optical Communications                                  | 30 |  |  |  |  |  |

|   |                     | 2.4.4 ECC for On-Chip Optical Interconnects                          | 30 |  |  |  |  |  |

|   | 2.5                 | Conclusions and Thesis Contributions                                 | 31 |  |  |  |  |  |

| 3 | Mo                  | deling and Analyzing Attenuation and Crosstalk in WDM ONoC           | 33 |  |  |  |  |  |

|   | 3.1                 | Introduction                                                         | 33 |  |  |  |  |  |

|   | 3.2                 | Chameleon Architecture                                               | 34 |  |  |  |  |  |

<u>Contents</u> ii

|   |     | 3.2.1 Architecture Overview                                       |  |  |  |  |  |

|---|-----|-------------------------------------------------------------------|--|--|--|--|--|

|   |     | 3.2.2 Optical Network Interface Architecture                      |  |  |  |  |  |

|   |     | 3.2.3 Communication Schemes                                       |  |  |  |  |  |

|   | 3.3 | Model of Attenuation                                              |  |  |  |  |  |

|   |     | 3.3.1 Fundamental Analysis                                        |  |  |  |  |  |

|   |     | 3.3.2 Analyzing loss and crosstalk at device level                |  |  |  |  |  |

|   |     | 3.3.2.1 MRs as perpendicular injector (Figure 3.10) 42            |  |  |  |  |  |

|   |     | 3.3.2.2 MRs as perpendicular ejector (Figure 3.11) 44             |  |  |  |  |  |

|   | 3.4 | Signal to noise ratio and loss model at system level              |  |  |  |  |  |

|   |     | 3.4.1 Propagation Loss                                            |  |  |  |  |  |

|   |     | 3.4.2 Bending Loss                                                |  |  |  |  |  |

|   |     | 3.4.3 Injector Loss                                               |  |  |  |  |  |

|   |     | 3.4.4 Ejector Loss                                                |  |  |  |  |  |

|   | 3.5 | Simulation Results                                                |  |  |  |  |  |

|   |     | 3.5.1 Technological and Architectural Hypotheses                  |  |  |  |  |  |

|   |     | 3.5.2 Results and Analysis on the Proposed Model                  |  |  |  |  |  |

|   | 3.6 | Conclusions                                                       |  |  |  |  |  |

|   |     |                                                                   |  |  |  |  |  |

| 4 |     | or Correction Codes for Energy-Efficient Optical Interconnects 51 |  |  |  |  |  |

|   | 4.1 | Problem Statement                                                 |  |  |  |  |  |

|   | 4.2 | Proposed Approach                                                 |  |  |  |  |  |

|   | 4.3 | Point-to-point Link and Energy/Performance Trade-offs             |  |  |  |  |  |

|   |     | 4.3.1 Communication Without ECC                                   |  |  |  |  |  |

|   |     | 4.3.2 Communication With ECC                                      |  |  |  |  |  |

|   |     | 4.3.3 BER and Laser Power Trade-Offs                              |  |  |  |  |  |

|   | 4.4 | Power and Energy Saving in Optical Interconnects                  |  |  |  |  |  |

|   |     | 4.4.1 Transmitted Laser Power                                     |  |  |  |  |  |

|   |     | 4.4.2 Power and Energy-per-Bit Saving                             |  |  |  |  |  |

|   |     | 4.4.2.1 Communication Without ECC                                 |  |  |  |  |  |

|   |     | 4.4.2.2 Communication With ECC 60                                 |  |  |  |  |  |

|   |     | 4.4.2.3 Power Saving Using ECC in Optical Interconnects 60        |  |  |  |  |  |

|   |     | 4.4.2.4 Energy-per-Bit Saving Using ECC 62                        |  |  |  |  |  |

|   |     | 4.4.3 Sensitivity of the Photo-Detector                           |  |  |  |  |  |

|   |     | 4.4.4 Trade-off Between BER and FEC Coding Gain 64                |  |  |  |  |  |

|   | 4.5 | Hardware Evaluation of ECC Techniques 67                          |  |  |  |  |  |

|   | 4.6 | Power and Energy Saving using ECC in Optical Interconnects 68     |  |  |  |  |  |

|   |     | 4.6.1 Power and Energy-per-Bit Saving                             |  |  |  |  |  |

|   |     | 4.6.2 BER and Laser Power Trade-Offs                              |  |  |  |  |  |

|   | 4.7 | Conclusions                                                       |  |  |  |  |  |

| _ | 04  | ical Network Interface Design 73                                  |  |  |  |  |  |

| 5 | _   | 3                                                                 |  |  |  |  |  |

|   | 5.1 |                                                                   |  |  |  |  |  |

|   | 5.2 | Run-time Adaptation of ONoC Energy and Performance                |  |  |  |  |  |

|   |     | 5.2.1 Considered Architecture and Applications                    |  |  |  |  |  |

|   |     | 5.2.2 Architecture of the Sequencer                               |  |  |  |  |  |

|   | F 6 | 5.2.3 Run-Time Management of Energy-Performance Trade-off 79      |  |  |  |  |  |

|   | 5.3 | ONoC Configuration Sequencer                                      |  |  |  |  |  |

Contents

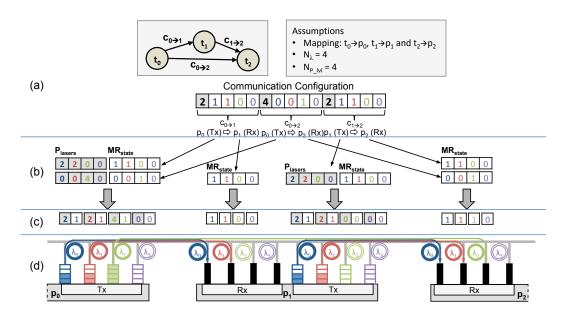

|          | 5.3.1   | Generation of Configuration                                    | 80         |

|----------|---------|----------------------------------------------------------------|------------|

| 5.       | 5.3.2   | ONoC Sequencing Illustration                                   | 82<br>82   |

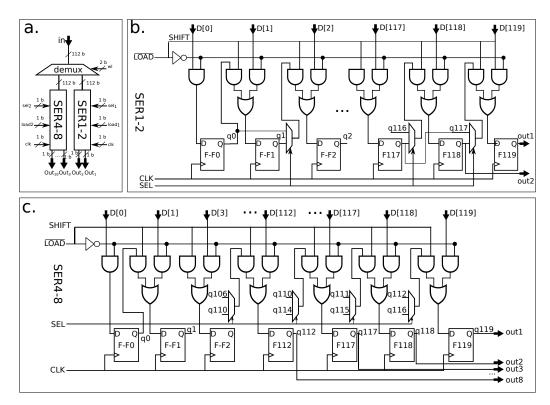

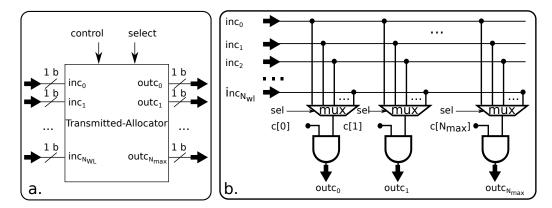

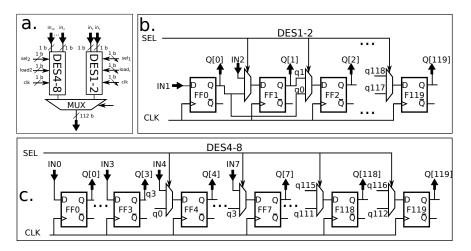

| 5.<br>5. |         | n of the ONI and OCS                                           | 84         |

| 0.       | 5.5.1   | Transmitters and Receivers for WDM in ONIs                     | 84         |

|          | 0.0.1   | 5.5.1.1 Operating Principle                                    | 84         |

|          |         | 5.5.1.2 Design of the Electrical – Optical Interface           | 87         |

|          |         | Serializer                                                     | 87         |

|          |         | Transmission Allocator                                         | 87         |

|          |         | Receiver                                                       | 88         |

|          | 5.5.2   | Results and Evaluation of WDM Stream Serialization and Deseri- |            |

|          |         | alization Interface                                            | 90         |

|          |         | Evaluation Methodology                                         | 90         |

|          |         | Synthesis Results                                              | 90         |

|          |         | Communication Latency                                          | 92         |

|          | 5.5.3   | Laser Driver                                                   | 96         |

|          |         | 5.5.3.1 Design of Laser Driver Circuit                         | 97         |

|          |         | 5.5.3.2 Methodology and Tools                                  | 97         |

|          |         | 5.5.3.3 Multi-Level Driver                                     | 98         |

|          |         | 5.5.3.4 Results                                                | 99         |

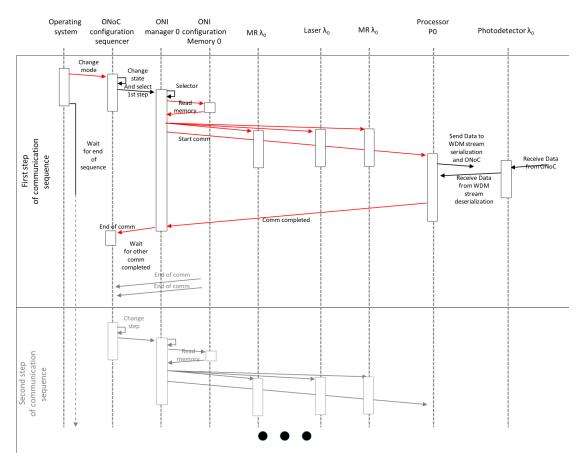

|          | 5.5.4   | ONI Manager                                                    | 101        |

|          | 5.5.5   | ONoC Configuration Sequencer                                   | 103        |

|          |         | 5.5.5.1 Results                                                | 105        |

| 5.       | .6 Cond | usion                                                          | 107        |

| 6 C      | onclusi | ns and Perspectives                                            | 108        |

| Autl     | hor's P | olications                                                     | 111        |

| Bibl     | iograph |                                                                | 111        |

| List     | of Acro | yms                                                            | 125        |

| List     | of Figu | es                                                             | <b>128</b> |

| List     | of Tabl | S                                                              | 131        |

### Abstract

Electrical network-on-chip (ENoC) has long been considered as the technology to improve the bandwidth and the performance of the interconnects in multiprocessor systems-onchip (MPSoCs). However, with the increase of the intellectual property (IP) cores integrated on a single chip, electrical interconnects are less and less suitable to adapt the bandwidth and latency requirements of the nowadays applications. In recent years, with low power consumption, low latency, and high data bandwidth properties, optical interconnect became an interesting solution to overcome these limitations. Indeed, Optical network on chip (ONoC) is based on waveguides and optical signals can be driven from source to destination with very low latency. But unfortunately, the optical devices used to built ONoCs suffer from some imperfections which introduce losses during communications. These losses (crosstalk noise and optical losses) are the very important factors which contribute to the energy efficiency and performance of the system. Furthermore, Wavelength Division Multiplexing (WDM) technology can help the designer to improve ONoC characteristics, especially the bandwidth and the latency. However, using the WDM technology leads to introduce new losses and crosstalk noises which negatively impact the Signal to Noise Ratio (SNR) and Bit Error Rate (BER). In detail, it can result in a higher BER and increases the power consumption and therefore reduces the energy efficiency of the optical interconnects.

In order to address these problems, we first model and analyze the optical losses and crosstalk in WDM based ONoC. The model can provide the analyzing of the worst case of loss and crosstalk with different parameters of optical ring network-on-chip. Based on this model, we propose a methodology to improve the performance and then to reduce the power consumption of optical interconnects rely on the forward error correction (FEC). We present two case studies of lightweight FEC with low implementation complexity and high error-correction performance under 28nm Fully-Depleted Silicon-On-Insulator

Contents 2

(FDSOI) technology. The results demonstrate the advantages of using FEC on the optical interconnect in the context of CHAMELEON ONoC. Secondly, we propose a complete design of optical network interface (ONI) which ic composed of the data flow allocation, integrated FECs, data serialization/deserialization, and the laser power driver. These different elements are presented in this manuscript. Rely on this interface, an energy efficiency allocation management can be supported at runtime due to the application demands. This runtime management of energy-performance can be integrated into the ONI manager through configuration manager which located at each ONI. Finally, the design of an ONoC configuration sequence (OCS) located at the centre of the optical layer is presented. By using the ONI manager, the OCS can configure ONoC at runtime according to the applications performance and energy requirements.

**Keywords** – Optical Network-On-Chip, Forward Error Correction, Optical Network Interface, Energy Efficiency, Design Space Exploration

### Chapter 1

## Introduction

Since several decades, Moore's law and International Technology Roadmap for Semiconductors (ITRS) forecasted that the number of transistors in an Integrated Circuit (IC) will double every 18 months. This increase now leads to the integration of hundreds of intellectual property (IP) cores into a single chip. In these multi-core parallel architectures, the data exchanges between cores can raise a major concern in overall system design: need for high performance interconnects for high data bandwidth communication. In this context, the design of on-chip interconnect plays a very important role for energy efficiency and performance of the overall system.

Electrical interconnects are the traditional candidate technology which can adapt to the application communication requirements. However, due to the characteristics of metal wire capacitance and inductive coupling [35], the increase in interconnect noise and propagation delay of global signals limits the overall system performance. Although a lot of effort has been made to solve these problems using many different interconnect architectures, until now, finding effective solutions to overcome these limitations remains a critical challenge.

New interconnects technologies such as three-dimensional (3D) stacking and optical interconnects could be a key solution for future on-chip interconnects. Nanophotonics interconnects are considered as one of the promising technologies, which is a key for the design of such next-generation of multi-processor system-on-chip. Optical interconnect allows for the increase of bandwidth as well as the reduction of noise, latency and power consumption. Another approach to improve the power and the performance of system

performance is 3D-stacked technology. Indeed, 3D stacking is a new technology that stacks many silicon wafers or multi-layers and interconnects vertically by using Through Silicon Vias (TSVs). This technology can improve the performance of a system in terms of power consumption, interconnection length and footprint. However, the combined use of 3D stacking and Optical Interconnect (OI) does not completely ensure overall performance. Instead, the exploration in terms of energy efficiency and performance, as well as the trade-off between Electrical-Optical exchanges, must be studied in this context.

### 1.1 Context of 3D Optical Network-on-Chip

#### 1.1.1 Optical Interconnect Technology

Photonics links have been often used from long distance communication to off-chip interconnects such as rack to rack, board to board, chip to chip or data central networks [104, 103, 23]. But since a couple of years, Silicon photonics seems to be a very interesting emerging technology for the integration of NoC on Multi-Processor System-On-Chip (MPSOC). This technology is based on the use of an optical wave-guide medium to transport optical signals from source to destination with a very short latency.

The key of this technology is the ability to use Complementary Metal-Oxide Semiconductor (CMOS) fabrication in larger-scale. Compared to electrical interconnects, the advantages of this technology are the reduction of crosstalk, the high bandwidth immunity to electromagnetic interference (EMI) and the potential lower power consumption.

These advantages can make optical technology becoming a promising technology to solve the problems of the electrical links.

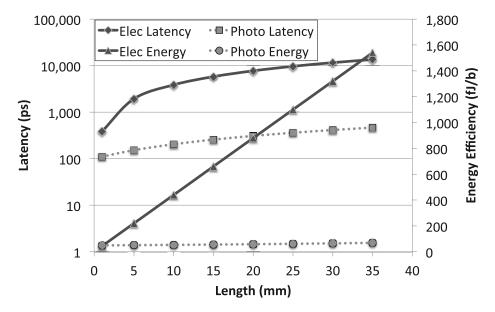

Figure 1.1 illustrates the latency and energy efficiency of electrical and optical interconnects as a function of distance between source and destination nodes. The data are extracted from ITRS<sup>1</sup> for a 16nm SOI technology. As we can see in this figure, the dotted lines present the potential of optical links compared to the electrical links (solid lines). For future multi-core processors, this evolution can offer the possibility to replace electrical links by on-chip optical links. By using this technology, the power consumption can

<sup>&</sup>lt;sup>1</sup>See http://www.itrs2.net/2011-itrs.html

be reduced and the bandwidth can be adapted to the requirements of data exchanges between a large number of cores in a single chip.

FIGURE 1.1: Latency and energy efficiency of electrical and optical interconnects as a function of distance for a 16nm technology (source ITRS)

The major advantages of Optical Interconnects (OI), compared to electrical interconnects in terms of latency and energy efficiency, appear for long distances between source and destination nodes. Furthermore, two important advantages must be considered. Firstly, the increasing data rate will not change energy efficiency because the optical loss does not depend on the data rate. Secondly, optical interconnects can increase bandwidth and data rate by using wavelength multiplexing division (WDM) technology. WDM multiplexes multi-optical carrier signals into a single optical wave-guide by using different wavelengths. Finally, compared to electrical links, optical links can also provide many communication strategies: point to point, broadcast, and varying bandwidth.

There are many reasons to claim that OI can overcome the bottleneck of electrical interconnects based on the signal propagation principle. In the optical domain, the optical signal carries information at a very high frequency and this signal is carried within the optical wave-guide. Then the optical signal is crosstalk and reflection immune. These advantages ensure that optical link has significant ability to support communications not only for long distances but also for on-chip interconnect multiprocessor systems.

#### 1.1.2 Three-Dimensional Integration

Future on-chip multi-core processor systems face a challenge due to the increasing amount of integrated IP cores on a single chip. These challenges are putting inflexible requirements for the MPSOC designer. Recently, optical interconnects show the possibility to become an emerging solution for on-chip interconnects due to their advantages of high bandwidth, high energy efficiency and low latency. Some of the approaches using ONoC have been recently proposed. These approaches are based on the integration of Optical NoC (ONoC) on a specific silicon wafer/layer. However, the disadvantages of this integration are the complexity and the optical wave-guide crossing losses. 3D-stacked technology is one of the promising solutions which can solve the communication problem between these layers. This technology allows for the integration of ONoC in multi-layer. This approach can reduce the wave-guide crossing, one of the main factor impacting the power budget of optical interconnects. Furthermore, 3D stacking provides a significant cost advantage, which leads to the simplification of designs as well as the manufacturing process.

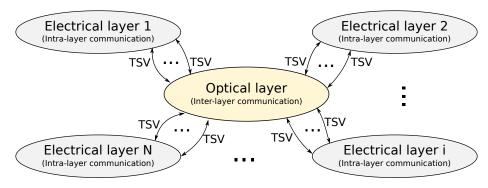

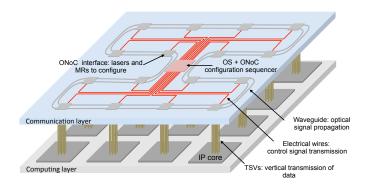

As we can see in Figure 1.2, a 3D ONoC is composed of an optical layer located between several electrical layers. Each electrical layer contains the Electrical NoC (ENoC) which is used to route the control packets and configure the Optical Network, whereas the optical layer includes the ONoC which consists of optical components such as lasers<sup>2</sup> [119], modulators [7, 92], photo-detectors [44], wave-guides [7]. In order to transfer data among

FIGURE 1.2: Architecture organization of a 3D Optical NoC [9]

electrical and optical layers, vertical interconnects through TSVs are employed. Communications between nodes of the different electrical layers (inter-layer communications) are supported by ONoC. Nodes on the same electrical layer communicate by intra-layer

$<sup>^2{\</sup>rm The~term}$  "lasers" originated as an acronym for "light amplification by stimulated emission of radiation."

communication. Recently, some companies have used 3D stacked technology in their chip manufacturing. For example, in 2007, IBM introduced chip with 3D-stacked technology [90]. In 2010, a new 3D-stacked technology which can integrate 100 silicon chips in a single package was proposed [91]. Even if 3D stacked technology can be interesting, it also induces new challenges, such as thermal problems. Indeed, thermal increase can lead to several undesirable effects such as the increase in power consumption, performance degradation and it generally reduces the reliability of the overall system. Recently, several approaches have been proposed for thermal issue management, for example by addressing new network topologies or task mapping.

To conclude, 3D ONoC is one of the most promising technologies for the next generation of MPSoC interconnects since it has the potential to reduce the interconnect length and the power consumption. However, 3D ONoC still has many open problems such as the design of optical network interface.

#### 1.2 Thesis Contributions

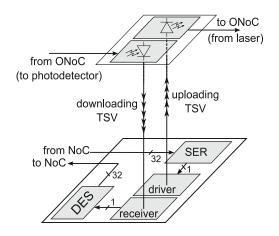

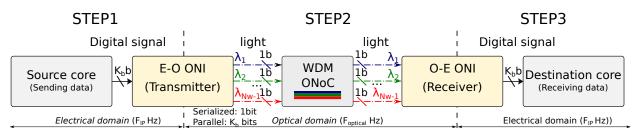

3D ONoC is a potential candidate in future MPSoC architecture. In this type of architecture, the electrical layers are connected to the ONoC by using vertical interconnects (TSVs) to upload and download the data between the different layers. More precisely, to emit optical data, the TSV is directly connected to an optical modulator to drive an on-chip laser source which is located in the transmitter of the optical network interface (ONI). At the receiver part of the destination ONI, a TSV is connected to a pair of microresonator and photo-detector. The transmission will be performed in a serial manner in order to reduce the number of TSVs. According to the capacity of optical interconnects with high throughput, the data serialization requires a high-performance ONI which has to be designed to modulate and demodulate data emitted between electrical and optical domains. Modulation and demodulation need to be performed at high frequency to provide high bandwidth.

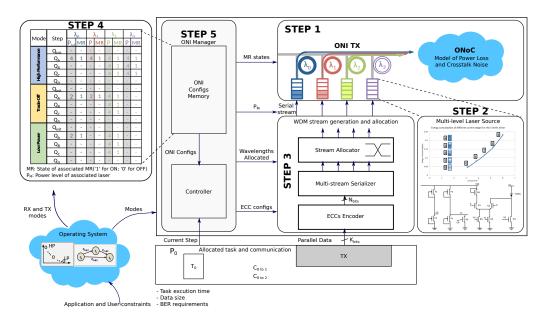

To address the Optical Network integration challenges, we propose a set of contributions which are summarised in the Figure 1.3. This figure illustrates the contributions of the thesis according to three main problems.

Figure 1.3: Representation of the components required for ONoC and highlight of the thesis contributions

- Energy efficiency on-chip optical interconnects based on the state of the art of Error Correcting Codes (ECC) (Step 1 and Step 3): ECCs have proved their abaility in optical communications [72, 100] or wireless sensor networks (WSN). From this context, we take advantage of ECC to improve the energy efficiency of optical interconnects for MPSoC. Our approach demonstrates the improvement of optical interconnects in terms of energy efficiency and communication reliability. The aim of this contribution is to find a trade-off between energy and performance.

- Design of high-performance optical interface based on the ECC (Step 2 and Step 4): The design of the ONI is one of the most important factors that contribute to the overall system performance. To the best of our knowledge, there are no global solution in the state of the art. Therefore, in this thesis, we propose the first complete optical network interface for WDM ONoC. This interface allows bandwidth and latency adaptations according to the different communication strategies.

- Management unit for the optical network interface (Step 4 and Step 5):

Based on the interface architecture and the design of the laser driver, we propose a

management unit for the optical network interface. This ONI manager consists of

an ONI configuration memory, which receives data from allocation protocol, and

a controller which is driven by allocated tasks and operating system. We have designed this interface, and evaluations and synthesis results of this unit are provided.

#### 1.3 Dissertation Organization

The thesis dissertation is organized as follows. In Chapter 2, we present the state of the art in which the detail of optical devices and structure of optical link are firstly described. Secondly, our target architecture and Optical Network Interface are presented. Thirdly, state of the art in terms of Error Correcting Code (ECC) with related works in optical communication and WSN are presented. In Chapter 3, we model and analyze the optical losses and the crosstalk in WDM communications. We define the mathematical formulations of the different losses and we also propose a global mathematical model for a point to point communication. In Chapter 4, we propose an energy efficient optical interconnect based on ECC. In this chapter, we propose to use ECCs to improve the energy efficiency in order to meet the communication requirements. Since we model the structure and losses of optical interconnects, we establish the trade-off between energyefficiency and system performance. In Chapter 5, we propose the complete design of the optical network interface in which the ONI has to be implemented as a co-design of both electronics and photonics domains, and where network issues, such as flow control, serialization, descrialization, and ECC integration, must be carefully evaluated. Furthermore, in this chapter, we also present the design of a management unit located in the electrical layer to control the interface and optimize the number of allocated wavelength according to the application requirements. Finally, conclusions and issues for future researches are discussed in Chapter 6.

### Chapter 2

# State-of-the-Art

Currently, optical interconnect is an attractive solution to address scalability issues in on-chip communication with low-power consumption, low latency, and high data rate and bandwidth. Some techniques, like error-correcting codes (ECC) have been used to improve the communication quality. In this chapter, an overview of optical interconnects including optical devices, like microring resonator, waveguide, photo-detector, and laser, is firstly presented in Section 2.1. Secondly, the classification of optical interconnects is described in Section 2.2 and several optical network-on-chip architectures are also presented. Thirdly, the main principle of ECC is presented in Section 2.4 and the use of this technique for ONoC is introduced. Finally, Section 2.5 concludes this state-of-the-art chapter.

#### 2.1 Photonics Interconnect

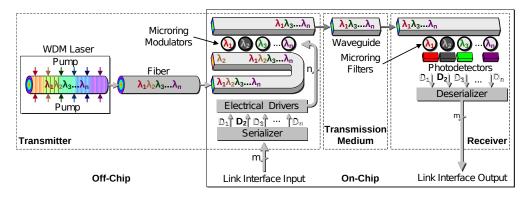

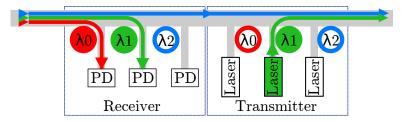

Compared to electrical interconnects, on-chip optical devices show a great potential to become an emerging candidate for on-chip interconnect due to their properties (low latency, high bandwidth, and low power consumption). In this section, we present an overview of the candidate optical interconnect of Figure 2.1 that directly connects a source and a destination. It is composed of three main parts: a transmitter, a receiver, and a medium. In Figure 2.1, the laser is an off-chip laser which can emit multiple wavelengths for the communication. These wavelengths are injected into the waveguide and they are modulated by the microring resonators (MRs). The transmitter consists

Figure 2.1: Overview of an optical interconnect using off-chip laser [74]

of the combination of the external laser, waveguides, serializer, electrical drivers and microring resonators. The signal is driven on the medium (waveguide) until it reaches a resonator which extracts and drives it towards the photodetector. At the receiver side, the signal is converted from the optical domain to the electrical domain by the photodetector and the serial data are converted into parallel data. Finally, the signal is transmitted to the destination by an electrical network which is located in the electrical layer.

#### 2.1.1 Transmitter

The transmitter converts the electrical signal into the optical signal. An optical transmitter includes a laser, a driver network, and a micro-ring resonator. In the following sections, the main optical devices are introduced step by step.

#### 2.1.1.1 Lasers

The position of the laser source can be categorized into two main types: on-chip and off-chip lasers. In this thesis, we focus on on-chip laser integrated into the same die with the other parts of the interconnect, without using an optical coupler to bring the light into the chip. We consider both modulation schemes: indirect and direct modulation. Compared to the off-chip laser, the on-chip laser can provide three key following advantages:

• First, it simplifies the integration in the design by relaxing constraints on the layout. Furthermore, the additional cost from an external laser source to the on-chip modulator is removed.

• Second, the flexibility and scalability of the network can be improved by optimizing the laser source placement on the layout.

• Third, the power consumption reduction can be enhanced by run-time management which can turn-on the laser when the communication occurs or turn-off when there is no communication to ensure. Furthermore, on-chip lasers with low-power consumption can be obtained by reduction of loss due to communication crosstalks. Moreover, for off-chip laser, the loss path is not only from source IP to destination IP, but also from the off-chip laser to source IP. Therefore, by using the on-chip laser, we can reduce the global loss and then reduce the required laser output power.

On-chip light source is an imperative and important device of silicon photonics technology. With features advantages, the on-chip laser shows the potential to become the enabling technology of on-chip light source. Recently, some new technologies have been presented for on-chip laser like Fabry-perot (FR), Distributed Feed-back (DBR) and Micro-disk [12, 80, 22, 101, 21].

Vertical cavity surface emitting laser (VCSELs) is also an interesting technology due to the footprint size as well as straightforward fabrication [5]. Particularly, VCSEL can provide the output power in the range of hundred microwatts, which can adapt the requirement of current and future nanophotonic interconnect. Additionally, double photonics crystal mirror VCSEL (PCM VCSEL) based on a complementary metal-oxide semiconductor are CMOS compatible, which allows for DWDM direct modulation and indirect modulation [94]. Thus, VCSELs are sufficiently compact to implement a large number in a single chip. By specializing the topology, we can avoid the waveguide crossing losses, which is a very costly element contributing to the power budget of the overall system.

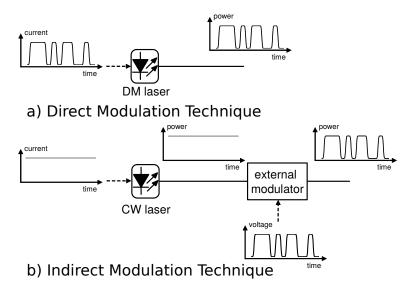

As previously mentioned, the main role of the laser is to produce the optical signal that will be sent into the waveguide. But this optical signal must also transport the information (data) from sender to receiver and, to ensure this feature, the optical signal must be modulated. There are two methods to modulate the signal: direct modulation (internal) and indirect modulation (external). The direct modulation method is the technique for which the optical signal is directly modulated by turning on or off the laser source (Figure 2.2.a). In the indirect method, the optical signal is always on. Meanwhile, the light

is modulated by an external device (MRs modulator) in order to control the light flow through the optical waveguide as illustrated in Figure 2.2.b.

FIGURE 2.2: Modulation schemes: a) direct modulation technique and b) indirect modulation technique [81]

#### 2.1.1.2 Microring Resonators

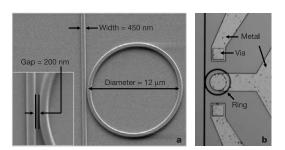

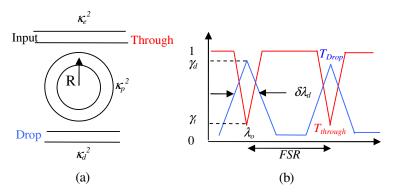

A Microring Resonator (MR) is an optical device which is built for optical interconnects. The main role of MR consists in extracting a specific wavelength from an optical signal and injecting this wavelength to another waveguide. The resonance of the wavelength can be modified to control the extraction or injection of the optical signal into the waveguide. Figure 2.3 illustrates the structure of an MR with a diameter of  $12\mu m$ . This is a passive

FIGURE 2.3: Structure of an actual  $12\mu m$ -diameter passive microring

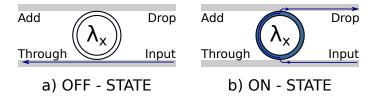

MR used for moving a certain wavelength from the waveguide to another. Figure 2.4.a and Figure 2.4.b show a microring Resonator in the OFF-resonate state and ON-resonate state, respectively. Each MR can be resonated at a given wavelength. When the MR is in OFF state, the wavelength continues in the main waveguide (from input to through

ports). Whereas, when the MR is turned ON, the wavelength is extracted from the main waveguide and injected inyo the second waveguide (from input to drop ports).

FIGURE 2.4: Microring Resonators states a) Off state; b) On state.

The resonated wavelength depends on both MR's diameter and effective refractive index [7]. These parameters are affected by the electrical charge and the thermal issue.

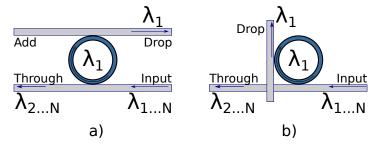

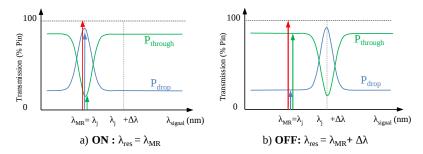

Based on the fabricated method, there are two types of MR: passive MR and active MR. The active micro-ring is used as a modulator to modulate the light which is emitted from the laser source (see Section 2.1.1.3). The active MR is used as an optical switch. It is biased during fabrication to extract only a single wavelength from one waveguide and reflect the others. The function of MR is similar to a switch with two states: OFF-resonate and ON-resonate. The wavelength is selected to drop into the MR. Furthermore, in order to avoid the optical crossing loss, which is one of the major factors impacting the energy efficiency, the MRs can be configured in parallel or perpendicular waveguide configuration. Figure 2.5.a and Figure 2.4.b show the MR in ON-state and OFF-state with  $\lambda_1$  in

Figure 2.5: Waveguides and MR positions; a) parallel configuration; b) perpendicular configuration

perpendicular and parallel waveguides configurations, respectively. In the perpendicular waveguide configuration, multi-layer technology are used to avoid the waveguide crossing losses (0.05dB to 0.2dB [10]). Communication between layers can be implemented by using vertical grating couplers as we can see in Figure 2.6.a. The perpendicular waveguide configuration is shown in Figure 2.6.b using vertical grating couplers. Due to its simple response, MRs can be used to build many important optical components such as optical router, optical switch, optical modulator and detector. However, MR is a device that is

FIGURE 2.6: a) The MR in parallel configuration is turned ON to select  $\lambda_1$  wavelength; b) The MR in perpendicular configuration is turned ON to select  $\lambda_1$ .

very sensitive to temperature issues. Therefore it can become a major source of errors if the temperature is not stable. In particular, MRs can suffer from the important shift in its resonant wavelength due to temperature increase, which can lead to stopping extraction from a waveguide or injection to a waveguide. Thus, architecture considerations need to be explored in order to improve interconnect energy efficiency.

#### 2.1.1.3 Modulators

As explained before, the modulation can be direct or indirect. When the modulation is direct, the photonics device which supports this feature is the laser. But when the modulation is indirect, the photonics device which supports this functionality is generally a microring. Indeed, because the resonance frequency of MR can be changed (by the carrier depletion), it can be used as a modulator. In this case, the MR is an active component which is controlled to modulate the optical signal from data to transport.

In the context of optical interconnects, on-off keying (OOK) coding is the simplest modulation technique which can adapt the communication speed and bandwidth requirements due to its simple implementation. In this method, logic '1' is represented by the presence of light in a given wavelength and logic '0' is the absence of light in this wavelength. This coding can be created by controlling an active MR (see Section 2.1.1.2) to:

- extract a wavelength from a waveguide and drop it onto another waveguide (case

of '1'),

- let the wavelength pass through the MR without extraction (case of '0').

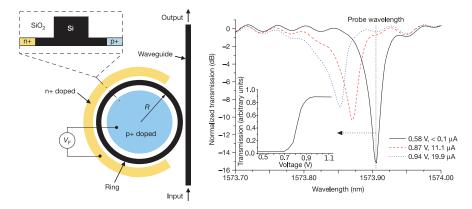

In order to control the MR, an electrical current is used to change the refractive index by changing the bias voltage applied on the modulator. Figure 2.7 shows the layout and DC measurement of an MR modulator in which the inset shows the cross-section of

the microring. R is the radius of microring resonator.  $V_F$  is voltage applied on the MR modulator.

FIGURE 2.7: a) Layout of the ring resonator-based modulator b) Transmission spectra of the ring resonator at the bias voltages of 0.58 V, 0.87 V, and 0.94 V, respectively.

#### 2.1.2 Optical Medium

Optical medium is the key component to transfer the optical signal between the transmitters and receivers in 3D ONoC. Based on the material, we can classify into different kinds of media: Air,  $SiO_2$ ,  $Si_3N_4$ , etc. In this section, we present some transmission media with different configurations and materials.

#### 2.1.2.1 Waveguide

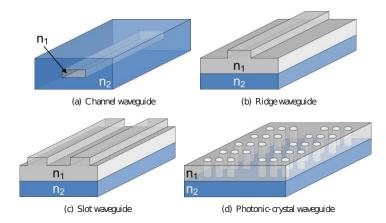

As depicted in Figure 2.8, there are four main configurations of waveguides: channel, ridge, slot, and photonics-crystal. Among them, the channel and ridge (Figure 2.8.a and Figure 2.8.b) are the most popular configurations used in on-chip interconnects [50]. Slot and photonics-crystal configurations (Figure 2.8.c and Figure 2.8.d) are less common.

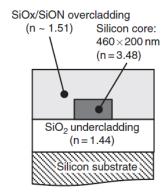

Figure 2.9 shows the cross-sectional structure of a waveguide which consists of different refractive indexes: a core with high refractive index surrounded by a lower refractive index material which is called cladding material. In the context of on-chip interconnects, there are many materials to construct the optical waveguides such as: glass, polymer, or semiconductor. Among them, semiconductors show the potential to become an emerging material due to their characteristics which can make a very high contrast between core and cladding. Especially, Silicon has shown its ability to become an attractive candidate

FIGURE 2.8: a) Channel b) Ridge c) Slot and d) Photonic-crystal waveguide configurations.

FIGURE 2.9: Cross-sectional structure of a typical cladding waveguide.

due to CMOS compatibility in the fabrication. Therefore, in this thesis, we assume that the material to construct waveguide is Silicon, although it could be glass, polymer or another semiconductor materials.

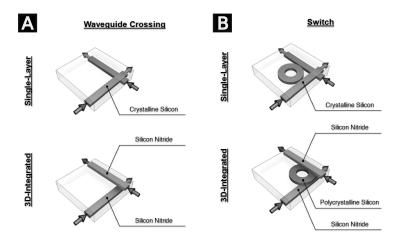

In addition, insertion optical loss is an important factor which affects the overall power consumption of the optical interconnect. Therefore, the loss of waveguide must be analyzed to explore carefully the optical network-on-chip architecture trade-off. In the optical waveguide, optical losses are composed of material absorption, scattering and two-photon absorption (TPA) [95]. Furthermore, the bending loss and waveguide crossing loss are the other sources of loss [40, 78, 47]. According to [59], the absorption of light in silica and silica oxide is negligible compared to the others. However, the crossing loss is the most important factor which directly impacts the power consumption in ONoC due to its high effect on communication quality. Therefore, in order to avoid the waveguide crossing and improve the power efficiency, the multi-layer technology could be used to replace single layer as illustrated in Figure 2.10. Waveguide crossing can be avoided by using multi

FIGURE 2.10: Waveguide crossing and Switching Element for both single-layer and 3D-integrated approaches [10]

optical layers technology. Indeed, the waveguide crossing (Figure 2.10.a) and switcher (Figure 2.10.b) are the most popular components used in optical network on-chip. The potential of the multi-layer technology can eliminate the waveguide crossings created by these elements, and improve the energy-efficient of optical interconnect.

#### 2.1.2.2 Through Silicon Via

In the 3D integrated circuit paradigm, Through Silicon Via (TSV) [39, 69, 110] is used for data transfer between different layers. Figure 2.11 illustrates the position of TSV in the interface of a potential 3D ONoC. An uploading TSV is used for connecting the

Figure 2.11: TSV's position in the optical network interface in the context of 3D ONoC [54]

electrical layer with the optical layer, then the electrical signal is used to modulate the

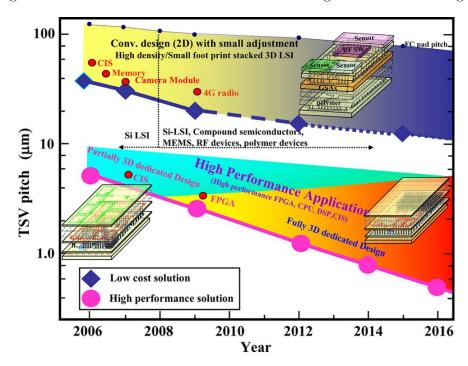

optical signal. A downloading TSV is used for connecting the optical layer to the electrical layer. At the optical layer, a photo-detector is used to convert the optical signal into the electrical signal, which is then transported by TSV. Size and pitch of TSVs are very important factors which impact the overall footprint. It is then clear that a trade-off must be found between the area needed for an Optical Network Interface (ONI) and the area of a set of processor cores, grouped in a cluster, which is connected to this ONI. Figure 2.12 shows the TSV size evolution according to ITRS. In this figure, the

Figure 2.12: TSV for three-dimensional large-scale integration (3D-LSI) technology roadmap from [69]

current TSV technologies for 3D-LSI are classified into two types, according to their sizes, and it appears that TSVs can become a dominating technology in the future of three-dimensional large-scale integration. In particular, TSV reduces the length of interconnects as well as the size and pitch of interconnects compared with the other interconnect technologies. Although TSVs provide many advantages such as electrical performance, low-power consumption and higher data bandwidth, it also presents some drawbacks which lead to some design challenges such as testing process, power distribution and thermal issue.

Therefore, the need for design exploration is very necessary to evaluate the interest of this technology.

#### 2.1.3 Receiver

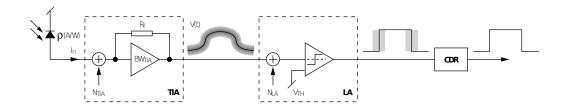

Optical receivers must support several functions which are: i) receiving optical signals, ii) converting them into electrical analog signals, iii) processing and restoring digital signals. In this section, we will present the general structure of an optical receiver in the context of on-chip optical interconnect. As the main part of the receiver is composed of photo-detectors which convert signals from optical to electrical domains, a classification of photo-detectors and the sensitivity of optical receivers are also presented.

FIGURE 2.13: Structure of a single-wave optical receiver.

The structure of a typical optical receiver is illustrated in Figure 2.13. It consists of a photo-detector (PD), a trans-impedance amplifier (TIA), a limiting amplifier (LA), and a clock data recovery (CDR) block. For the case of WDM scheme communications, each PD is associated to an MR to extract the corresponding optical signal from the main waveguide [14].

In Figure 2.13, the optical signal is directly extracted from the optical waveguide and sent to the photo-detector. The photo-detector converts optical signals into electrical currents. This current is transformed into a voltage which is then amplified by the transimpedance amplifier. The limiting amplifier acts as a comparator with a threshold voltage  $V_{th}$ . Clock-data recovery will then restore the original signal.

As one of elements of the optical receiver, PD is an optical device that directly converts optical signals into electrical signals. Currently, there are many types of photo-detectors used in Optical Network on-Chip with a variety of materials and structures such as silicon photo-detector [13], III-V semiconductors [38] and Germanium photo-detector [102].

Based on their structure, we can classify photo-detectors in two types: P-I-N photo-diode (PIN) [29] and avalanche photo-diode (ADP) [37]. In the context of on-chip optical interconnects, PIN photo-detector has been widely used as the optical receiver [29],

[44] due its its advantages in terms of dark current, responsivity, operation speed, and footprint.

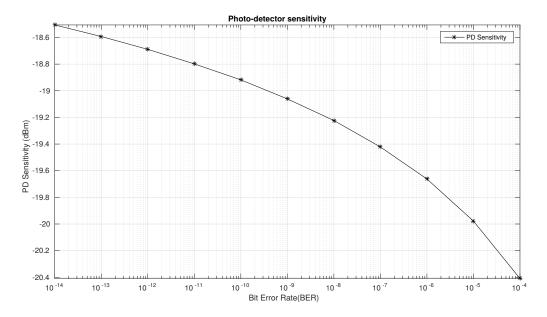

To obtain the power budget of the optical link, one important factor that needs to be considered is the photo-detector sensitivity. The sensitivity (in dBm) is the minimum optical power required at the receiver to achieve a given BER value. For example, if a sensitivity is  $P_{sen} = -25dBm$  at  $BER = 10^{-9}$ , this means that if the optical power at the optical receiver is greater than or equal to -25dBm, the system can operate reliably with  $BER = 10^{-9}$ . The computing of sensitivity and power budget will be presented in Section 4.4.3 in more details.

#### 2.2 Optical Network on-Chip – Some Case Studies

Recently, many WDM-based ONoCs have been presented in the literature with different designs. The differences between these designs come from their architectures and the components used to build the communication infrastructure.

More generally, ONoCs can be classified into two main categories: i) Circuit Switching ONoC and ii) ONoC based on Optical Crossbar. They will be described in more details in the following sections.

#### 2.2.1 ONoC based on Circuit Switching

As mentioned in Section 2.1.1.2, an active MR is a micro-ring which can be used as an optical switch to transmit the light in an optical waveguide. Hence most of the optical switching circuit interconnects are implemented based on active MR components. This kind of MR requires an electrical control network to change the state of the wavelength resonance by changing the reflective index. In circuit switching interconnects, the data transmission is divided into three steps. Firstly, control packets are routed in the electrical control network in order to reserve the optical path and configure the active micro-rings. Secondly, when the control packets are completely sent from the source to the destination, the optical path is established and active MRs are configured to turn ON or turn OFF based on traffic requirements. The optical data are sent directly from source to the destination. Finally, once the optical transmission is completed, an erase packet is sent

to relax the communication path and the optical devices. This transmission of erasing packet can also be used to prepare the reservation for the next communication slot.

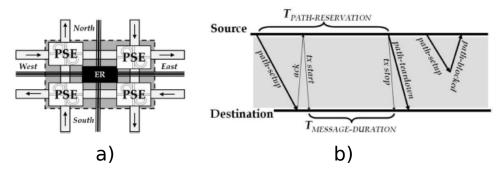

FIGURE 2.14: a) Basic optical router based on MRs, b) Qualitative timing diagram of a successful optical path setup and a blocked setup request [97]

Figure 2.14.a and Figure 2.14.b show the structure of router based on the Switching Circuit and the setup process in optical switching circuit interconnects [97]. Figure 2.14.a presents an optical router structure based on the four PSE (photonic switching elements) controlled by an electronic router (ER). In Figure 2.14.b, the timing diagram illustrates the timing discrepancy which includes the time to reserve the path before sending the packet to the destination. The disadvantage of an ONoC based on switching circuits is the time to set up the optical path which can reduce the latency and increase system power consumption. Recently, several ONoC based on switching circuits have been presented. For instance, [32, 109, 117] present ONoCs with Mesh topology, [118, 96] with Folder Torus, and [33] with Fat-Tree topology. All of them suffer from reservation time in the optical path which can be long.

Therefore, switching circuit technique can become a major challenge of the ONoC design. This problem can be solved by using the ONoC based crossbar introduced in the next section.

#### 2.2.2 ONoC based on Optical Crossbar

Crossbar ONoC is based on passive MRs which are set up to select a given wavelength. Therefore a source IP can directly send the data through the optical router with one or several predefined wavelengths. In crossbar ONoC, due to the property of passive microring which does not need to be tuned (MRs are already set up before the communication occurs), the message transmission does not require the time to set up the optical path

and the time to relax the MRs after finishing the transmission. Compared to switching ONoC, this technique has the advantage to reduce the overall latency. However, conflicts can appear in optical routers of the crossbar ONoC when many communications occur at the same time. These conflicts can be solved by using an arbitration that can be implemented by an optical network or an electrical network. For instance, when a communication occurs between a source and a destination at a given time, the destination cannot receive any data from other sources. Then, the destination sends a message to the arbitration to decline other connected requirements from other sources. The potential of the arbitration compared to the electrical control network of switching circuit network is the latency.

Because passive MR does not require the time for reservation as well as the time to relax after finishing the communication, this technique can exploit all the properties of the optical network which are the high bandwidth and the low latency. Furthermore, the power consumption of passive MRs is less than the power consumption of active MRs which require a bias current to be controlled. Then the power consumption of the overall system can be reduced. In this thesis, we focus on crossbar ONoCs with four different communication schemes. The following section introduces some of the existing ONoCs based on optical crossbars.

# 2.3 Survey of Existing ONoC Architectures Based on Communication Schemes

This section describes some case studies of the optical crossbar based interconnects with different architectures. Based on the communication schemes, there are many optical interconnects with different structures: SWSR (Single Writer Single Reader), MWSR (Multiple Writers Single Reader), SWMR (Single Writer Multiple Readers), and MWMR (Multiple Writers Multiple Readers). In this section, we present step by step these different structures. Each structure is illustrated by a typical example with its corresponding features.

#### 2.3.1 Single Writer Single Reader

SWSR is the simplest interconnect scheme. It relies on the wavelength routing between a source and a destination IP. For instance, Figure 2.15 illustrates the architecture and the connectivity strategy of the SNAKE ONOC [88]. SNAKE is a wavelength routing archi-

FIGURE 2.15: SNAKE ONoC a) architecture and b) connectivity strategy [88]

tecture based on passive MRs in which each pair of source and destination elements are connected by different wavelengths (Figure 2.15.b). The advantage of this communication scheme is its simplicity and low latency due to the non-blocking property. However, the disadvantage of SWSR is the lack of scalability which is limited by the number of optical resources such as the number of MRs, the number of wavelengths in a waveguide, and the number of lasers.

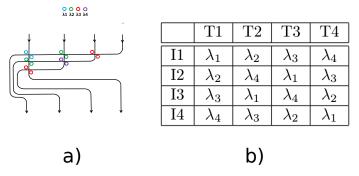

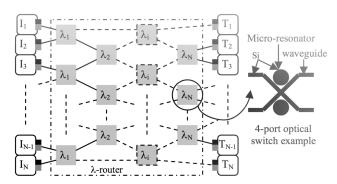

Another example of SWSR is the  $\lambda$ -Router represented in Figure 2.16 [11]. This ONoC is a

FIGURE 2.16:  $\lambda$ -Router a) architecture and b) connectivity matrix [11].

contention-free network, meaning that the  $\lambda$ -Router ONoC does not need any arbitration network. This property can be ensured because all destinations can receive the data without any conflict.

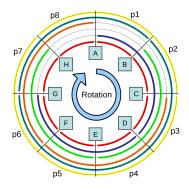

In ORNoC [53], Le Beux et al. present a new communication scheme for which SWSR channels can be reused by reusing the same wavelengths for different communications in

FIGURE 2.17: Optical Ring Network On-Chip (ORNoC) [53]

different parts of the waveguide. This technique is really interesting in particular because it can improve the energy efficiency. Figure 2.17 illustrates the architecture of ORNoC. In this architecture, the IPs are connected by ring topology waveguides. In the example presented in this figure, the waveguide supports 6 wavelengths which can be used together as communication channels to improve the bandwidth. As we can see, the red wavelength can be reused to connect the IPs from A to H. In order to improve the scalability and bandwidth as well as the energy efficiency, the SWSR can be extended to MWSR as presented in the following section.

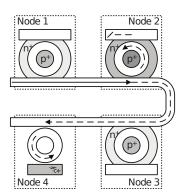

#### 2.3.2 Multiple Writers Single Reader

In MWSR, each IP source (processor core or cluster of cores) can send the data to all the remaining IPs but can only receive the data from one of them. This scheme of communication is illustrated in Figure 2.18 where an MWSR with four nodes is presented. In this example, Node 2 transmits data to Node 4. In this architecture, all of the three

FIGURE 2.18: A four-cluster single-bit MWSR bus

clusters (Nodes 1, 2, 3) can transmit to the remaining cluster (Node 4) using the same waveguide with different wavelengths.

A typical example of this kind of communication scheme is CORONA [105]. Figure 2.19

FIGURE 2.19: A Four Wavelength Data Channel Example of CORONA [105].

illustrates the architecture of CORONA in which MWSR is implemented. CORONA uses a 256-bit optical crossbar operating at 10 GHz to ensure communication between 64 clusters (each composed of four processor cores). CORONA combines arbitration and control flow into a single flow called optical token-based.

#### 2.3.3 Single Writer Multiple Readers

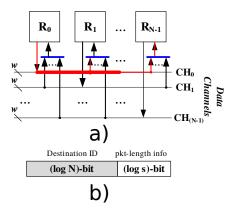

SWMR (also called "broadcast" communication scheme) is implemented by allowing the communication between one source IP and all remaining destination IPs [79, 48]. Figure 2.20 illustrates the SWMR communication scheme with the Firefly architecture. The source router  $R_0$  broadcasts data to all the other (N-1) routers. To ensure this communication, all the receivers must extract part of the optical energy from the waveguide, and all the photo-detectors must be aligned to the wavelength used by the sender. Therefore the laser power at the source side must be high enough to ensure that all receivers obtain sufficient optical power. In this case, more than N-1 times of the normal power must be produced by the sender to ensure detection on each receiver. In this communication scheme, by default, all the destinations are turned off. In step 1, by sending a reservation flit which contains the receiver address information and packet length (Figure 2.20.d), the corresponding receiver is turned ON to receive the data in step 2, while the others are turned OFF. Then, the power consumption needed for broadcast can be saved.

Figure 2.20: Implementations of the Firefly nanophotonic crossbar (a) Single-write-multi-read bus (SWMR), (b) Reservation flit [79].

#### 2.3.4 Multiple Writers Multiple Readers

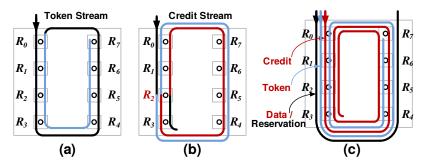

In MWMR, the combination of SWMR and MWSR is implemented in order to allow for all the source and destination IPs to access the interconnect medium. Compared to SWMR and MWSR, this communication scheme leads to the increase of optical insertion loss which is the main reason of high power consumption. Figure 2.21 illustrates the

FIGURE 2.21: (a) Token stream waveguide, (b) Credit stream waveguide, (c) Waveguides for all the three types of channels [78].

Flexishare architecture which uses a token-stream based arbitration network to assign the wavelengths. Figure 2.21.a shows the waveguide for the token streams which passes each router twice. Figure 2.21.b presents the credit streams in which the laser must be routed to the router distributing the credits first and then traverse all the routers twice, as highlighted with different colors.

### 2.4 Error Correction Codes to Improve Energy Efficiency

In this thesis, we present some methods that use error correction codes to improve energy efficiency and reliability of optical interconnects. Considering the power consumption of

optical devices, the implementation of ECC in a global communication path can be very interesting. In this section, we present the basic concept of ECC and the state of the art of this technique from different perspectives: Wireless Sensor Networks, Optical Communications, and On-Chip Optical Interconnect, respectively.

#### 2.4.1 Basic Concepts

Reliability and energy efficiency are the most important factors in digital communications. In such systems (digital communications, storage systems, etc.), error control is one of the most important techniques which contribute to the reliability and energy efficiency of the links. Hence, the use of error correction codes has become a critical problem in the design of such systems.

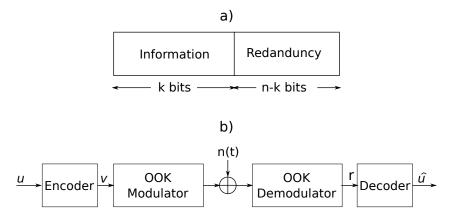

The basic concepts of ECC rely on the principle that some redundancy is added to the data to correct the errors which occur during the transmission. Figure 2.22.a shows

Figure 2.22: a) Concept of redundancy codes b) Example of a digital communication scheme [58]

the concept of block codes (systematic code<sup>1</sup> [58]) in which the right side (redundancy bits) is a function of the left side (information bits). Figure 2.22.b illustrates a coded digital communication in which a source sends the information bits (u), the encoder adds redundancy bits into the information bits. The data output of the encoder is called codeword (v) which consists of the information and redundancy bits (e.g., parity bits). During transmission through the medium, if some errors occur (due to the transmission noise), the decoder recovers the received bit (r) into the estimated information bits  $(\hat{u})$ .

<sup>&</sup>lt;sup>1</sup>In coding theory, a systematic code is any error-correcting code in which the input data is embedded in the encoded output.

#### 2.4.2 ECC in Wireless Sensor Networks (WSN)

Recently, there were many researchers focusing on error correcting codes for WSN. ECC has a very important role in this domain due to the error correction probability and energy efficiency properties. Studies of [36] and [93] examine the use of ECC in WSN for a range of ECC types which consist of both convolution and block codes. In addition, these publications provide the generic equation for the critical distance at which the ECC becomes energy efficient. Also, the implementation of several ECC schemes has been presented in these studies. In [106], Vuran et al. present the analysis and a comprehensive comparison between FEC (Forward Error Correcting), automatic repeat request (ARQ) and hybrid ARQ scheme in WSN. Recent researches focusing on convolutional and block codes for WSN are also presented in [98, 8, 41, 93].

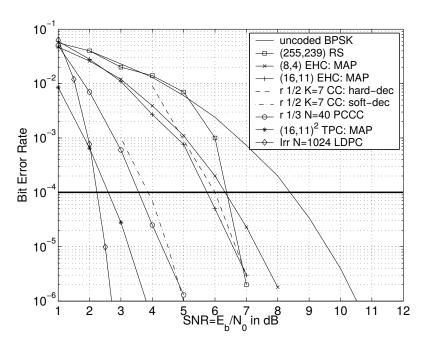

FIGURE 2.23: BER performance vs. SNR for several error-correcting codes [36].

Figure 2.23 compares the BER performance of some ECCs schemes [36]. As we can see in this figure, using ECC can provide significant lower SNR compared to an uncoded system.

#### 2.4.3 ECC in Optical Communications

ECC is considered as a typical approach used to improve the reliability and to reduce the power consumption in optical communications. In long-distance optical communications,

the development of ECC can be divided into three generations which correspond to the increase of ECC coding gain. In early day, D.Grover presents FEC in dispersion limited light-wave system which provides 2.5dB at BER =  $10^{-13}$  [31]. The first fully-fledged ECC for submarine optical transmission was deployed in the early 1990s. A typical example of the first generation is presented in [89] with Reed-Solomon codes RS(255,239). The second generation of FEC consists in the use of concatenated codes [30] for high-throughput DWDM submarine communications. The typical example of second generation FEC is RS(239,223) + RS(255,239) [68]. The most powerful FEC is the third generation which are based on soft decision decoding technique [67]. A comparison between the three

| Gen.     | Decision | Coding                                                         | Code rate | $NCG(dB) @10^{-13}$ |

|----------|----------|----------------------------------------------------------------|-----------|---------------------|

| $1^{st}$ | Hard     | Cyclic codes / Algebraic codes<br>e.g. RS(255,239)             | 0.93      | 5.8                 |

| $2^{nd}$ | Hard     | Concatenated codes e.g. $RS + BCH, RS + RS$                    | 0.93-0.79 | <10                 |

| $3^{rd}$ | Soft     | Soft-decision & Iterative decoding e.g. Block turbo code, LDPC | >0.80     | >10                 |

Table 2.1: Summary of three generations of FEC (data extracted from [67]).

generations of FECs is presented in Table 2.1 with the corresponding coding gain at  $BER = 10^{-13}$

#### 2.4.4 ECC for On-Chip Optical Interconnects

In optical interconnects (chip-to-chip interconnect or optical data link), ECC is also an approach to improve energy efficiency and reliability of communications links. In [75, 34, 70], the authors present the use of ECC based on ARQ to reduce the BER and optimize the bandwidth. In [34], the authors show the ability of FEC to relax the throughput and to improve the performance. The potential of FEC in two-dimensional optical data link with Golay codes to improve performance and reduce on-chip power consumption was demonstrated in [24]. For chip-to-chip optical interconnects, Jun Wang et al. present the comparison of different types of ECC using 90nm CMOS technology [107]. The experimental results presented in this paper conclude that ECC with Hamming code (87,80) is suitable for chip-to-chip optical interconnects. For on-chip interconnects, many methods of ECC using ARQ or Cyclic Redundancy Check (CRC) to provide a reliability optical link are presented in [73]. Also, Berger codes [6] are evaluated to detect

State of the Art

any number of unidirectional errors. However, Berger code implementations are too costly to become a good candidate for on-chip optical interconnects. In [26], a low complexity non-interactive BCH code<sup>2</sup> [15] is proposed to reduce the laser power and relax the stringent optical modulation amplitude requirements. This work is implemented using a 28 nm CMOS technology and results in 25% reduction of energy dissipation.

#### 2.5 Conclusions and Thesis Contributions

In this chapter, we first presented the state of the art of optical interconnects with various optical devices in three main parts: transmitter, medium, and receiver. Then, some architectures of existing ONoCs were introduced. With low-power consumption, low bandwidth, and high bandwidth property, optical interconnects show the ability to become an emerging candidate for future of on-chip interconnects. However, in order to limit the effect of optical losses and crosstalk noise and to improve energy efficiency, we propose in this thesis the use of error correcting codes. ECC is not only used to improve performance but also to reduce power needed for the laser due to its error-correcting ability. Considering the solutions proposed in the state of the art, we address the three major following problems in this thesis.

Energy efficiency on-chip optical interconnects based on the state of the art of Error Correcting Codes (ECC). The advantages of optical interconnects rely on the optical devices properties which provide high bandwidth, low latency and low-power consumption. However, due to the optical loss and crosstalk noise which can lead to errors occurring during the transmission, these optical devices can reduce the performance of the system. In this thesis, we take advantages of the ECC to provide an energy efficiency optical interconnect for 3D MPSoC. Our approach demonstrates some improvements of optical interconnects in terms of energy efficiency as well as communication reliability.

Design of high performance optical interface based on ECC. In this thesis, we propose a complete optical network interface for coded optical WDM ONoC. This

<sup>&</sup>lt;sup>2</sup>In channel coding theory, the BCH codes (Bose-Chaudhuri-Hocquenghem) form a class of cyclic error-correcting codes that are constructed using polynomials over a finite field (also called Galois field).

State of the Art

architecture of the interface leads to a simple design layout and allows for the adaptation of bandwidth and latency according to different communication strategies.

Optical network interface management unit. Based on the architecture of the optical network interface and the design of the laser driver which has been already addressed, we propose a management unit for the optical network interface. This ONI manager consists of several components, such as ONI configuration memory (which receives data from allocation protocol) and a controller (which is driven by allocated tasks and operating system).

In the next chapter, we model and analyze the optical loss and crosstalk noise which are two important factors contributing to the energy efficiency of the optical interconnect.

## Chapter 3

# Modeling and Analyzing Attenuation and Crosstalk in WDM ONoC

The attenuation and the crosstalk noise are very important factors contributing to the energy efficiency of the optical interconnect. The ONoC is constructed using MRs, which are one of the main sources of attenuation and crosstalk noise. In order to address the energy efficiency problem of optical interconnects, attenuation and crosstalk noise need to be explored and analyzed. This chapter is organized as follows. Section 3.1 introduces models of attenuation and crosstalk in ONoC. The architecture of CHAMELEON 3D ONoC is presented in Section 3.2. Section 3.3 details the fundamental analysis of attenuation and crosstalk noise at the device level. Based on this analytical model, Section 3.4 presents the analysis of crosstalk noise at the network level. Section 3.5 shows the results and discussion. Finally, Section 3.6 concludes this chapter.

#### 3.1 Introduction

The technology scaling down shows the potential of optical interconnects to replace the electrical interconnects with high-bandwidth and low-latency properties. Furthermore, in order to adapt to application requirements, WDM technology can help the designer to improve ONoC characteristics, and, in particular, to increase the bandwidth and

to reduce the latency. However, using the WDM technology leads to the appearance of attenuation and crosstalk noise between the signals which are transferred on different wavelengths. Depending on the architecture of the ONoC and the structure of the Optical Network Interface (ONI), the value of crosstalk noise and attenuation can be different. In [71], the author present an analysis model of attenuation and crosstalk noise in ONoC with three different topologies: Mesh, Folded-torus, and Fat-tree. In [20], Duong et al. present the analysis of crosstalk based on the SUOR ring topology.

This chapter proposes an analytical model of attenuation and crosstalk noise for both device level and network level in a WDM-based ONoC which is discussed in the next section. To address these problems and explore the contribution regarding energy efficiency, we first give an overview of CHAMELEON architecture. Secondly, we present the fundamental analysis of the signal power attenuation and crosstalk noise at the device level. Based on the model at the device level and the architecture of the network, we develop an analytic model, providing the worst case of attenuation and crosstalk for different network sizes of the CHAMELEON's architecture. The models proposed in this chapter are used in Chapter 4 for energy efficiency optimization and in Chapter 5 for the design of the ONI manager unit.

#### 3.2 Chameleon Architecture

Relying on the potential of optical interconnect properties with high bandwidth and low latency, ONoC is considered as one of the emerging solutions for future on-chip interconnects. In this section, we present a new version of ONoC architecture which is named CHAMELEON<sup>1</sup> [51] with three following features: a simple architecture, the optical network interface eases layout synthesis and run-time configuration, and various communication schemes. We step by step present these features in the following subsections.

#### 3.2.1 Architecture Overview

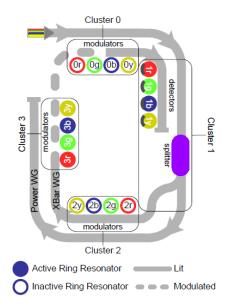

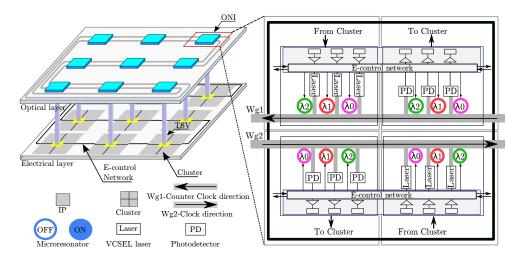

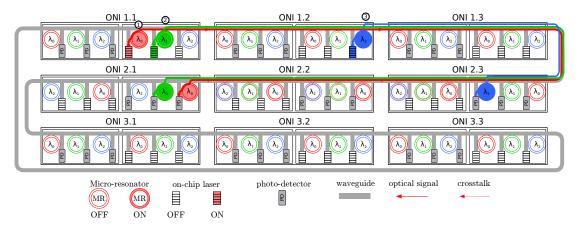

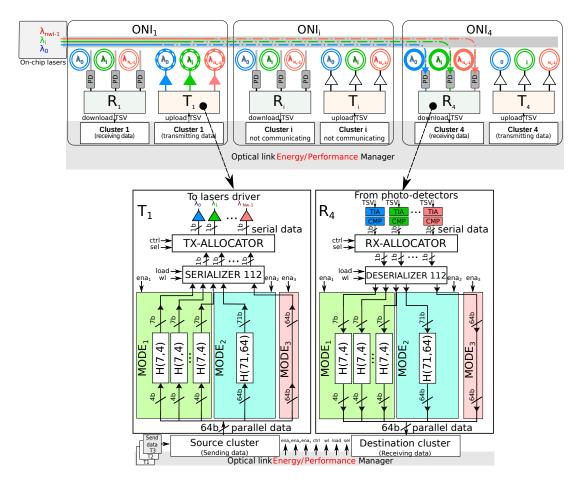

Figure 3.1 illustrates the Chameleon architecture and its optical network interface (ONI). Chameleon consists of two layers: an electrical layer implementing the IP network and an optical layer performing the optical interconnect. The ONI is located between the

<sup>&</sup>lt;sup>1</sup>CHAMELEON: Channel Efficient Optical Network-on-Chip – Lyon Institute of Nanotechnology

FIGURE 3.1: Chameleon optical interconnect and its Optical Network Interface (ONI)

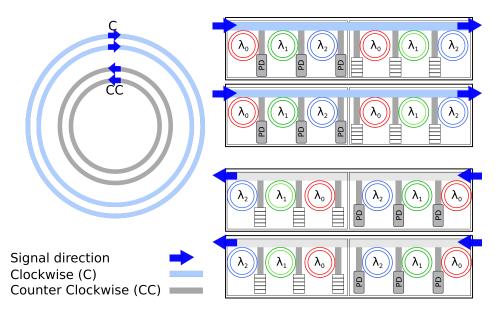

optical layer and the electrical layer. It consists of ring-based waveguides and a set of optical components such as Micro-Resonators (MRs), on-chip laser sources, photo-detectors, TSV, ONI manager unit. To improve the scalability and the bandwidth of the channel, multiple waveguides are used in both directions (clockwise and counter-clockwise). By using multiple-waveguides, we can reduce the communication distance to minimize the worst-case of attenuation of ONoC. In the electrical layer, the unit management is implemented to configure the MRs and the laser power level according to communication requirements. Compared to the other existing ONoCs, one of the most potential features of CHAMELEON is the regularity of its architecture and the possibility of reconfiguration at run-time. Indeed, the most straightforward architecture of ONI can lead to the ease in layout synthesis, and the run-time configuration feature contributes to the higher energy efficiency. Moreover, the combination of the reuse of wavelengths and WDM technology can increase the bandwidth and reduce the power consumption of the overall system.

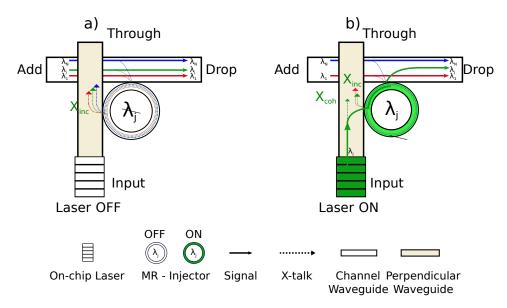

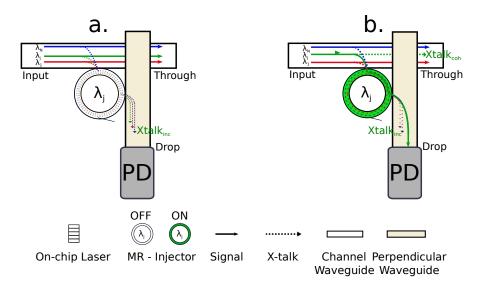

#### 3.2.2 Optical Network Interface Architecture

In Chameleon, the ONI architecture is one of the most important factors that impact overall system performance. Each ONI is composed of a transmitter and a receiver, as described in Figure 3.2. The transmitter is composed of on-chip lasers and MRs, which operate as injectors (to inject the signal into the waveguide). The receiver part is composed of photo-detectors and MRs, which operate as ejectors (to drop the signal from the waveguide and guide it to the photo-detector). MRs are configured to be switched

ON or switched OFF by an ONI management network located in the electrical layer (see Chapter 5) to perform the three following operations.

FIGURE 3.2: Illustration of the three operations in an ONI: injection, ejection and pass-through

- Injection. By turning ON the MR of the transmitter part, the light emitted by the

laser is injected into the channel waveguide. The light then propagates until reaching another MR (at destination ONI) which extracts the light from the waveguide.

Figure 3.2 illustrates the injection of a signal with wavelength λ<sub>1</sub> (in green color)

into the waveguide.

- **Ejection.** Optical signals propagating along the waveguide cross the MRs at the receiver side. The signals, whose wavelength matches with the wavelength of ON state MRs, are dropped into the perpendicular (or parallel) waveguide and reach the photo-detector. Figure 3.2 illustrates the ejection of signals with wavelengths  $\lambda_0$  and  $\lambda_1$  from the waveguide (in red and green colors).

- Pass-through. In this case, all the MRs in the transmitter and the receiver parts are in the OFF state. An optical signal propagating along the waveguide will not be ejected, and no optical signal with the same wavelength will be injected for the sake of coherency and to avoid interference. Then, the signal crosses the ONI without being modified, as represented by the signal at wavelength  $\lambda_2$  (in blue color) in Figure 3.2.

#### 3.2.3 Communication Schemes

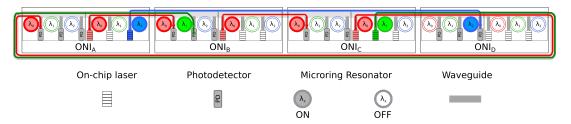

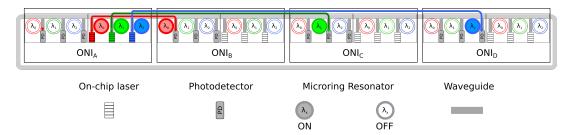

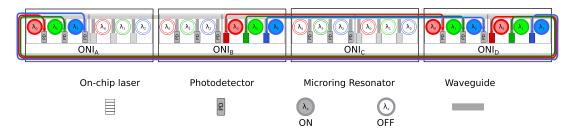

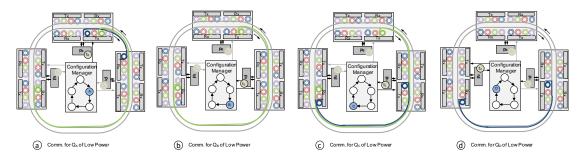

To support the communication requirements, an ONI manager can configure the MRs at run-time. Therefore, Chameleon provides many communication schemes corresponding to the application requirements: Single Writer Single Reader (SWSR), Single Writer Multi Reader (SWMR), Multi Writer Single Reader (MWSR), and High-Bandwidth Channel (HBC), as illustrated in Figure 3.3, Figure 3.4, Figure 3.5, and Figure 3.6.

SWSR (Single Writer Single Reader): By configuring the MRs, the point-to-point communication can be opened by using one or several wavelengths. Furthermore, by reusing one given wavelength, the channel partitioning can be obtained by performing multiple independent communications in the same waveguide. For instance, Figure 3.3 shows the point-to-point communications between:  $ONI_A \rightarrow ONI_B$ ,  $ONI_B \rightarrow ONI_C$  and  $ONI_C \rightarrow ONI_A$  using  $\lambda_0$  (in red);  $ONI_C \rightarrow ONI_B$  using  $\lambda_1$  (in green);  $ONI_A \rightarrow ONI_D$  using  $\lambda_2$  (in blue), respectively.

FIGURE 3.3: Single Writer Single Reader communication scheme

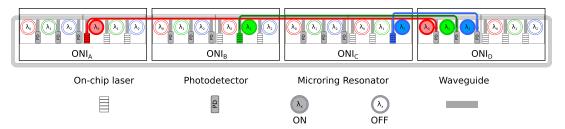

SWMR (Single Writer Multi Reader): This communication scheme can be implemented in Chameleon by allowing the communication between one ONI source and all the remaining ONIs. Figure 3.4 illustrates the SWMR communication between  $ONI_B$  with  $ONI_C$ ,  $ONI_D$ ,  $ONI_A$  by using  $\lambda_0$  (in red),  $\lambda_1$  (in green),  $\lambda_2$  (in blue), respectively.

Figure 3.4: Single Writer Multi Reader communication scheme

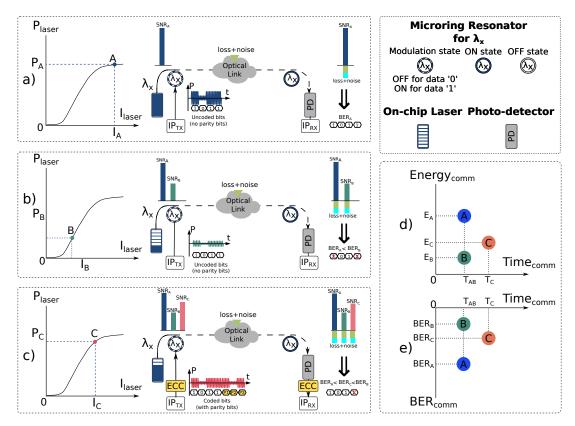

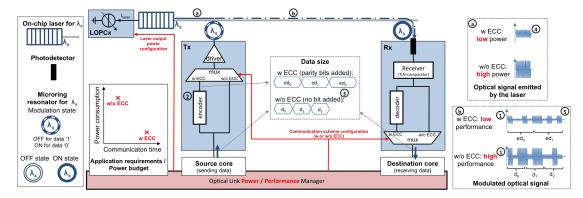

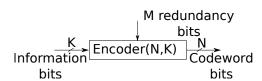

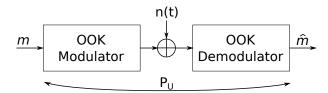

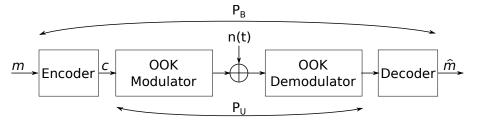

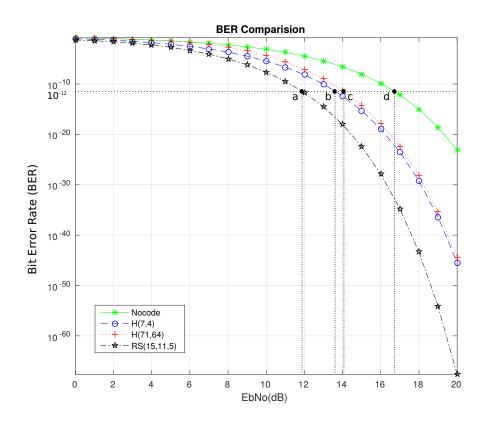

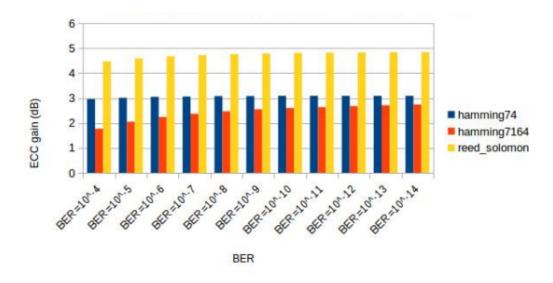

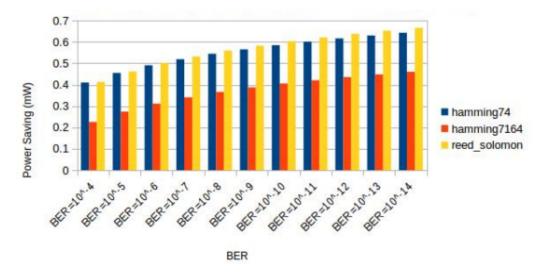

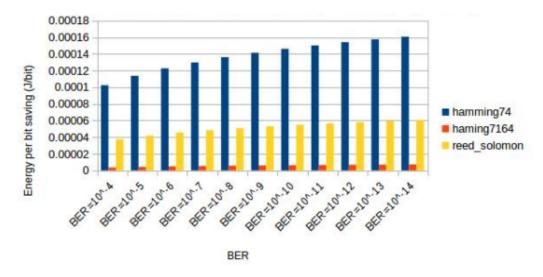

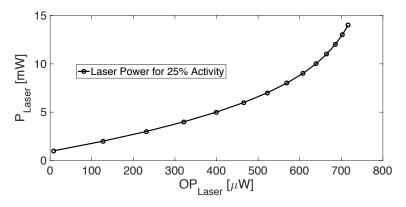

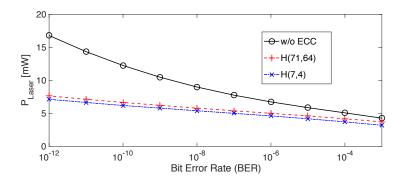

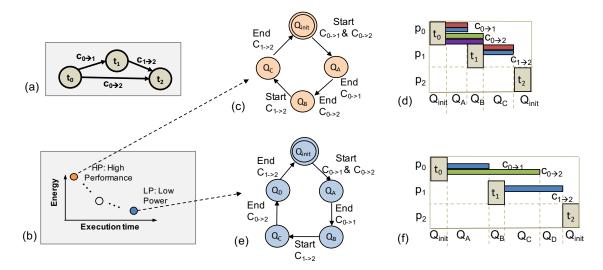

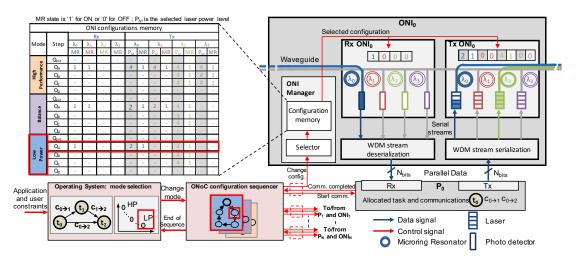

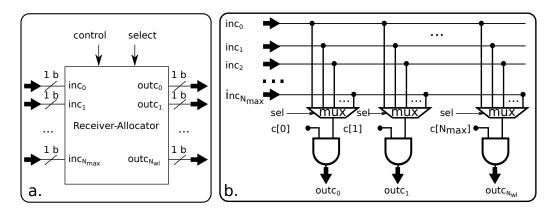

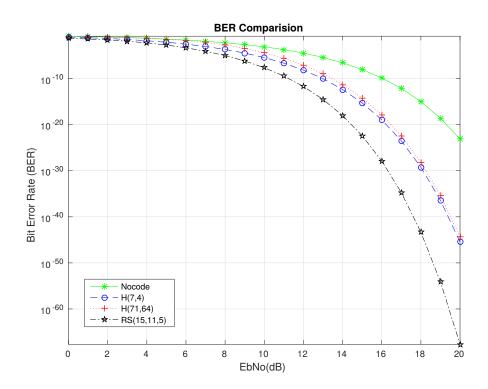

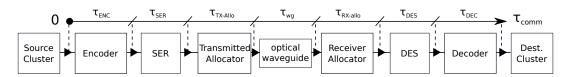

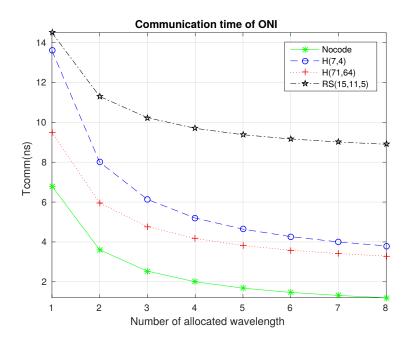

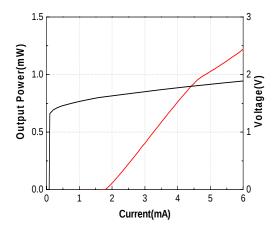

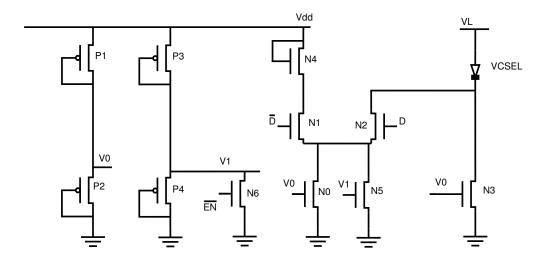

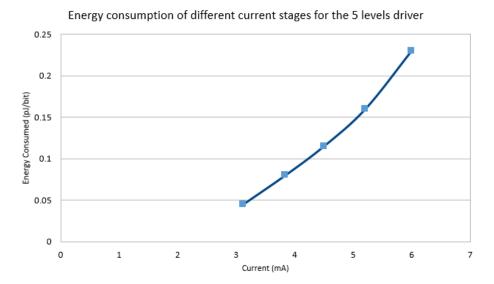

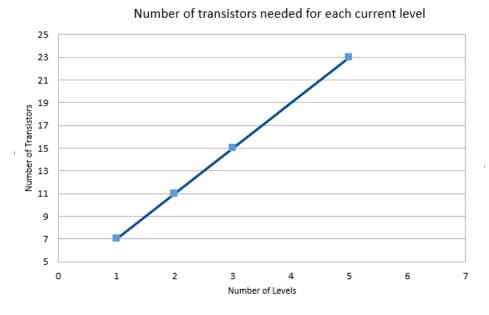

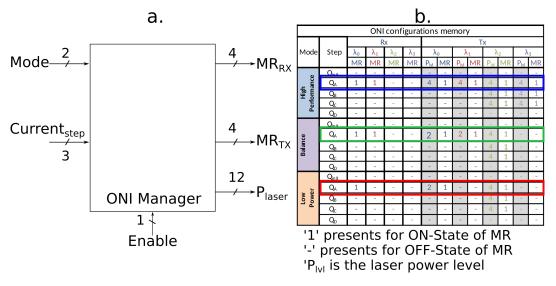

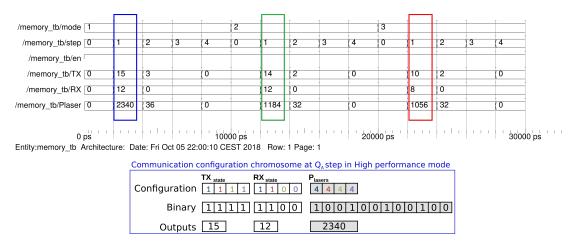

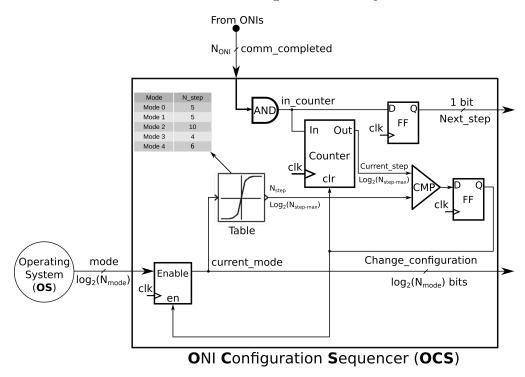

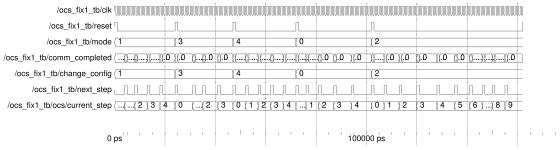

MWSR (Multi Writer Single Reader): The MWSR communication scheme can be implemented by allowing the communication between several ONI sources and a given ONI destination. This communication scheme is illustrated by Figure 3.5 in which the  $ONI_A$ ,  $ONI_B$ , and  $ONI_C$  respectively communicate with  $ONI_D$  by using  $\lambda_0$  (in red),  $\lambda_1$  (in green),  $\lambda_2$  (in blue), respectively.