# Minimising communication costs impact when scheduling real-time applications on multi-core architectures

Benjamin Rouxel

## ▶ To cite this version:

Benjamin Rouxel. Minimising communication costs impact when scheduling real-time applications on multi-core architectures. Computer Science [cs]. Université de Rennes 1, 2018. English. NNT: . tel-01945456v2

## HAL Id: tel-01945456 https://inria.hal.science/tel-01945456v2

Submitted on 21 Dec 2018  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITE BRETAGNE LOIRE MATHSTIC

# THÈSE DE DOCTORAT DE

L'UNIVERSITE DE RENNES 1 COMUE UNIVERSITE BRETAGNE LOIRE

Ecole Doctorale N°601 Mathématique et Sciences et Technologies de l'Information et de la Communication Spécialité : Informatique Par

# « Benjamin ROUXEL »

### « Minimising communication costs impact when scheduling real-time applications on multi-core architectures »

Thèse présentée et soutenue à RENNES , le 19 Décembre 2018 Unité de recherche : Irisa – UMR6074

#### Rapporteurs avant soutenance :

Claire Pagetti Ingénieur de recherche ONERA, Toulouse Matthieu Moy Maître de conférences Université de Lyon

#### Composition du jury :

| Président :<br>Examinateurs : | Daniel Chillet Professeur ENSSAT Lannion – Université Rennes 1<br>Joël Goossens Professeur Université Libre de Bruxelles<br>Frédéric Pétrot Professeur ENSIMAG, Grenoble |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dir. de thèse :               | Isabelle Puaut Professeur Université Rennes 1                                                                                                                            |

| Co-dir. de thèse :            | Steven Derrien Professeur Université Rennes 1                                                                                                                            |

Il vaut mieux se tromper en allant de l'avant que d'avoir raison en reculant. par Frédéric Dard

| Résumé de thèse 7 |                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                        |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Int               | Introduction                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                        |  |

| 1                 | 1.1 Ta<br>1.2 Pi<br>1.3 Tc<br>1.4 Ta<br>1.5 W<br>1.6 R<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.                                                         | eal-time systems and multi-core platforms         ask models and their expressiveness         redictable multi-core architectures         owards parallel and predictable execution models         owards parallel and predictable execution models         ask and Inter-core communication         Vorst-case execution time estimation         deal-time scheduling: a state of the art         .6.1       Classification of single-core schedulers         .6.2       Multi-core partitioned scheduling         .6.3       Multi-core global scheduling         .6.4       Multi-core hybrid scheduling         .6.5       Shared resource management on single-core and multi-core architectures | <ol> <li>17</li> <li>18</li> <li>21</li> <li>24</li> <li>26</li> <li>28</li> <li>29</li> <li>29</li> <li>30</li> <li>31</li> <li>32</li> <li>32</li> <li>33</li> </ol> |  |

| 2                 | 2.1 Ba<br>2.2 So<br>2.3 So<br>2.3 So<br>2.<br>2.4 Ea<br>2.<br>2.4 Ea<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>2. | ic static scheduling frameworks with worst-case contention         asic predictable multi-core architectures         oftware Model         .2.1 Inter-core communication         .2.1 Inter-core communication         .3.1 Example         .3.2 Integer Linear Programming (ILP) formulation         .3.3 Forward List Scheduling algorithm         .4.1 Scalability of the ILP formulation         .4.2 Quality of the heuristic compared to the ILP         .4.3 Impact of $T_{slot}$ on the schedule         .5.1 Example                                                                                                                                                                         | <b>35</b><br>36<br>38<br>39<br>40<br>41<br>44<br>46<br>47<br>48<br>49<br>50                                                                                            |  |

| 3                 | 3.1 M<br>3.2 In<br>3.3 R<br>3.3 3.<br>3.4 E                                                                                                        | uting the precise contention to build contention-aware schedules         Motivating example         Inproving worst-case communication cost         Resource-aware scheduling techniques         .3.1         Integer Linear Programming (ILP) formulation         .3.2         Forward List Scheduling algorithm                                                                                                                                                                                                                                                                                                                                                                                     | <b>51</b><br>52<br>54<br>56<br>56<br>58<br>62<br>63                                                                                                                    |  |

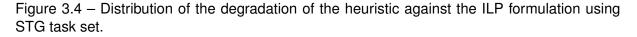

|                      | <ul><li>3.4.2 Quality of the heuristic compared to worst-contention communications</li><li>3.4.3 Quality of the heuristic compared to contention-free communications</li></ul> | 64<br>64 |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| 3.5                  | Related work                                                                                                                                                                   | 65       |  |

| 3.6                  |                                                                                                                                                                                | 66       |  |

| 4 Hidi               | ing communication latencies in contention-free schedules                                                                                                                       | 69       |  |

| 4.1                  | Hardware support                                                                                                                                                               | 70       |  |

| 4.2                  | Software & execution model support                                                                                                                                             | 71       |  |

| 4.3                  | Motivating example                                                                                                                                                             | 71       |  |

| 4.4                  | SPM allocation scheme                                                                                                                                                          | 74       |  |

| 4.5                  | Non-blocking contention-free scheduling techniques                                                                                                                             | 75       |  |

|                      | 4.5.1 Integer Linear Programming (ILP) formulation                                                                                                                             | 75       |  |

|                      | 4.5.2 Forward List Scheduling algorithm                                                                                                                                        | 79       |  |

| 4.6                  | Experiments                                                                                                                                                                    | 83       |  |

|                      | 4.6.1 Quality of the heuristic compared to the ILP                                                                                                                             | 83       |  |

|                      | 4.6.2 Blocking vs non-blocking communications                                                                                                                                  | 84       |  |

|                      | 4.6.3 Impact of fragmentation strategy                                                                                                                                         | 86       |  |

|                      | 4.6.4 Impact of topological sorting algorithm                                                                                                                                  | 88       |  |

| 4.7                  | Related Work                                                                                                                                                                   | 88       |  |

| 4.8                  |                                                                                                                                                                                | 90       |  |

| Conclu               | sion                                                                                                                                                                           | 91       |  |

| Appen                | dices                                                                                                                                                                          | 94       |  |

| STF                  | 2RTS benchmark suite                                                                                                                                                           | 94       |  |

| Bibliog              | raphy                                                                                                                                                                          | 95       |  |

| List of              | List of Figures                                                                                                                                                                |          |  |

| List of Algorithms   |                                                                                                                                                                                |          |  |

| List of Publications |                                                                                                                                                                                |          |  |

# **R**ÉSUMÉ DE THÈSE

L'année 1969 marqua le point culminant de la course à l'espace lorsque Neil Armstrong, Buzz Aldrin et Michael Collins firent un grand pas pour l'humanité lorsqu'ils marchèrent sur la Lune. Leur voyage commença avec le lancement de la fusée Saturn V qui est considéré comme le premier système critique. Pour assurer son contrôle, cette fusée inclue un ordinateur de guidage (Apollo Guidance Computer – AGC) qui exécute un système d'exploitation tempsréel. Celui-ci permettait aux astronautes d'entrer des commandes simples afin de commander la fusée. L'architecture matérielle inclue, entre autres, un processeur 16-bits simple-cœur offrant 64 Koctets de mémoire approximativement, et opère à une fréquence de 2,048 MHz<sup>1</sup>. Une comparaison naïve serait d'opposer ces caractéristiques techniques avec les téléphones portables intelligents de notre époque. En effet, ceux-ci offrent une puissance de calcul mille fois supérieure à celle qu'il a fallu pour envoyer des astronautes sur la Lune, et surtout pour les récupérer en un seul morceau. Depuis lors, la demande de puissance de calcul n'a cessé d'augmenter, amenant les fabricants de matériels a continuellement amélioré leurs processus de fabrication des puces informatiques. Les deux principales améliorations possibles ont pendant longtemps été l'augmentation de la densité des transistors et l'augmentation de la fréquence d'horloge. Ces augmentations suivirent la loi de Moore [Sch97] jusqu'en 2004, où elles atteignirent une limite technologique connue sous le nom du Mur de Puissance (Power Wall) [Kur01].

À cause du Mur de Puissance, l'augmentation de la densité et de la fréquence ne sont donc plus possible avec la technologie actuelle. La solution trouvée par les constructeurs, afin continuer d'augmenter la puissance de calcul des processeurs, est d'accroître le nombre de cœurs à l'intérieur d'une même puce. Il est dorénavant très facile de trouver des processeurs commerciaux grand public avec 4, 8 cœurs, ou même plus. Par exemple, les processeurs de la marque Intel<sup>©</sup> séries Core™i[3-9] contiennent de 2 à 18 cœurs. Les systèmes critiques ne peuvent échapper à l'évolution des processeurs, et, peu à peu, intègrent les processeurs multi/pluri-cœurs au sein de leur plateforme dans des domaines tel que l'automobile, l'aviation, ou l'espace [BDN+16; HMC+16].

L'informatique temps-réel-dur portent sur les applications calculant non seulement le bon résultat, mais, et encore plus important, qui le calculent dans le temps imparti. En plus des contraintes imposées aux systèmes classiques (e.g. performance, énergie), les systèmes temps-réels-dur ajoutent des contraintes temporelles (eg. temps de relâche, échéances, ...). De plus, manquer une contrainte temporelle, dans un système temps-réel-dur, mène à un échec total du système, ce qui peut avoir des conséquences désastreuses. Par exemple, dans le domaine de l'aviation, un manquement d'échéance peut causer la perte de vies humaines ; dans le domaine de l'aéro-spatiale, des milliards de dollars peuvent être gâchés avec le satellite brûlant inopinément dans l'atmosphère.

Concevoir un système temps-réel-dur nécessite des garanties strictes et plus d'attention que pour tout autre système, en particulier en ce qui concerne les contraintes temporelles. Afin d'obtenir les garanties les plus fortes, les performances pire cas sont calculées *a priori* avec,

<sup>1.</sup> https://en.wikipedia.org/wiki/Apollo\_Guidance\_Computer

entre autres, l'estimation statique du plus long temps d'exécution (Worst-Case Execution Time – WCET) et de politiques d'ordonnancement statiques. Les plates-formes multi-cœurs sont une solution très attrayante pour la mise en œuvre de systèmes temps-réel-dur. Lorsque ces plateformes sont spécifiquement conçues dans un souci de prévisibilité, elles offrent à la fois de bonnes performances et la possibilité de détermine des performances pire cas précises. De plus, les applications parallèles permettent d'exploiter pleinement toutes les ressources disponibles au sein des architectures multi-cœurs. La meilleure représentation pour les applications parallèles fournit explicitement à la fois les dépendances et les concurrences entre les tâches, car ces informations sont obligatoires pour calculer de manière statique des performances pire des cas précises. Avant d'exécuter une application sur une plateforme multi-cœur, une étape obligatoire est de décider sur quel cœur et quand exécuter les tâches de l'application. Un ordonnanceur place les tâches sur les cœurs, et ordonnent leur exécution sur le cœur. Les décisions de placement et d'ordonnancement ont un impact sur le temps d'exécution global de l'application sur les processeurs multi-cœurs. Le point central de cette dissertation est la construction d'une politique d'ordonnancement dont l'objectif est de minimiser la taille de l'ordonnancement.

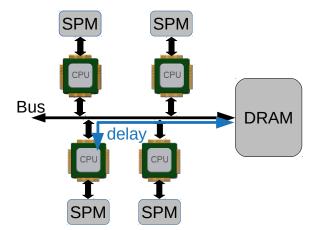

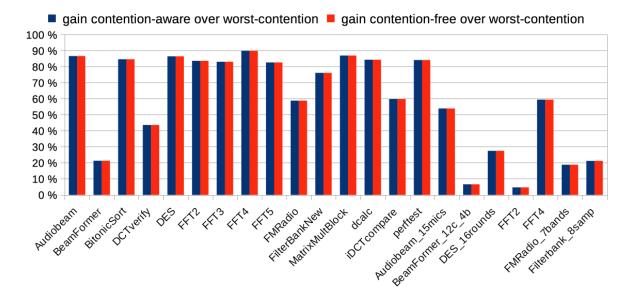

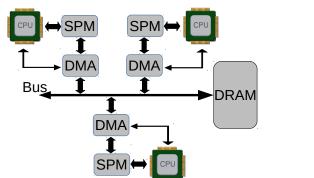

Cette thèse présente deux méthodes d'ordonnancement statiques ayant pour but d'optimiser les performances globales d'une application donnée tout en garantissant des contraintes temporelles fortes. Elles peuvent être classées comme partitionnées statiques et non préemptives. La mise en œuvre des stratégies d'ordonnancement proposées inclut à la fois une formulation à base de programmation en nombre entier (Integer Linear Programming - ILP) et un algorithme approximatif basé sur une heuristique gloutonne similaire à l'ordonnancement par liste. Les formulations ILP fournissent une description non ambiguë du problème étudié, et servent également de base pour évaluer la gualité de la proposition d'algorithme heuristique. Les deux stratégies d'ordonnancement ciblent des plateformes multi-cœurs dans lesquelles, les cœurs sont inter-connectés par un bus arbitrée avec une politique de tournoi à la ronde juste (FAIR-Round-Robin). Chaque cœur est également supposé avoir accès à une mémoire locale privée, ou mémoire bloc-notes (ScratchPad Memory - SPM). Dans cette dissertation, les applications parallèles sont considérées représentées sous forme de graphiques de tâches acycliques (Directed Acyclic Graphs - DAG). Afin de tirer parti au mieux d'architectures à mémoire bloc-notes, le modèle d'exécution utilisé est Acquisition Exécution Restitution (AER) [MNP+16]. Il force les accès mémoire à être isolés des phases de calcul. Cette séparation permet d'abord de lire les données d'entrée depuis la mémoire globale dans la SPM, puis d'exécuter le code sans interférence avec les autres cœurs, et enfin d'écrire les données produites de la SPM vers la mémoire externe. Dans les approches défendues dans cette thèse, les tâches de communication sont supposées ne transférer que des données via la mémoire principale (les communications de SPM à SPM ne sont pas autorisées). Dans un premier temps, les communications sont limitées à un mode bloquant, Chapitres 2 et 3, puis le mode non bloquant est pris en charge au Chapitre 4. Ce travail a pour objectif essentiel de minimiser l'impact de ces communications sur la durée globale d'exécution de l'application.

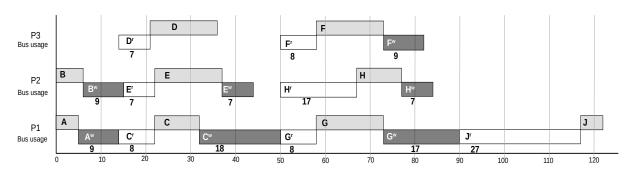

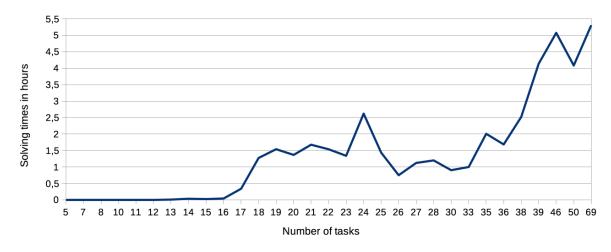

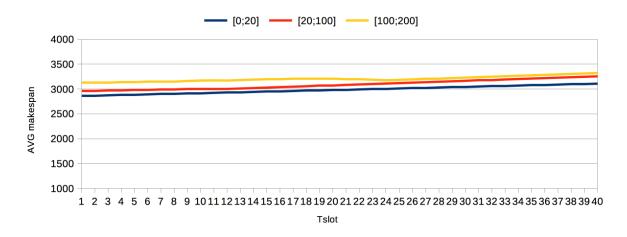

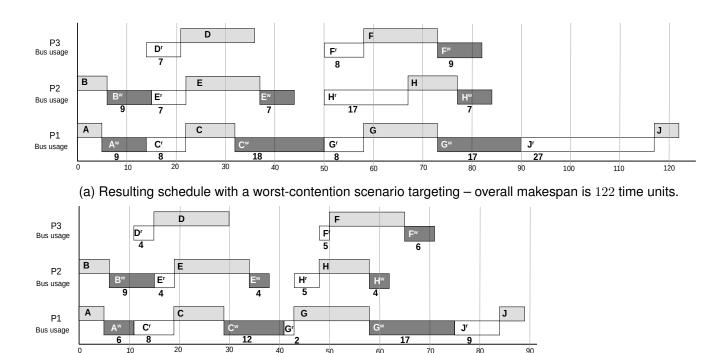

Avec les architectures multi-cœurs, plusieurs cœurs peuvent accéder au bus partagé en même temps. Par conséquent, le calcul des latences de transfert, entre les cœurs et la mémoire hors puce via le bus, doit prendre en compte un délai de contention. Ce délai dépend généralement du nombre de cœurs en conflit pour l'accès au bus partagé. Le calcul des latences de communication dans le Chapitre 2 utilise un délai de contention dans le cas le plus défavorable, qui considère toujours que tous les autres cœurs demandent également à accéder au bus partagé, au même instant. Même si très pessimiste, ce cas défavorable fournit une base de référence permettant la comparaison lors de l'ajout, à l'ordonnancement, de conscience des conflit dans le Chapitre 3. Une évaluation empirique montre que la résolution d'un problème d'ordonnancement, tout en recherchant un optimum exact ne s'adapte pas aux grand problèmes (comme prévu). Pour les cas de test impliquant un grand nombre de tâches, le seul moyen d'obtenir une solution consiste à s'appuyer sur une méthode approximative. Ensuite, une évaluation empirique, dans la Section 2.4.3, montre que le paramètre spécifique  $T_{slot}$  d'un bus FAIR Round-Robin, a un impact négligeable sur la durée de l'ordonnancement.

Le modèle de conflit dans le cas le plus défavorable est un choix sûr par construction, mais il conduit à une sur-approximation importante qui est ensuite affinée dans le Chapitre 3. Dans ce chapitre, la méthode d'ordonnancement proposée utilise la connaissance de la structure de l'application conjointement à celle de l'ordonnancement courant, pour affiner, au moment de la conception et pour chaque phase de communication, la pire quantité réelle d'interférences. Cette méthode s'est révélée efficace avec l'évaluation empirique de la section 3.4 montrant une amélioration moyenne de 59% par rapport au pire des scénarios. Toutefois, des expériences ont également montré que, dans la plupart des cas, le fait de permettre à l'ordonnanceur de choisir entre éviter les contentions dans l'ordonnancement ou les autoriser avec un calcul précis de celles-ci, aboutissait à des ordonnancement exempts de conflits. Cette observation doit cependant être mise en perspective avec le fait que les travaux présentés ne considèrent que des graphes de tâches avec la sémantique AER.

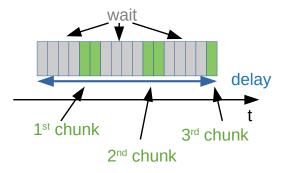

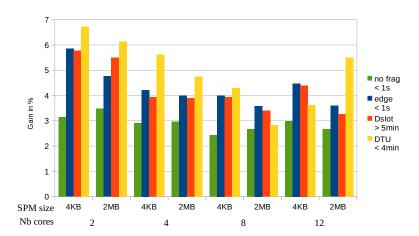

Afin de poursuivre l'affinement des délais de contention, la contribution du Chapitre 4 décrit une méthode d'ordonnancement statique générant des ordonnancements sans contention et dont les communications sont non-bloquantes. L'ordonnanceur tire parti du moteur d'accès direct à la mémoire (Direct Memory Access engine - DMA) et de la SPM à double accès, afin de masquer les accès au bus lorsque l'unité de traitement est occupée à effectuer des calculs. L'approche présentée fragmente les communications pour augmenter les possibilités de chevauchement avec les calculs. L'évaluation empirique montre que, comparée à un scénario sans chevauchement, cette approche améliore la longueur d'ordonnancement 4% en moyenne sur les applications en flux-continu (8% sur les graphes de tâches synthétiques). Néanmoins, des expériences montrent également que le fait de permettre différentes stratégies de fragmentation peut augmenter encore le gain; lorsque l'on évite des frais de transfert minimes, jusqu'à 6,5% avec les applications de flux-continu. En outre, différentes méthodes de tri provenant de l'algorithme heuristique sont évaluées, mais aucunes d'elles ne semblent surpasser aucunes autres. Enfin, l'implémentation réalisée avec succès est résumée, elle porte sur la réalisation des ordonnancements générés par l'heuristique avec pour cible une grappe de la plateforme Kalray MPPA Bostan [DVP+14]. Sur cette plate-forme, le gain observé pour l'ordonnancement avec fragmentation par arc du graphe, par le paramètre  $D_{slot}$ , ou par DTU en mode non bloquant est respectivement : 36%, 22% et 24%. Avec des gains au-delà de nos attentes, cette mise en œuvre valide les avantages de notre stratégie d'ordonnancement.

## Contenu de la thèse

Le reste de cette thèse est divisé en quatre chapitres principaux, résumés comme suit :

**Chapitre 1** introduit le contexte de cette thèse à travers une revue des systèmes temps-réel et des plateformes multi-cœurs. Cela commence par les modèles d'applications fondamentaux et leur expressivité. Ensuite, des plateformes multi-cœurs sont présentées, dans lesquelles la prévisibilité et le déterminisme sont des caractéristiques essentielles. Des caractéristiques similaires sont ensuite prises en compte dans les modèles d'exécution qui spécifient comment les applications parallèles sont exécutées sur des plateformes multi-cœurs. Enfin, un examen des travaux précédents sur les stratégies d'ordonnancement / placement pour les applications en temps réel sur des architectures mono-cœurs / multi-cœurs est présenté.

**Chapitre 2** présente la infrastructure d'ordonnancement extraite de la littérature et utilisée comme base pour les contributions suivantes. Notre infrastructure peut calculer un placement et un ordonnancement statiques pour une application s'exécutant sur un multi-cœur en tenant compte d'hypothèses initiales simples (par exemple, le cas le plus défavorable de conflits). Toutes ces hypothèses restrictives sont abandonnées dans les chapitres suivants, à savoir la prise de conscience de la contention dans le Chapitre 3, et l'évitement des conflits dans le Chapitre 4. L'infrastructure est d'abord détaillée avec une formulation ILP (Integer Linear Programming) et à l'aide d'un modèle de contention projetant le cas le plus défavorable. Ensuite, un algorithme basé sur l'ordonnancement par liste est présenté. Il utilise le même modèle de conflits mais permet de mieux s'adapter aux grandes applications. Certaines expériences initiales démontrent la viabilité de l'heuristique.

**Chapitre 3** décrit une nouvelle technique permettant de prendre en compte la quantité réelle d'interférences lors de l'ordonnancement hors ligne. Il présente la méthodologie et sa mise en œuvre à la fois via une technique demandant un calcul intensif mais fournissant des résultats exacts, et via un algorithme plus rapide mais fournissant des résultats approximatifs. Enfin, les expériences démontrent que la sur-approximation de l'algorithme est limitée, suivi des gains de la méthode opposé à celle du chapitre **??** qui inclue un scénario de conflit pire cas. La dernière expérience discute les améliorations de cette méthode par rapport à une méthode existante adaptée dont les ordonnancements sont sans conflit.

**Chapitre 4** relâche certaines des hypothèses restrictives sur le matériel afin de s'appuyer sur une plateforme plus réaliste. Tout d'abord, la restriction sur la taille de la mémoire SPM (ScratchPad Memory) est supprimée tandis que le temps de latence pour transmettre des données sur le bus est masqué. Pour augmenter les possibilités de masquage, la communication est fragmentée. Les expériences valident d'abord le comportement de l'heuristique par rapport à la formulation ILP. Ensuite, le gain est exprimé par rapport à l'infrastructure de base du Chapitre 2 incluant un scénario de communication non-masquant et non-fragmenté. La dernière expérience traite de la taille des fragments utilisée dans les stratégies de planification.

**Chapitre 5** conclut cette thèse en résumant toutes les contributions présentées. Des travaux futurs possibles sont ensuite introduits afin d'optimiser davantage l'ordonnancement des systèmes temps-réel-dur sur du architectures multi-cœurs.

# INTRODUCTION

In 1969, Neil Armstrong, Buzz Aldrin and Michael Collins made a giant leap for mankind when walking on the moon. Their journey started with the launch of the rocket *Saturn V* which is considered as the first safety-critical system. The rocket included the Apollo Guidance Computer (AGC) which ran a real-time operating system. This system enabled astronauts to enter simple commands to control the rocket. The hardware architecture included, among other devices, a 16-bits single-core processor which had approximately 64 Kbytes of memory and operated at 2.048 MHz<sup>2</sup>. As a naive comparison, modern smartphones offer a thousand times more computing capacity than it was required to launch and safely return astronauts from the moon. Computational demand has kept increasing ever since, and hardware manufacturers continuously improved chip manufacturing techniques, both in terms of transistors density and clock frequency. Until 2004, this growth followed the Moore's law [Sch97]. Until it reached a technological limit, known as the Power Wall [Kur01]. This limit initiated from power leakage and heat of the chip which both increase with the diminishing size and the raise of transistors frequency.

Due to the Power Wall, increasing the density and frequency was not an option anymore. The solution found to augment the processors computational power without increasing the frequency was to extend the number of cores within a chip. It is now very common to find commercial mainstream processors with 4, 8 or more cores. For example, the Intel<sup>©</sup> Core<sup>™</sup>i[3-9] includes from 2 to 18 cores. Critical systems cannot escape from this processors' evolution and now increasingly include multi-/many-core processors at the heart of their hardware, such as automotive, avionic or space industries [BDN+16; Per17]. Therefore, the innate idea of this dissertation integrates this evolution by targeting multi-core usage in safety-critical systems.

Real-time computing refers to applications that compute correct results but, and more importantly, applications that perform *on-time*. As pictured in Figure 1, their goal is not to be fast, but rather to be *on-time*. In addition to usual system constraints (e.g. performance, energy), real-time systems include timing constraints that need to be satisfied by the system in order to provide a safe computation. Examples of timing constraints are, among others, release time, deadline, worst-case execution time, .... In a safety-critical system with timing constraints, failing one constraint can lead to disastrous consequences. For example, in the avionic domain, a timing constraint failure can cause a waste of human lives in a crash; for a satellite, billion euros might end wasted with the satellite burning into the atmosphere. Depending on their criticality level, real-time systems can be classified in three categories [SR94]:

<sup>2.</sup> https://en.wikipedia.org/wiki/Apollo\_Guidance\_Computer

**Hard**: missing a timing constraint is a total system failure.

**Firm**: infrequent timing constraint misses are tolerable, but may degrade the system's quality of service.

**Soft**: the usefulness of a result degrades after its deadline, thereby degrading the system's quality of service

Figure 1 – Real-time is not real-fast

Designing a hard real-time system requires more attention and strict guarantees, especially on timing constraints, than any other systems, from Reineke [RGB+07] : "An important part in the design of hard real-time systems is the proof of punctuality which is determined by the worst-case performance of the system.". In this context, the worst-case performance corresponds to the execution scenario where the time to execute the software on the hardware is the longest possible. In addition, to enforce the strongest guarantees, this worst-case performance is computed a priori, which means without actually executing the software on the platform (this is also known as a *static* approach). However, determining the worst-case performance is extremely tedious, especially when determined a priori. Main issues originate from the absence of detailed information on the hardware parts. Indeed, in modern complex multi-core platforms, many components speculate on the execution flow (e.g. out-of-order pipelines, branch and value prediction, shared cache levels, ...) . Because results from speculations are hard to predict without actually executing the program, this ends in an under-utilisation of the platform capacity as in practice the over-provisioned worst-case has almost no chance to actually happen. In addition, manufacturers mostly hide, in their commercial platforms, such details about the architecture due to intellectual property restrictions. In some specific cases, hard real-time system designers mostly rely on custom architectures designed for their domain (e.g. the Leon processor from the European Space Agency (ESA) [Gai02] or on an abstraction of the platform [BB08]). Due to cost constraints (specific platforms are expensive) and the absence of constraints regarding the application domain, contributions of this dissertation show how to reduce this over-provisioning when computing worst-case performance on an abstracted multi-core architecture.

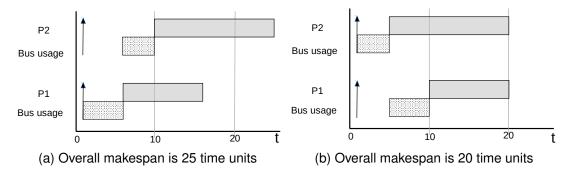

Multi-core hardware platforms, even when designed specifically for hard real-time systems, lead to unpredictability when two or more cores request an access to the same resource at an identical moment in time. In this case, it might be impossible<sup>3</sup> to determine, *a priori*, the actual granting order. However, this order has an impact on the worst-case performance as one task can complete before an other one. Figure 2 shows two executions where the X-axis denotes time and where solid arrows are release times. On both figures, a computing task (plain box) follows a bus request (dotted box). Each computing task is executed on an individual core, named *P*1 or *P*2. In addition, a shared bus connects the two cores. Because only one bus

<sup>3.</sup> This, obviously, depends on the arbitration policy, for example it is easy to determine the order with a TDM arbiter, but impossible with a RR one where the worst-case should be considered. See Section 1.4 for a review on arbiters.

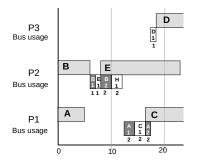

request can be performed at a time (mutually exclusive), both of them initiate from different cores, therefore need to be scheduled. In Figure 2a, the overall makespan is 25 time units where it decreases to 20 time units in Figure 2b just by inverting the granting order of the two bus requests. It is therefore clear that the order of bus requests impacts the final overall execution time of the application. This *shared bus* is the central component of this study.

Figure 2 - Illustrating example showing the importance of the execution order

Prior to run an application on a multi-core platform, a mandatory step is to decide on which core and when to execute application tasks. A scheduler maps tasks on cores and orders their execution on this core. As seen in Figure 2, mapping and scheduling decisions impact the overall execution time of a parallel application on a multi-core processor. The main point of this dissertation is the construction of scheduling policies where the objective is to minimise the schedule length while taking care of bus accesses.

Even when relaxing the indeterminism caused by context sensitive hardware decisions (speculative features, or arbiters), worst-case performance analyses can be unable to provide a result. Indeed, some common software features (e.g dynamic memory allocation, *goto*) lead to statically unpredictable behaviours. Despite programming rules to avoid such indeterministic behaviours, the compiler plays an important role for worst-case performance. At compile time, the timing behaviour can drastically change due to optimisations [PDC+18]. Thus, safety-critical applications require specific programming languages as well as verified compilers to determine and prove worst-case performance. Programming language features and compilers are out of the scope of this dissertation, and in this work, we only consider compilers where optimisation passes are disabled.

In summary, the presented work of this thesis targets hard real-time applications running on multi-core platforms. More specifically, we focus on bus requests management and aim at decreasing the impact of worst-case transmission latencies. This, in turns, decreases the over-provisioning of hardware resources, and inherently increases the utilisation of the platform reaching the goal of minimising the worst-case performance.

### Challenges in real-time systems

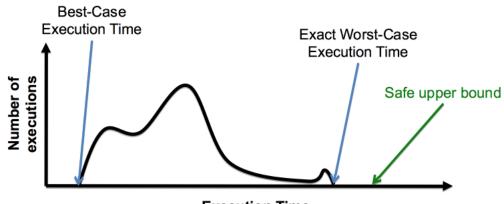

Guaranteeing that timing constraints are met on both single-core and multi-core platforms is challenging. The first challenge lies in the computation of the Worst-Case Execution Times (WCET). WCET estimates correspond to a safe and tight upper bound of the execution time

of an application executing on a given platform. As represented by Figure 3, a safe WCET estimate must be proven to be higher or equal to any effective execution time. For hard realtime systems, static WCET analyses produce the strongest guarantees on the results in terms of both safety and accuracy. Achieving such complex analyses requires detailed information on the hardware platform (pipeline, caches, ...) to devise tight estimates [WEE+08]. A common practice is to perform the analysis at the binary level, as this is the closest representation to what is executed by the hardware. However, control flow information (e.g. loop bounds) are generally lost at compile time, although they are required to estimate WCETs [LPR14]. In order to be safe, the WCET estimation assumes conservative hypotheses, where reducing the induced pessimism remains a challenging issue.

Execution Time

Figure 3 – Worst-Case Execution Times (WCET)

Once WCETs are estimated, a scheduling policy defines the execution order of tasks. Based on this policy, a task might be delayed, or pre-empted (paused and resumed), or forced to wait for a (software/hardware) resource to be available. The task is then blocked for a certain amount of time. The addition of a WCET estimate and a blocking time corresponds to the Worst-Case Response Time (WCRT). Therefore, computing this blocking time and the WCRT is a major challenge for real-time systems.

In addition, the schedule generated according to a given policy must enforce that the execution order implied will enforce a timing constraint for all tasks of the application. Proving the feasibility of a scheduling policy and bounding its computational complexity is still an open problem for certain combinations of policies and task models. For example, in a very recent work Ekberg et al. [EY17] have proven that using sporadic tasks with fixed priority scheduling on uniprocessor is a NP-Hard problem.

Moreover, multi-core platforms need a mapping of tasks on cores along with a schedule. Mapping analysis decides on what core a task will be mapped, Coffman et al. [CGJ96] have shown that this problem is NP-hard as it reduces to the well known bin-packing problem.

The main evolution from single-core to multi-core architecture focuses on the management of shared hardware resources (buses, shared last level of cache, ...) that are shared temporally and physically. When running multiple tasks on a single core, only a single task can execute on the processor and can have access to other resources at a given time instant. When dealing with multiple cores, multiple tasks will compete to access software/hardware resources (e.g. bus, sensors, semaphores ...) at an identical moment in time. Access requests must then be ordered/prioritized, since only a single request can be fulfilled at a time. These tasks, hence, interfere with each other and such interferences influence their predictability and timing behaviour. Identifying the region in which contention occur, and precisely estimate this contention is an other key challenge as it has a significant impact on the WCRT of tasks. Since it is difficult in general to guarantee the absence of resource conflicts during execution, current WCRT techniques either produce pessimistic WCRT estimates or constrain the execution to enforce the absence of conflicts, often at the price of a significant hardware under-utilisation.

### Contributions

Contributions of this work address hard real-time applications running on multi-core platforms and are applied at design time. The general contribution focuses on bus requests management and aims at decreasing the impact of worst-case transmission latencies on schedule length. The presented work optimises the overall schedule makespan and increases the utilisation of the platform.

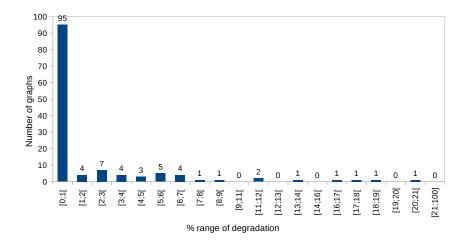

The first proposed method aims at determining the effective amount of interferences in a static schedule in order to reduce the pessimism of worst-case contention model. It consists in a *contention-aware* scheduling strategy that produces time-triggered schedules of the application's tasks. Based on knowledge of the application's structure, this scheduling strategy precisely estimates the *effective* contention, and minimises the overall makespan of the schedule. An Integer Linear Programming (ILP) solution of the scheduling problem is presented, as well as a heuristic algorithm that generates schedules very close to the ILP results (2 % longer on average), with a much lower time complexity. The heuristic improves by 59% the overall makespan of resulting schedules compared to a worst-case contention baseline.

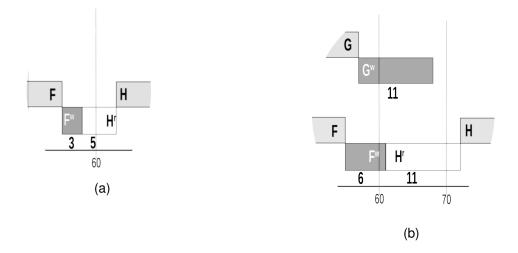

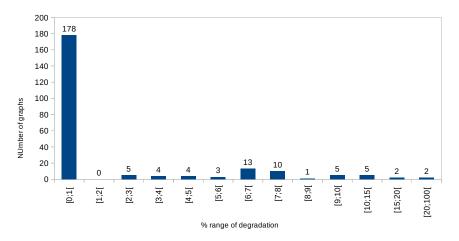

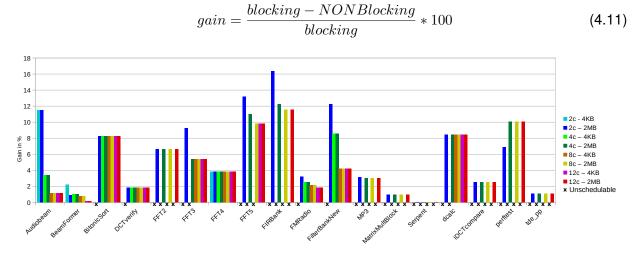

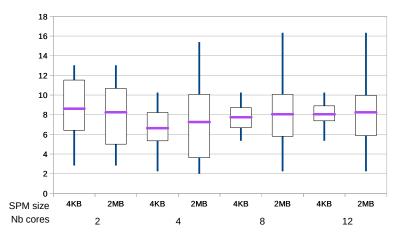

We extend our first approach to further reduce the overall schedule makespan by relaxing previous assumptions on the hardware, which in turns, enables new scheduling opportunities. The second contribution therefore proposes techniques to select ScratchPad Memory (SPM) contents off-line, jointly with schedule generation, in a way such that the cost of SPM load-ing/unloading is hidden, thanks to overlapping communication and computation phases. More precisely, we take advantage of communication fragmentation to bring more opportunities to benefit from such overlapping. Experimental results show the effectiveness of the proposed techniques on streaming applications and on synthetic task-graphs. The length of generated schedules is reduced by 4% on average on streaming application (8% on synthetic task graphs) by overlapping communications and computations.

All the code of the scheduler is available at https://gitlab.inria.fr/brouxel/methane.

## Thesis outline

The rest of this thesis is divided into four main chapters, summarised as follows:

**Chapter 1** introduces the context of this thesis through a review of real-time systems and multi-core platforms. It starts with the fundamental application models and their expressive-

ness. Then, multi-core platforms are presented, in which predictability and determinism are key features. Similar features are considered, afterwards, with execution models which specify how parallel applications are executed on multi-core platforms. Finally, a review of prior results on scheduling/mapping strategies for real-time applications on single-/multi-core architectures is given.

**Chapter 2** presents the scheduling framework extracted from the literature and used as a baseline for following contributions. Our framework can compute a static mapping and scheduling for an application mapped on a multi-core considering simple initial hypotheses (e.g. worst-case contention). All those restrictive hypothesis are lifted in following chapters, i.e. contention-awareness in Chapter 3, and free from contention in Chapter 4. The framework is first detailed with an Integer Linear Programming (ILP) formulation, and using a worst-case contention model. Then, a list-scheduling-based algorithm is presented which uses the same contention model to scale better on larger applications. Some initial experiments demonstrate the viability of the heuristic.

**Chapter 3** describes a novel technique to account for the effective amount of interference in off-line scheduling algorithm. It presents the methodology and its implementation in both a computationally intensive but exact method and in a faster but approximate algorithm. Finally, experiments demonstrate the limited over-approximation of the algorithm, along with gains over the framework from Chapter 2 with a worst-case contention scenario. The last experiment discusses the improvements over an adapted state-of-the-art algorithm with contention-free scenario.

**Chapter 4** lifts some of our restrictive hypotheses on the hardware in order to rely on a more realistic platform. First, the restriction on the size of the ScratchPad Memory (SPM) is removed while the latency to transmit data on the bus is hidden. To increase hiding opportunities, communication are fragmented. Experiments first validate the behaviour of the heuristic over the ILP formulation. Then, the gain is expressed over Chapter 2 baselines with a non-overlapping and non-fragmented communication scenario. The last experiment discusses the size of the fragment used in the scheduling strategies.

**Chapter 5** concludes this dissertation by summing up all presented contributions. Then possible future works are devised to further optimise the schedule makespan of hard real-time software on multi-core hardware.

# HARD REAL-TIME SYSTEMS AND MULTI-CORE PLATFORMS

Designing hard real-time systems implies to carefully select all hardware and software components. In order to guarantee the timing behaviour of the system. This chapter lists different possibilities where the production of a safe system is the Holy Grail.

We assume that a real-time system contains a number of tasks, that fulfil the functional requirements. A task generally exhibits a variation in its execution time. The Worst-Case Execution Time (WCET) estimate of a task corresponds to an upper bound of any possible execution time for that particular task.

Then all tasks from the set will eventually be executed on a given core, but only one can execute at a time per core. Hence, a scheduling policy describes how to construct an execution order for a given task-set, also known as a schedule. At design time, a schedulability analysis proves (or disproves) that the pair tasks-set, scheduling policy is schedulable, i.e. a schedule exists and meets all timing constraints.

The task WCET estimation is influenced by the schedule, for example, the initial cache state for a task depends on the task previously executed. Moreover, analysing the schedulability of a system requires each task WCET estimate. As a consequence, both WCET estimation and schedulability analysis are co-dependent, as each one impacts the other.

The evolution to multi-core architectures increases this co-dependence. In the general case, mapping decisions influence the WCET estimation accuracy. Indeed, two cores impact each other WCET estimations when mapped on different cores with overlapping request time on a shared resource.

To break this co-dependence, nowadays techniques manage to enforce timing isolation. The isolation in time enables to study the timing behaviour of a component in independence from the others with the guarantee that no other components will affect the result. Applying this timing isolation principle can be accomplished at different levels from the hardware with cache locking or ScratchPad Memory (SPM) (e.g. [PP07]), on the execution model with the separation of the memory access from the computation (e.g. [PBB+11]), or on the communication model with contention-free mechanism (e.g. [BDN+16]).

This chapter reviews these different key concepts to, at the end, focus on state-of-the-art techniques on scheduling. It is organised as follows. First, Section 1.1 introduces different task models and Section 1.2 different hardware designs for real-time systems. Then, Section 1.3 presents execution models enforcing timing isolation, followed by Section 1.4 describing available communication configurations. Next, Section 1.5 summarises methods to determine WCETs. Finally, Section 1.6 presents a review on real-time scheduling targeting multi-core architectures before concluding in Section 1.7.

### 1.1 Task models and their expressiveness

A task model, a.k.a workload model, describes the properties of a real-time application. At a coarse grain, tasks compose the *application*. A *task* corresponds to a piece of code. At a finer grain, tasks infer task instances, known as *jobs*. Each job corresponds to an instance of a task that is effectively scheduled and executed on the platform. A task can generate multiple jobs depending on its timing properties and the studied time window. Jobs are ordered and job *i* must complete before job i + 1. Depending on the level of abstraction and expressiveness of further task models, properties defined for tasks and/or jobs include :

- WCET: an upper bound of any possible execution time,

- period: the frequency at which the task/job is ready for execution,

- deadline: the time at which the execution must be complete,

- predecessors/successors: execution order constraints.

Differences between task models essentially come from the amount of exhibited information (expressiveness), the amount of applications it can represent (flexibility), and the applied generalisation (abstraction level). This section does not attempt to be exhaustive as the multiplicity of task models is tremendous, but it covers the wide range of possibilities. For a list of other task models, the reader is advised to look into [SY15].

The seminal work from Liu and Layland [LL73] introduced the periodic task model. It represents applications where jobs arrival times appear at a known and strict frequency after the first one (defined at designed time). Then, each job must terminate before a deadline relative to its arrival time. The lack of flexibility in term of restrictive periodicity was latter relaxed by Mok [Mok83] with sporadic tasks. This allows releasing tasks at later time point as long as at least a minimum time interval as elapsed between two firings (pseudo-period). Both cases are said periodical task models as they generate an infinite sequence of job instances, released periodically. In addition each job must end before the next one is released.

Three other sub-categories classify the aforementioned task models depending on the deadline property for the entire tasks set. If for all tasks the deadline is equal to the period [LL73], the tasks set is *implicit*. If all deadlines are inferior or equal to the period then the category is *constrained* deadlines, while *arbitrary* deadline is otherwise used [Mok83].

Above-mentioned task models lack of flexibility. As an example, a MPEG decoder sequentially receives, decodes and displays video frames. In such codec, a frame is periodically bigger than others, and thus requires more computational time. Applying the same task/function to all frames results in an over-provisioning of the system as most frame computation need less processor time. The Multi-Frame model [MC96] and its Generalisation (GMF) [BCG+99] allow to configure different properties, such as WCET estimates, per jobs originating from an identical task.

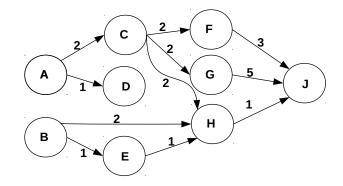

Another class of embedded real-time systems concerns signal processing applications. They mainly focus on images, sounds or any digital signals, e.g. a wireless router, surveillance camera, .... This type of application processes an uninterrupted flow of information. The expressiveness of seminal periodic task model does not capture this flow of information which is transmitted from task to task. In [Ack82], Ackerman expressed the *data-flow program graph* task model, known as Directed Acyclic Graph (DAG) when no cycle are present. This representation increases the expressiveness of the task-model by exhibiting dependencies between

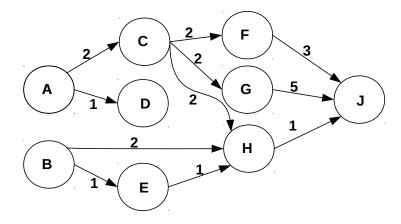

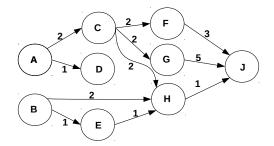

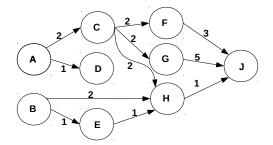

Figure 1.1 – Example of an application represented by a DAG

tasks, thus exposing the parallelism of the application. In data-flow graphs, nodes represent computations (tasks) and edges represent communications between tasks. An edge is present when a task is causally dependent on another one, meaning the source of the edge needs to complete prior to run the target. The edge corresponds to a First In First Out (FIFO) channel where the source produces a certain amount of tokens, and the sink consumes all of them. An example is presented by Figure 1.1 where labels on edges represent the number of tokens.

Similarly to periodic task models, a data-flow graph instance is called an *iteration* and a job is a task instance inside an *iteration*. Then, the DAG may iteratively executes until the end of time (or platform is shutdown). Hence, jobs execution order follows aforementioned constraint, job *i* finished before job i+1. But, the iteration j+1 can start before the completion of iteration *j* as long as jobs dependencies are satisfied. This allows to exploit job parallelism, i.e. pipelining [TPG+14].

In data-flow graphs, timing properties (e.g. period, deadline) can be attached to graph itself and not anymore stated for each task and job. All tasks must therefore complete their execution between the release time and the deadline of the whole graph. A multi-task application is then a multi-DAG application as in [Per17].

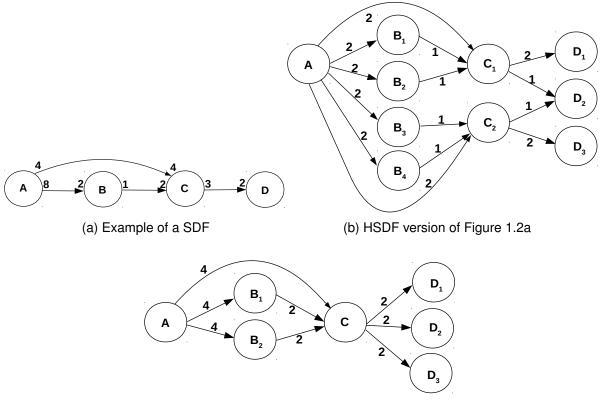

In general DAGs, edge sinks consume all tokens produced by the corresponding source in one job execution. To overcome this limitation, Synchronous Data-Flow (SDF) graphs [LM87] allow different production/consumption rates between two actors of an edge. An additional constraint on SDF forces the amount of transiting tokens to be known at compile time which allows static analysis on the graph, see Figure 1.2a.

Due to different rates of production and consumption of tokens on an edge, SDF graphs need an expansion pass prior to be scheduled. The larger expansion builds an Homogeneous Data-Flow graphs (HSDF) [LM87], where all production/consumption rates are equal to 1 (there is as much tokens produced than consumed). Despite of the exponential complexity when expanding SDFs, HSDF representations are required [GHK+13] to determine, *a priori*, the amount of node repetitions and all number of transmitted tokens. Figure 1.2b presents the example HSDF obtained after expanding the SDF from Figure 1.2a.

Due to the inherent complexity of building a HSDF, middle size graph representations have been proposed by Zacki [Zak13]. Partial Expansion Graph (PEG) exposes more parallelism than SDF, with potentially less tasks than HSDF. Therefore, using strength from both initial representations.

(c) One possible PEG from the SDF in 1.2a

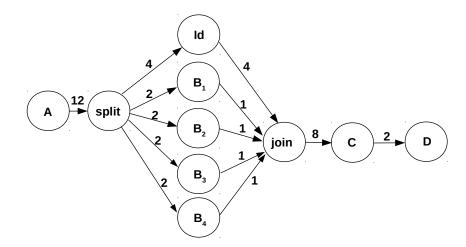

In streaming applications, fork-join graphs [TKA02] correspond to an adaptation of SDF graphs. Identically to SDF, they can include different production/consumption rates. They also need to be expanded for further analyses. In contrast to SDF, all actors, except specific fork and join nodes, can have one and only one predecessor and successor. Figure 1.3 exhibits an expanded version of a sample fork-join graph.

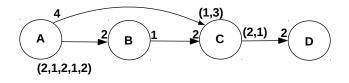

Applying the multi-rate idea from GMF to SDF, Bilsen et al. [BEL+96] introduced the Cyclo-Static Data-Flow graph (CSDF). CSDF graphs allow to have different production/consumption rates within a period to jobs of the same task. The example from Figure 1.4 present a CSDF where, for example, actor C has a firing rate of (2, 1) on its output edge. Then actor C alternatively produces 2 tokens then 1 token, then 2 ....

Synchronous Data-Flow applications can be represented with different languages, such as Esterel [BC84], StreamIT [TKA02] or Prelude [PFB+11]. They all have their specificities, Prelude targets multi-periodic synchronous system, while StreamIT generates fork-join graphs targeting streaming applications. All help building parallel applications represented by graphs.

These DAGs do not necessarily need to be built from scratch, which would require an important engineering effort. It is possible to extract tasks from legacy sequential code as in [FDC+13; CM12; CEN+13].

The literature abounds of other graph-based task model, e.g. Hierarchical Task Graph [GP94], Dynamic Data Flow graphs [BDT13]. Only the most common were presented here and

Figure 1.3 – Expanded example of a fork-Join graph

Figure 1.4 – Example of a CSDF

not all of them are suitable for critical applications. An attractive task model for real-time system lies in its expressiveness (no ambiguities, expose parallelism) without too much flexibility (concise) and too high abstraction (remain implementable), therefore allowing proof of timing behaviour.

### 1.2 Predictable multi-core architectures

For a long time, increasing the computational power of a processor meant increasing the processor clock frequency. Then, manufacturers started to increase the number of cores within a chip instead of the clock frequency, due to technological limits.

In general-purpose multi-core processors, speculative features are key concepts to increase average case performance but mostly worsen WCET estimates. These features are also major sources of indeterminism at different levels: micro-architecture, predictors, memory hierarchy, inter-connection medium, and arbiters. Compared to single-core architectures, in multi-core platforms, the indeterminism comes mainly from interferences when cores try to access a shared hardware element. To fulfil all requirements, hard real-time systems need specific architectures with both properties :

Determinism: it corresponds to the absence of randomness. With identical given inputs, a

deterministic system always produces identical results. Then, with real-time systems, determinism also includes timing constraints where these identical results require identical

production times.

Predictability: it corresponds to the ability to determine the produced result in advance (without executing the system) for given inputs. Again, with real-time systems, predictability includes the ability to guarantee that timing constraints are met without actually executing the system.

Real-time-oriented multi-core architectures are classified according to the presence of timing anomalies or domino effects [WGR+09; HRW15]. Timing anomalies on the WCET arise when the local worst-case does not entail the global worst-case [CHO12]. The often cited example [LS99] comes from an instruction cache miss that is the local worst-case of a cache analysis, but turns out to not lead to the global worst-case in presence of an out-of-order pipeline. The domino effect is a specific kind of anomalies where an initial local state have an expected impact on the local WCET, but no convergence is possible on the global WCET. For example, the execution time of a loop body differs according to the initial state (caches, pipeline, ...) when entering the loop [Ber06]. Following four general architecture categories classify the further next multi-core architectures:

- Composable: the timing of a program running on a core is not influenced by ones running on other cores (no domino effect) and is free from timing anomalies, such as Patmos+Argo [SSP+11; KS14];

- Full timing compositional: platforms do not exhibit timing anomalies but core analysis are dependent (domino effect), such as Kalray [DVP+14];

- Compositional with constant bound effect: these exhibit timing anomalies but no domino effects, such as TriCore [WCM16];

- Non-compositional: all other architectures, especially general purpose ones, that include timing anomalies and domino effect.

Following is a, non exhaustive, list of architectures designed for predictability and determinism.

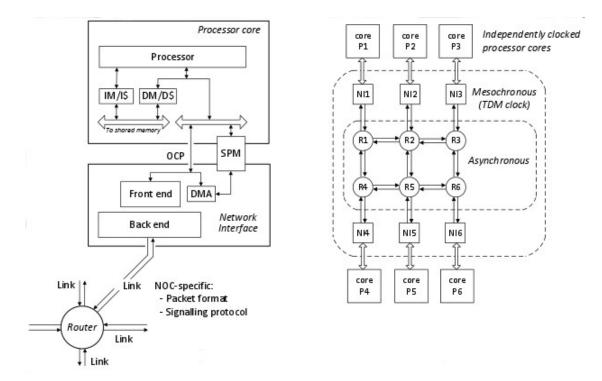

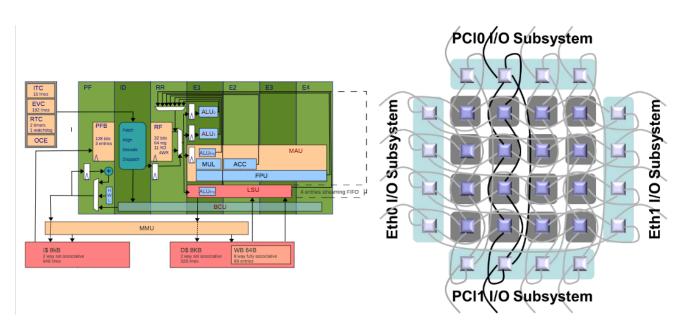

The academic core *Patmos* from Shoeberl et al. [SSP+11] is available on FPGA. It contains a simple RISC in-order pipeline with five stages, see Figure 1.5. All timing information of the Instruction Set Architecture (ISA) are available in [SBH+15]. Different caches/local memories configurations make this core a good candidate for research work. It includes the common instruction/data caches with Least Recently Used (LRU) policy, which is known to be predictable [RGB+07]. But it also comes with other cache types: method cache [DHP+14], heap cache [SHP13; HPS10], stack cache [ABS13]. Split caches separate the source of indeterminism from dynamic allocation and split analyses. Instead of split caches, it is possible to connect the core pipeline to a ScratchPad Memory (SPM). Such memories are more predictable than caches [PP07; MB12] as they are managed by software. Then a compiler decides what and when to store/load data to/from it. To integrate Patmos on a multi-core platform, it is shipped with two fully predictable Networks on Chip (NoC):

- i) a bluetree NoC [SCP+14] to access the off-chip memory with a Time Division Multiplexing arbiter;

- ii) a 2-D Mesh NoC [SBS+12; KS14; KS15; KSS+16] to enable inter-core communication, also using time division for the arbitration policy.

Figure 1.5 – Patmos core (left side) and its Argo NoC (right side), from [KS14]

The Patmos core+Argo NoC is a fully composable architecture, free from timing anomalies, and allows composable analysis due to the full timing isolation thanks to Time Division Multiple Access (TDMA) arbiters.

The commercial platform *Kalray MPPA 256* [DVP+14] contains 256 cores organised in 16 tiles of 16 cores each (see Figure 1.6). All tiles are connected to a 2-D bi-torus NoC enabling packets to transit between tiles, to the off-chip memory, or I/O devices. Inside a tile, the 16 cores are connected to every 16 memory banks (SMEM) through 8 buses (cores are paired). In addition, the SMEM can be configured to enable a private memory to each core, similarly to the SPM in Patmos core. All cores are based on a simple RISC pipeline with seven stages. A vast literature dealing with the Kalray MPPA exists, e.g. [HMC+16; BDN+16; SS16; Per17].Its strengths include an important computational power and design choices with predictability in mind. Some sources of indeterminism still subsist, for example when a tile receives a packet from the NoC: the fixed priority arbiter gives a higher priority to packets coming from the NoC, then they are store in the SMEM; this process adds a delay to cores inside the tile that would also access the same memory bank, and packets coming from the NoC are hardly predictable. The Kalray MPPA is a fully compositional architecture, where WCETs of tasks running on each core are influenced by other cores or NoC incoming packets (domino effects).

From the automotive domain, Wang et al. [WCM16] use a TC27x TriCore micro-controller from Infineon<sup>1</sup>. This platform includes a SPM attached to each core. With its three cores, two identical cores TC1.6P and another core TC1.6E, this processor is heterogeneous. But all these three cores execute the same instructions set. Two independent on-chip buses allow

<sup>1.</sup> TriCore Microcontroller, http://www.infineon.com/

Figure 1.6 - Kalray core (left side) and its NoC (right side), from [DVP+14]

shared resources interconnection, as well as, system peripherals accesses. A Direct Memory Access (DMA) engine connects the global off-chip memory and cores. The TriCore is assumed, but not formally proven, to belong to the category of compositional architectures with constant-bounded anomalies [AEF+14].

### 1.3 Towards parallel and predictable execution models

An execution model defines how programs are processed by the hardware. The very first execution model was described by Turing [Tur37]. He detailed how to manipulate symbols on a strip of tape according to a table of rules. This principle was then adapted into von Neumann architecture [Neu82], or in sequential programming language such as C [Rit93].

To benefit from the multiplicity of cores in modern architectures, execution models expose the parallelism of an application. OpenMP [MB12] provides an extension to C code based on pragmas to expose possible parallel regions of code. GPU architectures exhibit a specific execution model [ND10] based on group of instructions, i.e. a warp, where all instructions inside a group execute in parallel.

Task models based on graph, e.g. SDF graph [LM87], naturally expose the potential concurrency of applications. Gordon et al. [GTA06] present a method to benefit from all sources of parallelism implied by the SDF task model, in particular they use task pipelining to maximise the throughput of the application.

In hard real-time systems, timing verification can be facilitated with following execution models. For example, Pushner et al. [Pus03] limit the program to a single-path, leaving the exploration of the longest path trivial, see Section 1.5 for WCET estimation details.

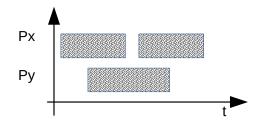

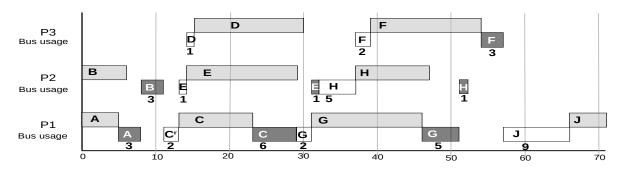

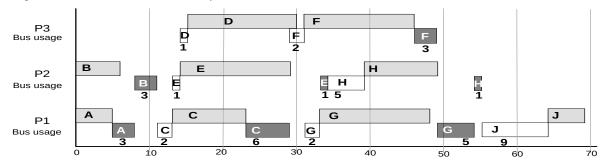

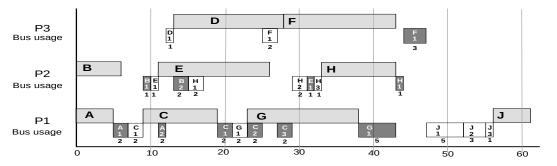

Figures 1.7 oppose the three execution models commonly used in the literature with respect to accesses to the main memory. Figure 1.7a presents three tasks (rectangles) running on two

(a) Example of three tasks with original execution model. No possible differentiation between computation and communication.

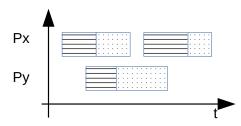

(b) Example of three tasks using PREM, a memory phase accesses the off-chip memory to write or read data, then the execute phase can compute without any more accesses to the shared memory.

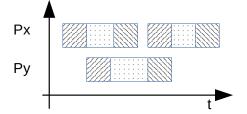

(c) Example pf three tasks using AER, a read phase first fetch data from the main memory, then an execute phase executes without any access to the shared memory, finally a write phase writes back data to the main memory.

Figure 1.7 – Task representation with different execution model

cores (Px, Py), where the X-axis is the time. In this original execution model, memory accesses and computation are undistinguishable. Therefore it is very difficult to determine if and when memory accesses arise, and moreover if they interfere. A safe solution is therefore to compute a pessimistic WCET for each task where all instructions accessing the memory are considered interfering with similar instructions from other cores.

With the PRedictable Execution Model (PREM), Pellizzoni et al. [PBB+11] decompose a task in two parts : i) unload modify data produced by the preceding task to the off-chip memory if need be, then load code and data required by the task into a local private memory; ii) execute the code without anymore access to the off-chip memory. Figure 1.7b sketches an example composed with three tasks (rectangles). Each task is divided in two parts, horizontal line boxes for memory accesses and dotted boxes for computation phases. This decomposition enforces composability in parallel execution by isolating memory access phases from execution ones. The WCET of the execution phase can then be computed in isolation. Hence, if coupled with a SPM, a software-managed memory, it increases the likelihood of predictability as memory are located in space and time. Lately, PREM became more and more popular, e.g. [MDC14; AWP15; BMV+15; MBB+15; BDN+16]. The main reason lies in the predictability improvement by isolating memory accesses. In addition, Light-PREM [MDC14] allows to automatically adapt any (legacy-)application to the PREM model.

Durrieu et al. [DFG+14] extend PREM with Acquisition Execution Restitution (AER) to en-

able this timing isolation principle with dependent tasks. AER [MNP+16] unloads the data produced by a task just after its execution in a third phase. Figure 1.7c displays an example composed with, again, three tasks (rectangles). Each task is divided in three parts, slashed lines boxes for *acquisition* phase, dotted boxes for *execution* phases, and backslashed lines boxes for *restitution* phases. Coupled with a SPM-based architecture, AER is very powerful to isolate multi-core interferences, hence it improves the predictability. With such an execution model, it is possible to load all the data into the SPM, execute the code without any further access to the main memory and then write back results to the off-chip memory.

## 1.4 Task and Inter-core communication

Aside from the execution model, the communication model defines how tasks exchange data, and how data transit on the hardware between computational units. First, most common communication mediums are either a bus or a Network on Chip (NoC). Second, the data transmission scheme organises sending and receiving point of data. When dealing with a task model that contains only independent tasks, this last transmission setting becomes optional. NoCs are out of the scope of this dissertation and will not be discussed anymore.

**Communication medium** A bus is limited by a bandwidth, also known as a bitrate in this specific case, which corresponds to the amount of data transmitted per time unit. The major source of hardware interferences originates on bus accesses generated by cores. Indeed, the bus connects every core together and with other devices (e.g. I/O devices, off-chip memory), leaving only one possible path for data transmission. Bus requests are scheduled with the help of an arbiter, that enforces a mutual exclusion on bus accesses as only one can access the bus at a time.

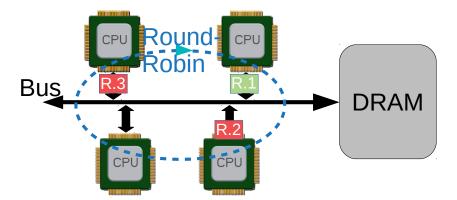

Figure 1.8 – Representation of the Round-Robin policy principle. Access order is R.1, R.2, R.3

The probably most used bus arbitration policy is the Round-Robin (RR) [Ens77]. Access requests are enqueued (one queue per core) and served in a round-robin fashion, pictured in Figure 1.8. In order to improve the predictability, a FAIR-RR arbitration policy [Ens77] limits the request access time for each core to the bus with a time sharing mechanism.

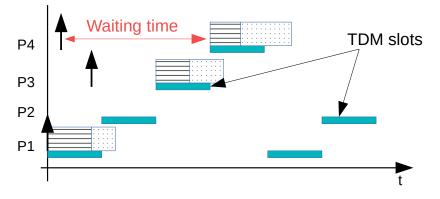

Figure 1.9 – Example of a TDMA arbitration scheme. Blue filled boxes are TDM slots, granting time for the corresponding core where horizontal-lined boxes represent memory accesses as in PREM in Figure 1.7b

Time Division Multiple Accesses (TDMA) arbitration policy [Ens77] enforces timing isolation and increases the predictability of the hardware [SCT10]. Figure 1.9 pictures a TDMA arbiter example. Each blue-filled boxes are TDM slots, and horizontal-lined boxes are memory accesses as in the PREM example from Figure 1.7b. Each core receives a time slot (TDM slot) in which the arbiter grants the access to the communication medium. TDM slots are guaranteed to not overlap, thus ensuring an access in mutual exclusion to the shared resource. The arbiter stores a table with the granting rules when booting up the platform. Then, the core is allowed to access the bus only when its time slot is active. TDMA arbiters suffer from an under-utilisation of hardware resources. A core must wait for its allocated time interval to process its request, and a time slot is wasted if the allocated core has no pending request to transmit [WS11]. To overcome this situation, Poseidon [SSP+14] tries to build the table with application structure knowledge and scheduling time slots in order to minimise the waiting time for the shared resource.

Round-Robin arbiters do not suffer from the drawbacks of TDMA ones, but they lack of predictability. Hence, FAIR-RR arbiters fill this gap by overcoming all drawbacks from vanilla Round-Robin arbiters and TDMA arbiters with the increase of predictability and no waste of resources time. FAIR-RR arbiters seem therefore to be the best candidate for multi-core architectures in the context of embedded real-time systems.

**Data transmission scheme** Data transmission schemes are architecture dependent. They depend on the hardware capabilities in terms of available hardware elements and configuration options.

When a Direct Memory Access (DMA) is available, data transmissions can occur while the core, which issued the transmission, is processing some computation; transmission are therefore *non-blocking* [GPP09]. If no DMA is available, cores initiate their requests and wait until the end of the transmission; transmissions are therefore *blocking* [PNP15].

When a SPM is available, if a producer and a consumer are mapped on the same core, then their shared data do not have to be transferred to the main memory. They can use the shared SPM, thus saving two bus requests; communications use shared memory with placement optimisation [RDP17]. However, choosing this type of communication must be carefully thought as data produced may be used by other tasks running on other cores. When only caches are available, the software can not decide what to store in an other cache than its own. Therefore, tasks running on cache-based architectures should exchange their data through the off-chip memory; communications use the *shared memory* [PNP15].

Lastly, if the hardware offers a global addressing policy along with SPMs, every memory cell has a different address SPM/off-chip/..., then producers can store data into the consumer SPM or the consumer can read data from the producer SPM; communications are *direct* [SPS+15].

### 1.5 Worst-case execution time estimation

Worst-Case Execution Time (WCET) estimation has been widely studied over the years. This section aims at giving the key techniques to perform this analyse and not an in depth study. For more information on WCET estimation, a survey is available in [WEE+08].

WCET estimation corresponds to an upper bound of any possible execution time for a software task on a hardware platform. WCET estimates properties include both safety and tightness. A safe WCET estimate is guaranteed above any possible execution of the program. While a tight WCET estimate limits the over-approximation (see Figure 3 from the Introduction).

When a WCET analysis considers a task executed on a dedicated hardware, without any other task, the WCET estimate is said to be in isolation from the system. Main studies identify WCET estimates in isolation and WCET estimates including interferences from other tasks.

From [WEE+08], there exists three major categories of WCET estimation techniques:

- Measurement based techniques: they run the software several times on the hardware (or a simulator) with different inputs to generate the worst-case behaviour. This method results in tight estimates by nature. But there is no guarantee that the worst-case behaviour is found, if the worst-case input is never exercised. Therefore this method is not safe for critical systems;

- Probabilistic methods: they construct a probabilistic curve from WCET measurements. They differ from the above-mentioned techniques in the number of runs which is lower. These methods aim at giving a worst-case execution time with a confidence probability. Tightness in results depends on the probabilistic law applied and safety can be discussed with the probabilistic confidence factor;

- Static methods: they are from far the most safe, but safety comes at the cost of a possible over-approximation. To generate tight and safe results, these analyses run at the binary level. It is usually divided in two steps to first account for the micro-architecture timing behaviour; i.e. data address analysis, cache analysis, branch predictor analysis, pipeline analysis and so on .... And second, a higher level analysis computes the worst-case execution path of the application and then the WCET estimate, e.g. Implicit Path Enumeration Technique (IPET).

Apply state-of-the-art WCET analysis techniques, with multi-core architectures, impose to guarantee the absence of interference caused by other cores, or further analyses are required to augment WCET estimates by accounting for these interferences. Kelter [Kel15] accounts for the contention on the bus. Potop et al. [PP13] add the communication cost into the IPET

problem. Ozaktas et al. [ORS13] computes the stall time induced by critical sections and add them to the IPET problem.

### 1.6 Real-time scheduling: a state of the art

Real-time scheduling determines the execution order of tasks on a processor. Then, targeting multi-core architectures, mapping algorithms determine on which core a task will run. Most of the times, scheduling on single-core architecture is NP-hard, e.g. with fixed-priority and sporadic tasks [EY17]. Mapping+scheduling on multi-core architectures is therefore classified as a NP-hard problem [CGJ96], because the mapping step reduces to the known bin-packing problem. For the sake of simplicity, when not explicitly stated in the following, a multi-core scheduling algorithm refers to both a mapping and a scheduling algorithm.

The literature on multi-core real-time scheduling is tremendously vast. Davis and Burns [DB11] sort scheduling algorithms in three main categories: i) partitioned, ii) global, and iii) hybrid. Following the classification of single-core schedulers, further review focuses on multi-core architectures where the main content focuses on partitioned (including static/off-line) scheduling, while other scheduling policies are summarised. More details on scheduling strategy and schedulability analysis are available in this very same survey [DB11].

#### 1.6.1 Classification of single-core schedulers

The two first major categories of schedulers represent the construction moment of the selection order: *off-line* or *on-line*. The former, statically pre-computes off-line an execution sequence for each core. Then at runtime, a dispatcher executes the generated schedule. The latter executes *on-line*, and determines the next task to execute according to some criteria, the most common being assigned priorities and current execution state.