### Memory and data aware scheduling

Loris Marchal

#### ▶ To cite this version:

Loris Marchal. Memory and data aware scheduling. Distributed, Parallel, and Cluster Computing [cs.DC]. École Normale Supérieure de Lyon, 2018. tel-01934712

## HAL Id: tel-01934712 https://inria.hal.science/tel-01934712

Submitted on 26 Nov 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### MÉMOIRE D'HABILITATION À DIRIGER DES RECHERCHES

présenté le 30 mars 2018

#### à l'École Normale Supérieure de Lyon

par

#### **Loris Marchal**

# Memory and data aware scheduling

(Ordonnancement tenant compte de la mémoire et des mouvements de données)

#### Devant le jury composé de :

| Umit Çatalyürek    | Georgia Tech., USA      | Rapporteur   |

|--------------------|-------------------------|--------------|

| Pierre Manneback   | Polytech-Mons, Belgique | Examinateur  |

| Alix Munier Kordon | Univ. Paris 6           | Examinatrice |

| Cynthia Phillips   | Sandia Nat. Lab., USA   | Rapportrice  |

| Yves Robert        | $ENS\ Lyon$             | Examinateur  |

| Denis Trystram     | Grenoble INP            | Rapporteur   |

# Preamble

In this habilitation thesis, I have chosen to present the work that I have done on memory-aware algorithms, and on related studies on data movement for matrix computations. This choice, needed to give coherence to this document, leaves out a number of contributions, mainly in the area of task scheduling, but still represents the main research domain which I contributed to, since my PhD ten years ago.

This manuscript is organized as follows: Chapter 1 presents the motivation and context of this work, and contains a short survey of the existing studies on memory-aware algorithms that are the basis of the work presented later. Then, my contributions are divided into two parts: Part I gathers the studies on memory-aware algorithms for task graph scheduling, while Part II collects other studies focusing on minimizing data movement for matrix computations. When describing my contributions, I have chosen to present the simplest algorithms in full details, and to give only the intuition for the most complex results. Most proofs are thus omitted. They are available in the referred publications or research reports. Chapter 10 concludes the document and open some perspectives. The appendices contain the bibliography (Appendix A) and my personal publications (Appendix B). Note that references to personal publications start with a letter corresponding to their type and are sorted chronologically by type, while other references are numbered alphabetically.

Last but not least, the "we" pronoun used in this document is not only employed out of politeness, but recalls that all these contributions originate from a collaborative work with all my co-authors. In particular, I owe a lot to my talented PhD students: Mathias Jacquelin, Julien Herrmann and Bertrand Simon.

# Contents

| P | ream | ble                                                        | iii |

|---|------|------------------------------------------------------------|-----|

| 1 | Mo   | tivation and context                                       | 1   |

|   | 1.1  | Motivation                                                 | 2   |

|   |      | 1.1.1 On the importance of data movement                   | 2   |

|   |      | 1.1.2 Algorithms and memory usage                          | 3   |

|   | 1.2  | Two pebble game models                                     | 5   |

|   |      | 1.2.1 (Black) pebble game for memory minimization          | 5   |

|   |      | 1.2.2 Red-Blue pebble game for data transfer minimization  | 8   |

|   | 1.3  | I/O lower bounds for matrix computations                   | 11  |

|   |      | 1.3.1 More on matrix product                               | 11  |

|   |      | 1.3.2 Extension to other matrix computations               | 13  |

|   | 1.4  | Memory-aware task graph scheduling                         | 15  |

|   |      | 1.4.1 Generalized pebble games for task graph scheduling . | 15  |

|   |      | 1.4.2 Peak memory minimizing traversals for task trees     | 16  |

|   |      | 1.4.3 Minimizing I/O volume when scheduling task trees     | 20  |

|   | 1.5  | Conclusion                                                 | 21  |

|   |      |                                                            |     |

| Ι | Tas  | sk graph scheduling with limited memory                    | 23  |

| 2 | Me   | mory-aware dataflow model                                  | 27  |

|   | 2.1  | Proposed dataflow model                                    | 27  |

|   | 2.2  | Emulation of the pebble game and complexity                | 28  |

|   | 2.3  | Equivalence with Liu's model on trees                      | 30  |

|   | 2.4  | Problem definitions                                        | 31  |

|   | 2.5  | Adaptation of previous algorithms on trees                 | 31  |

| 3 | Pea  | k Memory and I/O Volume on Trees                           | 35  |

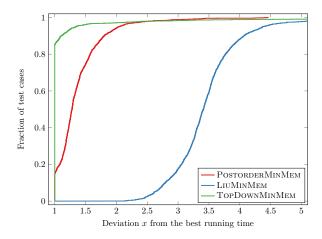

|   | 3.1  | Postorder traversals for memory minimization               | 35  |

|   | 3.2  | Another optimal algorithm on trees                         | 37  |

|   |      | 3.2.1 Top-down vs. bottom-up orientation of the trees      | 37  |

|   |      | 3.2.2 The TopDownMinMem algorithm                          | 38  |

|   |      | 3.2.3 Performance of TopDownMinMem                         | 40  |

vi *CONTENTS*

|    | 3.3          | Results and open problems for MiniO                 | 4  |

|----|--------------|-----------------------------------------------------|----|

|    |              | 3.3.1 MinIO without splitting data                  | 41 |

|    |              | 3.3.2 MinIO with paging                             | 42 |

|    | 3.4          | Conclusion of the chapter                           | 45 |

| 4  | Pea          | k memory of series-parallel task graphs             | 47 |

|    | 4.1          | Introduction on series-parallel task graphs         | 47 |

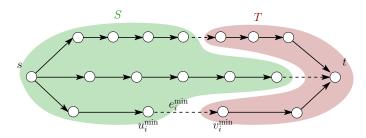

|    | 4.2          | Optimal algorithm for parallel-chain graphs         | 48 |

|    | 4.3          | Optimal algorithm for series-parallel graphs        | 50 |

|    | 4.4          | Conclusion of the chapter                           | 52 |

| 5  | Hyl          | orid scheduling with bounded memory                 | 53 |

|    | 5.1          | Adaptation to hybrid platforms                      | 53 |

|    | 5.2          | Tree traversals with pre-assigned tasks             | 54 |

|    |              | 5.2.1 Application model                             | 54 |

|    |              | 5.2.2 Problem complexity and inapproximability      | 56 |

|    | 5.3          | Task graph scheduling with bounded memories         | 57 |

|    |              | 5.3.1 Integer Linear Programming formulation        | 58 |

|    |              | 5.3.2 Heuristics                                    | 59 |

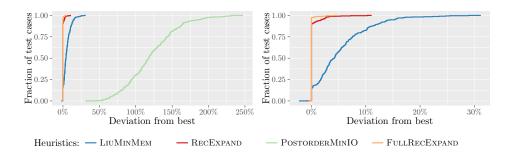

|    |              | 5.3.3 Experimental evaluation through simulations   | 60 |

|    | 5.4          | Conclusion of the chapter                           | 64 |

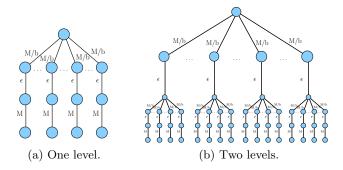

| 6  | Mei          | mory-aware parallel tree processing                 | 65 |

|    | 6.1          | Complexity of the bi-objective problem              | 65 |

|    |              | 6.1.1 Problem model and objectives                  | 65 |

|    |              | 6.1.2 NP-completeness of the bi-objective problem   | 66 |

|    | 6.2          | Heuristics for the bi-objective problem             | 68 |

|    |              | 6.2.1 Processing subtrees in parallel               | 68 |

|    |              | 6.2.2 List-scheduling heuristics                    | 70 |

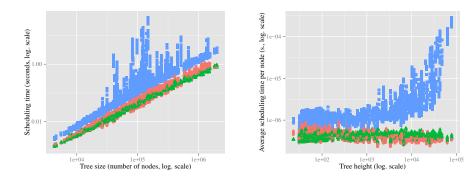

|    |              | 6.2.3 Experimental comparison                       | 72 |

|    | 6.3          | Memory-bounded tree scheduling                      |    |

|    |              | 6.3.1 Simplifying assumptions                       | 74 |

|    |              | 6.3.2 Memory constrained list-scheduling heuristics | 74 |

|    |              | 6.3.3 Memory booking heuristic                      | 76 |

|    |              | 6.3.4 Refined activation scheme                     | 77 |

|    | 0.4          | 6.3.5 Experimental comparisons of the heuristics    | 80 |

|    | 6.4          | Conclusion of the chapter                           | 84 |

| II | $\mathbf{M}$ | inimizing data movement for matrix computations     | 87 |

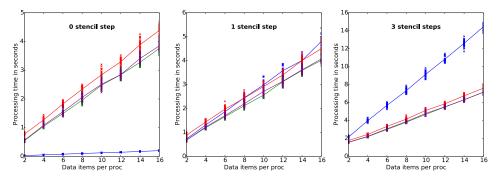

| 7  | Mat          | trix product for memory hierarchy                   | 91 |

| •  | 7.1          | Introduction                                        | 91 |

|    | 7.2          | Platform model                                      | 92 |

|    |              |                                                     |    |

| CONTENTS | vii |

|----------|-----|

|          |     |

|    | 7.3<br>7.4<br>7.5 | Objectives                                                   | 93<br>94<br>94<br>95<br>97<br>97 |

|----|-------------------|--------------------------------------------------------------|----------------------------------|

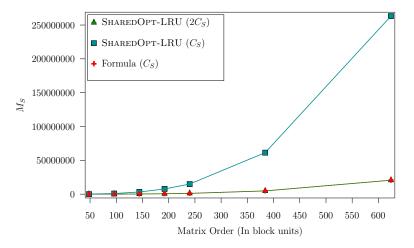

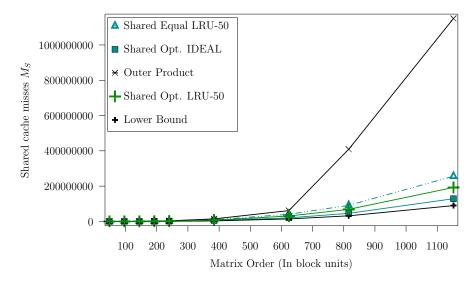

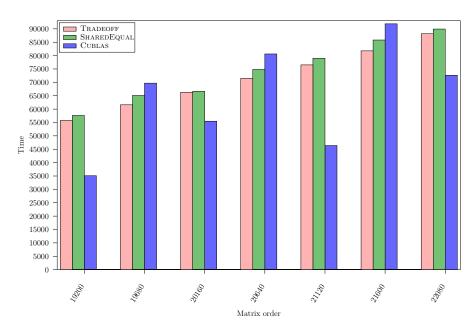

|    |                   | 7.6.1 Evaluation through simulations                         | 99                               |

|    | 7.7               |                                                              | 102<br>103                       |

|    |                   | •                                                            | 100                              |

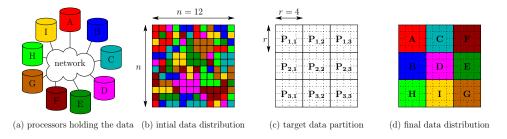

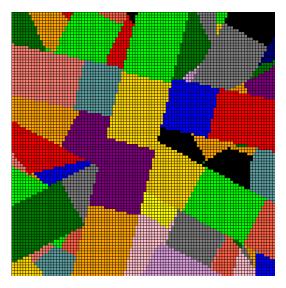

| 8  |                   |                                                              | 105                              |

|    | 8.1<br>8.2        | Introduction                                                 |                                  |

|    | 8.3               | Problem modeling                                             |                                  |

|    | 0.5               |                                                              | 108 - 108                        |

|    |                   | 8.3.2 Redistribution minimizing the number of parallel steps |                                  |

|    | 8.4               | Coupling redistribution and computation                      |                                  |

|    |                   | 8.4.1 Problem complexity                                     |                                  |

|    |                   | 8.4.2 Experiments                                            |                                  |

|    | 8.5               | Conclusion of the chapter                                    | 115                              |

| 9  | Dyn               | amic scheduling for matrix computations                      | 117                              |

|    | 9.1               | Introduction                                                 | 117                              |

|    | 9.2               | Problem statement                                            |                                  |

|    | 9.3               | Lower bound and static solutions                             |                                  |

|    | 9.4               | Dynamic data distribution strategies                         |                                  |

|    | 9.5               | Analysis and optimization                                    |                                  |

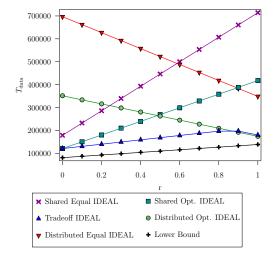

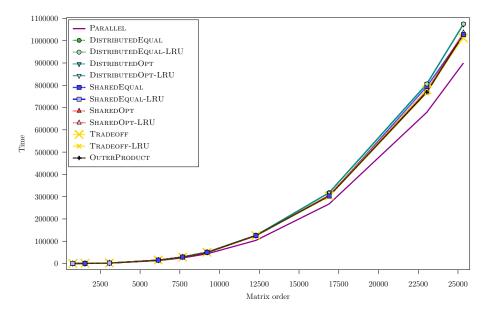

|    | 9.6<br>9.7        | Evaluation through simulations                               |                                  |

|    | 9.7               | Extension to matrix-matrix multiplication                    |                                  |

|    | 9.9               | Conclusion of the chapter                                    |                                  |

|    | ~                 | •                                                            |                                  |

| 10 | Con               | clusion and perspectives                                     | 131                              |

| A  | Bibl              | iography 1                                                   | 133                              |

| В  | Pers              | sonal publications                                           | 143                              |

viii *CONTENTS*

# List of Algorithms

| 1  | Naive-Matrix-Multiply            |

|----|----------------------------------|

| 2  | BLOCKED-MATRIX-MULTIPLY          |

| 3  | PostorderMinMem (Liu's model)    |

| 4  | LIUMINMEM (Liu's model)          |

| 5  | PostorderMinIO (Liu's model)     |

| 6  | PostorderMinMem (dataflow model) |

| 7  | LIUMINMEM (dataflow model)       |

| 8  | PostorderMinIO (dataflow model)  |

| 9  | EXPLORE                          |

| 10 | TopDownMinMem                    |

| 11 | FULLRECEXPAND                    |

| 12 | ParallelChainMinMem 50           |

| 13 | SERIESPARALLELMINMEM             |

| 14 | ParSubtrees                      |

| 15 | SplitSubtrees                    |

| 16 | LISTSCHEDULING                   |

| 17 | LISTSCHEDULINGWITHMEMORYLIMIT    |

| 18 | MEMBOOKINGINNERFIRST             |

| 19 | ACTIVATION                       |

| 20 | SharedOpt                        |

| 21 | BESTDISTRIBFORVOLUME             |

| 22 | BESTDISTRIBFORSTEPS              |

| 23 | DYNAMICOUTER                     |

| 24 | DynamicOuter2Phases              |

# Chapter 1

# Motivation and context

Scientific applications are always looking for increased performance, not only to solve the same problems faster, but also to target larger problems. This is for example the case for numerical simulations: to get more accurate results, one needs to use finer mesh sizes and thus to solve larger systems. Most of the machines devoted to scientific computation, ranging from the small cluster to the supercomputer, are complicated to use efficiently. Firstly, they often embed heterogeneous computing cores, such as dedicated accelerators. Secondly, the memory available for computation is limited and hierarchically organized, leading to non-uniform memory access times. Lastly, supercomputers including a very large number of cores are subject to core failures. In this document, we concentrate on the second point, and more precisely on the fact that the amount of fast memory available for the computation is limited. We propose various scheduling and mapping algorithms that take the memory limit into account and aim at optimizing application performance. We mainly consider two types of applications: well-known linear algebra kernels, such as matrix multiplication, and applications that are described by a directed acyclic graph of tasks. In this latter case, the edges of the graph represent the dependencies between these tasks in the form of input/output data. Note that this task-based representation of computations is very common in the theoretical scheduling literature [34] and sees an increasing interest in High Performance Computing: to cope with the complexity and heterogeneity in modern computer design, many HPC applications are now expressed as task graphs and rely on dynamic runtime schedulers for their execution, such as StarPU [8], KAAPI [44], StarSS [72], and Parsec [16]. Even the OpenMP standard now includes task graph scheduling constructs [71]. We assume that the graph of tasks is known before the application and thus does not depend on the data itself. An example of application which is well modeled by a task graph is the QR-MUMPS software [3], which computes a QR factorization of a sparse matrix using multifrontal direct methods.

In this chapter, we first detail the motivation to optimize algorithms for a limited amount of memory. We then present two basic pebble games that were introduced in the literature to formalize the problem of computing with bounded memory. The first one deals with reducing the memory footprint of a computation, while the second one aims at reducing the amount of input/output operations in an out-of-core computation, that is, a computation that does not fit into the available memory. We then take the opportunity of this thesis to present a quick survey on the lower bounds and algorithms that were proposed in the literature for these two problems. Some of them were only published in specific application domains, and to the best of our knowledge, have never been gathered and presented under the same formalism, as done here. Our objective is to give the intuition of these results, which is why we provide their proof when they are short enough. The contributions of this habilitation thesis, presented in the following chapters, are based on these results and extend some of them.

#### 1.1 Motivation

#### 1.1.1 On the importance of data movement

Fast memory, that is the immediate storage space available for the computation, has always been a scarce resource in computers. However, the amount of available memory has largely increased in the previous decade, so that one could imagine that this limitation is about to vanish. However, when looking at the evolution of memory bandwidth and of processor speed, the future is not so bright: it has been acknowledged that the processing speed of a micro-processor (measured in floating point operations per seconds) has increased annually by 59% on average from 1988 to 2004, whereas the memory bandwidth (measured in byte per second) has increased annually only by 26%, and the memory latency (measured in seconds) only by 5% on the same period [48]. This means that the time to process the data is reduced at a much higher pace to the time to move the data from the memory to the processor. This problem is known as the "memory wall" in micro-processor design, and has been alleviated by the introduction of cache memories: the large but slow memory is assisted with a small but fast cache.

Thus, to overcome the decrease of the memory bandwidth/computing speed ratio, chips manufacturer have introduced a hierarchy of caches. This makes the performance of an application very sensitive to data locality: only the applications that exhibit a large amount of temporal locality (data reuse within a short time interval) or spatial locality (successive use of data from close storage locations) may take advantage of the speed of the processor. Furthermore, the cost of data movement is expected to become dominant also in terms of energy [80, 68]. Thus, avoiding data movement and favoring data reuse are crucial both to obtain good performance and to limit en-

ergy consumption. Numerous works have considered this problem. In this introductory chapter, we concentrate on some theoretical studies among them, namely how to design algorithms and schedules that have good and guaranteed performance in a memory-limited computing environment. In particular, we will not cover the numerous studies in hardware design or compilation techniques that target the same problem, because they are mainly orthogonal to the present approach.

#### 1.1.2 Algorithms and memory usage

Let us consider here a very simple problem, the matrix product, to show how the design of the algorithm can influence the memory usage and the amount of data movement<sup>1</sup>. We consider two square  $n \times n$  matrices A and B, and we compute their product C = AB.

#### **Algorithm 1:** Naive-Matrix-Multiply(n, C, A, B)

```

\begin{array}{c|c} \mathbf{for} \ i = 0 \rightarrow n-1 \ \mathbf{do} \\ \hline \mathbf{for} \ j = 0 \rightarrow n-1 \ \mathbf{do} \\ \hline C_{i,j} = 0 \\ \hline \mathbf{for} \ k = 0 \rightarrow n-1 \ \mathbf{do} \\ \hline C_{i,j} = C_{i,j} + A_{i,k} B_{k,j} \end{array}

```

We consider that this algorithm is executed on a simple computer, consisting of a processing unit with a fast memory of size M. In addition to this limited memory, a large but slow storage space is available. In the following, we assume that this space is the disk and has unlimited available storage space.<sup>2</sup> Our objective is to minimize the data movement between memory and disk, also known as the volume of I/O (input/output), that is the number of A, B and C elements that are loaded from the disk to the memory, or written back from the memory to the disk. We assume that the memory is limited, and cannot store more than half a matrix, i.e.,  $M < n^2/2$ .

In Algorithm 1, all B elements are accessed during one iteration of the outer loop. Thus, as the memory cannot hold more than one half of B, at least  $n^2/2$  elements must be read. For the n iterations, this leads to  $n^3/2$  read operations. This is huge as it is the same order of magnitude of the number of computations  $(n^3)$ .

Fortunately, it is possible to improve the I/O behavior of the matrix product by changing the algorithm. We set  $b = \sqrt{M/3}$  and assume that n is a multiple of b. We consider the blocked version of the matrix product, with

<sup>&</sup>lt;sup>1</sup>A large part of this section is adapted from [83].

<sup>&</sup>lt;sup>2</sup>Note that this study detailed for the case "main memory vs. disk" may well apply to other pairs of storage such as "fast small cache vs. large slower memory".

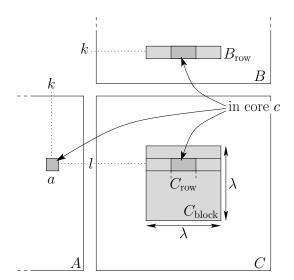

block size b, as detailed in Algorithm 2. In this algorithm  $C_{i,j}^b$  denotes the block of size b at position (i,j) (all elements  $C_{k,l}$  such that  $ib \leq k \leq (i+1)b-1$  and  $jb \leq l \leq (j+1)b-1$ ).

#### **Algorithm 2:** Blocked-Matrix-Multiply(n, C, A, B)

```

\begin{aligned} b &\leftarrow \sqrt{M/3} \\ \textbf{for } i &= 0, \rightarrow n/b - 1 \textbf{ do} \\ & & \textbf{for } j = 0, \rightarrow n/b - 1 \textbf{ do} \\ & & \textbf{for } k = 0, \rightarrow n/b - 1 \textbf{ do} \\ & & & \textbf{Naive-Matrix-Multiply}(n, C_{i,j}^b, A_{i,k}^b, B_{k,j}^b) \end{aligned}

```

Each iteration of the inner loop of the blocked algorithm must access 3 blocks of size  $b^2$ . Thanks to the choice of b, this fits in the memory, and thus, each of these  $3b^2$  elements are read and written at most once. This leads to at most 2M data movements. Since there are  $(n/b)^3$  iteration of the inner loop, the volume of I/O of the blocked algorithm is  $O((n/b)^3 \times 2M) = O(n^3/\sqrt{M})$ .

Changing the algorithm has allowed us to reduce the amount of data movements. The question is now: can we do even better? Interestingly, the answer is no, and it is possible to prove that any matrix product algorithms will perform at least  $\Omega(n^3/\sqrt{M})$  I/O operations. We present here the proof of this results by Toledo [83].

*Proof.* We consider here a "regular" matrix product algorithms, which performs  $n^3$  elementary multiplications (we thus exclude Strassen-like algorithms). We decompose the execution of such an algorithm into phases, such that in all phases, the algorithm exactly performs M I/O operations (except in the last phase, which may contains less). We say that a  $C_{i,j}$  element is alive in a phase if some  $A_{i,k} \times B_{k,j}$  product is computed in this phase.

During phase p, at most 2M elements of A can be used for the computation: at most M may initially reside in the memory, and at most M are read. We denote these elements by  $A_p$ . Similarly, at most 2M elements of B can be accessed during this phase, they are noted  $B_p$ . We distinguish two cases for the elements of  $A_p$ :

- $S_p^1$  is the set of rows of A with at least  $\sqrt{M}$  elements in  $A_p$  (thus,  $|S_1^p| \leq 2\sqrt{M}$ ). Each of these rows can be multiplied with at most  $|B_p|$  elements of B, resulting in at most  $4m^{3/2}$  elementary products.

- $S_p^1$  is the set of rows of A with fewer than  $\sqrt{M}$  elements. Each of these rows contributes to a different alive  $C_{i,j}$ . Thus, they contribute to at most  $\sqrt{M} \times 2M$  elementary multiplications.

Overall, a phase consists in at most  $6M^{3/2}$  products. The total number of full phases is thus lower bounded by  $\lfloor n^3/6M^{3/2} \rfloor \geq n^3/6M^{3/2} - 1$ , and the volume of I/O is at least  $n^3/6\sqrt{M} - 1/M$  which is in  $\Omega(n^3/\sqrt{M})$  as soon as  $M < n^2/2$  (our initial assumption).

This example of the matrix product highlights several facts. Firstly, the choice of the algorithms impacts how the memory is accessed, and several algorithms which have similar computational complexity may exhibit very different memory and I/O behavior. Secondly, it is possible to exhibit lower bounds on the volume of I/O, especially thanks to the analysis in phases. Thirdly, thanks to these lower bounds, we may prove that some algorithms have optimal or asymptotically optimal I/O volume.

In the rest of this introductory chapter, we will present the pebble game models that laid the ground for most theoretical studies on memory or I/O minimization (Section 1.2). We will then present some fundamental results for memory and I/O minimization which are derived from these models and their extensions, and which are the basis of the work presented in this manuscript (Sections 1.3 and 1.4).

#### 1.2 Two pebble game models

In this section, we review two pebble game models that lay the foundations of the problems studied in this manuscript. We first present the classical pebble-game that was introduced to model register allocation problems and is related to memory minimization. We then introduce the I/O pebble-game that deals with data movement minimization.

#### 1.2.1 (Black) pebble game for memory minimization

We present here the first theoretical model that was proposed to study the space complexity of programs. This model, based on a pebble game, was originally used to study register allocation. Registers are the first level of storage, the fastest one, but also a scarce resource. When allocating registers to instructions, it is thus crucial to use them with caution and not to waste them. The objective is thus to find the minimum amount of registers that is necessary for the correct execution of the program. Minimizing the number of registers is similar to minimizing the amount of memory. For the sake of consistency, we present the pebble game as a problem of memory size rather than register number minimization. This does not change the proposed model nor the results, but allows us to present all results of this chapter with the same model and formalism.

The pebble-game was introduced by Sethi [78] to study the space complexity of "straight-line" programs, that is, programs whose control flow

does not depend on the input data. A straight-line program is modeled as a directed acyclic graph (DAG): a vertex represents an instruction, and an arc between two vertices  $i \to j$  means that the results of the vertex i is used for the computation of j.

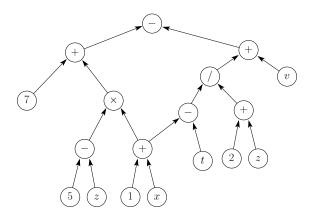

Figure 1.1: Graph corresponding to the computation of the expression  $7 + (5-z) \times (1+x) - (1+x-t)/(2+z) + v$

When processing a vertex, all its inputs (as well as the result) must be loaded in memory, and the goal is to execute the program using the smallest amount of memory. Memory slots are modeled as pebbles, and executing the program is equivalent to playing a game on the graph with the following rules:

- (PG1) A pebble may be removed from a vertex at any time.

- (PG2) A pebble may be placed on a source node at any time.

- (PG3) If all predecessors of an unpebbled vertex v are pebbled, a pebble may be placed on v.

The goal of the game is to put a pebble on each output vertex at some point of the computation, and to minimize the total number of pebbles needed to reach this goal. In this game, pebbling a node corresponds to loading an input in memory (rule PG2) or computing a particular vertex (rule PG3). From a winning strategy of this game, it is thus straightforward to build a solution to the original memory allocation problem.

Note that the game does not ensure that each vertex will be pebbled only once. Actually, in some specific graphs, it may be beneficial to pebble several times a vertex, that is, to compute several times the same values, to save a pebble needed to store its value. A variation of the game, named the *Progressive Pebble Game*, forbids any recomputation, and thus models the objective of minimizing the amount of memory without any increase in the computational complexity. In this latter model, the problem of determining

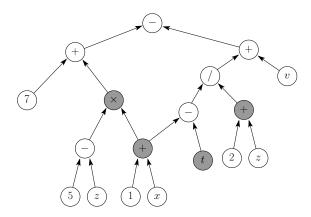

Figure 1.2: Playing the (black) pebble game on the graph of Figure 1.1. Dark nodes are the ones currently pebbled, meaning that four values are now in memory:  $(5-z) \times (1+x)$ , 1+x, t and 2+z.

whether a directed acyclic graph can be processed with a given number of pebbles has been shown NP-hard by Sethi [78]. The more general problem allowing recomputation is even more difficult, as it has later been proved PSPACE-complete by Gilbert, Lengaeur and Tarjan [45]. Another variant of the game slightly changes rule PG3 and allows to *shift* a pebble to an unpebbled vertex if all its predecessors are pebbled. Van Emde Boas [86] shows that it can at most decrease the number of pebbles required to pebble the graph by one, but in the worst case the saving is obtained at the price of squaring the number of moves needed in the game.

A simpler class of programs consists in trees rather than general graphs: for example, arithmetic expressions are usually described by in-trees (rooted directed trees with all edges oriented towards the root), unlike the one of Figure 1.1 which uses a common sub-expression twice. In this special case, the problem gets much simpler: Sethi and Ullman [79] designed an optimal scheme which relies on the following theorem.<sup>3</sup>

**Theorem 1.1.** An optimal solution for the problem of pebbling an in-tree with the minimum number of pebbles using rules PG1 - PG3 is obtained by a depth-first traversal which orders subtrees by non-increasing values of P(i), where the peak P(v) of the subtree rooted at v is recursively defined by:

$$P(v) = \begin{cases} 1 & \text{if } v \text{ is a leaf} \\ \max_{i=1\dots k} P(c_i) + i - 1 & \text{where } c_1, \dots c_k \text{ are the children of } v \\ \text{such that } P(c_1) \ge P(c_2) \ge \dots \ge P(c_k) \end{cases}$$

<sup>&</sup>lt;sup>3</sup>When pebble shifting is allowed, the minimum number of pebbles needed to pebble a tree is the Strahler number (as outlined in [39]), which is a measure of a tree's branching complexity that appears in natural science, such as in the analysis of streams in a hydrographical bassin [82] or in biological trees such as animal respiratory and circulatory systems https://en.wikipedia.org/wiki/Strahler\_number.

The first step to prove this result is to show that depth-first traversals are dominant, i.e., that there exists an optimal pebbling scheme which follows a depth-first traversal. Pebbling a tree using a depth-first traversal adds a constraint on the way a tree is pebbled: consider a tree T and any vertex v whose children are  $c_1, \ldots c_k$ , and assume w.l.o.g that the first pebble that is put in the subtree rooted at v is in the subtree rooted at its leftmost child  $c_1$ . Then, in a depth-first traversal, the following pebbles must be put in the subtree rooted at  $c_1$ , until  $c_1$  itself holds a pebble (and all pebbles underneath may be removed). Then we are allowed to start pebbling other subtrees rooted at  $c_2, \ldots, c_k$ . These traversals are also called postorder, as the root of a subtree is pebbled right after its last child.

To prove that depth-first traversals are dominant, we notice that whenever some pebbles have been put on a subtree rooted at some vertex v, it is always beneficial to completely pebble this subtree (until its root v, which uses a single vertex) before starting pebbling other subtrees.

The second step to prove Theorem 1.1 is to justify the order in which the subtrees of a given vertex must be processed to give a minimal number of pebbles. This result follows from the observation that after having pebbles i-1 subtrees, i-1 pebbles should be kept on their respective roots while the  $i^{\text{th}}$  subtree is being pebbled.

The pebble-game model has been successfully used to obtain space-time complexity tradeoffs, that is, to derive relations between the number of pebbles and the number of moves, such as in [62]. Another variant, called the black-white pebble game has been proposed to model non deterministic execution [61, 67], where putting a white pebble on a node corresponds to guessing its value; a guessed vertex has to be actually computed later to check the value of the guess. In Section 1.4.1, we will come back to this model to present its extension to heterogeneous pebble sizes.

#### 1.2.2 Red-Blue pebble game for data transfer minimization

In some cases, the amount of fast storage (i.e., memory) is too limited for the complete execution of a program. In that case, communication are needed to move data from/to a second level of storage (i.e., disk), which is usually larger but slower. Because of the limited bandwidth of the secondary storage, the amount of data transfers, sometimes called Input/Output (or simply I/O) volume, is a crucial parameter for performance, as seen in Section 1.1.1. Once again, we present this problem for the pair (main memory,disk), but this may well apply to any pair of storages in the usually deep memory hierarchy going from the registers and fastest caches to the slowest storage systems.

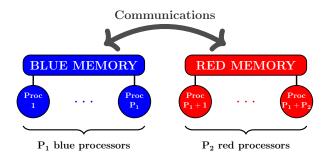

While the first pebble game allows to model algorithms under a limited memory, Hong and Kung have proposed another pebble game to tackle the I/O volume minimization in their seminal article [50]. This game uses two types of pebbles (of different colors) and thus is also called the red/blue pebble game to distinguish with the original (black) pebble game. The goal is to distinguish between the main memory storage (represented by red pebbles), which is fast but limited, and the disk storage (represented by blue pebbles), which is unlimited but slow. As in the previous model, a computation is represented by a directed acyclic graph. The red and blue pebbles can be placed on vertices according to the following rules:

- (RB1) A red pebble may be placed on any vertex that has a blue pebble.

- (RB2) A blue pebble may be placed on any vertex that has a red pebble.

- (RB3) If all predecessors of a vertex v have a red pebble, a red pebble may be placed on v.

- (RB4) A pebble (red or blue) may be removed at any time.

- $\bullet$  (RB5) No more than S red pebbles may be used at any time.

Figure 1.3: Playing the red/blue pebble game on the graph of Figure 1.1. The two red nodes represent values that are currently in memory, whereas the two blue nodes represent values that have been computed but then been evicted to disk. Before pebbling node (1+x)-t, a red pebble has to be put again on node 1+x, corresponding to reading this value from the disk.

The goal of the game is to put a red pebble on each output vertex at some point of the computation, and to use the minimum number of RB1/RB2 rules to reach this goal. Red vertices represents values that currently lies in the main memory, after a computation, while blue pebbles represents values that are on disk. A value on disk may be read from disk (rule RB1) and similarly a value in memory can be stored on disk (rule RB2). Finally, we may compute a value if all its inputs are already in memory (rule RB3).

The volume of I/O is the total number of moves using rules RB1 or RB2, that is the total number of data movements between memory and disk.

The main results of Hong and Kung [50] relies on the decomposition of a computation, that is, a traversal of the graph, into a S-partition. A S-partition is defined as a family of vertex subsets  $V_1, \ldots V_h$  such that:

- (C1) The  $V_i$ s define a partition of the graph's vertices;

- (C2) Each  $V_i$  admits a *dominator set* of at most S vertices, where a dominator set D of V is a set of vertices such that any path from a source to a vertex of V goes through a vertex of D;

- (C3) The minimum set of each  $V_i$  has at most S vertices, where the minimum set of V is the set of vertices in V that have no successors in V;

- (C4) There is no cyclic dependence between the  $V_i$ s (we say there is a dependence between two subsets  $V_i, V_j$  if there exists an arc  $u \to v$  such that  $u \in V_i$  and  $v \in V_j$ ).

Using this S-partition, Hong and Kung proves the following theorem:

**Theorem 1.2.** Any complete computation of a directed acyclic graph using at most S red pebbles is associated to a 2S-partition such that

$$S(h-1) \le V \le Sh$$

where V is the volume of I/O, i.e., the total number of moves using rules RB1 and RB2 in the computation.

One of the corollaries of this result was a first proof of the  $O(n^3/\sqrt{M})$  bound on I/O volume for product of two  $n^2$  matrices, which was later simplified by Irony, Toledo and Tiskin [54] to derive the results presented in Section 1.1.2. In the original proof by Hong and Kung, a S-partition is constructed by decomposing any valid computation into phases where at most S moves using rules RB1 and RB2 occur in each phase. Thus, a dominator set of each  $V_i$  can be constructed by considering both the vertices holding a red pebble at the beginning of  $V_i$  and the vertices red by using rule RB1. As in the previous proof, each case contributes for at most S vertices, thus proving a 2S-partition.

Thanks to this theorem, Hong and Kung derive the following lemma:

**Lemma 1.1.** For any directed acyclic graph G, given a memory of size M, the minimum I/O volume satisfies

$$Q \ge S(H(2M) - 1)$$

where H(2M) is the minimum size of any 2M-partition of G.

This lemma is then used to derive I/O lower bounds on some specific computations, such as the Fast Fourier Transform or the matrix multiplication.

In [50], Hong and Kung laid the foundations of I/O analysis, by introducing some key ideas: consider phases where the number of data transfers is equal to the size of the memory, and then bound the number of elementary computation steps that may be perform in each phase. This is precisely what we have done in Section 1.1.2 to exhibit a lower bound on the I/O operations of the matrix product. Since then, it has been largely used for the I/O analysis of numerous operations and extended to more complex memory models. Among many others, the book of Savage [75] presents several extensions, in particular for a hierarchical memory layout. Some recent works still build on the Hong and Kung model to compute I/O lower bounds for complex computational directed acyclic graphs [36]. In the following section, we will present some extensions of these ideas to design algorithms that minimizes I/O volume for linear algebra operations.

#### 1.3 I/O lower bounds for matrix computations

We now present some development of the techniques introduced in the previous section, in order to derive I/O lower bounds for linear algebra operations. We first review some extensions on the matrix product presented in Section 1.1.2, and then move to extensions for other linear algebra operations.

#### 1.3.1 More on matrix product

Before moving to more complex linear algebra operations, we go back to the classical matrix product in order to present some improvements and extensions of the basic result presented in Section 1.1.2.

In [54], Irony, Toledo and Tiskin proposed a new proof of the lower bound on data transfers presented in Section 1.1.2. This proof also relies on a decomposition into phases of M data transfers each, where M is the size of the memory. However, the upper bound on the number of elementary computations that may be performed in one phase comes from the following lemma.

**Lemma 1.2.** Consider the conventional matrix multiplication algorithm C = AB. With access to  $N_A$  elements of A,  $N_B$  elements of B and contributions to  $N_C$  elements of C, no more than  $\sqrt{N_A N_B N_C}$  elementary multiplications can be performed.

This lemma relies on the discrete Loomis-Whitney inequality [66], which relates the cardinality of a finite subset V of  $\mathbb{Z}^D$  to the cardinalities of its

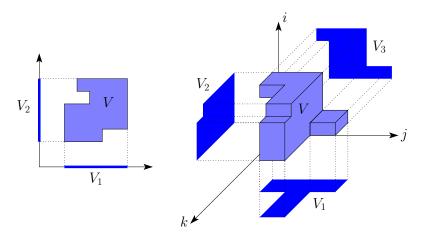

d-dimensional projections, for  $1 \le d \le D$ . In particular, as illustrated on the right part of Figure 1.4, for D=3 and d=2, if  $V_1, V_2, V_3$  denotes the orthogonal projections of V on each coordinate planes, we have

$$|V|^2 \le |V_1| \cdot |V_2| \cdot |V_3|,$$

where |V| is the volume of V and  $|V_i|$  the area of  $V_i$ .

Figure 1.4: Use of Loomis-Whitney inequality, in two and three dimensions (left: D=2, d=1, which gives  $|V| \leq |V_1| \cdot |V_2|$ , right: D=3, d=2, leading to  $|V|^2 \leq |V_1| \cdot |V_2| \cdot |V_3|$ ).

In our context, V is the set of indices (i, j, k) such that the elementary product of  $A_{i,k}B_{k,j}$  is performed in a given time interval. The projection  $V_1$  of V along the i axis corresponds to the set of B elements accessed for the computation, the projection  $V_2$  along the j axis corresponds to the set of used A elements, and the projection  $V_3$  along the k axis corresponds to elements of C for which some contribution is computed. The lemma directly follows from the Loomis-Whitney inequality.

This lemma is used in [54] with the same decomposition in phases presented in Section 1.1.2: in a phase, at most M data transfers (read and write) are performed. The number  $N_A$  of elements of A which can be used for the computation during one phase is bounded by 2M, as at most M elements are in the memory, and at most M can be read. Similarly, we have  $N_B \leq 2M$  and  $N_C \leq 2M$ . Thus, the number of elementary products during one phase is at most  $\sqrt{N_A N_B N_C} \leq 2\sqrt{2} M^{3/2}$ . Therefore, the number of full phases is at least  $\lfloor n^3/2\sqrt{2}M^{3/2} \rfloor$  and the number of data transfers is at least

$$\left(\frac{n^3}{2\sqrt{2}M^{3/2}} - 1\right)M.$$

In [59], Langou carefully optimized this analysis and obtained a lower bound of  $2\frac{n^3}{\sqrt{M}} - 2M$  on data transfers.

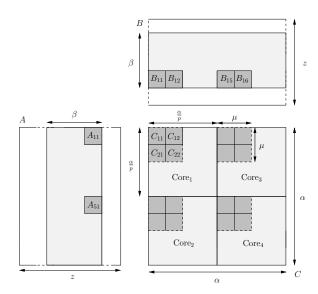

Similar bounds may also be obtained for parallel algorithms. On P processors, at least one processor is in charge of computing  $n^3/P$  elementary products. By applying the previous reasoning to this processor, Irony, Toledo and Tiskin [54] proved that one processor has to perform at least  $\frac{n^3}{2\sqrt{2}P\sqrt{M}}-M$  communications. They also studied the case of 2D-block algorithms algorithm (such as Algorithm 2) where each processors holds  $O(n^2/P)$  elements, and the case of 3D-block algorithms, where the input matrices are replicated and each processor holds  $O(n^2/P^{2/3})$  elements. In both cases, they exhibit communication lower bounds and show there exist algorithms in the literature that are asymptotically optimal.

#### 1.3.2 Extension to other matrix computations

In [10], Ballard, Demmel, Holtz and Schwartz extended the previous results to many other matrix computations, by introducing the notion of generalized matrix computations. They noticed that many existing matrix algorithms could be formulated as two nested loops on i and j containing an update of the following form:

$$\forall (i,j), \quad C_{i,j} \leftarrow f_{i,j} \left( g_{i,j,k}(A_{i,k}, B_{k,j}) \text{ for } k \in S_{i,j}, K \right)$$

$$\tag{1.1}$$

where:

- Matrices A,B,C may be reordered, and may even overlap;

- $f_{i,j}$  and  $g_{i,j,k}$  represent any functions that depend non-trivially on their arguments, that is, the computation of  $f_{i,j}$  requires at least one data to be kept in memory while scanning its arguments, and both  $A_{i,k}$  and  $B_{k,j}$  must be in memory while computing  $g_{i,j,k}$ ;

- K represents any other arguments for  $f_{i,j}$

The formulation of the matrix product as a generalized matrix computation is straightforward: simply take the product as  $g_{i,j,k}$ ,  $S_{i,j} = 1, ..., n$  and the sum as  $f_{i,j}$ . Moreover, other matrix computations, such as the LU Gaussian elimination, can also be described in this form. The classical algorithm for LU elimination is made of two nested loops on i and j containing the following updates:

$$L_{i,j} = (A_{i,j} - \sum_{k < j} L_{i,k} \cdot U_{k,j}) / U_{j,j} \text{ for } i > j$$

$$U_{i,j} = A_{i,j} - \sum_{k < i} L_{i,k} \cdot U_{k,j} \text{ for } i \le j$$

It may be transformed into Equation (1.1) by setting A = B = C, where the lower triangular part of A classically represents L and its upper triangular part represents U,  $g_{i,j,k}$  multiplies  $A_{i,k} = L_{i,k}$  with  $A_{k,j} = U_{k,j}$  for all indices k in  $S_{i,j} = \{k < j\}$  if i > j and  $S_{i,j} = \{k < i\}$  otherwise, and finally  $f_{i,j}$  performs the sum of its arguments, subtracts the result from  $A_{i,j}$  (and divides it by  $U_{j,j}$  in the case i > j).

Then, a generalized matrix computation may be analysed by decomposing the computations into phases corresponding to a given amount of data transfers, as in the case of the matrix product, in order to derive I/O lower bounds. Again, exactly M data transfers are perform in a phase (except in the last one). In order to bound the number of computations done in a phase, Ballard et al. propose to distinguish both the origin (root) and the destination of each data:

- Root 1: the data is already in the memory in the beginning of the phase, or is read during the phase (at most 2M such data);

- Root 2: the data is computed during the phase (no bound);

- Destination 1: the data is still in the memory at the end of the phase, or is written back to disk (at most 2M such data);

- Destination 2: the data is discarded (no bound).

Usually, we may discard the case where the algorithm computes some data which is then discarded (Root 2/Destination 2). Then, we consider V the set of indices (i,j,k) of  $g_{i,j,k}$  operations computed in a given phase,  $V_A$  the set of indices (i,k) of A values used in the computations,  $V_B$  the set of indices (k,j) of B values used in the computations, and  $V_C$  the set of indices (i,j) of the corresponding  $f_{i,j}$  operations. For each of the A,B and C cases, all data either originate from Root 1 or target Destination 1 (since we exclude Root 2/Destination 2), and thus we can bound  $V_X \leq 4M$ . Using the Loomis-Whitney inequality, we know that  $V \leq \sqrt{(4M)^3}$ . For a total number G of  $g_{i,j,k}$  computations, at least  $\lfloor G/V \rfloor$  phases are full, and thus the number of data transfer is lower bounded by

$$M \left| \frac{G}{\sqrt{(4M)^3}} \right| \ge \frac{G}{8\sqrt{M}} - M.$$

In [10], this analysis is also successfully applied to Cholesky and QR factorizations, and to algorithms computing eigenvalues or singular values.

The discovery of these lower bounds led to the design of parallel algorithms for many linear algebra operations that aim at minimizing the amount of communications while keeping up with perfect load balancing

in order to optimize performance. These algorithms are usually known as *communication-minimizing*, *communication-avoiding* or *communication-optimal* (see [9, 29, 30] among others).

#### 1.4 Memory-aware task graph scheduling

We now move to the problem of scheduling applications described by directed acyclic task graphs, as presented in the introduction of this chapter. A major difference with what was presented above is the heterogeneity of the data sizes: up to now, we only considered data of unit size. However, task graphs usually model computations of coarser grain, so that tasks may produce data of larger and heterogeneous sizes.

Most existing studies on memory-aware task graph scheduling were done in a very particular application domain, namely the factorization of sparse matrices through direct methods. We gather here their main results as well as the main proof arguments. For the sake of coherence, we translate these results into our own formalism.

#### 1.4.1 Generalized pebble games for task graph scheduling

In [65], Liu introduced a variant of the (black) pebble game, called the generalized pebble game to account for data with different sizes. In this model, a vertex of the directed acyclic graph is no longer a single instruction which needs a single register, but a coarser-grain task with a given memory requirement. His objective was to study a particular linear algebra operation (the sparse matrix factorization using direct multifrontal method), which is described as a tree of elementary factorizations. Before processing the actual factorization, the tree of tasks is built, and it is easy to compute what is the amount of memory needed by each task. To model the computation, he proposed to associate a value  $\tau_x$  with each vertex x, which represents the number of pebbles needed to satisfy x. The rules of the (black) pebble game are then adapted to this new model:

- (GPG1) A pebble may be removed from a vertex at any time.

- (GPG2) A pebble may be placed on a source node at any time.

- (GPG3) If all predecessors of an unpebbled vertex v are satisfied, new pebbles may be placed on v, or moved to v from its predecessors.

The objective is, starting with no pebbles on the graph, to satisfy all outputs of the graph (that is, the root of the tree in this particular case). Note that because rule GPG3 allows to move pebbles, this is an extension of the variant with pebble shifting of the black pebble game presented in Section 1.2.1. In this model, the number of pebbles needed to satisfy a vertex v represents the

size of the output of the computational task of v, as these pebbles must stay on v until its successor is computed (i.e., pebbled). Rather than number of pebbles, we will now refer to memory amounts:  $\tau_k$  represents the size of the output data of task k, and the goal is to minimize the *peak memory*, that is the maximum amount of memory used by a traversal at any time.

#### 1.4.2 Peak memory minimizing traversals for task trees

Since the generalized pebble game is an extension of the pebble game, it naturally inherits its complexity: computing a schedule of a given graph that minimizes the peak memory is NP-complete. Adapting the algorithm described in Section 1.2.1 to compute optimal tree traversals is an interesting question, that has been studied by Liu [64, 65]. First, we should note that postorder traversals are not dominant anymore in this heterogeneous model: it may well happen that a vertex v has a large output  $\tau_v$  while its input (the sum of its children outputs) is relatively small. In that case, it is not true anymore that v must be processed right after its last child, as this will increase the memory consumption, and thus decrease the memory available for other parts of the tree. However, postorder traversals are simple to implement and it is thus interesting to compute the one with smallest peak memory.

#### Best postorder traversal

The following theorem, proposed by Liu [64] is an adaptation of Theorem 1.1 for heterogeneous trees. It allows to compute the best postorder traversal for peak memory minimization, which is given in Algorithm 3.

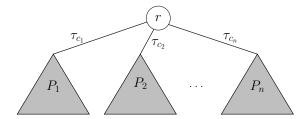

**Theorem 1.3.** Let T be a vertex-weighted tree rooted at r, where  $\tau_v$  is the size of the data output by vertex v. Let  $c_1, \ldots, c_k$  be the children of r and  $P_i$  be the smallest peak memory of any postorder traversal of the subtree rooted at  $c_i$ . Then, an optimal postorder traversal is obtained by processing the subtrees by non-increasing  $P_i - \tau_{c_i}$ , followed by r. Assuming that  $P_1 - \tau_{c_1} \ge P_2 - \tau_{c_2} \ge \cdots P_k - \tau_{c_k}$ , the number of pebbles needed by the best postorder traversal is:

$$P = \max \left( P_1, \tau_{c_1} + P_2, \tau_{c_1} + \tau_{c_2} + P_3, \dots \sum_{i=1}^{k-1} \tau_{c_i} + P_k, \tau_r \right)$$

(1.2)

*Proof.* This results can be proven by a simple exchange argument: Consider two subtrees rooted at  $c_i$  and  $c_j$  such as  $P_i - \tau_{c_i} \leq P_j - \tau_{c_j}$ . If the subtree rooted at  $c_i$  is processed right before  $c_j$ , their contribution to the peak memory is:

$$P_{i,j} = \sum_{k \in B} \tau_{c_k} + \max \left( P_i, c_i + P_j \right)$$

Figure 1.5: Illustration of Theorem 1.3.

where  $\{c_k, k \in B\}$  is the set of roots of subtrees processed before i. If we exchange the two subtrees, that is, process i right after j, we get:

$$P_{j,i} = \sum_{k \in R} \tau_{c_k} + \max \left( P_j, c_j + P_i \right)$$

Note that  $P_j \leq c_i + P_j$  and  $c_j + P_i \leq c_i + P_j$  since  $P_i - \tau_{c_i} \leq P_j - \tau_{c_j}$ . Thus  $P_{j,i} \leq P_{i,j}$ .

```

Algorithm 3: PostorderMinMem (T)

```

**Data:**  $T = (V, E, \tau)$ : tree with vertex-weights

**Result:**  $(\pi, P)$ : Postorder schedule and its minimal peak memory

if  $V = \{u\}$  then return  $((u), \tau_u)$

Let r be the root of T,  $c_1, c_2 \dots c_k$  its children and  $T_1, T_2, \dots T_k$  the corresponding subtrees

for i = 1 to k do

$(\pi_i, P_i) \leftarrow \text{PostorderMinMem}(T_i)$

Sort the k subtrees such that  $P_1 - \tau_{c_1} \ge \cdots \ge P_k - \tau_{c_k}$

$\pi \leftarrow \text{Concatenate } \pi_1, \pi_2, \dots, p_k \text{ and add } r \text{ at the end}$

Compute P as in Equation (1.2)

return  $(\pi, P)$

#### Best general traversal

Despite their simplicity, postorder traversals are not optimal. In a second study, Liu proposed a more complex algorithm to compute optimal traversals for peak memory minimization [65]. This strategy, detailed in Algorithm 4 consists in a recursive algorithm. To compute an optimal traversal for a tree rooted at vertex k, it first recursively computes an optimal traversal for the subtrees rooted at each of its children, then merges them and finally adds the root at the end. The difficult part is of course how to merge the children traversals. Contrarily to a postorder traversal, in a general traversal, there is no reason to process the subtrees one after the other. One may want to

interleave the processing on one subtree with that of the others. Liu makes the observation that, in an optimal traversal, the switching points between the subtrees' processing have to be local minima in the memory profile: while processing one subtree  $T_i$ , there is no reason to switch to  $T_j$  if one can reduce the memory needed for  $T_i$  by processing one more task. This remark leads to slicing the traversal into atomic parts, called *segments*. The end-points of segments (which are local minima in the memory profile) are called *valleys*, while the peak memory vertices of each segment are called *hills*. The memory consumption at valleys and hills are denoted by V and H and are defined as follows, for a given traversal:

- $H_1$  is the peak memory of the whole traversal;

- $V_1$  is the minimum amount of memory which occurs after the step when  $H_1$  is (last) reached;

- $H_2$  is the peak memory after the step when  $V_1$  is (last) reached;

- $V_2$  is the minimum amount of memory occurring after the step when  $H_2$  is (last) reached;

- etc

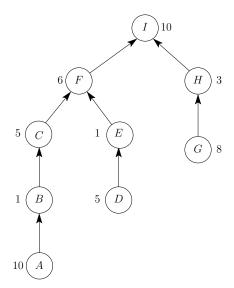

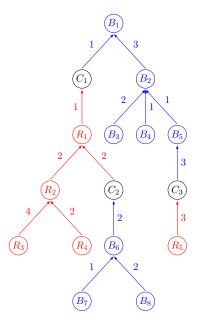

The sequence of hill-valley ends when the last vertex is reached. The segments consist of the vertices comprised between two consecutive valleys  $]V_i, V_{i+1}]$ . Take for example the tree depicted on Figure 1.6, and consider first the subtree rooted in C. It has a single valid traversal, (A, B, C) which is decomposed in two segments [A, B] (H = 10, V = 1) and [C] (H = 5, V = 5). Its sibling subtree, rooted at E, has a traversal consisting in a single segment [D, E] (H = 5, V = 1).

Figure 1.6: Example of tree in Liu's model.

To merge the traversals of the subtrees, the first step is to compute all hill-valley segments. Then the lists of segments are merged using the following criterion: if several segments are available (one for each subtree in the beginning), it is always beneficial to start with the segment with the maximum (hill - valley) difference. Intuitively, the residual memory will only increase when processing segments, so it is better (i) to start with the segment with larger peak memory (hill) to avoid large memory consumption later, and (ii) to start with the segment with smaller residual memory (valley) to ensure an increase of memory as small as possible. Note that this is the same argument that made us process subtrees in decreasing  $P_i - \tau_i$  to derive the best postorder.

In the example of Figure 1.6, when merging the traversals from subtrees rooted at C and E, we will first take segment [A,B] (H-V=9), then [D,E] (H-V=4) and finally [C] (H-V=0). By adding the root, we get the optimal traversal (A,B,D,E,F) for this subtree, now decomposed in the following segments:

| segment | hill | valley |

|---------|------|--------|

| A       | 10   | 1      |

| [D, E]  | 6    | 2      |

| [C,F]   | 6    | 6      |

The subtree rooted at H is a single segment [G, H] (H = 8, V = 3). We repeat the same merging procedure and get the following optimal traversal: (A, B, G, H, D, E, C, F, I), of peak memory 10. Note that the best postorder traversal reaches a peak memory of 13 (G, H, A, B, C, D, E, F, I).

In [65], Liu proves that the worst-case runtime complexity of the algorithm is in  $O(n^2)$ , where n is the number of nodes in the tree. To reach this complexity, a multiway-merge algorithm is used to merge t hill-valley segments in time  $O(n \log t)$ . Surprisingly, this algorithm seems to have been independently rediscovered by Lam et al. [58]. Using optimized data structures for storing the segments, they decreased its complexity to  $O(n \log^2 n)$ .

```

Algorithm 4: LIUMINMEM (T)

```

$\pi \leftarrow \text{Merge segments } s_i^j \text{ sorted by non-increasing } H_i^j - V_i^j, \text{ add the root } r \text{ at the end}$

return  $\pi$

This algorithm derives from Yannakakis work on min-cut linear arrangement [89]. This is the problem of finding a linearization of an undirected (unweighted) graph such that for any point of this linear ordering, the number of edges that cross this point (cutwidth) is minimal. This problem was known to be NP-complete for general graphs [42] and Yannakakis proposed a polynomial algorithm for undirected trees. Note that adding weights renders min-cut linear arrangement NP-complete on undirected trees [69]. The peak memory minimization presented above exactly corresponds to the weighted version of min-cut linear arrangement, but on directed trees when all edges are directed towards the root.

#### 1.4.3 Minimizing I/O volume when scheduling task trees

We now move to the case where the available memory is too limited and cannot accommodate all the data needed for the processing of one tree, as presented in Sections 1.2.2 and 1.3. This corresponds to a tree with peak memory larger than the available memory. Our objective is then to make a moderate use of the secondary storage, that is, to minimize the amount of data movement between fast memory and disk. This is frequently called out-of-core computation. In this context, Agullo et al. show how to compute the postorder traversal that minimizes the I/O volume [4].

We consider a given postorder described by a function PO such that PO(i) < PO(j) means that i is processed before j. We define the storage requirement, which may be larger than the available memory M, of a subtree  $T_i$  rooted at node i, which is very similar to the peak memory of a postorder seen in the previous section:

$$S_i = \max \left( \tau_i, \max_{j \in Children(i)} \left( \sum_{k \in PS(j)} \tau_k + S_j \right) \right)$$

where Children(i) denotes the set of children of task i, PS(j) is the set of siblings of j that are scheduled before i in PO (formally,  $PS(j) = \{k \in Children(i), PO(k) < PO(j)\}$ ). The amount  $A_i$  of main memory that is used to processed this subtree in PO is then  $A_i = \min(S_i, M)$ . Finally, the I/O volume of this traversal can be computed recursively:

$$V_i = \max \left( \underbrace{\max_{j \in Children(i)} \left( \sum_{k \in PS(j)} \tau_k + A_j \right)}_{\text{peak memory demand during the processing of } T_i \right) + \sum_{j \in Children(i)} V_j$$

The only term in the previous formula that depends on the subtree ordering is

$$\max_{j \in Children(i)} \left( \sum_{k \in PS(j)} \tau_k + A_j \right).$$

We recognize the previous expression of the peak memory of a postorder traversal, where  $P_j$  has been replaced by  $A_j$ . Similarly, this expression is minimized when subtrees are processed in non-increasing order of  $A_i - \tau_i$ , which is done by Algorithm 5.

```

Algorithm 5: PostorderMinIO (T, M)

```

**Data:**  $T = (V, E, \tau)$ : tree with vertex-weights, M: memory bound **Result:**  $(\pi, S)$ : postorder schedule with minimal I/O and its storage requirement S

if  $V = \{u\}$  then return  $((u), \tau_u)$

Let r be the root of T,  $c_1, c_2 \dots c_k$  its children and  $T_1, T_2, \dots T_k$  the corresponding subtrees

for i = 1 to k do  $(\pi_i, S_i) \leftarrow \text{PostorderMinIO}(T_i)$   $A_i \leftarrow \min(S_i, M)$

Sort the k subtrees such that  $A_1 - \tau_{c_1} \ge \cdots \ge A_k - \tau_{c_k}$  $\pi \leftarrow \text{Concatenate } \pi_1, \pi_2, \dots, p_k \text{ and add } r \text{ at the end}$

$$S \leftarrow \max \left( \tau_i, \max_{1 \le j \le k} \sum_{l=1}^{j-1} \tau_l + S_j \right)$$

return  $(\pi, S)$

#### 1.5 Conclusion

We presented in this chapter a few theoretical studies that allow us to estimate the amount of memory needed for a computation, or the amount of data movement between the main memory and a secondary storage, whenever the former is too limited in size. The two seminal works [78, 50] both rely on playing games with pebbles, which represent storage slots in the primary or secondary storage. They have later been extended to derive I/O lower bounds for several types of computations, including matrix operations, and to schedule task graphs in a memory-limited computing environnement. Note that the work on task graphs is still subject to many limitations: indeed, it is restricted to trees, it does not take into account parallel processing, nor the fact that memory can be distributed. In the following chapters, we will extend these results to overcome some of these limitations.

The choice of the results presented above is subjective and influenced by the rest of the manuscript: we have mainly concentrated on linear algebra operations and task graph scheduling, as it lays the basis for the extensions presented in the following chapters. There exist numerous studies that take a different approach to study algorithms under memory limited conditions.

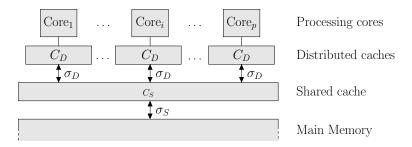

Models for parallel processing using shared memory were first proposed based on the PRAM model [56]. On the opposite, distributed memory systems were studied through models such as LogP [26]. The External Memory model [1, 88] was proposed to account for I/O between the memory and the cache, of limited size M and block size B, which corresponds to the size of the consecutive data that is read/written in a single step from/to the memory. It has later been extended to several distributed caches sharing the same memory (Parallel External Memory) [7]. Most of the studies in these models aim at deriving the complexity of fundamental operations (sorting, prefix sum), and sometimes more specific operations (graph algorithms, Fast Fourier Transform, LU factorization).

The idea of cache-oblivious algorithms as proposed in [41] is to design algorithms that do not depend on any machine-related parameters, such as cache size, but that minimize the amount of data moved to the cache, or even through a hierarchy of caches. The main idea to design such algorithms is to use a recursive divide-and-conquer approach: the problem is divided into smaller and smaller subproblems. Eventually, the data of a subproblem will totally fit into the cache (and similarly for smaller subproblems) and is computed without any data transfer. Such algorithms have been proposed for several operations that are naturally expressed in a recursive way, such as Fast-Fourier-Transform, matrix multiplication, sorting or matrix transposition.

# Part I Task graph scheduling with limited memory

#### Foreword

In the following chapters, we present some contributions on memory-aware task graph scheduling: we target either peak-memory minimization, or in the case of a bounded memory, total I/O volume minimization or makespan minimization. Most of these results builds on the previous algorithms designed for trees and described in the previous chapter (more specifically, Algorithms Postorderminmem, Liuminmem and Postorderminio).

Before presenting our contributions, we first introduce in Chapter 2 a new and more flexible model of memory-aware task graphs, that is used throughout the next chapters, as well as the straightforward adaptation of these three algorithms in this model. Then, Chapter 3 presents new results on the sequential processing of trees, Chapter 4 shows an extension to Series-Parallel graphs, Chapter 5 focuses on processing task graphs on hybrid platforms, and Chapter 6 concentrates on the parallel processing of task trees.

# Chapter 2

# Memory-aware dataflow model

We start by introducing a new task graph model for structured applications that takes memory footprint into account; this model, called the dataflow model, is used throughout the next four chapters. We prove that it inherits the complexity<sup>1</sup> of the pebble game, shows its equivalence with Liu's generalized pebble game on trees, and then adapt the three algorithms presented in the previous chapter for trees to this model.

# 2.1 Proposed dataflow model

We consider structured applications described by a directed acyclic graph (DAG) G = (V, E), where vertices represent tasks and edges represent the dependencies between these tasks, in the form of input/output data. The integer n denotes the number of vertices in V, which are indifferently called tasks or nodes. We adopt a different model for introducing weights representing the memory behavior of the tasks, which we believe is more general and better suited for general task graphs (in opposition to trees). In our model, both vertices and edges are weighted: the weight on vertex i, denoted by  $m_i$ , accounts for the memory size of the program of task i as well as its temporary data, that is, all the data that must be kept in memory as long as task i is running, but can safely be deleted afterwards. The weight of edge (i,j), denoted by  $d_{i,j}$ , represents the size of the data produced by task i and used as an input by task j.

Trees are a notable particular type of graphs that we study in the following chapters. We denote by Children(i) the set of children of a node iand by parent(i) its parent. We generally consider in-trees, with all depen-

$<sup>^1\</sup>mathrm{In}$  all contributions, "complexity" refers to "runtime complexity", unless otherwise stated.

28 CHAPTER 2.

dencies oriented towards the root. For such trees, we simplify the notation  $d_{i,parent(i)}$  to  $d_i$ .

We now characterize the memory behaviour of a sequential processing of the tree. We assume that during the processing of a task, both the input data, the output data and the program and temporary data must reside in memory. The memory needed for processing of task i is thus

$$\mathit{MemReq}(i) = \sum_{(j,i) \in E} d_{j,i} + \sum_{(i,k) \in E} d_{i,k} + m_i.$$

Note that other data (not involving task i) may be stored in memory during this processing. After processing a subset V' of nodes, if there is no ongoing computation, the size of the data remaining in memory is given by

$$\sum_{\substack{(i,j) \in E \text{ s.t.} \\ i \in V' \text{ and } j \notin V'}} d_{i,j}.$$

Finally, if task k is being processed and tasks in V' are completed, the size of the data in memory is:

$$\begin{aligned} \mathit{MemUsage}(V',k) = \sum_{\substack{(i,j) \in E \text{ s.t.} \\ i \in V' \text{ and } j \not\in V'}} d_{i,j} + m_k + \sum_{(k,j) \in E} d_{k,j}. \end{aligned}$$

Note that the first sum accounts among other for the input data of task k, while the second one contains its output data. In the sequential case, a schedule of the tasks (also called traversal of the graph) is defined by a permutation  $\sigma$  of [1,n] such that  $\sigma(t)=i$  indicates that task i is processed at step t. For a given schedule  $\sigma$ , the peak memory can be computed as follows:

$$PeakMemory(\sigma) = \max_{t=1,...n} MemUsage(\{\sigma(t') \text{ with } t' < t\}, \sigma(t)).$$

# 2.2 Emulation of the pebble game and complexity

This dataflow model differs from the original pebble game presented in the previous chapter (Section 1.2.1) as it considers that a task with several successors produces a different data for each of them, whereas in the pebble game, a single pebble is placed on such a task to model its result. However, we show in the following theorem that the dataflow model is able to emulate the pebble game, and thus, inherits its complexity.

**Theorem 2.1.** Let G = (V, E, d, m) be a vertex- and edge-weighted graph representing a computation in the dataflow model. Computing the minimum peak memory of any schedule of G is PSPACE-complete.

*Proof.* The problem is clearly in PSPACE, as checking all n! possible schedules of a graph may easily be done in polynomial space. We prove the completeness by transforming a DAG G representing a computation in the pebble game to another DAG G' under the dataflow model and showing that any schedule in G corresponds to a schedule in G' with the same peak memory. The final result follows from the pebble game being PSPACE complete on DAGs without recomputation [45].

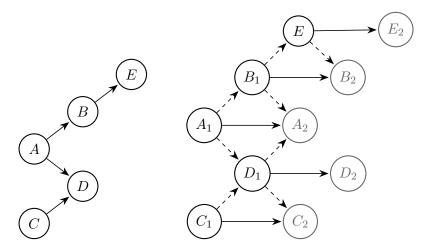

Let G = (V, E) be a DAG representing a computation under the pebble game model. We build the dataflow graph G' = (V', E', d, m) such that:

- For each node i of V, we define two nodes  $i_1$  and  $i_2$  of V', connected by an edge  $(i_1, i_2)$  of unit weight  $(d_{i_1, i_2} = 1)$ . Intuitively,  $i_1$  represents the allocation of the pebble on i and  $i_2$  its removal. The edge weight stands for the cost of the pebble between these two events.

- For each edge (i, j) of E, we build two edges  $(i_1, j_1)$  and  $(j_1, i_2)$  in E' of null weight  $(d_{i_1,j_1} = d_{j_1,i_2} = 0)$ . The first edge states that a pebble must be placed on i before placing one on j, and the second edge ensures that j is pebbled before the removal of the pebble on i.

- All nodes have temporary data of null size  $(m_i = 0 \text{ for all } i)$ .

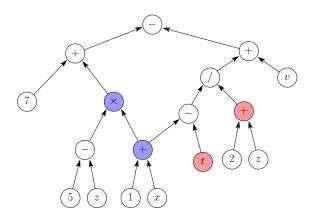

Figure 2.1 illustrates this construction on a toy example. We now prove that G can be traversed with B pebbles without recomputation if and only if G' can be scheduled with a memory of size B.

Figure 2.1: Example of the transformation of an instance of the pebble game (left) into an instance of peak memory minimization in the dataflow model (right). Dashed edges have null weight.

First, we suppose that there exists a pebbling scheme  $\pi$  which processes G with B pebbles. We transform  $\pi$  into a schedule  $\sigma$  of G: when  $\pi$  pebbles

30 CHAPTER 2.

a node i of G,  $\sigma$  executes the node  $i_1$  of G'; when  $\pi$  removes a pebble from a node i of G,  $\sigma$  executes the node  $i_2$  of G'. One can easily check that  $\sigma$  is a valid schedule on G' as  $\pi$  is a valid traversal of G without recomputation. Besides, at any time, the memory used by  $\sigma$  is equal to the numbers of nodes i of G such that  $i_1$  is executed but not  $i_2$ , which is equal to the number of pebbles required by  $\pi$ , so that  $\sigma$  is a valid schedule of G using a memory of size G.

Now, we suppose there exists a schedule  $\sigma$  of G' with a memory peak equal to B. We transform  $\sigma$  into a pebbling scheme  $\pi$  of G: when  $\sigma$  executes a node  $i_1$ ,  $\pi$  pebbles the node i, and when  $\sigma$  executes a node  $i_2$ ,  $\pi$  removes the pebble of node i. Similarly, we easily verify that  $\pi$  is a valid pebbling scheme of G without recomputation since  $\sigma$  is a valid traversal of G', and that  $\pi$  uses no more than B pebbles.

# 2.3 Equivalence with Liu's model on trees

The proposed dataflow model differs from the generalized pebble game on trees of Liu presented in the previous chapter (Section 1.4.1) as it distinguishes between the size of the memory needed during the computation and the size of the output of a task. However, on task trees, both models are general enough to emulate each other:

- Given a tree  $T=(V,E,\tau)$  in Liu's model, we construct a tree T'=(V,E,n,f) in the dataflow model with  $d_i=\tau_i$  and  $m_i=-\tau_i$ . We easily check that the memory usage after processing a subset of nodes and during the computation of a node is the same in T and in T'.

- Given a tree T = (V, E, n, f) describing a computation in the dataflow model, we build a tree  $T' = (V', E', \tau)$  in Liu's model such that:

- for each vertex i in V, there are two vertices  $i_1, i_2$  in V' and an edge  $(i_1, i_2)$  in E',

- for each edge (i, j) in E, there is an edge  $(i_2, j_1)$  in E'

- the weights are given by  $\tau_{i_1} = \sum_{(j,i)\in E} d_j + m_i + d_i$  and  $\tau_{i_2} = d_i$ .

We also verify that for a given processing order of the vertices of V, by processing nodes in the same order and each  $i_2$  right after  $i_1$ , the memory usage in T' after each  $i_1$  is the same as the memory usage in T during the processing of i, while the memory after  $i_2$  corresponds to the memory after completing i.

Finally, note that on task graphs that are not trees, our new model considers that a task i with several successors  $j_1, j_2, \ldots$  produces one different data for each of them  $(d_{i,j_1}, d_{i,j_2}, \ldots)$ .

# 2.4 Problem definitions

We consider a computing system composed of a main memory, in which the data of the task currently processed must reside, and a secondary storage, such as a disk. As we have seen in the previous chapter, the order chosen to process the tasks plays a key role in determining which amount of main memory or I/O volume is needed for a complete execution of a task graph. More precisely, here are the two main problems that are addressed in this part:

**MinMemory:** Determine the minimum amount of main memory that is required to execute a task graph without any access to secondary memory, as well as a schedule of the tasks that achieves this amount of memory.

**MinIO:** Given the size M of the main memory, determine the minimum I/O volume that is required to execute a task graph as well as a corresponding schedule of the tasks and a schedule of the I/O operations.

In the following, we generally assume that tasks are processed sequentially, one after the other (except in Chapter 6 and in Section 5.3 of Chapter 5).

# 2.5 Adaptation of previous algorithms on trees

For the sake of completeness, we present below a modified version of the three algorithms on trees reported in the previous chapter, namely POSTORDER-MINMEM, LIUMINMEM and POSTORDERMINIO. The adaptation to the dataflow model is most of the time straightforward. For LIUMINMEM, we choose to detail the decomposition of a schedule into segments, so that one could easily implement it from this description. Note that the "sort" statement is actually a "MergeSort", as outlined by Liu in its original algorithm [65], as segments within a specific sub-schedule  $\pi_i$  are already sorted. In the following chapters, when we refer to one of these algorithms, this always denotes its version for the dataflow model.

32 CHAPTER 2.

# **Algorithm 6:** PostorderMinMem (T) (dataflow model)

**Data:** T = (V, E, d, m): tree in the dataflow model

**Result:**  $(\sigma, P)$ : postorder schedule and its minimal peak memory

if  $V = \{u\}$  then return  $((u), d_u + m_u)$

Let r be the root of T,  $c_1, c_2 \dots c_k$  its children and  $T_1, T_2, \dots T_k$  the corresponding subtrees

for i = 1 to k do

$$(\sigma_i, P_i) \leftarrow \text{PostorderMinMem}(T_i)$$

Sort the k subtrees such that  $P_1-d_{c_1}\geq \cdots \geq P_k-d_{c_k}$

$\sigma \leftarrow \text{Concatenate } \sigma_1, \sigma_2, \dots, \sigma_k \text{ and add } r \text{ at the end}$

$$P \leftarrow \max \left( d_r + m_r + \sum_{j=1}^k d_{c_j}, \max_{1 \leq j \leq k} \sum_{\ell=1}^{j-1} d_{c_\ell} + P_j \right)$$

return  $(\sigma, P)$

# **Algorithm 7:** LiuMinMem (T) (dataflow model)

**Data:** T = (V, E, d, m): tree in the dataflow model

**Result:**  $\sigma$ : schedule with minimal peak memory

if  $V = \{u\}$  then return (u)

Let r be the root of T and  $T_1, T_2, \dots T_k$  its subtrees

for i = 1 to k do

$\sigma_i \leftarrow \text{LiuMinMem}(T_i)$

$$v_0^i \leftarrow 0, \, s \leftarrow 1, \, j \leftarrow 1$$

while  $s < NumberOfNodes(T_i)$  do

$$H_j^i \leftarrow \max_{t \geq s} \left( d_{\sigma_i(t)} + m_{\sigma_i(t)} + \sum_{k \in Children(\sigma_i(t))} d_k \right)$$

Let  $h_j^i$  be the largest index t achieving the previous maximum

$$V_j^i = \min_{t \ge h_j^i} \left( d_{\sigma_i(t)} \right)$$

Let  $v_j^i$  be the largest index t achieving the previous minimum NB: we have identified in  $\sigma_i$  the jth segment at indices  $[v_{j-1}^i+1,v_j^i]$ , with hill  $H_j^i$  and valley  $V_j^i$   $s \leftarrow v_j^i+1, \ j \leftarrow j+1$

$$[v_{j-1}^i+1,v_j^i]$$

, with hill  $H_j^i$  and valley  $V_j$

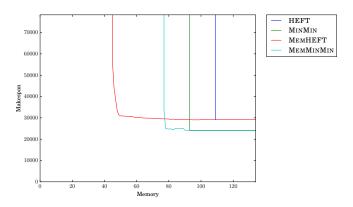

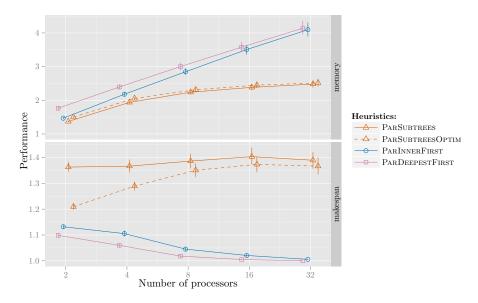

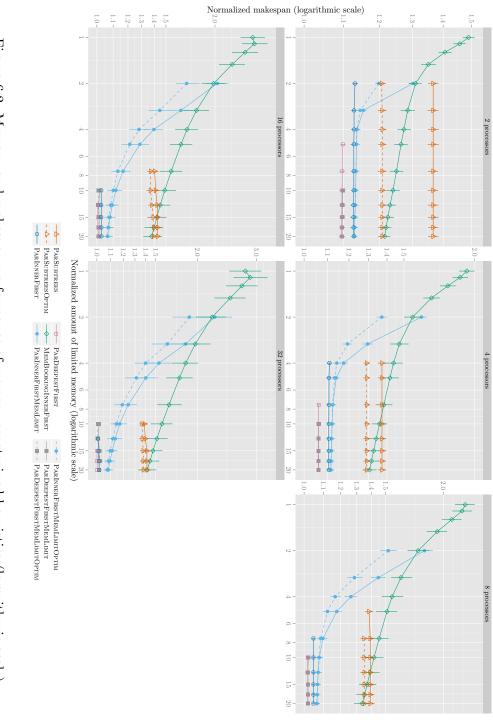

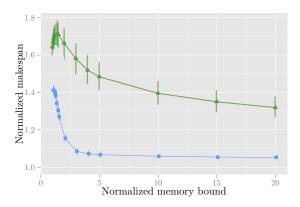

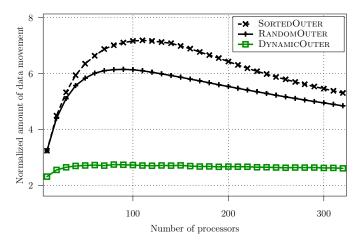

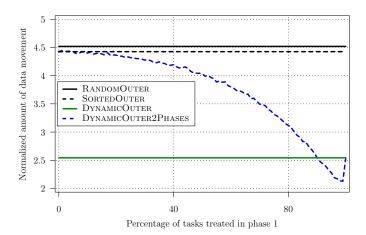

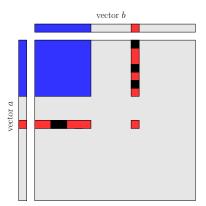

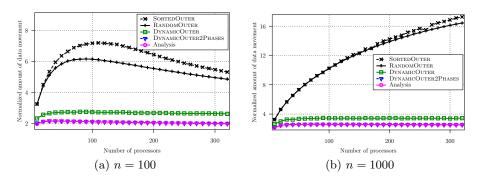

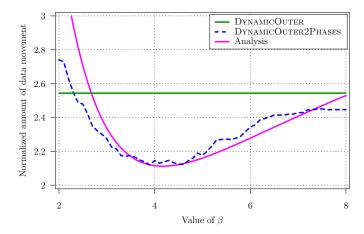

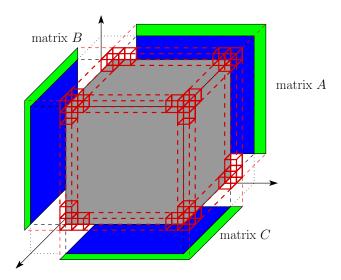

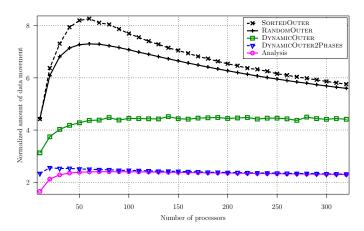

$L \leftarrow \text{sort all } (H_i^i, h_i^i, V_i^i, v_i^i) \text{ quadruplets by non-increasing } H_i^j - V_i^j$  $\sigma \leftarrow \emptyset$