# Ordonnancement temps-réel conscient des caches dans des architectures multi-cœurs : algorithmes et réalisation

Viet Anh Nguyen

# ▶ To cite this version:

Viet Anh Nguyen. Ordonnancement temps-réel conscient des caches dans des architectures multicœurs : algorithmes et réalisation. Architectures Matérielles [cs.AR]. Université de Rennes 1 [UR1], 2018. Français. NNT : . tel-01933422

# HAL Id: tel-01933422 https://inria.hal.science/tel-01933422

Submitted on 23 Nov 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

ANNÉE (2018)

**THÈSE** / **UNIVERSITÉ DE RENNES 1** sous le sceau de l'Université Bretagne Loire

pour le grade de DOCTEUR DE L'UNIVERSITÉ DE RENNES 1

Mention : Informatique

École doctorale MATHSTIC

présentée par

# Viet Anh NGUYEN

préparée à l'unité de recherche IRISA – UMR6074 Institut de Recherche en Informatique et Système Alétoires

Cache-conscious Off-Line Real-Time Scheduling for Multi-Core Platforms: Algorithms and Implementation

### Thèse soutenue à Rennes le 22 Février 2018

devant le jury composé de : **Steven DERRIEN** Professeur, Professeur, Université de Rennes 1 / Président **Christine ROCHANGE** Professeur, Université Paul Sabatier Toulouse / Rapporteur **Mathieu JAN** Ingénieur-chercheur, CEA / Rapporteur **Damien HARDY** Maître de conférences, Université de Rennes 1 / Examinateur **Frédéric PÉTROT** Professeur, ENSIMAG Grenoble / Examinateur **Isabelle PUAUT** Professeur, Université de Rennes 1 / Directeur de thèse

# Acknowledgments

This thesis becomes a reality with the support of many individuals. I would like to express my sincere thanks to all of them.

First of all, I would like to express my gratitude to my supervisors, Professor Isabelle PUAUT and Associate Professor Damien HARDY of University of Rennes 1, for their unwavering support and guidance.

I also would like to thank my committee members, whose gave me fruitful comments to enhance the quality of the thesis.

In addition, I appreciate the supports of all permanent staffs and my colleagues in PACAP team. Your help have made my job very much easier and more enjoyable.

And finally, I would like to thank my family. You have always encouraged and believed in me. You have helped me to focus on what has been a hugely rewarding.

Table of contents

# Contents

| Table of contents |                                                                             |                         |                                                                                                         |    |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------|----|--|--|--|--|

| Ré                | ésumé                                                                       | de la t                 | hèse en langue Francaise                                                                                | 3  |  |  |  |  |

| 1                 | Introduction                                                                |                         |                                                                                                         |    |  |  |  |  |

|                   | 1                                                                           | Hard 1                  | real-time multi-core systems: timing predictability challenges                                          | 7  |  |  |  |  |

|                   | 2                                                                           |                         | tives and solution overview                                                                             | 9  |  |  |  |  |

|                   |                                                                             | $2.1^{\circ}$           | Cache-conscious scheduling algorithms                                                                   | 9  |  |  |  |  |

|                   |                                                                             | 2.2                     | Implementation of cache-conscious schedules                                                             | 10 |  |  |  |  |

|                   | 3                                                                           | Contri                  | butions                                                                                                 | 10 |  |  |  |  |

|                   | 4                                                                           |                         | ization                                                                                                 | 11 |  |  |  |  |

| 2                 | Real-time systems and multi-core platforms: background and state-of-the-art |                         |                                                                                                         |    |  |  |  |  |

|                   | 2.1                                                                         | Backg                   | round                                                                                                   | 13 |  |  |  |  |

|                   |                                                                             | 2.1.1                   | Real-time systems                                                                                       | 13 |  |  |  |  |

|                   |                                                                             | 2.1.2                   | Worst-case execution time estimation                                                                    | 14 |  |  |  |  |

|                   |                                                                             | 2.1.3                   | Real-time task scheduling                                                                               | 16 |  |  |  |  |

|                   |                                                                             | 2.1.4                   | Time-predictable multi-core hardware                                                                    | 18 |  |  |  |  |

|                   |                                                                             | 2.1.5                   | Cache memories                                                                                          | 20 |  |  |  |  |

|                   | 2.2                                                                         | Timin                   | g analysis for multi-core systems: state-of-the-art                                                     | 23 |  |  |  |  |

|                   |                                                                             | 2.2.1                   | WCET analysis techniques for multi-core architectures                                                   | 23 |  |  |  |  |

|                   |                                                                             | 2.2.2                   | Task scheduling algorithms for multi-core architectures                                                 | 24 |  |  |  |  |

|                   | 2.3                                                                         | Summ                    | ary and thesis context                                                                                  | 25 |  |  |  |  |

| 3                 | Cache-conscious scheduling: algorithms 27                                   |                         |                                                                                                         |    |  |  |  |  |

|                   | 3.1                                                                         | System                  | n model and problem formulation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 27 |  |  |  |  |

|                   |                                                                             | 3.1.1                   | Hardware model                                                                                          | 27 |  |  |  |  |

|                   |                                                                             | 3.1.2                   | Task and execution model                                                                                | 28 |  |  |  |  |

|                   |                                                                             | 3.1.3                   | Assumptions                                                                                             | 29 |  |  |  |  |

|                   |                                                                             | 3.1.4                   | Scheduling problem statement                                                                            | 29 |  |  |  |  |

|                   | 3.2                                                                         | Cache                   | -conscious task scheduling methods                                                                      | 30 |  |  |  |  |

|                   |                                                                             | 3.2.1                   | Cache-conscious ILP formulation                                                                         | 31 |  |  |  |  |

|                   |                                                                             | 3.2.2                   | Cache-conscious list scheduling method (CLS)                                                            | 33 |  |  |  |  |

|                   | 3.3                                                                         | Experimental evaluation |                                                                                                         |    |  |  |  |  |

### Contents

|                             |                                                             | 3.3.1                                                                         |                       | ental conditions                                                                                                        | 35         |  |  |  |

|-----------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

|                             | 9.4                                                         | 3.3.2                                                                         |                       | ental results                                                                                                           | $40 \\ 49$ |  |  |  |

|                             | 3.4                                                         |                                                                               | Related work          |                                                                                                                         |            |  |  |  |

|                             | 3.5                                                         | Summ                                                                          |                       | 50                                                                                                                      |            |  |  |  |

| 4                           | 4 Cache-conscious scheduling: implementation                |                                                                               |                       |                                                                                                                         |            |  |  |  |

|                             | 4.1                                                         |                                                                               |                       | the Kalray MPPA-256 machine                                                                                             | 51         |  |  |  |

|                             | 4.2 General structure of our proposed time-driven scheduler |                                                                               |                       |                                                                                                                         |            |  |  |  |

|                             | 4.3                                                         | Practical challenges                                                          |                       |                                                                                                                         |            |  |  |  |

|                             |                                                             | 4.3.1                                                                         | 1 0                   |                                                                                                                         |            |  |  |  |

|                             |                                                             | 4.3.2                                                                         | Shared bus contention |                                                                                                                         |            |  |  |  |

|                             |                                                             | 4.3.3                                                                         | Delay to              | the start time of tasks because of the execution of the schedul-                                                        |            |  |  |  |

|                             |                                                             |                                                                               | ing time              | -checking function                                                                                                      | 55         |  |  |  |

|                             |                                                             | 4.3.4                                                                         | Absence               | of hardware-implemented data cache coherence                                                                            | 56         |  |  |  |

|                             | 4.4                                                         | Adaptation of time-driven cache-conscious schedules to the practical issues 5 |                       |                                                                                                                         |            |  |  |  |

|                             |                                                             | 4.4.1                                                                         | Data str              | uctures                                                                                                                 | 58         |  |  |  |

|                             |                                                             | 4.4.2                                                                         | Restricti             | ons of the execution of an application                                                                                  | 60         |  |  |  |

|                             |                                                             | 4.4.3                                                                         | Adapting              | g basic cache-conscious schedules to the practical effects                                                              | 60         |  |  |  |

|                             | 4.5                                                         | Code                                                                          | generator             |                                                                                                                         | 65         |  |  |  |

|                             | 4.6                                                         | Exper                                                                         | imental ev            | valuation                                                                                                               | 69         |  |  |  |

|                             |                                                             | 4.6.1                                                                         | Experim               | ental conditions                                                                                                        | 70         |  |  |  |

|                             |                                                             |                                                                               | 4.6.1.1               | Benchmarks                                                                                                              | 70         |  |  |  |

|                             |                                                             |                                                                               | 4.6.1.2               | Constants estimation                                                                                                    | 70         |  |  |  |

|                             |                                                             |                                                                               | 4.6.1.3               | WCET and number of cache misses estimations when con-                                                                   |            |  |  |  |

|                             |                                                             |                                                                               |                       | tention free                                                                                                            | 71         |  |  |  |

|                             |                                                             |                                                                               | 4.6.1.4               | Experimental environment                                                                                                | 72         |  |  |  |

|                             |                                                             | 4.6.2                                                                         | Experim               | ental results                                                                                                           | 72         |  |  |  |

|                             |                                                             |                                                                               | 4.6.2.1               | Validation of the functional correctness and the timing cor-<br>rectness of benchmarks when executing on a Kalray MPPA- |            |  |  |  |

|                             |                                                             |                                                                               |                       | 256 compute cluster $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                    | 72         |  |  |  |

|                             |                                                             |                                                                               | 4.6.2.2               | Quantification of the impact of different practical issues on                                                           |            |  |  |  |

|                             |                                                             |                                                                               |                       | adapted cache-conscious schedules                                                                                       | 73         |  |  |  |

|                             |                                                             |                                                                               | 4.6.2.3               | Evaluation the performance of ACILP                                                                                     | 74         |  |  |  |

|                             | 4.7                                                         |                                                                               | 76                    |                                                                                                                         |            |  |  |  |

|                             | 4.8                                                         | Summary                                                                       |                       |                                                                                                                         |            |  |  |  |

| 5                           | Con                                                         | clusion                                                                       |                       |                                                                                                                         | 79         |  |  |  |

| Bi                          | bliogi                                                      | aphie                                                                         |                       |                                                                                                                         | 89         |  |  |  |

|                             |                                                             |                                                                               |                       |                                                                                                                         |            |  |  |  |

| Publications of the authors |                                                             |                                                                               |                       |                                                                                                                         |            |  |  |  |

| Ta                          | Table of figures                                            |                                                                               |                       |                                                                                                                         |            |  |  |  |

| Ał                          | Abstract                                                    |                                                                               |                       |                                                                                                                         |            |  |  |  |

$\mathbf{2}$

### Résumé de la thèse en langue Francaise

Les systèmes temps-réel, dont le respect du temps de réponse est tou aussi important que la correction fonctionnelle, se sont maintenant répandus dans notre vie quotidienne. En particulier, les applications temps-réel peuvent être trouvées dans les voitures, les avions, les centrales nucléaires. De plus, selon [1] le marché des systèmes embarqués va certainement être témoin d'une forte demande dans les années à venir. Le marché des systèmes embarqués était évalué à 84,55 milliards de dollars US en 2016 et il est prévu qu'il grossisse à un taux de croissance annuel recomposé de 4.05% entre les années 2017 et 2023.

Avec la demande toujours plus grandissante pour des applications sûres mais intensives en terme de calcul, l'utilisation d'architectures mono-cœurs n'est plus un choix judicieux pour le déploiement de systèmes temps-réel, et ce dû aux limites technologiques de ce type d'architecture (par exemple, limite de puissance énergétique [2]). Afin de dépasser cette limitation, les géants de la fabrication de puces ont créés de nouveaux processeurs, appelés processeurs multi-cœurs, dans lesquels plusieurs cœurs sont intégrés sur la même puce. Les processeurs multi-cœurs se sont montrés plus efficaces en terme d'énergie avec un ratio coût/performance bien meilleur que leur ancêtre mono-cœur [3], en effet ils améliorent les performances des applications par exploitation du parallélisme de niveau threads. Des examples d'architectures multi-cœurs incluent le Kalray MPPA-256 [4], le Tilera Tile CPUs [5], ou encore le Xeon Phi de chez Intel [6].

La migration des systèmes temps-réel vers une utilisation des processeurs multi-cœurs remplit les attentes de performance des applications gourmandes en ressources, mais lève de nombreux problèmes de prévisibilité temporelle. Dû aux effets matériels des processeurs multi-cœurs, garantir les contraintes temporelles des applications critiques et parallèles est un vrai challenge.

L'un des challenges les plus importants est d'estimer, avec précision, le Pire Temps d'Exécution (PTE) du code s'exécutant sur le multi-cœur. Il existe de nombreuses méthodes pour estimer le PTE sur processeur mono-cœur [7]. Ces techniques prennent en compte à la fois les chemins d'exécution du programme et la micro-architecture du cœur. Étendre ces méthodes aux architectures multi-cœurs est difficile, et ce dû aux ressources matérielles, tel que les caches ou les bus, qui sont partagées entre les cœurs, rendant ainsi l'estimation du PTE des tâches dépendant de l'exécution des autres tâches s'exécutant sur les autres cœurs [8, 9]. De plus, sur les architectures avec des caches locaux, l'estimation du PTE des tâches dépend du contenu du cache au démarrage de la tâche, ce qui dépend de la stratégie d'ordonnancement d'exécution des tâches. Le pire temps d'exécution d'une tâche n'est donc plus unique. Il dépend du contexte d'exécution de la tâche (les tâches s'exécutant avant, s'exécutant en concurrence), ce contexte est défini par la stratégie d'ordonnancement et de placement. Dans les faits, il est possible de considérer une estimation pire cas indépendante du contexte, mais la valeur résultante serait trop pessimiste.

De manire symétrique, l'estimation du PTE d'une tâche est nécessaire pour déterminer le placement et l'ordonnancement d'une tâche. Par conséquent, l'ordonnancement et l'estimation du PTE considérant des processeurs multi-cœurs sont des problèmes interdépendants, référés à une situation de poule et d'œuf. À cause de cette interdépendance, nous pensons que des stratégies d'ordonnancement prenant en compte l'entièreté du matériel multi-cœur doivent être définies. Prendre en compte les PTEs dépendants du contexte aide à l'amélioration de la qualité des ordonnancements, c'est à dire à la réduction de la longueur de ces derniers. Les travaux de thèse présentés dans ce document considèrent la variation du PTE des tâches dû aux effets des caches locaux.

### Présentation des objectifs et solutions

Algorithme d'ordonnancement conscient du cache. Nous proposons deux techniques d'ordonnancement pour des architectures multi-cœurs équipées de caches locaux, celles-ci incluent une méthode optimale utilisant une formulation de Programmation Linéaire en Nombre Entier (PLNE), et une méthode heuristique basée sur de l'ordonnancement par liste.

Ces deux techniques ordonnancent une seule application parallèle modélisée par un graphe de tâches, et génèrent un ordonnancement statique partitionné et non-préemptif. Dû à l'effet des caches locaux, chaque tâche  $\tau_j$  n'est pas caractérisée par une seule valeur de PTE mais plutôt par un ensemble de valeurs de PTE. Le PTE le plus pessimiste d'une tâche, noté  $PTE_{\tau_j}$ , est observé lorsqu'il n'y a pas de réutilisation de contenu chargé dans le cache par la tâche s'exécutant immédiatement avant  $\tau_j$ . Un ensemble de valeurs de PTE noté  $PTE_{\tau_i \to \tau_j}$  représente les PTEs d'une tâche  $\tau_j$  lorsque  $\tau_j$  réutilise des informations de  $\tau_i$ , chargées aussi bien dans le cache d'instructions que de données par la tâche  $\tau_i$  s'exécutant immédiatement avant  $\tau_j$  sur le même cœur. L'objectif de ces deux techniques est de générer un ordonnancement dont la longeur est aussi courte que possible.

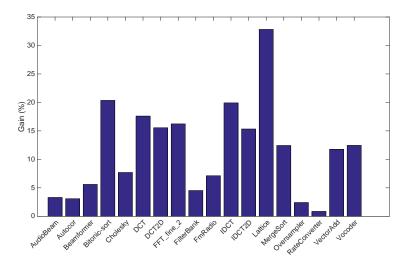

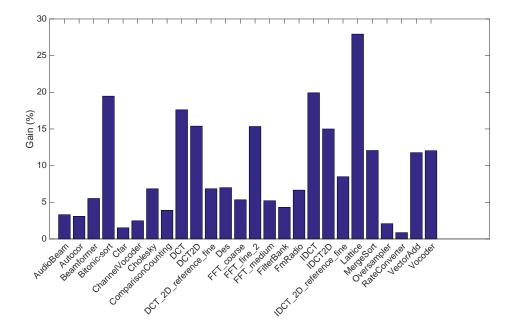

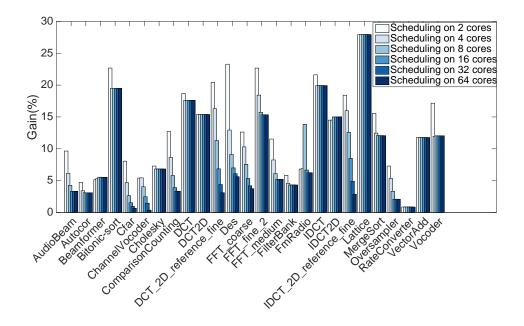

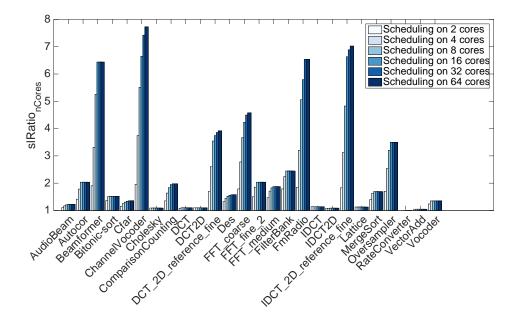

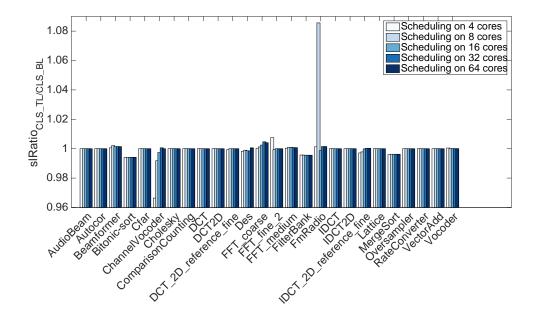

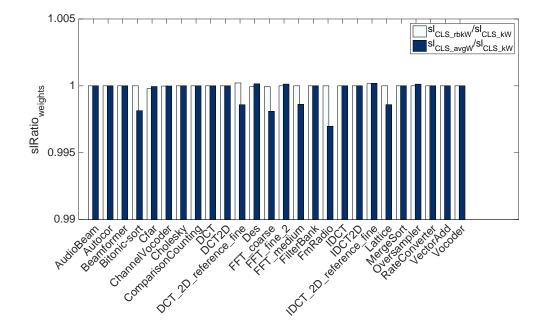

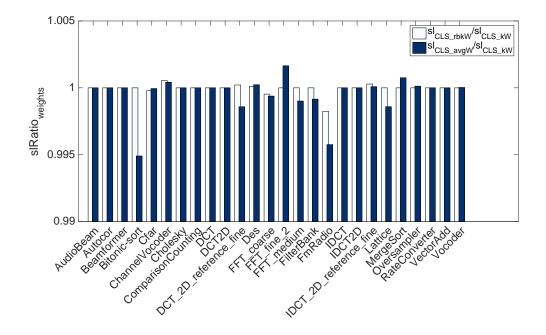

Les évaluations expérimentales sur les cas de tests de la suite de tests StreamIt [10] montrent des réductions significatives sur la longeur des ordonnancements générés par les techniques conscientes du cache comparées à leurs équivalentes ignorant les cache privés. La réduction de la taille de l'ordonnancement observée sur des applications de streaming est de 11% en moyenne avec la méthode optimale et de 9% en moyenne avec l'heuristique. De plus, l'heuristique proposée montre un bon compromis entre longueur des ordonnancement par heuristique génère des résultats très rapidement, i.e. 1 second est nécessaire pour générer l'ordonnancement d'un graphe de tâches complexe contenant 548 tâches sur un processeur de 16 cœurs. La différence entre la taille des ordonnancements générés par l'heuristique et la méthode optimale est faible, i.e., 0.7% en moyenne.

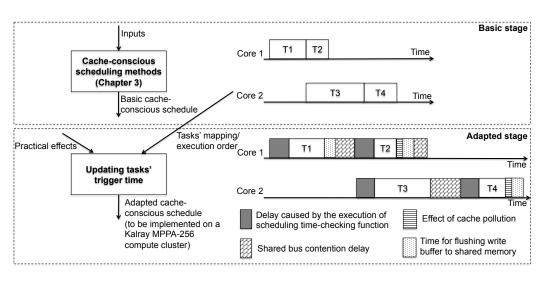

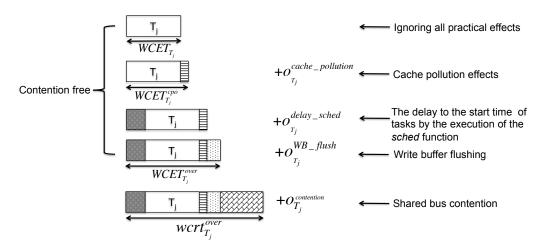

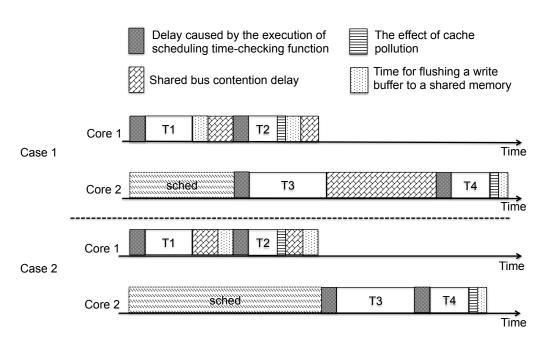

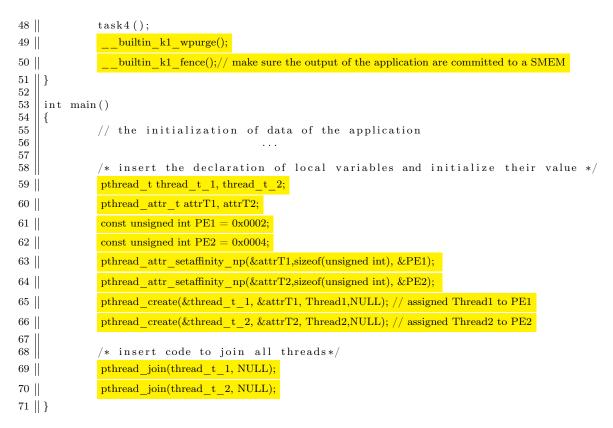

Implémentation de méthodes d'ordonnancement conscientes du cache. Nous avons réalisé l'implémentation d'un ordonnancement dirigé par le temps et conscient du cache pour le Kalray MPPA-256, un processeur multi-cœur en grappe. Pour autant que nous le sachions, nous sommes les premiers à créer et implémenter un tel ordonnanceur pour cette machine. Pour l'implémentation, nous avons premièrement identifié les challenges qui surviennent avec ce type d'implémentation, ce qui inclue:

- la pollution du cache et les délais de démarrage d'une tâche dû à l'exécution de l'ordonnanceur ;

- la contention sur le bus partagé ;

• l'absence de cohérence des caches de données.

Ces facteurs expérimentaux ont amené une augmentation du temps d'exécution des tâches, donc changeant le temps de fin des tâches entrainant, ainsi, des modifications du temps de début des tâches suivantes afin de garantir les relations de précédence entre tâches. Á partir de ce constat, nous proposons une formulation PLNE modifiant des ordonnancements conscients du cache en les adaptant aux facteurs expérimentaux identifiés, tout en garantissant la satisfaction des précédences entre tâches et une minimisation de la longueur de l'ordonnancement. De plus, nous proposons une stratégie pour générer le code d'une application prévue pour la machine cible d'après son ordonnancement.

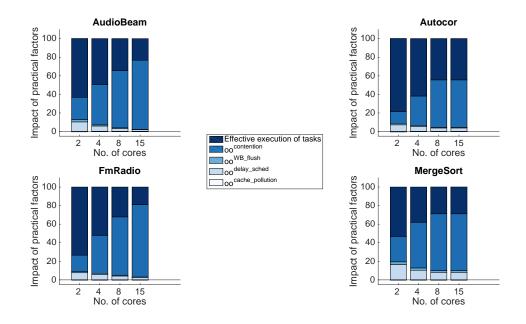

La validation expérimentale des benchmarks avec la suite StreamIT montre la correction fonctionnelle et temporelle de notre implémentation. De plus, nous montrons qu'il est très rapide de trouver des *ordonnancements conscients du cache et adaptables* avec notre formulation PLNE. Enfin, nous quantifions l'impact des facteurs expérimentaux sur la durée de ces ordonnancements, et nous avons pu observé le facteur le plus impactant la longeur de l'ordonnancement: la contention.

## Contributions

Les contributions principales des travaux présentés dans cette thèse sont les suivants:

- Nous défendons et validons expérimentalement l'importance d'adresser les effets des caches privés sur les PTEs des tâches lors de l'ordonnancement sur des architectures multi-coœur.

- Nous proposons une méthode d'ordonnancement basée sur PLNE pour statiquement trouver un ordonnancement partitionné et non-préemptif d'une application parallèle modélisée par un graphe dirigé et acyclique. Afin de réduire les temps de génération des ordonnancements, nous proposons également une technique heuristique basée sur de l'ordonnancement par liste.

- Nous fournissons les résultats expérimentaux montrant, entre autres, que les ordonnanceurs proposés génèrent des ordonnancements plus courts que leurs équivalents ignarant les caches locaux.

- Nous identifions les challenges réels qui surviennent lors de l'implémentation d'ordonnancements conscients du cache et dirigés par le temps sur la machine Kalray MPPA-256, et proposons nos stratégies pour dépasser ces challenges.

- Nous explorons l'impact des différents facteurs expérimentaux sur les ordonnancements conscients du cache.

## Organisation

Cette thèse, rédigé en langue anglaise, est divisée en 5 chapitres.

- Dans le chapitre 1, nous introduisons les concepts de ces travaux de thèse. Premièrement, nous posons le problème qui a motivé ces travaux. Puis nous présentons les objectifs, ainsi qu'une vue d'ensemble des solutions proposées pour tacler les problèmes identifiés en amont. En second lieu, nous résumons brièvement les contributions de cette thèse.

- Dans le chapitre 2 (chapitre introductif), nous présentons les connaissances prérequises ainsi que les travaux apparentés de la communauté des systèmes temps-réel multi-cœurs. Nous commencons par introduire quelques concepts généraux impliquant les systèmes temps-réel, l'analyse PTE, et l'ordonnancement de tâches. Nous décrivons aussi brièvement la plateforme multi-cœur, les propriétés désirées de prédictabilité dans les architectures multi-cœurs, et les caractéristiques des mémoires caches. Ensuite nous classifions et décrivons brièvement les travaux principaux de la communauté temps-réel sur l'analyse PTE et l'ordonnancement de tâches pour les plateformes multi-cœurs, ce qui nous permet d'identifier les aspects peu étudiés, spécifiquement le problème d'ordonnancement considérant les effets des caches privés.

- Dans le chapitre 3, nous décrivons la génération d'ordonnancement conscient des cache privés. Deux méthodes d'ordonnancement sont présentées pour générer des ordonnancements statiques et non-préemptifs d'une application parallèle, incluant une méthode optimale et une heuristique. Nous présenterons aussi une évaluation de la performance des méthodes d'ordonnancement proposées en termes de qualité des ordonnancements et de rapidité de génération.

- Dans le chapitre 4, nous présentons l'implémentation d'ordonnancements conscients du cache et dirigés par le temps pour les machines Kalray MPPA-256. Nous commencons par décrire l'architecture de la plateforme, suivi de notre implémentation de l'ordonnancement. Ensuite nous identifions les défis réels qui surviennent lors du déploiement des ordonnancements sus-mentionnés, et présentons nos stratégies pour dépasser les difficultés identifiées. Enfin une évaluation expérimentale valide la correction fonctionnelle et temporelle de notre implémentation.

- Dans le chapitre 5, nous concluons ces travaux de thèse et proposons des perspectives de travaux futurs.

# Chapter 1

# Introduction

# 1 Hard real-time multi-core systems: timing predictability challenges

Real-time embedded systems, i.e., those for which timing requirements prevail over performance requirements, are now widespread in our everyday lives. In particular, real-time applications can be found in personal cars, airplanes, space ships, nuclear plants. Additionally, according to [1] the embedded systems market is likely to witness a high growth in the coming years. The embedded systems market was valued at USD 84.55 Billion in 2016 and is expected to grow at a Compound Annual Growth Rate (CAGR) of 4.05% between 2017 and 2023.

With the ever-increasing demand for safer but more compute-intensive applications, single-core architectures are no longer suitable choices for deploying real-time systems due to the technological limits of the architectures (typically referred to as power-wall [2]). In order to overcome the issue, the leading chip manufacturers have been offering new computing platforms, called *multi-core platforms*, in which multiple cores are integrated within a single chip. Multi-core platforms have been shown to have more energy-efficient and better performance-per-cost ratio than their single-core counterpart [3], as they improve the application performance by exploiting thread-level parallelism. Examples of multi-core architectures include the Kalray MPPA-256 [4], Tilera Tile CPUs [5], and Intel Xeon Phi [6].

Migrating real-time systems to multi-core platforms ensures the satisfaction of computeintensive applications' performance, but raises the issue of the timing predictability of the systems. Due to the effects of multi-core hardware (i.e., for example, local caches, shared resources between cores), guaranteeing the real-time constraints of safety-critical parallel applications on multi-core platforms is challenging.

One important challenge is to precisely estimate the Worst-Case Execution Time (WCET) of codes executing on multi-cores. Many WCET estimation methods have been designed in the past for single-core architectures [7]. Such techniques take into account both the program paths and the core micro-architecture. Extending them to multi-core architectures

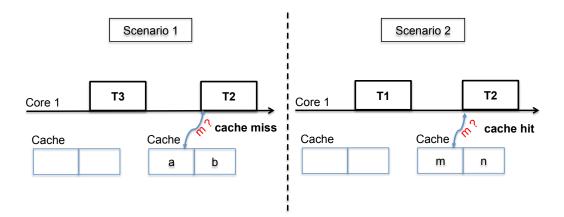

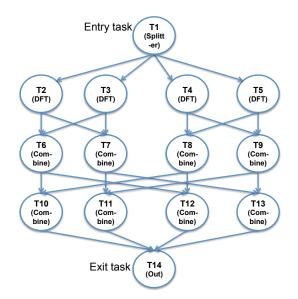

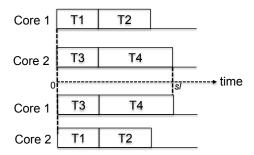

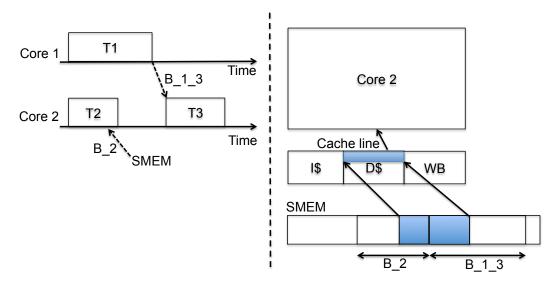

Figure 1.1: The influence of scheduling strategies on the WCET of tasks

is challenging, because some hardware resources, such as caches or buses are shared between cores, which makes the WCET of a task dependent on the tasks executing on the other cores [8, 9]. Additionally, on architectures with local caches, the WCET of a task depends on the cache contents when the task starts executing, which depends on the scheduling strategy. The WCET of one task is thus no longer unique. It depends on the execution context of the task (tasks executed before it, concurrent tasks), which is being defined by the scheduling strategy. In fact, ones could consider a context-independent WCET for a task, but the value would be too pessimistic.

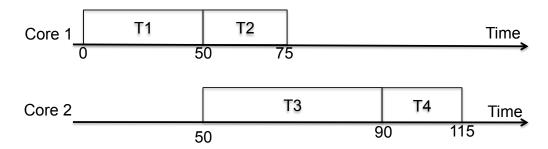

Motivating example. Let us consider an overly simplified system made of three tasks, named T1, T2, and T3, executing on a dual-core processor, for which each core is equipped with an unified private cache containing two lines. T1 and T2 access to the same memory block, named m, whereas T3 is code and data independent with both T1 and T2. We consider two execution scenarios to reveal the effect of scheduling strategies on tasks' WCET. In the first scenario, T2 is placed on the same core as T3 and executes right after T3 (as illustrated in the left side of Figure 1.1). In the second scenario, T2 is placed on the same core as T1 and executes right after T1 (as illustrated in the right side of Figure 1.1). We assume that the contents of the cache at the beginning are empty. In the first scenario, the request of T2 for the memory block m is a cache miss since at the requesting time the memory block has not been loaded in the cache yet. As a consequence, T2 has to wait until the memory block m is loaded from the main memory to the cache. In contrast, in the second scenario, the request of T2 for the memory block m is a cache hit since the memory block is already stored in the cache during the execution of T1. Since the access to the cache is much faster than the access to the main memory, the worst-case execution time of T2 in the second scenario is lower than its worst-case execution time in the first scenario.

This example shows the influence of the mapping and the execution order of tasks on their worst-case execution time due to the effect of private caches. Systematically, the worst-case execution time of tasks are needed for scheduling strategies to determine the mapping and

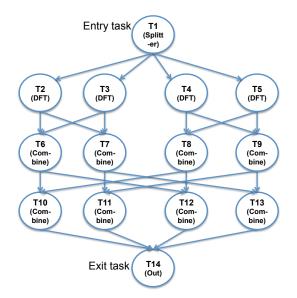

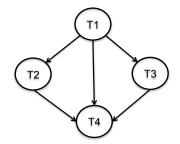

Figure 1.2: Task graph of a parallel version of a 8-input Fast Fourier Transform (FFT) application [11]

the scheduling of the tasks. Therefore, task scheduling and WCET estimation for multi-core platforms are inter-dependent problems, referred to as a chicken and egg situation.

**Thesis claims.** Due to the aforementioned interdependent problems, we believe that scheduling strategies that are aware of the multi-core hardware have to be defined. Taking into account context-sensitive WCETs for a task rather than a single context-independent WCET helps to enhance the quality of schedules, i.e., reduce schedules length (or makespan). In the scope of this PhD work<sup>1</sup>, we consider the variation of the WCET of a task due to the effect of private caches.

# 2 Objectives and solution overview

#### 2.1 Cache-conscious scheduling algorithms

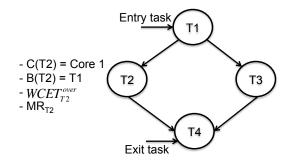

Our first objective in the thesis is to propose cache-conscious scheduling strategies, that take benefit of cache reuse between tasks. Each task has distinct WCET values depending on which other task has been executed before it on the same core (WCETs are contextsensitive). The proposed scheduling strategies map tasks to cores and schedules tasks on cores; the goal is to account for cache reuse to obtain the shortest schedules. We focus on a single parallel application, modeled as a task graph, in which nodes represent tasks

$<sup>^1{\</sup>rm This}$  PhD work is a part of PIA project CAPACITES (Calcul Paralléle pour Applications Critiques en Temps et Sûreté.), reference P3425-146781

and edges represent dependence relations between them. Additionally, in cache-conscious schedules generation, we solely consider the effect of private caches, while other hardware related factors are left for implementation stage.

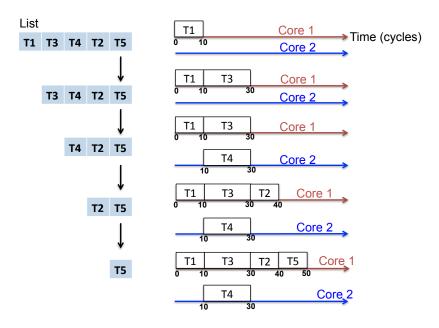

We propose two different methods to determine a static partitioned non-preemptive schedule aiming at minimizing the schedule length, for a parallel application by taking into account the variation of tasks' WCETs due to reuse of code and data between tasks. The first method is based on an Integer Linear Programming (ILP) formulation and produces optimal schedules under the considered hypotheses. The second method is a heuristic method, which is based on list scheduling. The proposed heuristic scheduling approach produces schedules very fast, and the length of heuristic schedules are close to the optimal ones.

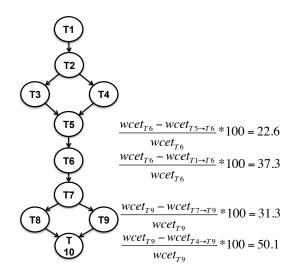

To further motivate our research, let us consider an example, a 8-input Fast Fourier Transform application [11]. Its task graph is shown in Figure 3.2. For instance, T2 and T3 feature code reuse since they call the same function, and T2 and T6 feature data reuse since the output of T2 is the input of T6. On that example, we observe a reduction of the WCETs of tasks of 10.7% on average when considering the cache affinity between pairs of tasks that may execute consecutively on the same core. The schedule length for that parallel application was reduced by 8% by using the Integer Linear Programming (ILP) technique presented in Chapter 3 as compared to its cache-agnostic equivalent.

Noted that the definition of the WCET of a task in this PhD work is different with the one defined in the literature. In the literature, the WCET of a task is defined as upperbound of the execution times of the task when executing in isolation. Our definition about the WCET of a task is upperbound of the execution times of the task when considering the contents of the cache at the beginning of the execution of the task.

#### 2.2 Implementation of cache-conscious schedules

Once the benefit of considering the effect of private caches on task scheduling is shown, our successive target is to implement time-driven cache-conscious schedules on a real multi-core hardware, that is the Kalray MPPA-256 machine [4]. In the implementation stage, we first identify the practical challenges arising when deploying those schedules on the machine, such as shared bus contention, the effect of time-driven scheduler itself, the absence of hardware-implemented data cache coherence. Those practical effects require modification of the cache-conscious schedules. We thus propose an ILP formulation to adapt the cache-conscious schedules to the identified practical factors, such that the precedence relations of tasks are still satisfied, and the schedules length of the adapted schedules are minimized. Additionally, we propose a strategy for generating the code of applications to be executed on the machine according to the adapted cache-conscious schedules.

### 3 Contributions

The main contributions of the PhD work are as follows:

• We argue and experimentally validate the importance of addressing the effect of private caches on tasks' WCETs in scheduling.

- We propose an ILP-based scheduling method and a heuristic scheduling method to statically find a partitioned non-preemptive schedule of a parallel application modeled as a directed acyclic graph.

- We provide experimental results showing, among others, that the proposed scheduling techniques result in shorter schedules than their cache-agnostic equivalent.

- We identify the practical challenges arising when implementing time-driven cacheconscious schedules on the Kalray MPPA-256 machine, and propose our strategies for overcoming the identified challenges.

- We investigate the impact of different practical factors on cache-conscious schedules.

# 4 Organization

The rest of this thesis is divided into three main chapters. In Chapter 2, we present fundamental background and literature review about real-time multi-core systems. We begin by introducing some general concepts dealing with real-time systems, WCET analysis, and task scheduling. We also briefly describe multi-core platforms, the desired properties of time-predictable multi-core architectures, and the characteristics of cache memories. We then classify and briefly describe the main works from the real-time literature related to WCET analysis and task scheduling for multi-core platforms. This allows us to identify some aspects that have not been much studied, specifically the scheduling problem that takes into account the effect of private caches.

Once those fundamental knowledge are introduced, we present the different contributions of the PhD work. In Chapter 3, we describe cache-conscious schedules generation. Two scheduling methods are presented for generating static partitioned non-preemptive schedules of parallel applications, including an optimal method and a heuristic one.

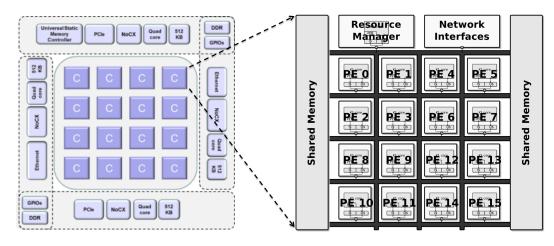

The implementation of time-driven cache-conscious schedules on the Kalray MPPA-256 machine is presented in Chapter 4. We first describe the architecture of the machine, and our time-driven scheduler implementation. We then identify the practical challenges arising when deploying the time-driven cache-conscious schedules on the machine, and present our strategies for overcoming the identified issues.

Finally, in Chapter 5, we conclude this PhD work and propose some perspectives for future work.

# Chapter 2

# Real-time systems and multi-core platforms: background and state-of-the-art

In this chapter, we present fundamental background and the literature review about realtime multi-core systems. We begin by introducing general concepts dealing with real-time systems, worst-case execution time (WCET) analysis, and task scheduling. We also briefly describe multi-core platforms, the desired properties of time-predictable multi-core architectures, and the characteristics of cache memories. We then classify and briefly describe the main works from the real-time literature related to WCET analysis and task scheduling for multi-core platforms.

# 2.1 Background

### 2.1.1 Real-time systems

Real-time systems are defined as systems in which the correctness of the system depends not only on the logical result of computation, but also on the time at which the results are produced [12].

Real-time systems are subjected to timing constraints. Depending on the criticality of those timing constraints, real-time systems can be classified in three categories [13]:

- Soft real-time systems: missing deadlines does not cause the systems to fail, but it may cause performance degradation. Examples of soft real-time systems include Internet Protocol (IP) communication, video streaming.

- *Hard real-time systems*: missing deadlines may cause catastrophic consequences on these systems. Examples of hard real-time systems include engine control unit, cruise control system in automotive systems, flight control systems, and chemical/nuclear plant control systems.

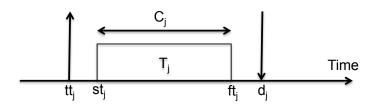

Figure 2.1: Typical parameters of real-time tasks

In order to support hard real-time applications, the following properties are necessary when designing real-time systems [13].

- *Timeliness*. Real-time systems have to produce the correct results in a timely manner. In other words, both functional correctness and timing correctness have to be satisfied.

- *Predictability*. The upperbounds of the execution times of tasks must be able to be estimated offline, and the satisfaction of timing constraints of tasks must be able to be checked before the system starts executing.

- *Efficiency*. Most real-time systems are embedded into small devices with hard constraints in term of space, weight, energy, memory, and computational power. Therefore, managing available resources efficiently is an essential feature of real-time systems.

- *Fault tolerance*. Real-time systems should not be damaged by single hardware and software failures.

In general, a real-time task can be characterized by the following parameters (as illustrated in Figure 2.1)

- Arrival time  $(tt_i)$ . The time at which the task is ready to execute,

- Start time  $(st_i)$ . The actual time at which the task starts executing,

- Computation time  $(C_j)$ . The upperbound of the execution times of the task when executing in isolation, referred to as worst-case execution time (WCET).

- Finish time  $(ft_i)$ . The time at which the task finishes its execution,

- Deadline  $(d_j)$ . The time before which the task should be completed.

### 2.1.2 Worst-case execution time estimation

The worst-case execution time (WCET) of a task is the maximum of its execution times under any input configurations and any initial hardware states [7].

The WCET of tasks are required to validate timing constraints. Therefore, WCET estimation is an essential step in the development and the validation process for hard real-time systems.

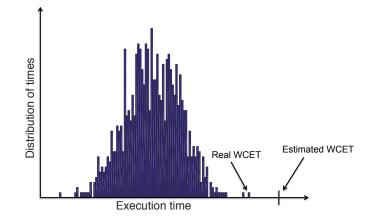

Figure 2.2: The variation of execution times of a task depending on the input data or different behavior of environment

As shown in Figure 2.2, a task may have variation of execution times depending on different input data or different initial hardware states. It is in general impossible to determine the exact WCET for a task (real WCET in the figure) since it is too time consuming to explore exhaustively all possible executions. Therefore, WCET analysis techniques, which produce estimated WCET for tasks (estimated WCET in the figure), are in need.

The estimated WCET is defined as the upperbound of estimated execution times of a task when executing in isolation. For simplicity, we use the term "WCET" as "estimated WCET" hereafter. In [7], Wilhelm et al. give an overview of the WCET analysis techniques and the available WCET analysis tools. According to this survey, WCET analysis techniques can be classified into the following categories:

- *Static WCET analysis methods*: the methods derive the WCET of tasks without running them on real hardwares. The approaches combine static analysis techniques with the abstract models of hardware architectures to produce WCET.

- *Measurement-based methods*: the methods measure the actual execution times of tasks when executing them on a real processor or a simulator of the processor under representative test conditions. Then the WCET of tasks are estimated based on the measured values according to a specific formulation. For example, for end-to-end measurements, the WCET of a task is equal to the maximum of its actual execution times.

Typically, static WCET analysis methods require three steps:

- *Flow analysis.* That step builds the control flow graph of the task under analysis from its executable code, and determines the loop bounds, as well as feasible execution paths through the task [14, 15].

- Low-level analysis. In that step, the worst-case execution costs of basic blocks are computed with taking into account the trace of the target hardware (e.g., caches,

pipeline, etc.). An example of the techniques that analyze the trace of hardware components is abstract interpretation [16].

• WCET computation. In the step, the WCET of the task is derived by combining the worst-case execution costs of basic blocks estimated in the second step with the loop bounds and the feasible execution paths found in the first step. The popular method used to find the longest execution path and its execution time is the Implicit Path Enumeration Technique (IPET) [17]. IPET considers all execution paths implicitly by using integer linear programming.

Static WCET analysis techniques vs. measurement-based methods. There are two main criteria for evaluating the quality of estimated results produced by WCET analysis techniques. The first criterion is *safety*, i.e., whether the upperbound of the execution times is produced or not. The second criterion is *precision*, i.e., how close of the produced upperbound to the exact value. In other words, the estimated WCETs have not to be *underestimated*, but should not be *overestimated* too much.

The static WCET analysis methods cover all feasible execution paths and consider all possible context dependencies of processor behavior. Therefore, the methods guarantee that the estimated WCETs are safe (assuming the hardware model is safe). For this safety, the methods have to model processors behavior. Since the abstraction models lose information, especially for complex hardwares architecture, so that the estimated WCETs are possibly imprecise. Several commercial and academic tools that use static analysis techniques to compute WCETs are available, such as aiT [18], Bound-T [19], OTAWA [20] or Heptane [21].

On the other hand, measurement-based methods use measurements instead of modeling processor behavior. The changes in execution times of tasks due to hardware context-dependent may be missed if the measurements are not performed in the worst-case initial state of hardwares. Additionally, in general it is too time consuming to derive input data that lead to the worst-case execution path. As a consequence, the estimated WCETs resulted by measurement-based methods are not guaranteed to be safe. The advantage of the methods is that it is simple to apply them to a new hardware architecture since the abstract model of the hardware architecture is not required. Rapitime distributed by Rapita Ltd [22] is one of the commercial tools that perform measurements in the process of estimating WCETs.

#### 2.1.3 Real-time task scheduling

For single-core platforms, task scheduling is a process that determines when and in what order tasks should execute. For multi-core platforms, along with the aforementioned scheduling problem for every core, task scheduling also attempts to solve a mapping problem, which determines on which cores tasks should execute.

Task models and the objective of task scheduling. In the literature, there are many task models have been used in real-time task scheduling. In this review, instead of listing all task models, we present two particular classifications of them according to dependencies between tasks, and the frequency of execution of tasks.

- Independent task models and dependent task models. In the independent task models, there is no dependencies between tasks, whereas, in the dependent task models, there are precedence relations between pairs of tasks. Directed Acyclic Graph (DAG) [23] is one of representative graphs used for dependent task models.

- Single execution task models and recurrent execution task models. In single execution task models, tasks have one and only one execution instance, whereas, in recurrent execution task models, tasks compose of an infinite sequence of jobs (as described in the survey [24]). Examples of recurrent execution task models are periodic task models, in which the distance of arrival times of jobs belong to the same task are fixed, and sporadic task models, in which the distance of arrival times of arrival times of these jobs are varied.

When applying to single execution task models, the objective of task scheduling methods is to minimize schedules length (or makespan), whereas, when applying to recurrent execution task models, the objective of task scheduling methods is to ensure that all tasks meet their deadline.

**Classification of task scheduling algorithms.** The task scheduling algorithms for single-core platforms can be classified as:

- *preemptive scheduling*: a task can be preempted by a higher priority task during its execution.

- *non-preemptive scheduling*: once a task starts executing, it will execute until completion without being preempted.

In preemptive scheduling algorithms, a task which requires "urgent" service (i.e., task whose deadline is reached soon) is allowed to preempt the current execution task for possessing computing resources of the core. Preemptions introduce runtime overheads due to preemption itself, cache misses, and prefetch mechanisms. Furthermore, due to the preemption, hardwares' state (e.g., caches, pipeline, etc.) are hard to manage. As a consequence, the preemption costs are difficult to predict [25, 26]. For overcoming this issue, many approaches have been proposed (read [27] for a survey). Some approaches have been proposed to limit the number of preemptions for each task, thus reducing the preemption costs. Besides, some approaches explicitly introduce preemption points in programs for improving the predictability of the preemption costs.

Regarding the allocation of tasks on multi-core platforms, task scheduling algorithms can be classified as:

- global scheduling: a task is allowed to execute on different cores.

- partitioned scheduling: a task is allocated to one and only one core.

In global scheduling, the migration of tasks leads to the change of hardware state (i.e., cache contents), which causes migration overheads are hard to predict. Semi-partitioned scheduling techniques [28] which make most tasks non-migrating, have been proposed to overcome this issue.

Figure 2.3: An example of multi-core architecture

Additionally, task scheduling algorithms can be classified based on the relative time (to the execution of applications) at which the scheduling decisions are made.

- online scheduling: the allocation and the schedule of tasks are determined at run time [29].

- offline scheduling: the allocation and the schedule of tasks are determined before the execution of applications [23].

Furthermore, according to the way used of activating the execution of tasks, task scheduling algorithms can be classified as:

- *event-driven scheduling*: the execution of tasks are triggered at the emergence of a specific event.

- *time-driven scheduling*: the execution of tasks are triggered at predefined instants of time.

### 2.1.4 Time-predictable multi-core hardware

Multi-core architectures. According to the Moore's Law [30] the number of transistors on a chip doubles once in every 18 months to meet growing demands on computing power. Studies in [2] have shown that integrating more and more transistors on a single core to meet the demands comes along with major bottlenecks such as issues on power consumption, heat dissipation, chip fabrication costs, as well as faulty hardware. Those issues impair the reliability and the life expectancy of chips, and require more budgets for cooling systems. The consideration on those issues is the key driving force behind the development of multicore architectures.

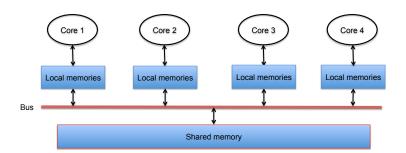

Typically, a multi-core architecture is a single chip which contains several cores on the chip (as illustrated in Figure 2.3). As compared to single-core architectures in which tasks running at the same time compete against each other for chip's computing resources, in multi-core architectures those tasks can be assigned to different cores to run in parallel, thus boosting the performance of systems [3]. Additionally, with the capability of executing tasks in parallel, cores inside multi-core architectures are not necessarily clocked at a high

frequency. That property makes multi-core architectures more energy efficient than singlecore architectures [31].

According to the demand of applications, multi-core architectures can be implemented in different ways. Multi-core architectures can be implemented as a group of homogeneous cores or as a group of heterogeneous cores or as a combination of both. In homogeneous multicore architectures, all cores are identical, whereas heterogeneous multi-core architectures consist of dedicated application specific cores. Each core is equipped with local memories (e.g., caches, scratchpad memories (SPM)). Tasks executing on different core can share data either through a shared memory or with the support of cache coherence protocol (if have) [32].

Major challenges faced by multi-core architectures. Although multi-core architectures offer many advantages, the technology faces a number of major challenges. First of all, in order to exploit the computing power of multi-core architectures, applications are required to be written in a way that exposes parallelism. Therefore, it requires to redesign a huge amount of legacy programs developed for single-core architectures. For addressing this issue, much effort have been spent on developing compilers to automatically generate parallel tasks for a given application [33]. Additionally, many parallel programming interfaces have been proposed, such as OpenMP [34], Pthreads [35].

The most important challenge arising when embedding multi-core architectures into realtime systems is shared resources contentions [8, 9]. Cores inside a multi-core architecture share hardware resources, such as bus, memories. Due to hardware sharing, the execution of tasks are delayed (when they access shared resources currently used by another core). Precisely estimating the delays offline is hard since the delays depend on many factors, such as the concurrent tasks involve to the contentions, the actual time at which the contentions occur, and the resources arbitration policy. Many research have been spent on limiting the issue, including the research in task timing analysis, in task scheduling, as well as in time-predictable multi-core architectures. The brief overview of the research in task timing analysis, and task scheduling will be given in Section 2.2.1, and Section 2.2.2, respectively. In the rest of the section, we describe the main characteristics of time-predictable multi-core architectures.

**Time-predictable multi-core architectures.** The main objective in designing timepredictable multi-core architectures is to eliminate (or mitigate) properties that make WCET analysis difficult, and potentially excessively pessimistic. The desired characteristics of timepredictable multi-core architectures are summarized as follows:

- Timing compositionality. The architectures with that property allow the result of worst-case timing analysis of each hardware component can be simply added together to determine the worst-case execution time of whole systems [36]. An example of multi-core platforms having that property is Kalray MPPA-256 [4].

- Spatial and temporal shared resource isolation. Isolating shared resources helps to mitigate the amount of possible interferences at the hardware level. This will isolate spatial and temporal of concurrent tasks running on different cores. Therefore, WCET

analysis for a task can be carried out independently. Such architecture is proposed in [37], which uses time-division multiple access(TDMA)-based bus sharing policy. In that architecture, the bus schedule contains slots of a certain size, each with start time, that are dedicated to cores. Therefore, any memory accesses issued by a core in its bus slots is guaranteed to be contention free. However, dedicating bus slots to cores impairs average performance of multi-core systems. The reason is that memory accesses of a core must to wait until its dedicated bus slots even though there is no requests from other cores.

- Local memories accesses are predictable. Such architectures with that property use software-controlled memory, i.e., scratchpad. Scratchpad is a fast on-chip memory and it is explicitly controlled by the user or managed by the system software, e.g., a compiler. Therefore, each memory access to scratchpad becomes predictable. T-Crest [38] is an example of multi-core platforms equipped with scratchpad memories.

- Controlling the time at instruction set architecture (ISA) level. PRET (precision time machine) [39] has been developed with this goal in mind. In that architecture, ISA is extended with time constraints. Therefore, the bounds (i.e., lower bound and upper bound) of the execution time of a code block are specified, which can be used to improve the estimation of shared resources contentions.

Since most designs for multi-core architectures are not dedicated to real-time systems, and there is a trade-off between the performance of whole systems and the timing predictability needed to be considered, so that it still requires a lot of work in the future to produce efficient time-predictable multi-core architectures.

#### 2.1.5 Cache memories

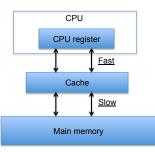

Main principles. As demonstrated in [40], there is a big gap between the processor and memory speeds. In order to improve the performance of whole systems, bridging that gap is in need. Cache memories have been proposed with that goal in mind. As depicted in Figure 2.4, a cache is a memory located between the processor registers and the main memory. A cache is smaller than a main memory, and the access time to the cache is much faster than the main memory. The function of a cache is to store the memory blocks loaded from the main memory. Therefore, the later accesses to those blocks by the core will be served directly by the cache. When the core finds a memory block it needs in the cache, the access to the memory block is a cache miss. A cache miss has a much higher cost (in term of access time, and power consumption) than a cache hit [41], because missing blocks have to be loaded into the cache from the main memory.

The effectiveness of caches is based on the principle of locality of references, explained as follows:

• *spatial locality*: there is a high probability that a reference will be requested if a reference close to it has been requested recently, i.e., instructions are often requested sequentially.

Figure 2.4: The location of cache

• *temporal locality*: already-requested references are more likely to be requested again in the near future, i.e., instructions in a loop.

Caches can be categorized depending on the type of information they store:

- Instruction caches: store only program instructions;

- Data caches: store only program data;

- Unified caches: store both program instructions and program data.

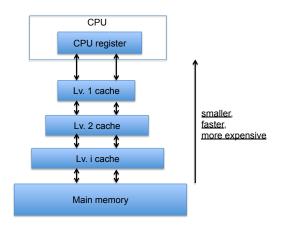

According to [42], smaller caches have lower access latencies, whereas larger caches have higher ones. However, smaller caches are more costly than higher ones. For achieving fast memory accesses, and at the same time providing large memory space at the low cost, memory hierarchies have been introduced. As shown in Figure 2.5, the memory hierarchy is made of several cache levels. Caches which are closer to the CPU are smaller, faster, and more costly than ones which are further to the CPU.

Figure 2.5: An example of memory hierarchy

**Cache organization.** A cache is divided into equal-sized cache lines. Each cache line can store one memory block loaded from the main memory, which contains a set of data (for the data cache) or several instructions (for the instruction cache) in order to benefit from spatial locality. Since the number of cache lines is lower than the number of main memory blocks, blocks stored in the cache will be evicted and replaced by new ones loaded from the main memory.

Different strategies (which are described in [43]) have been proposed for determining to which cache line a given memory block will be mapped:

- *Direct mapping*: a memory block is mapped into only one possible cache line. The mapping is determined based on the address of the memory block.

- Fully-associative mapping: a memory block is mapped to any cache line.

- Set-associative mapping: a cache is divided into sets of equal number of cache lines, and a memory block is mapped to any cache line in a particular set. The address of the memory block is used to determine to which set the memory block is mapped.

For fully-associative mapping and set-associative mapping, when the set to which a new memory block is mapped is full, it is essential to have a *replacement policy* to decide which cached items should be evicted to make room for the new one. For direct mapping, there is only one possible location to which a memory block is mapped, so that it does not require a replacement policy.

Panda et al. [44] give a survey of replacement policies, including optimal and suboptimal algorithms. The optimal algorithm is the one that can look into the future and determine what should be placed in the cache according to the limit of the cache's capacity and organization [45]. However, in case of dynamic systems in which memory references are only revealed at run time, the optimal strategies can not be applied. For those systems, there is no optimal replacement policy (according to [46]). Therefore, a number of sub-optimal replacement policies have been proposed:

- Least Recently Used (LRU): the memory block which has been least recently used is discarded.

- *First-In First-Out (FIFO)*: the memory block which has been in the cache longest is discarded.

- Least Frequently Used (LFU): the memory block which has experienced the fewest references is discarded.

The study in [47] showed that LRU is the best policy among these replacement policies in term of cache-state predictability.

**Timing anomalies.** The presence of caches substantially improves the performance of programs, but makes the timing behavior of the processors harder to predict. Lundqvist et al. [48] first defined the notion of the timing anomaly for out-of-order processors, stating that a cache hit which is locally faster (than a cache miss) leads to an increase of the execution time of the whole program.

# 2.2 Timing analysis for multi-core systems: state-of-theart

### 2.2.1 WCET analysis techniques for multi-core architectures

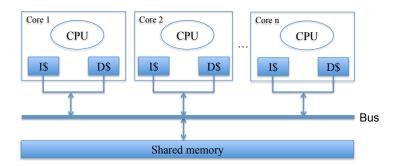

In static WCET analysis for single core platforms, the task under analysis is assumed to be not influenced by any external events, i.e., things related to the execution of another task or hardware devices, such as memory refreshes. However, this assumption needed to be reconsidered when applying to multi-core platforms since resources sharing introduces interferences on the execution of tasks [8, 9]. The interferences include data corruption, i.e., data stored in the shared cache, which is currently used by a task is invalidated by concurrents tasks, as well as conflicts on shared bus, i.e., several tasks have accesses to shared memories at the same time.

Due to the effect of shared resources contentions, WCETs produced by measurementbased techniques for multi-core platforms are possibly unsafe. The reason is that it is too time consuming to exhaustively capture all possible shared resources contentions at run time of tasks. In the section, we focus on static WCET analysis techniques, which is the most suitable when considering hard real-time tasks.

Many approaches have been proposed to address the resources sharing issues. According to the survey in [49], those approaches can be classified into two categories:

- The first category includes approaches that take all possibles interferences into account when computing the WCET of a task. Most approaches in that category require the knowledge of all tasks that may execute concurrently to the task under analysis. Some solutions have been proposed to analyze all possible contentions on shared caches by concurrent tasks [50, 51, 52, 53]. Those approaches first separately perform cache analysis (for both private caches and shared caches) for every task (i.e., by ignoring interferences). The analyzed results for the shared cache are then modified with considering interferences (caused by concurrent tasks). Additionally, some solutions have been proposed for modeling the interaction of shared caches and shared bus with other basic microarchitectural components, such as pipeline and branch predictor [54]. Furthermore, event-bus arbitration and more complex processor pipeline have been analyzed in [55, 56].

- The second category includes approaches that aim at controlling contentions to ease the WCET estimation. Most approaches in that category analyze the timing behavior of tasks independently with the support of either predictable hardware models or predictable execution models, which ensure the temporal and spatial isolation between running tasks. Shared cache thrashing can be avoided by using cache partitioning techniques [57, 58]. Additionally, the accesses of tasks to the shared memory can be isolated through either bank privatization [59, 60] or memory bandwidth reservation [61, 62, 63, 64, 65]. Furthermore, PRedictable Execution Model (PREM) [66] has been proposed to make the execution of tasks more predictable. In PREM, the code and data of a task are prefetched in the local memories (i.e., private locked cache or scratchpad memory) of the core to which the task is assigned, thus preventing those data from being evicted by the execution of concurrent tasks.

Along with WCET analysis approaches that address the resources sharing issues, there are many approaches focusing on communication/synchronization between tasks executing on different cores [67, 68, 69, 70]. In [67], they provide formulas that combine the WCETs of code snippets and the worst-case stall time (WCST) due to synchronization to obtain the WCET of a parallel application. In [69], they introduce new locking primitives to reduce the WCST, thus improving the estimated WCET of whole applications. In contrast to those approaches in which WCET analysis of different code snippets are performed separately, the approach proposed in [70] integrates the timing analysis of code regions running on the same core at once. By doing that, the hardware states (i.e., cache state) between the execution of different code regions on the same core are captured accurately, which improve the estimated WCET of the application.

### 2.2.2 Task scheduling algorithms for multi-core architectures

Much research effort has been spent on scheduling for multi-core platforms. Research on real-time scheduling for independent tasks is surveyed in [7]. This survey gives a taxonomy of multi-core scheduling strategies: global vs. partitioned vs. semi-partitioned, preemptive vs. non preemptive, time-driven vs. event-driven. Besides, there are many studies on real-time scheduling for dependent tasks. A seminal study in this class of work is presented in [71]. In this study, tasks are scheduled with respect to their precedence relations (i.e., tasks are only ready to be executed after the termination of their predecessors). Along with precedence relations between tasks, the scheduling approach presented in [72] also considers exclusion relations between tasks (i.e., at a time only one task has accesses to shared resources). The scheduling problem addressed in these works is partitioned non-preemptive scheduling. As noted in [73], finding optimal solution for partitioned non-preemptive scheduling problems is NP-hard. In order to overcome the issue, a lot heuristic scheduling approaches are proposed (please refer to [23] for the survey of these approaches). Additionally, there are scheduling approaches that simultaneously schedule tasks and messages exchanged between them. Techniques proposed in [74, 75] consider core-to-core communication, while techniques proposed in [76, 77, 78] consider communication through Network-On-Chip(NoC). Furthermore, many scheduling methods that address the effect of shared resources contentions have been proposed. The main concept of the approaches are presented below.

Taking into consideration shared resources contentions in task scheduling. Most scheduling approaches in that category integrate interference delays in task scheduling problem. The goal is to minimize shared resources interference so as to minimize the schedules length. The underlying concept of these scheduling approaches is based on the fact that WCET estimation and tasks scheduling are interdependent problems, i.e., scheduling algorithms require WCETs of tasks as prior knowledge, whereas, the WCETs of tasks are varied depending on their mappings and their execution order. Such scheduling approaches in the category have been proposed in [79, 80, 81]. In [79, 80] they focus on modeling shared cache contention, whereas in [81] they focus on modeling shared bus contention. Also attempting to reduce shared bus contention, but in [82], Martinez et al. approaches in a different way. Given the fixed mapping and the execution order of tasks, they introduce slack time between the execution of pairs of tasks consecutively assigned to the same core to limit the

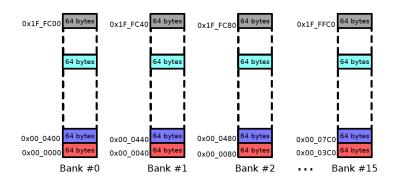

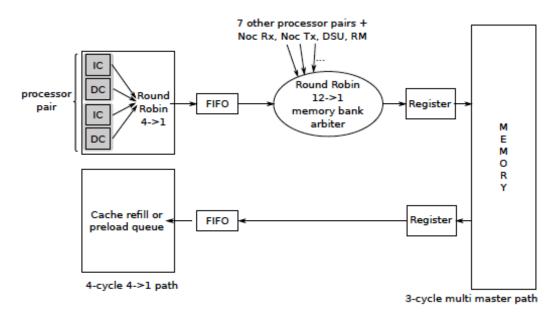

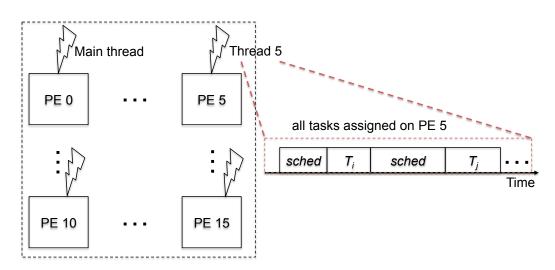

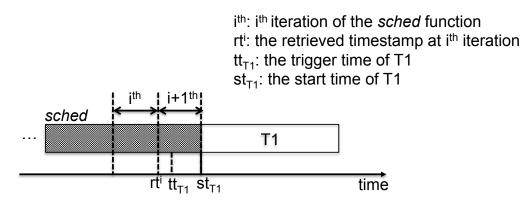

contention between concurrent tasks. In that way, the contentions that existed in existing schedules are reduced.