### Secure Implementation of Block Ciphers against Physical Attacks

Dahmun Goudarzi

#### ▶ To cite this version:

Dahmun Goudarzi. Secure Implementation of Block Ciphers against Physical Attacks. Cryptography and Security [cs.CR]. ENS Paris - Ecole Normale Supérieure de Paris, 2018. English. NNT: . tel-01896103v1

### HAL Id: tel-01896103 https://inria.hal.science/tel-01896103v1

Submitted on 15 Oct 2018 (v1), last revised 24 Dec 2018 (v2)

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT

de l'Université de recherche Paris Sciences et Lettres PSL Research University

Préparée à l'École normale supérieure

# Secure Implementation of Block Ciphers against Physical Attacks

École doctorale n°386 Sciences Mathématiques de Paris Centre

Spécialité Informatique

Soutenue par **Dahmun Goudarzi** le 21 septembre 2018

Dirigée par **Matthieu Rivain** et **Damien Vergnaud**

#### COMPOSITION DU JURY

Mme. Canteaut Anne INRIA Paris Examinatrice

M. Fouque Pierre-Alain Université de Rennes 1 Rapporteur

Mme. Handschuh Helena Rambus Examinatrice

M. Pointcheval David CNRS, École normale supérieure Examinateur

M. Renault Guénaël ANSSI Examinateur

M. Rivain Matthieu CryptoExperts Directeur de thèse

M. Schwabe Peter Radboud University Rapporteur

M. Vergnaud Damien UPMC Directeur de thèse

# Secure Implementation of Block Ciphers against Physical Attacks

Dahmun Goudarzi Thèse de doctorat dirigée par Matthieu Rivain et Damien Vergnaud

### Résumé

Depuis leur introduction à la fin des années 1990, les attaques par canaux auxiliaires sont considérées comme une menace majeure contre les implémentations cryptographiques. Parmi les stratégies de protection existantes, une des plus utilisées est le masquage d'ordre supérieur. Elle consiste à séparer chaque variable interne du calcul cryptographique en plusieurs variables aléatoires. Néanmoins, l'utilisation de cette protection entraîne des pertes d'efficacité considérables, la rendant souvent impraticable pour des produits industriels.

Cette thèse a pour objectif de réduire l'écart entre les solutions théoriques, prouvées sûres, et les implémentations efficaces déployables sur des systèmes embarqués. Plus particulièrement, nous nous intéressons à la protection des algorithmes de chiffrement par bloc tel que l'AES, dont l'enjeu principal revient à protéger les boîtes-s avec un surcoût minimal.

Nous essayons tout d'abord de trouver des représentations mathématiques optimales pour l'évaluation des boîtes-s en minimisant le nombre de multiplications (un paramètre déterminant pour l'efficacité du masquage, mais aussi pour le chiffrement homomorphe). Pour cela, nous définissons une méthode générique pour décomposer n'importe quelle boîte-s sur un corps fini avec une complexité multiplicative faible. Ces représentations peuvent alors être évaluées efficacement avec du masquage d'ordre supérieur. La flexibilité de la méthode de décomposition permet également de l'ajuster facilement selon les nécessités du développeur. Nous proposons ensuite une méthode formelle pour déterminer la sécurité d'un circuit évaluant des schémas de masquages. Cette technique permet notamment de déterminer de manière exacte si une attaque est possible sur un circuit protégé ou non. Par rapport aux autres outils existants, son temps de réponse n'explose pas en la taille du circuit et permet d'obtenir une preuve de sécurité quelque soit l'ordre de masquage employé. De plus, elle permet de diminuer de manière stricte l'emploi d'outils coûteux en aléas, requis pour renforcer la sécurité des opérations de masquages.

Enfin, nous présentons des résultats d'implémentation en proposant des optimisations tant sur le plan algorithmique que sur celui de la programmation. Nous utilisons notamment une stratégie d'implémentation bitslice pour évaluer les boîtes-s en parallèle. Cette stratégie nous permet d'atteindre des records de rapidité pour des implémentations d'ordres élevés. Les différents codes sont développés et optimisés en assembleur ARM, un des langages les plus répandus dans les systèmes embarqués tels que les cartes à puces et les téléphones mobiles. Ces implémentations sont, en outre, disponibles en ligne pour une utilisation publique.

## **Abstract**

Since their introduction at the end of the 1990s, side-channel attacks are considered to be a major threat to cryptographic implementations. Higher-order masking is considered to be one the most popular existing protection strategies against such attacks. It consists in separating each internal variable in the cryptographic computation into several random variables. However, the use of this type of protection entails a considerable efficiency loss, making it unusable for industrial solutions.

The goal of this thesis is to reduce the gap between theoretical solutions, proven secure, and efficient implementations that can be deployed on embedded systems. More precisely, I analyzed the protection of block ciphers such as the AES encryption scheme, where the main issue is to protect the s-boxes with minimal overhead in costs.

I have tried, first, to find optimal mathematical representations in order to evaluate the s-boxes while minimizing the number of multiplications (an important parameter for masking schemes, but also for homomorphic encryption). For this purpose, I have defined a generic method to decompose any s-box on any finite field with a low multiplicative complexity. These representations can then be efficiently evaluated with higher-order masking. The flexibility of the decomposition technique further allows the developer to easily adapt it to its needs.

Secondly, I have proposed a formal method for measuring the security of circuits evaluating masking schemes. This technique allows to define with exact precision whether an attack on a protected circuit is feasible or not. Unlike other tools, its computation time is not exponential in the circuit size, making it possible to obtain a security proof regardless of the masking order used. Furthermore, this method can strictly reduce the use of costly tools in randomness required for reinforcing the security of masking operations.

Finally, I present some implementation results with optimizations at both algorithmic and programming levels. I particularly employ a *bitslice* implementation strategy for evaluating the s-boxes in parallel. This strategy leads to speed record for implementations protected at high orders. The different codes are developed and optimized in ARM assembly, one of the most popular programming language in embedded systems such as smart cards and mobile phones. These implementations are also available online for public use.

# **Acknowledgments**

Je tiens tout d'abord à remercier Matthieu Rivain qui m'a donné l'opportunité de rejoindre la famille CryptoExperts, dans un premier temps en stage, puis en me renouvelant sa confiance en encadrant ma thèse pour une aventure qui aura duré 3 ans. Matthieu (a.k.a Patrooonnn) m'a transmis sa passion de la recherche (avec ses problèmes à 1 cocktail), du dévoleppement (avec ce duel sur l'AES en ARM, ou les challenges sur la multiplication) et il m'a permis de mûrir tant sur le plan cryptographique que sur le plan humain. Sans lui, je n'aurai probablement pas poussé mes études jusqu'à un doctorat. Nos nombreuses nuits blances (notamment celle du CHES 2016) resteront parmi mes meilleurs souvenirs de jeune chercheur. Je suis fier et honoré d'avoir pu être ton "premier".

Je tiens également à remercier Damien Vergnaud d'avoir accepté d'être mon directeur de thèse. Damien aurait pu faire le choix de regarder passer cette thèse passivement, comme cela peut arriver dans certaines CIFRE. Au contraire, Damien s'est investi dans ma thèse et sa culture cryptographique et mathématiques ont été précieuses. Nos nombreuses heures passées au tableau, à faire des démos ou à déchiffrer des papiers, parfois très obscurs, ont été fondamentales dans mon apprentissage. J'ai hâte de continuer nos collaborations en cours dans le futur. Je te remercie également d'avoir élargi ma collection rétro grâce à ton site magique!

Je remercie Anne Canteaut, Pierre-Alain Fouque, Helena Handschuh, David Pointcheval, Guénael Renault et Peter Scwhabe de me faire l'honneur de constituer mon jury de thèse. I particulary thank Pierre-Alain and Peter for taking the time of reviewing my PhD manuscript during their holidays!

Je suis également reconnaissant envers Guenael Renault d'avoir été un des meilleurs professeurs que j'ai croisé durant ma scolarité. Guenael m'a sorti d'une période obscure où je comptais arrêter mes études pour m'accueillir dans son master et me mettre sur la chemin de la cryptographie. Sa présence, son amitié, et ses conseils ont été primordiaux à l'aboutissement de mon parcours. Et puis sans lui, je n'aurai jamais pu implémenter des pivots de Gauss tous les ans sans discontinuité de la L3 au doctorat ou être dans le staff de "Le Ches"!

J'adresse également mes remerciements aux coauteurs et collaborateurs avec qui j'ai eu la chance de travailler ces dernières années. Merci donc à Srinivas Vivek, Anthony Journault, François-Xavier Standaert, Antoine Joux, Sonia Belaid, Victor Lomné, Jérémy Jean, Thomas Prest, Alain Passelegue et Ange Martinelli. Je tiens également à remercier André Chailloux, Thomas Debris, Jean-Pierre Tillich et Nicolas Sendrier de m'avoir donné l'opportunité de travailler pendant 4 mois à l'INRIA avec eux sur une proposition de signature. La une confiance totale qu'ils m'ont accordée pour le developpement de leur schéma m'a permis de franchir un cap professionnel important.

Cette thèse n'aura pas pu être faite sans l'environnement et la famille de CryptoExperts. J'aimerais donc remercier les membres (présents ou passés) qui la composent: Pascal Paillier (a.k.a Big Boss), Thomas Baignères, Sonia Belaid, Cécile Delerablée, Matthieu Finiasz,

viii Acknowledgments

Louis Goubin, Antoine Joux, Tancrède Lepoint, Chantal Lundvel, Michele Minelli, Matthieu Rivain et Junwei Wang. Mes conjugaisons de franglais, mon fin palet, les heures à faire du theory crafting, les jeux mobiles débiles, les jeux mobiles moins débiles, les organisations de cryptoparty, ma fameuse salade diet ou les sandwich Dahmun, tightProve, les high-five post acceptation, les brainstorms jeux de mots pourris pour à peu près tout et n'importe quoi, les 36000 propositions de logos (dont celles de Pascal), les paris pour l'Euro, les discutions sur le transhumanisme ou l'organisation d'un Cartathon, les courses metro, le slack, Ibizacrypt, les glaces (ah ces traîtresses), les riiiiiibssssssss, Keil (foutu Keil, un jour je te reconstruirai from scratch), la présence systématique de Big Boss tard le soir les semaines de deadline, la brigade du JouxPointFi et son intransigeance, les débats politiques, les pistaches, les vidéos de foot, Mathematica, New-York, Santa-Barbara, Vienne, Saint-Malo, agoranov, le linksys qui crame, la dégustation de caviar iranien, le champagne pour presque toutes les occasions possibles, le tapis de souris italien et le coq français, les courses carrefour, la tentative ratée de CM, les points synchros, LA partie d'echec (qui n'est pas finie!) mais surtout ce phénoménal "pot" (dans tous les sens du terme) de départ. Merci à vous pour tous ces moments partagés et pour le support et l'aide que vous m'avez fournis. Stylé de ouf, tu peux pas test!

J'ai eu la chance de pouvoir effectuer ma thèse dans l'équipe Crypto de l'ENS auprès de collègues mais surtout amis: Michel Abdalla, Balthazar Bauer, Sonia Belaid, Fabrice Benhamouda, Raphael Bost, Florian Bourse, Celine Chevalier, Jeremy Chotard, Simon Cogliani, Mario Cornejo, Geoffroy Couteau, Edouard Dufour Sans, Rafael Del Pino, Aurelien Dupin, Pierre-Alain Dupont, Pooya Farshim, Houda Ferradi, Georg Fuchsbauer, Romain Gay, Chloe Hebant, Julia Hesse, Louiza Khati, Pierrick Meaux, Thierry Mefenza, Michele Minelli, Anca Nitulescu, Michele Orru, Alain Passelegue, David Pointcheval, Thomas Prest, Razvan Rosie, Melissa Rossi, Adrian Thillard, Bogdan Ursu, Damien Vergnaud, and Hoeteck Wee. Merci pour ces escapes, soirées quizz, soirées jeux de sociétés, la finale du TI, ces horreurs d'aquariums, mon mug, secret santa, cryptnic, les fins de journées à la Montagne et surtout ces moments en conférence. J'aimerais aussi remercier l'équipe administrative de l'ENS et les membres du SPI: Jacques Beigbeder, Lise-Marie Bivard, Isabelle Delais, Nathalie Gaudechoux, Joelle Isnard, Valerie Mongiat, Ludovic Ricardou et Sophie Jaudon.

Je tiens également à exprimer ma gratitude aux personnes qui ont pris le temps de relire les versions préliminaires de ce mémoire: Ange, Aurélien, Laetitia, Matthieu F., Michele, Nima, Pierrick, Sonia, Thomas, Titâm et Mam.

Mes amis ont constitué une part importante de cette thèse. Leur expliquer ce que je faisais n'a pas toujours été facile mais ils ont toujours répondu présent quand j'avais besoin de me détacher de la cryptographie, qu'il s'agisse faire du sport, des escapes games, sauver new-york d'une épidémie ou Azeroth de la légion ardente. Les énumérer serait fastidieux mais ils se reconnaitront dans cette liste (et aussi, probablement, car il me reste 10 minutes avant d'aller à l'imprimerie). J'aimerais donc remercier la team h4, la team fac, la team magic, la team des Iraniens Z'ailés (retrouver nos "nombreux buts" sur Dailymotion!), la team CGI, la team ASP6, la colloque des fous malades, la colloque des bouchers Dunkerque, la team Capull, la team Panthéon et Montpar', la team Escape, les Quizzlords et la team Vegas Babyy.

Enfin, j'aimerai remercier ma famille d'avoir été présente depuis le début. Mon père et ma mère pour tout ce qu'ils m'ont inculqué et qui constitue ce que je suis aujourd'hui mais surtout pour leur soutien inconditionel, notamment lors de mes nombreux changements de parcours. Mon frère Tiam, pour m'avoir transmis toutes les passions que j'ai. Dès le plus jeune âge,

il m'a appris à regarder les mathématiques comme un jeu, m'a initié à l'informatique lors des premiers balbutiements d'Internet, mais aussi faut le dire, ses blagues vraiment nulles et souvent embarassantes! Daye, mon oncle, mon modèle, merci pour tes passages fréquents à Paris où sur un coup de tête on allait au Parc. Amouh et Ameh, pour m'avoir offert mon premier travail comme caissier et laveur de voitures, pour les après-midis aux casinos, les duels épiques de backgammon ou les virées en camping-car. Mon cousin Freever qui à 13 ans m'a mis un bouquin de C dans les mains et m'a donné 5 ans pour que je l'assimile et qu'on monte notre boîte de jeux vidéos. La dernière partie attend toujours, mais je ne perds pas espoir! Mes cousins Ashley, Jo, Nima et Sheyda, nos soirées parisiennes, new-yorkaises ou californiennes. Merci à Olivier, pour ta patience, ta mémoire fléchissante, mais surtout d'avoir veillé sur moi durant une période charnière. Tes tentatives de traits d'humour n'ont rien à envier à celles de Tiam! Et à mon neveu Nilai pour tout ce qu'il apporte à notre famille, sa joie, sa malice lorsqu'il me laisse lui acheter du Coca en douce ou monter sur mes épaules, sa passion pour les "bikinis", c'est-à-dire les croquemonsieurs, pour les néophytes.

# **Contents**

# Chapter 1

## Introduction

Cryptography is the science of secret, being both an ancient art from the antiquity and a new science for which scientific research has grown popular since the seventies. From ancient history, its use was essential to allow different military entities to communicate about vital information (army positions or numbers, resource disposal, etc.) without risking any leakage in case enemies intercept a message. Its ground goal is hence to guarantee the confidentiality of the information, namely the fact that only the authorized parties (namely that possess a certain cryptographic key) can understand encrypted information. With the rise of new technologies and the Internet, protecting communications and sensible data has become a crucial issue. Modern cryptography has then transitioned to answer the needs of the society as much as in democratising itself to no longer only serve military purposes but also to protect anyone's privacy, as well as in diversifying its utility. Nowadays, cryptography can provide confidentiality (only the sender and the receiver can understand the communication), authenticity (the receiver can verify from who he received the communication) and data integrity (the communication has not been altered during its transfer).

Since the 1970's, we distinguish two types of cryptography: secret-key cryptography and public-key cryptography. The former allows to establish secure communication when the two representatives share a secret private key that is used for both encryption and decryption (hence its other designation of symmetric cryptography), whereas the latter uses a pair of different keys, a public key and a private key, where the public key is used for encryption and the private key for decryption (hence its other designation of asymmetric cryptography). In this thesis, we will mainly focus on symmetric cryptography, and more particularly on cryptographic schemes called block ciphers. One of the most prevailing and deployed block ciphers is the Advanced Encryption Standard (AES) proposed by Daemen and Rijmen in 1998 and standardized by the National Institute of Standards and Technology (NIST) in 2001. Based on a substitution-permutation network, this encryption scheme is very efficient both in hardware and software. The security of this scheme, as for most symmetric cryptographic solutions, does not rely on formal security proofs but on the fact that since its release in the public domain 20 years ago no attack that performs better than an exhaustive search of the secret key has been found.

In order to render cryptographic applications easy and transparent for day to day usage, industry opted in the middle of the 1980's for a hardware solution that could fit inside a pocket: the smart card. Those cards are tiny computers that store secret keys and can perform cryptographic operations such as encryption, personal identification or authentication. The most famous ones are credit cards, the French Carte Vitale or SIM cards in our mobile phones. This solution represents a difficult cryptographic challenge as once deployed in the wild, it should guarantee the protection of the stored secrets from malicious adversaries that

can have a total control of the hardware.

In the late 1980's, Kocher introduced the first physical attack against cryptographic hardware such as embedded systems. This kind of attack differs from the one in the classical model, namely the black-box model, where the adversary can only access the input and the output of the cryptosystem to recover its secret key. Through physical access to the device evaluating cryptographic operations, the adversary can obtain information on intermediate computations that directly depends on the secret key, and can hence break the underlying cryptosystem. In particular, the adversary can exploit side channels of the hardware such as the computation time, the power consumption of the device or its electro-magnetic emanation during the computation. Those attacks are particularly efficient and disastrous since one can easily get access to the target device such as smart cards, and utilize those side-channels.

Among the existing countermeasures against physical attacks to protect block cipher implementations, the most widely used is (higher-order) masking. It consists in splitting every sensitive variable in the cryptographic computation into several random values, denoted shares, so that at the end of the computation the sum of all the shares is equal to the expected result. This is a sound countermeasure as it has been formally proven that the higher the number of shares, the more difficult for the attacker to recover the secret key. However, applying higher-order masking to protect a cryptographic implementation implies a strong overhead in performance which can make its deployment in an industrial context unrealistic. In fact, the performance losses come from the fact that elementary arithmetic operations are replaced with tools that perform secure operations on encodings of sensitive variables. The linear operations, such as addition, have a computation time that is linear in the number of masks, whereas the computation time of non-linear operations such as multiplication is quadratic in the number of masks. Hence, the bottleneck of protecting encryption schemes with higher-order masking is to efficiently compute those non-linear operations, which in a standard block cipher are the substitution boxes (s-boxes). Many theoretical schemes have been proposed to tackle the issue of efficient masking schemes. However most of them are still considered impracticable as soon as the masking order grows.

In the last couple of years, a first step towards efficient implementation of higher-order masking has been made. The solution is to look at the s-box as a polynomial over a finite field and to find an efficient way to represent it so that the number of multiplications required for its evaluation is minimized. Two main approaches have been studied in the literature. The first one targets specific s-boxes (such as the one of the AES) to exploit the particularity of their algebraic structure and get very efficient representation in terms of number of multiplications involved. The second one tackles this issue on any kind of functions and aims to get a generic decomposition technique. For both approaches, a new problem quickly arose. In fact, once the representation of the s-box has been found, its evaluation requires several compositions of masked operations which can introduce security flaws due to multiple manipulations of a same encoding. To thwart such security flaws, the solution is to generate new fresh encodings of the intermediate variables at carefully chosen positions in the masking scheme evaluation. However, this requirement introduces new overheads in efficiency as generating fresh encodings requires a large amount of randomness. Hence, an other issue of masking schemes is to reduce the randomness requirements.

This is why this thesis will be focusing on producing efficient secure implementations of block ciphers against physical attacks and bridging the gap between theoretical masking schemes and concrete practical implementations for which the overhead in efficiency is lowered such that the underlying implementation can be deployed in industrial solutions. To solve this problem, I have first started doing an implementation case study of all existing masking schemes in ARM assembly. This study resulted in the first concrete comparisons between all the polynomial solutions proposed in the state-of-the-art. I have also investigated an alternative to polynomial methods for specific block ciphers such as the AES which is based on bitslicing at the s-box level. This led to significantly faster implementations compared to polynomial solutions. Following this line of work, I studied the use of bitslicing for random s-boxes and proposed a method to get a representation of Boolean circuit with a minimalized multiplicative complexity. This new method led to implementation that are asymptotically faster than the classical polynomial approach but less efficient for small masking orders. Hence, I proposed a more generic framework that allows to decompose any polynomial over any finite field of characteristic two and encapsulating the previous methods (the polynomial approach and the Boolean approach). In all produced implementations, and more specifically for the AES s-box with a bitslice strategy, I have chosen a very conservative approach of inserting a refresh gadget after each multiplication to guarantee the security of the implementation. This conservative choice was backed up by the state-of-the-art tools that analyze the security of a circuit. However, these tools happen to produce false negatives and can hence lead to overkill in security gadgets. Therefore, I proposed a formal verification tool that can exactly check the security of an s-box implementation for any masking order. This allows to reduce by a factor of two the randomness requirement for the implementation of the AES s-box.

#### 1.1 Personal Contributions

The detailed list of my personal publications with full names, authors, and conferences is given at the end of the introduction. Here I briefly describe the goal of each of these papers, as well as the results they achieve.

#### 1.1.1 Contributions in this Thesis

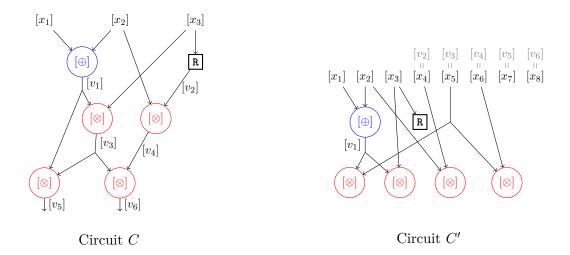

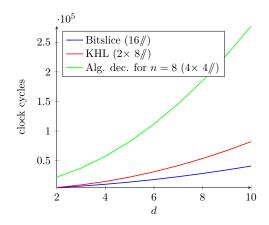

[CHES:GouRiv16] In this paper, we present a generic method to find a Boolean representation of an s-box with efficient bitsliced higher-order masking. Specifically, we propose a method to construct a circuit with low multiplicative complexity. Compared to previous works on this subject, our method can be applied to any s-box of common size and not necessarily to small s-boxes. We use it to derive higher-order masked s-box implementations that achieve important performance gain compared to optimized state-of-the-art implementations.

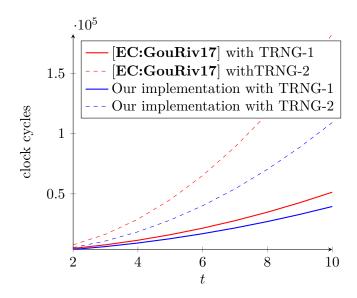

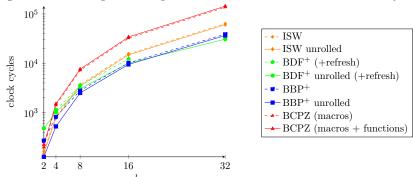

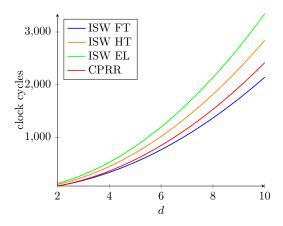

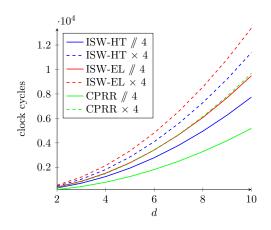

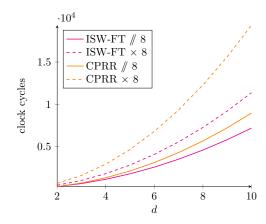

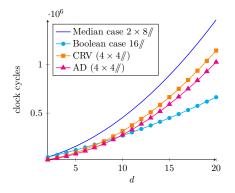

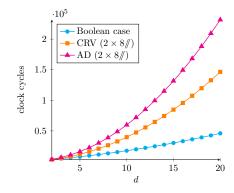

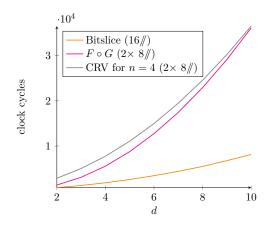

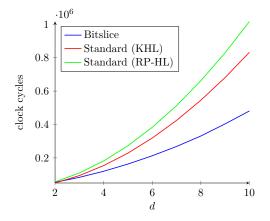

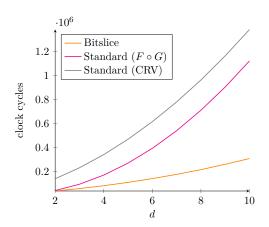

[EC:GouRiv17] In this paper, we investigate efficient higher-order masking techniques by conducting a case study on ARM architectures (the most widespread architecture in embedded systems). We follow a bottom-up approach by first investigating the implementation of the base field multiplication at the assembly level. Then we describe optimized low-level implementations of the ISW scheme and its variant (CPRR) due to Coron et al. (FSE 2013). Finally we present improved state-of-the-art polynomial decomposition methods for s-boxes with custom parameters and various implementation-level optimizations. We also investigate an alternative to these methods which is based on bitslicing at the s-box level. We describe new masked bitslice implementations of the AES and PRESENT ciphers. These implementations happen to be significantly faster than (optimized) state-of-the-art polynomial methods.

- **[CHES:GRVV17]** In this paper, we propose a generalized decomposition method for s-boxes that encompasses several previously proposed methods while providing new trade-offs. It allows to evaluate  $n\lambda$ -bit to  $m\lambda$ -bit s-boxes for any integers  $n, m, \lambda \geq 1$  by seeing it a sequence of m n-variate polynomials over  $\mathbb{F}_{2^{\lambda}}$  and by trying to minimize the number of multiplications over  $\mathbb{F}_{2^{\lambda}}$ .

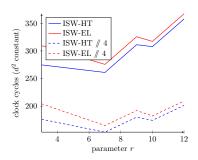

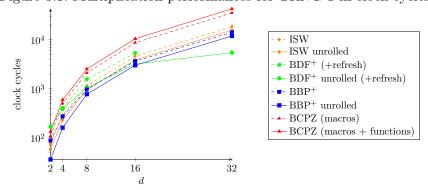

- [COSADE:GJRS18] In this paper, we optimize the performance and compare several recent masking schemes in bitslice representation on 32-bit ARM devices, with a focus on multiplication. Our main conclusion is that efficiency (or randomness) gains always come at a cost, either in terms of composability or in terms of resistance against horizontal attacks. Our evaluations should therefore allow a designer to select a masking scheme based on implementation constraints and security requirements. They also highlight the increasing feasibility of (very) high-order masking that are offered by increasingly powerful embedded devices, with new opportunities of high-security devices in various contexts.

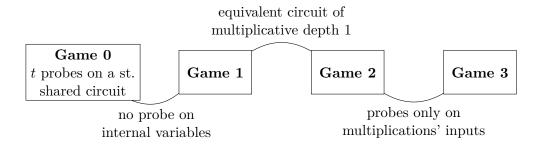

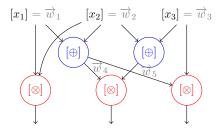

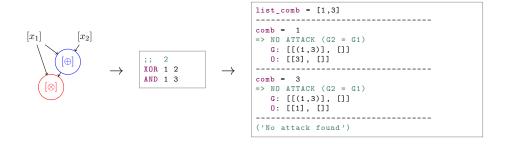

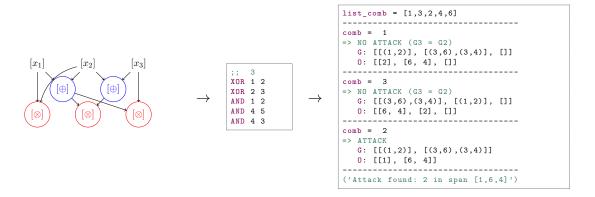

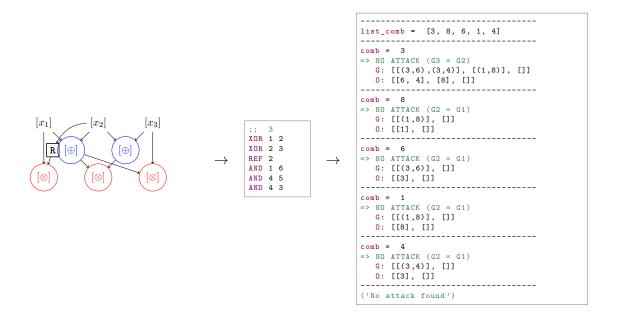

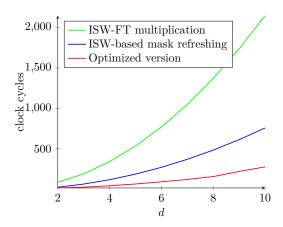

- [AC:BelGouRiv18] In this paper, we exhibit the first method able to clearly state whether a shared circuit composed of standard gadgets (addition, multiplication and refresh) is t-probing secure or not. Given such a composition, our method either produces a probing-security proof (valid at any order) or exhibits a security flaw that directly imply a probing attack at a given order. Compared to the state-of-the-art tool maskComp, our method can drastically reduce the number of required refresh gadgets to get a probing security proof, and thus the randomness requirement for some secure shared circuits. We apply our method to a recent AES implementation secured with higher-order masking in bitslice and we show that we can save all the refresh gadgets involved in the s-box layer, which results in a significant performance gain.

#### 1.1.2 Other contributions

- [SAC:GouRivVer16] In this paper, we extend existing attacks that exploit a few bits of the nonce to fully recover the secret key of elliptic-curve signature implementations protected with common countermeasures. Specifically, we extend the famous Howgrave-Graham and Smart lattice attack when the nonces are blinded by the addition of a random multiple of the elliptic-curve group order or by a random Euclidean splitting. We then assume that noisy information on the blinded nonce can be obtained through a template attack targeting the underlying scalar multiplication and we show how to characterize the obtained likelihood scores under a realistic leakage assumption. To deal with this scenario, we introduce a filtering method which given a set of signatures and associated likelihood scores maximizes the success probability of the lattice attack. Our approach is backed up with attack simulation results for several signal-to-noise ratio of the exploited leakage.

- [AC:GouJouRiv18] In this paper, we show how to compute in the presence of noisy leakage with a leakage rate up to  $\tilde{O}(1)$  in complexity  $\tilde{O}(n)$ . We use a polynomial encoding allowing quasilinear multiplication based on the fast Number Theoretic Transform (NTT). We first show that our scheme is secure in the random-probing model with leakage rate  $O(1/\log n)$ . Using the reduction by Duc *et al.* this result can be translated in the noisy leakage model with a  $O(1/|\mathcal{F}|^2 \log n)$  leakage rate. However, as in the

work of Andrychowicz et al. [EC:AndDziFau16], our construction also requires  $|\mathcal{F}| = O(n)$ . In order to bypass this issue, we refine the granularity of our computation by considering the noisy leakage model on logical instructions that work on constant-size machine words. We provide a generic security reduction from the noisy leakage model at the logical-instruction level to the random-probing model at the arithmetic level. This reduction allows us to prove the security of our construction in the noisy leakage model with leakage rate  $\tilde{O}(1)$ .

#### 1.2 Organization of this Thesis

In Chapter ??, I first detail all of the state-of-the-art solutions for masking schemes and some overview of the software choices we made throughout this thesis. In Chapter ??, I propose a generic decomposition method for any s-boxes to obtain efficient implementations. In Chapter ??, I formally define how the security of a circuit protected with higher-order masking can be reduced to problem of linear algebra. Then, I propose a formal verification tool that given a circuit outputs if an attack exists or not for any masking order. In Chapter ??, I detail optimisations at the algorithmic and assembly levels and give implementation results for the state-of-the-art methods as for the different schemes proposed in this thesis. Finally, I conclude in Chapter ?? with a brief summary of what I achieved and open questions that remain to be answered after this work.

# Chapter 2

# **Preliminaries**

#### 2.1 Higher-Order Masking

Among the existing protection strategies against physical attacks, one of the most widely used relies on applying secret sharing at the implementation level, which is known as (higher-order) masking. This strategy achieves provable security in the so-called probing security model [C:IshSahWag03] and noisy leakage model [EC:ProRiv13; EC:DucDziFau14], which makes it a prevailing way to obtain secure implementations against side-channel attacks.

#### 2.1.1 Description

Higher-order masking consists in sharing each internal variable x of a cryptographic computation into d random variables  $x_1, x_2, \ldots, x_d$ , called the shares and satisfying

$$x_1 + x_2 + \dots + x_d = x, (2.1)$$

for some group operation +, such that any set of d-1 shares is randomly distributed and independent of x. In this manuscript, we will consider the prevailing Boolean masking which is based on the bitwise addition of the shares. It has been formally demonstrated that in the noisy leakage model, where the attacker gets noisy information on each share, the complexity of recovering information on x grows exponentially with the number of shares [C:CJRR99; EC:ProRiv13]. This number d, called the masking order, is hence a sound security parameter for the resistance of a masked implementation.

When dth-order masking is involved to protect a block cipher, a so-called dth-order masking scheme must be designed to enable the computation on masked data. To be sound, a dth order masking scheme must satisfy the two following properties:

- completeness: at the end of the encryption/decryption, the sum of the d shares must give the expected result;

- probing security: every tuple of d-1 or less intermediate variables must be independent of any sensitive variable.

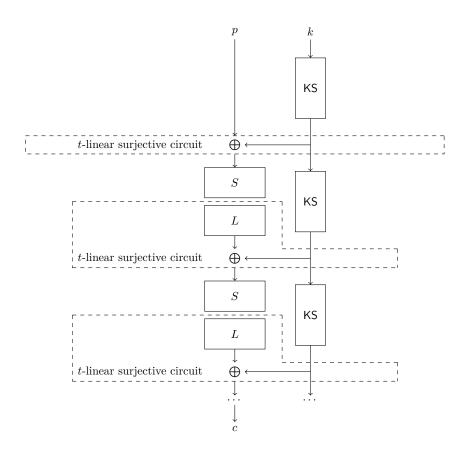

#### 2.1.2 Masking Block Ciphers

Most block cipher structures are composed of one or several linear transformation(s), and a non-linear function, the s-box (where the linearity is considered w.r.t. the bitwise addition). Computing a linear transformation  $x \mapsto \ell(x)$  in the masking world can be done in O(d) complexity by applying  $\ell$  to each share independently. This clearly maintains the probing security and the completeness holds by linearity since we have  $\ell(x_1) + \ell(x_2) + \cdots + \ell(x_d) = \ell(x)$ . On the other hand, the non-linear operations (such as s-boxes) are more tricky to compute on the shares while ensuring completeness and probing security.

The state-of-the-art solutions to perform a multiplication between two masked variable x and y are all based on the following rationale:

- 1. Compute the  $d^2$  cross products  $x_i y_j$ , for  $1 \le i, j \le d$ ;

- 2. Combine the cross products to get d output shares (in order to keep completeness);

- 3. Interleave fresh randomness in the previous step to avoid security flaws (in order to keep the probing security).

The main differences between all the solution in the literature are on how to implement this three different stages (see for instance [C:IshSahWag03; EC:BBPPTV16; CHES:BCPZ16; EC:BDFGSS17]).

#### 2.1.3 Implementation Transformation

We now describe how to transform the implementation of a block cipher into a secure implementation with higher-order masking.

#### 2.1.3.1 Encoding

Let us first detail how to encode every input of the block cipher into masked variables. Let d be the masking order. A random d-sharing of an element  $x \in \mathbb{F}_{2^n}$  is defined as follows:

**Definition 2.1.1.** Let  $x \in \mathbb{F}_{2^n}$  and  $d \in \mathbb{N}$ . A d-sharing of x is a tuple  $(x_i)_{i=1}^d \in \mathbb{F}_{2^n}^d$  satisfying  $\sum_{i=1}^d x_i = x$ .

A *d*-sharing is said to be *uniform* if, for a given x, it is uniformly distributed over the subspace of tuples satisfying  $x = \sum_{i=1}^{d} x_i$ . A uniform sharing of x is such that any m-tuple of its shares  $x_i$  is uniformly distributed over  $\mathbb{F}_2^m$  for any  $m \leq d$ . We further denote by Enc the probabilistic algorithm that maps an element  $x \in \mathbb{F}_{2^n}$  to a random uniform d-sharing of x:

$$\mathsf{Enc}(x) \mapsto (x_1, x_2, \dots, x_d) \ . \tag{2.2}$$

The corresponding decoding function Dec is defined as:

$$Dec(x_1, x_2, \dots, x_d) := \sum_{i=1}^{d} x_i$$

(2.3)

It is easy to check that we have  $\Pr(\mathsf{Dec}(\mathsf{Enc}(x)) = x) = 1$  for every  $x \in \mathbb{F}_{2^n}$ .

#### **2.1.3.2 Gadgets**

To perform operations on masked variables, we define new building blocks called gadgets that perform a given operation on d-sharings. For instance, for some two-input operation \*, a \*-gadget takes two input sharings  $\mathsf{Enc}(x_1)$  and  $\mathsf{Enc}(x_2)$  and it outputs a sharing  $\mathsf{Enc}(y)$  such that  $y = x_1 * x_2$ . In this thesis, we will only consider gadgets that take one input (refresh, squaring, or evaluation of a quadratic function) or two inputs (addition, subtraction, multiplication). Specifically, a gadget performs several elementary operation on the shares of the inputs in order to get the desired outputs. We give in the following some examples of the most used gadgets in this thesis.

• Addition gadget. Let  $(x_i)_{i=1}^d$  be a d-sharing of x and  $(y_i)_{i=1}^d$  be a d-sharing of y. To compute a d-sharing  $(z_i)_{i=1}^d$  of z = x + y, we simply compute:

$$(z_1, z_2, \dots, z_d) \leftarrow (x_1 + y_1, x_2 + y_2, \dots, x_d + y_d)$$

• **Field squaring gadget.** Let  $(x_i)_{i=1}^d$  be a *d*-sharing of x. To compute a *d*-sharing  $(z_i)_{i=1}^d$  of  $z=x^2$ , we simply compute:

$$(z_1, z_2, \dots, z_d) \leftarrow (x_1^2, x_2^2, \dots, x_d^2)$$

• Field multiplication gadget. Let  $(x_i)_{i=1}^d$  be a d-sharing of x and  $(y_i)_{i=1}^d$  be a d-encoding of y. To compute a d-sharing  $(z_i)_{i=1}^d$  of  $z = x \cdot y$ , we simply compute:

$$(z_1, z_2, \dots, z_d) \leftarrow \mathsf{IswMult}((x_1, x_2, \dots, x_d), (y_1, y_2, \dots, y_d))$$

where IswMult denotes the secure multiplication proposed by Ishai, Sahai and Wager and described in the following section (Section ??). Other algorithms for this operation are described in Chapter ??.

Finally, another type of gadget exists that does not perform an operation on d-sharing but from an input d-sharing of a secret variable x, produces a fresh random uniform d-sharing of this variable. This type of gadgets is called refresh gadget and works as follows:

• Refresh gadget. Let  $(x_i)_{i=1}^d$  be a d-sharing of x. To compute a d-sharing  $(z_i)_{i=1}^d$  of z=x, we simply compute:

$$(z_1, z_2, \dots, z_d) \leftarrow \mathsf{Refresh}(x_1, x_2, \dots, x_d)$$

The details on how to compute soundly the Refresh function are detailed hereafter. Basically, the idea is to perform a secure multiplication between an encoding of x and an encoding of 1, namely the d-sharing  $(1,0,\ldots,0)$ .

It is easy to see that to remain efficient, the goal is to find a secure implementation of the block cipher that minimizes the number of field multiplication, quadratic evaluation and refresh gadgets, as they are the ones with a quadratic complexity in the masking order. In this manuscript, we will equally use the denomination of gadgets and secure operations (namely secure multiplication, secure evaluation, etc...).

#### 2.1.3.3 Transformation

Now that we have defined encodings of sensitive variables and gadgets that perform simple operations on encodings, we can describe how to transform an implementation of a block cipher into a secure implementation protected with higher-order masking. To do so, every elementary operation in the implementation of the block cipher is transformed into the corresponding gadget working on d-sharings. Hence, the secure implementation takes as inputs d-sharings corresponding to each input of the block cipher thanks to the encoding function Enc. At the end of the computation, the output d-sharings of the computation are transformed into the outputs of the block-ciphers with the help of the decoding function Dec. At carefully chosen positions in the secure implementation, refresh gadgets are inserted in order to ensure the security of the implementation (see Chapter ?? for more details).

#### 2.1.4 Probing security

The probing security was first introduced in the seminal work of Ishai, Sahai, and Wager at Crypto 2003 [C:IshSahWag03]. It has been used to prove the security of several of the masking schemes in the literature. The definition of the probing security is defined as follows:

**Definition 2.1.2** (from [C:IshSahWag03]). Let d be the masking order and  $1 \le t \le d$  an integer. A algorithm is t-probing secure if and only if any set of at most t intermediate variables is independent from the secret.

Informally speaking, in this model, we suppose that the adversary can probe up to t intermediate computations in the secure implementation. Namely, she can place up to t probes in any of the elementary operations performed by the gadgets. As each of the elementary operations in a gadget are performed on shares, the attacker recovers the knowledge of the one or two shares processed by the operation. This can be seen as probing one software instruction where one probe allows to recover information on either the source of the instruction (namely one or two operands) or the destination (namely the output of the instruction). Then with the information provided by her probes, the adversary tries to find some dependence with the secret. If such dependence does not exist, then the secure implementation is said to be t-probing secure. One of the strongest advantages of this model is that it allows to do elegant and easy proofs to ensure the security of the secure implementation.

This model is also practically relevant and realistic as it catches what an adversary performs with an higher-order side-channel attack. In fact, in a practical scenario the attacker tries to find points of interest in the leakage trace corresponding to the evaluation of the implementation. Then he tries to recombine these point of interests to find a statistical correlation with the secret. Hence, the point of interests can be seen as placing probes in the secure implementation.

#### 2.2 Secure Non-Linear Operations

We now review some (widely used) constructions from the literature to compute masking gadgets for non-linear operations. The two operands  $x, y \in \mathbb{F}_{2^n}$  of the non-linear operation gadget are represented as random d-sharings  $(x_1, x_2, \ldots, x_d)$  and  $(y_1, y_2, \ldots, y_d)$ . Specifically, we focus on the scheme proposed by Ishai, Sahai, and Wagner (ISW scheme) for the secure multiplication [C:IshSahWag03], and its extension by Coron, Prouff, Rivain and Roche (CPRR scheme) to secure any quadratic function [FSE:CPRR13; C:CPRR15].

#### 2.2.1 Ishai-Sahai-Wagner Multiplication

From two d-sharings  $(x_1, x_2, \ldots, x_d)$  and  $(y_1, y_2, \ldots, y_d)$ , the ISW scheme computes an output d-sharing  $(z_1, z_2, \ldots, z_d)$  as follows:

- 1. for every  $1 \le i < j \le d$ , sample a random value  $r_{i,j}$  over  $\mathbb{F}_{2^n}$ ;

- 2. for every  $1 \le i < j \le d$ , compute  $r_{j,i} = (r_{i,j} + x_i \cdot y_j) + x_j \cdot y_i$ ;

- 3. for every  $\leq i \leq d$ , compute  $z_i = x_i \cdot y_i + \sum_{i \neq i} r_{i,j}$ .

One can check that the output  $(z_1, z_2, ..., z_d)$  is well a d-sharing of the product  $z = x \cdot y$ . We indeed have  $\sum_i z_i = \sum_{i,j} x_i \cdot y_j = (\sum_i x_i)(\sum_j y_j)$  since every random value  $r_{i,j}$  appears exactly twice in the sum and hence vanishes.

#### 2.2.2 Mask refreshing

The ISW multiplication was originally proved probing secure at the order  $t = \lfloor (d-1)/2 \rfloor$  (and not d-1 as one would expect with masking order d). The security proof was later made tight under the condition that the input d-sharings are based on independent randomness [CHES:RivPro10]. In some situations, this independence property is not satisfied. For

instance, one might have to multiply two values x and y where  $x = \ell(y)$  for some linear operation  $\ell$ . In that case, the shares of x are usually derived as  $x_i = \ell(y_i)$ , which clearly breaches the required independence of input shares. To deal with this issue, one must refresh the sharing of x. However, one must be careful doing so since a bad refreshing procedure might introduce a flaw [FSE:CPRR13]. A sound method for mask-refreshing consists in applying an ISW multiplication between the sharing of x and the tuple  $(1,0,0,\ldots,0)$  [EC:DucDziFau14; EC:BBDFGS15]. This gives the following procedure:

- 1. for every  $1 \le i < j \le d$ , randomly sample  $r_{i,j}$  over  $\mathbb{F}_{2^n}$  and set  $r_{j,i} = r_{i,j}$ ;

- 2. for every  $1 \le i \le d$ , compute  $x'_i = x_i + \sum_{j \ne i} r_{i,j}$ .

It is not hard to see that the output sharing  $(x'_1, x'_2, \ldots, x'_d)$  well encodes x. One might think that such a refreshing implies a strong overhead in performance (almost as performing two multiplications) but this is still better than doubling the number of shares (which roughly quadruples the multiplication time). Moreover, we show in Chapter ?? that the implementation of such a refreshing procedure can be very efficient in practice compared to the ISW multiplication.

#### 2.2.3 Coron-Prouff-Rivain-Roche evaluation

The CPRR scheme was initially proposed in [FSE:CPRR13] as a variant of ISW to securely compute multiplications of the form  $x \mapsto x \cdot \ell(x)$  where  $\ell$  is linear, without requiring refreshing. It was then shown in [C:CPRR15] that this scheme (in a slightly modified version) could actually be used to securely evaluate any quadratic function f over  $\mathbb{F}_{2^n}$ . The method is based on the following equation

$$f(x_1 + x_2 + \dots + x_d) = \sum_{1 \le i < j \le d} f(x_i + x_j + s_{i,j}) + f(x_j + s_{i,j}) + f(x_i + s_{i,j}) + f(s_{i,j})$$

$$+ \sum_{i=1}^d f(x_i) + (d+1 \mod 2) \cdot f(0) \quad (2.4)$$

which holds for every  $(x_i)_i \in (\mathbb{F}_{2^n})^d$ , every  $(s_{i,j})_{1 \leq i < j \leq d} \in (\mathbb{F}_{2^n})^{d(d-1)/2}$ , and every quadratic function f over  $\mathbb{F}_{2^n}$ .

From a d-sharing  $(x_1, x_2, ..., x_d)$ , the CPRR scheme computes an output d-sharing  $(y_1, y_2, ..., y_d)$  as follows:

- 1. for every  $1 \leq i < j \leq d$ , sample two random values  $r_{i,j}$  and  $s_{i,j}$  over  $\mathbb{F}_{2^n}$ ,

- 2. for every  $1 \le i < j \le d$ , compute  $r_{j,i} = r_{i,j} + f(x_i + s_{i,j}) + f(x_j + s_{i,j}) + f((x_i + s_{i,j}) + x_j) + f(s_{i,j})$ ,

- 3. for every  $1 \le i \le d$ , compute  $y_i = f(x_i) + \sum_{j \ne i} r_{i,j}$ ,

- 4. if d is even, set  $y_0 = y_0 + f(0)$ .

According to Equation (??), we then have  $\sum_{i=1}^{d} y_i = f(\sum_{i=1}^{d} x_i)$ , which shows that the output sharing  $(y_1, y_2, \dots, y_d)$  well encodes y = f(x).

In [FSE:CPRR13; C:CPRR15] it is argued that in the gap where the field multiplication cannot be fully tabulated ( $2^{2n}$  elements is too much) while a function  $f: \mathbb{F}_{2^n} \to \mathbb{F}_{2^n}$  can

be tabulated  $(2^n \text{ elements fit})$ , the CPRR scheme is (likely to be) more efficient than the ISW scheme. This is because it essentially replaces (costly) field multiplications by simple look-ups.

#### 2.3 Polynomial Methods for S-boxes

An approach to reduce the number of multiplication involved in the evaluation of the s-box in masking schemes is to consider the s-box as a polynomial over a finite field. This way, the problem of efficiently evaluating the non-linear part becomes equivalent to studying fast evaluation of polynomials over  $\mathbb{F}_{2^n}$ . In [FSE:CGPQR12], Carlet, Goubin, Prouff, Quisquater and Rivain, were the first to give a countermeasure based on polynomial representation of the s-box and proposed two methods to evaluate it. Then in [CHES:CorRoyViv14], Coron, Roy and Vivek extend their approach to propose a new generic method for fast evaluation of polynomials over binary fields.

In [FSE:CGPQR12] the notion of cyclotomic class is introduced, which will be used for the CRV method.

**Definition 2.3.1.** [Cyclotomic class] Let n be the number of input bits of the s-box and let  $\alpha \in [0; 2^n - 2]$ . The cyclotomic class of  $\alpha$  is the set  $C_{\alpha}$  defined by:

$$C_{\alpha} = \{\alpha.2^i \mod 2^n - 1 \ ; \ i \in [0; n-1]\}$$

A cyclotomic class allows to get efficient masked operations: a power  $x^{\alpha}$  can be computed from  $x^{\beta}$  without any non-linear multiplications if  $\alpha$  and  $\beta$  are in the same cyclotomic class since it only requires squarings.

#### 2.3.1 Coron-Roy-Vivek method

The CRV method was proposed by Coron, Roy and Vivek in [CHES:CorRoyViv14]. It consists in representing an s-box S(x) over  $\mathbb{F}_{2^n}[x]/(x^{2^n}-x)$  as

$$S(x) = \sum_{i=1}^{t-1} p_i(x) \cdot q_i(x) + p_t(x) , \qquad (2.5)$$

where  $p_i(x)$  and  $q_i(x)$  are polynomials with monomials in  $x^L$  for some set of cyclotomic classes  $L = C_{\alpha_1=0} \cup C_{\alpha_2=1} \cup C_{\alpha_3} \cup \ldots \cup C_{\alpha_\ell}$  such that for every  $i \geq 3$ ,  $\alpha_i = \alpha_j + \alpha_k \mod 2^n - 1$  for some j, k < i (or more generally  $\alpha_i = 2^w \cdot \alpha_j + \alpha_k \mod 2^n - 1$  with  $k \in [0, n-1]$ ). Such polynomials can be written as:

$$p_i(x) = \sum_{j=2}^{\ell} l_{i,j}(x^{\alpha_j}) + c_{i,0} \text{ and } q_i(x) = \sum_{j=2}^{\ell} l'_{i,j}(x^{\alpha_j}) + c'_{i,0} , \qquad (2.6)$$

where the  $l_{i,j}, l'_{i,j}$  are linearized polynomials over  $\mathbb{F}_{2^n}[x]/(x^{2^n}-x)$  and where the  $c_{i,0}, c'_{i,0}$  are constants in  $\mathbb{F}_{2^n}$ .

In [CHES:CorRoyViv14], the authors explain how to find such a representation. In a nutshell, one randomly picks the  $q_i$ 's and searches for  $p_i$ 's satisfying Equation (??). This amounts to solving a linear system with  $2^n$  equations and  $t \cdot |L|$  unknowns (the coefficients of the  $p_i$ 's). Note that when the choice of the classes and the  $q_i$ 's leads to a solvable system,

then it can be used with any s-box (since the s-box is the target vector of the linear system). We then have two necessary (non sufficient) conditions for such a system to be solvable, and one additional for the sake of efficiency:

- 1. the set L of cyclotomic classes is such that  $t \cdot |L| \geq 2^n$

- 2. all the monomials can be reached by multiplying two monomials from  $x^L$ , that is  $\{x^i \cdot x^j \mod (x^{2^n} x) \; ; \; i, j \in L\} = x^{[0,2^n-1]}$

- 3. every class (but  $C_0 = \{0\}$ ) have the maximal cardinality of n. Under this additional constraint, Condition ?? leads to the following inequality:  $t \cdot (1 + n \cdot (\ell 1)) \ge 2^n$ .

Minimizing the number of nonlinear multiplications while satisfying this constraint leads to parameters  $t \approx \sqrt{2^n/n}$  and  $\ell \approx \sqrt{2^n/n}$ .

Based on the above representation, the s-box can be evaluated using  $(\ell-2)+(t-1)$  nonlinear multiplications (plus some linear operations). In a first phase, one generates the monomials corresponding to the cyclotomic classes in L. Each  $x^{\alpha_i}$  can be obtained by multiplying two previous  $x^{\alpha_j}$  and  $x^{\alpha_k}$  (where  $x^{\alpha_j}$  might be squared w times if necessary). In the masking world, each of these multiplications is performed with a call to ISW. The polynomials  $p_i(x)$  and  $q_i(x)$  can then be computed according to Equation (??). In practice the linearized polynomials are tabulated so that at masked computation, applying a  $l_{i,j}$  simply consists in performing a look-up on each share of the corresponding  $x^{\alpha_j}$ . In the second phase, one simply evaluates Equation (??), which takes t-1 nonlinear multiplications plus some additions. We recall that in the masking world, linear operation such as additions or linearized polynomial evaluations can be applied on each share independently yielding an O(d) complexity, whereas nonlinear multiplications are computed by calling ISW with an  $O(d^2)$  complexity. The performance of the CRV method is hence dominated by the  $\ell+t-3$  calls to ISW.

#### 2.3.2 Algebraic decomposition method

The algebraic decomposition method was proposed by Carlet, Prouff, Rivain and Roche in [C:CPRR15]. It consists in using a basis of polynomials  $(g_1, g_2, \ldots, g_r)$  that are constructed by composing polynomials  $f_i$  as follows

$$\begin{cases} g_1(x) = f_1(x) \\ g_i(x) = f_i(g_{i-1}(x)) \end{cases}$$

(2.7)

The  $f_i$ 's are of given algebraic degree s. In our context, we consider the algebraic decomposition method for s = 2, where the  $f_i$ 's are (algebraically) quadratic polynomials. The method then consists in representing an s-box S(x) over  $\mathbb{F}_{2^n}[x]/(x^{2^n} - x)$  as

$$S(x) = \sum_{i=1}^{t} p_i(q_i(x)) + \sum_{i=1}^{r} \ell_i(g_i(x)) + \ell_0(x) , \qquad (2.8)$$

with

$$q_i(x) = \sum_{j=1}^r \ell_{i,j}(g_j(x)) + \ell_{i,0}(x) , \qquad (2.9)$$

where the  $p_i$ 's are quadratic polynomials over  $\mathbb{F}_{2^n}[x]/(x^{2^n}-x)$ , and where the  $\ell_i$ 's and the  $\ell_{i,j}$ 's are linearized polynomials over  $\mathbb{F}_{2^n}[x]/(x^{2^n}-x)$ .

As explain in [C:CPRR15], such a representation can be obtained by randomly picking some  $f_i$ 's and some  $\ell_{i,j}$ 's (which fixes the  $q_i$ 's) and then searching for  $p_i$ 's and  $\ell_i$ 's satisfying Equation (??). As for the CRV method, this amounts to solving a linear system with  $2^n$  equations where the unknowns are the coefficients of the  $p_i$ 's and the  $\ell_i$ 's. Without loss of generality, we can assume that only  $\ell_0$  has a constant term. In that case, each  $p_i$  is composed of  $\frac{1}{2}n(n-1)$  monomials, and each  $\ell_i$  is composed of n monomials (plus a constant term for  $\ell_0$ ). This makes a total of  $\frac{1}{2}n(n-1) \cdot t + n \cdot (r+1)$  unknown coefficients. In order to get a solvable system we hence have the following condition:  $(1) \frac{1}{2}n(n-1) \cdot t + n \cdot (r+1) \ge 2^n$ . A second condition is  $(2) 2^{r+1} \ge n$ , otherwise there exists some s-box with algebraic degree greater than  $2^{r+1}$  that cannot be achieved with the above decomposition i.e. the obtained system is not solvable for every target S.

Based on the above representation, the s-box can be evaluated using r + t evaluations of quadratic polynomials (the  $f_i$ 's and the  $q_i$ 's). In the masking world, this is done with the help of CPRR evaluations. The rest of the computation are additions and (tabulated) linearized polynomials which are applied to each share independently with a complexity linear in d. The cost of the algebraic decomposition method is then dominated by the r + t calls to CPRR.

#### 2.3.3 Specific Methods for AES and PRESENT

Specific methods that target the algebraic structure of a particular s-box have also been proposed in the literature. In this thesis, we mainly focus on the s-box of the AES and of PRESENT as they are popular block-ciphers, the former beeing the standard for encryption and the latter one of the most efficient lightweight block-ciphers.

#### 2.3.3.1 Rivain-Prouf Decomposition

Many works have studied masking schemes for the AES s-box and most of them are based on its peculiar algebraic structure. This s-box is defined as the composition of the *inverse* function  $x \mapsto x^{254}$  over  $\mathbb{F}_{2^8}$  and an affine function:  $S(x) = \mathrm{Aff}(x^{254})$ . The affine function being straightforward to mask with linear complexity, the main issue is to design an efficient masking scheme for the inverse function. In [CHES:RivPro10], Rivain and Prouff introduced the approach of using an efficient addition chain for the inverse function that can be implemented with a minimal number of ISW multiplications. They show that the exponentiation to the power of 254 can be performed with 4 nonlinear multiplications plus some (linear) squarings, resulting in a scheme with 4 ISW multiplications. In [FSE:CPRR13], Coron et al. propose a variant where two of these multiplications are replaced CPRR evaluations (of the functions  $x \mapsto x^3$  and  $x \mapsto x^5$ ).\(^1\) This was further improved by Grosso et al. in [AFRICACRYPT:GroProSta14] who proposed the following addition chain leading to 3 CPRR evaluations and one ISW multiplications:  $x^{254} = (x^2 \cdot ((x^5)^5)^5)^2$ . This addition chain has the advantage of requiring a single function  $x \mapsto x^5$  for the CPRR evaluation (hence a single LUT for masked implementation). Moreover it can be easily checked by exhaustive

<sup>&</sup>lt;sup>1</sup>The original version of the RP scheme [CHES:RivPro10] actually involved a weak mask refreshing procedure which was exploited in [FSE:CPRR13] to exhibit a flaw in the s-box processing. The CPRR variant of ISW was originally meant to patch this flaw but the authors observed that using their scheme can also improve the performances. The security of the obtained variant of the RP scheme was recently verified up to masking order 4 using program verification techniques [EC:BBDFGS15].

$\overline{F}$

2

$\mathbf{F}$

6

5

3

D

search that no addition chain exists that trades the last ISW multiplication for a CPRR evaluation.

#### 2.3.3.2 Kim-Hong-Lim (KHL) method

This method was proposed in [CHES:KimHonLim11] as an improvement of the RP scheme. The main idea is to use the tower field representation of the AES s-box [AC:SMTM01] in order to descend from  $\mathbb{F}_{2^8}$  to  $\mathbb{F}_{2^4}$  where the multiplications can be fully tabulated. Let  $\delta$  denote the isomorphism mapping  $\mathbb{F}_{2^8}$  to  $(\mathbb{F}_{2^4})^2$  with  $\mathbb{F}_{2^8} \equiv \mathbb{F}_{2^4}[x]/p(x)$ , and let  $\gamma \in \mathbb{F}_{2^8}$  and  $\lambda \in \mathbb{F}_{2^4}$  such that  $p(x) = x^2 + x + \lambda$  and  $p(\gamma) = 0$ . The tower field method for the AES s-box works as follows:

```

1. a_h \gamma + a_l = \delta(x), \ a_h, a_l \in \mathbb{F}_{2^4}

2. d = \lambda a_h^2 + a_l \cdot (a_h + a_l) \in \mathbb{F}_{2^4}

3. d' = d^{14} \in \mathbb{F}_{2^4}

4. a'_h = d' \ a_j \in \mathbb{F}_{2^4}

5. a'_l = d' (a_h + a_l) \in \mathbb{F}_{2^4}

6. S(x) = \text{Aff}(\delta^{-1}(a'_h \gamma + a'_l)) \in \mathbb{F}_{2^8}

```

At the third step, the exponentiation to the 14 can be performed as  $d^{14} = (d^3)^4 \cdot d^2$  leading to one CPRR evaluation (for  $d \mapsto d^3$ ) and one ISW multiplication (plus some linear squarings).<sup>2</sup> This gives a total of 4 ISW multiplications and one CPRR evaluation for the masked AES implementation.

#### 2.3.3.3 Method for PRESENT

$\frac{x}{S(x)}$

G(x)

F(x)

$7 \mid E \mid 9$

As a 4-bit s-box, the PRESENT s-box can be efficiently secured with the CRV method using only 2 ISW multiplications, where the field multiplications are fully tabulated. The algebraic decomposition method would give a less efficient implementation with 3 CPRR evaluations. Another possible approach is to use the fact that the PRESENT s-box can be expressed as the composition of two quadratic functions  $S(x) = F \circ G(x)$ . This representation (which is recalled in Table ??) was put forward by Poschmann  $et\ al.$  in [JC:PMKLW11] to design an efficient threshold implementation of PRESENT. In our context, this representation can be used to get a masked s-box evaluation based on 2 CPRR evaluations. Note that this method is asymptotically slower than CRV with 2 full-table ISW multiplications. However, due to additional linear operations in CRV,  $F \circ G$  might actually be better for small values of d.

|                         |   |   |   |   |   |   |   | ( | , |   |   | , |   |   |

|-------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0                       | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | В | С | D | E |

| $\overline{\mathbf{C}}$ | 5 | 6 | В | 9 | 0 | Α | D | 3 | E | F | 8 | 4 | 7 | 1 |

D

$C \mid 4 \mid 6$

$5 \mid C$

Α

F

$1 \mid 8$

9

$\mathbf{E}$

Table 2.1: PRESENT s-box  $S(x) = F \circ G(x)$ .

2

7 | A | 3

В

$B \mid 0 \mid 4$

<sup>&</sup>lt;sup>2</sup>The authors of [CHES:KimHonLim11] suggest to perform  $d^3 = d^2 \cdot d$  with a full tabulated multiplication but this would actually imply a flaw as described in [FSE:CPRR13]. That is why we use a CPRR evaluation for this multiplication.

#### 2.4 Bitslice Strategy

Bitslicing is an implementation strategy initially proposed by Biham in [FSE:Biham97b]. It consists in performing several parallel evaluations of a Boolean circuit in software where the logic gates can be replaced by instructions working on registers of several bits. As nicely explained in [CHES:MatNak07], "in the bitslice implementation one software logical instruction corresponds to simultaneous execution of  $\ell$  hardware logical gates, where  $\ell$  is a register size [...] Hence bitslice can be efficient when the entire hardware complexity of a target cipher is small and an underlying processor has many long registers."

In the context of higher-order masking, bitslicing can be used at the s-box level to perform several secure s-box computations in parallel. One then needs a compact Boolean representation of the s-box, and more importantly a representation with the least possible nonlinear gates. Specifically, based on a Boolean circuit for an s-box S, one can perform  $\ell$  parallel evaluations of S in software by replacing each gate of the circuit with the corresponding bitwise instruction, where  $\ell$  is the bit-size of the underlying CPU architecture. It results that the only nonlinear operations in the parallel s-box processing are bitwise AND instructions between  $\ell$ -bit registers which can be efficiently secured using the ISW scheme. Such an approach achieves important speedup compared to polynomial methods since (i) ISW-based ANDs are substantially faster than ISW-based field multiplications in practice, (ii) all the s-boxes within a cipher round are computed in parallel. Such an approach was applied in [FSE:GLSV14] to design block ciphers with efficient masked computations. To the best of our knowledge, it has never been applied to obtain fast implementations of classical block ciphers such as AES or PRESENT.

#### 2.4.1 ISW Logical AND

The ISW scheme can be easily adapted to secure a bitwise logical AND between two m-bit registers. From two d-sharings  $(a_1, a_2, \ldots, a_d)$  and  $(b_1, b_2, \ldots, b_d)$  of two m-bit strings  $a, b \in \{0, 1\}^m$ , the ISW scheme computes an output d-sharing  $(c_1, c_2, \ldots, c_d)$  of  $c = a \wedge b$  as follows:

- 1. for every  $1 \le i < j \le d$ , sample an m-bit random value  $r_{i,j}$ ,

- 2. for every  $1 \leq i < j \leq d$ , compute  $r_{j,i} = (r_{i,j} \oplus a_i \wedge b_j) \oplus a_j \wedge b_i$ ,

- 3. for every  $1 \leq i \leq d$ , compute  $c_i = a_i \wedge b_i \oplus \bigoplus_{j \neq i} r_{i,j}$ .

If the architecture size is  $\ell$ , we can hence perform  $\ell$  secure logical AND in parallel. Moreover a logical AND is a single instruction so we expect the above ISW logical AND to be faster than the ISW field multiplications.

### 2.5 ARM Assembly

In this thesis most of the implementation produced to benchmark and compare the different masking schemes are developed in ARM assembly, a low level implementation language widely used in mobile devices and smart cards. Most ARM cores are RISC processors composed of sixteen 32-bit registers, labeled RO, R1, ..., R15. Registers RO to R12 are known as *variable*

registers and are available for computation.<sup>3</sup> The three last registers are usually reserved for special purposes: R13 is used as the stack pointer (SP), R14 is the link register (LR) storing the return address during a function call, and R15 is the program counter (PC). The link register R14 can also be used as additional variable register by saving the return address on the stack (at the cost of push/pop instructions). The gain of having a bigger register pool must be balanced with the saving overhead, but this trick enables some improvements in many cases.

In ARM v7, most of the instructions can be split into the following three classes: data instructions, memory instructions, and branching instructions. The data instructions are the arithmetic and bitwise operations, each taking one clock cycle (except for the multiplication which takes two clock cycles). The memory instructions are the load and store (from and to the RAM) which require 3 clock cycles, or their variants for multiple loads or stores (n + 2 clock cycles). The last class of instructions is the class of branching instructions used for loops, conditional statements and function calls. These instructions take 3 or 4 clock cycles. This classification is summarized in Table ??.

Table 2.2: ARM instructions.

One important specificity of the ARM assembly is the barrel shifter allowing any data instruction to shift one of its operands at no extra cost in terms of clock cycles. Four kinds of shifting are supported: the logical shift left (LSL), the logical shift right (LSR), the arithmetic shift right (ASR), and the rotate-right (ROR). All these shifting operations are parameterized by a shift length in [1,32] (except for the logical shift left LSL which lies in [0,31]). The latter can also be relative by using a register but in that case the instruction takes an additional clock cycle.

Another feature of ARM assembly that can be very useful is the branch predication. This feature allows any instruction to be conditionally executed with respect to a (data dependent) flag value (e.g. the carry flag, the zero flag, etc.). In the context of secure embedded implementations, we have to ensure a data-independent operation flow in order to prevent timing and/or simple side-channel attacks. We must therefore avoid data-dependent conditional branches. For this reason we do not make use of the branch predication, except when it involves non-sensitive data such as loop counters.

### 2.6 Open Problems

As explained in this chapter, gadgets performing operation on d-sharing are the ground building block of masking schemes. As the multiplication gadgets require a quadratic number of field operations with respect to the masking order, an interesting line of work could be

<sup>&</sup>lt;sup>3</sup>Note that some conventions exist for the first four registers RO-R3, also called *argument registers*, and serving to store the arguments and the result of a function at call and return respectively.

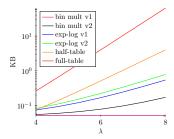

to find efficient ways to perform those operations. In fact, field multiplications are the core operations in the evaluation of multiplication gadgets. As soon as the field size grows, field multiplication can not be fully tabulated due to the size of the look-up tables. Hence, studying and optimizing at the implementation level different approaches to perform those field multiplications, such as the Karatsuba multiplication or the exp-log multiplication, can lead to efficient multiplication gadgets with different time and memory trade-offs.

In the past few years, several new secure multiplication schemes have been proposed based on the ISW multiplication method to get more efficient (at the cost of security) or more secure (at the cost of effiency) multiplication gadgets. However, no work made a concrete comparison between these different secure multiplications to better understand the performance gains and overheads that correspond to their different security guarantees. Moreover, several lines of work are based on the fact that the CPRR evaluation scheme should outperform the ISW multiplication scheme to justify their efficiency. However, no concrete comparisons at an implementation level have been made to corroborate the state-of-the-art intuition.

One of the missing part of all the proposed masking schemes to get an efficient polynomial decomposition of an s-box is a concrete comparison of them in practice. In fact, no work has produced a fair implementation of all the solutions and analysed the performance results to have clear insight on which method to use. It also seems like going down in a smaller field to perform the decomposition allows to get more efficient implementation results. Pushing forward this approach could be of interest by going over the Boolean field. Under this field, the costly field multiplication becomes a simple bitwise AND and with a bitslice strategy this could allow some significant improvement in the performance gain.

The idea of working on smaller field could also be ported to generic methods. In fact, the CRV method could be extend to any finite field to produce more efficient decomposition. One could produce generic methods for any s-box that is defined with respect to the s-box input and output and the field size. Then, the developer could instantiate the decomposition with these parameters on any finite field of characteristic 2 to get the most suitable decomposition depending on his requirements. For instance, as the bitslice strategy seems to be promising to obtain efficient masking schemes, it can be interesting to have a decomposition method for generic s-boxes over the Boolean field.

Finally, most of the masking schemes are very consuming in terms of randomness requirement due to the multiplication gadgets but also the refresh gadgets. Minimizing the randomness consumption is hence an important line of work in order to produce efficient implementations of masking schemes. Several formal verification tools have been developed in the recent years to ensure the probing security of masking schemes by placing refresh gadgets at carefully chosen positions. However, it sometimes happen that those tools lead to add refresh gadgets at uncessary positions (in terms of probing security). It can be interesting to find a formal method that allows to guarantee the probing security of an implementation with a tight number of inserted refresh gadgets, compared to existing solutions, in order to lower the randomness usage.

# Chapter 3

# **Decomposition**

#### 3.1 Introduction

As explained in Chapter ??, the most widely-used solution is to consider the representation as a polynomial function over a finite field (using Lagrange's interpolation theorem) and to find an efficient way to evaluate this polynomial. In order to obtain an efficient implementation of an s-box protected with higher-order masking, the first challenge is to find an efficient representation of it, where the number of multiplications involved in the evaluation is minimized.

The first generic method to mask any s-box at any masking order d was proposed in 2012 by Carlet, Goubin, Prouff, Quisquater and Rivain [FSE:CGPQR12] (following prior work by Rivain and Prouff for the AES block cipher [CHES:RivPro10]). The core idea is to split the evaluation of the polynomial representation of the s-box into simple operations over  $\mathbb{F}_{2^n}$  (namely, addition, multiplication by a constant, squaring and regular multiplication of two distinct elements), where n denotes the number of input bits of the s-box. Among these operations, only the regular multiplication of two distinct elements is non-linear (since squaring over a characteristic 2 finite field is linear), and one can use the secure multiplication algorithms to evaluate them [CHES:RivPro10; EC:BBPPTV16; CHES:BCPZ16]. Carlet et al. [FSE:CGPQR12] defined the masking complexity (also known as multiplicative complexity and non-linear complexity) of an s-box as the minimal number of such multiplications necessary to evaluate the corresponding polynomial and they adapted known methods for polynomial evaluation based on cyclotomic classes (see [FSE:CGPQR12] for details).

This technique was later improved by Roy and Vivek in [CHES:RoyViv13] using cyclotomic cosets addition chains. They notably presented a polynomial evaluation method for the DES s-boxes that requires 7 non-linear multiplications (instead of 10 in [FSE:CGPQR12]). They also presented a lower-bound on the length of such a chain and showed that the multiplicative complexity of the DES s-boxes is lower bounded by 3. In 2014, Coron, Roy and Vivek [CHES:CorRoyViv14] proposed a heuristic method which may be viewed as an extension of the ideas developed in [FSE:CGPQR12] and [CHES:RoyViv13]. The so-called CRV method considers the s-box as a polynomial over  $\mathbb{F}_{2^n}$  and has heuristic multiplicative complexity  $O(2^{n/2}/\sqrt{n})$  instead of  $O(2^{n/2})$  proven multiplicative complexity for the previous methods. They also proved a lower bound of  $\Omega(2^{n/2}/\sqrt{n})$  on the multiplicative complexity of any generic method to evaluate n-bit s-boxes. For all the tested s-boxes their method is at least as efficient as the previous proposals and it often requires fewer non-linear multiplications (e.g. only 4 for the DES s-boxes).

# 3.2 Approach

In this chapter, we propose a generalized decomposition method for s-boxes. More precisely, in our approach any  $n\lambda$ -bit s-box for some integers  $n \geq 1$  and  $\lambda \geq 1$  can be seen as a polynomial (or a vector of  $m \geq 1$  polynomials) over  $\mathbb{F}_{2^{\lambda}}^{n}$ . We first start by defining the multiplicative complexity for s-boxes and some lower bounds. We prove a lower bound of  $\Omega(2^{\lambda n/2}\sqrt{m/\lambda})$  for the complexity of any method to evaluate  $n\lambda$ -bit to  $m\lambda$ -bit s-boxes. We then describe our generalized decomposition method for which we provide concrete parameters to achieve a decomposition for several triplets  $(n, m, \lambda)$  and for exemplary s-boxes of popular block ciphers (namely PRESENT [CHES:BKLPPR07], SC2000 [FSE:SYYTIYTT01], CLEFIA [FSE:SSAMI07] and KHAZAD [NESSIE:BarRij00]).

Depending on the s-box, our generalized method allows one to choose the parameters n, m and  $\lambda$  to obtain the best possible s-box decomposition in terms of multiplications over  $\mathbb{F}_{2^{\lambda}}$ . In particular, for  $8 \times 8$  s-boxes, the CRV decomposition method [CHES:CorRoyViv14] (n=1, m=1,  $\lambda=8$ ) is a special case of this generalized decomposition method. We also investigate a particular case of our decomposition, the Boolean case, where  $n=8, m=8, \lambda=1$ . For this specific instantiation, we can apply a bitslicing strategy for the implementation part and some improvement tailored for the Boolean field.

# 3.3 Multiplicative Complexity of Generic S-boxes

#### 3.3.1 Notations and notions

Let  $\lambda$  be a positive integer. Then  $\mathbb{F}_{2^{\lambda}}$  denotes the finite field with  $2^{\lambda}$  elements. Let  $\mathcal{F}_{\lambda,n}$  be the set of functions from  $\mathbb{F}^n_{2^{\lambda}}$  to  $\mathbb{F}_{2^{\lambda}}$ . Using Lagrange's interpolation theorem, any function  $f \in \mathcal{F}_{\lambda,n}$  can be seen as a multivariate polynomial over  $\mathbb{F}_{2^{\lambda}}[x_1,x_2,\ldots,x_n]/(x_1^{2^{\lambda}}-x_1,x_2^{2^{\lambda}}-x_2,\ldots,x_n^{2^{\lambda}}-x_n)$ :

$$f(x) = \sum_{u \in [0, 2^{\lambda} - 1]^n} a_u x^u , \qquad (3.1)$$

where  $x = (x_1, x_2, \dots, x_n)$ ,  $x^u = x_1^{u_1} \cdot x_2^{u_2} \cdot \dots \cdot x_n^{u_n}$ , and  $a_u \in \mathbb{F}_{2^{\lambda}}$  for every  $u = (u_1, \dots, u_n) \in [0, 2^{\lambda} - 1]^n$ .

The multiplicative complexity of a function in  $\mathcal{F}_{\lambda,n}$  (also called the non-linear complexity) is defined as follows:

**Definition 3.3.1.** Let f be a function in  $\mathcal{F}_{\lambda,n}$ . The multiplicative complexity of f is the minimal number of  $\mathbb{F}_{2^{\lambda}}$ -multiplications required to evaluate it.

In the following, an s-box S is characterized with respect to 3 parameters: the number of input elements n; the number of output elements m; and the bit-size of the elements  $\lambda$ . In other words, an s-box with  $\lambda n$  input bits and  $\lambda m$  outputs bits is represented as follows:

$$\forall x \in \mathbb{F}_{2\lambda}^n, \mathcal{S}(x) = (f_1(x), f_2(x), \dots, f_m(x)), \tag{3.2}$$

where the functions  $f_1, f_2, \ldots, f_m \in \mathcal{F}_{\lambda,n}$  are called the *coordinate functions* of S.

The multiplicative complexity of an s-box  $S: x \mapsto (f_1(x), f_2(x), \dots, f_m(x))$ , denoted C(S), is naturally defined as the multiplicative complexity of the family of its coordinate functions. We shall also call the multiplicative complexity of a given circuit the actual number of multiplication gates involved in the circuit, so that the multiplicative complexity of a circuit gives an upper bound of the multiplicative complexity of the underlying s-box.

#### 3.3.2 Multiplicative Complexity Lower Bound for S-boxes

Roy and Vivek presented in [CHES:RoyViv13] a lower-bound on the length of cyclotomic coset addition chains and used it to derive a logarithmic lower bound on the multiplicative complexity of an s-box (i.e. on the minimal number of such multiplications necessary to evaluate the corresponding polynomial). As mentioned in Chapter ??, Coron *et al.* [CHES:CorRoyViv14] improved this lower bound and showed that the non-linear complexity of any generic method to evaluate n-bit s-boxes when seen as a polynomial defined over  $\mathbb{F}_{2^n}$  is in  $\Omega(2^{n/2}/\sqrt{n})$ .

In the following section, we generalize their approach and provide a new lower bound on the multiplicative complexity of a sequence of n-variate polynomials over  $\mathbb{F}_{2^{\lambda}}$ . Following [CHES:RoyViv13], we define the multiplicative complexity notion for such a sequence as follows:

**Definition 3.3.2** (Polynomial chain). Let  $\lambda \geq 1$ ,  $n \geq 1$ ,  $l \geq 1$  and  $m \geq 1$  be four integers and let  $f_1, \ldots, f_m \in \mathbb{F}_{2^{\lambda}}[x_1, \ldots, x_n]$  be a sequence of n-variate polynomials over  $\mathbb{F}_{2^{\lambda}}$ . A polynomial chain  $\overrightarrow{\pi}$  for  $(f_1, \ldots, f_m)$  is a sequence  $\overrightarrow{\pi} = (\pi_i)_{i \in \{-n, \ldots, \ell\}}$  and a list  $(i_1, \ldots, i_m) \in \{-n, \ldots, \ell\}^m$  with

$$\pi_{-n} = x_n, \ \pi_{1-n} = x_{n-1}, \ \dots, \ \pi_{-1} = x_1, \ \pi_0 = 1,$$

$$\pi_{i_j} = f_j(x_1, \dots, x_n) \bmod (x_1^{2^{\lambda}} + x_1, \dots, x_n^{2^{\lambda}} + x_n), \ \forall j \in \{1, \dots, m\},\$$

and such that for every  $i \in \{1, ..., \ell\}$ , one of the following condition holds:

- 1. there exist j and k in  $\{-n, \ldots, i-1\}$  such that  $\pi_i = \pi_j \cdot \pi_k$ ;

- 2. there exist j and k in  $\{-n, \ldots, i-1\}$  such that  $\pi_i = \pi_j + \pi_k$ ;

- 3. there exists j in  $\{-n, \ldots, i-1\}$  such that  $\pi_i = \pi_i^2$ ;

- 4. there exists j in  $\{-n, \ldots, i-1\}$  and  $\alpha \in \mathbb{F}_{2^{\lambda}}$  such that  $\pi_i = \alpha \cdot \pi_i$ .