## Methodology and Tools for Energy-aware Task Mapping on Heterogeneous Multiprocessor Architectures

Baptiste Roux

## ▶ To cite this version:

Baptiste Roux. Methodology and Tools for Energy-aware Task Mapping on Heterogeneous Multiprocessor Architectures. Embedded Systems. Université de Rennes 1, 2017. English. NNT: . tel-01672814

## HAL Id: tel-01672814 https://inria.hal.science/tel-01672814

Submitted on 27 Dec 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

**ANNÉE 2017**

## THÈSE / UNIVERSITÉ DE RENNES 1

sous le sceau de l'Université Bretagne Loire

pour le grade de

## DOCTEUR DE L'UNIVERSITÉ DE RENNES 1

Mention : Traitement du signal et Télécommunications

Ecole doctorale MathSTIC

présentée par

# Baptiste Roux

préparée à l'unité de recherche IRISA (UMR 6074) Institut de Recherche en Informatique et Systèmes Aléatoires École Nationale Supérieure des Sciences Appliquées et de Technologie

Methodology and Tools

for Energy-aware Task

Mapping on

Heterogeneous

Multiprocessor

Architectures

Thèse soutenue à Rennes le 23 novembre 2017

devant le jury composé de :

Virginie FRESSE MCF - Université Jean Monnet / rapporteur Frédéric ROUSSEAU PR - Université Grenoble Alpes / rapporteur Jean-Philippe DELAHAYE Ingénieur - DGA MI / examinateur Bertrand GRANADO PR - Université Pierre et Marie Curie / examinateur Loic LAGADEC PR - ENSTA Bretagne / examinateur Matthieu GAUTIER MCF - Université Rennes 1 / co-directeur de thèse Olivier SENTIEYS PR - Université Rennes 1 / directeur de thèse

ii

## Résumé

Au cours de la dernière décennie, la conception des systèmes embarqués a évolué dans l'optique d'augmenter la puissance de calcul tout en conservant une faible consommation d'énergie. À titre d'exemple, les véhicules autonomes tels que les drones sont un domaine d'application représentatif qui combine de la vision, des communications sans fil avec d'autres noyaux de calculs intensifs, le tout avec un budget énergétique limité. Avec l'avènement des systèmes multicœurs sur puce (MpSoC), la simplification des processeurs a diminué la consommation d'énergie par opération, alors que leur multiplication a amélioré les performances. Cependant, l'apparition du phénomène de *dark silicon* a conduit à l'intégration d'accélérateurs matériels spécialisés au sein des systèmes multicœurs. C'est ainsi que sont nées les architectures massivement multicœurs hétérogènes (HMp-SoC) combinant des processeurs généralistes (SW) et des accélérateurs matériels (HW). Pour ces architectures hétérogènes, les performances et la consommation d'énergie dépendent d'un large ensemble de paramètres tels que le partitionnement HW/SW, le type d'implémentation HW et le coût de communication entre les organes de calcul HW et SW conduisant ainsi à un immense espace de conception.

Dans cette thèse, nous étudions des méthodes permettant la réduction de la complexité de développement et de mise en œuvre d'applications efficaces en énergie sur HMpSoC. De nombreuses contributions sont proposées pour améliorer les outils d'exploration de l'espace de conception (DSE) avec des objectifs énergétiques. Tout d'abord, une définition formelle de la structure HMpSoC est introduite ainsi qu'une méthode de représentation générique axée sur la hiérarchie mémoire. Ensuite, un outil de modélisation rapide de l'énergie est proposé et validé sur plusieurs applications. Ce modèle énergétique sépare les sources d'énergie en trois catégories (calcul statique, dynamique et communications) et calcule leurs contributions sur la consommation globale de manière indépendante. Basée sur une étude précise des communications, cette approche calcule rapidement la consommation d'énergie pour une répartition donnée d'application sur un HMpSoC. Dans un deuxième temps, nous proposons une méthodologie permettant l'exploration énergétique d'accélérateurs sur HMpSoC. Cette méthode s'appuie sur le modèle de consommation précédent couplé à une formulation de programmation linéaire en nombre entier mixte (MILP). Cela permet de sélectionner efficacement les accélérateurs HW et le partitionnement HW/SW et ainsi d'obtenir une implémentation efficace en énergie pour une application tuilée. Les expériences réalisées ont montré la complexité du processus de validation d'outils/algorithmes de DSE sur une large gamme d'applications et d'architectures. Afin de résoudre ce problème, nous proposons un simulateur d'architectures HMp-SoC intégrant un modèle de consommation permettant d'observer l'exécution d'applications. La structure de l'architecture cible est décrite à l'aide d'un fichier de configuration basé sur le modèle de représentation générique précédent. Ce fichier est chargé dynamiquement lors du démarrage du simulateur. De plus, ce simulateur est associé à un générateur d'applications permettant la création d'un large ensemble d'applications représentatives du domaine. Ce générateur se base sur un ensemble de schémas de calcul et de communication élémentaire qu'il combine pour obtenir une application complète. Les applications ainsi obtenues peuvent être enrichies par des informations de placement et automatiquement exécutées sur le simulateur. Cet ensemble d'outils a pour objectif de faciliter la validation de nouveaux algorithmes ciblant le placement efficace en énergie d'application sur une large gamme d'architectures HMpSoC.

### Abstract

During the last decade, the design of embedded systems was pushed to increase computational power while maintaining low energy consumption. As an example, autonomous vehicles such as drones are a representative application domain which combines vision, wireless communications and other computation intensive kernels constrained with a limited energy budget. With the advent of Multiprocessor System-on-Chip (MpSoC) architectures, simplification of processor cores decreased power consumption per operation, while the multiplication of cores brought performance improvement. However, the *dark silicon* issue led to the benefit of augmenting programmable processors with specialized hardware accelerators and to the rise of Heterogeneous MpSoC (HMpSoC) combining both software (SW) and hardware (HW) computational resources. For these heterogeneous architectures, performance and energy consumption depend on a large set of parameters such as the HW/SW partitioning, the type of HW implementation or the communication cost between HW and SW cores therefore leading to a huge design space.

In this thesis, we study how to reduce the development and implementation complexity of energy-efficient applications on HMpSoC. Multiple contributions are proposed to enhance Design Space Exploration (DSE) tools with energy objectives. First, a formal definition of HMpSoC structure is introduced alongside with a generic representation focused on the memory hierarchy. Then, a fast power modelling tool is proposed and validated on several applications. This power model separates the power sources in three families (static, dynamic computation and dynamic communication) and computes their contributions on global consumption independently. With a fine grain communications study, this approach rapidly computes energy consumption for a given application mapping on a HMpSoC. In a second time, we propose a methodology for energy-driven accelerator exploration on HMpSoC. This method builds upon the previous power model coupled with an Mixed Integer Linear Programming (MILP) formulation and enables to efficiently select HW accelerators and HW/SW partitioning which achieve energy efficient-mapping of a tiled application. The experiments involved in these contributions show the complexity of DSE validation process on a wide range of applications and architectures. To address these issues, we introduce a HMpSoC simulator embedding a power model to monitor application execution. Properties of targeted architectures are described, at run-time with the previous generic representation model. Furthermore, this simulator is coupled with an application generator framework that could build an infinite set of representative applications following predefined computation models. The obtained applications could then be enriched with mapping directive and executed on the simulator. This combination enables to ease the research and validation of new DSE algorithms targeting energy-aware application mapping on a wide range of HMpSoC architectures.

# Contents

| 1.1       Radio logicielle       2         1.2       Tendances architecturales       2         2       Architectures cibles       3         2.1       Architectures cibles       3         2.2       Structure des applications       4         3       Flot de conception & Contributions       5         3.1       Extraction du parallélisme       5         3.2       Creation de l'EPDG       5         3.3       Estimation de l'énergie       6         3.4       Exploration de l'espace de conception       6         3.5       Platforme d'émulation de HMpSoC       8         4       Conclusion       11         1       General context       11         1.1       Software-Defined Radio       12         1.2       DVB-S2: a relevant SDR application example       12         2       Technology progress and architecture trends       14         2.1       Towards the integration of deciated HW accelerators       14         2.1       Towards the integration of deciated HW accelerators       14         2.2       Energy efficiency: the next challenge of embedded systems       15         3       Contributions of the Thesis       15       15      <                                                                      | 0 | Rés  | umé étendu 1                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|---------------------------------------------------------------|

| 1.2       Tendances architecturales       2         2       Architectures et applications cibles       3         2.1       Architectures cibles       3         2.2       Structure des applications       3         3       Flot de conception & Contributions       5         3.1       Extraction du parallélisme       5         3.2       Creation de l'EPDG       5         3.3       Estimation de l'énergie       6         3.4       Exploration de l'espace de conception       6         3.5       Platforme d'émulation de HMpSoC       8         4       Conclusion       11         1       General context       11         1.1       Software-Defined Radio       12         1.2       DVB-S2: a relevant SDR application example       12         2       Technology progress and architecture trends       14         2.1       Towards the integration of dedicated HW accelerators       14         2.2       Technology progress and architecture trends       15         3       Contributions of the Thesis       15         4       Organization of the document       16         2       Technology progress architectures       19         1                                                                                  |   | 1    | Contexte général                                              |

| 2       Architectures et applications cibles       3         2.1       Architectures cibles       3         2.2       Structure des applications       4         3       Flot de conception & Contributions       5         3.1       Extraction du parallélisme       5         3.2       Creation de l'EPDG       5         3.3       Estimation de l'énergie       6         3.4       Exploration de l'espace de conception       6         3.5       Platforme d'émulation de HMpSoC       8         4       Conclusion       8         1       Introduction       11         1.1       Software-Defined Radio       12         1.2       DVB-S2: a relevant SDR application example       12         2.1       Towards the integration of dedicated HW accelerators       14         2.1       Towards the integration of dedicated HW accelerators       14         2.2       Energy efficiency: the next challenge of embedded systems       15         3       Contributions of the Thesis       15         4       Organization of the document       16         2       Heterogeneous Architectures       20         1.1       Dedicated SDR architectures       20                                                                          |   |      | 1.1         Radio logicielle         2                        |

| 2.1       Architectures cibles       3         2.2       Structure des applications       4         3       Flot de conception & Contributions       5         3.1       Extraction du parallélisme       5         3.2       Creation de l'EPDG       5         3.3       Estimation de l'énergie       6         3.4       Exploration de l'espace de conception       6         3.5       Platforme d'émulation de HMpSoC       8         4       Conclusion       8         1       Introduction       11         1       General context       11         1.1       Software-Defined Radio       12         1.2       DVB-S2: a relevant SDR application example       12         2       Technology progress and architecture trends       14         2.1       Towards the integration of dedicated HW accelerators       14         2.2       Energy efficiency: the next challenge of embedded systems       15         3       Contributions of the Thesis       15         4       Organization of the document       16         2       Heterogeneous Architectures: Structures and Applications       19         1.1       Dedicated SDR architectures       20                                                                            |   |      | 1.2 Tendances architecturales                                 |

| 2.2       Structure des applications       4         3       Flot de conception & Contributions       5         3.1       Extraction du parallélisme       5         3.2       Creation de l'EPDG       5         3.3       Estimation de l'énergie       6         3.4       Exploration de l'espace de conception       6         3.5       Platforme d'émulation de HMpSoC       8         4       Conclusion       8         1       Introduction       11         1.1       General context       11         1.1       Software-Defined Radio       12         1.2       DVB-S2: a relevant SDR application example       12         2.1       Technology progress and architecture trends       14         2.1       Towards the integration of dedicated HW accelerators       14         2.2       Energy efficiency: the next challenge of embedded systems       15         3       Contributions of the Thesis       15         4       Organization of the document       16         2       Heterogeneous Architectures: Structures and Applications       19         1.1       Dedicated SDR architectures       20         1.2       Generic HMpSoC representation       25                                                              |   | 2    | Architectures et applications cibles                          |

| 3       Flot de conception & Contributions       5         3.1       Extraction du parallélisme       5         3.2       Creation de l'EPDG       5         3.3       Estimation de l'engie       6         3.4       Exploration de l'espace de conception       6         3.5       Platforme d'émulation de HMpSoC       8         4       Conclusion       8         1       Introduction       11         1.1       Software-Defined Radio       12         1.2       DVB-S2: a relevant SDR application example       12         1.2       DVB-S2: a relevant SDR application example       14         2.1       Towards the integration of dedicated HW accelerators       14         2.1       Towards the integration of dedicated HW accelerators       14         2.2       Energy efficiency: the next challenge of embedded systems       15         3       Contributions of the Thesis       15         4       Organization of the document       16         2       Heterogeneous Architectures: Structures and Applications       19         1.1       Dedicated SDR architectures       20         1.2       Generic HMpSoC representation       25         2.1       Generic HMpSoC architect                                      |   |      |                                                               |

| 3       Flot de conception & Contributions       5         3.1       Extraction du parallélisme       5         3.2       Creation de l'EPDG       5         3.3       Estimation de l'énergie       6         3.4       Exploration de l'espace de conception       6         3.5       Platforme d'émulation de HMpSoC       8         4       Conclusion       8         1       Introduction       11         1.1       Software-Defined Radio       12         1.2       DVB-S2: a relevant SDR application example       12         1.2       DVB-S2: a relevant SDR application example       14         2.1       Towards the integration of dedicated HW accelerators       14         2.1       Towards the integration of dedicated HW accelerators       14         2.2       Energy efficiency: the next challenge of embedded systems       15         3       Contributions of the Thesis       15         4       Organization of the document       16         2       Heterogeneous Architectures: Structures and Applications       19         1.1       Dedicated SDR architectures       20         1.2       Generic HMpSoC carchitectures       21         2.1       Generic HMpSoC archite                                      |   |      | 2.2 Structure des applications                                |

| 3.1       Extraction du parallélisme       5         3.2       Creation de l'EPDG       5         3.3       Estimation de l'énergie       6         3.4       Exploration de l'espace de conception       6         3.5       Platforme d'émulation de HMpSoC       8         4       Conclusion       8         1       Introduction       11         1.1       Software-Defined Radio       12         1.2       DVB-S2: a relevant SDR application example       12         2.1       DVB-S2: a relevant SDR application example       12         2.2       Technology progress and architecture trends       14         2.1       Towards the integration of dedicated HW accelerators       14         2.2       Energy efficiency: the next challenge of embedded systems       15         3       Contributions of the Thesis       15         4       Organization of the document       16         2       Heterogeneous Architectures: Structures and Applications       19         1       Survey on MpSoC architectures       20         1.2       Generic HMpSoC representation       25         2.1       Generic HMpSoC architecture       25         2.2       Oriented tree for memory hierarchie                                      |   | 3    |                                                               |

| 3.2       Creation de l'ÉPDG       5         3.3       Estimation de l'énergie       6         3.4       Exploration de l'espace de conception       6         3.4       Exploration de l'énergie       6         3.4       Exploration de l'énergie       6         3.5       Platforme d'émulation de HMpSoC       8         4       Conclusion       8         1       Introduction       11         1.1       General context       11         1.2       DVB-S2: a relevant SDR application example       12         2.2       Technology progress and architecture trends       14         2.1       Towards the integration of dedicated HW accelerators       14         2.2       Energy efficiency: the next challenge of embedded systems       15         3       Contributions of the Thesis       15         4       Organization of the document       16         2       Heterogeneous Architectures: Structures and Applications       19         1       Survey on MpSoC architectures       20         1.2       General Purpose architectures       20         1.2       General Purpose architectures       21         2.4       Generic HMpSoC representation       25 <th></th> <th></th> <th>3.1 Extraction du parallélisme</th> |   |      | 3.1 Extraction du parallélisme                                |

| 3.3       Estimation de l'énergie       6         3.4       Exploration de l'espace de conception       6         3.5       Platforme d'émulation de HMpSoC       8         4       Conclusion       8         1       Introduction       11         1       General context       11         1.1       Software-Defined Radio       12         1.2       DVB-S2: a relevant SDR application example       12         2.7       Technology progress and architecture trends       14         2.1       Towards the integration of dedicated HW accelerators       14         2.2       Energy efficiency: the next challenge of embedded systems       15         3       Contributions of the Thesis       15         4       Organization of the document       16         2       Heterogeneous Architectures: Structures and Applications       19         1       Dedicated SDR architectures       20         1.2       Generic HMpSoC representation       25         2.1       Generic HMpSoC representation       27         3.2       Oriented tree for memory hierarchies       26         3       Application structure and representation       27         3.1       Parallelism-Level <td< th=""><th></th><th></th><th>•</th></td<>       |   |      | •                                                             |

| 3.4       Exploration de l'espace de conception       6         3.5       Platforme d'émulation de HMpSoC       8         4       Conclusion       8         1       Introduction       11         1       General context       11         1.1       Software-Defined Radio       12         1.2       DVB-S2: a relevant SDR application example       12         2       Technology progress and architecture trends       14         2.1       Towards the integration of dedicated HW accelerators       14         2.2       Energy efficiency: the next challenge of embedded systems       15         3       Contributions of the Thesis       15         4       Organization of the document       16         2       Heterogeneous Architectures: Structures and Applications       19         1       Dedicated SDR architectures       19         1.1       Dedicated SDR architectures       20         1.2       Generic HMpSoC architectures       21         2.4       Generic HMpSoC architectures       25         2.1       Generic HMpSoC architecture       25         2.2       Oriented tree for memory hierarchies       26         3       Application structure and representation <th></th> <th></th> <th></th>            |   |      |                                                               |

| 3.5       Platforme d'émulation de HMpSoC       8         4       Conclusion       8         1       Introduction       11         1       General context       11         1.1       Software-Defined Radio       12         1.2       DVB-S2: a relevant SDR application example       12         2       Technology progress and architecture trends       14         2.1       Towards the integration of dedicated HW accelerators       14         2.2       Energy efficiency: the next challenge of embedded systems       15         3       Contributions of the Thesis       15         4       Organization of the document       16         2       Heterogeneous Architectures: Structures and Applications       19         1       Survey on MpSoC architectures       20         1.2       Generic HMpSoC representation       25         2.1       Generic HMpSoC architectures       20         1.2       Generic HMpSoC representation       25         2.1       Generic HMpSoC representation       26         3       Application structure and representation       27         3.1       Parallelism-Level       27         3.2       Data Flow programming models       30                                                     |   |      |                                                               |

| 4       Conclusion       8         1       Introduction       11         1       General context       11         1.1       Software-Defined Radio       12         1.2       DVB-S2: a relevant SDR application example       12         2       Technology progress and architecture trends       14         2.1       Towards the integration of dedicated HW accelerators       14         2.2       Energy efficiency: the next challenge of embedded systems       15         3       Contributions of the Thesis       15         4       Organization of the document       16         2       Heterogeneous Architectures: Structures and Applications       19         1       Dedicated SDR architectures       19         1.1       Dedicated SDR architectures       20         1.2       Generic HMpSoC architectures       21         2       Generic HMpSoC architectures       21         2       Generic HMpSoC architecture       25         2.1       Generic HMpSoC architecture       25         2.2       Oriented tree for memory hierarchies       26         3       Application structure and representation       27         3.1       Parallelism-Level       27 </th <th></th> <th></th> <th></th>                        |   |      |                                                               |

| 1Introduction111General context111.1Software-Defined Radio121.2DVB-S2: a relevant SDR application example122Technology progress and architecture trends142.1Towards the integration of dedicated HW accelerators142.2Energy efficiency: the next challenge of embedded systems153Contributions of the Thesis154Organization of the document162Heterogeneous Architectures: Structures and Applications191Survey on MpSoC architectures191.1Dedicated SDR architectures201.2Generic HMpSoC architectures212Generic HMpSoC architectures252.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models303.4Mixed programming models303.4Mixed programming models303.4Mixed programming models303Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                            |   | 4    | -                                                             |

| 1General context111.1Software-Defined Radio121.2DVB-S2: a relevant SDR application example122Technology progress and architecture trends142.1Towards the integration of dedicated HW accelerators142.2Energy efficiency: the next challenge of embedded systems153Contributions of the Thesis154Organization of the document162Heterogeneous Architectures: Structures and Applications191Dedicated SDR architectures191.1Dedicated SDR architectures201.2Generic HMpSoC representation252.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models303.4Mixed programming models303.5Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                     |   |      |                                                               |

| 1.1Software-Defined Radio121.2DVB-S2: a relevant SDR application example122Technology progress and architecture trends142.1Towards the integration of dedicated HW accelerators142.2Energy efficiency: the next challenge of embedded systems153Contributions of the Thesis154Organization of the document162Heterogeneous Architectures: Structures and Applications191Survey on MpSoC architectures201.2Generic HMpSoC representation252.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models303.4Mixed programming models303.4Mixed programming models303.4Mixed programming models303.4Mixed programming models303.4Mixed programming models303.4Mixed programming models303Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                                    | 1 | Intr | oduction 11                                                   |

| 1.2DVB-S2: a relevant SDR application example122Technology progress and architecture trends142.1Towards the integration of dedicated HW accelerators142.2Energy efficiency: the next challenge of embedded systems153Contributions of the Thesis154Organization of the document162Heterogeneous Architectures: Structures and Applications191Survey on MpSoC architectures191.1Dedicated SDR architectures201.2Generic HMpSoC representation252.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models303.4Mixed programming models303.4Mixed programming models303.4Mixed programming models303.4Mixed programming models303.4Mixed programming models303.4Mixed programming models303Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                               |   | 1    | General context                                               |

| 2       Technology progress and architecture trends       14         2.1       Towards the integration of dedicated HW accelerators       14         2.2       Energy efficiency: the next challenge of embedded systems       15         3       Contributions of the Thesis       15         4       Organization of the document       16         2       Heterogeneous Architectures: Structures and Applications       19         1       Survey on MpSoC architectures       19         1.1       Dedicated SDR architectures       20         1.2       General Purpose architectures       21         2       Generic HMpSoC representation       25         2.1       Generic HMpSoC architecture       25         2.2       Oriented tree for memory hierarchies       26         3       Application structure and representation       27         3.1       Parallelism-Level       27         3.2       Data Flow programming models       30         3.4       Mixed programming models       30         3.4       Mixed programming models       30         3.4       Generic application structure       32         3       Power Modelling and Computer-Aided Design Tools       35                                                    |   |      | 1.1Software-Defined Radio12                                   |

| 2.1Towards the integration of dedicated HW accelerators142.2Energy efficiency: the next challenge of embedded systems153Contributions of the Thesis154Organization of the document162Heterogeneous Architectures: Structures and Applications191Survey on MpSoC architectures191.1Dedicated SDR architectures201.2General Purpose architectures212Generic HMpSoC representation252.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models303.4Mixed programming models303.4Mixed programming models303Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      | 1.2 DVB-S2: a relevant SDR application example                |

| 2.2Energy efficiency: the next challenge of embedded systems153Contributions of the Thesis154Organization of the document162Heterogeneous Architectures: Structures and Applications191Survey on MpSoC architectures191.1Dedicated SDR architectures201.2General Purpose architectures212Generic HMpSoC representation252.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models303.4Mixed programming models303.4Mixed programming models303Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 2    | Technology progress and architecture trends                   |

| 3Contributions of the Thesis154Organization of the document162Heterogeneous Architectures: Structures and Applications191Survey on MpSoC architectures191.1Dedicated SDR architectures201.2General Purpose architectures212Generic HMpSoC representation252.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models283.3Control Flow programming models303.4Mixed programming models304Generic application structure323Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      | 2.1 Towards the integration of dedicated HW accelerators      |

| 4Organization of the document162Heterogeneous Architectures: Structures and Applications191Survey on MpSoC architectures191.1Dedicated SDR architectures201.2General Purpose architectures212Generic HMpSoC representation252.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models283.3Control Flow programming models303.4Mixed programming models304Generic application structure323Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      | 2.2 Energy efficiency: the next challenge of embedded systems |

| 2Heterogeneous Architectures: Structures and Applications191Survey on MpSoC architectures191.1Dedicated SDR architectures201.2General Purpose architectures212Generic HMpSoC representation252.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models283.3Control Flow programming models303.4Mixed programming models304Generic application structure323Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 3    | Contributions of the Thesis                                   |

| 1Survey on MpSoC architectures191.1Dedicated SDR architectures201.2General Purpose architectures212Generic HMpSoC representation252.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models283.3Control Flow programming models303.4Mixed programming models303Generic application structure323Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 4    | Organization of the document 16                               |

| 1Survey on MpSoC architectures191.1Dedicated SDR architectures201.2General Purpose architectures212Generic HMpSoC representation252.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models283.3Control Flow programming models303.4Mixed programming models303Generic application structure323Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2 | Het  | erogeneous Architectures: Structures and Applications 19      |

| 1.2General Purpose architectures212Generic HMpSoC representation252.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models283.3Control Flow programming models303.4Mixed programming models304Generic application structure323Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      |                                                               |

| 2Generic HMpSoC representation252.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models283.3Control Flow programming models303.4Mixed programming models304Generic application structure323Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      | 1.1 Dedicated SDR architectures                               |

| 2.1Generic HMpSoC architecture252.2Oriented tree for memory hierarchies263Application structure and representation273.1Parallelism-Level273.2Data Flow programming models283.3Control Flow programming models303.4Mixed programming models304Generic application structure323Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      | 1.2 General Purpose architectures                             |

| 2.2       Oriented tree for memory hierarchies       26         3       Application structure and representation       27         3.1       Parallelism-Level       27         3.2       Data Flow programming models       28         3.3       Control Flow programming models       30         3.4       Mixed programming models       30         4       Generic application structure       32         3       Power Modelling and Computer-Aided Design Tools       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 2    | Generic HMpSoC representation                                 |

| 2.2       Oriented tree for memory hierarchies       26         3       Application structure and representation       27         3.1       Parallelism-Level       27         3.2       Data Flow programming models       28         3.3       Control Flow programming models       30         3.4       Mixed programming models       30         4       Generic application structure       32         3       Power Modelling and Computer-Aided Design Tools       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      | 2.1 Generic HMpSoC architecture                               |

| 3       Application structure and representation       27         3.1       Parallelism-Level       27         3.2       Data Flow programming models       28         3.3       Control Flow programming models       30         3.4       Mixed programming models       30         4       Generic application structure       32         3       Power Modelling and Computer-Aided Design Tools       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      |                                                               |

| 3.2       Data Flow programming models       28         3.3       Control Flow programming models       30         3.4       Mixed programming models       30         4       Generic application structure       32         3       Power Modelling and Computer-Aided Design Tools       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 3    | Application structure and representation                      |

| 3.2       Data Flow programming models       28         3.3       Control Flow programming models       30         3.4       Mixed programming models       30         4       Generic application structure       32         3       Power Modelling and Computer-Aided Design Tools       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      | 3.1 Parallelism-Level                                         |

| 3.3       Control Flow programming models       30         3.4       Mixed programming models       30         4       Generic application structure       32         3       Power Modelling and Computer-Aided Design Tools       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |      |                                                               |

| 3.4Mixed programming models304Generic application structure323Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      |                                                               |

| 4Generic application structure323Power Modelling and Computer-Aided Design Tools35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 4    |                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3 | Pow  | ver Modelling and Computer-Aided Design Tools 35              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      |                                                               |

|   |      | 1.1      | Low-level estimation techniques                  |

|---|------|----------|--------------------------------------------------|

|   |      |          | 1.1-1 Circuit/Transistor level                   |

|   |      |          | 1.1-2 Logic/Gate level                           |

|   |      |          | 1.1-3 Register Transfer level                    |

|   |      | 1.2      | High-level estimation techniques    37           |

|   |      |          | 1.2-1 Architectural-level                        |

|   |      |          | 1.2-2 Functional-level                           |

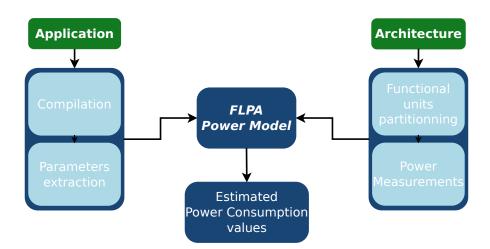

|   | 2    | Comp     | uter Aided Design tools                          |

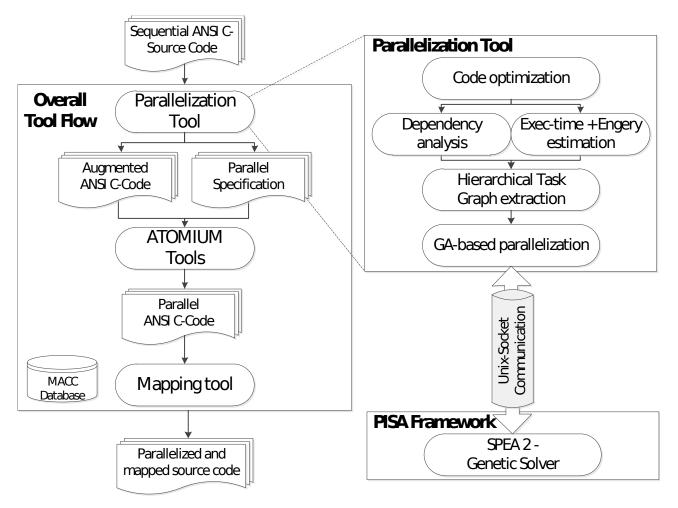

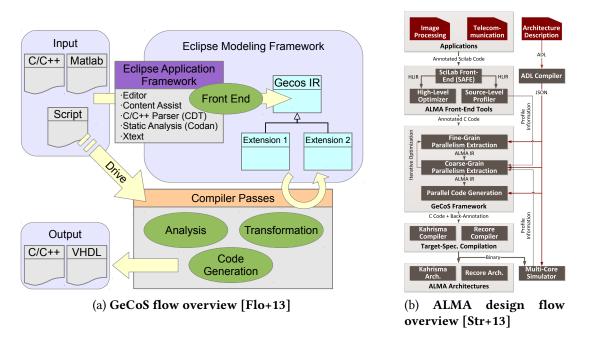

|   |      | 2.1      | Parallelism-extraction                           |

|   |      |          | 2.1-1 Algorithms                                 |

|   |      |          | 2.1-2 Frameworks and Tools                       |

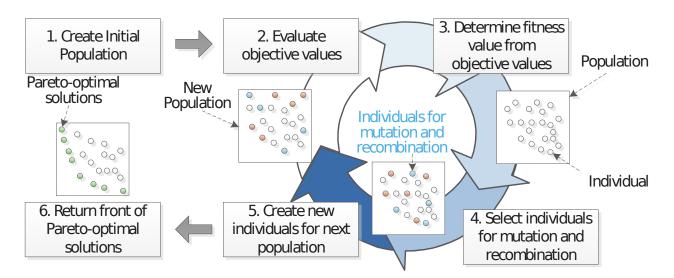

|   |      | 2.2      | HMpSoC Design Space exploration                  |

|   |      |          | 2.2-1 Simulation-based DSE                       |

|   |      |          | 2.2-2 Analytical-based DSE                       |

|   |      |          | 2.2-3 Hardware focused DSE                       |

|   |      |          |                                                  |

| 4 | Fast | Power    | · Modeling for HMpSoC 55                         |

|   | 1    | Comn     | unication-Based Power Model                      |

|   |      | 1.1      | Computation energy cost                          |

|   |      | 1.2      | Communication energy cost                        |

|   |      | 1.3      | Static energy cost                               |

|   | 2    | Deep-    | dive on two Architectures                        |

|   |      | 2.1      | Micro-benchmark principle                        |

|   |      |          | 2.1-1 General structure of a micro-benchmark set |

|   |      | 2.2      | Kalray MPPA                                      |

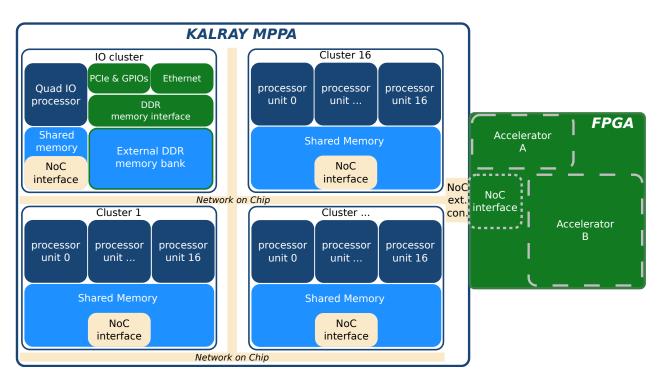

|   |      |          | 2.2-1 MPPA structure                             |

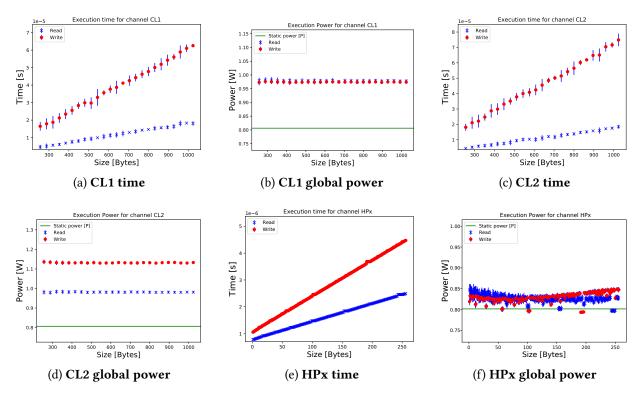

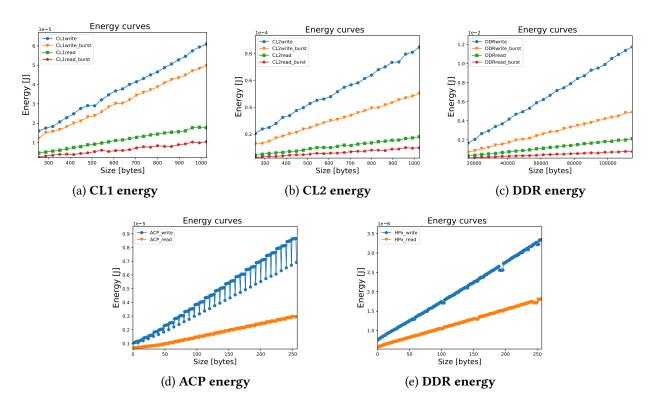

|   |      |          | 2.2-2 Power analysis                             |

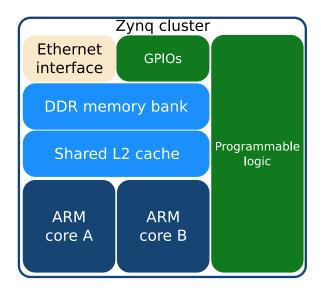

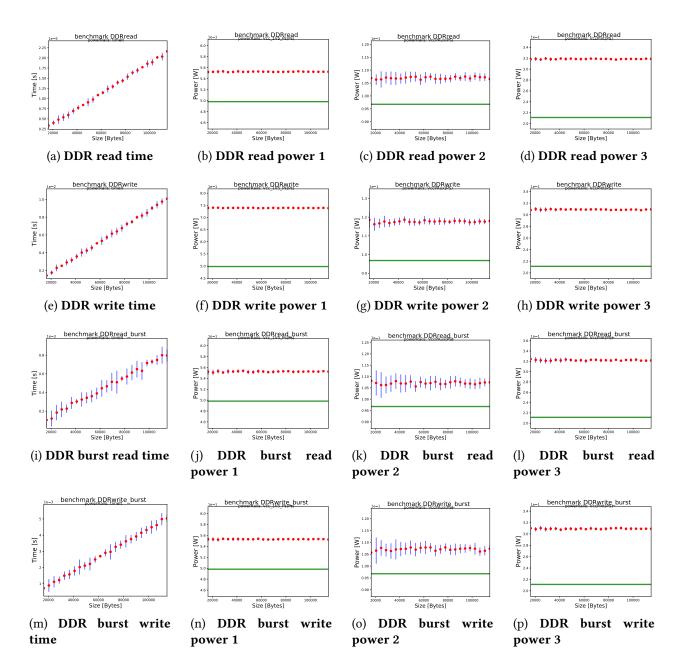

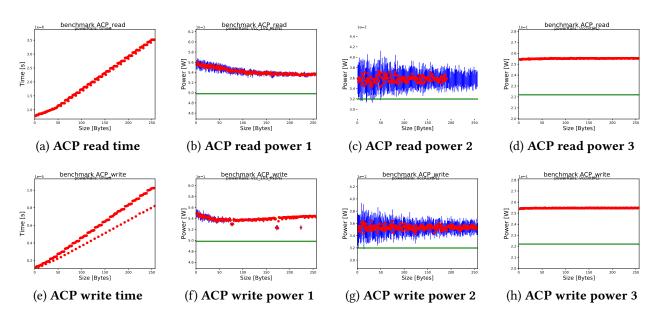

|   |      | 2.3      | Xilinx Zynq                                      |

|   |      |          | 2.3-1 Zynq structure                             |

|   |      |          | 2.3-2 Power analysis                             |

|   | 3    | Power    | model validation on Xilinx zynq                  |

|   |      | 3.1      | The mutant application principle                 |

|   |      | 3.2      | Mutant validation                                |

|   | 4    | Concl    | usion                                            |

|   |      |          |                                                  |

| 5 | Ene  | <b>.</b> | iven Accelerator Exploration for HMpSoC 79       |

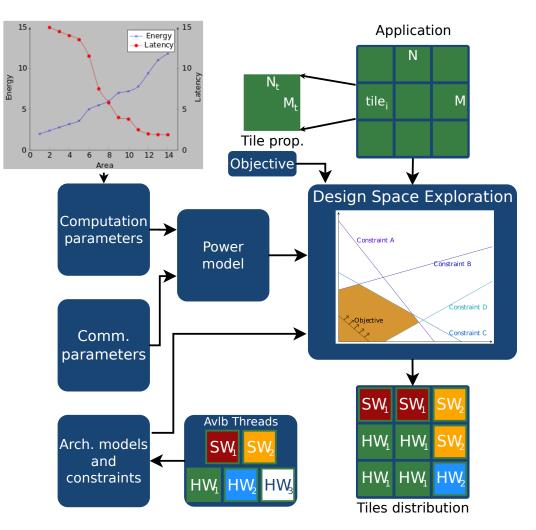

|   | 1    | Overv    | iew of Proposed Tiled-DSE Flow                   |

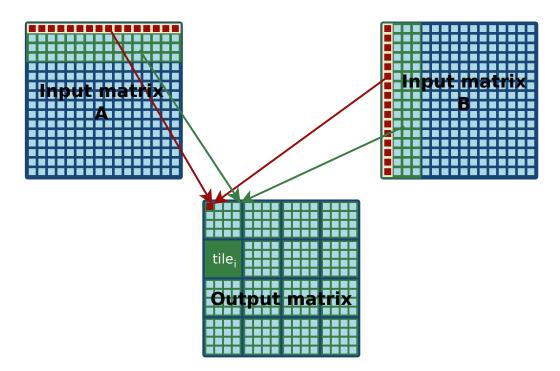

|   |      | 1.1      | Tiling-based parallel applications    80         |

|   |      | 1.2      | Heterogeneous Architectures    82                |

|   |      | 1.3      | Tiled-DSE Objectives    82                       |

|   |      | 1.4      | Energy and execution time models83               |

|   |      |          | 1.4-1         Computation time         83        |

|   |      |          | 1.4-2         Energy consumption         83      |

|   | 2    |          | utation Parameter Extraction                     |

|   | 3    | Design   | n Space Exploration of Tiled Applications        |

|   |      | 3.1      | Exhaustive search                                |

|   |      | 3.2      | MILP formulation                                 |

|   |      |          | 3.2-1 Model constraints                          |

|   |      |          | 3.2-2 Cost functions                             |

|   |      |          | 3.2-3 Objective functions                        |

|   | 4   | Experin  | mental Setup                                         |       |

|---|-----|----------|------------------------------------------------------|-------|

|   |     | 4.1      | Application kernels                                  |       |

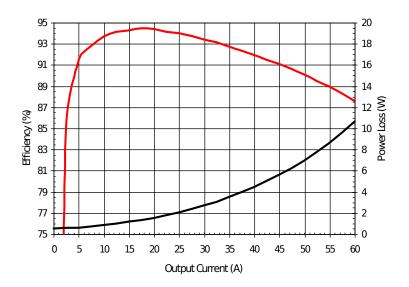

|   |     | 4.2      | Measurement infrastructure                           | . 89  |

|   |     | 4.3      | Hardware implementations                             | . 89  |

|   |     | 4.4      | Software implementations                             | . 92  |

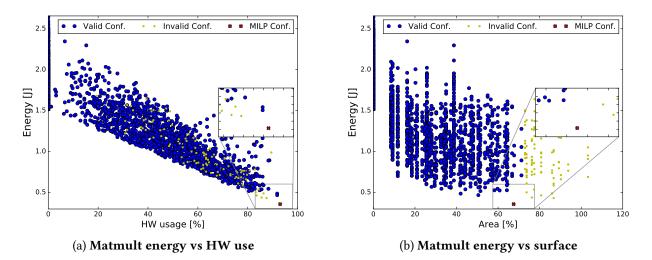

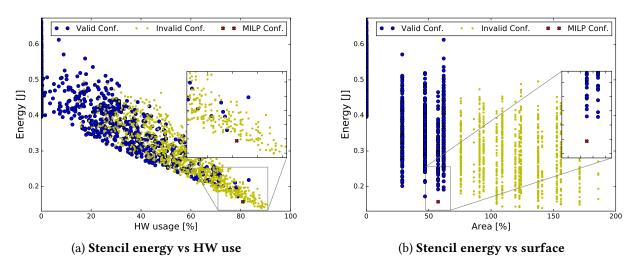

|   | 5   | Explora  | ation Results                                        | . 92  |

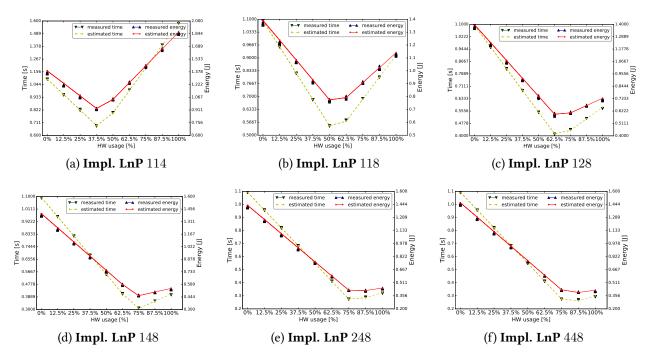

|   |     | 5.1      | Parameter extraction                                 | . 93  |

|   |     | 5.2      | MILP optimization                                    | . 93  |

|   |     | 5.3      | Precision and gain factors                           | . 94  |

|   | 6   | Conclu   | ision                                                | . 95  |

| 6 | HM  | pSoC Ei  | mulation Platform                                    | 97    |

|   | 1   | Motiva   | ations                                               | . 97  |

|   | 2   | Archite  | ecture emulation layer                               | . 98  |

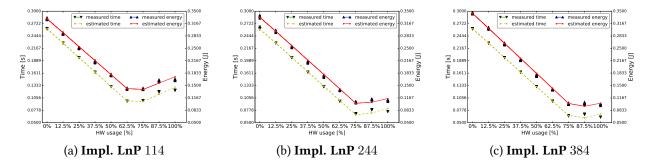

|   |     | 2.1      | Underlying technologies                              | . 98  |

|   |     |          | 2.1-1 QEMU                                           | . 98  |

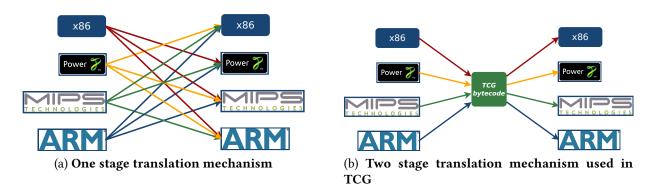

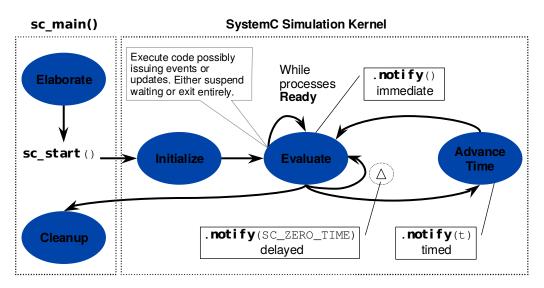

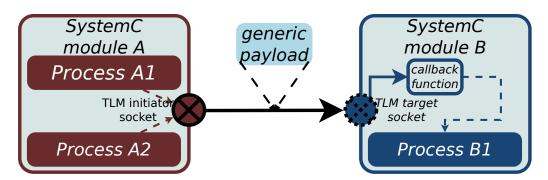

|   |     |          | 2.1-2 SystemC                                        | . 100 |

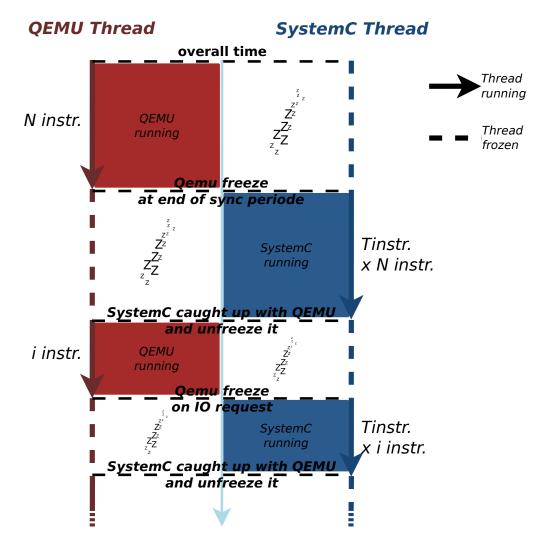

|   |     |          | 2.1-3 SystemC and QEMU association                   | . 102 |

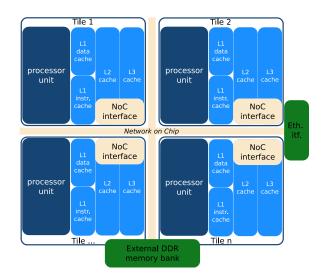

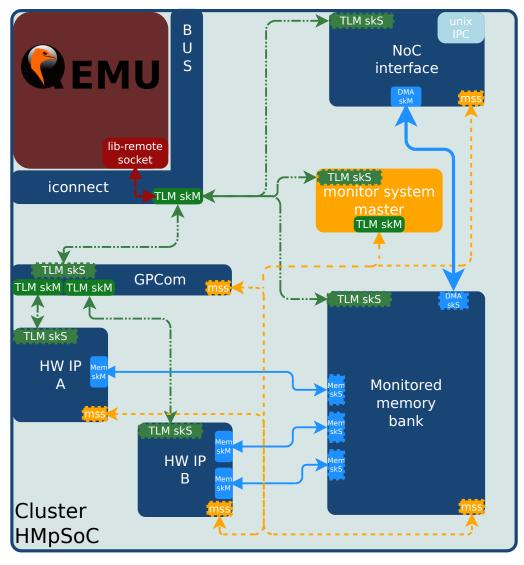

|   |     | 2.2      | Emulator structure                                   | . 104 |

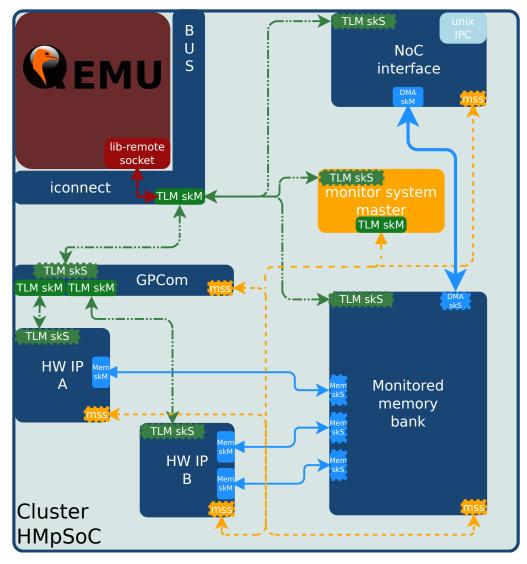

|   |     |          | 2.2-1 Cluster structure                              | . 104 |

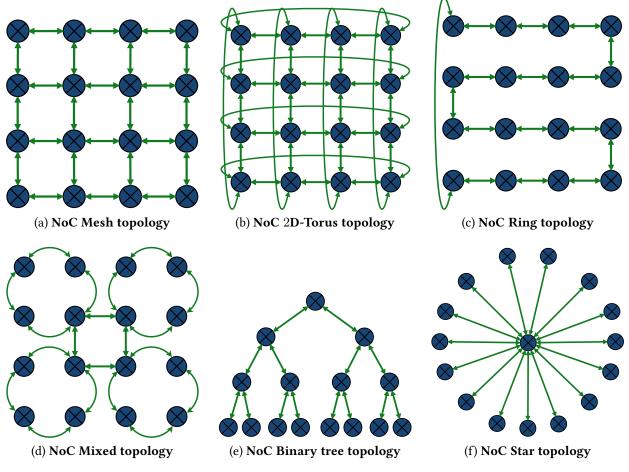

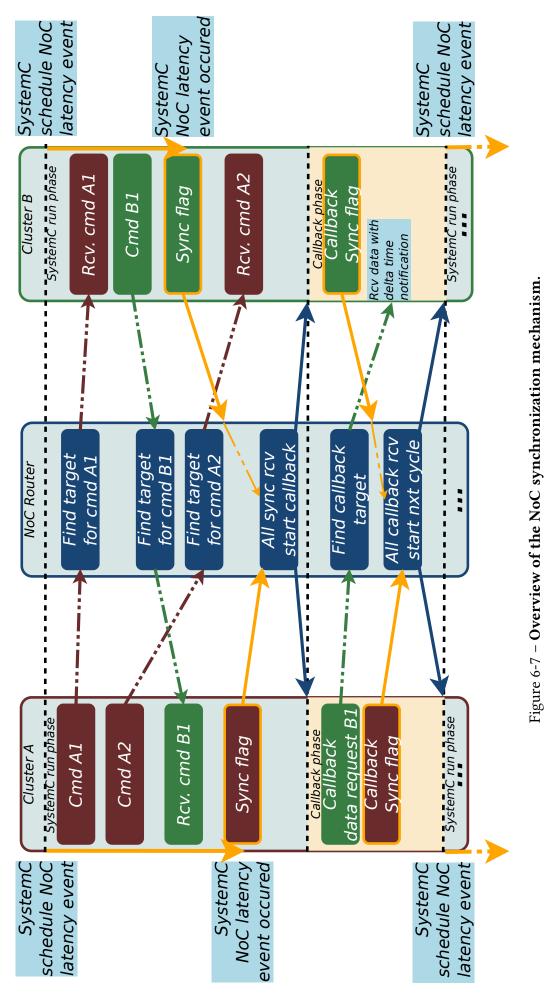

|   |     |          | 2.2-2 NoC structure                                  | . 105 |

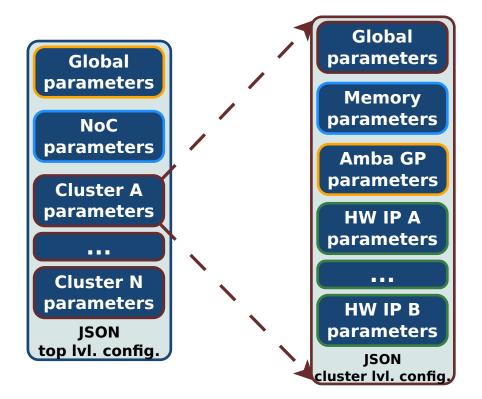

|   |     |          | 2.2-3 Configuration facilities                       | . 108 |

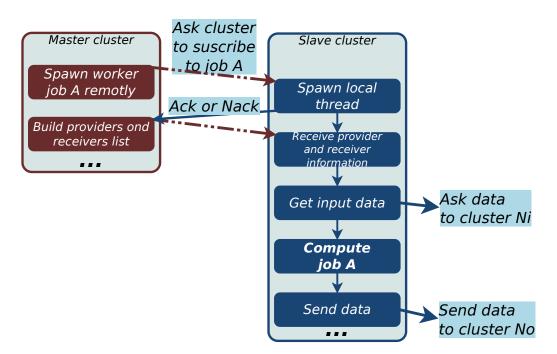

|   |     | 2.3      | Execution framework and cluster management           | . 108 |

|   |     |          | 2.3-1 Communication monitoring                       | . 108 |

|   |     |          | 2.3-2 NoC management                                 | . 110 |

|   |     |          | 2.3-3 Execution scheme                               | . 110 |

|   | 3   | Applica  | ation layer                                          | . 111 |

|   |     | 3.1      | Representative applications: the dwarf principle     | . 111 |

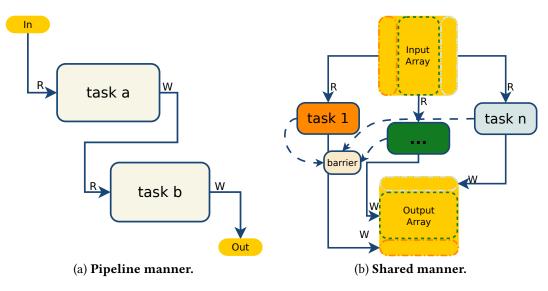

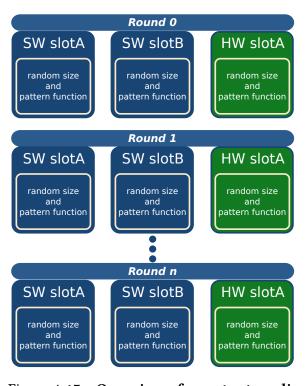

|   |     | 3.2      | Dwarfs implementation within the execution structure |       |

|   |     |          | 3.2-1 Wrapper structure and communication scheme     |       |

|   |     |          | 3.2-2 SW implementations                             | . 114 |

|   |     |          | 3.2-3 HW implementations                             |       |

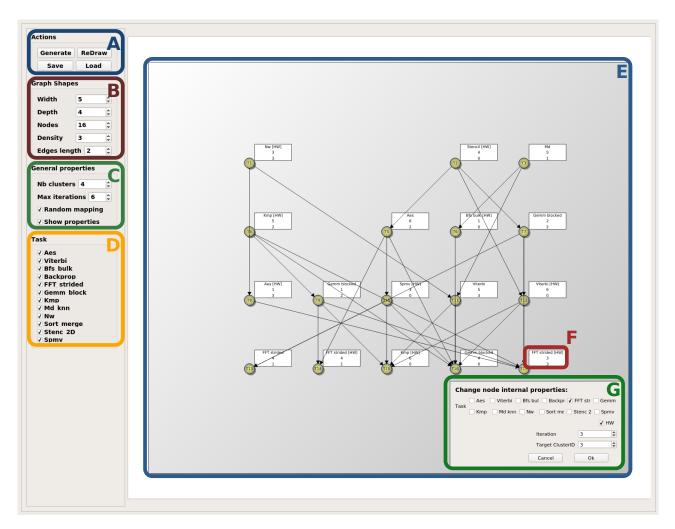

|   |     | 3.3      | Generic graph generation                             |       |

|   |     |          | 3.3-1 Generator structure                            |       |

|   |     |          | 3.3-2 Graph execution and monitoring facilities      |       |

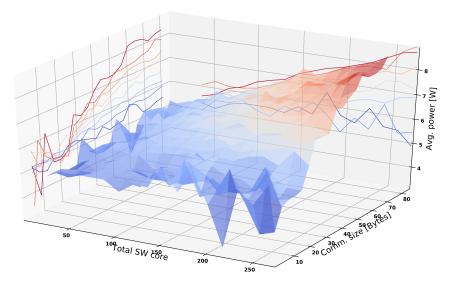

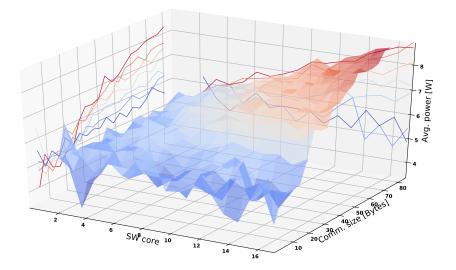

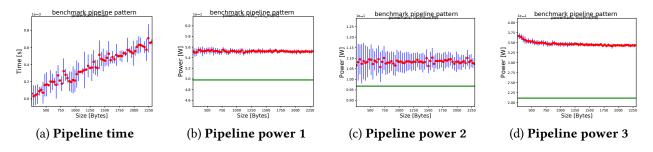

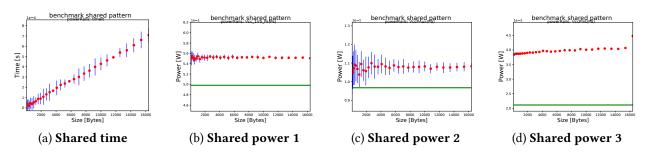

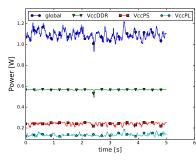

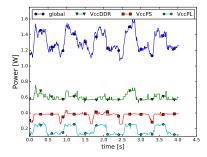

|   |     | 3.4      | Communication energy monitoring results              |       |

|   | 4   |          | ision                                                |       |

| 7 | Con | clusion  | 1 & Perspectives                                     | 119   |

|   | 1   | Conclu   |                                                      | . 119 |

|   | 2   | Perspec  | ctives                                               | . 121 |

| Ι | Δn  | pendio   |                                                      | 123   |

|   |     | -        |                                                      |       |

| A | Man | ual loo  | op-nest modification                                 | 125   |

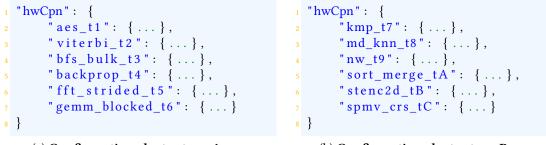

| B | HM  | pSoC co  | onfiguration file                                    | 127   |

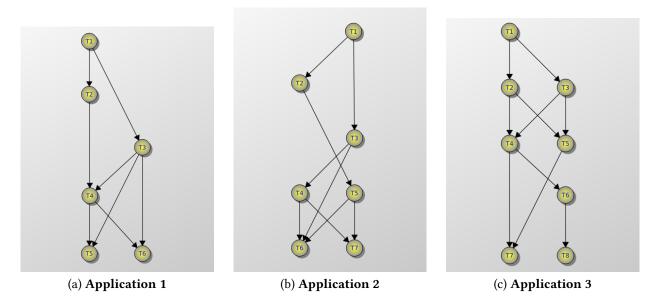

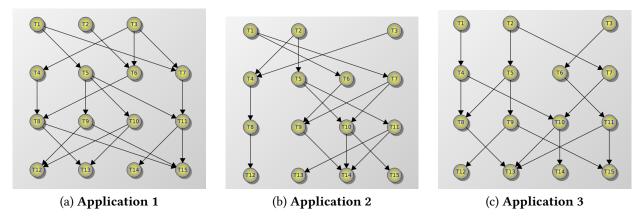

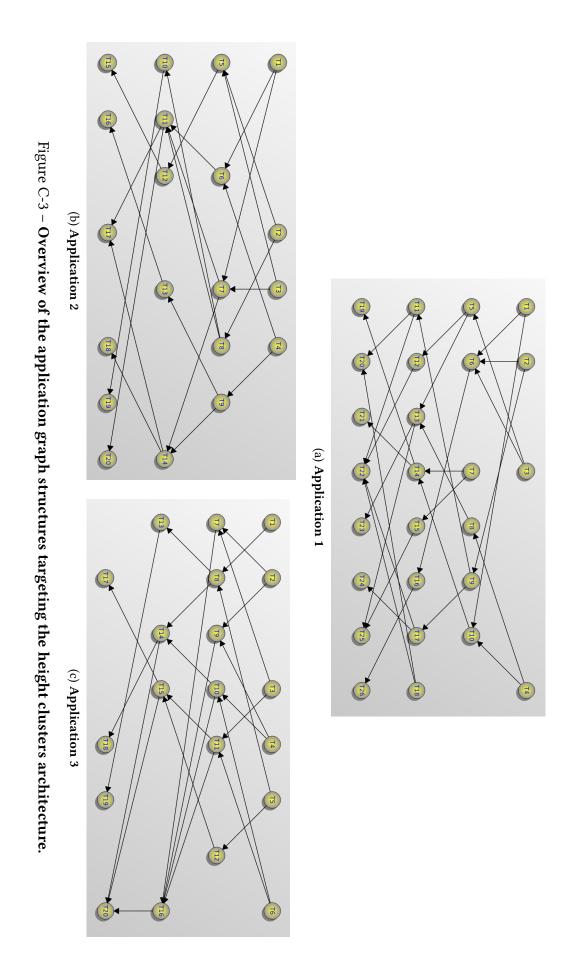

| С | Gen | erated a | applications graph                                   | 131   |

| Publications    | 133 |

|-----------------|-----|

| Bibliography    | 135 |

| List of Figures | 144 |

| List of Tables  | 145 |

| Acronymes       | 148 |

## Chapitre **ZÉRO**

# **RÉSUMÉ ÉTENDU**

## 1 Contexte général

Les systèmes embarqués ont par définition des ressources énergétiques limitées. Un des verrous à l'augmentation des débits des objets communicants et embarqués est de pouvoir réaliser un nombre important de traitements sous cette contrainte d'énergie finie ou de puissance dissipée maximale. La mise en œuvre de la liaison de données entre les drones et une station de base terrestre est une application qui entre dans ce contexte. En effet, la gestion de l'énergie est un verrou limitant la durée des missions de ces drones. Ainsi, réduire la consommation des traitements numériques embarqués est un challenge important.

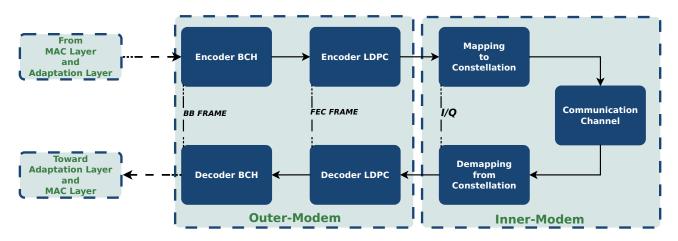

Cette thèse a été cofinancée par l'Institut National de Recherche en Informatique et en Automatique (INRIA) et la Direction Générale de l'Armement (DGA). Cette étude est née de besoins inhérents aux applications embarquées dans les drones de la DGA. Ces derniers utilisent un lien radio basé sur le standard DVB-S2 avec une architecture matérielle standard basée sur l'association d'un FPGA, d'un DSP et d'un processeur généraliste. L'utilisation de ces trois composants distincts complexifie le processus de reconfiguration et diminue les performances énergétiques globales. Cette thèse a pour but d'explorer les opportunités offertes par les nouvelles architectures hétérogènes associant processeurs généralistes et accélérateurs matériels avec le paradigme de communications reconfigurables basé sur la radio logicielle. L'objectif premier est de mettre en avant les forces et les faiblesses de ces architectures et de soulever les difficultés liées à la conception d'applications efficaces en énergie sur ces architectures hétérogènes. À long terme, nous voulons proposer une formalisation de ces architectures ainsi que des outils et des méthodes facilitant le développement d'applications économes en énergie sur ces architectures.

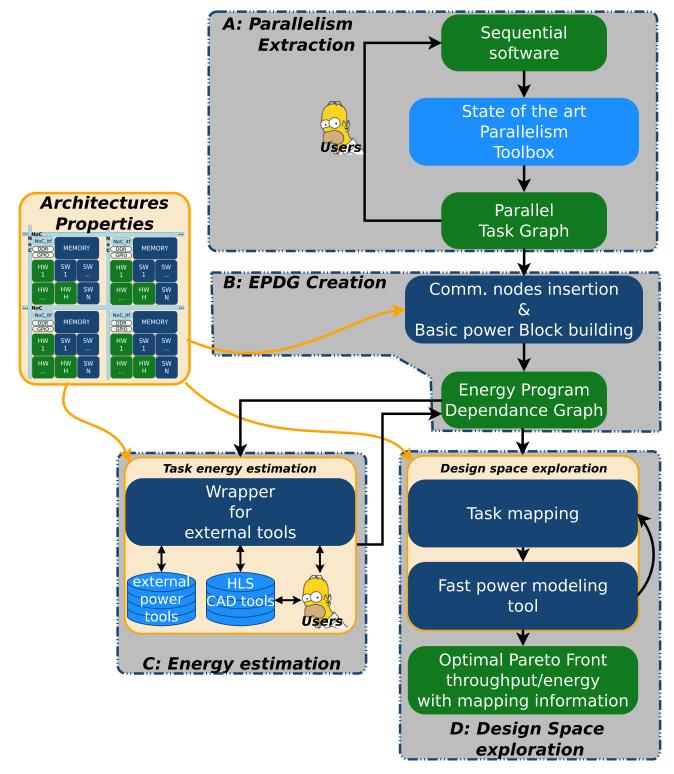

Dans ce chapitre, nous résumons le contexte de l'étude ainsi que les différentes contributions apportées au cours de la thèse. Dans les sous sections suivantes, nous présentons le concept de radio logicielle et les différentes avancées dans le monde de la microélectronique ayant entraîné l'apparition des architectures hétérogènes. La section 2 introduit la structure générique des architectures considérées ainsi qu'une méthode de représentation mettant l'accent sur les canaux de communications. Nous présentons également le format de représentation utilisé pour la description d'application. Enfin, nous introduisons un flot de développement orienté sur l'énergie ainsi que les travaux réalisés au vu de son adoption. Pour finir, la section 4 résume les différents éléments présentés dans ce document. Section 1 — Contexte général

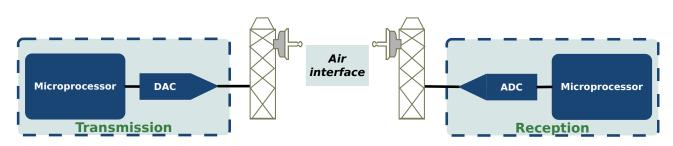

FIGURE 0-1 - Structure globale d'une radio logicielle idéale.

### **1.1 RADIO LOGICIELLE**

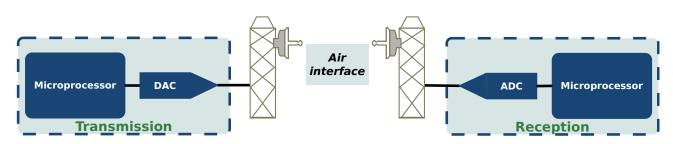

Le concept de radio logicielle trouve ses fondements dans le domaine militaire avec la nécessité d'assurer l'inter-opérabilité des équipements à l'aide de plateformes pouvant générer plusieurs formes d'ondes et normes de communication grâce à une simple reprogrammation. En effet, le cycle de vie des applications militaires est assez long et il est essentiel de les maintenir et d'assurer leur inter-opérabilité avec les applications à venir. Ce concept a été introduit pour la première fois dans les années 90 par Joseph Mitola [Mit93]. Il consiste à réduire la partie analogique à son strict minimum pour avoir plus de flexibilité de reconfiguration avec la partie numérique. Une architecture de radio logicielle idéale serait composée d'un convertisseur placé directement derrière l'antenne et d'un composant numérique programmable tel qu'un microprocesseur dédié aux traitements. Cela est illustré sur la Figure 0-1. Cette structure, permettant une flexibilité totale, est l'objectif ultime d'un système de radio logicielle. Malheureusement, numériser le signal juste après l'antenne requière une haute fréquence d'échantillonnage des convertisseurs et représente un frein. De plus, les implémentations de radio logicielle basées sur des microprocesseurs généralistes présentent certaines limites notamment liées aux performances énergétiques et aux débits atteignables. Néanmoins, la plupart des algorithmes utilisés est hautement parallèle et nécessite des performances de calculs importantes qui pourraient tirer profit des nouvelles architectures multicœurs hétérogènes et ainsi traiter les problèmes de consommation d'énergie au prix d'une programmation plus complexe.

#### **1.2 TENDANCES ARCHITECTURALES**

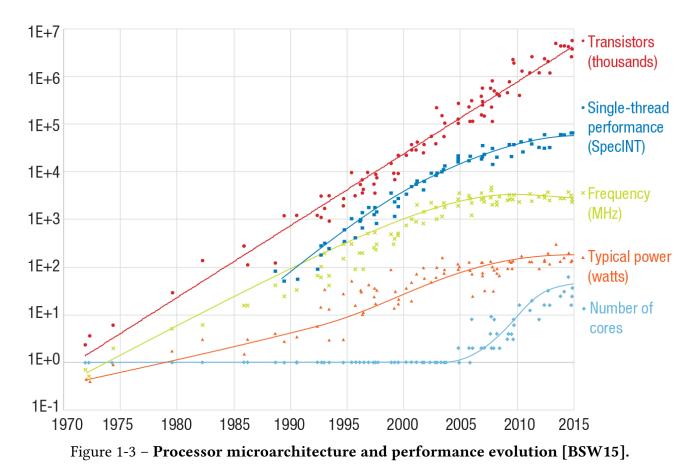

Par le passé, la loi de Moore [Moo65] prédisant le doublement du nombre de transistors sur puce tous les 18 mois, a été un moteur fondamental de l'évolution des microarchitectures. Associée à la loi de Dennard [Den+74] prédisant la diminution de la tension et du courant d'alimentation des transistors en proportion de leur taille, une série de circuits, d'architectures et de compilateurs a émergé, conduisant ainsi à une augmentation exponentielle des performances. Ces dernières ont été obtenues en passant progressivement d'architectures simple-cœur à des architectures multicœurs pour tirer pleinement profit du nombre de transistors disponibles. Malheureusement, un nouveau phénomène appelé "dark silicon" lié à la limitation de la densité de puissance dissipée sur une puce [Esm+11] est apparu. Ce dernier empêche l'utilisation simultanée de l'ensemble des transistors présents sur la puce et a poussé les concepteurs d'architectures à intégrer des accélérateurs matériels au sein des microarchitectures. C'est ainsi que sont nées les architectures multicœurs hétérogènes intégrant plusieurs cœurs processeurs et des accélérateurs matériels. Outre le gain en performance, ces architectures ont induit de nouvelles problématiques en termes de développement. En effet, avec la multiplication du nombre et du type d'organes de calcul, l'espace d'exploration est devenu immense. Ainsi, lorsque la consommation devient un facteur clé, il est essentiel de pouvoir explorer cet espace au plus tôt dans le flot de développement pour obtenir des solutions efficaces en énergie.

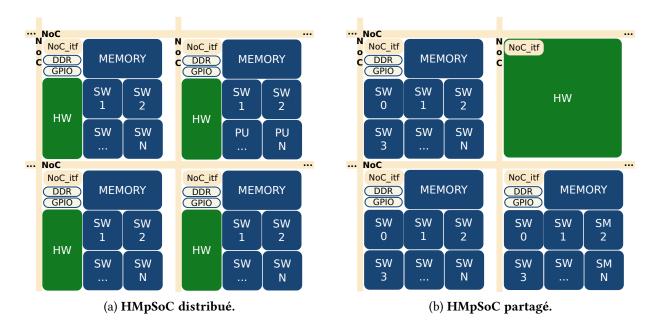

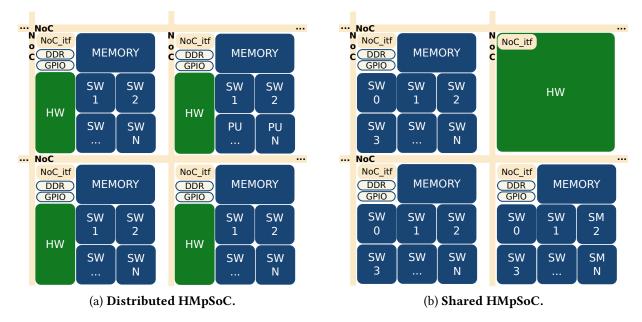

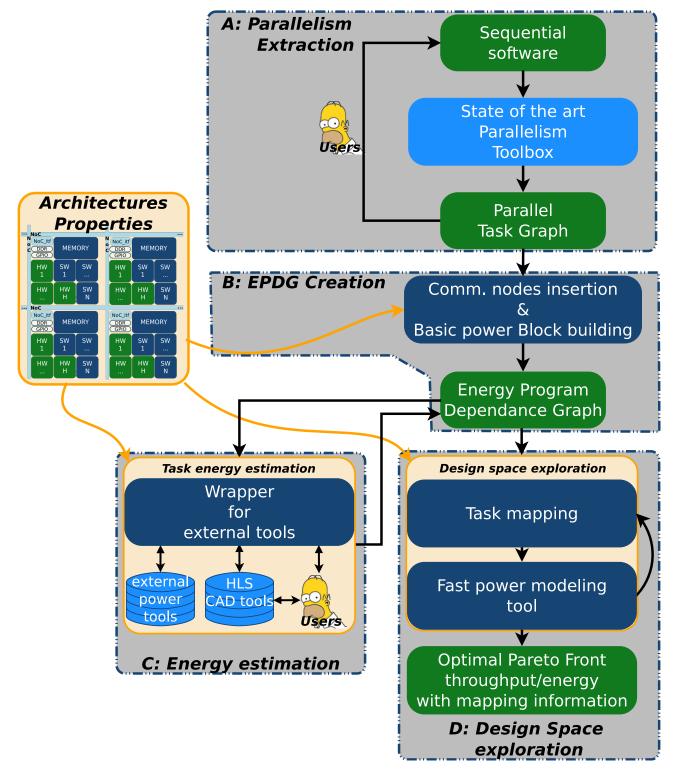

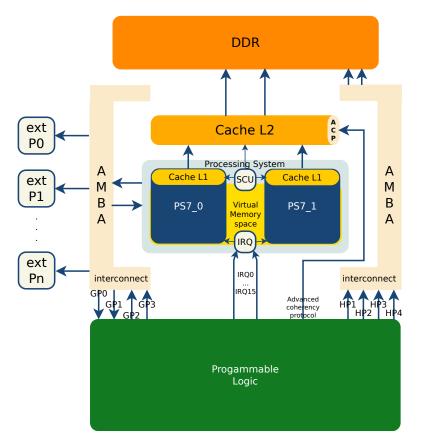

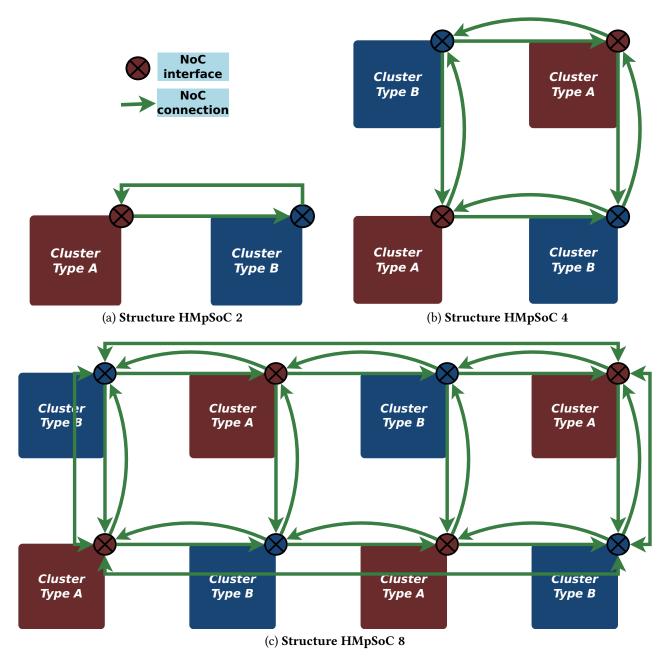

FIGURE 0-2 – Structure des architectures HMpSoC.

## **2** ARCHITECTURES ET APPLICATIONS CIBLES

Dans cette section, nous présentons le formalisme utilisé dans la suite du document pour décrire les architectures et les applications utilisées.

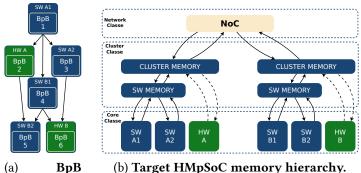

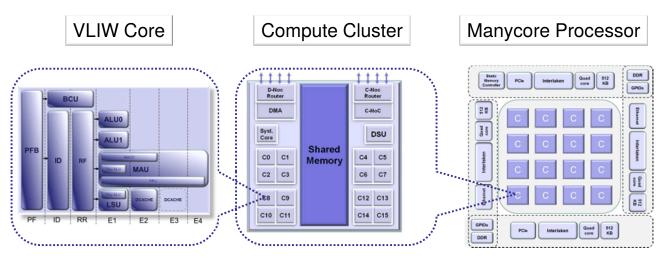

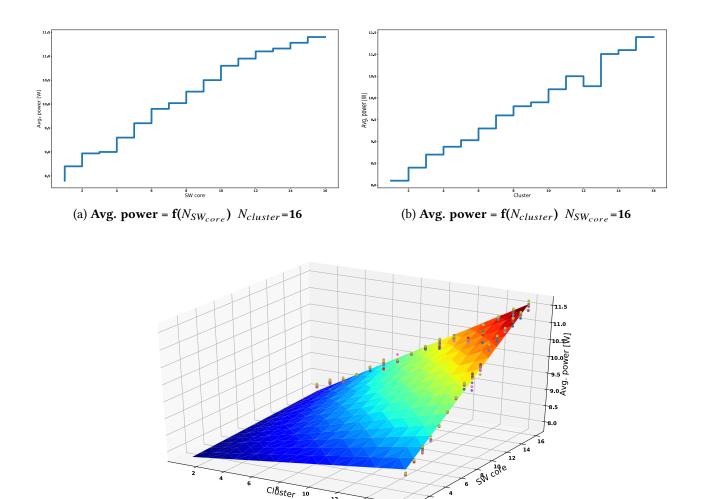

### 2.1 ARCHITECTURES CIBLES

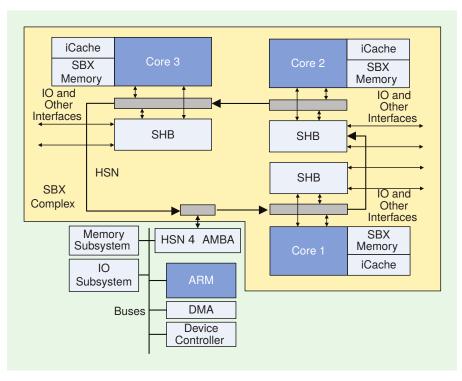

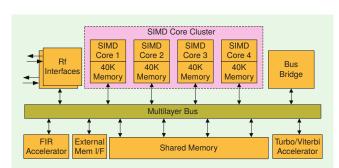

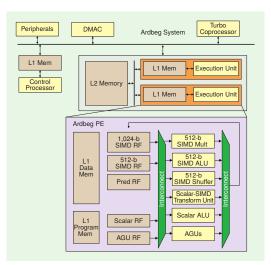

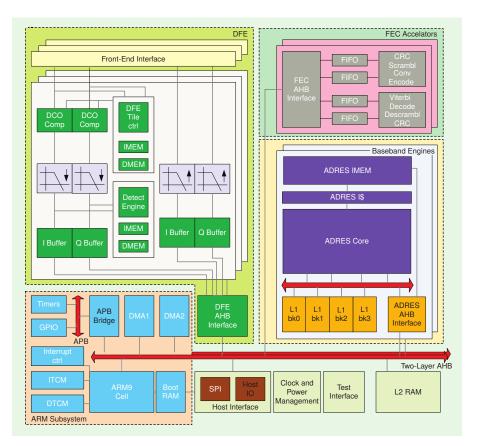

Pour que notre étude puisse être appliquée à un large panel d'architectures, nous avons commencé par décrire de manière générique la structure des architectures ciblées. Pour cela, nous avons étudié diverses architectures utilisées dans le domaine de la radio logicielle ainsi que des architectures plus généralistes. Les architectures multicœurs sont généralement composées d'un ensemble de mémoires, de processeurs, d'éléments d'interconnexion et d'entrées/sorties. Lorsqu'elles intègrent des accélérateurs matériels, elles deviennent hétérogènes dans le sens où elles associent des processeurs généralistes (SW) et des accélérateurs matériels (HW). Une représentation générique de ces architectures, appelées HMpSoC, est proposée dans la Figure 0-2. Elle est construite à l'aide de clusters connectés par un réseau sur puce (NoC). Chaque cluster est composé de N cœurs de calcul logiciels associés à un accélérateur matériel de taille S. Au niveau du cluster, les communications sont effectuées grâce à une mémoire partagée. Suite à cette description, deux familles de HMpSoC peuvent être construites en fonction du placement des accélérateurs matériels dans l'architecture. Dans le cas où ils sont placés au sein de chaque cluster ( $S \neq 0$ ), on obtient des *HMpSoC distribués* (Figure 0-2a). Ils permettent d'obtenir des communications rapides entre la partie matérielle et la partie logicielle mais en conséquence, la taille maximale des accélérateurs est réduite. Dans le cas où les accélérateurs sont placés au niveau cluster, on obtient deux types de cluster : les clusters logiciels  $(N \neq 0 \text{ et } S = 0)$ ; et les clusters matériels ( $S \neq 0 \text{ et } N = 0$ ). Les architectures ainsi obtenues sont appelées HMpSoC partagés (Figure 0-2b). Cette approche permet d'avoir des accélérateurs matériels de grande taille et de les partager entre les clusters. En contrepartie, ils induisent une augmentation des temps de communications entre la partie logicielle et la partie matérielle.

Les familles de HMpSoC introduites précédemment peuvent définir un grand nombre d'architectures. Pour cibler, avec précision, une architecture particulière au sein de ces familles, nous avons

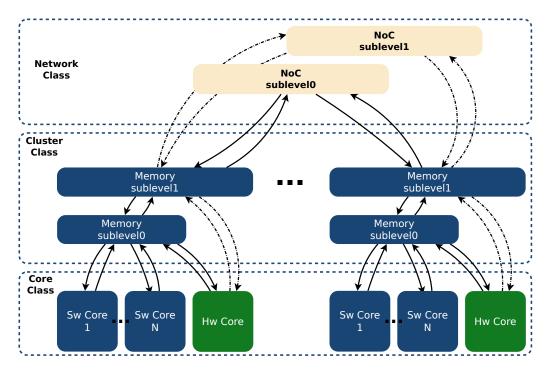

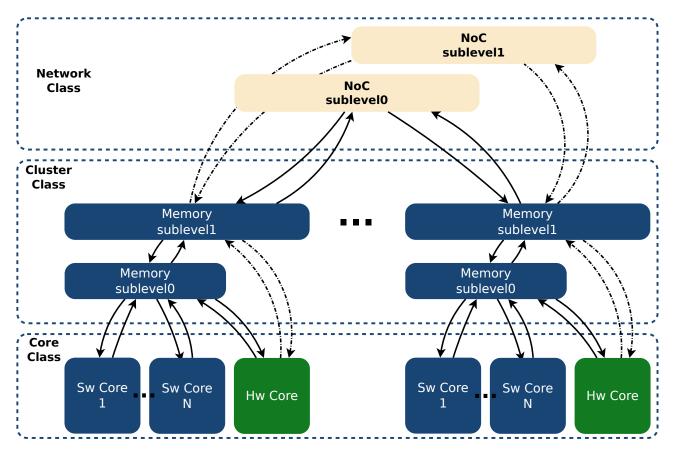

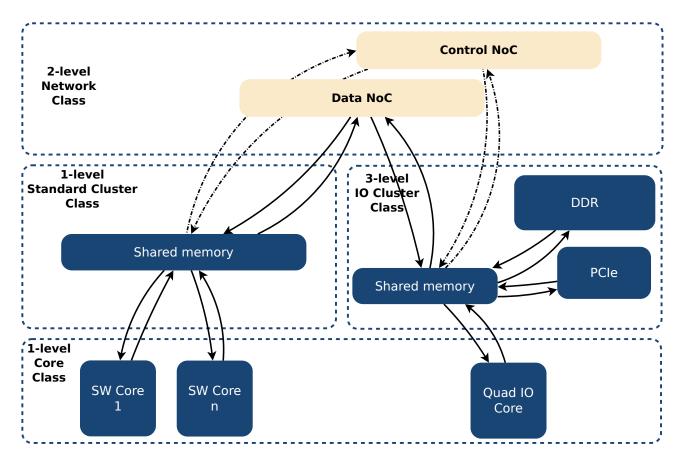

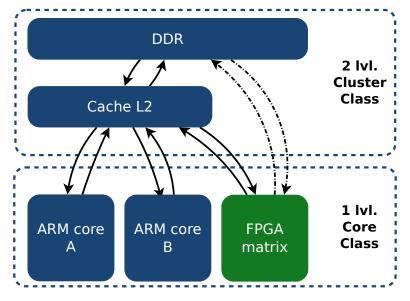

FIGURE 0-3 - Représentation d'un HMpSoC basée sur la hiérarchie mémoire.

besoin d'une représentation générique. Pour cela, nous avons proposé une représentation basée sur la hiérarchie mémoire décrite à l'aide d'un arbre orienté (Figure 0-3). Cette représentation divise la hiérarchie mémoire d'un HMpSoC en trois niveaux principaux : réseau, cluster et cœur. Chaque niveau contient des sous-niveaux, avec les propriétés suivantes.

- Au niveau réseau, les sous-niveaux sont disjoints de façon à ce que chaque sous-niveau puisse être utilisé indépendamment.

- Au niveau cluster, les sous-niveaux sont mixtes, c'est-à-dire qu'ils sont liés entre eux mais restent accessibles à chaque sous-niveau.

- Au niveau cœur, les sous-niveaux sont liés. L'accès au sous-niveau de profondeur L passe par les L 1 sous-niveaux supérieurs.

Pour décrire avec précision une architecture cible, les caractéristiques de chaque classe mémoire doivent être définies, telles que la profondeur de chaque sous-niveau, le débit des canaux, ainsi que le coût des communications.

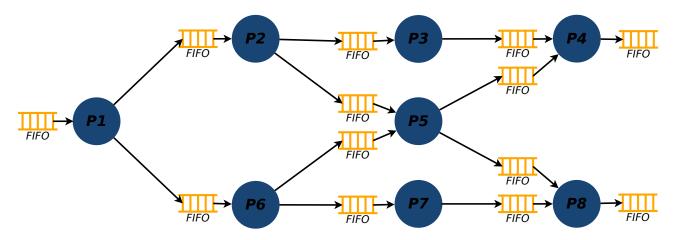

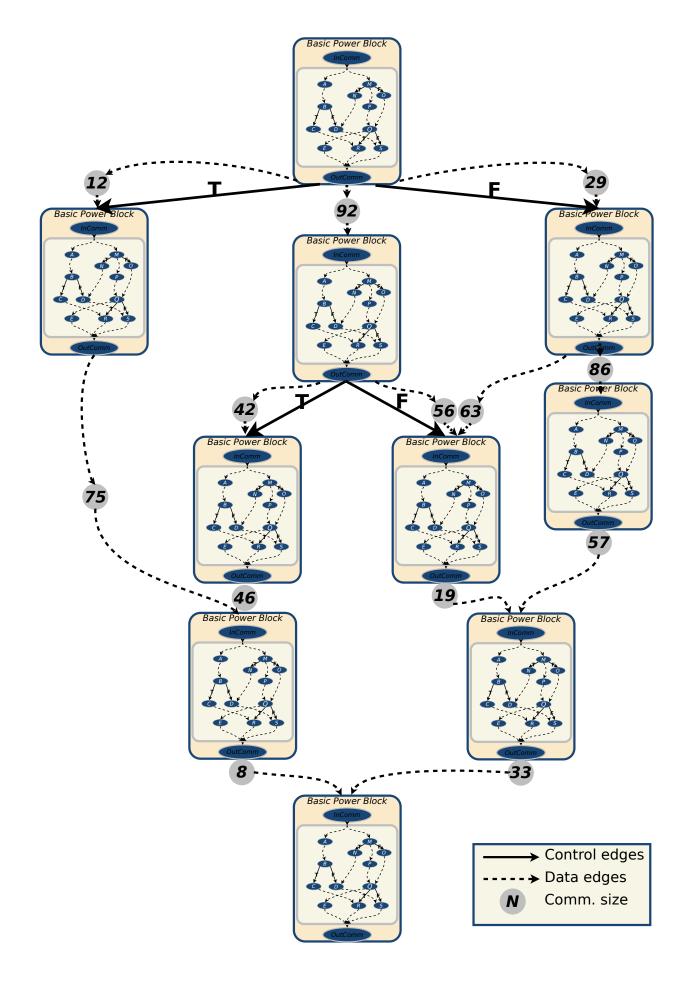

### 2.2 STRUCTURE DES APPLICATIONS