# Heterogeneous cluster computing for many-task exact optimization - Application to permutation problems ${\rm Jan\ Gmys}$

## ▶ To cite this version:

Jan Gmys. Heterogeneous cluster computing for many-task exact optimization - Application to permutation problems. Distributed, Parallel, and Cluster Computing [cs.DC]. Université de Mons (UMONS); Université de Lille, 2017. English. NNT: . tel-01652000

# HAL Id: tel-01652000 https://inria.hal.science/tel-01652000

Submitted on 29 Nov 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Grascomp École Doctorale Sciences Pour l'Ingénieur, Université de Lille Nord-de-France

# **THÈSE**

# préparée dans le cadre d'une cotutelle pour obtenir le grade de

Docteur en Sciences de l'Ingénieur de l'Université de Mons Docteur en Informatique et applications de l'Université de Lille

présentée et soutenue publiquement par

# Jan Gmys

le 19 décembre 2017

Heterogeneous cluster computing for many-task exact optimization - Application to permutation problems

# devant le jury composé de

|              | Patricia Stolf,      | Maître de conférence | Université Toulouse Jean-Jaurès   |

|--------------|----------------------|----------------------|-----------------------------------|

|              | Imen Chakroun,       | Researcher           | IMEC                              |

|              | Pierre Manneback,    | Professeur           | Université de Mons                |

|              | Frédéric Sемет,      | Professeur           | École Centrale de Lille           |

|              | Andrzej Jaszkiewicz, | Professeur           | Poznan University of Technology   |

| Rapporteurs  | Franck Cappello,     | Senior Researcher    | Argonne National Laboratory (USA) |

|              | Farouk Yalaoui,      | Professeur           | Université de Technologies Troyes |

| Directeurs   | Daniel Tuyttens,     | Professeur           | Université de Mons                |

|              | Nouredine Melab,     | Professeur           | Université de Lille               |

| Co-directeur | Mohand Mezmaz,       | Chargé de Recherche  | Université de Mons                |

### **Abstract:**

Branch-and-Bound (B&B) is a tree-based exploration method for exactly solving combinatorial optimization problems by implicit enumeration of the solution space. B&B dynamically generates large irregular search trees which need to be processed in parallel as only very small problem instances can be solved within a reasonable amount of time on a sequential computer. The latest *Top500* ranking of the world's largest supercomputers confirms the tendency towards heterogeneous systems including GPUs and multi-core/many-core processors as main building blocks. This thesis revisits the design and implementation of B&B for hybrid multi-core and multi-GPU platforms, from single-node systems to large-scale heterogeneous high performance computing clusters. Although B&B is a generic method, the design of parallel B&B is strongly influenced by both the characteristics of the tackled problem and the target architecture. The focus is put on permutation-based combinatorial problems, using the Flowshop Scheduling Problem (FSP), the Quadratic Assignment Problem (QAP) and the *n*-Queens puzzle problem as test-cases.

An innovative data structure dedicated to permutation problems, called Integer-Vector-Matrix (IVM) is used for the efficient storage and management of the pool of sub-problems instead of conventional data structures (e. g. stacks, deques, priority queues). The principle of parallel IVM-based B&B is to have several independent B&B processes use their private IVM for the exploration of different parts of the search space, which are compactly encoded as intervals. Several IVM-based parallel B&B algorithms are presented in this thesis. For shared-memory multi-core processors, we propose a hybrid multi-core-GPU B&B that can use available GPU devices for the acceleration of the bounding operator, which is often the most time-intensive part of B&B. Targeting GPUs and single-node multi-GPU systems, we present the first B&B algorithm that runs entirely on the GPU, using different parallelization models for coarse- and fine-grained permutation problems. In order to exploit heterogeneous clusters with multiple distributed GPUs and multi-core CPUs, both approaches are combined using the master-worker paradigm.

In order to balance the workload IVM-based B&B processes exchange intervals in a work stealing approach. Indeed, considering the highly irregular nature of B&B, one of the main challenges is the dynamic distribution of subproblems (nodes of the B&B tree) among a large set of processors. The design of efficient work stealing strategies is therefore a central contribution of this thesis. Interval-based work stealing strategies are proposed for multi-core B&B, including its GPU-accelerated variant and for GPU-centric B&B, performing work stealing inside the GPU. Using hierarchical work stealing approaches, inter-GPU and inter-node load balancing approaches are proposed for

single-node multi-GPU systems and hybrid distributed clusters.

A second major challenge raised by the irregularity of B&B is the efficient use of single-instruction multiple-data processing at the instruction-level, as well as the minimization of detrimental effects from irregular memory access patterns. Targeting Intel multicore and many-integrated core (MIC) processors, a vectorizable implementation of the FSP bounding operator is proposed. In order to improve control flow efficiency and reduce instruction replay overhead, alternative mapping schemes are presented for the GPU-centric B&B.

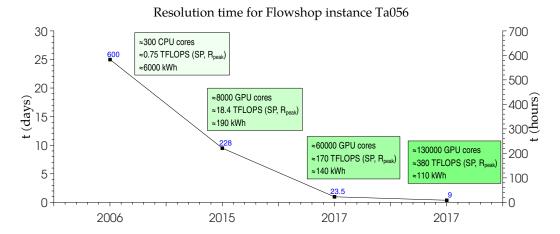

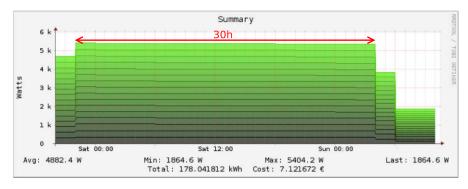

Extensive experimental evaluations are performed using the three test-cases, revealing input-dependent behaviors. Results demonstrate the scalability of the approach at different levels, with respect to the number of CPU cores, GPU cores, GPU devices and heterogeneous compute nodes. In particular the use of multi-GPU systems and large clusters allows to solve instances whose exact resolution is otherwise impractical. For a class of 20 jobs-on-20 machines FSP instances with sequential execution times between 15 minutes and 22 hours, the resolution time using four GPUs ranges from 1 second to 1 minute, i. e. an improvement of three orders of magnitude compared to a single CPU core. A large FSP instance, defined by 50 jobs and 20 machines, whose resolution requires 25 days of processing on more than 300 CPU cores is solved within 9 hours on a cluster containing 36 GPUs.

## **Keywords:**

Branch-and-Bound, Combinatorial optimization, High-performance computing, GPU computing, Permutation problems

#### Résumé:

L'algorithme Branch-and-Bound (B&B, en Français, séparation et évaluation) est fréquemment utilisé pour la résolution exacte de problèmes d'optimisation combinatoire. Il s'agit d'une méthode de recherche arborescente qui procède par énumération implictite de l'ensemble de solutions. L'algorithme génère des arbres de recherche souvent très larges et fortement irréguliers qui doivent être explorés en parallèle, car seules des petites instances peuvent être résolues en un temps raisonnable sur une machine séquentielle. Le dernier classement mondial des supercalculateurs les plus puissants (Top500) confirme que ces derniers tendent à être de plus en plus hétérogènes, combinant processeurs multicore, many-core et processeurs graphiques (GPUs). Dans cette thèse nous réexaminons la conception et l'implémentation d'algorithmes B&B sur de larges plateformes hétérogènes de calcul haute performance. En dépit de sa généricité, la conception d'algorithmes B&B parallèles est fortement influencée par les caractéristiques du problème résolu et de l'architecture ciblée. Nous nous concentrons sur des problèmes combinatoires définis sur l'ensemble des permutations. Le problème d'ordonnancement Flow-Shop (FSP), le problème d'affectation quadratique (QAP) et le problème des *n*-dames sont utilisés comme cas d'étude.

Une structure de données originale (appelée IVM ou Integer-Vector-Matrix) dédiée aux problèmes de permutation est utilisée pour le stockage et la gestion efficaces du pool de sous-problèmes (noeuds de l'arbre). Dans le B&B parallèle basé sur IVM, plusieurs processus B&B indépendants explorent en parallèle différentes parties de l'espace de recherche en utilisant leur structure IVM privée. Chaque partie de l'espace de recherche assigné à un processus B&B est encodée de manière compacte sous forme d'un intervalle de nombres factoriels.

Plusieurs algorithmes B&B basés sur IVM sont présentés dans cette thèse. Pour des processeurs multi-coeurs à mémoire partagée, nous proposons un algorithme hybride qui utilise les GPUs disponibles pour l'accélération de l'évaluation de sous-problèmes, celle-ci étant souvent la partie la plus coûteuse en temps. Ciblant les GPUs et les systèmes multi-GPUs, nous proposons le premier algorithme B&B executé entièrement sur l'accélérateur, utilisant deux modèles de parallélisation adaptés aux problèmes à granularité fine et grossière. Pour l'exploitation de clusters hétérogènes à mémoire distribuée, les approches multi-core et GPU sont combinées en les intégrant dans un modèle fermier-travailleur.

Afin d'équilibrer la charge de travail dynamiquement, les processus B&B basés sur IVM s'échangent des intervalles en utilisant une approche de vol de tâches. A cause de la nature fortement irrégulière et imprévisible de l'algorithme B&B, la répartition dynamique de sous-problèmes parmi l'ensemble des processeurs représente en effet un

des défis majeurs. Par conséquent, la conception de stratégies de vol de tâches occupe une place centrale dans cette thèse. Des strategies de vol de tâches basées sur les intervalles de nombres factoriels sont proposées pour le B&B multi-core (accéléré par GPU) et pour le B&B basé sur GPU, équilibrant la charge à l'intérieur du GPU. En utilisant une approche hiérarchique du vol de tâches, des mécanismes d'équilibrage de charge inter-GPUs et inter-noeuds sont proposés pour des systèmes multi-GPUs et pour des clusters hybrides à mémoire distribuée.

L'utilisation efficace du traitement "instruction unique, données multiples" (SIMD) est un second défi posé par l'irrégularité inhérente à l'algorithme B&B. En effet, la divergence de contrôle et les accès mémoire irréguliers dégradent fortement la performance du traitement SIMD, qui est un levier de performance important au niveau des instructions. Ciblant l'exploitation des registres SIMD des processeurs multi-core et MIC, une nouvelle implémentation vectorisable de la borne inférieure utilisée pour le FSP est présentée. Pour reduire les effets négatifs de la divergence de contrôle sur l'efficacité du traitement par GPU, des mappings alternatifs pour l'implémentation sur GPU des différents opérateurs B&B sont présentés.

Des évaluations expérimentales approfondies utilisant les trois cas d'étude ont été effectuées, révélant l'impact du problème résolu sur le comportement des algorithmes. Les résultats expérimentaux démontrent une bonne scalabilité des approches proposées à plusieurs niveaux: par rapport au nombre de coeurs CPU et GPU, par rapport au nombre de GPUs utilisés et par rapport au nombre de noeuds hétérogènes dans le B&B distribué.

En particulier, l'utilisation de systèmes multi-GPUs et de larges clusters de GPUs permet une résolution d'instances de problèmes qui serait impraticable séquentiellement. Pour une classe d'instances du FSP ( $20 \times 20$ ) avec un temps de résolution entre 15 minutes et 22 heures sur un seul coeur CPU, le temps de résolution sur 4 GPUs est compris entre 1 seconde et 1 minute, soit trois ordres de grandeur plus court. Une très grande instance du FSP définie par 50 jobs et 20 machines, dont le temps de résolution séquentiel est estimé à 22 ans, est résolue en 9 heures sur un cluster de calcul équipé de 36 GPUs.

### Mots clés

Branch-and-Bound parallèle, Optimisation combinatoire, Caclul haute performance, Processeurs Graphiques, Problèmes de Permutation

# **Contents**

| C  | Contents                               |                                         |                                                    | 1  |  |  |

|----|----------------------------------------|-----------------------------------------|----------------------------------------------------|----|--|--|

| In | trodu                                  | ıction                                  |                                                    | 1  |  |  |

| 1  | Parallel Branch-and-Bound algorithms   |                                         |                                                    | 8  |  |  |

|    | 1.1                                    | duction                                 | 9                                                  |    |  |  |

|    | 1.2                                    | Solvir                                  | ng permutation combinatorial optimization problems | 10 |  |  |

|    |                                        | h-and-Bound algorithms                  | 11                                                 |    |  |  |

|    |                                        | 1.3.1                                   | Terminology and general description                | 12 |  |  |

|    |                                        | 1.3.2                                   | Models for parallel Branch-and-Bound               | 14 |  |  |

|    |                                        | 1.3.3                                   | Challenges in parallel Branch-and-Bound            | 17 |  |  |

|    | •                                      |                                         | outing Environments                                | 20 |  |  |

|    |                                        |                                         | ed work                                            | 25 |  |  |

|    |                                        | 1.5.1                                   | B&B for multi-core CPUs                            | 25 |  |  |

|    |                                        | 1.5.2                                   | B&B for Graphics Processing Units                  | 27 |  |  |

|    |                                        | 1.5.3                                   | Hybrid and distributed parallel B&B                | 29 |  |  |

|    | 1.6 Test-cases: Permutation-based COPs |                                         | ases: Permutation-based COPs                       | 30 |  |  |

|    |                                        | 1.6.1                                   | Flowshop Scheduling Problem (FSP)                  | 30 |  |  |

|    |                                        | 1.6.2                                   | Quadratic Assignment Problem (QAP)                 | 32 |  |  |

|    |                                        | 1.6.3                                   | <i>n</i> -Queens Problem                           | 33 |  |  |

|    |                                        | 1.6.4                                   | B&B tree analysis of the test problems             | 34 |  |  |

| 2  | IVN                                    |                                         | d B&B for multi-/many-core systems                 | 39 |  |  |

|    | 2.1                                    | Introd                                  | duction                                            | 41 |  |  |

|    | 2.2                                    | 2.2 IVM-based parallel Branch-and-Bound |                                                    |    |  |  |

|    |                                        | 2.2.1                                   | IVM-based serial B&B                               | 41 |  |  |

|    |                                        | 2.2.2                                   | Position vector: factoradic numbers                | 44 |  |  |

|    |                                        | 2.2.3                                   | Work units: intervals of factoradics               | 46 |  |  |

2 Contents

|   |      | 2.2.4                        | Work unit communication                             | 48  |  |  |

|---|------|------------------------------|-----------------------------------------------------|-----|--|--|

|   | 2.3  | Work                         | stealing for IVM-based B&B on multi-core CPUs       | 50  |  |  |

|   |      | 2.3.1                        | Work stealing using factoradic intervals            | 51  |  |  |

|   |      | 2.3.2                        | Victim selection policies                           | 51  |  |  |

|   |      | 2.3.3                        | Granularity policies                                | 54  |  |  |

|   | 2.4  | Accle                        | ration of bounding operator                         | 55  |  |  |

|   |      | 2.4.1                        | GPU acceleration                                    | 55  |  |  |

|   |      | 2.4.2                        | Vectorization of the FSP bounding procedure         | 57  |  |  |

|   | 2.5  | Exper                        | riments                                             | 59  |  |  |

|   |      | 2.5.1                        | Evaluation of data structures for B&B               | 60  |  |  |

|   |      | 2.5.2                        | GPU-acceleration of the bounding operator           | 62  |  |  |

|   |      | 2.5.3                        | Evaluation of Work Stealing Strategies              | 63  |  |  |

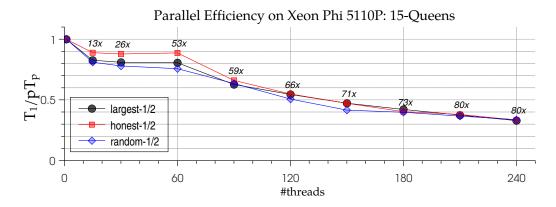

|   |      | 2.5.4                        | Performance evaluation on Intel Xeon Phi            | 67  |  |  |

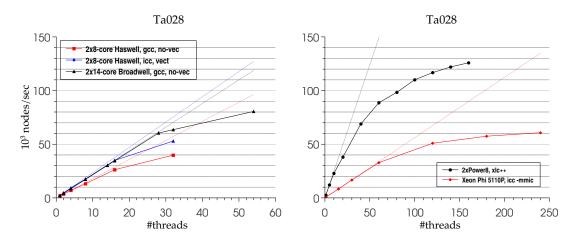

|   |      | 2.5.5                        | MC-B&B: performance on different multi-core CPUs    | 70  |  |  |

|   | 2.6  | Concl                        | usions                                              | 71  |  |  |

| 3 | GPU  | PU-centric Branch-and-Bound  |                                                     |     |  |  |

|   | 3.1  |                              |                                                     |     |  |  |

|   | 3.2  | Discussion of design choices |                                                     |     |  |  |

|   | 3.3  | -                            |                                                     |     |  |  |

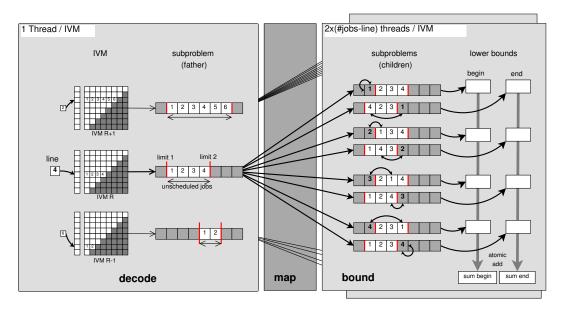

|   |      | 3.3.1                        | GPU-B&B: 2-level parallelization                    | 81  |  |  |

|   |      | 3.3.2                        | Thread-data mapping and branch divergence reduction | 86  |  |  |

|   |      | 3.3.3                        | GPU-BT: 1-level parallelization                     | 90  |  |  |

|   | 3.4  | Work                         | stealing strategies for GPU-B&B                     | 92  |  |  |

|   |      | 3.4.1                        | Victim Selection policies                           | 92  |  |  |

|   |      | 3.4.2                        | Work stealing for multi-GPU-B&B                     | 96  |  |  |

|   | 3.5  | Exper                        | riments                                             | 97  |  |  |

|   |      | 3.5.1                        | Evaluation of Mapping approaches                    | 97  |  |  |

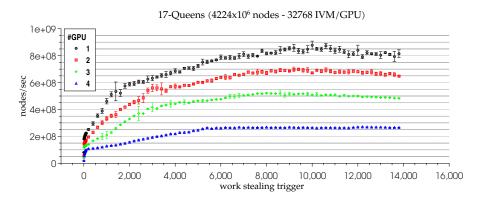

|   |      | 3.5.2                        | Evaluation of Work Stealing strategies              | 101 |  |  |

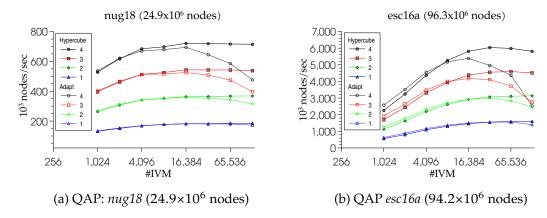

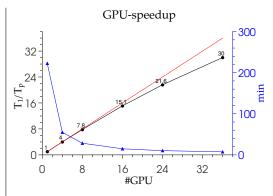

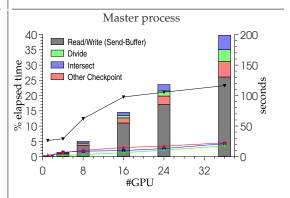

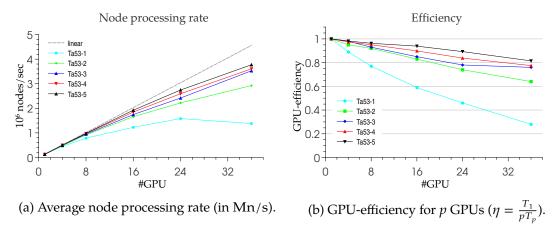

|   |      | 3.5.3                        | Scalability analysis                                | 103 |  |  |

|   |      | 3.5.4                        | Multi-GPU-B&B performance evaluation                | 107 |  |  |

|   |      | 3.5.5                        | Hybrid CPU-multi-GPU-B&B                            | 111 |  |  |

|   | 3.6  | Concl                        | usions                                              | 114 |  |  |

| 4 | Brai | nch-and                      | d-Bound for hybrid HPC clusters                     | 117 |  |  |

|   | 4.1  |                              | duction                                             | 118 |  |  |

|   | 4.2  |                              | for hybrid clusters                                 | 118 |  |  |

|    |       | 4.2.1    | B&B@Grid                                   | 118 |

|----|-------|----------|--------------------------------------------|-----|

|    |       | 4.2.2    | Design of hybrid distributed B&B           | 120 |

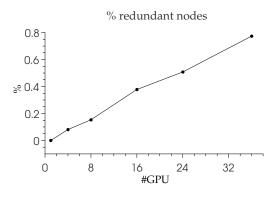

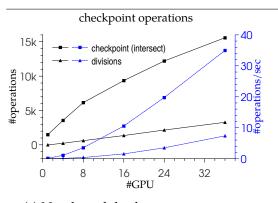

|    |       | 4.2.3    | Redundant exploration                      | 122 |

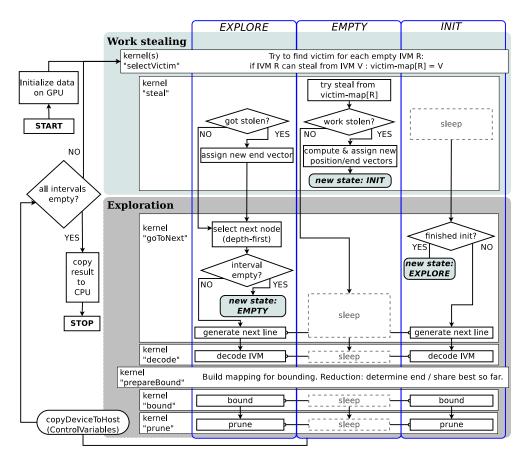

|    |       | 4.2.4    | Implementation of worker process           | 124 |

|    | 4.3   | Exper    | riments                                    | 127 |

|    |       | 4.3.1    | Experimental protocol                      | 127 |

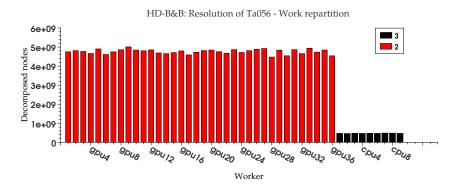

|    |       | 4.3.2    | Resolution of very large problem instances | 127 |

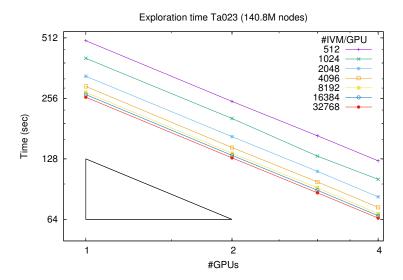

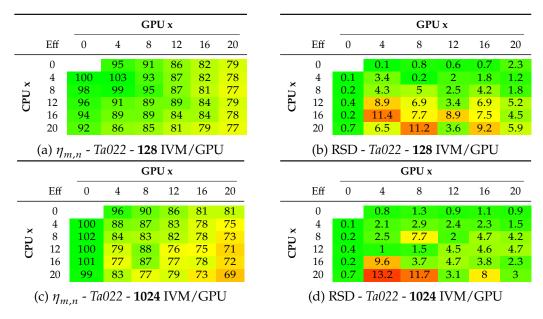

|    |       | 4.3.3    | Scalability: Ouessant                      | 132 |

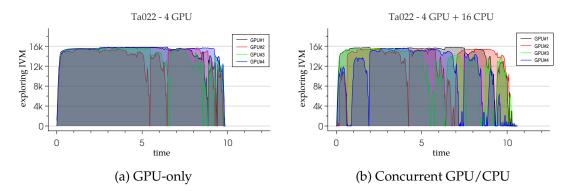

|    |       | 4.3.4    | Hybrid CPU/GPU scalability                 | 135 |

|    |       | 4.3.5    | Solving other 50×20 FSP instances          | 137 |

|    | 4.4   | Concl    | lusion                                     | 138 |

| 5  | Con   | ıclusioı | ns and Perspectives                        | 140 |

| Li | st of | Figures  | S .                                        | 158 |

| Li | st of | Tables   |                                            | 160 |

| A  | App   | endix    |                                            | I   |

|    | A.1   | Tree s   | sizes                                      | I   |

|    | A.2   | Lower    | r bounds: complexities                     | I   |

|    | Α3    | Hardy    | ware                                       | П   |

4 Contents

# Introduction

Permutation-based optimization or constraint satisfaction problems frequently arise in industrial and economic applications such as routing, scheduling and assignment. Solving such problems consists in finding one or several permutation(s) that minimize/maximize<sup>1</sup> a given cost function or, respectively, satisfy a given set of constraints.

In this thesis we address NP-hard combinatorial optimization problems. Heuristic approaches are able to find near-optimal solutions in a reasonable amount of time, but they fail in general to find optimal solutions. Conversely, exact methods allow to find the optimal solution(s) with a proof of optimality, but the required computation power can be very huge. One of the most used exact methods to solve COPs is the Branch-and-Bound (B&B) algorithm. B&B implicitly enumerates all possible solutions by dynamically constructing and exploring a tree. This is done using four operators: branching, bounding, selection and pruning. Using the branching operator, the algorithm recursively decomposes the problem into smaller subproblems. A bounding function is used to compute lower bounds on the optimal cost of these subproblems. Using these lower bounds, the pruning operator discards subproblems from the search that cannot lead to an improvement of the best solution found so far. The tree-traversal is guided by the selection operator which returns the next subproblem to be processed according to a predefined strategy (e.g. depth-first search). Due to the pruning of branches the explored tree is highly irregular and unpredictable in size and shape.

Although the lower bound-based pruning mechanism of B&B significantly reduces the number of explored nodes, B&B algorithms often generate very large trees. Using a single processing core only small or moderately-sized instances can be solved in a reasonable amount of time. For this reason, over the last decades, parallel computing has been revealed as an attractive way to deal with larger instances.

Over the past 20 years we have witnessed an impressive evolution of computing technologies. Computer architects, programmers and researchers are moving towards

<sup>1.</sup> Without loss of generality the minimization case is considered in this thesis.

2 Introduction

heterogeneous (or hybrid/collaborative) computing which aims at matching the requirements of each application to the strengths of the different architectures present in a heterogeneous computing system [MV15]. The biannual list of the most powerful supercomputers in the world, Top500 [16], reveals that advances in computer system design, microprocessor architecture, memory subsystem and networking allow to deliver factor 2 performance increase every 18 - 24 months. While a similar growth is predicted over the next 10 years, this is being achieved through a huge increase in hardware complexity [GR14]. The cost of moving data, in terms of energy and time, is often greater than the cost of computations, although memory subsystems have evolved to an impressive level of complexity [Dre07]. As energy-efficiency has become a key issue, the trend towards more complex and more heterogeneous HPC systems is likely to continue. The rise of low-power processors and system-on-chip (SoC) designs, driven by the mobiledevice market, indicate that future HPC systems are likely to contain a large number of heterogeneous, more or less powerful components [GR14]. An increasing number of heterogeneous components (and lower operating voltages) may lead to higher failure rates, calling for fault-tolerant algorithms and highly efficient communication schemes, to cite just two of the tremendous challenges that lie ahead in the field of HPC [Cap09; CGG+14].

The B&B algorithm can be used to solve basically any type of COP. Despite the genericity of B&B, the nature of the problem being solved has a strong impact on fundamental design and implementation decisions. In particular, the choice of the most suitable parallelization model and of the most suitable target architecture is determined mainly by the computational characteristics of the node evaluation function. Knowing that billions of nodes need to be evaluated, if possible in parallel, the following questions are crucial. Is the operation of evaluating a node very time and/or memory-consuming? Memory or compute-bound? Parallelizable, vectorizable? The research advances that have been made over the last decade, exploring the use of GPUs for B&B algorithms illustrate how the problem-dependent answers to these questions impact design choices.

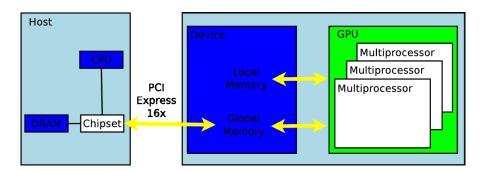

One parallelization approach consists in generating large pools of nodes on the host CPU and offloading them to the GPU, where the nodes are evaluated in parallel. This approach has been applied for instance to the Flowshop Scheduling Problem (FSP) [CMMB13; VDM13] and Knapsack problems [LE12]. To reduce the data volume transferred between host and device, the branching and pruning operators are also implemented on the device [Cha13]. Using multiple streams in order to overlap data transfers and careful tuning of the size of offloaded pools [Cha13] help further decrease the overhead incurred by CPU-GPU communications.

For problems where the node-evaluation cost is relatively low this approach becomes less efficient, as data transfers and the sequential selection and insertion of nodes become bottlenecks. For such fine-grained applications an approach that focuses on performing the search itself in parallel on the GPU is preferred. It consists in exploring the B&B tree on the CPU until a predefined cutoff depth, storing all frontier nodes in a data structure. After this initial search, this set is sent to the GPU and each node in this set is used as a root for a concurrent exploration of the associated subtree. For instance, this approach has been successfully applied to the *n*-Queens [LLW+15a], the Traveling Salesman [CMNL11] and Multiproduct Batch Plant problems [BHG15]. However, such approaches fail to explore highly irregular trees efficiently, as they rely on a static workload repartition.

This thesis deals with the mapping of the B&B algorithm onto heterogeneous computing systems. The focus is put on solving large instances of three well-known permutation-problems, the Flowshop Scheduling Problem (FSP), the Quadratic Assignment Problem (QAP) and the *n*-Queens Problem. These three use cases present different characteristic features and we aim at matching the algorithm with the heterogeneous target architecture in a transparent way for any of the three test-problems. The computing environments considered are shared-memory multi-core CPUs, Many-Integrated Core (MIC) processors, Graphics Processing Units (GPU) and hybrid clusters integrating these three processing units.

As for other algorithms, data structures play a major role in the performance of a B&B algorithm [MR90]. In [Ler15], a data structure using an Integer, a Vector and a Matrix (called IVM) was introduced as an alternative for linked-list-based data structures which are conventionally used in B&B algorithms for permutation problems. In [Ler15], Leroy compares IVM with linked-list-based data structures from a theoretical point of view and experimental results reported in [MLMT14] show that IVM, compared to linked-lists (LL), allows to reduce the amount of time spent in managing the pool of subproblems as well as memory requirements for storing this pool. The B&B algorithms for multi-core, many integrated core (MIC), GPU and hybrid clusters integrating the former three, which are developed in this thesis are based on the IVM data structure.

The addressed issues and proposed contributions are summarized in the following:

• In [Ler15; MLMT14] IVM has only been applied to the Flowshop Scheduling Problem (FSP) and the experimental evaluation is limited to the cost of managing the pool of subproblems. Therefore, our first contribution consists in validating the IVM data structure by revisiting the approach considering other permutation 4 Introduction

**Problems**, namely the Quadratic Assignment Problem (QAP) and the *n*-Queens Problem. In order to establish the utility of IVM for permutation problems in general, it is important to investigate with problems that present different characteristic features, in particular the shape of the explored tree and the computational complexity of the node evaluation function. Indeed, the performance of B&B is strongly influenced by these two problem-dependent parameters.

- We present an IVM-based multi-core algorithm (MC-B&B) for these three problems, as well as work stealing strategies using intervals of factoradics as work units exchanged between threads. Based on MC-B&B, we propose a hybrid GPU-accelerated multi-core B&B algorithm (GMC-B&B). In addition to the parallel exploration of the B&B tree, each thread in GMC-B&B concurrently offloads subproblems to the GPU, where the corresponding lower bound values are computed in parallel. Work stealing strategies for dynamic load balancing are revisited for the accelerated algorithm. For comparison, equivalent linked-list based versions of both algorithms are implemented and experimentally compared to the IVM-based approach.

- Another challenging issue related to B&B for multi-core CPUs is vectorization. In addition to being composed of multiple cores, almost all modern CPUs provide vector instruction sets (e. g. AVX, ARM NEON, AVX2, AVX-512) operating on 128, 256 resp. 512 bit registers (allowing 4, 8 resp. 16 32-bit operations to be performed in one cycle). In order to make full use of the processing capabilities of multi-core CPUs, the computationally intensive parts of an algorithm should be vectorized. In some cases this can be automatically achieved through compiler support, while other cases require rethinking the algorithmic structure of the code. For the FSP, the CPU implementation of the lower bounding procedure is revisited and a vectorization mechanism is proposed.

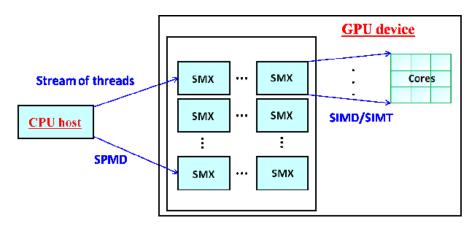

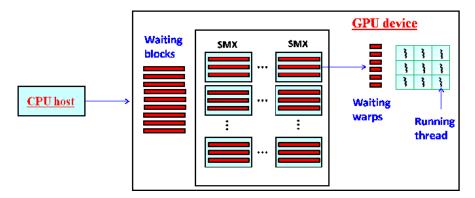

- We propose a (multi-)GPU-based B&B algorithm (GPU-B&B) that implements the entire algorithm as well as load balancing mechanisms on the GPU. To the best of our knowledge it is the first B&B algorithm to perform the entire search process on the GPU. At the core of GPU-B&B is the IVM data structure, whose small and constant memory footprint is better suited to GPUs than conventional LL-based data structures. Using IVM, thousands of tree explorations are performed in parallel and the evaluation of nodes is in turn parallelized to add a second level of fine-grained parallelism. The implementation of B&B on GPU is challenging because its irregular nature contrasts with the regularity of the GPU architecture

- and execution model. Indeed, irregular instruction flow and unstructured memory access patterns are highly detrimental to the performance of GPU processing, as they cause bandwidth penalties and instruction serialization. As a well-informed choice of the thread-data mapping can minimize these effects, different mapping schemes are proposed for the four B&B operators.

- The choice of the best parallelization model depends on the problem being solved. When the application is computationally dominated by a relatively costly bounding procedure (e. g. FSP, QAP) the two-level parallelization of GPU-B&B is well-suited, because the overhead incurred by handling the nested level is compensated by performance gains. However, for fine-grained problems with inexpensive node evaluation functions, like in heuristic backtracking algorithms [RK93], parallel node evaluation is inefficient. For the efficient resolution of fine-grained permutation problems on GPUs we propose a GPU-based backtracking algorithm (GPU-BT). In contrast to the 2-level GPU-B&B, workers perform multiple iterations of B&B within the same kernel until the number of idle worker reaches a critical threshold and a load balancing phase is triggered.

- Dynamic load balancing is a crucial component of parallel tree search algorithms. As GPU-B&B completely bypasses the CPU and performs massively parallel searches on irregular trees, it is necessary to design and implement an efficient mechanism for load balancing inside the GPU. Adapting CPU-based approaches like the work stealing strategies used in MC-B&B to the GPU is not straightforward, as these approaches require locking and mutual exclusion mechanisms, unavailable or inefficient on GPUs. Therefore, the work stealing mechanism for IVM-based B&B is rethought and adapted to the single-instruction multiple-data (SIMD) execution model of the GPU and multi-GPU systems. We propose five work stealing strategies to tackle the problem of work load imbalance inside the GPU. These strategies use different topologies (e. g. ring and hypercube), victim selection policies and mechanisms to adapt themselves to the different phases of the parallel exploration process (ramp-up and shutdown). The proposed load balancing approach is used by both variants of the algorithm.

- In order to solve very large permutation COPs, like the 50-job FSP instance *Ta*056 [Tai93] which requires 22 CPU-years to be solved to optimality, all available resources of a hybrid GPU- and/or MIC-accelerated cluster must be used. For that purpose we revisit the B&B@Grid approach [MMT07a] on heterogeneous clusters combining multi-core CPUs and GPUs. The original B&B@Grid approach is a fault-tolerant

6 Introduction

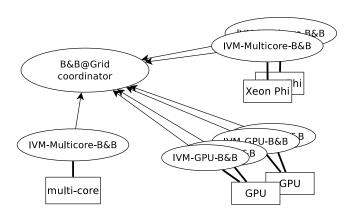

and highly scalable algorithm designed for computational grids. In this master-worker approach, workers in this algorithm are single-core processors. The design of the coordinator process which distributes work units across distributed compute nodes is revisited with the goal of including GPU devices, MIC and multi-core processors. We evaluate the proposed hybrid distributed B&B algorithm (HD-B&B) on a cluster with a total of 130 000 GPU cores located at the IDRIS<sup>2</sup> institute.

This thesis is organized in four chapters.

Chapter 1 introduces all the background and prerequisites necessary to the comprehension of the global document, namely the B&B algorithm, associated data structures and the FSP, QAP and *n*-Queens problems. The introduction of the algorithm and the test-cases is completed by a preliminary analysis of the sequential B&B algorithm. This introductory chapter also provides an overview of the different computing environments and the main features of the respective architectures. It contains a summary of the major parallelization strategies for B&B, a literature overview and synthesis of existing work dealing with parallel B&B classified by the target computational platform (GPU and MIC many-core processors, multi-core systems, computational grids and hybrid cluster systems).

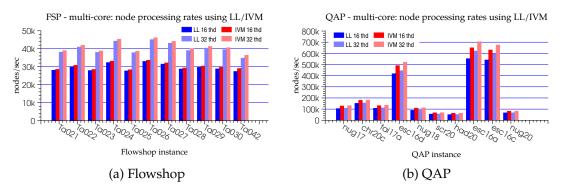

Chapter 2 contains our contributions targeting multi-core systems, including the many-integrated core (MIC) architecture. First, it introduces the sequential IVM-based B&B algorithm, followed by the parallel IVM-based B&B for multi-core processors and associated work stealing strategies. Then, it describes the GPU-accelerated multi-core algorithm and the extension of the work stealing strategies to the hybrid MC-B&B. After presenting the approach that consists in accelerating the bounding operator on GPU, its acceleration through vectorization is addressed. The presence of obstacles for the automatic compiler-assisted vectorization of the most time-consuming parts is discussed. The proposed solutions include a vectorizeable re-implementation of the lower bound for the FSP. In the last section of this chapter, a detailed experimental study evaluates and compares the presented algorithms. We evaluate the performance of the (accelerated) multi-core algorithm, comparing its linked-list and IVM-based implementations for the three test problems. The efficiency of the vectorization approaches and the proposed work stealing strategies is also evaluated and discussed. Finally, a scalability analysis on different multi-core processors concludes this chapter.

<sup>2.</sup> Institut du développement et des ressources en informatique scientifique

Chapter 3 deals with the GPU-centric implementation of B&B. It starts by discussing and exposing fundamental design choices and challenges related to the constraints imposed by the SIMD execution model and the hierarchical memory organization of GPUs. The remainder of this chapter is organized in three parts: (1) a description of both variants of the GPU-centric B&B algorithm (2) a description of the GPU-based work stealing approach, including its extension to multi-GPU systems and (3) the experimental evaluation of the GPU-B&B algorithm. First, the implementation of the GPU-centric B&B algorithm using a two-level parallelization is presented, providing details on the implementation of each operator. A particular focus is put on the issue of branch divergence: the sources of branch divergence are identified and thread-to-data mappings that help solving this issue are presented. Then, the challenges faced by the two-level GPU-B&B when dealing with fine-grained permutation problems are identified and an alternative, single-level variant of the algorithm is presented. The following section addresses the crucial issue of load balancing inside the GPU. It contains a general description of the approach, followed by a presentation of five work stealing strategies for GPU-based work stealing and an hierarchical work stealing approach for inter-GPU load balancing in multi-GPU systems. In the final part of this chapter, the performance of the proposed GPU-B&B algorithm is evaluated. Experiments are performed with the three test-cases on a multi-GPU system composed of four GPUs.

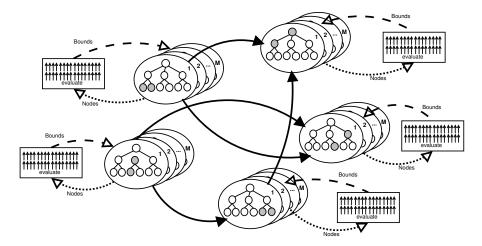

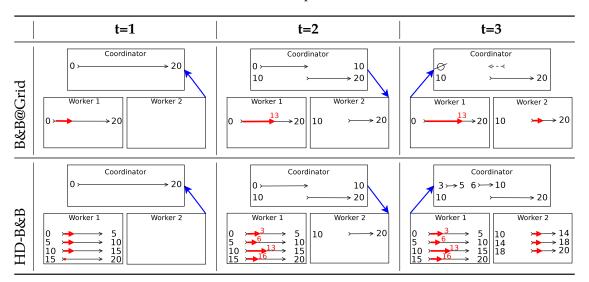

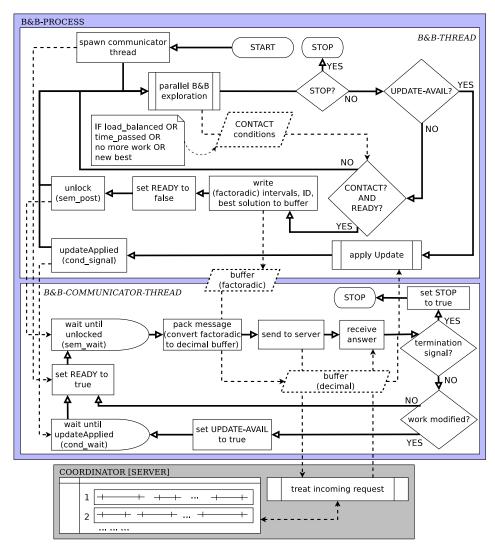

Chapter 4 presents a hybrid distributed B&B algorithm based on the B&B@Grid approach. It starts by describing the original B&B@Grid approach, upon which the proposed HD-B&B algorithm is build. In order to enable the use of multi-core and many-core-based workers in B&B@Grid, a redefinition of work units is proposed and the implications of this modification are discussed. A detailed description of the master and worker processes is provided, focusing on the revisited communication scheme. Finally, HD-B&B is experimented on three different GPU-enhanced clusters with up to 36 GPUs. The experimental evaluation includes scalability and stability analysis and concludes by a perspective on solving very large, unsolved FSP instances.

Finally, in Chapter 5 some concluding remarks are drawn and some future extensions of the proposed approaches are presented.

# Chapter 1

# Parallel Branch-and-Bound algorithms

| Conte | nts                                                     |                                         |    |

|-------|---------------------------------------------------------|-----------------------------------------|----|

| 1.1   |                                                         |                                         |    |

| 1.2   | Solving permutation combinatorial optimization problems |                                         |    |

| 1.3   | Branch-and-Bound algorithms                             |                                         |    |

|       | 1.3.1                                                   | Terminology and general description     | 12 |

|       | 1.3.2                                                   | Models for parallel Branch-and-Bound    | 14 |

|       | 1.3.3                                                   | Challenges in parallel Branch-and-Bound | 17 |

| 1.4   | Comp                                                    | outing Environments                     | 20 |

| 1.5   | 1.5 Related work                                        |                                         |    |

|       | 1.5.1                                                   | B&B for multi-core CPUs                 | 25 |

|       | 1.5.2                                                   | B&B for Graphics Processing Units       | 27 |

|       | 1.5.3                                                   | Hybrid and distributed parallel B&B     | 29 |

| 1.6   | 1.6 Test-cases: Permutation-based COPs                  |                                         |    |

|       | 1.6.1                                                   | Flowshop Scheduling Problem (FSP)       | 30 |

|       | 1.6.2                                                   | Quadratic Assignment Problem (QAP)      | 32 |

|       | 1.6.3                                                   | <i>n</i> -Queens Problem                | 33 |

|       | 1.6.4                                                   | B&B tree analysis of the test problems  | 34 |

# 1.1 Introduction

Combinatorial optimization problems (COP) consist in finding an object within a finite (or countably infinite) set which is optimal according to a given criterion.

Formally, a COP can be defined as a couple (X, f), where X is the search space and  $f: X \to R$  the objective function to be minimized<sup>1</sup>. Constraints that must be fulfilled by a feasible solution  $x \in X$  can be incorporated in the definition of the search space X or the objective function f. The objective function f takes its values in a totally ordered set, usually the set of real numbers or integers. The value f(x) measures the cost (e. g. quality, time, benefit) of solution  $x \in X$ . The goal is to find one or multiple solution(s)  $x^* \in X$  that is (are) feasible and for which  $f(x^*) \le f(x)$ ,  $\forall x \in X$ .

Many COPs can be modeled as optimization problems defined on sets of permutations. For instance, the solution of a permutation-based COP may represent:

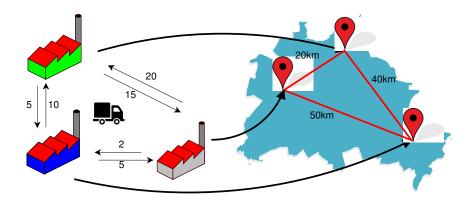

- a scheduling of a set of jobs, such that the completion time of a manufacturing product is minimized (a scheduling problem),

- an assignment of facilities to locations such that the placement cost is minimized (an assignment problem),

- a planning of routes such that the total length of the routes is minimized (a traveling salesman problem).

In such problems candidate solutions are permutations of n integers 1, 2, ..., n. The number n represents the number of jobs to schedule, the number of facilities to assign, etc. and is referred to as the *problem size*. As the set of permutations of size n is of cardinality n!, the search space associated with a permutation-based COP is usually very large, even for values of n that may seem moderate. While a permutation problem of size 5 could be easily solved by enumerating all 120 feasible solutions, this approach becomes clearly unfeasible for problems of size 50 or 100 which admit about  $3 \times 10^{64}$ , respectively  $10^{158}$  candidate solutions.

This thesis focuses on permutation-based COPs. In particular, we address NP-hard hard permutation-based COPs. Three permutation-based problems are used as test-cases: the Permutation Flowshop Scheduling Problem (FSP), the Quadratic Assignment Problem (QAP) and the *n*-Queens problem. A detailed introduction of these problems is provided later, in Section 1.6 of this chapter. Formally, the *n*-Queens problem is not an optimization problem, because it consists in finding (all) feasible solutions and no notion

<sup>1.</sup> Without loss of generality we consider the minimization case: the maximization of f is equivalent to the minimization of -f.

of optimality is defined. However, one may model this constraint satisfaction problem as a COP by defining the objective function as a constraint-checking function which assigns 0 to feasible and 1 to infeasible solutions.

# 1.2 Solving permutation combinatorial optimization problems

Approaches to solving COPs can be classified into two main categories: exact and approximate methods [Tal09]. Approximate methods aim at finding near-optimal solutions in a reasonable amount of time, exploring parts of the solution space where good quality solutions are expected to be found. Among the most used approximate methods are metaheuristics. Roughly described, metaheuristics are general-purpose optimization methods that require limited problem-specific information. Metaheuristics are either single solution-based or population-based. While the former consider a single initial solution which is iteratively improved (e. g. Hill-Climbing, Simulated Annealing), the latter operate on a set of solutions which are collectively or independently improved (e. g. Evolutionary Algorithms, Ant Colonies). However, heuristics and metaheuristics provide no error quantification. Even if a heuristic method finds the/an optimal solution it does not provide a certificate of optimality. Knowledge of exact solutions to benchmark instances for COPs is therefore valuable for assessing the quality of a heuristic method for a class of problems. Also, some highly cost-critical applications may benefit from closing even small optimality gaps.

While high-quality solutions to COPs can often be found within a few seconds, exact solving may require a huge amount of time and computational resources. This is due to the enumerative nature of exact methods, which require, in the worst case, a number of iterations which grows exponentially with the problem size. The most naive exact method consists in completely enumerating the solution space. For obvious reasons this is only feasible for very small problem sizes. A more sophisticated and widely used exact method is the branch-and-bound (B&B) algorithm. B&B dynamically builds and explores a tree using four operators: branching, bounding, selection and elimination. The B&B approach recursively decomposes the problem into smaller subproblems for which lower bounds on their optimal solution are computed. Based on these lower bounds the elimination operator discards unpromising subproblems which have lower bounds greater than the best solution found so far. This is also known as *pruning* of tree branches or *fathoming* of parts of the search space. A detailed description of the B&B algorithm is provided in Section 1.3 of this chapter.

Many other exact resolution methods are B&B-like tree-search algorithms. Besides

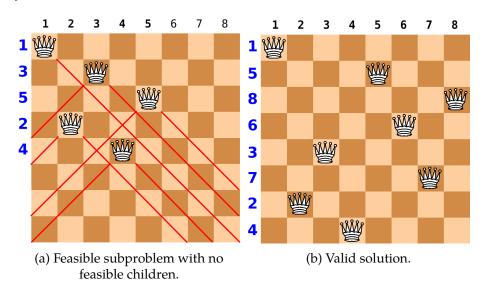

simple B&B there are two main variants: branch-and-cut (B&C) and branch-and-price (B&P). There are other less known variants of B&B such as branch-and-peg [GGS04], branch-and-win [PC04], and branch-and-cut-and-solve [CZ06]. This list is certainly not exhaustive. It is also possible to consider a divide-and-conquer algorithm as a B&B algorithm, as it is enough to remove the pruning operator from B&B. Some authors consider B&C, B&P, and the other variants as different algorithms than B&B and use B&X to refer to algorithms like B&B, B&C, B&P, etc. In this document B&B refers to simple B&B or any of its variants. Backtracking is a fundamental paradigm frequently used to solve constraint satisfaction problems and can also be interpreted as a special case of a depth-first search (DFS) B&B algorithm. The difference is that backtracking does not use a bounding operator to detect unpromising nodes. However it may incorporate pruning mechanisms, for instance based on evaluating the feasibility of a subproblem, which can be seen as a binary bounding function.

Compared to complete enumeration the pruning of branches significantly reduces the size of the explored tree. However, for many COPs the execution time of B&B significantly increases with the input size and only small or moderately sized instances can be practically solved with sequential algorithms. For this reason, the use of parallel computers is an attractive way to deal with larger instances of COPs. One might argue that there is no point in applying B&B to NP-hard COPs, unless we have an exponential number of processors for parallel processing. However, the approach may actually perform well for a given problem and parallel computing may provide the necessary computing power to solve instances up to a certain size. Running times for B&B are very hard to predict because it requires an estimate of the tree-size. This means that the decision whether an exact algorithm for a given problem is useful, can only be founded on empirical data.

The combination of approximate and exact methods is a promising approach. For instance, metaheuristics can be used to accelerate the search process of B&B, and B&B may provide candidate solutions that improve the quality of the approximate method. As the focus of this thesis is put on the efficient design of B&B on parallel computers, we refer the reader to [Meh11; Tal09] for more information on this subject.

# 1.3 Branch-and-Bound algorithms

This section provides a comprehensive overview of the B&B algorithm. As we focus on permutation-based problems, it is assumed in the following that B&B is applied to solve a permutation problem.

# 1.3.1 Terminology and general description

The B&B algorithm proceeds by implicit enumeration of all the solutions of the problem being solved. Exploration of the space of potential solutions (search space) is performed by dynamically building a tree where:

- The **root node** represents the initial problem to be solved (the search space *X*).

- **Internal nodes** represent subproblems of the initial problem (subspaces  $S \subset X$ ).

- Leaf nodes are possible solutions.

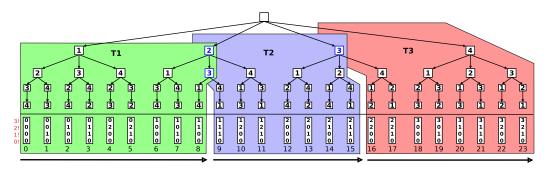

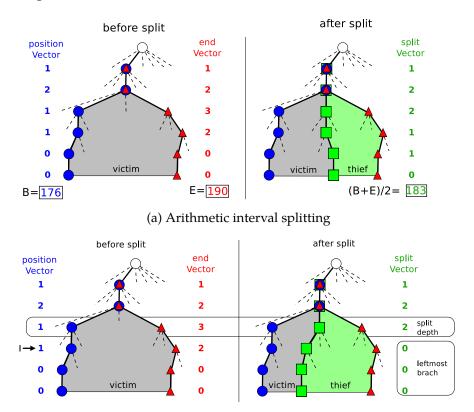

A complementary and useful point of view is to consider B&B as a method for iteratively constructing solutions. Suppose B&B is applied to solve a permutation problem of size 4 which consists in finding an optimal scheduling of the jobs {1,2,3,4} <sup>2</sup>. If none of the jobs is fixed at a particular position, all 4! permutations can be attained from this state. This initial state corresponds to the root node and will be denoted /1234/. The jobs written before the first slash symbol ("/") are scheduled at the beginning, jobs behind the second ("/") symbol are scheduled at the end, and jobs in between are not yet scheduled. A possible way of constructing candidate solutions is to fix each of the unscheduled jobs successively at the first, second, third position, and so on. At the first level this yields four internal nodes 1/234/,2/134/,3/124/,4/123/. The number of scheduled jobs in an internal node is called its *depth* or its *level*. A leaf node is a node in which all jobs are scheduled, for example 234//1, or simply 2341. Both points of view, recursive "partitioning of search space" on the one hand and iterative "construction of solution" on the other, provide equivalent descriptions of the B&B tree and vocabulary related to both is used interchangeably.

All nodes generated and not yet processed are kept in a data structure. In the beginning this data structure contains only the initial problem. The algorithm saves the best solution found so far (also called the *incumbent*) as well as the associated cost (also referred to as the *upper bound*). The latter is either initialized at  $\infty$  or at the cost of a feasible solution known beforehand (for instance, found by an approximate method). This upper bound can be improved from an iteration to another. At each iteration of the algorithm:

The bounding operator is used to compute a lower bound on the minimal cost

of a subproblem. In order to include the possibility of applying the algorithm

to constraint satisfaction problems, the bounding operator is frequently called

<sup>2.</sup> Throughout the remainder of this thesis we will refer to the elements of a permutation as jobs.

node evaluation function in this document. The node evaluation function solely depends on the problem being solved. There are essentially two possible modes of evaluation, called lazy and eager evaluation [CP99]. In the eager evaluation mode bounds are computed as soon as nodes are generated, i.e. bounding is called after the branching operator. In the lazy evaluation mode bounds are only computed if really necessary, i.e. after selection and before the branching operator. The algorithms presented in this thesis use the eager evaluation mode.

- The **pruning operator** uses the lower bound value of a subproblem to decide whether it is kept in the data structure for further exploration or discarded from the search. Infeasible subproblems and problems whose lower bound is greater than the best solution found so far can be eliminated.

- The **branching operator** divides a subproblem into several smaller, pairwise disjoint subproblems. In general, this is achieved by partitioning the search space into smaller subspaces on which the same optimization problem is defined. The internal nodes generated by branching a node *A* are called *A's children*. For permutation problems, a possible branching scheme consists in assigning all untried alternatives to a fixed position in the permutation. This is known as polytomic branching [Rou87], in contrast to dichotomic branching, which generates two children per node. The following polytomic branching scheme is used in this work. Two sets of children nodes are generated, by fixing jobs at the first free position at the beginning and at the end, respectively. Both sets are evaluated and the set which is likely to lead to a smaller B&B tree is retained (based on a heuristic estimate). Generated subproblems are added to the data structure which is used to store unexplored subproblems.

- The **selection operator** chooses the next subproblem to be expanded among all pending subproblems. This choice follows a predefined exploration strategy. The selection of a node could be based on its depth, which leads to a depth-first exploration strategy (DFS). In DFS the entire subtree rooted in the current node is fathomed before another node is processed. A best-first selection strategy could also be used. It is based on the presumed capacity of the selected node to yield good solutions. However, memory requirements for pure best-first search are often excessive. DFS prescribes no particular order of exploration among sibling nodes. Therefore, nodes on the same level can be processed in increasing order according to their lower bounds. Unless indicated differently the B&B algorithms presented are based on this best-bound DFS exploration strategy.

Whenever the algorithm reaches a valid solution, this latter is evaluated and compared to the best solution found so far. If an improvement of this latter is possible, it is updated. The algorithm stops when the selection operator fails to choose a node to expand because the pool of pending nodes is empty. At the end of this dynamic exploration process the best found solution is proven to be optimal.

The size of the explored B&B tree strongly depends on the quality of the bounding operator, i.e. the tightness of the lower bounds. Moreover, for a given bounding function the tree size also depends on the rate at which the upper bound decreases towards the optimal cost - in other words, on the search strategy defined by the selection operator.

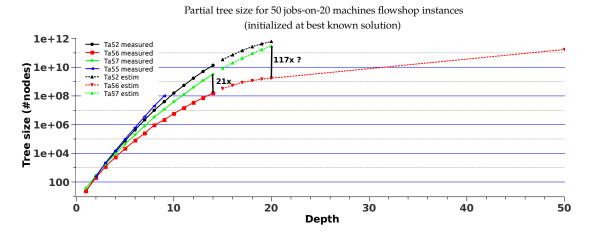

If the algorithm is initialized at an optimal solution  $x^*$ , then B&B explores exactly the nodes x for which  $LB(x) < f(x^*)^3$ . Independently from the search strategy, these nodes must be explored in order to prove the optimality of  $x^*$ . The tree formed by these (critical) nodes is called the *critical tree*.

### 1.3.2 Models for parallel Branch-and-Bound

The parallelization of B&B is well-studied and different classifications have been proposed [Mel05; TdB92; GC94]. The taxonomy presented in this subsection is the one from [Mel05] which is based on the classification of Gendron and Crainic [GC94]. Four models are identified: (1) parallel tree exploration, (2) parallel evaluation of bounds, (3) parallel evaluation of a bound, and (4) multi-parametric.

### Parallel tree exploration model

In the parallel tree exploration model several disjoint search subspaces (branches of the B&B tree) are explored in parallel. This means that all four operators, selection, branching, bounding and pruning, are applied in parallel to different subproblems. This can be done either synchronously or asynchronously. In synchronous mode the B&B algorithm has several phases in which the B&B processes perform their exploration independently. The B&B operators are applied in parallel to multiple data (e.g. work pools, nodes, lower bounds). Between these phases exploration processes are synchronized and can exchange information, such as the best solution found so far. In asynchronous mode the B&B processes communicate in an unpredictable manner.

Among the four models, the parallel tree exploration model is the most frequently used. One of the reasons is that the degree of parallelism in this model can be very

<sup>3.</sup> Or  $LB(x) \le f(x^*)$ , if the goal is to find *all* optimal solutions, not only *one*. For all problems considered in this thesis, except n-Queens, the goal is to find one optimal solution and/or prove its optimality.

high, especially when solving large instances. Each B&B process holds one or several work units which correspond to subspaces of the total search space. The number of explorers that can be kept busy simultaneously therefore depends on (1) the rate at which new subproblems are generated and (2) the efficient assignment of subproblems to B&B processes. In both modes, synchronous and asynchronous, load balancing is one of the main issues raised by this model. Indeed, as the B&B tree is highly irregular, some branches contain much more work than others. Among other issues are the placement and management of the set of pending subproblems. Especially in distributed contexts, the communication of the best solution found so far and termination detection also become challenging.

This parallelization model alters the order in which nodes are explored and therefore the size of the explored tree. A parallel tree exploration B&B may indeed find an optimal solution much faster than its sequential counterpart, or, on the contrary, expand much more nodes to find such a solution. In other words, in parallel tree-search B&B the number of expanded non-critical nodes does not only depend on the search strategy, but also on other factors, like work load distribution and communication schemes. Therefore, in synchronous and asynchronous parallel tree exploration B&B speedup anomalies may occur [DKT95].

Aside from the potentially very high degree of parallelism, the popularity of this parallelization approach is also due to its genericity. As this model does not affect the bounding operator, it can be applied to any COP without prior knowledge of its characteristics, at least in principle. Therefore, this model is used by most frameworks that aim at facilitating the implementation of B&B algorithms. This parallelization model corresponds to the "type 2" (tree-based) parallelism in the classification of Gendron and Crainic [GC94]. It falls in the category of "high-level" parallelization in the classification of Trienekens and de Bruin [TdB92].

### Parallel evaluation of bounds model

Another source of parallelism is the parallel evaluation of bounds. After the decomposition of a node all its children may be evaluated in parallel. The degree of parallelism in this model depends on the branching scheme and varies according to the depth of a node in the tree. In order to reach a high degree of parallelism the selection and branching operators can be applied multiple times until a pool of children nodes is large enough to be efficiently evaluated in parallel [Cha13]. This model leads to more fine-grained parallelism than the parallel tree exploration model. It is well-suited in cases where the evaluation is costly. Moreover, if the node evaluation is regular (in the sense that

each node represents approximately the same amount of work), it is well-suited for Single Instruction-Multiple Data (SIMD) processing. This model can be nested inside the parallel tree exploration model. As the previous model, this model is generic in the sense that it requires no knowledge of the particular problem being solved. If nodes are evaluated directly after their generation, this model does not change the amount of work done or the shape of the B&B tree.

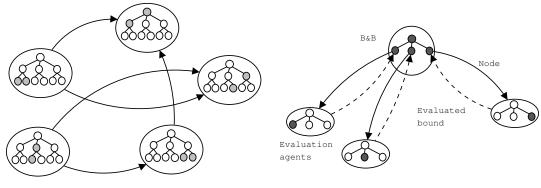

- (a) Parallel tree exploration model

- (b) Parallel evaluation of bounds model

Figure 1.1: Illustration of main parallelization models used in this thesis.

#### Parallel evaluation of a bound/solution model

At an even lower level, the evaluation of a bound or solution itself may be parallelized in some cases. This depends on the possibility of parallelizing the node evaluation function that is used. As this model only modifies the bounding operator it can be nested inside both previous models to add a third level of parallelism. For problems with a very compute intensive bounding function the model may also be used alone. The parallel evaluation of a bound model has no impact on the search trajectory. Like the previous model, it is also known as "node-based" [GC94] or "low-level" [TdB92] parallelization.

## Multi-parametric model

Of the four identified models the multi-parametric model is the less studied one. It is a coarse-grained parallelization that consists in launching multiple independent B&B processes that explore the same search space with different algorithm parameters. For instance, the different B&B algorithms may use different branching schemes or selection strategies. In [KK84] only one of the B&B algorithms uses the actual current upper bound (UB) while the others are  $\epsilon$ -approximations using  $UB - \epsilon$  ( $\epsilon > 0$ ) as upper bound. In this

model redundant explorations are very likely to occur.

### 1.3.3 Challenges in parallel Branch-and-Bound

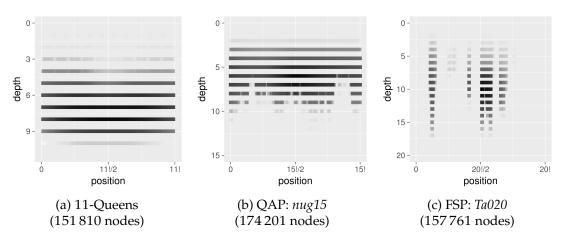

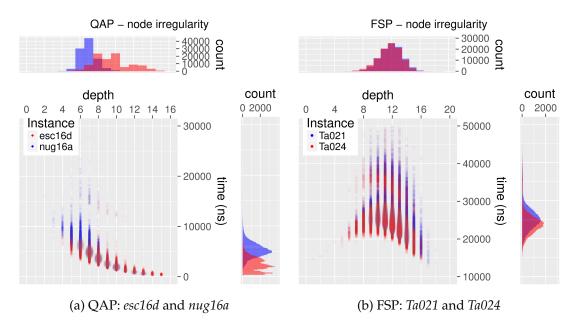

Irregularity. Most of the difficulties that arise when implementing a parallel B&B algorithm are direct consequences of the algorithm's irregularity. In each of the four presented parallelization models irregularity manifests itself in a different way. Because of the unpredictable pruning of branches, some subproblems require much more computation time than others, which leads to load imbalance. As subproblems are dynamically assigned to processing units at runtime, dynamic load balancing is a requirement for an efficient exploitation of the available computing resources. The parallel evaluation of nodes yields a more fine-grained and often more regular workload. However, the evaluation of nodes may require a variable amount of time, depending on the problem being solved and the depth of each node.

The search space management as well as the problem-dependent node evaluation subroutines are often characterized by highly irregular control flows. In a permutation problem the memory accesses during node evaluation depend on the partially constructed solution. Many accesses are therefore masked and have irregular and unpredictable strides. Diverging instruction flows and random memory access patterns are well-known to be major obstacles to SIMD processing. This may compromise the efficient usage of GPUs and/or vector processing units - two of the main factors that have increased the performance of HPC systems over the last decade.

**Work pool management.** We call *work pool* the data structure that is used to store generated and not yet evaluated subproblems. A subproblem is usually implemented as a structure containing all information necessary for its evaluation. The role of the work pool is essentially to allow the insertion/retrieval of subproblems. Moreover, the work pool may maintain subproblems in a certain order, facilitating the implementation of a search strategy. For instance, DFS corresponds to processing nodes in last-in first-out (LIFO) order and is therefore naturally implemented by a stack. Best-first search is usually implemented using priority queues. In general, priority queues offer good flexibility, because it is enough to change the sorting criterion to implement another search strategy.

In parallel B&B there are different strategies for implementing the work pool. One approach is to use a single centralized work pool, concurrently accessed by all workers to pick subproblems for branching/evaluation. In shared memory systems all workers concurrently access the same work pool to get subproblems. After branching the subproblem each worker (thread) inserts the evaluated and non-pruned children into the pool. In

single-pool approaches synchronization between workers to gain exclusive access to the pool is inevitable. These concurrent accesses may create a bottleneck and memory contention, limiting the scalability of the approach. In distributed memory configurations the single pool strategy is implemented using the master-worker paradigm. Again, the scalability of this approach is limited as the master process becomes a bottleneck.

Multiple-pool approaches aim at solving this issue by using several pools. There are variants of multiple pool B&B algorithms. The most popular are collegial, grouped and mixed [GC94]. In the collegial variant each worker has its private pool. The grouped approach uses one shared pool for a group of workers and the mixed variant combines both approaches using a hierarchy of pools. Multiple pool strategies alleviate the bottleneck problem that occurs in single-pool approaches but they raise the issue of balancing the workload between multiple pools. Also, the sharing of knowledge among workers, like the best known solution and termination detection, become non-trivial. Generally speaking, multiple pool approaches require more sophisticated communication models than single pool approaches.

**Load balancing.** While the single work-pool approach implicitly balances the work load among workers, multiple-pool approaches require explicit dynamic load balancing. Over the last decade work stealing [BL99] has been widely adopted as a standard way to distribute tasks among workers. In the context of B&B tasks are subproblems (nodes of the B&B tree). In a work stealing algorithm, each thread uses a double-ended queue (deque) for storing tasks. Locally, a thread uses the tail of its deque as a stack, popping tasks to execute and pushing newly generated tasks onto the stack. When a thread's deque is empty it becomes a *thief* and steals tasks from the head of another thread (called *victim*). Expressed in terms of a multiple-pool B&B algorithm, when a work pool is empty, one thread associated with the pool steals nodes from another work pool.

There are mainly two reasons for using deques in work stealing approaches. The first is that stealing tasks from the head of the deque may allow the victim thread to continuously work on the deque's tail without being slowed down by steal operations (work-first principle [FLR98]). A first non-blocking work stealing deque that prevents contention during concurrent operations was proposed by Arora, Blumofe, and Plaxton [ABP01]. Dinan *et al.* [DLS+09] propose a work-stealing deque partitioned into a local and a public portion using a periodically updated pointer. This data structure, called a split-queue, allows lockless accesses to both portions of the deque and requires locking only for updating the split-pointer. The scalability of this work stealing using split-queues has been demonstrated on up to 8 192 distributed processing cores. In [ACR13] it is

reported that concurrent deque operations require expensive memory fences, which has led to recent interest in implementations of work stealing with non-concurrent (private) data structures [ACR13; vDvdP14]. The second reason concerns the granularity of the work stealing mechanism. In B&B, like in many task parallel applications, nodes at the bottom of the task stack (i.e. older tasks) represent a larger amount of work as recently spawned tasks on top of the stack. Granularity (i.e. the number of nodes that are stolen) is one of the characteristic features of a work stealing strategy, together with the policy of selecting the work stealing victim. A recent survey of work stealing methods for scheduling parallel computations can be found in [YH17].

**Data Structures.** The two previous paragraphs illustrate the central role of the data structure used for the storage of the huge number of subproblems. As mentioned, work pools are usually implemented as stacks, deques or priority queues. Operations on the B&B tree, like node selection, insertion of branched nodes and work transfers between multiple pools are implemented as push and pop operations on dynamic sized data structures. We generically refer to this type of dynamic data structure as *linked-lists* (LL).

Using such data structures has many advantages. For instance, it is relatively easy to adapt B&B to different problems by changing the definition of a node. Similarly, the search strategy can be modified easily, for instance by using a different sorting criterion for a priority queue. However, departing from the general case of B&B, the particular structure of a class of problems can be exploited, making it possible to use other types of data structures.

For example, a DFS-B&B applied to a 0-1 integer COP could use a single bit array of length n (problem size) and an integer d indicating the current depth of the search. The values of the bit array up to depth d represent the current partial solution and on each level the algorithm successively tries the alternatives 0/1. Branching consists in incrementing the current depth d. Backtracking is performed by decrementing d and incrementing the bit array. The basic idea is that it is not necessary to explicitly store all frontier nodes, because they can be deduced from the current active node. It should be emphasized that this is possible because the maximal B&B tree (which would be explored if no pruning was used) is known in advance, and the exploration order (DFS) is deterministic.

For permutation problems the structure of the search space can also be exploited to design alternative data structures for DFS-B&B. One example are bitsets, which allow a very compact implementation of DFS [SRR08; Ric97]. For instance, DFS-B&B for permutation problems can be implemented using only one vector and two integers for

the search procedure. A vector is used to store the current partial solution and the first integer indicates the current depth of the search. The second integer is seen as a bitset that keeps track of already scheduled jobs. The bit k of this second integer is set if and only if job k is already scheduled. Searching the B&B tree in depth-first order is performed by incrementing the positions of the vector while using the integer to check whether a partial solution is valid. Such a bitset-based approach has a very small and constant memory footprint. Bitset-based sequential implementations of backtracking can be extremely fast, for instance for solving the n-Queens problem [Zon02; PE17; Som]. However, it is unclear how dynamic load balancing could be performed with such bitset-based data structures. Also, as only one node is generated at once, it does not seem possible to use the parallel evaluation of bounds model.

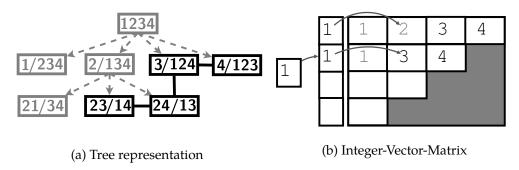

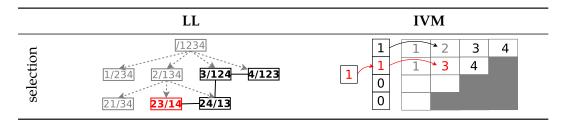

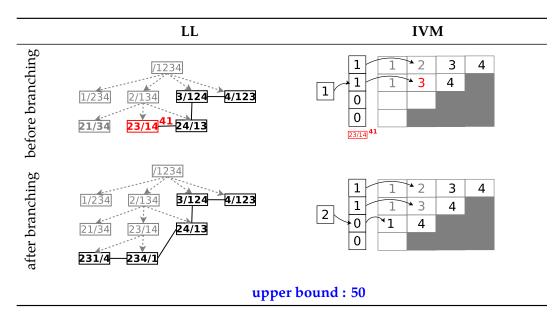

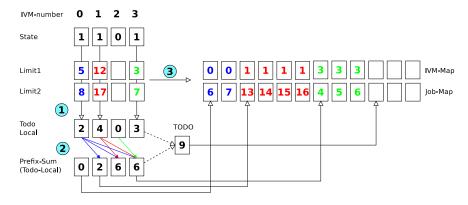

The so-called Integer-Vector-Matrix (IVM) data structure [MLMT14] is an innovative data structure dedicated to solving permutation-based COPs. In terms of flexibility and compactness, IVM can be seen as a compromise between bitsets and linked-lists. IVM is more flexible than bitsets, but less compact. It is more compact than LL-based data structures, but offers less flexibility. IVM uses an integer to indicate the current depth of the search, a vector to indicate the path of the current node, and a matrix to store the unscheduled jobs at each level. Like bitset-based B&B, IVM-based B&B can be performed with constant memory requirements. IVM also allows to define splittable work units intervals - which can be exchanged between workers to implement dynamic load balancing. In [Ler15] the advantages of using IVM in multi-core B&B algorithms, compared to conventional linked-list, are shown theoretically and experimentally. The reported results show that, for  $20 \times 20$  FSP instances, IVM-based B&B consumes on average 60 times less memory, requires about 9 times less CPU time for pool management, performs less context switches and produces less page faults than its LL-based counterpart. However, IVM does not offer the same flexibility as LL-based data structures: as mentioned, IVM is dedicated to permutation-problems and depth-first search.

All algorithms presented in this thesis are based on the IVM data structure. A detailed description of IVM and the IVM-based B&B algorithm are provided in Section 2.2.

# 1.4 Computing Environments

High Performance Computing (HPC) technologies are evolving at high pace and architectures of computing systems become increasingly complex. The programmer has to understand the hierarchical organization of these machines in order to take advantage of the full computing power they are able to provide. A detailed technical description of

the hardware used in this thesis, or a discussion of current and future developments in HPC goes beyond the scope of this chapter. However, the design of algorithms presented in this thesis is, to a large extend, guided by the architecture of the targeted computing platform. Therefore, this section attempts to provide some context, giving a brief outline of current trends and challenges in HPC and a succinct description of the hardware used in this thesis. There is abundant literature discussing the impressive evolution of computing systems over recent years, for example [GR14; EBS+11; Dre07; KDK+11; Mär14; OHL+08], to cite only a few. Appendix A.3 lists the main technical specifications of computing devices used in this document.

Energy efficiency of computing systems has become very important. When CPUs had a single processing core, performance increase was mainly achieved by increasing the clock frequency and through improved instruction pipelining. As increasing frequencies led to unsustainable power consumptions, over the past ten years performance was improved by using multiple cores running at slightly lower frequencies. This is made possible by the shrinking manufacturing process (2004: 90 nm, 2017: 14 nm) and the subsequent growth of transistor count. In the latest edition (June 2017) of the biannual TOP500 [16] ranking of the worlds fastest supercomputers no system has less than 4 CPU cores per socket and more than half of the systems in the TOP500 list have at least 12 cores per socket or more. The x200 generation of Intel's Xeon Phi processors (code-named Knight's Landing) are composed of more than 60 cores operating at a base frequency of 1.4 GHz each.

In order to increase core-level performance, in recent years the trend has been to use wider SIMD vector instructions. Most modern multi-core processors have instruction set extensions, allowing to operate simultaneously on multiple data objects residing in the same registers. Therefore it becomes increasingly important to exploit data parallelism (SIMD) besides instruction-level parallelism (ILP) and thread-level parallelism (TLP). For instance, Intel's Xeon Phi processors provide 512-bit wide vector registers, allowing up to 16 single-precision operations to be performed in one clock cycle. Launched in 2008, the AVX (up to 256-bit) vector extensions for x86 processors can substantially improve per-core performance, provided the compute-intensive portions of the executed code allow SIMD processing.

Including all these levels of parallel processing capability, the theoretical single-precision peak performance of a multi-core processor is given by:

#cores × clock rate × #instructions/cycle

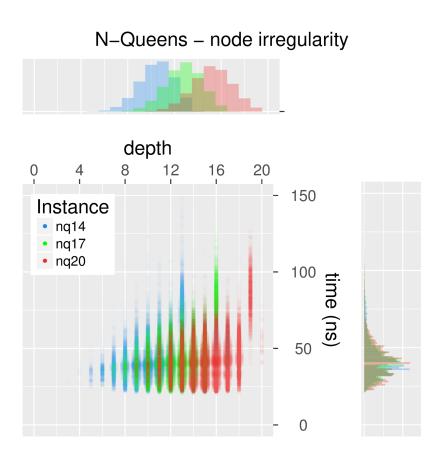

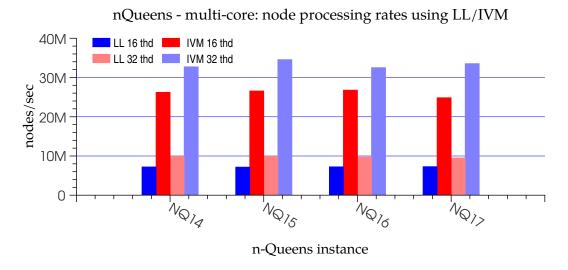

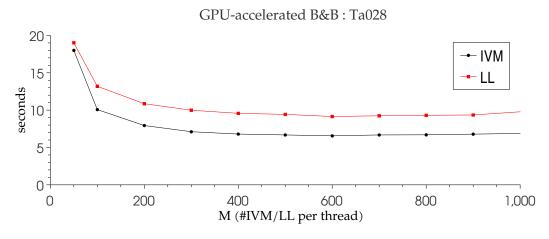

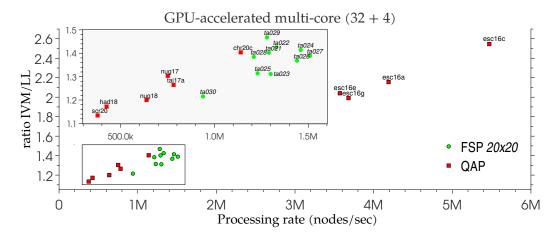

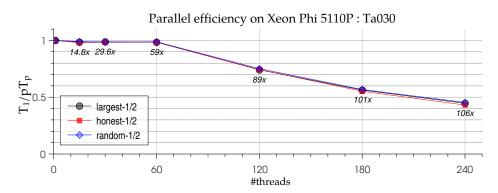

This shows that, without efficient exploitation of thread-level parallelism and, if possible, data parallelism one can only achieve a small fraction of the theoretical peak performance.