# Revisiting Wide Superscalar Microarchitecture

#### Andrea Mondelli

#### ▶ To cite this version:

Andrea Mondelli. Revisiting Wide Superscalar Microarchitecture. Hardware Architecture [cs.AR]. Université de Rennes, 2017. English. NNT: 2017REN1S054. tel-01597752v2

# HAL Id: tel-01597752 https://inria.hal.science/tel-01597752v2

Submitted on 18 Jan 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE / UNIVERSITÉ DE RENNES 1

sous le sceau de l'Université Bretagne Loire

pour le grade de

#### DOCTEUR DE L'UNIVERSITÉ DE RENNES 1

Mention: Informatique

Mathmatiques et Sciences et Technologies de l'Information et de la Communication (MATHSTIC)

présentée par

# Andrea Mondelli

préparée à l'unité de recherche INRIA Institut National de Recherche en Informatique et Automatique Université de Rennes 1

Revisiting

Wide

Superscalar

Microarchitecture

Thèse soutenue à Rennes le 12 Septembre 2017

devant le jury composé de :

Steven Derrien

Professeur à l'Université de Rennes 1 / Président

Bernard Goossens

Professeur à l'Université de Perpignan / rapporteur

Smail Niar

Professeur à l'Université de Valenciennes/rapporteur

Karine Heydemann

Maître de conference / examinateur

André Seznec

Directeur de recherche, INRIA Rennes / directeur de thèse

Pierre Michaud

Chargé de recherche, INRIA Rennes / co-directeur de thèse

Dear Mary, do you [know who] will be on the boats? I'm still in Gaza, waiting for you. I will be at the boat to greet you. **Stay human**. Vik.

Vittorio Arrigoni

# Remerciements

# Contents

| R | ésum | é en F | rançais                                             | 5  |

|---|------|--------|-----------------------------------------------------|----|

| 1 | Intr | oducti | ion                                                 | 9  |

|   | 1.1  | Purpo  | ose of this work                                    | 9  |

|   | 1.2  | -      | ibutions                                            | 10 |

|   | 1.3  |        | nization                                            | 12 |

| 2 | Stat | e of t | he Art                                              | 13 |

|   | 2.1  | From   | Pipeline to Superscalar                             | 13 |

|   | 2.2  |        | mance Technique of Superscalar Processors           | 16 |

|   |      | 2.2.1  | Instruction Level Parallelism                       | 16 |

|   |      | 2.2.2  | The Branch Predictor                                | 18 |

|   |      | 2.2.3  | The Register Renaming                               | 18 |

|   |      | 2.2.4  | Out-of-Order Execution                              | 20 |

|   | 2.3  | Wide-  | issue complexity                                    | 22 |

|   |      | 2.3.1  | Limits of performance scaling                       | 22 |

|   |      | 2.3.2  | Impact of critical components                       | 24 |

|   |      | 2.3.3  | Front-end bandwidth                                 | 25 |

|   |      | 2.3.4  | Level-one data cache                                | 25 |

|   |      | 2.3.5  | Bypass network paths                                | 26 |

|   |      | 2.3.6  | Load/Store queues                                   | 27 |

|   |      | 2.3.7  | Reduce the complexity by limiting pipeline activity | 29 |

|   | 2.4  | Cluste | ering                                               | 29 |

|   |      | 2.4.1  | Clustered microarchitectures                        | 30 |

|   |      | 2.4.2  | Issue Buffer                                        | 31 |

|   |      | 2.4.3  | Steering                                            | 32 |

|   |      | 2.4.4  | Write Specialization                                | 35 |

|   |      | 2.4.5  | Bypass network and intercluster delay               | 37 |

|   |      | 2.4.6  | Clustering in Commercial Superscalar Processors     | 37 |

|   |      | 2.4.7  | Clustered VLIW/DSP architectures                    | 39 |

|   | 2.5  | Energ  | v saving exploiting loops                           | 40 |

|   |      | 2.5.1    | Saving loop energy in the front-end                           | 40 |

|---|------|----------|---------------------------------------------------------------|----|

|   |      | 2.5.2    | Using a dedicated cache for loops                             | 41 |

|   |      | 2.5.3    | Saving loop energy in the back-end                            | 44 |

|   |      | 2.5.4    | Loop accelerators                                             | 45 |

|   |      | 2.5.5    | Industrial adoption of loop cache solutions                   | 46 |

| 3 | Wio  | de Issu  | ue Clustered Microarchitecture                                | 47 |

|   | 3.1  | A case   | e of increasing single-thread IPC                             | 47 |

|   | 3.2  |          | imental Framework                                             | 49 |

|   |      | 3.2.1    | Simulation Setup                                              | 49 |

|   |      | 3.2.2    | Benchmarks                                                    | 50 |

|   |      | 3.2.3    | Baseline Microarchitecture                                    | 51 |

|   | 3.3  | Poten    | tial IPC gains from a more complex superscalar microarchi-    |    |

|   |      | tectur   | e                                                             | 54 |

|   | 3.4  | Dual-    | Clustered Configurations                                      | 55 |

|   |      | 3.4.1    | Dual-Cluster with baseline instruction window size            | 57 |

|   |      | 3.4.2    | Dual-cluster with double instruction window                   | 57 |

|   |      | 3.4.3    | Analysis                                                      | 60 |

|   |      | 3.4.4    | Possible steps toward the proposed dual-cluster configuration | 62 |

|   | 3.5  | Energ    | y Considerations                                              | 63 |

|   |      | 3.5.1    | Static EPI                                                    | 63 |

|   |      | 3.5.2    | Gating intercluster communications for reduced dynamic EPI    | 64 |

|   | 3.6  | Summ     | nary                                                          | 65 |

| 4 | Exp  | oloiting | g loops for reducing energy in a superscalar out-of-order     |    |

|   | core | 9        |                                                               | 67 |

|   | 4.1  | Baseli   | ne and Experimental Setup                                     | 68 |

|   | 4.2  | Loop     | Buffer and Loop Detector                                      | 69 |

|   |      | 4.2.1    | Description                                                   | 70 |

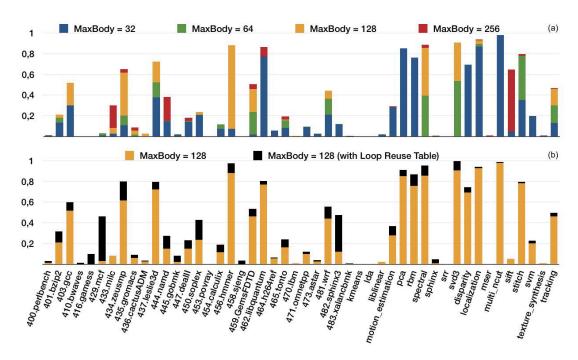

|   |      | 4.2.2    | Loop buffer size                                              | 73 |

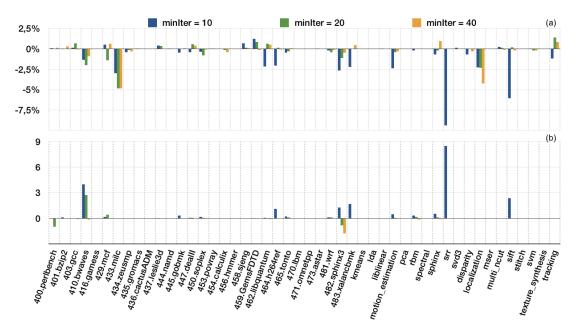

|   |      | 4.2.3    | Tuning MinIter                                                | 74 |

|   | 4.3  | Redur    | ndant Micro-Op Removal                                        | 76 |

|   |      | 4.3.1    | Proposed mechanism                                            | 76 |

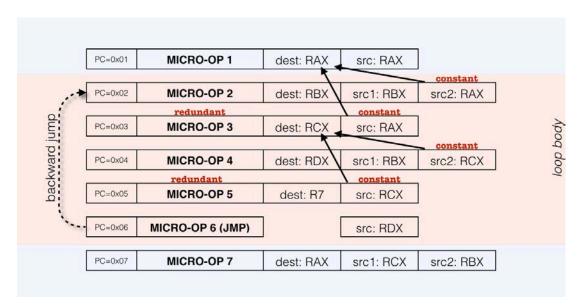

|   |      | 4.3.2    | Identification of redundant micro-ops                         | 77 |

|   |      | 4.3.3    | Modification of register renaming                             | 78 |

|   |      | 4.3.4    | Loads and stores                                              | 79 |

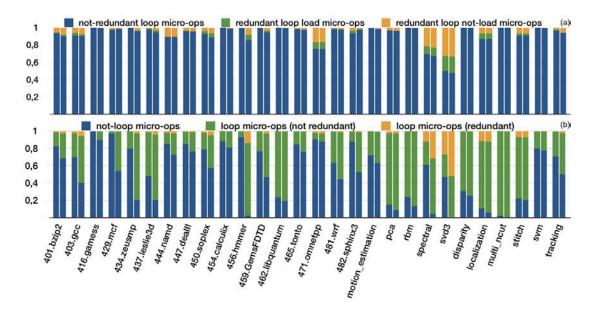

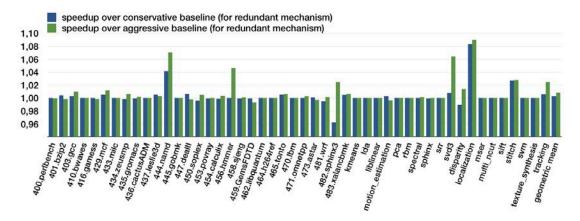

|   |      | 4.3.5    | Simulation Results                                            | 80 |

|   |      | 4.3.6    | Compiler Optimization impact: a case study                    | 82 |

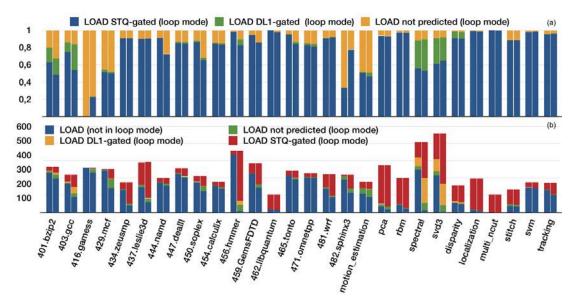

|   | 4.4  | Reduc    | ging the energy of loads                                      | 86 |

|   |      | 4.4.1    | Speculative load execution                                    | 86 |

|   |      | 4.4.2    | DL1/STQ gating?                                               | 88 |

| CONTENTS | 3 |

|----------|---|

|----------|---|

|    |       | 4.4.3 Store Queue and DL1 gating in Loop Mode      | 90 |

|----|-------|----------------------------------------------------|----|

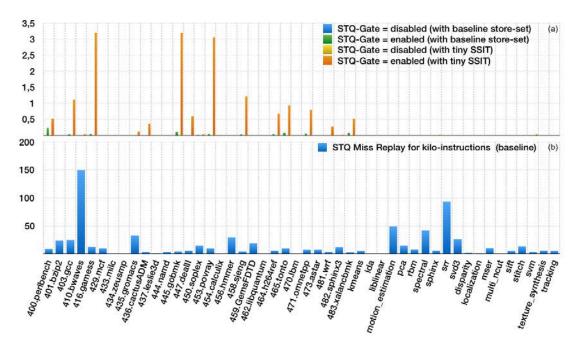

|    |       | 4.4.4 STQ gating alone                             | 91 |

|    |       | 4.4.5 DL1 gating alone                             | 91 |

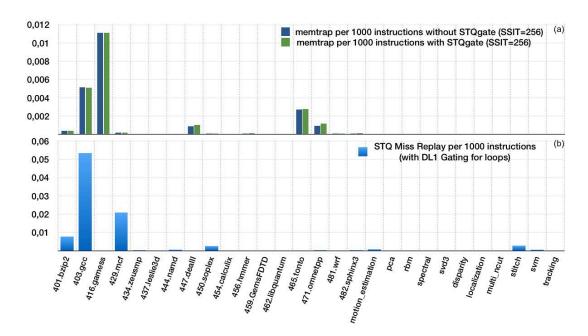

|    |       | 4.4.6 STQ gating and DL1 gating combined           | 92 |

|    |       | 4.4.7 Gating the memory dependence predictor table | 94 |

|    | 4.5   | Summary                                            | 95 |

| 5  | Con   | clusion                                            | 97 |

|    | 5.1   | The superscalar architecture of the future         | 97 |

|    | 5.2   | Exploiting loops for power consumption             | 99 |

|    | 5.3   | Perspectives                                       | 99 |

| Bi | bliog | graphy 1                                           | 03 |

| Αι | ıthoı | r's Publications 1                                 | 18 |

| Li | st of | Acronyms 1                                         | 23 |

| Li | st of | Figures 1                                          | 25 |

# Résumé en Français

Depuis plusieurs décennies, la fréquence des processeurs à usage général n'a cessé d'augmenter grâce aux transistors de plus en plus rapides et aux micro-architectures avec des pipelines plus profonds. Cependant il y a environ 10 ans, à cause des courants de fuite et de la température, la finesse de gravure des processeurs a atteint sa limite physique. Depuis lors, la fréquence des processeurs n'a pas augmenté. Au lieu d'augmenter la fréquence du processeur, les fabricants ont intégré plus de cœurs sur une seule puce, agrandi la hiérarchie de caches et amélioré l'efficacité énergétique.

Mettre plus de cœurs sur une seule puce a augmenté le rendement de la puce et bénéficie aux applications parallèles. Cependant, avoir plus de cœurs ne suffit pas. Il est également important d'accélérer les processeurs individuellement.

En outre, la réduction de la consommation énergétique est devenue un objectif majeur lors de la conception d'une micro-architecture pour la haute performance. Certaines fonctionnalités ont été introduites dans les unités superscalaires principalement pour réduire la consommation énergétique. Un exemple de fonctionnalité est le tampon de boucles ("loop buffer"), qui est maintenant mis en œuvre dans plusieurs micro-architectures superscalaires. Le but d'un tampon de boucle est d'économiser l'énergie dans le bloc avant du microprocesseur (cache d'instructions, prédicteur de branchements, décodeur, etc.) lors de l'exécution d'une boucle avec un corps assez petit pour tenir dans cette mémoire tampon spécifique.

Pendant l'exécution d'une boucle, les instructions décodées sont fournies au bloc arrière directement depuis le tampon de boucle: le cache d'instructions, les tables de prédiction de branchement, et la plupart de la logique du bloc avant peuvent être en mode horloge fermée (clock gated), ce qui réduit la consommation énergétique de la partie avant.

Si la fréquence du processeur reste constante, la seule possibilité laissée libre pour l'amélioration des performances des applications séquentielles dans les futurs processeurs est d'augmenter l'exploitation du parallélisme d'instructions (ILP). Certaines améliorations des micro-architectures (e.g., une meilleure prédiction de branchement) améliorent simultanément la performance et l'efficacité énergétique. Cependant, améliorer l'exploitation du parallélisme d'instructions a généralement un coût: augmentation de la surface de silicium, de la consommation d'énergie, des efforts de conception, etc. Par conséquent, la micro-architecture est modifiée lentement, incrément par incrément.

En effet, les fabricants de processeurs ont fait des efforts continus afin d'exploiter davantage l' ILP avec de meilleurs prédicteurs de branchements, de meilleurs préchargeurs de données, de plus grandes fenêtres d'instructions, ajout de registres physiques, et ainsi de suite. Par exemple, la micro-architecture Intel Nehalem

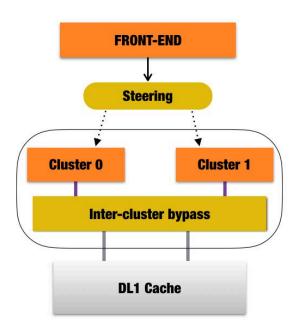

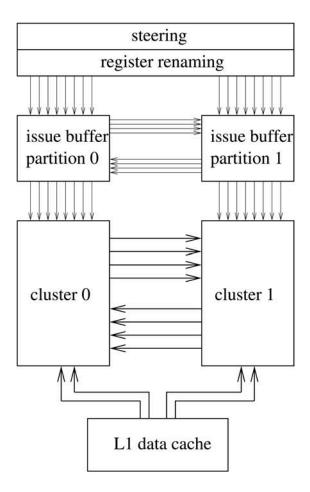

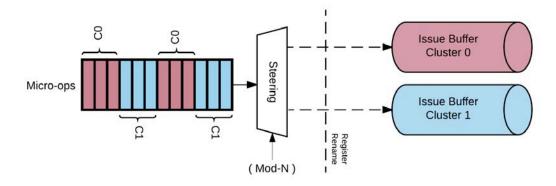

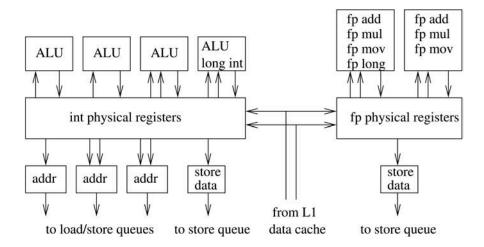

Figure 1: Exemple d'architecture en grappe.

peut émettre 6 micro-opérations par cycle à partir d'un tampon d'exécution (issue buffer) de 36 entrées, tandis que les plus récentes micro-architectures Intel Haswell peuvent émettre 8 micro-opérations par cycle à partir d'un tampon de 60 entrées.

Cette thèse décrit ce que devraient être les unités superscalaires dans les 10 ans à venir et explore la possibilité d'exploiter le comportement des boucles afin de réduire la consommation énergétique au-delà du bloc avant. Certaines propositions ont été publiées notamment sur les accélérateurs de boucles et sur les unités superscalaires à bloc arrière non conventionnel. Il est soutenu que la taille de la fenêtre d'instructions peut être augmentée en combinant le regroupement (clustering) et la spécialisation des registres d'écriture (register write specialization).

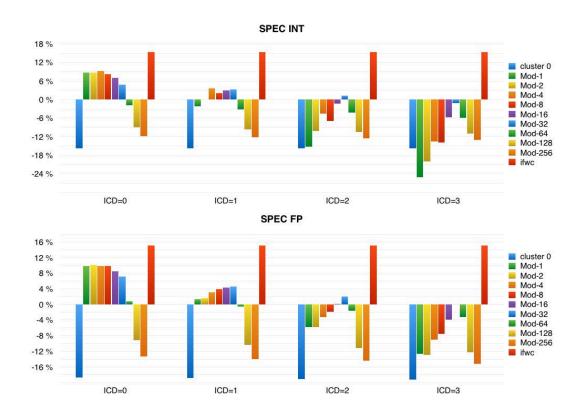

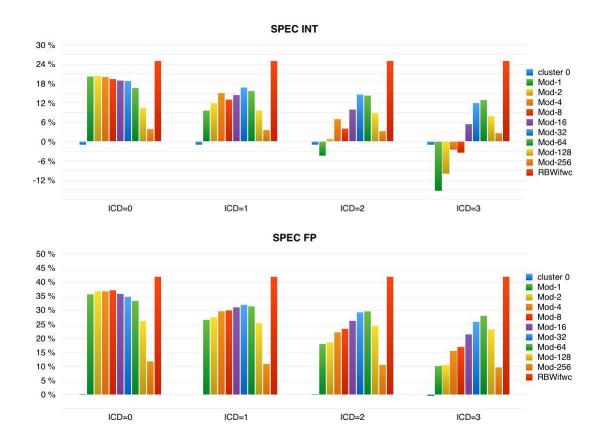

Une différence majeure avec les précédentes études sur les micro-architectures en grappe (Figure 1) est l'utilisation de grappes larges (wide issue clusters), contrairement aux études passées qui étaient principalement axées sur des petites grappes (narrow issue cluster). Le passage de petites grappes à des grappes larges n'est pas qu'un changement quantitatif, mais a aussi un impact qualitatif sur le problème de regroupement, et en particulier sur la politique de pilotage (steering policy). De précédentes études sur les politiques de pilotage ont montré que, tout en réalisant un bon équilibrage de charge, la réduction des communications inter-groupe est un problème difficile. L'une des conclusions d'une décennie de travaux sur les politiques de pilotage est que les plus simples tel que Mod-3

génèrent une perte significative du nombre d'instructions par cycle (IPC), alors que les politiques de pilotage qui minimisent la perte IPC sont trop complexes pour les implémentations matérielles.

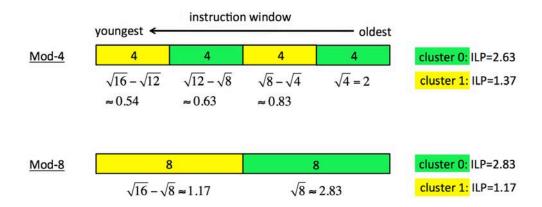

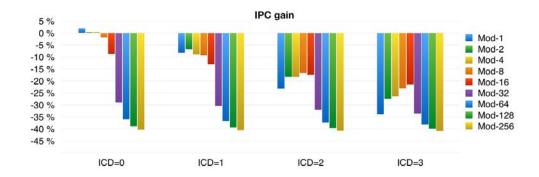

De facto, cette étude montre que considérer des grappes larges a un impact dramatique sur les performances de Mod-N, l'une des politiques de pilotage les plus simples. Mod-N envoie N instructions consécutives à une grappe, puis les N prochaines à une autre grappe, et ainsi de suite de façon circulaire. Baniasadi et Moshovos ont constaté que, pour les petites grappes, la valeur optimale de N est en général très faible et préconisent une politique Mod-3. Il semblerait qu'après l'article de Baniasadi et Moshovos, personne n'ait considéré la politique Mod-N autre que Mod-3.

Force est de constater qu'avec des grappes larges, si la fenêtre d'instructions est assez grande et compte tenu d'un délai inter-groupe réaliste, la valeur optimale de N est beaucoup plus grande que trois, généralement plusieurs dizaines. Grâce à la localité des données dépendantes, une politique Mod-64 conduit à beaucoup moins de communications inter-grappe qu'une politique Mod-3. En conséquence, Mod-64 tolère plus les retards inter-grappe que Mod-3. En outre, environ 40% des valeurs produites par une grappe n'ont pas besoin d'être transmises à une autre grappe, ce qui permet de réduire l'énergie dépensée dans les communications inter-grappe.

La seconde contribution propose deux optimisations indépendantes et orthogonales concernant la consommation énergétique et exploitant les boucles. La première optimisation détecte les micro-opérations redondantes produisant le même résultat à chaque itération puis supprime définitivement ces micro-opérations. La seconde optimisation se concentre sur la diminution de l'énergie consommée des micro-opérations de chargement (load), en détectant les situations où un chargement n'a pas besoin d'accéder à la file d'attente des enregistrements (store queue) ou n'a pas besoin d'accéder au cache de données de niveau 1 (DL1).

Les optimisations proposées ont un impact négligeable sur la performance de calcul, elles concernent essentiellement la consommation énergétique.

# Chapter 1

# Introduction

## 1.1 Purpose of this work

For several decades, the clock frequency of general purpose processors was growing thanks to faster transistors and microarchitectures with deeper pipelines. However, about ten years ago, technology hit leakage power and temperature walls. Since then, the clock frequency of high-end processors did not increase. Instead of increasing the clock frequency, processor makers integrated more cores on a single chip, enlarged the cache hierarchy and improved energy efficiency.

Putting more cores on a single chip has increased the total chip throughput and benefits some applications with thread-level parallelism. However, many applications have low thread-level parallelism [BDMF10]. So having more cores is not sufficient. It is important also to accelerate individual threads.

Moreover, limiting the energy consumption has become a major challenge when designing a high-performance microarchitecture. Some microarchitecture features have been introduced in superscalar cores mainly for reducing energy. An example of such feature is the *loop buffer* today implemented in several superscalar microarchitectures [Int16a, Lan11, Rup12]. The purpose of a loop buffer is to save energy in the core's front-end (instruction cache, branch predictor, decoder, etc.) when executing a loop with a body small enough to fit in the loop buffer. During the loop execution, decoded instructions are provided to the backend directly from the loop buffer: the instruction cache, branch prediction tables, and most of the front-end logic can be clock gated, which reduces front-end power consumption<sup>1</sup>.

If the clock frequency remains constant, the only possibility left for higher single-thread performance in future processors is to exploit more Instructionlevel Parallelism (ILP). Certain microarchitecture improvements (e.g., better

<sup>&</sup>lt;sup>1</sup>A recent white paper by NVIDIA mentions a 50% reduction of the front-end power in the ARM Cortex-A15, thanks to the loop buffer [NVI13]

branch predictor) can simultaneously improve performance and energy efficiency. However, in general, exploiting more ILP has a cost in silicon area, energy consumption, design effort, etc. Therefore, nowadays the microarchitecture evolves slowly, incrementally, taking advantage of technology scaling. Processor makers have made continuous efforts to exploit more ILP, with better branch predictors, better data prefetchers, larger instruction windows, more physical registers, and so forth. For example, the Intel Nehalem microarchitecture (November 2008) can issue 6 micro-ops per cycle from a 36-entry issue buffer, while the more recent Intel Haswell microarchitecture (June 2013) can issue 8 micro-ops per cycle from a 60-entry issue buffer [Int16a].

#### 1.2 Contributions

The first contribution of this thesis is an exploration of the possible design of a very wide issue superscalar processor (16-issue processor). Such a processor could be a core of the high-end multicores ten years from now. A major difference with past research on clustered microarchitecture is that we assume wide issue clusters ( $\leq$  8-issue), whereas previous research mostly focused on narrow issue clusters ( $\leq$  4-issue). Going from narrow issue to wide issue clusters is not just a quantitative change, it has a qualitative impact on the clustering problem, in particular on the steering policy. Past research on steering policies showed that minimizing intercluster communications while achieving good cluster load balancing is a difficult challenge.

One of the conclusions of a decade of research on steering policies was that simple steering policies generate significant performance opportunity loss while steering policies minimizing performance loss are too complex for hardware-only implementations [BM00, SZ05, CCGG08].

This study shows that considering wide issue instead of narrow issue clusters has a dramatic impact on the performance of Mod-N, one of the simplest steering policy. Mod-N sends N consecutive instructions to a cluster, the next N instructions to another cluster, and so forth in round-robin fashion [BM00]. Baniasadi and Moshovos found that, on narrow issue clusters, the optimal value of N is generally very small, advocating a Mod-N policy. To the best of our knowledge, after Baniasadi and Moshovos's paper, nobody has considered Mod-N policies other than Mod-N.

We find that, with wide issue clusters, if the instruction window is large enough and considering a realistic intercluster delay, the optimal value of N is much larger than three, typically several tens. Owing to data-dependence locality, a Mod-64 policy leads to much fewer intercluster communications than a Mod-3 policy. As a result, Mod-64 tolerates greater intercluster delays than Mod-3. Moreover, about

Contributions 11

40% of the values produced by a cluster do not need to be forwarded to the other cluster, which permits reducing the energy spent in intercluster communications.

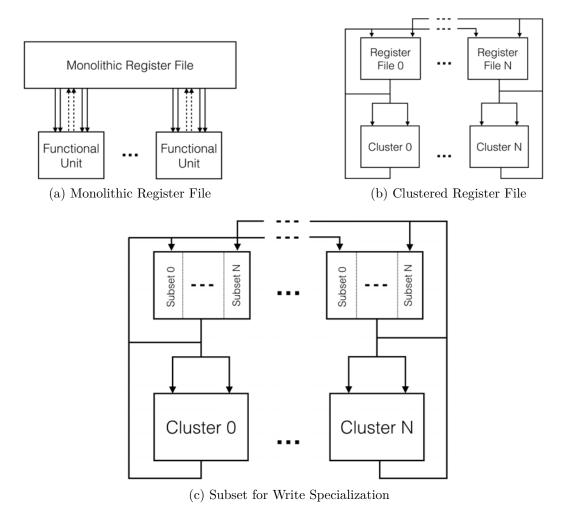

We argue that the instruction window and the issue width can be augmented by combining clustering [LFK<sup>+</sup>93, Kes99, PJS97] and register write specialization [CPG00, ZK01, STR02].

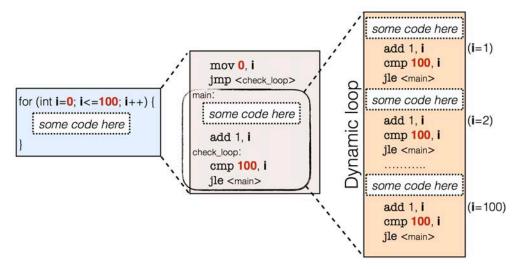

Many programs spend a significant part of the execution in loops [Kob84]. The second contribution is an exploration of the possibility of exploiting loop behaviors to reduce energy consumption beyond the front-end. Some propositions have been published for loop accelerators [CHM08, SIT<sup>+</sup>14, NGS15] or for unconventional superscalar core back-ends [HNL14]. Sodani and Sohi, in [SS97], pointed out that redundant execution exists in most programs. In this thesis, we propose two independent and orthogonal energy optimizations exploiting loops.

The first optimization we propose is a mechanism to detect redundant microops producing the same result on every iteration and to remove these micro-ops from the execution core. The simplest case of redundancy is when a micro-op reads all its operands from registers not modified in the loop. Registers remain unchanged when values are set before entering the loop. A micro-op that only reads these constant values can be considered redundant, and the produced value is constant through the different iterations. In this way, the *redundancy status* can spread to other micro-ops, and the loop buffer can be manipulated to remove these micro-ops.

We propose the modification of register renaming to keep alive the physical register that holds the result of a redundant micro-op, and we describe a solution to recover the register file in case of trap or loop exit. The proposed modification uses a small fully associative table called Redundant Load Table to keep track of conflicts between stores and removed loads. We evaluate the impact of removing redundant micro-ops and the cost of hardware modifications.

The second optimization focuses on saving energy consumed by load microops. We detect situations where a load does not need to access the store queue or does not need to access the Level-1 data cache (DL1). In the conventional case, every load checks the store queue (STQ) and the DL1 simultaneously, but one of these two accesses is useless. We predict in which queue the load will hit the data, to avoid the unnecessary accesses.

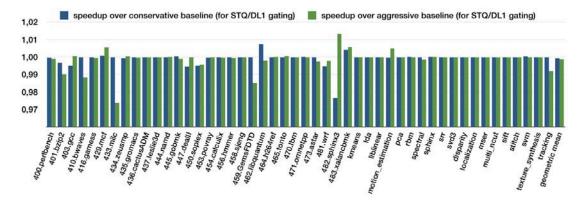

The proposed methods allow the gating of STQ or DL1. These methods can be used together (they are orthogonal) or independently of each other. We describe the effects of wrong DL1/STQ gating prediction and the opportunities that tested benchmarks offer for each type of gating.

We also test this mechanism with a configuration which emulates what happens for very large instruction footprint applications. We first analyze each type of gating individually, then combined, focusing on the performance impact of this energy saving solution. The optimizations proposed have a negligible impact on performance but they mostly generate energy consumption saving.

## 1.3 Organization

This thesis is organized as follows. Chapter 2 presents a summary of the state of the art related to the two main contributions of this thesis. It describes what was done in the last two decades for increasing back-end performances with clustered micro-architecture and decreasing the power consumption using loops.

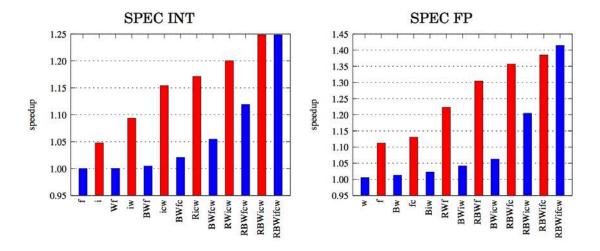

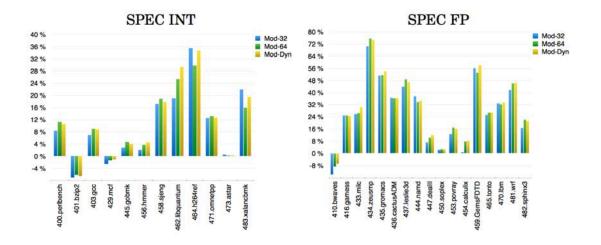

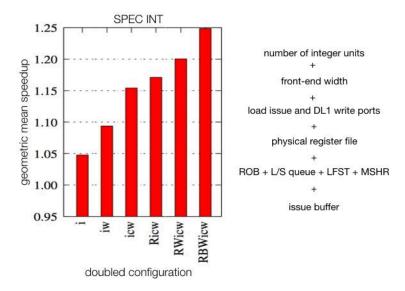

The first contribution is described in Chapter 3. We argue for using some of the benefits of technology scaling for increasing single-thread Instruction per cycle (IPC). We explore the performance impact of various microarchitecture parameters, and we show that, by doubling all the parameters of a modern highend core simultaneously, the IPC of SPEC INT benchmarks could be increased by 25% on average, that of SPEC FP by 40%. We focus on the performance impact of clustering the out-of-order engine, finding that significant performance gains are still possible, despite the intercluster delay, provided the instruction window parameters are doubled. We show that a Mod-64 steering policy tolerates intercluster delays of a few cycles. We explain how the energy consumption of intercluster communications can be reduced by detecting micro-ops whose results are not needed by the other cluster.

The second contribution is described in Chapter 4. In this section, some statistics about the loop behavior of benchmarks are provided. Then we describe and evaluate the two energy optimizations proposed: the removal of redundant micro-ops, and the DL1/STQ gating. We offer an overview of how the two gating technique can be combined.

Chapter 5 concludes this thesis, with considerations about the future of superscalar architecture using the clustered back-end and about future uses of the dynamic instruction reuse technique for power consumption reduction.

# Chapter 2

# State of the Art

Microprocessors are the hearts of most of the electronic systems we use, today. Not only computers, smartphones, tablets, but also cars, dishwasher, TV and so on. In Computer Science, the architecture of microprocessors has been evolving from the first microprocessor¹ to the recent Intel/AMD microprocessors. Today the technology allows the creation of tiny microprocessors capable of executing several times more instructions than supercomputers 20 years ago. A common (and most of the time, commercial) way to evaluate this capability is the clock speed. This value, expressed in Hertz, was a kind of keyword in past commercials. The reality is quite different: clock speed and processor's performance are different, and they express different processor capabilities.

The large use of microprocessors in smart and portable devices like laptops or smartphones opened the eyes on another important feature of modern processors as well as performance: the energy consumption.

## 2.1 From Pipeline to Superscalar

Design and work with microarchitectures means conceiving new solutions for the datapath. The datapath can be defined as the path that the instructions must fulfill within the processor to finish their execution. Different instructions may need different datapath, and an instruction generally requires more execution time if it is to fulfill a longer path within the datapath, and then passes through a larger number of logic gates.

A fundamental concept in the study of the microarchitecture is the Instruction Set Architecture (ISA). The ISA describes those aspects of the architecture design that are visible to the programmer. It is the set of basic instructions that the

<sup>&</sup>lt;sup>1</sup>The term "microprocessor" is attributed to Viatron Computer Systems describing the custom integrated circuit used in their System 21 small computer system announced in 1968

State of the Art

microprocessor can perform. Two microprocessors that use the same ISA can have two completely different microarchitectures, and consequently different ways to execute instructions and different execution times. In the rest of the thesis, the words microarchitecture and architecture will be used interchangeably.

The scalar pipeline architecture is an implementation that assumes one instruction is executed at each clock cycle and each component can be used only by one instruction per cycle. This is one of the simplest architecture to design, but its speed is limited by the longest path, by the long delay of memory compared to the registers and by the slower component. The evolution from pipeline to superscalar allowed to increase performances increasing the hardware complexity.

The pipelining allows the partial overlap of instructions, thus trying to exploit their potential inherent parallelism, also called Instruction-level Parallelism (ILP). The actual degree of instruction parallelism that it is possible to exploit, however, depends on several factors, like the limited number of available functional units, the data dependencies between instructions and the presence of branch instructions.

In an ideal situation, we have two solutions to increase performance of the pipeline: increase the clock frequency and execute more instructions in parallel.

If we increase the clock frequency (which means using a shorter clock cycle), the clock must be sized to allow the instruction to pass through the portion of datapath content in a single pipeline stage. So that the pipeline can continue to operate, it is necessary to redesign the architecture, dividing the work in a greater number of stages, in each of which it is possible to perform the least amount of work permitted by the new shorter clock cycle.

However, if the number of pipeline stages (also called *depth of the pipeline*) is increased, there will be more instructions running in parallel, and therefore the parallelism inherent in the running program is potentially fully exploited. In other words, the number of pipeline stages and the clock frequency (and the length of the clock cycle) are closely related to each other impacting the actual performance.

The increase of the depth of pipeline was heavily exploited by the Pentium IV, in which the architects were able to reach frequencies that touched the 4 GHz with a pipeline of nearly 30 stages [HSU+01]. Unfortunately, it was not possible to exploit this technique indefinitely, because of architectural and technological problems. The increased complexity of the pipeline and thus of its control unit, the thickness of the link between transistors, the interferences, energy consumption and heat dissipation are all typical problems of a deep pipeline [AHKB00].

Executing more instructions in parallel, called *multiple issue* execution, means executing two or more independent instructions, i.e., they do not need the result produced by any other instruction executed in the same clock cycle. The multiple issue execution requires sophisticated functional units, and a sufficient number of

| IF      | ID   | EX       | MEM | WB  |     |     | ins | truction 1 |

|---------|------|----------|-----|-----|-----|-----|-----|------------|

| IF      | ID   | EX       | MEM | WB  |     |     | ins | truction 2 |

| 1 Total | IF   | ID       | EX  | MEM | WB  | 10. | ins | truction 3 |

|         | IF   | ID       | EX  | MEM | WB  |     |     | 1          |

|         |      | IF       | ID  | EX  | MEM | WB  |     |            |

|         |      | IF       | ID  | EX  | MEM | WB  |     | ļ          |

|         |      |          | IF  | ID  | EX  | MEM | WB  | i          |

|         |      |          | IF  | ID  | EX  | MEM | WB  |            |

|         |      | 2.0      |     | IF  | ID  | EX  | MEM | WB         |

| -       | time | <b>→</b> |     | IF  | ID  | EX  | MEM | WB         |

Figure 2.1: The basic outline of a superscalar execution for instruction from 1 to i and more. In the real implementation, the pipeline stages are more than 5, but the execution of the instructions can still be conceptually divided into few basic phases. In this example two instructions can use the same pipeline phases under ideal conditions, and we have CPI=0.5

functional units must be available to execute multiple instructions in parallel. It must be possible to fetch multiple instructions from the instruction memory and multiple operands from the data memory at each clock cycle. It must be possible to address more CPU registers in parallel, and it must be possible to read and write registers used by instructions executed in the same clock cycle.

In a pipelined architecture without multiple issue execution, in an ideal case of absence of dependencies, one instruction is completed at every clock cycle: the Cycle per Instruction (CPI) is equal to 1. In a multi-issue pipelined architecture, instead, it is virtually possible to complete the execution of more than one instruction per clock cycle, having a CPI less than 1 (Figure 2.1).

In order to implement the multiple issues, the logic unit must be able to determine which and how many instructions it is possible to execute in a given clock cycle. Once identified these instructions, they are put in an *issue packet* and issued in the same clock cycle. The multi-issue processors can be conceptually divided into two categories, depending on how (and especially when) this identification is carried out.

In static multi-issue processors, the selection of which instructions can be issued in parallel is made by the compiler, that is in software. When this job is entirely done by the compiler, we call it Static Instruction-level Parallelism.

In dynamic multi-issue processors, the processor resolves at run-time the dependencies and decides which instructions execute in parallel. Obviously, there is a limit to the number of instructions that the logic unit can examine to identify as an independent group of instructions. This limit depends on the architecture State of the Art

implementation and on the fact that the search is done at run-time and the processor has a short time window (the clock cycle) to detect them. The number of identified independent instructions may change at each clock cycle (up to the maximum allowed by the architecture). This latter solution is called Dynamic Instruction-level Parallelism.

# 2.2 Performance Technique of Superscalar Processors

#### 2.2.1 Instruction Level Parallelism

Determining the instructions dependencies is essential to quantifying how much parallelism exists in a program and how it can be exploited. If two instructions are independent, they can be executed simultaneously and in any order in the pipeline, so long as there are sufficient resources (i.e., functional units). If two instructions are dependent, they must be executed in order, and they can overlap only partially. Two dependent instructions can stay in the pipeline at the same time but in "sufficiently distant" phases. In order to exploit the parallelism offered by programs, it is essential to determine the dependencies between instructions.

If we consider two instructions, i and j, with i appearing before j, we can have tree kinds of data hazard:

- **Read-After-Write (RAW)** Instruction j tries to read a register or memory location before it is written by i. The instruction j would read the old value that is incorrect. In this case, j cannot continue the execution because the data j needs is not yet available. The processor must notice the dependence of j from i and suspend its execution until the missing data is available. This is also called true dependency.

- Write-After-Write (WAW) Instruction j tries to write a register or memory location before it is written by i. The two writing end in the wrong order, leaving the register with a value written by i instead of j. This is an output dependency.

- Write-After-Read (WAR) Instruction j tries to write a register or memory location before i reads it. The instruction i reads a wrong value. This is an anti-dependency, which rarely occurs because in most of the pipeline the reading of the operands usually takes place "very before" (the Instruction Decode (ID) phase) the actual write (in the Write-Back (WB) phase).

The dynamic pipeline scheduling consists of a set of run-time techniques to reduce the frequency and the duration of the hazards, like changing the order in which the instructions are executed or renaming the registers.

The Out-of-Order execution makes it possible to maximize the use of computing resources by executing instructions according to their availability. For example, stalling the instruction fetch on the occurrence of any single branch would result in very poor performance, therefore, the processor uses prediction to predict the outcome of branches. This technique is called speculation, and can be applied at compile time or can be hardware based; we will focus on the latter. Speculation techniques require specific recovery mechanisms in case of wrong predictions.

Several speculation techniques [CR00, SVS96, Smi81, SMR05, LWS96] have been proposed in the literature and implemented in commercial architectures. Branch prediction consists in predicting the execution flow direction in the presence of branch instructions. A high percentage of instructions are branches, and a "good" branch predictor, trying to predict both the direction of the branch and the target address of a jump, can give important benefits in terms of performance and power saving.

Speculation can also be applied to the memory accesses (*Data Prefetching*), trying to predict the data that will be needed soon, loading it into caches before it is actually required. Data Prefetching is useful to improve tolerance to the high memory latency, and it can be implemented either via software or hardware. Software prefetching is typically implemented using the compiler [MLG92, AS79, McI98].

The hardware prefetcher tries to exploit spatial locality making available, in the cache, the block or blocks containing the data that will be needed soon. This prefetching can be done through identification of specific memory access patterns or through use of special threads usually called *helper threads* [SKS14, KLW<sup>+</sup>04, LDH<sup>+</sup>05, KST11]. The downsides of an aggressive data prefetching are the risk of polluting the cache with useless data and wasting bandwidth.

Another type of speculation is the *Load-Hit* speculation. It consists in predicting that the load instruction will hit the first level cache, issuing instructions following the load early. In the case of a misprediction, however, the load and the instructions scheduled after the load need to be rescheduled. Load-Hit speculation allows instructions that depend on a load to benefit from the possibility of issuing early, but it requires a mechanism for re-issuing these instructions in case of cache miss predicted as hit.

Load and store queues allow executing memory instructions keeping the correct order of memory accesses. Each load must wait until all prior store addresses are calculated. However, it is possible to predict the dependency between load and store and anticipate the load issue. Load speculation allows the early execution of loads, and it postpones the check of correctness to subsequent pipeline

State of the Art

stages. In the case of a mispeculation, it is necessary to perform a roll-back<sup>2</sup>, discarding the load and all instructions issued after the load [CR00].

#### 2.2.2 The Branch Predictor

The branch prediction was introduced in order to eliminate control hazards. Programs are not linear sequences of instructions, but they are full of branch-like operations.

A branch predictor requires hardware structures that keep track of program execution and branch instructions history like previously taken direction and target addresses of previous jumps. The branch predictor tables are read during the fetch phase, and the Program Counter (PC) of the branch instruction is used to query these tables in order to choose the next instruction to fetch. There are numerous implementations of the branch predictor. Recent branch predictors, like TAGE [SM06], achieve a high prediction accuracy.

#### 2.2.3 The Register Renaming

An essential component of modern Out-of-Order architectures is the register renaming. The architecture features a limited number of logical registers. This limit implies the existence of false register dependencies, as illustrated in the example in Figure 2.2. The ability of the system to exploit the instruction level parallelism is limited by false dependencies between instructions which use the same logical registers but work on independent data. It is possible, however, to have a higher number of physical registers in the system. During the register renaming stage, each logical register is renamed and assigned to an available physical register. The association between logical and physical registers is kept in a specific table. This solution tries to eliminate false register dependencies while maintaining true data dependencies between instructions.

The first example of register renaming, proposed in 1967, was Tomasulo's algorithm [Tom67]. This algorithm is based on the use of a Register Allocation Table (RAT) to keep track of renamed registers. In modern architectures, the information about which physical register to release is kept in the Reorder Buffer (ROB) and used when the instruction is committed. The renaming uses a table that contains a list of the actual free physical register, and if there are no free registers, the front-end stalls.

The major key of the Tomasulo's scheme is the Reservation Station (RS) associated with the functional units, where the instructions, after the instruction fetch and decode, wait to be executed.

<sup>&</sup>lt;sup>2</sup>The roll-back mechanism could be different on different architectures

| Program<br>Counter | Instruction (with false positive) | Instruction (without false positive) |  |  |

|--------------------|-----------------------------------|--------------------------------------|--|--|

| 0x01               | eax = mem[Addr1]                  | rl = mem[Addr1]                      |  |  |

| 0x02               | ebx = mem[Addr2]                  | r2 = mem[Addr2]                      |  |  |

| 0x03               | eax = eax + ebx                   | rl = rl + r2                         |  |  |

| 0x04               | mem[Addr1] = eax                  | mem[Addr1] = rl                      |  |  |

| 0x05               | eax = mem[Addr3]                  | r3 = mem[Addr3]                      |  |  |

| 0x06               | ebx = mem[Addr4]                  | r4 = mem[Addr4]                      |  |  |

| 0x07               | eax = eax - ebx                   | r4 = r4 - r3                         |  |  |

| 0x08               | mem[Addr <b>3</b> ] = eax         | mem[Addr4] = r4                      |  |  |

Figure 2.2: Instructions from 0x05 to 0x08 are independent of instructions from 0x01 to 0x04, but the processor cannot finish the load at 0x05 and 0x06 until the register eax is written, otherwise the value written at Addr1 will be wrong. With the rename of architectural registers to physical registers, the false dependence disappears.

The Reservation Stations and the load/store buffer consist of multiple fields, implemented by internal registers (invisible to the ISA) that allow storing the information required to handle the entire mechanism.

The Tomasulo scheme has two essential characteristics:

- 1. The access to the operands is performed in a distributed manner

- 2. The WAW and WAR hazards are eliminated

If the CPU fetches a new instruction at each clock cycle, the use of Reservation Station allows to have multiple consecutive instructions running simultaneously, and the RS themselves act as additional registers.

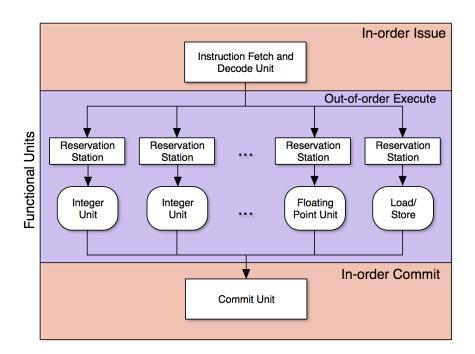

Several variants of Tomasulo's original algorithm were proposed, like adding the Register Update Unit [SV87] or additional structures [Smi98], in order to maintain and restore the precise microarchitectural state. In the solution proposed by Smith and Pleszkun [Smi98] the instructions are kept in the ROB until the in-order commit. The Tomasulo's scheme with an in-order commit is shown in Figure 2.3.

The Tomasulo algorithm and its variant with the Reorder Buffer have been used in commercial architecture like Intel P6 [Col05, Gwe95]. The Intel P6 introduced, in the Intel Family, the Speculative Execution and the Out-of-Order (OoO) mechanism, called *dynamic execution* by Intel.

An overview of register renaming techniques was described by Sima in his survey [Sim00].

Figure 2.3: A simplifier overview of Tomasulo's Reservation Stations associated with Functional Units. Instructions are fetched and decoded in order, and sent to RS according to their type, thus the type of functional unit required. Using a Reorder Buffer, it is possible to have an in-order commit that helps the handling of precise interrupts.

In this thesis, we propose a register renaming modification in order to support the loop mechanism proposed in Chapter 4.

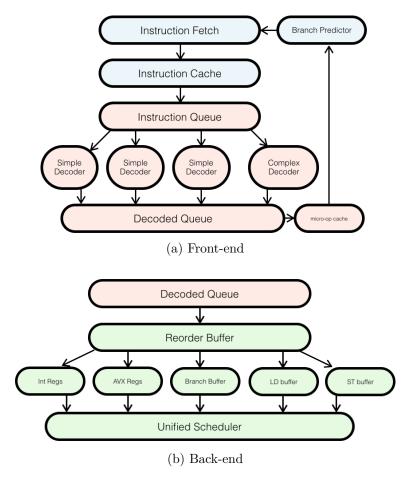

#### 2.2.4 Out-of-Order Execution

The evolution of single core processors has allowed exploiting the instruction level parallelism through the introduction of Out-of-Order (OoO) execution. The OoO execution allows to schedule instructions which are ready to be executed without order restrictions, allowing to reduce the impact of chip connection latency and the underlying memory latency. The use of OoO implies the introduction of new hardware components, like the ROB, the issue queues, the load/store queues, and so on. These new components lead to an increase in complexity, compared to in-order processors.

In order to understand the ideas proposed in this thesis, it is necessary to give a brief summary of the main OoO structures present in modern microarchitectures, briefly describing how they work and in which way they can be modified.

All the instructions in the Out-of-Order back-end are handled by the ROB. The ROB is the First-In-First-Out (FIFO) queue we described in previous sections. Instructions are read from the instruction cache, then decoded, and inserted in the ROB in an ordered sequence. At the end of the execution, each instruction is removed from the ROB in the same order in which it was inserted. In this way, the order of execution is guaranteed for all committed instructions. The instructions can be executed out of order, depending on source data and hardware resource availability.

The instruction dependencies are guaranteed by the use of an *Issue Queue*. This queue contains the instructions ready to be executed, and it is used by the scheduler to decide the issue sequence. The total number of instructions in the issue queue is a subset of the instructions in the ROB. When an instruction is executed, it may produce a result that is used by another instruction in the issue queue.

Each time an instruction is executed, all the ready instructions in the issue queue are informed about the availability of the result and, eventually, can become ready. The *ready* status depends on the availability of required data input and the availability of the Functional Unit (FU) required to execute the instruction. The issue queue can be implemented as a single queue or divided into multiple queues. The Alpha 21264 [Kes99], for example, uses an integer issue queue and a floating-point issue queue. In a clustered architecture, described later, it is possible to have separated issue queues for each cluster.

The dispatch of instructions from the issue queue to Functional Units, in the OoO engine, is based on two steps: the Wake-Up and Select, as mentioned in previous section. In a given clock cycle, there are instructions in the Issue Queue waiting to be executed. These instructions wait for the availability of their input operands. The input operand of a given instruction is ready when the producer of this operand is executed, and the operand become available. When operands are available, the instruction in the Issue Queue is flagged as ready and could be chosen in the next Select step for the execution.

Since the hardware resources are limited (i.e., there are not enough available functions units), a dynamic selection of instructions to execute is made. The dynamic selection happens during the *Select step*. The selection of the ready instructions to dispatch is based on a specific heuristic; the common one is to choose the oldest ready instruction in the Instruction Window.

When the ready instruction is selected, its tag is broadcasted to the Issue Queue to inform other instructions about the future availability of the result. This information allows, in the next Wake-Up step, to flag new instructions as ready to execute. From now on, these instruction become *ready* and they can be selected in the Select step in the next cycle.

Speculation is possible also in the Wake-Up phase. For load instructions,

22 State of the Art

for example, the scheduler cannot determine in advance how many cycles will be necessary to complete the memory access. The load can miss in memory, and the time needed to complete the execution can grow from a few cycles to hundred of cycles. When a load is selected and executed, it is possible to speculate about its execution latency and execute dependency instruction according to this speculation. If the load misses in Level-1 Data Cache (DL1), we have a mispeculation, and a recovery mechanism is necessary.

The *Load Speculation* was proposed to resolve this delay issue for memory operations [FS96, MBVS97, YERJ99] and different solutions were proposed in the literature, i.e., the Store Set [CE98].

The memory instructions (load and store) use two specific structures called Load Queue (LDQ) and Store Queue (STQ), a Content-Addressable-Memory (CAM) structures used to identify dependencies between load and store instructions. Their purpose is to maintain the correct memory access order and verify dependencies between memory addresses. Load/Store units are generally maintained as two separate queues.

# 2.3 Wide-issue complexity

The introduction of the out-of-order execution in superscalar architectures has introduced a further degree of complexity. Indeed it is not sufficient to increase the total number of Functional Units in order to have a multiple-issue execution. The Instruction Window size limits the number of instruction that can be potentially selected by the scheduler at each cycle. The superscalar processor implementation requires changes at all stages of the pipeline. It is necessary to carry out, each cycle, the fetch, the decode and rename of multiple instructions. Also, the register file and the cache memory require modifications to allow the access of multiple instructions per cycle.

## 2.3.1 Limits of performance scaling

Exploiting Instruction-level Parallelism is an efficient way to increase the performance of microarchitectures. A way to evaluate the performance is counting the number of instructions executed per cycle (IPC). The IPC is equivalent to performance when the clock frequency is fixed, for a given binary.

Performance can also be evaluated in terms of raw execution speed. In the past years, a common way to increase the processor performance (and the commercial attractiveness) was the clock frequency. Increasing the frequency requires taking into account physical limits, like internal wire delay and the delay of individual hardware components. In the last ten years, the semiconductor fabrication node

of companies like Intel moved from the 65 nm of Intel Conroe/Merom to 14 nm of Skylake. Transistors are getting smaller, but not faster, and the wire connections between them are becoming a major problem due to delay [AHKB00]. It is possible to reduce the clock period by increasing the number of pipeline stages, but it may increase the overhead of the latches between pipeline stages, as well as phenomena such as clock skew and jitter.

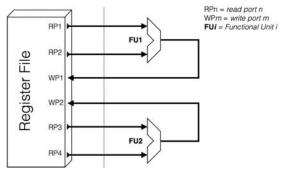

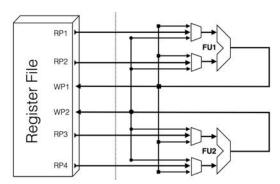

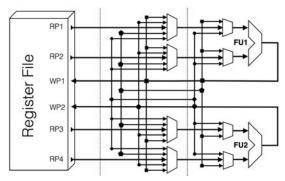

There is a technological problem for the scaling of the wire delay: the wire delay does not scale at the same pace as the gate delay. This problem is greater for global wires, as we need connections through an ever-increasing number of gates along technology. Along with the wire problem, energy consumption is another factor to consider. For example, the energy consumption increases with the size of the register file [PJS97, San06]. The area occupied by the register file increases linearly with the number of registers, but quadratically with the number of ports. The power consumption of the register file, then, increases quadratically compared to the processor width, since the number of ports required is proportional to the number of instructions which need to access the register file.

Palacharla studied the design complexity, defining it as "the delay through the critical path of a piece of logic, and the longest path through any of the pipeline stages determines the clock speed" [Pal98]. It is necessary to find new methods to increase performances and reduce the power consumption without increasing the complexity. The increase of computational capability usually results in an increase of the size of structures. This increase is reflected by the growth of design complexity and energy consumption. This trend can not go on any longer, since problems on wire delay, clock period size, etc., lead to a slowdown of performance improvements.

Many research works have focused the attention on the limits inherent to physical scalability [Bor99, Mat97]. These limits, for example, were put in evidence by Agarwal et al. [AHKB00]. They examined the effects of technology scaling on clock speed and wire delay on a hypothetical aggressive microprocessor, concluding that the scaling rate of performance cannot remain constant. In the deep sub-micron fabrication processes there is no future for large monolithic cores and the limits of technology constraints will become bigger in future designs. They proposed that future microprocessors should be partitioned into independent physical regions, with a focus on the latency for communicating among partitions.

In a superscalar architecture, performance scaling is not limited only by wire delay. As described by Palacharla *et al.* [PJS97], many of the elements in the pipeline present a complexity that requires further considerations. Palacharla *et al.* analyzed components such as the register rename logic, the wake-up logic, selection logic and data bypass logic, comparing three different technologies (0.8  $\mu$ m,

24 State of the Art

$0.35~\mu m$  and  $0.18~\mu m$ ). They proposed a new architectural paradigm that addresses the above problems: partitioning part of the architecture into smaller and simple units, called clusters, running at a high clock rate.

#### 2.3.2 Impact of critical components

All these modifications have increased the architecture complexity. The trend, starting after the Pentium 4, is to keep the same clock frequency but increase the ability to exploiting the ILP, also increasing the wide-issue capabilities. As a consequence, we have an increase in hardware complexity, opening the door to new challenges for the research.

One of the most performance-critical components of superscalar architectures is the issue logic. Optimizing the issue logic makes it possible to maximize the amount of ILP that it is possible to exploit during the program executions. Increase the complexity permits to have wider microarchitectures, with instruction window wide enough to allow more in-fly instructions in the out-of-order engine, maximizing the resources usage. Having a big issue queue allows the issue logic to select the next instructions among a larger number of waked up instructions, allowing to minimize the number of functional units that, in a given clock cycle, are idle.

Increase the wide-issue requires more systems buses. For example, with N functional units, it is possible to generate N different results from N instructions being executed in the same clock cycle. These results will be compared with each entry of the Issue Queue, in order to select which instruction is possible to wake-up. To do this comparison, for each entry, we need  $2 \times N$  comparators because of the two operators.

If the Issue Queue is W entries, a total of  $2 \times N \times W$  comparison is required. Increasing N and W means increasing the total number of comparators, buses, and wires needed. A small increase of wide-issue involves adding much hardware. Also, increasing the complexity also increases the power consumption. In modern microarchitectures, power consumption has become a greater problem than in the past. In this thesis, we will try to address this issue proposing solutions to reduce the number of instructions executed in the OoO engine exploiting loops. The use of loop buffer will allow us to identify redundant instructions and even redundant memory access. We will see how exploiting loops helps to reduce power consumption.

Wide-issue architectures require a significant number of interconnection wires between components like FUs, buffers and so on. Due to the miniaturization, the wire-delay has become one of the dominant components of the total delay, also limiting the increase of clock cycle. In order to design a microarchitecture, it is necessary to take into account the trade-off between performance, clock cycle, and complexity [PJS97].

Different solutions have been proposed in the literature to try to reduce the complexity of one or more part of microarchitectures, such as for register rename [San06], register file [STR02], load/store queue [POV03], issue logic [CG01, TP08], dispatch queue [RG09] and so on.

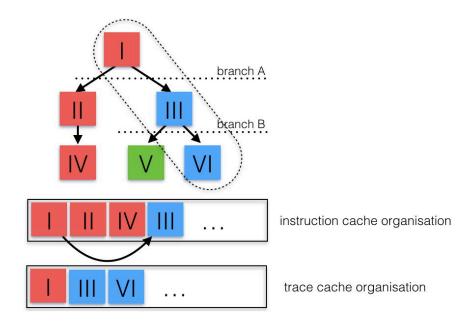

#### 2.3.3 Front-end bandwidth

Executing more instructions per cycle requires fetching more instructions per cycle. A possible way to increase the front-end bandwidth is to predict and fetch two basic blocks per cycles instead of one, as in the Alpha EV8 [SFKS02], and scale instruction decode accordingly. However, decode itself may be a microarchitecture bottleneck for Complex Instruction Set Computer (CISC) instructions sets such as Intel x86. A trace cache (aka decoded I-cache or micro-op cache in the Intel Sandy Bridge and Haswell microarchitectures [Int16a]) addresses this issue. A trace cache stores in traces micro-ops that are likely to be executed consecutively in sequential order [RBS96] (Figure 2.4).

It is possible to transform traces dynamically to increase performance and/or decrease energy consumption [FPP98]. In particular, Jacobson *et al.* proposed to perform constant propagation before storing a trace for future reuse [JS99].

A trace cache is also a solution to the register renaming bandwidth problem. When creating a trace, intra-trace dependencies can be determined, and this information can be stored along with the trace. The number of read and write ports of the rename table can be reduced: each read-after-write or read-after-read occurrence within a trace saves one read port on the rename table, and each write-after-write occurrence saves one write port [VM97]. The number of read and write ports of the rename table is part of the trace format definition.

#### 2.3.4 Level-one data cache

Increasing the issue width also means increasing the L1 data cache load/store bandwidth. The need for sustainable cache bandwidth requires an exploration of new low-cost techniques in order to meet the requirement of modern microprocessors, paying attention also to the power consumption. Several solutions are possible for increasing the load/store bandwidth. The multi-porting solution allows N cache accesses per cycle using an N-ported cache in which each port is independent. This solution is expensive, and not used in commercial processors. The Alpha 21264 [Kes99] implements a time-divided multiplexer solution with a virtual multi-porting in which the cache run at twice the clock speed of the processor. This solution, unfortunately, does not scale well with the increase of issue width. Unlike the Alpha 21264, the Alpha 21164 [Cor94] implemented a

Figure 2.4: Difference between conventional cache and trace cache for the dynamic path: I - III - VI. In trace cache any instruction may appear multiple times because if can be part of different traces. In conventional cache the frequency of taken branches limits the maximum bandwidth per memory port.

dual-copy replication solution in which two copies of the cache are kept coherent. The consistency is permitted by writing the data on both cache copies on each store. The replication requires more die area and has limitations in scalability.

Recent high-end processors use banking to provide the adequate bandwidth. The first example of 2-bank interleaving data cache was proposed in the MIPS R10000 [Yea96], and extended in subsequent architectures. Moreover, alternative solutions based on interleaved caches [RTDA97], replication caches [AZ05], power-efficient caches [DB07] or balanced caches [RFD13], were proposed to resolve different problems in modern processors. Banking leads to the possibility of conflicts when several loads/stores issued simultaneously access the same bank.

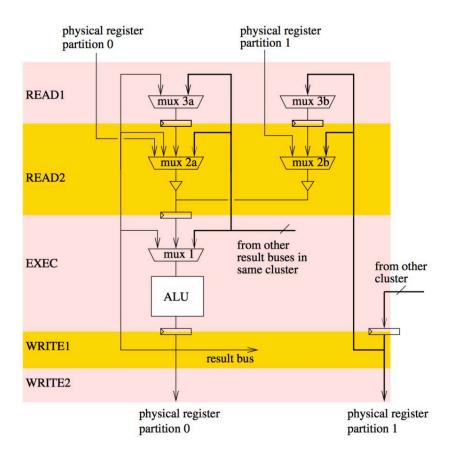

## 2.3.5 Bypass network paths

When an instruction completes the execution, the result is written in the register file. A subsequent instruction that uses that value as input should wait to read the data from the register (Figure 2.5a). The bypass network in necessary to execute dependent instructions in consecutive cycles. In modern architecture, a broadcast-based bypass network is used to bypass result values produced by an instruction to subsequent consumers (Figure 2.5b). This bypass logic requires

introducing more hardware in the datapath. The complexity introduced by the bypasses is proportional to the issue width, and to the number of pipeline stages (Figure 2.5c), i.e., a significant amount of wiring area is used on the chip [ACR95], and the wire delay is an increasing problem in technology era [fS13]. Moreover, the use of wide multiplexers and the number of long wires when we increase bypass width have a substantial impact on power consumption [TSR<sup>+</sup>98].

In a fully bypassed design, the number of bypass paths grows quadratically with the issue width. For example, considering an issue width W and a pipeline with N stages after the first stage in which a 2-input FU results become available, we need  $2 \times N \times W^2$  bypass paths. The scaling of bypass delay is also affected by the reduction of feature size [PJS97], increasing the difficulty of implementing a single cycle bypass network in wide superscalar architectures.

#### 2.3.6 Load/Store queues

The load queue is for guaranteeing a correct execution while allowing loads to execute speculatively before older independent stores. The load queue is searched when a store retires. When there is a load queue, the store queue is mostly for preventing memory dependencies to hurt performance. The store queue is searched when a load executes.

Enlarging the instruction window to exploit more ILP may require the load/store queues to be enlarged too. However, conventional load/store queues are fully associative structures which cannot be enlarged straightforwardly. Clustering the OoO engine does not solve the load/store queues scalability problem. Specific solutions may be needed, e.g., [BZ06, CL04, SMR05, SL06]. For this study, we ignore the problem, and we assume that it is possible to enlarge load/store queues without impacting the clock cycle or the load latency.

The reduction of structure accesses for energy saving is not a novel idea. A large number of loads miss in the STQ [SDB+03, POV03], and some researchers have tried to reduce the number of STQ accesses, for lower energy consumption. Sethumadhavan *et al.* consider filtering accesses to the load/store queues with Bloom filters [SDB+03].

With the Store Set technique, it is possible to create *sets* of conflicting memory instructions [CE98]. Park *et al.* [POV03] filter the STQ searches by modifying the Store Set memory dependence predictor [MBVS97] so that loads that are predicted to be independent of all the stores in the instruction window only access the L1 data cache, not the STQ.

Observing that accessing the L1 data cache generally costs much more energy than accessing load/store queues, Nicolaescu *et al.* proposed the *cached LSQ*: they modify a unified load/store queue (LSQ) so that it behaves like an L0 data cache, with the L1 cache accessed only upon an LSQ miss [NVN03]. They assumed that

(a) Simplified scheme for a no-bypass design of execution engine

(b) Value-bypass implementation using multiplexers

(c) Value-bypass implementation for deep pipeline

Figure 2.5: Each functional unit is connected to read and write ports through latches. Increasing the pipeline depth, the data could be forwarded from different stages of the producer to different stages of the consumer. It requires more multiplexers and more wires.

Clustering 29

the LSQ latency is three times shorter than the L1 cache latency. In order to avoid the performance penalty of serializing accesses to the cached LSQ and L1 cache, Carazo *et al.* proposed to predict L0 hits with a bimodal predictor and a Bloom filter: when a L0 hit is predicted, the LSQ and L1 cache are accessed in series, otherwise they are accessed in parallel [CAC+10]. Like Nicolaescu *et al.*, Carazo *et al.* assume a 1-cycle latency for the LSQ.

#### 2.3.7 Reduce the complexity by limiting pipeline activity

Due to the end of Dennard scaling [DGR<sup>+</sup>74], the energy benefits obtained from new generations of transistor densities is reducing. To address this problem, it is necessary to explore solutions in which the transistor switching should be limited, along limiting the clock cycle, and optimize the existing design. Furthermore, the demand for computational efficiency is continuing to increase. These problems force architects to take into account new energy constraints and eliminate, whenever possible, unnecessary pipeline activity. For example, the front-end in modern architecture like ARM Cortex-A15, represents a predominant source of power consumption [Lan11], forcing to find new architectural solutions independent of technology improvement.

The implementation of dedicated memory for loops helps to save energy in front-end, reducing the impact of fetch, decode and rename. However, despite potential energy saving, no commercial out-of-order processor has attempted to exploit loops behavior to save energy in the back-end. As we will see, in the back-end and specifically in the out-of-order engine, a source of power consumption that we will try to eliminate is the access in parallel to the data cache and store buffer by load instructions. We will see that we can reduce these accesses introducing small hardware modification to support a mechanism of prediction for memory instructions.

# 2.4 Clustering

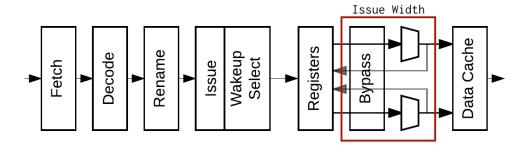

We can consider the baseline superscalar model shown in Figure 2.6. During the fetch phase, instructions are read from the instruction cache memory and decoded. In this phase, multiple instructions are delivered to the OoO execution engine. A predictor is used to fetch a continuous stream of good-path instructions. The main goal is to keep functional units busy as much as possible. Every instruction is converted by one or multiple decoders in RISC-like instructions (called *micro-ops* in Intel architecture) and register operands are renamed.

Significant IPC gains can be obtained by increasing the issue width, the frontend width, and the instruction window size.

Figure 2.6: Simplified Superscalar pipeline. The Clustering allow to increase the issue width of the back-end.

In this section, we emphasize on clustering as a solution to increase the issue width without increasing the complexity of the microarchitecture.

#### 2.4.1 Clustered microarchitectures

Clustering was proposed in the 1990s as a solution for reducing the clock cycle of superscalar processors [PJS97, FCJ97].

The basic idea is to partition the Execution Units (EUs) into clusters so that the output of one EU can be used as input by any other EU in the cluster in the next clock cycle through a local bypass network [GLM10].

In [PJS97] an architecture with the dependence-based steering policy was proposed. In this architecture, the issue window is replaced by simpler FIFO queue structures, in order to reduce the clock period without reducing the IPC. Based on the fact that dependent instructions execute sequentially, the idea is to steer<sup>3</sup> dependent instructions to the same queue, and to issue only the instructions at the head of each queue. The dependencies between instructions are evaluated using specific hardware tables that keep track of the assigned cluster for each register producer. The steering logic uses this table to understand the instruction dependency and, eventually, uses this information for deciding to which cluster to assign the instruction, following a specific heuristic. In their work, Palacharla et al. have evaluated the performance of the dependence-based architecture with 2x4-way clustered system<sup>4</sup>. They compared it with a conventional 8-way microarchitecture, founding the clustered solution allows a faster clock cycle than the conventional one, but with the cost of a small performance degradation.

Clustering can also be applied to the issue buffer (one issue buffer partition per

<sup>&</sup>lt;sup>3</sup>The steering is performed at run-time during the rename phase

<sup>&</sup>lt;sup>4</sup>Two clusters, each of which contains four FIFOs and four functional units

Clustering 31

cluster). Hence clustering is a solution to two of the most significant frequency bottlenecks in the OoO engine: the bypass network and the issue buffer. The price to pay is that communications between clusters require an extra delay, which may impact the performances.

A natural form of clustering, which has been used in several superscalar processors, is to have an integer cluster and a floating-point cluster. This form of clustering does not generate intercluster communications, and the term "clustered microarchitecture" is mostly applied to cases where intercluster communications are frequent.

Clustering introduces a degree of freedom for instructions that can execute on several clusters. Choosing on which cluster to execute an instruction is called steering. Microarchitectures such as the DEC Alpha 21264 [FF98, Kes99] that cluster the EUs but not the scheduler do the steering at instruction issue (execution-driven steering [PJS97]). Microarchitectures such as the IBM POWER7 [SKS+11] that cluster both the EUs and the scheduler do the steering before inserting the instruction into the issue buffer (dispatch-driven steering [PJS97]). An example of dispatch-driven clustered scheme is shown in Figure 2.7.

Execution-driven steering does a good job at mitigating the impact of the intercluster delay, as the scheduler can send an instruction to the cluster where it can execute sooner [PJS97]. However, execution-driven steering limits the size of the issue buffer, not only because the issue buffer does not benefit from clustering (unlike the bypass network), but also because postponing the steering until issue makes it part of the scheduling loop, which impacts the clock frequency.

Zyuban and Kogge proposed clustering as a solution for decreasing the Energy per instruction (EPI) for a given IPC [ZK01]. Like us, they considered wide-issue clusters. However, they did not quantify the IPC improvements that clustering can provide under a fixed clock cycle.

The Integer-Decoupled architecture proposed by Palacharla [Pal98] is based on the necessity of using the floating-point subsystem resources during integer intensive code. The idea is to avoid the resource idling augmenting the floating-point units to perform simple integer operations. The benefits obtained during the execution of integer intensive workload compensates the little hardware complexity introduced in the Floating Point (FP) subsystem.

#### 2.4.2 Issue Buffer

Clustering the issue buffer like the EUs (as in the IBM POWER7) permits increasing the total issue buffer capacity without impacting the clock cycle: the select operation is done independently on each issue buffer partition, and the wake-up operation is pipelined between the partitions, taking advantage of the

Figure 2.7: Example of 2-cluster Out-of-Order engine, assuming dispatch-driven steering and register write specialization (which puts steering before register renaming).

intercluster delay [GNK $^+$ 01].

## 2.4.3 Steering

Ideally, one wants both a good cluster load balancing and limited intercluster communications. However, these two goals contradict each other. The main problem is to achieve a good trade-off between load balancing and intercluster communications while still being able to steer several instructions simultaneously.

Several papers have studied steering policies for clustered microarchitectures. Some papers proposed different variants of dependence-based steering policies trying to steer dependent instructions to the same cluster to minimize intercluster communications, while trying to maintain sufficient load balancing be-

Clustering 33

Figure 2.8: In Mod-N steering algorithm the destination cluster alternates every N micro-ops. C0 is Cluster 0, C1 is Cluster 1.

tween clusters [PJS97, CPG99, CPG00, FRB01, GLG04, SZ05]. However, these dependence-based policies are complex, and steering multiple instructions per cycle is an implementation challenge [SZ05, CCGG08].

Some authors proposed steering policies taking into account register dependencies [PJS97, CPG99, CPG00, BM00, GLG04]. However, these dependency-based steering policies are complex and make steering a clock frequency bottleneck, as the steering bandwidth must match the register renaming bandwidth.

A brief summary of various steering mechanism proposed in the literature [BM00, PG00, CPG00] is as follows:

**First-Fit** Assignment of instructions to the same cluster until it fills up completely. Each time a cluster is full, the next instructions are assigned to a new cluster, chosen using different possible heuristics: the cluster with the fewest assigned instructions, the next cluster in a specific sequence (in case of more than two clusters), the cluster close to became full, and so on

**Load-cut (LC)** Assignment of instructions to the same cluster until a load is encountered, except for sequences of consecutive loads. The intuition behind this heuristic is that a chain of dependent instructions could be introduced by a load.

Branch-Cut (BC) Assignment to the same cluster until a branch<sup>5</sup>, based on

<sup>&</sup>lt;sup>5</sup>According to Baniasardi and Moshovos [BM00], using only *backward* branches does not give significant performance improvements. Moreover, both BC at LC provide, on average, similar performance improvements

the idea that a branch instruction is used to divide different blocks of instructions, and instructions within basic-block should be mostly dependent.

Slice-based mechanisms Based on the Slice (SLC) concept, described by Sastry et al. [SPS98] (e.g., LdSt Slice, Br Slice, Non-Slice), in which the steering is done for groups of correlated instructions. The idea is to reduce the number of intercluster communications by assigning all parents instructions and their consuming child to the same cluster.

Register Mapping Based mechanisms They use a distributed register file and a generated copy instruction for reading operands on a different cluster. These steering mechanisms (e.g., Simple RMB, Balanced RMB, Advanced RMB) try to minimize the number of intercluster communications by assigning each instruction to the cluster in which the highest number of its source operands are mapped [CPG01].

Steering solutions can be categorized as adaptive or unadaptive, instruction-based or group-based, complex or simple concerning of hardware implementation.

In our work, we consider a very simple steering policy:  $\operatorname{Mod-}N$ .  $\operatorname{Mod-}N$  steers N instructions to a cluster, the next N instructions to the next cluster, and so on in round robin fashion [BM00] as shown in Figure 2.8.  $\operatorname{Mod-}N$  is simple enough to be implemented in hardware.

Baniasadi and Moshovos compared several different steering policies and found that a simple Mod-3 steering policy performs relatively well on their microarchitecture configuration (four 2-issue clusters, 1-cycle intercluster delay) [BM00].

In contrast to solutions like Mod-N, simple and with little need of hardware modifications, algorithms that perform the steering by using a predictive heuristic have been studied. Tune et al. [TLTC01] proposed a steering policy based on the run-time predicted critical-path. In their architecture, each cluster has its issue queue and a copy of the register file. The critical-path predictor works with two simultaneous phases: identify instructions of critical paths and predict future critical instructions using those already identified. The instruction is identified as critical through a mechanism of threshold that uses a counter in a dedicated Critical Path Buffer. They found a better performance improvement for the simplest solution (the Blind one) when applied to the dual-cluster configuration, but for 4-cluster configuration the situation looks different and a more accurate (and complex) assignment is required.

More complex mechanisms of critical path detection were proposed, like the idea of Field, Rubin and Bodik [FRB01] based on the observation that the compiler ability to identify the critical path is limited to the data dependencies. They indicate that the critical path varies depending on the architecture's resource

Clustering 35