## Adaptive and Intelligent Memory Systems

Aswinkumar Sridharan

#### ▶ To cite this version:

As winkumar Sridharan. Adaptive and Intelligent Memory Systems. Hardware Architecture [cs. AR]. INRIA Rennes - Bretagne Atlantique and University of Rennes 1, France, 2016. English. NNT: . tel-01442465

## HAL Id: tel-01442465 https://inria.hal.science/tel-01442465

Submitted on 20 Jan 2017

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE / UNIVERSITÉ DE RENNES 1

sous le sceau de l'Université Européenne de Bretagne

pour le grade de

#### **DOCTEUR DE L'UNIVERSITÉ DE RENNES 1**

Mention: Informatique

École doctorale Matisse

présentée par

## Aswinkumar Sridharan

préparée à l'unité de recherche INRIA Institut National de Recherche en Informatique et Automatique – Université de Rennes 1

# Adaptive and Intelligent Memory Systems

# Thèse soutenue à Rennes le 15 Décembre 2016

devant le jury composé de :

#### Lionel LACASSAGNE

Professeur à University Pierre et Marie Curie / Président

#### Pierre Boulet

Professeur à l'Université de Lille 1 / Rapporteur

#### Stéphane MANCINI

Professeur à l'ENSIMAG, Institut Polytechnique de Grenoble / Rapporteur

#### Angeliki Kritikakou

Maître de conférence, Universite de Rennes 1 / Examinatrice

#### Biswabandan PANDA

PostDoc à l'INRIA Rennes – Bretagne Atlantique / Membre

#### André Seznec

Directeur de recherche à l'INRIA Rennes – Bretagne Atlantique / Directeur de thèse

# Acknowledgement

First of all, I would like to thank my parents for their unconditional support and love they have showered over all these years. I would also like to equally thank my sister for her constant support and encouragement.

Then, I wish to thank my friends (several of them): each one of them have contributed in his own way. Mentioning their names and their individual contributions would span multiple pages. I would also like to thank my lab and office mates, who were all helpful at different stages of my Ph.D.

I also take this opportunity to thank my teachers during school, college, and university who have taught me subjects and life lessons, which all have kept me in pursuit of higher education. In particular, I sincerely thank Prof. N. Venkateswaran (Waran), my undergraduate adviser who was very instrumental in my pursuing a Ph.D. He gave me an opportunity to work with him during my undergraduate days, which gave exposure to computer architecture.

I thank Professors at UPC, who taught me advanced courses in computer architecture. In particular, I thank Prof. (late) Nacho Navarro, who gave me an opportunity to work with him as an intern at Barcelona Supercomputing Center (BSC). My tenure as an intern exposed me to CUDA (GPU) programming.

I sincerely thank my Ph.D. adviser, Dr. Andre Seznec, for his guidance throughout the course of Ph.D. study. As an adviser, he was very instrumental in driving me along the right direction of work. He was always ready and available for discussions and give feedback on the work. His constant support has resulted in the timely completion of my Ph.D. I sincerely thank you once again!

I thank Dr. Biswabandan Panda for his useful discussions during the course of the second work. In particular, I thank your careful drafting of the paper during its submission. I equally cherish the cricket discussions we have had during the whole of last year!

I also take this opportunity to thank the jury members: Prof. Lionel Lacassagne for presiding over the jury, Prof. Pierre Boulet and Prof. Stephane Mancini for accepting to be the reporters of the thesis. I would also like to thank Prof. Angeliki Kritikakou for accepting to be the examinator of the defense.

Finally, I thank The Almighty for associating me with the right people.

Table of Contents

| A  | cknow  | ledgem  | ent                                                                                                            | -1 |

|----|--------|---------|----------------------------------------------------------------------------------------------------------------|----|

| Та | able o | f Conte | ents                                                                                                           | 0  |

| Rέ | ésumé  | en Fra  | ınçais                                                                                                         | 5  |

|    | 0.1    | Interfé | érence causée par le préchargement                                                                             | 7  |

|    | 0.2    | Quest   | ions de recherche                                                                                              | 8  |

|    | 0.3    |         | ibutions de cette thèse                                                                                        | 9  |

|    |        | 0.3.1   | Priorisation adaptive et discrète des applications                                                             | 9  |

|    |        | 0.3.2   | Préchargement passe-bande : Un mécanisme de gestion du précharge<br>ment basé sur la fraction de préchargement | 9  |

|    |        | 0.3.3   | Gestion des demandes de préchargement au cache de dernier niveau                                               |    |

|    |        |         | partagé en tenant en compte de la réutilisation des lignes                                                     | 10 |

|    | 0.4    | Organ   | sisation de la thèse                                                                                           | 10 |

| 1  | Intro  | oductio | n                                                                                                              | 11 |

|    | 1.1    | Proble  | em of Inter-application Interference                                                                           | 12 |

|    |        | 1.1.1   | Managing last level cache in the context of large scale multi-core                                             |    |

|    |        |         | systems                                                                                                        | 13 |

|    |        | 1.1.2   | Handling Prefetcher-caused Interference                                                                        | 13 |

|    | 1.2    | Resear  | rch Questions                                                                                                  | 14 |

|    | 1.3    | Thesis  | s Contributions                                                                                                | 15 |

|    |        | 1.3.1   | Adaptive and Discrete Application Prioritization for Managing                                                  |    |

|    |        |         | Last Level Caches on Large Multicores                                                                          | 15 |

|    |        | 1.3.2   | Band-pass Prefetching: A Prefetch-fraction driven Mechanism                                                    |    |

|    |        |         | for Prefetch Management                                                                                        | 15 |

|    |        | 1.3.3   | Reuse-aware Prefetch Request Management : Handling prefetch                                                    |    |

|    |        |         | requests at the shared last level cache                                                                        | 15 |

|    | 1.4    | Thesis  | s Organization                                                                                                 | 16 |

| 2  | Bacl   | kground | 1                                                                                                              | 17 |

|    | 2.1    | Cache   | Management Policies                                                                                            | 17 |

|    |        | 2.1.1   | Cache Replacement Policies                                                                                     | 18 |

|    |        |         | 2.1.1.1 Insertion Priority Prediction                                                                          | 19 |

|   |                       | 2.1.1.2 Reuse distance prediction                                           | 21  |

|---|-----------------------|-----------------------------------------------------------------------------|-----|

|   |                       | 2.1.1.3 Eviction priority prediction                                        | 22  |

|   |                       | 2.1.2 Cache Bypassing                                                       | 22  |

|   |                       | 2.1.3 Cache partitioning techniques                                         | 23  |

|   | 2.2                   | Cache Management in the presence of Prefetching                             | 24  |

|   |                       | 2.2.1 Managing prefetch requests at the shared cache                        | 24  |

|   |                       | 2.2.2 Prefetch-filter based Techniques                                      | 25  |

|   |                       | 2.2.3 Adaptive Prefetching Techniques                                       | 26  |

|   | 2.3                   | Conclusion                                                                  | 26  |

| 3 | Disc                  | crete and De-prioritized Cache Insertion Policies                           | 29  |

|   | 3.1                   | Introduction                                                                | 29  |

|   | 3.2                   | Motivation                                                                  | 30  |

|   |                       | 3.2.1 A case for discrete application prioritization:                       | 32  |

|   | 3.3                   | Adaptive Discrete and de-prioritized Application PrioriTization             | 33  |

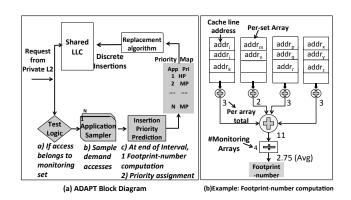

|   |                       | 3.3.1 Collecting Footprint-number                                           | 34  |

|   |                       | 3.3.2 Footprint-number based Priority assignment                            | 35  |

|   |                       | 3.3.3 Hardware Overhead                                                     | 37  |

|   |                       | 3.3.4 Monitoring in a realistic system:                                     | 37  |

|   | 3.4                   | Experimental Study                                                          | 38  |

|   |                       | 3.4.1 Methodology                                                           | 38  |

|   |                       | 3.4.2 Benchmarks                                                            | 39  |

|   |                       | 3.4.3 Workload Design                                                       | 40  |

|   | 3.5                   | Results and Analysis                                                        | 40  |

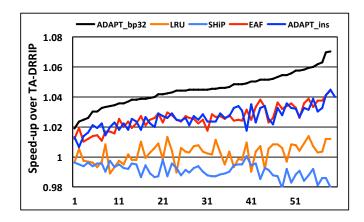

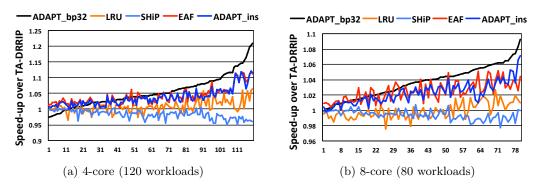

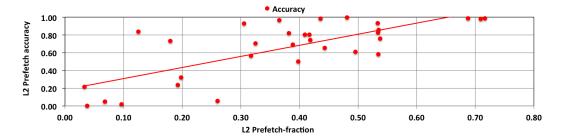

|   |                       | 3.5.1 Performance on 16-core workloads                                      | 40  |

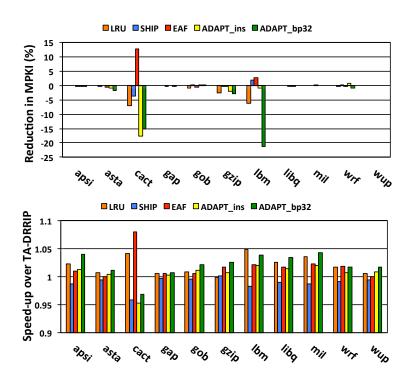

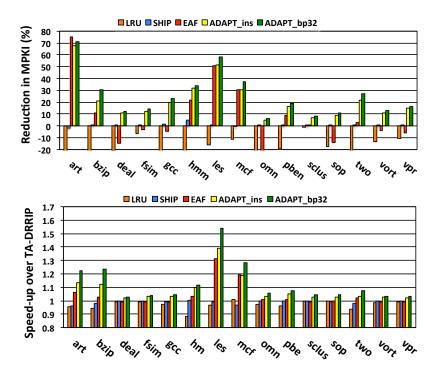

|   |                       | 3.5.2 Impact on Individual Application Performance                          | 42  |

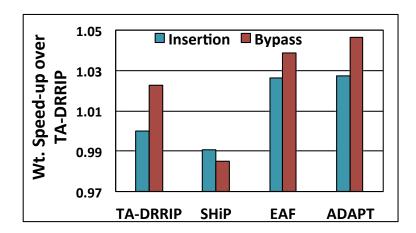

|   |                       | 3.5.3 Impact of Bypassing on cache replacement policies                     | 42  |

|   |                       | 3.5.4 Scalability with respect to number of applications                    | 44  |

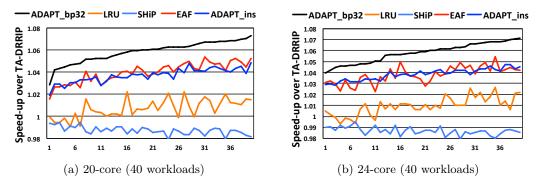

|   |                       | 3.5.5 Sensitivity to Cache Configurations                                   | 45  |

|   | 3.6                   | Conclusion                                                                  | 45  |

| 4 | Ban                   | d-pass Prefetching: A Prefetch-fraction driven Prefetch Aggressiveness Con- |     |

|   | $\operatorname{trol}$ | Mechanism                                                                   | 47  |

|   | 4.1                   | Introduction                                                                | 47  |

|   | 4.2                   | Background                                                                  | 48  |

|   |                       | 4.2.1 Baseline Assumptions and Definitions                                  | 49  |

|   |                       | 4.2.2 Problem with the state-of-the-art Mechanisms                          | 49  |

|   | 4.3                   | Motivational Observations                                                   | 50  |

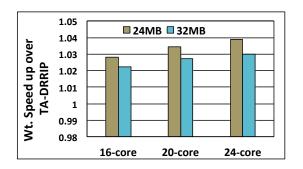

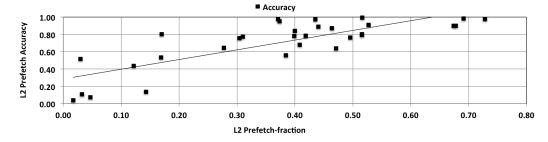

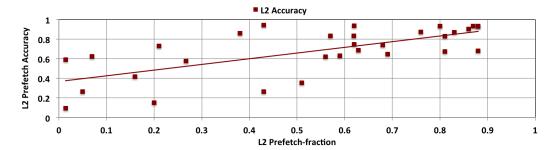

|   |                       | 4.3.1 Correlation between Prefetch-accuracy and Prefetch-fraction           | 50  |

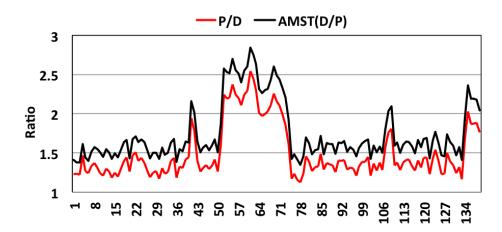

|   |                       | 4.3.2 Correlation between Prefetcher-caused delay and Prefetch-fraction     | 52  |

|   | 4.4                   | Band-pass prefetching                                                       | 53  |

|   |                       | 4.4.1 High-pass Prefetch Filtering                                          | 53  |

|   |                       | 4.4.1.1 Measuring Prefetch-fraction                                         | 54  |

|   |                       | 4.4.2. Low page Profetch Filtening                                          | E 1 |

|    |        |                            | 4.4.2.1 Estimation of Average Miss Service Time            | 55         |  |  |

|----|--------|----------------------------|------------------------------------------------------------|------------|--|--|

|    |        | 4.4.3                      | Overall Band-Pass Prefetcher                               | 57         |  |  |

|    | 4.5    | Experi                     | mental Setup                                               | 58         |  |  |

|    |        | 4.5.1                      | Baseline System                                            | 58         |  |  |

|    |        | 4.5.2                      | Benchmarks and Workloads                                   | 58         |  |  |

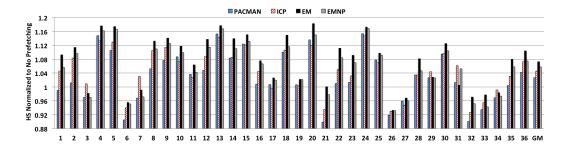

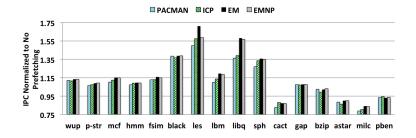

|    | 4.6    | Results                    | s and Analyses                                             | 60         |  |  |

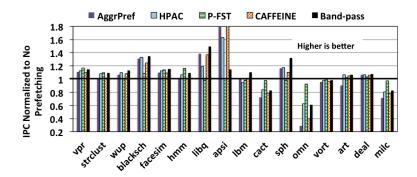

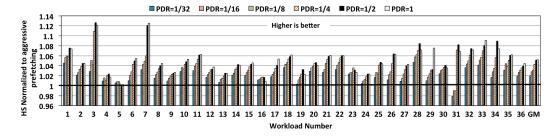

|    |        | 4.6.1                      | Performance of High-pass Prefetching                       | 60         |  |  |

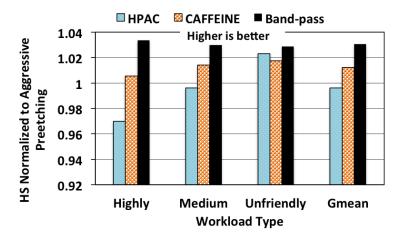

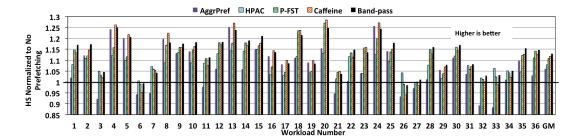

|    |        | 4.6.2                      | Performance of Band-pass Prefetching                       | 61         |  |  |

|    |        | 4.6.3                      | Impact on Average Miss Service Times                       | 62         |  |  |

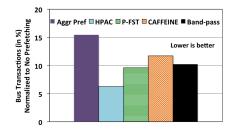

|    |        | 4.6.4                      | Impact on Off-chip Bus Transactions                        | 63         |  |  |

|    |        | 4.6.5                      | Understanding Individual Mechanisms                        | 64         |  |  |

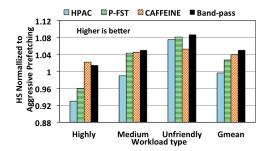

|    |        | 4.6.6                      | Sensitivity to Workload Types                              | 65         |  |  |

|    |        | 4.6.7                      | Sensitivity to Design Parameters                           | 66         |  |  |

|    |        | 4.6.8                      | Sensitivity to AMPM Prefetcher                             | 68         |  |  |

|    |        |                            | 4.6.8.1 Impact on Off-chip Bus Transactions:               | 69         |  |  |

|    |        |                            | 4.6.8.2 Sensitivity to Workload Types:                     | 70         |  |  |

|    |        | 4.6.9                      | Using prefetcher-accuracy to control aggressiveness        | 70         |  |  |

|    |        | 4.6.10                     | Hardware Overhead                                          | 70         |  |  |

|    | 4.7    | Conclu                     | sion                                                       | 71         |  |  |

| 5  | Reus   | se-aware                   | e Prefetch Request Management                              | 73         |  |  |

|    | 5.1    | Introdu                    | $\operatorname{uction}$                                    | 73         |  |  |

|    | 5.2    | Backgr                     | ound                                                       | <b>7</b> 4 |  |  |

|    | 5.3    | Experi                     | mental Setup                                               | 75         |  |  |

|    |        | 5.3.1                      | Baseline System                                            | 75         |  |  |

|    |        | 5.3.2                      | Benchmarks and Workloads                                   | 76         |  |  |

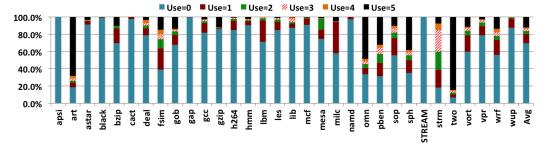

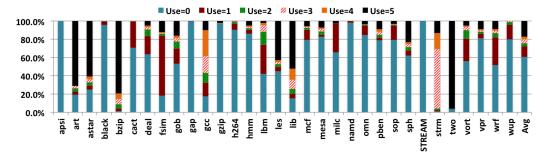

|    | 5.4    | Motiva                     | ational Observations                                       | 77         |  |  |

|    | 5.5    | Reuse-                     | aware Prefetch Management                                  | 80         |  |  |

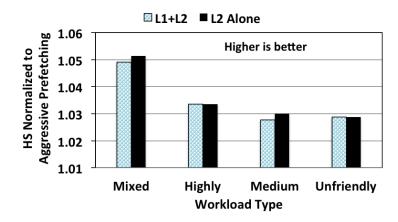

|    |        | 5.5.1                      | Understanding the Prefetch Request Management Mechanisms . | 80         |  |  |

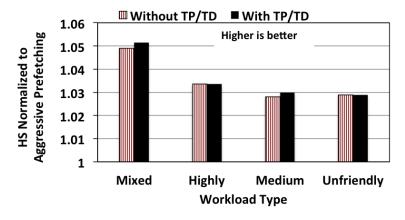

|    | 5.6    | Enhan                      | cing the State-of-the-art Mechanisms                       | 82         |  |  |

|    | 5.7    | Inferen                    | ice                                                        | 84         |  |  |

|    | 5.8    | Conclu                     | sion                                                       | 84         |  |  |

| 6  | Cone   | Conclusion and Future Work |                                                            |            |  |  |

|    | 6.1    | Perspe                     | ctives                                                     | 87         |  |  |

|    |        | 6.1.1                      | Managing last level caches                                 | 87         |  |  |

|    |        | 6.1.2                      | Prefetcher Aggressiveness Control                          | 88         |  |  |

| Gl | ossar  | y                          |                                                            | 89         |  |  |

| Βi | bliogr | anhv                       |                                                            | 99         |  |  |

|    | Ü      |                            |                                                            |            |  |  |

| Ta |        | figures                    |                                                            | 101        |  |  |

# Résumé en Français

L'écart de performance entre le processeur et la mémoire (DRAM) se creuse de plus en plus, au point d'être appelé "mur mémoire" ". Ce terme se réfère à l'augmentation du nombre de cycles processeur nécessaire pour effectuer un accès mémoire (c'est-à-dire accéder à un circuit en dehors de la puce contenant le processeur) à mesure que de nouvelles générations de processeurs sont conçues. Alors que les architectes étaient au courant de cet écart croissant, Wulf et McKee ont été parmi les premiers chercheurs à formuler ce phénomène dont l'impact allait grandissant. Cet écart de performance croissant entre le processeur et le système mémoire est dû au technologies disparates avec lesquelles les deux composants sont mises en œuvre. En effet, les fabricants de puces (ex., processeurs) sont capables de réduire la taille des transistors, tandis qu'il est difficile de réduire la taille des condensateurs (utilisés dans la mémoire), en raison de problèmes de fiabilité.

Les premières solutionsà ce problème sont axées sur le maintien du processeur occupé quand il est en attente de données venant de la mémoire, en l'autorisantà exécuter des instructions dans le désordre, ainsi que sur l'émission de multiples instructions par cycle, mécanismes qui exploitent le parallélisme niveau instruction (ILP). Le préchargement de données depuis la mémoire dans des mémoires caches directement sur la puce ainsi que l'utilisation de caches multi-niveaux permettent aussi de limite l'impact du "mur mémoire". Les recherches ultérieures dans cette direction se sont concentrées sur la conception de meilleures techniques micro-architecturales pour améliorer les performances du processeur et cette tendance a continuée au cours d'une décennie entre les années 90 et le début des années 2000. Cependant, des facteurs tels que l'augmentation de la complexité de la conception de tels systèmes, les limites sur l'ILP extractible ainsi que les questions de puissance et de température, ont contraints les fabricants de processeurs de porter leur attention vers la réplication de plusieurs processeurs (cœurs) sur une même puce pour de meilleures performances.

D'une part, la réduction de la taille des transistors décrite par la loi de Moore permet d'intégrer plus de transistors sur une surface donnée. Par conséquent, à chaque génération de processeurs, les fabricants de puces continuent d'intégrer plus de cœurs afin d'utiliser les transistors disponibles. Déjà, il existe des systèmes possédant plusieurs dizaines de cœurs. Cette tendanceà l'intégration de plus de cœurs sur les processeurs est susceptible de se poursuivreà l'avenir, car elle augmente les capacités de calcul en augmentant le nombre d'opérations qui peuvent être effectuées par unité de temps. Dans le même temps, on augmente la quantité de données transférée sur la puce afin

d'être que lesdites données soient traitées. Par conséquent, le système mémoire doit pouvoir fournir des données à tous les cœurs pour une performance soutenue. Cependant, la vitesse du système mémoire reste plus faible que la vitesse du processeur. Cela différence est exacerbée dans les processeurs multi-cœurs car le système mémoire est maintenant partagé par plusieurs cœurs. Typiquement, un accès à la mémoire passe par différentes structures (files d'attente), qui sont soumises à divers délais en fonction de la vitesse à laquelle les demandes de mémoire sont traitées ainsi que des différents retards d'ordonnancement. Les délais dus à ces files d'attente impactent les performances des processeurs multi-cœurs.

Ce problème est encore aggravé par la limitation des ressources qui connectent le processeur et la mémoire. En particulier, le processeur est connectéà la mémoire des broches et des canaux métalliques sur la carte mère. Ces broches et fils forment le bus mémoire, qui est coûteux en terme de consommation d'énergie et en latence. L'ITRS prévoit que le nombre de broches qui relient le processeur avec le bus de la mémoire n'augmente que 10 % par an par rapport au nombre de cœurs par processeur, qui double tous les dix-huit mois. Par conséquent, la quantité de données qui peuvent être transféréesà partir du système mémoire vers chaque cœur du processeur est de plus en plus limitée, ce qui ajoute au problème de latence des systèmes mémoires. Au total, le " mur mémoire " peut être considéré comme étant composé du " mur de la latence " et du " mur du débit ".

Problème d'interférences inter-applications Dans les paragraphes précédents, nous avons discuté des limitations technologiques du système mémoire et par conséquent, son manque de performance par rapport aux processeurs modernes. Alors que les contraintes technologiques servent comme un facteur limitant la performance de la mémoire et par conséquent, la performance globale du système multi-cœurs, le caractère partagé de la hiérarchie mémoire, à savoir le cache de dernier niveau et les canaux mémoires liant le processeur au système mémoire, ajouteà ce problème. Les applications ont tendanceà interférer les unes avec les autres au niveau de ces ressources partagées. Par exemple, une ligne de cache peut être expulsée par une ligne de cache d'une autre application, un phénomène connu comme la "pollution de cache". De même, le grand nombre de requêtes mémoire générées par les applications agressives peuvent retarder le traitement des requêtes générées par d'autres applications. Ces deux problèmes sont exacerbés en présence de préchargement, à cause duquel les interférences dues au partage des ressources mémoires (cache(s) et canaux) pourrait conduireà des ralentissements encore plus prononcés. Par conséquent, les processeurs haute performance utilisent des mécanismes pour gérer les interférences entre les applications au niveau des ressources partagées. L'objectif de cette thèse est d'aborder ces deux problèmes dans le contexte des processeurs many-coeurs, c'est-à-dire les systèmes multi-cœurs avec seize ou plusieurs cœurs sur une puce. Dans les paragraphes qui suivent, nous examinons les deux problèmes dans le contexte des systèmes multi-cœursà grande échelle (many-cœurs).

Gestion du dernier niveau de cache dans le contexte des processeurs many-coeurs

L'augmentation du nombre d'applications en cours d'exécution sur un processeur multi-cœurs augmente la diversité des différentes charges de travail auxquelles le système mémoire doit répondre. En particulier, le cache de dernier niveau est partagé

par des applications se comportant différemment dans leurs accès au système mémoire (i.e., nombre d'accès, motifs d'adresses). Pour utiliser efficacement la capacité de la mémoire cache, l'algorithme de gestion de cache doit prendre en compte les différentes caractéristiques des applications, et donc prioriser l'accèsà la mémoire cache partagée. La nécessité d'attribuer des priorités différentes aux multiples applications s'exécutant de façon concurrente est aussi une conséquence des besoins en performance et en équité des systèmes haute performance commerciaux (i .e., cloud, datacenters). De tels systèmes, où les ressources de la hiérarchie de mémoire sont partagées entre les applications, nécessitent l'attribution de différentes priorités aux applications selon leur caractère critique (pour une certaine définition de critique). Pour répondreà une telle exigence, un nouveau mécanisme pouvant capturer efficacement les différents comportements des applications lors de l'exécution et permettantà la politique de gestion du cache d'appliquer des priorités différentes entre les applications est nécessaire.

Des mécanismes antérieurs ont proposé différentes façons de prédire le comportement des applications relatifsà la réutilisation de lignes de mémoire cache. DIP, TA-DIP et TA-DRRIP peuvent prédire le comportement des applications en mettant en œuvre des politiques complémentaires pour déterminer si une application tire des bénéfices de la présence du cache, ou non. Le prédicteur Hit-Predictor, basé sur les signatures, utilise une région de la mémoire ou de compteurs de programmes (PC) pour prédire le comportement de réutilisation de ces régions de mémoire ou PCs. De même, Evicted Adress Filter (EAF) prédit au niveau de la ligne de cache. Dans tous ces mécanismes, le principe sous-jacent est d'observer les accès réussis ou manqués de groupe de lignes ou de lignes de cache et de prédire le comportement de réutilisation. Ces mécanismes ont été développés pour des systèmes simples, puis étendu aux systèmes multi-cœurs (jusqu'à 4 cœurs). Cependant, une telle approche n'est pas fiable dans le contexte des processeurs many-cœurs. Un défaut de cache ne reflète pas nécessairement le comportement réel d'une application. En effet, les défauts de cache ne sont pas seulement une conséquence du comportement de l'application; ils sont également une conséquence du comportement des autres applications s'exécutant de façon concurrente. Par conséquent, un nouveau mécanisme qui capture efficacement la façon dont une application peut utiliser le cache est nécessaire. La première partie de cette thèse se concentre sur ce mécanisme.

## 0.1 Interférence causée par le préchargement

Le préchargement matériel est un mécanisme visantà cacher la latence du système mémoire utilisé dans les processeurs commerciaux. Il fonctionne par l'apprentissage d'un motif dans les accèsà la mémoire cache (il considère les adresses de blocs) et l'envoi de requêtes vers la mémoire afin de précharger des blocs de cache l'application peut accéderà l'avenir. Un préchargement permettant d'obtenir un bloc en temps voulu permet de complètement masquer la latence de la mémoire. Cependant, une ligne de cache préchargée qui n'est au final jamais accédée par le processeur gaspille de la bande passante et peut expulser un bloc de cache utile lors de son insertion. Le préchargement

peut également retarder les accès d'autres applications. Alors que les effets positifs et négatifs du préchargement ont été étudiées dans le contexte des uniprocesseurs (un seul cœurs), son impact est d'autant plus important dans le contexte des systèmes multicœurs et many-coeurs. Par conséquent, le préchargement agit comme une épéeà double tranchant et exige une gestion attentive. Cette gestion peut être approchée selon deux dimensions. Tout d'abord, le contrôle du nombre de demandes de préchargement qui sont émises dans le système et d'autre part, la gestion des priorités des demandes de préchargement au niveau cache partagé. Les deuxième et troisième contributions de cette thèse sont axées sur ces deux problèmes.

Des travaux antérieurs sur le contrôle de l'agressivité de l'unité de préchargement tels que hiérarchique (ACVL) et CAFÉINE n'atténuent pas complètement les interférences causées par l'unité de préchargement dans les systèmes multi-cœurs. ACVL utilise plusieurs paramètres, qui selon leurs valeurs, permettent d'inférer qu'une application donnée interfère. Cependant, les différents seuils d'inférence conduisentà des décisions incorrectes sur les applications qui provoquent des interférences car la valeur de seuil d'une métrique donnée ne reflète pas bien le comportement d'une application, en raison du grand nombre d'applications s'exécutant de façon concurrente. De même, CAFÉINE utilise une méthode approximative pour estimer la latence d'accès moyenneà la mémoire pour mesurer les économies en cycles en raison de préchargement. Cependant, cette approximation conduità des décisions biaisées en faveur de préchargement agressif, en ne tenant pas comptes des interférences potentielles. Au total, ces mécanismes fournissent encore de la place pour une meilleure gestion des ressources partagées en présence de préchargement.

Pour traiter les demandes de préchargement dans les caches partagés, les travaux antérieurs tels que Prefetch-Aware Cache Management (PACMAN) et (ICP) observent le comportement de la réutilisation des lignes de cache préchargées dans le contexte de caches de petites tailles. Plus précisément, les deux contributions supposent implicitement que les blocs de cache préchargés sontà usage unique. Cependant, dans le contexte de caches plus grands, cette hypothèse n'est pas toujours vraie ; les lignes de cache préchargées ont un comportement de réutilisation différent. Par conséquent, il y a possibilité de mieux gérer les demandes de préchargement dans les caches partagés.

#### 0.2 Questions de recherche

Dans le sillage des discussions présentées ci-dessus, cette thèse se concentre sur les réponses aux questions de recherche suivantes :

Question 1: Y at-il un mécanisme de gestion de la mémoire cache qui est capable d'isoler efficacement le comportement applications dynamiquement, et qui permet une meilleure gestion de la mémoire cache partagée lorsqu'un grand nombre d'applications partagent le cache?

Question 2: Y at-il un mécanisme pratique qui traite efficacement les interférences causées par l'unité de préchargement dans les systèmes multi-cœurs?

Question 3: Y at-il un mécanisme de gestion de cache qui prend également en compte

les caractéristiques de l'utilisation des données préchargées pour une meilleure gestion?

#### 0.3 Contributions de cette thèse

Dans cette thèse, nous proposons des solutions qui tentent de résoudre chacune des questions de recherche mentionnés ci-dessus. Nos solutions aux problèmes sont les contributions de cette thèse:

#### 0.3.1 Priorisation adaptive et discrète des applications

Pour faire face aux interférences au niveau de la mémoire cache partagée, nous introduisons le numéro d'empreinte afin d'approcher dynamiquement l'empreinte de cache (le nombre de lignes du cache appartenantà l'application) des applicationsà l'exécution. Pour un cache donné, le numéro d'empreinte est défini comme étant le nombre d'accès uniques (adresses de blocs de mémoire cache) qu'une application génère vers ce cache dans un intervalle de temps. Puisque le numéro d'empreinte se rapproche explicitement et quantifie la taille du jeu de travail des applications, il prévoit la possibilité d'attribuer des priorités différentesà chaque application. Puisque nous utilisons des circuits indépendants en dehors la structure de cache principale pour estimer le numéro d'empreinte, il n'est pas affecté par les succès/échecs qui se produisent au niveau du cache partagée. Le comportement d'une application en isolation est donc correctement capturé. Sur la base des valeurs estimées de numéros d'empreintes, l'algorithme de remplacement détermine les priorités à attribuer aux applications. Au total, l'estimation du numéro d'empreinte permet (i) de faire appliquer différentes priorités (discrètes) aux différentes applications et (Ii) capturer efficacement l'utilitaire de cache des applications.

# 0.3.2 Préchargement passe-bande : Un mécanisme de gestion du préchargement basé sur la fraction de préchargement

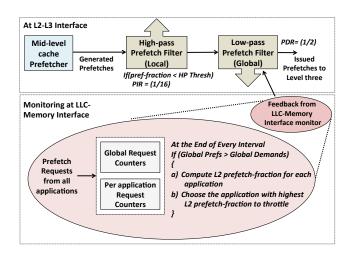

Notre solution repose sur deux observations fondamentales sur l'utilité du préchargement et les interférences causées par l'unité de préchargement. En particulier, nous observons (i) une forte corrélation positive existe entre la quantité de demandes de préchargement qu'une application génère et la précision du préchargement. Autrement dit, si la fraction de demandes de préchargement générée est faible, la précision de l'unité de préchargement est également faible. La deuxième observation est que plus le nombre total de demandes de préchargement dans le système est grand, plus la pénalité dueà l'absence d'une ligne dans le cache de dernier niveau est grande. Sur la base de ces deux observations, nous introduisons le concept de fraction de préchargement, afin de déduireà la fois l'utilité du préchargement et les interférences causées par l'unité de préchargement. Notre mécanisme contrôle le flux de demandes de préchargement en fonction de la fraction de préchargement, de façon analogue au filtre passe-bande venant du domaine du traitement du signal. Par conséquent, nous nous référonsà ce mécanisme comme le préchargement passe-bande.

# 0.3.3 Gestion des demandes de préchargement au cache de dernier niveau partagé en tenant en compte de la réutilisation des lignes

Notre solution permet l'observation que les blocs de cache préchargés ont différentes caractéristiques d'utilisation. Dans une application, certains blocs de cache préchargés sont accédésà plusieurs reprises tandis que d'autres ne sont pas utilisés du tout. Nous observons également que l'utilisation du préchargement varie selon les applications. Par conséquent, nous mesurons les caractéristiques d'utilisation des blocs de cache préchargésà l'exécution pour déterminer leurs priorités lors de remplacements dans le cache de dernier niveau.

#### 0.4 Organisation de la thèse

Le reste de la thèse est organisé comme suit: dans le chapitre 2, nous présentons la gestion de la mémoire cache partagée et la gestion des interférences lors des accèsà la mémoire partagée. Ensuite, nous discutons des mécanismes état de l'art qui ont été proposées pour traiter les deux problèmes que la thèse tente de résoudre. Parallèlement, nous décrivons également leurs lacunes. Dans le chapitre 3, nous présentons notre première solution: un mécanisme adaptatif de priorisation d'application qui gère le cache partagé de dernier niveau. Nous décrivons notre mécanisme de suivi qui capture le numéro d'empreinte des applications, et notre algorithme de remplacement, qui utilise des numéros d'empreintes pour attribuer des priorités aux lignes de cache des différentes applications. Ensuite, nous évaluons notre solution et comparons nos mécanismesà l'état de l'art. Dans le chapitre 4, nous présentons le préchargement passe-bande, et discutons en détail les deux observations qui conduisentà la solution proposée, notre approche pratique pour mesurer la durée moyenne d'une requête mémoire. Nous évaluons ensuite notre contribution et le comparonsà l'état de l'art des mécanismes de contrôle de l'agressivité de l'unité de préchargement. Le chapitre 5 présente notre troisième contribution. Nous décrivons notre mécanisme pour estimer les caractéristiques d'utilisation de l'unité de préchargement puis décrivons l'algorithme qui exploite les caractéristiques d'utilisation pour attribuer des priorités aux demandes de préchargement. Par la suite, nous présentons notre évaluation et la comparaison par rapport aux mécanismes pertinents de l'état de l'art. Enfin, nous présentons notre conclusion et les directions pour la recherche future dans le dernier chapitre.

## Chapter 1

## Introduction

The growing performance gap between the processor and the DRAM based memory systems is referred to as the Memory Wall. In particular, it refers to the growing increase in number of processor cycles it takes for an off-chip memory access to be serviced by the memory system, as we move from one generation to the next generation of processor chips. While architects had been aware of this growing discrepancy, Wulf and Mckee [WM95] were one of the first researchers to formulate this then impending phenomenon. This growing performance gap between the processor and the memory system is due to disparate technologies with which the two components are implemented, because chip makers are able to scale down the size of transistors, while capacitors do not scale down as gracefully as transistors due to reliability issues of capacitors.

Early solutions to this problem focused on keeping the processor busy while it is waiting for the data from memory by executing instructions out-of-order, mechanisms that exploit Instruction Level Parallelism (ILP) through issuing multiple instructions, pre-fetching data from the memory and storing them on the on-chip caches, and employing multi-level caches. Subsequent research along this direction focussed on designing better micro-architectural techniques to improve processor performance and this trend continued over a decade between the 90s and early 2000s. However, factors such as increasing design complexity of such systems, limits on the extractable ILP, power and thermal issues, forced chip makers to shift their focus toward replicating or employing multiple processor cores on the same chip, Chip Multi-Processing (CMP), or Multi-core processors for higher performance.

On the one hand, transistor scaling driven by Moore's law allows to pack more transistors in a given area of a chip. Consequently, with every generation of processors, chip makers keep packing more cores. Already, there are systems that host multiple processor cores and that are capable of running tens of threads. This trend of packing more processor cores on a chip is likely to continue in the future. Integrating more cores on a processor chip increases the computational capabilities in terms of the number of operations that can be performed per unit of time. At the same time, it increases the amount of data that has to be brought on-chip to process. Therefore, the memory system is expected to provide data to the processor at a higher rate for sustained

12 Introduction

performance. However, the speed of the memory system continues to lag behind the processor speed. This becomes even more critical in multi-core processors, because the memory system is now shared by multiple cores. Typically, an access to the memory goes through different queuing structures, which are subject to various queuing delays depending on the rate at which the memory requests are cleared and scheduling delays. The delay on these queuing structures impact the performance of these processor cores.

This problem is further exacerbated by the limitation of resources that connect processor and memory systems. A processor chip is connected to the memory chip by pins and metal channels on the motherboard. These pins and wires form the memory bus, which is expensive in terms of power consumption and implementation [Onu, RKB+09, ITR]. ITRS [ITR] predicts that the number of pins, which connect the processor with the memory bus grows only 10% per year as compared to the number of processor cores, which doubles every eighteen months. Therefore, the amount of data that could be transferred from the memory system to the processor is also limited, which adds to the memory systems' latency problem. While latency wall is prevalent in single-core performance, its combination with limited bandwidth availability limits the performance of a multi-core system. The phenomenon in which the bandwidth becomes a major bottleneck factor in achievable system performance is referred to as the Bandwidth wall [RKB+09]. Altogether, the memory wall can be viewed as to comprise of the latency wall and the bandwidth wall [Pat04].

### 1.1 Problem of Inter-application Interference

In the previous section, we discussed the technological limitations of the memory system and hence, its performance lag with respect to the processor cores. While technological constraints serve as one limiting factor to memory performance and hence, overall multi-core system performance, the shared nature of the memory-hierarchy, namely the last level cache and off-chip memory channels, adds to this problem. Applications tend to interfere with each other at these shared resources. For example, a cache line of one application could be evicted by a cache line of another application, which is referred to as Cache Pollution. Similarly, memory requests of memory-intensive applications could delay the service of other meek applications, or delay each other at the off-chip memory access. These two problems are exacerbated in the presence of prefetching<sup>1</sup>, and interference at these shared resources could lead to severe slow-down [EMLP09, ELMP11, WJM<sup>+</sup>11, SYX<sup>+</sup>15, PB15, JBB<sup>+</sup>15, Pan16, LMNP08, LS11, BIM08]. Therefore, highperformance processors employ mechanisms to manage interference among applications at these shared resources. The goal of this thesis is to address these two problems in the context of large scale multi-core processors. That is, multi-core systems with sixteen or more cores on a chip. In the following subsections, we discuss the two problems in the context of large-scale multi-core systems.

<sup>&</sup>lt;sup>1</sup>We define prefetching shortly.

# 1.1.1 Managing last level cache in the context of large scale multi-core systems

Increasing the number of applications that run on a multi-core processor increases the diversity of characteristics and the memory demands the system must cater to. In particular, the last level cache is shared by applications with diverse memory behaviors. For efficiently utilizing the cache capacity, the cache management algorithm must take into account the diverse characteristics of applications, and accordingly prioritize them at the shared cache. Further, the need for enabling different priorities across applications is fueled by the fairness and performance objectives of commercial grid systems. Such commercial systems, where the memory-hierarchy resources are shared among applications, require enforcing different priorities across applications depending on their criticality, cost-involved, and other factors. In order to meet such a requirement, a new mechanism that effectively captures the diverse behaviors of applications at run-time and allows the cache management policy to enforce different priorities across applications, is needed.

Prior mechanisms have proposed different ways to predict the reuse behavior of applications. Dynamic Insertion Policies [QJP+07], Thread Aware-Dynamic Insertion Policies [JHQ<sup>+</sup>08] and Thread Aware-Dynamic ReReference Interval Prediction [JTSE10] predict the behavior by implementing complementary policies to determine if an application is cache friendly or not. Signature based Hit-Predictor [WJH<sup>+</sup>11] uses memory region or Program counter (PC) signatures to predict the reuse behavior on these memory or PC regions. Similarly, Evicted Address Filter (EAF) [SMKM12] makes prediction on a per-cache line basis. In all these mechanisms, the underlying principle is to observe the hits or misses on individual cache lines or a group of cache lines and predict the reuse behavior. These mechanisms have been developed for single core systems and then extended to multi-cores (up to 4 cores). However, such an approach is not accurate or reliable in the context of large scale multi-cores. A cache miss does not necessarily reflect the actual reuse behavior of an application, because cache misses are not only a consequence of the reuse behavior of the application; they are also a consequence of the behavior of co-running applications. Therefore, a new mechanism that efficiently captures how well an application could utilize the cache is needed. The first part of the thesis focusses on addressing this problem.

#### 1.1.2 Handling Prefetcher-caused Interference

Hardware prefetching is a memory latency hiding mechanism employed in present day commercial processors. It works by learning a pattern in cache accesses (in block addresses) and issues prefetch requests on the possible cache block addresses that the application may access in the future. A timely prefetch request completely hides the off-chip latency of the memory access. However, a prefetched cache line that is never accessed wastes bandwidth and may evict a useful cache block. Prefetching may also delay the demand requests of other applications apart from wasting bandwidth and polluting useful cache lines. While both positive and negative effects of prefetching have been

14 Introduction

studied in single-core context [SMKP07, WJM<sup>+</sup>11, SYX<sup>+</sup>15], its impact is more so in the context of multi-core system. Therefore, prefetching acts as a double-edged sword and requires careful management at the shared memory-hierarchy. Handling prefetch requests at the shared memory resources (last level cache and off-chip memory access) can be viewed in two-dimensions. Firstly, controlling the number of prefetch requests that are issued in the system and secondly, to manage the priorities of prefetch requests at the shared cache. The second and third contributions of this thesis are focussed on these two problems.

Prior works on prefetcher aggressiveness control such as Hierarchical Prefetcher Aggressiveness Control (HPAC) [EMLP09] and CAFFEINE [PB15] do not completely alleviate the problem of prefetcher-caused interference in multi-core systems. HPAC uses multiple metrics, which are driven by their threshold values, to infer interference by a given application. However, threshold based inference of interference lead to incorrect decisions on the applications that cause interference because threshold value of a given metric does not reflect the run-time behavior of an application due to interference caused when large number of applications run on the system. Similarly, CAFFEINE uses an approximate method to estimate average memory access latency to measure savings in cycles due to prefetching (that is, prefetch usefulness). However, approximating average memory access latency estimation leads to biased decisions in favor of aggressive prefetching, overlooking interference. Altogether, these mechanisms still provide room for better managing shared resources in the presence of prefetching.

To handle prefetch requests at the shared caches, prior works such as Prefetch-Aware Cache Management (PACMAN) [WJM+11] and Informed Cache Prefetching (ICP) [SYX+15] observe the reuse behavior of prefetched cache lines from the context of small caches. Specifically, the two works implicitly assume prefetched cache blocks as single use (that is, used only once) cache blocks. However, in the context of larger caches, this observation does not always hold true; prefetched cache lines have different reuse behavior. Therefore, there is more opportunity to better manage the prefetch requests at the shared last level caches.

#### 1.2 Research Questions

In the wake of the discussions presented above, this thesis focusses on answering the following research questions:

- Question 1: Is there a cache management mechanism that is able to efficiently isolate applications' run-time behavior, and that allows for better shared cache management when large number of applications share the cache?

- Question 2: Is there a practical mechanism that efficiently addresses prefetchercaused interference in multi-core systems?

- Question 3: Is there a cache management mechanism that also takes into account prefetched data's reuse characteristics for better management?

Thesis Contributions 15

#### 1.3 Thesis Contributions

In this thesis, we propose solutions that attempt to solve each of the aforementioned mentioned research questions. Our solutions to the problems are the contributions of this thesis:

#### 1.3.1 Adaptive and Discrete Application Prioritization for Managing Last Level Caches on Large Multicores

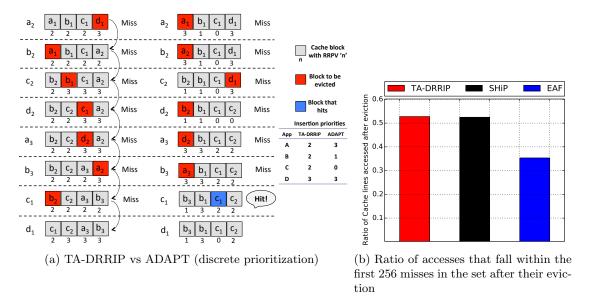

To address interference at the shared cache, we introduce the Footprint-number metric to dynamically approximate the last level cache footprint of applications at run-time. Footprint-number is defined as the number of unique accesses (cache block addresses) that an application generates to a cache set in an interval of time. Since Footprint-number explicitly approximates and quantifies the working-set size of applications, it provides scope for implementing different priorities across applications. Since we use independent circuits outside the main cache structure to estimate Footprint-number, it is not affected by the hits/misses that happen at the shared cache. An application's isolated cache utility is reliably captured. Based on the estimated Footprint-number values, the replacement algorithm decides the priorities across applications. Altogether, Footprint-number estimation allows (i) to enforce different (discrete) priorities across applications and (ii) efficiently capture the cache utility of applications.

# 1.3.2 Band-pass Prefetching: A Prefetch-fraction driven Mechanism for Prefetch Management

Our solution is built upon two fundamental observations on prefetch usefulness and prefetcher-caused interference. In particular, our work finds (i) a strong positive correlation to exist between the amount of prefetch requests an application generates and prefetch-accuracy. That is, if the fraction of prefetch requests generated is low, the accuracy of the prefetcher is also low. The second observation is that, the more the aggregate number of prefetch requests in the system, the higher the miss penalty on the demand misses at the last level cache. Based on the two observations, we introduce the concept of prefetch-fraction to infer both prefetch-usefulness and prefetcher-caused interference. Prefetch-fraction of an application is defined as the fraction of L2 prefetch requests the prefetcher of an application generates with respect to its total requests (demand misses, L1 and L2 prefetch requests). Using prefetch-fraction, our mechanism controls the flow of prefetch requests between a range of prefetch-to-demand ratios, which is analogous to Band-pass filter from signal processing domain. Hence, we refer to this mechanism as Band-pass prefetching.

# 1.3.3 Reuse-aware Prefetch Request Management : Handling prefetch requests at the shared last level cache

Our solution makes observation that prefetched cache blocks have different use characteristics. Within an application, some prefetched cache blocks are accessed multiple

times while some others are not used at all. We also observe that prefetch use characteristics vary across applications. Therefore, we measure the use characteristics of prefetched cache blocks at run-time to determine their priorities during cache replacements at the last level cache.

#### 1.4 Thesis Organization

The remainder of the thesis is organized as follows: in Chapter 2, we present the background on shared cache management and managing interference at the shared off-chip memory access. Then, we discuss state-of-the art mechanisms that have been proposed to handle the two problems that the thesis attempts to solve. Alongside, we also describe their shortcomings. In Chapter 3, we present our first solution: An Adaptive and Discrete Application Prioritization mechanism that manages shared last level caches. We describe our monitoring mechanism that captures Footprint-numbers of applications, and our replacement algorithm, which uses Footprint-number values to assign priorities to cache lines of applications. Then, we evaluate our solution and compare against state-of-the-art mechanisms. In Chapter 4, we present Band-pass Prefetching, discuss in detail the two observations that lead to our proposed solution, our practical approach to measure average miss service times. We then evaluate our contribution and compare against state-of-the-art prefetcher aggressiveness control mechanisms. Chapter 5 presents our third contribution. We describe our mechanism to estimate prefetch use characteristics and then describe the algorithm that leverages the use characteristics to assign priorities for prefetch requests. Subsequently, we present our evaluation and comparison against the relevant state-of-the-art mechanisms. Finally, we present our conclusion and direction for future research in the last chapter.

## Chapter 2

# Background

In this chapter, we provide background on shared cache management mechanisms and discuss the state-of-the-art in shared cache management. Then, we provide background on hardware prefetching followed by discussions on state-of-the-art managing prefetching in the context of multi-core processors.

#### 2.1 Cache Management Policies

Shared cache management can be broadly classified into explicit or hard partitioning and implicit or soft partitioning mechanisms. Before going into specific policies under each category, we will first describe these mechanisms.

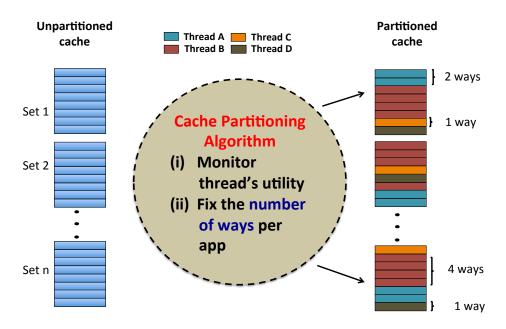

Hard Partitioning: Hard partitioning mechanisms allocate fixed budget of cache space per application such that the sum of the partitions equals the total cache size. Figure 2.1 shows an example how a cache that is managed by hard partitioning looks. The left part of the figure shows the unmanaged or unpartitioned cache. The right side shows the partitioned cache. This example shows a scenario where an 8-way associative cache is shared by four threads or applications. The cache partitioning algorithm allocates a fixed number of ways per set for every application or thread based on a cache utility model. The model estimates how well a thread makes use of the cache ways allocated to it in terms of reduction in number of misses. When an application finds a miss, the replacement policy selects a cache line within the application's partition of cache ways. If thread A in the figure finds a miss on Set 1, the replacement policy evicts the zeroth way, which is occupied by thread A for replacement.

Soft Partitioning: Soft partitioning mechanism is simply called cache replacement, because there is no explicit allocation of cache ways among applications, and the cache replacement policy just decides to evict the cache line that has the least-priority in the recency order enforced by the policy. If an application finds a miss, the replacement policy can select any cache line (that meets least-priority criterion) irrespective of which application it belongs to. Cache replacement (or, soft partitioning) based cache management is the preferred way since cache partitioning method is constrained by scalability. That is, caches need to be highly associative for cache partitioning to be applied when

Example: 4 threads sharing 8-way associative cache

Figure 2.1: An example showing how hard partitioned cache looks

the cache is shared by larger number of applications. We discuss this in detail in the later part of this chapter.

Numerous studies have been proposed in the past under each category. First we discuss implicit cache partitioning schemes and then, discuss cache partitioning schemes.

#### 2.1.1 Cache Replacement Policies

Cache replacement policies base their replacement decisions using reuse distance information. Reuse distance is defined as the number of interleaving cache accesses between consecutive accesses to the same cache line. A cache line with a shorter reuse distance implies that the given cache line will be reused immediately, while a larger reuse distance means that the given cache line will be reused after long period of time. While some approaches explicitly measure the reuse distance of cache lines, most approaches make qualitative prediction on reuse distance values. Because, measuring reuse distance values for individual cache lines require huge bookkeeping with respect to cache block addresses. On the other hand, making qualitative prediction on reuse distance is much simpler in terms of hardware overhead: few bits (2 or 4-bit) information per cache line.

The typical example of reuse distance prediction based cache replacement is the state-of-the-art Least Recently Used (LRU) policy. It works by ordering the cache lines of a given set in a recency order. On a cache miss, the cache line with least priority in the recency order is evicted. For the missing cache line, LRU policy implicitly assigns

Most Recently Used, that is the highest priority in the recency chain. Dynamic Insertion Policy (DIP) [QJP+07] is one of the foremost studies to break this implicit assumption on cache insertions. They break cache replacement into two sub-problems of eviction and insertion. Several works have been proposed in the past that enhance the eviction and insertion decisions of the LRU policy. In the following sub-sections, we discuss cache replacement policies that take different approaches to make insertion and eviction decisions.

#### 2.1.1.1 Insertion Priority Prediction

As mentioned above, cache replacement involves eviction a cache line and inserting the missing cache line. Several mechanisms have fallen in-line with this principle, and in particular with making prediction on cache insertions. Here, we discuss mechanisms that use different approaches to base prediction on insertion priorities of cache lines.

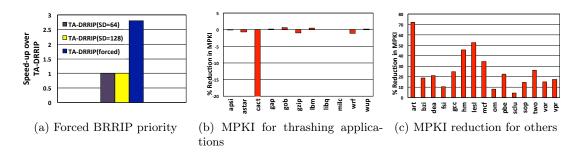

Querishi et.al. observe that the LRU policy thrashes for applications with working set size larger than the cache. Typically, the LRU policy evicts the least recently used cache line and inserts the missing cache line with the most recently used priority. In doing so, LRU policy allocates every missing cache line with highest priority and therefore, allows each of them to stay in the cache for a long duration of time before getting evicted. However, for such applications, DIP observes that thrashing can be avoided by allowing only a part or fraction of the working-set to be allowed to stay longer in the cache, while leaving the remaining or larger part of the working-set to stay much shorter in the cache. To achieve this, DIP alters the insertion policy by inserting the missing cache line with the highest MRU priority only probabilistically (1/32 times). In all other cases, the priority of the cache lines remain at LRU. The idea is that those LRU inserted cache lines are eventually filtered out on subsequent misses and avoiding thrashing. This variant policy is referred to as Bi-modal insertion policy (BIP). However, for recency-friendly applications, LRU is still the best policy. They propose set-dueling to dynamically learn the best policy for a given application. TADIP [JHQ+08] proposes a thread-aware methodology to dynamically learn the insertion priorities in a shared cache environment.

DRRIP [JTSE10] proposes to predict the reuse behavior of cache lines as re-reference interval buckets. That is, cache lines of a set are classified into different re-reference intervals as opposed to a particular re-reference or reuse value. While LRU based recency chain makes relative ordering between cache blocks within a set, RRIP allows multiple cache blocks to exist under same re-reference interval. RRIP uses 2-bit per cache line to encode re-reference interval information which allows a cache block to exist in one among four states or re-reference buckets. The highest state represents immediate re-reference, while the lowest state represents distant re-reference interval. On a cache miss, the cache line with distant re-reference interval value (3) is chosen for eviction. Unlike LRU or DIP, RRIP does not insert a cache line with highest priority, immediate re-use. From studies performed on applications from gaming and multimedia segments, RRIP discovers new access patterns namely, scan, a long sequence of cache lines with no reuse and mixed pattern where recency-friendly pattern mixed with scan

20 Background

access pattern. To handle workloads with different access patterns, RRIP propose Static Re-reference Interval Prediction, SRRIP and Bi-modal Re-reference Interval Prediction, BRRIP. While SRRIP handles mixed and scan type of access patterns, BRRIP handles thrashing patterns. SRRIP policy inserts the cache lines with RRIP value 2, which is neither immediate or distant re-reference interval, and called intermediate re-reference interval. Doing so, allows cache lines of recency-friendly pattern to stay long enough until they are reused. At the same time, cache lines of scan type applications are evicted soon as compared to inserting with highest, immediate priority. Insertion value of 2 is experimentally determined.

As with DIP, RRIP uses set-dueling to dynamically learn the best of the two polices for an application. t uses the same methodology [JHQ<sup>+</sup>08] to manage applications in shared cache environment. A thread-aware RRIP (TA-DRRIP) is our baseline cache replacement policy.

While DIP and RRIP policies make insertion priority prediction at the granularity of applications, mechanisms like Signature-based Hit Prediction, SHiP [WJH<sup>+</sup>11] and Evicted Address Filter, EAF [SMKM12] make predictions at finer granularities. SHiP classifies cache accesses into groups that are identified by PCs, Instruction Sequences or Memory regions. Grouping based on PC signatures yield the best results. To make insertion decisions, SHiP uses a table of 2-bit saturing counters that stores the hit/miss information per signature. It further uses an outcome bit per cache line that indicates a hit or miss on it. When a cache line is evicted, based on the outcome bit the counter associated with that signature is incremented or decremented. When a new cache line is inserted, if value of the counter is maximum, it indicates the cache lines associated with that signature are highly reused. The new cache line is inserted with intermediate (like SRRIP) re-reference prediction. While a minimum value indicates no or poor reuse and the new cache line is inserted with distant re-reference (like BRRIP) prediction.

Evicted Address Filter (EAF) proposed by Seshadri et.al. further enhances the prediction granularity to individual cache lines. A filter is used to decide the insertion priority of the missing cache line. The idea is to hold the evicted cache addresses in the filter, which size is same as that of the cache. If a cache access misses at the cache but hits in the filter is an indication that the cache block is prematurely evicted from the cache. Therefore, the missing cache line is inserted with intermediate (like SRRIP) priority. If the cache access misses both in the cache and filter, it is inserted with distant (like BRRIP) priority.

All these approaches use only binary (SRRIP or BRRIP) insertion policies. Under large scale multi-core context, where applications needs to be differently prioritized, these mechanisms cannot be adapted to enable such discrete prioritization. Further, SHiP and EAF predict priorities at the granularity of individual or regions of cache lines and appear as finer classification mechanisms<sup>1</sup>. However, in commercial designs [CMT][arc], which use a software-hardware co-designed approach to resource management, the system software decides fairness or performance objectives only at an ap-

<sup>&</sup>lt;sup>1</sup>Finer classification we mention here should not to be confused with discrete classification that we propose. We refer to discrete as having (> 2) priorities across applications.

plication granularity. Hence, it is desirable that the cache management also performs application level performance optimizations.

#### 2.1.1.2 Reuse distance prediction

The mechanisms discussed above make only qualitative estimate (predictions) on the reuse behavior of cache lines and classify them as to have either intermediate or distant reuse. However, some studies [TH04, KPK07, KS08, PKK09, EBSH11, SKP10, DZK<sup>+</sup>12] explicitly compute the reuse distance value of cache lines at run-time and perform replacements using the explicit value of reuse distance. Since the reuse distances of cache lines can take wider range of values, measuring reuse distance at run-time is typically complex, requires significant storage and modifying the cache tag arrays to store reuse distance values for cache lines. Here, we describe some of the important works in this domain.

[TH04] predicts the inter reference gap of cache lines and assigns them as weights. Their work is based on the observation that the inter reference gap distribution of a cache block takes only few discrete values and that cache blocks with same re-reference counts have same inter reference gap distribution. Thus, cache blocks are grouped (classified) based on the number of re-references. Essentially, classification of blocks signify different inter reference gaps (or, priorities). During its lifetime, a cache block moves from one class to another before being evicted. [KPK07, PKK09] capture the reuse distance of cache blocks using the PCs that access them. They observe only few PCs to contribute to the most of the cache accesses. However, these techniques apply to single-thread context. Since reuse distance computation for all cache blocks incurs significant overhead, some studies have proposed to sample cache accesses and compute the reuse distance for select cache blocks [EBSH11, SKP10, DZK+12].

[SKP10] observe that in multi-threaded environments, the timing of interactions between the threads does not affect stack distance computation. Hence, stack distance can be computed in parallel for all threads. They use sampling to track the reuse distance of individual threads. In their approach, the stack distance of cache lines receiving invalidation (on coherence update) from another thread is approximated to have very distant reuse (maximum reuse distance value). This is because such a cache line would receive a coherence miss anyway. This assumption may not be optimal in certain cases. For example, assume certain threads share a cache block and frequently access/update the cache block. Threads which read the updated block gets an coherence miss and subsequently, gets from the other thread. Forcing a distant reuse on such cache blocks could make the replacement policy to inadvertently give low priority and cause early evictions resulting in frequent off-chip accesses. Further, their approach may be counter-productive when combined with any on-chip cache management technique as in [KKD13].

[DZK<sup>+</sup>12] propose the protecting distance (PD) metric to protect cache lines until certain number of accesses. Also, they propose a hit-rate model which dynamically checks if inserting a cache line would improve the hit-rate. If not, the cache line is bypassed. They extend the hit-rate model to decide per-thread PD that maximizes

22 Background

the hit-rate of the shared cache. Computing protecting distance is quite complex and incurs significant hardware overhead in terms of logic and storage. For large number of applications, computing optimal PDs may require searching across a large reuse distance space. Conversely, ADAPT requires only tracking a limited number of accesses (sixteen) per set and simple logic to compute Footprint-number.

[MRG11] propose a novel cache organization that builds on the idea of delinquent PCs. They logically partition the cache as main-ways and deli-ways. While cache lines accessed by all PCs can access main-ways, only cache lines accessed by certain delinquent PCs (policy which is based on the observation that delinquent PCs have different eviction to reuse distance. The idea is to store the lines evicted from the main-ways into deli-ways and retain the cache lines for duration beyond their eviction. There are two problems with their approach. Firstly, for their scheme to work well, the cache needs to have larger associativity, which adds significant energy overhead. Secondly, when there are large number of applications sharing the cache, their algorithm may not be able to find the optimal set of delinquent PCs across all applications and assign deli-ways among them.

#### 2.1.1.3 Eviction priority prediction

Victim selection techniques try to predict cache lines that are either dead or very unlikely to be re-used soon [LR02, LFHB08, LFF01a, WAM13]. A recent proposal, application-aware cache replacement [WAM13] predicts cache lines with very long re-use distance using hit-gap counters. Hit-gap is defined as the number of accesses to a set between two hits to the same cache line. Precisely, the hit-gap gives the maximum duration for which the cache line should stay in the cache. On replacements, a cache line residing closer to/beyond this hit-gap value is evicted. In many-cores, under their approach, certain recency-friendly applications could get hidden behind memory-intensive applications and would suffer more misses. However, ADAPT would be able to classify such applications and retain their cache lines for longer time. Further, this mechanism requires expensive look-up operations and significant modifications to the cache tag array.

#### 2.1.2 Cache Bypassing

Bypassing cache lines was proposed in many studies [CT99, JCMH99, McF92, GAV95, GW10, KKD13]. Run-time Cache Bypassing [JCMH99] proposes to bypass cache lines with low-reuse behaviors while few others try to address conflict misses by bypassing cache lines that could pollute the cache. All these techniques either completely bypass or insert all requests. For thrashing applications, retaining a fraction of the working set is beneficial to the application [QJP<sup>+</sup>07]. However, in many-core caches, such an approach is not completely beneficial. Inserting cache lines of thrashing applications with least-priority still pollutes the cache. Instead, bypassing most of their cache lines is beneficial both to the thrashing application as well as the overall performance. As we show in the evaluation section, bypassing least-priority cache lines is beneficial to other replacement policies as well.

Segmented-LRU [GW10] proposes probabilistic bypassing of cache lines. The tag of the bypassed cache line and the tag of the victim cache line (which is actually not evicted) are each held in separate registers. If an access to the virtual victim cache line is found to occur ahead of the bypassed cache line, the bypass is evaluated to be useful. This mechanism functions well in single-core context and small-scale multi-cores. However, in many-cores, as demonstrated in the motivation section, observing the hits and misses on the shared cache is not an efficient way to decide on policies as they may lead to incorrect decisions. On the contrary, ADAPT decides to bypass cache lines based on Footprint-number of applications which does suffer from the actual activity of the shared cache since the application behavior is determined explicitly.

[KKD13] studies data locality aware management of Private L1 caches for latency and energy benefits. An on-chip mechanism detects locality (spatial and temporal) of individual cache lines. On an L1 miss, only lines with high locality are allocated at L1 while the cache lines with low locality are not allocated at L1 (just accessed from L2). Thus, caching low locality data only at the shared cache (L2) avoids polluting the private L1 cache and saves energy by avoiding unnecessary data movement within on-chip hierarchy. The principal difference from our approach is that they manage private caches by forcing exclusivity on select data while we manage shared caches by forcing exclusivity on select application cache lines.

#### 2.1.3 Cache partitioning techniques

Cache partitioning techniques [CS07, NLS07, XL09, QP06, GST13] focus on allocating fixed-number of ways per set to competing applications. Typically, a shadow tag structure [QP06] monitors the application's cache utility by using counters to record the number of hits each recency-position in the LRU stack receives. Essentially, the counter value indicates the number of misses saved if that cache way were not allocated to that application. The allocation policy assigns cache ways to applications based on their relative margin of benefit. The shadow tag mechanism exploits the stack property of LRU [MGST70].

While these studies are constrained by the number of cache ways in the last level cache and hence, suffer from scalability with number of cores, some studies have proposed novel approaches to fine-grained cache partitioning [SK11, MRG12, BS13] that breaks the partitioning-associativity barrier. These mechanism achieve fine-grained (at cache block level) through adjusting the eviction priorities. Jigsaw [SK11] shares the same hardware mechanism as Vantage [BS13], but uses a novel software cache allocation policy. The policy is based on the insight that miss-curves are typically non-convex and the convex-hull of the miss-curves provides scope for efficient and a faster allocation algorithm. Vantage, however, uses the same lookahead allocation policy  $(O(N^2)$  algorithm) as in UCP. PriSM [MRG12] proposes a pool of allocation policies which are based on the miss-rates and cache occupancies of individual applications.

Essentially, these mechanisms require quite larger associative shared cache. For tracking per-application utility, 256-way associative, LRU managed shadow tags are required [SK11][BS13]. Further, these techniques require significant modification to the

24 Background

existing cache replacement to adapt to their needs. On the contrary, ADAPT is simple and does not require modification to the cache states. Only the insertion priorities are altered.

#### 2.2 Cache Management in the presence of Prefetching

Hardware prefetching helps to hide long latency memory operation by predicting the future access of an application. When the prefetch request arrives before the demand access (for which prefetch was sent) needs the data, it becomes timely and useful. While a prefetch request that is in transit (yet to arrive) from the main memory may still be useful depending on the criticality of the missing data. A prefetched data that is never used or accessed by the demand stream wastes the memory bandwidth and could potentially cause pollution of useful data at the shared cache. The opportunity cost of wasted bandwidth and pollution becomes higher in the context of multi-core systems, where memory bandwidth and last level cache is shared. Therefore, prefetch requests have to be managed at both the cache as well as off-chip memory access.

#### 2.2.1 Managing prefetch requests at the shared cache

Several studies have proposed prefetch request handling at the caches [DDS95, BC95, Lin01, LRBP01, LFF01b, ZL03, CFKL95, PGG<sup>+</sup>95, AB05, STS08, SMKP07, WJM<sup>+</sup>11, SYX<sup>+</sup>15]. In this following, we only discuss prefetch-aware cache management mechanisms in the context of shared last level caches.

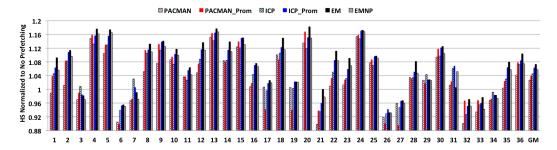

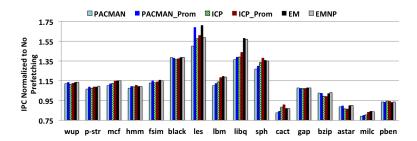

Wu et. al. [WJM<sup>+</sup>11] find that treating both prefetch and demand requests on cache insertions and cache update operations is detrimental to performance. Because, the use characteristics of demands and prefetch requests are different. At the last level cache prefetch requests are either never accessed or mostly used only once. That is, after the first access by demand, the prefetched data is never accessed again as subsequent accesses is filtered by the level two cache. Therefore, in order to avoid such prefetched cache block occupying cache space for longer duration of time and polluting, they propose to modify the promotion and insertion policies for prefetch requests. On prefetch-hits, the cache line is never promoted, while on cache insertion, prefetched cache lines are always inserted with distant reuse priority. Altogether, they propose Prefetch-Aware Cache MANagement (PACMAN) for handling prefetch requests at the LLC.

Seshadri et. al. propose Informed Cache Prefetching, ICP to further enhances cache management in the presence of prefetching by accounting prefetch-accuracy information. When prefetched cache blocks are inserted with distant priority, chances are high that a useful prefetched block could get evicted before a demand actually uses it. Inserting a prefetched cache block with high priority avoids this problem. However, since prefetched cache blocks are mostly used only once, inserting them at MRU position would result in pollution. Therefore, they propose two mechanisms. The first mechanism, called ICP-Demotion, demotes the cache line to LRU priority on prefetch-hits. The second mechanism called ICP-AP uses a prefetch-accuracy predictor to determine the insertion

priority. If the predictor predicts the prefetcher to be accurate, the mechanism inserts it with MRU priority, otherwise, the cache line is inserted with LRU priority.

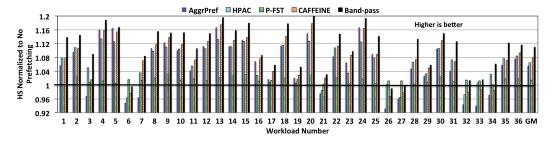

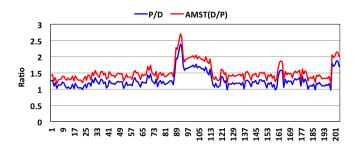

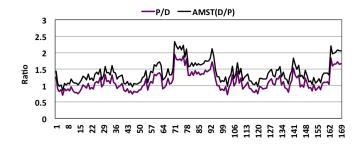

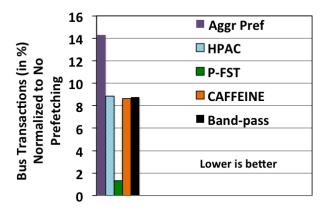

#### 2.2.2 Prefetch-filter based Techniques