#### UNIVERSITÉ DE GRENOBLE

#### **THÈSE**

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE ALPES

Spécialité : Informatique

Arrêté ministèriel: 7 août 2006

Présentée par

#### **Duco van Amstel**

Thèse dirigée par **Fabrice Rastello** et co-encadrée par **Benoît Dupont de Dinechin**

préparée au sein de l' **INRIA** et de **l'École Doctorale MSTII**

## **Optimisation de la Localité des Données sur Architectures Manycœurs**

Thése soutenue publiquement le 18 / 07 / 2016, devant le jury composé de :

Mr. François Bodin

Professeur, IRISA, Président

Mr. Albert Cohen

Directeur de Recherche, Inria, Rapporteur

Mr. Benoît Dupont de Dinechin

Directeur technique, Kalray S.A, Co-Encadrant de thèse

Mr. François Irigoin

Directeur de Recherche, MINES ParisTech, Rapporteur

Mr. Fabrice Rastello

Chargé de Recherche, Inria, Directeur de thèse

Mr. Ponnuswamy Sadayappan

Professor, Ohio State University, Examinateur

## Data Locality on Manycore Architectures

a dissertation by

Duco Yalmar van Amstel

## **Acknowledgments**

The work which is related in this manuscript is not that of a single person. It rather is the synthesis of a continuous flow of discussions, exchanges and collaborative effort. In this regard I extend my deepest gratitude towards both Kalray and Inria for giving me the opportunity to work on this most exciting project. The industrial context has proven to be a rich learning ground and I would like to thank Benoît de Dinechin for showing me the way. The same can be said about my research team where Fabrice Rastello has taught me the importance of persevering in my efforts even when you're trust in the chosen approach is waning. His guidance and inspiration will stay with me for a long time.

Many people have contributed in one way or another in this project and naming all of them would make for a very long list. Nonetheless I give my sincere thanks to Lukasz Domagala, Yves Durand and Dr. Sadayappan, my co-authors, who all have helped me at numerous times on a wide variety of subjects. I also would like to thank all my colleagues at Kalray: Céline, Marc, Frédéric, Nicolas, Patrice, Alexandre, Renaud & others, as well as those at Inria: François, Fabian, Diogo, Imma, Frédéric, ...

On a more personal note I am most gratefull to my parents Marit & Walter for teaching a young boy the importance of being curious, as curiosity is the brightest of torches and most certainly did not kill the cat (except for Schrödinger's). Last but not least I cannot leave out my beloved and most precious Bérengère for sharing both the best and the toughest moments of my work, with always an unconditionnal support.

### Résumé

L'évolution continue des architectures des processeurs a été un moteur important de la recherche en compilation. Une tendance dans cette évolution qui existe depuis l'avènement des ordinateurs modernes est le rapport grandissant entre la puissance de calcul disponible (IPS, FLOPS, ...) et la bande-passante correspondante qui est disponible entre les différents niveaux de la hiérarchie mémoire (registres, cache, mémoire vive). En conséquence la réduction du nombre de communications mémoire requis par un code donnée a constitué un sujet de recherche important. Un principe de base en la matière est l'amélioration de la localité temporelle des données : regrouper dans le temps l'ensemble des accès à une donnée précise pour qu'elle ne soit requise que pendant peu de temps et pour qu'elle puisse ensuite être transféré vers de la mémoire lointaine (mémoire vive) sans communications supplémentaires.

Une toute autre évolution architecturale a été l'arrivée de l'ère des multicœurs et au cours des dernières années les premières générations de processeurs manycœurs. Ces architectures ont considérablement accru la quantité de parallélisme à la disposition des programmes et algorithmes mais ceci est à nouveau limité par la bande-passante disponible pour les communications entres cœurs. Ceci a amène dans le monde de la compilation et des techniques d'optimisation des problèmes qui étaient jusqu'à là uniquement connus en calcul distribué.

Dans ce texte nous présentons les premiers travaux sur une nouvelle technique d'optimisation, le *pavage généralisé* qui a l'avantage d'utiliser un modèle abstrait pour la réutilisation des données et d'être en même temps utilisable dans un grand nombre de contextes. Cette technique trouve son origine dans le pavage de boucles, une techniques déjà bien connue et qui a été utilisé avec succès pour l'amélioration de la localité des données dans les boucles imbriquées que ce soit pour les registres ou pour le cache. Cette nouvelle variante du pavage suit une vision beaucoup plus large et ne se limite pas au cas des boucles imbriquées. Elle se base sur une nouvelle représentation, le *graphe d'utilisation mémoire*, qui est étroitement lié à un nouveau modèle de besoins en termes de mémoire et de communications et qui s'applique à toute forme de code exécuté itérativement.

Le pavage généralisé exprime la localité des données comme un problème d'optimisation pour lequel plusieurs solutions sont proposées. L'abstraction faite par le graphe d'utilisation mémoire permet la résolution du problème d'optimisation dans différents contextes. Pour l'évaluation expérimentale nous montrons comment utiliser cette nouvelle technique dans le cadre des boucles, imbriquées ou non, ainsi que dans le cas des programmes exprimés dans

un langage à flot-de-données. En anticipant le fait d'utiliser le *pavage généralisé* pour la distribution des calculs entre les cœurs d'une architecture manycœurs nous donnons aussi des éléments de réponse pour modéliser les communications et leurs caractéristiques sur ce genre d'architectures.

En guise de point final, et pour montrer l'étendue de l'expressivité du *graphe d'utilisation mémoire* et le modèle de besoins en mémoire et communications sous-jacent, nous aborderons le sujet du débogage de performances et l'analyse des traces d'exécution. Notre but est de fournir un retour sur le potentiel d'amélioration en termes de localité des données du code évalué. Ce genre de traces peut contenir des informations au sujet des communications mémoire durant l'exécution et a de grandes similitudes avec le problème d'optimisation précédemment étudié. Ceci nous amène à une brève introduction dans le monde de l'algorithmique des graphes dirigés et la mise-au-point de quelques nouvelles heuristiques pour le problème connu de joignabilité mais aussi pour celui bien moins étudié du partitionnement convexe.

## **Abstract**

The continuous evolution of computer architectures has been an important driver of research in code optimization and compiler technologies. A trend in this evolution that can be traced back over decades is the growing ratio between the available computational power (IPS, FLOPS, ...) and the corresponding bandwidth between the various levels of the memory hierarchy (registers, cache, DRAM). As a result the reduction of the amount of memory communications that a given code requires has been an important topic in compiler research. A basic principle for such optimizations is the improvement of temporal data locality: grouping all references to a single data-point as close together as possible so that it is only required for a short duration and can be quickly moved to distant memory (DRAM) without any further memory communications.

Yet another architectural evolution has been the advent of the multicore era and in the most recent years the first generation of manycore designs. These architectures have considerably raised the bar of the amount of parallelism that is available to programs and algorithms but this is again limited by the available bandwidth for communications between the cores. This brings some issues that previously were the sole preoccupation of distributed computing to the world of compiling and code optimization techniques.

In this document we present a first dive into a new optimization technique which has the promise of offering both a high-level model for data reuses and a large field of potential applications, a technique which we refer to as *generalized tiling*. It finds its source in the already well-known loop tiling technique which has been applied with success to improve data locality for both register and cache-memory in the case of nested loops. This new "flavor" of tiling has a much broader perspective and is not limited to the case of nested loops. It is build on a new representation, the *memory-use graph*, which is tightly linked to a new model for both memory usage and communication requirements and which can be used for all forms of iterate code.

Generalized tiling expresses data locality as an optimization problem for which multiple solutions are proposed. With the abstraction introduced by the *memory-use graph* it is possible to solve this optimization problem in different environments. For experimental evaluations we show how this new technique can be applied in the contexts of loops, nested or not, as well as for computer programs expressed within a dataflow language. With the anticipation of using *generalized tiling* also to distributed computations over the cores of a manycore

architecture we also provide some insight into the methods that can be used to model communications and their characteristics on such architectures.

As a final point, and in order to show the full expressiveness of the *memory-use graph* and even more the underlying memory usage and communication model, we turn towards the topic of performance debugging and the analysis of execution traces. Our goal is to provide feedback on the evaluated code and its potential for further improvement of data locality. Such traces may contain information about memory communications during an execution and show strong similarities with the previously studied optimization problem. This brings us to a short introduction to the algorithmics of directed graphs and the formulation of some new heuristics for the well-studied topic of reachability and the much less known problem of convex partitioning.

## **Contents**

| Acknov  | vledgments                                              | i   |

|---------|---------------------------------------------------------|-----|

| Résume  | <b>5</b>                                                | iii |

| Abstrac | et e e e e e e e e e e e e e e e e e e                  | V   |

| Conten  | ts                                                      | vii |

| Introdu | ction                                                   | 1   |

| The     | Memory-Wall                                             | 2   |

| Tilin   | g and the need for a communication model                | 4   |

| The     | advent of manycore architectures                        | 5   |

| A hi    | gh-level framework                                      | 6   |

| 1. Mem  | ory Usage & Operational Intensity                       | 9   |

| 1.1     | Context and goal                                        | 10  |

| 1.2     | State-of-the-art                                        | 11  |

| 1.3     | The memory-use graph                                    | 12  |

| 1.4     | Memory usage of a code                                  | 18  |

| 1.5     | IO cost of a code                                       | 23  |

| 2. Com  | munication Costs in a Manycore Environment              | 27  |

| 2.1     | Context and goal                                        | 28  |

| 2.2     | Architecture of a general-purpose Network-on-Chip       | 29  |

| 2.3     | State of the art                                        | 33  |

| 2.4     | Quality-of-Service: why and how?                        | 34  |

| 2.5     | $(\sigma, \rho)$ traffic on the MPPA manycore processor | 36  |

| 3. Gene | ralized Tiling                                    | 47  |

|---------|---------------------------------------------------|-----|

| 3.1     | Context and goal                                  | 48  |

| 3.2     | A change of perspective                           | 48  |

| 3.3     | Tiling model                                      | 48  |

| 3.4     | The use of Constraint Programming                 | 55  |

| 3.5     | Tiling with heuristics                            | 56  |

| 3.6     | From theory to practice                           | 63  |

| 4. Gene | eralized Register Tiling                          | 67  |

| 4.1     | Context & goal                                    | 68  |

| 4.2     | State of the art                                  | 68  |

| 4.3     | Implementing generalized tiling for registers     | 70  |

| 4.4     | Experimental results                              | 76  |

| 5. Gene | ralized Dataflow Tiling                           | 79  |

| 5.1     | Context & goal                                    | 80  |

| 5.2     | State of the art                                  | 81  |

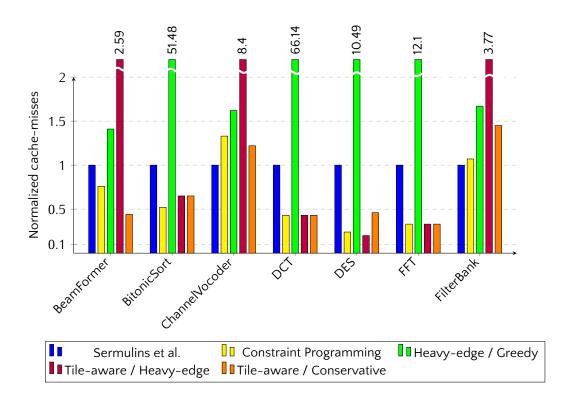

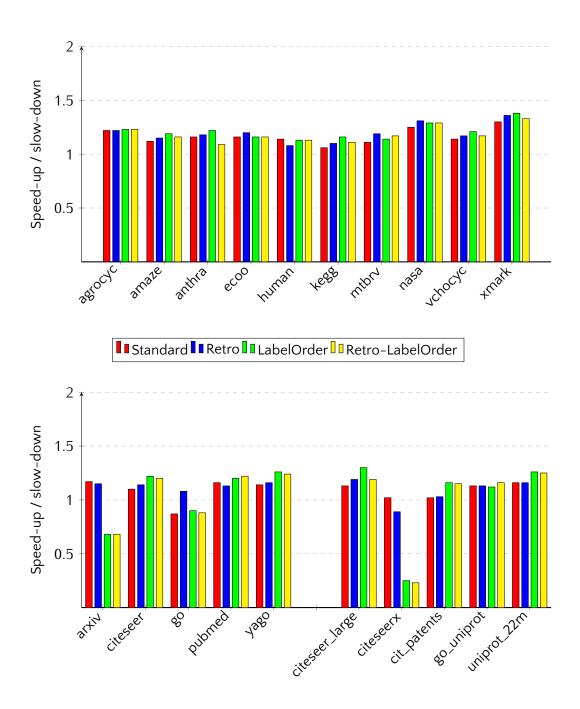

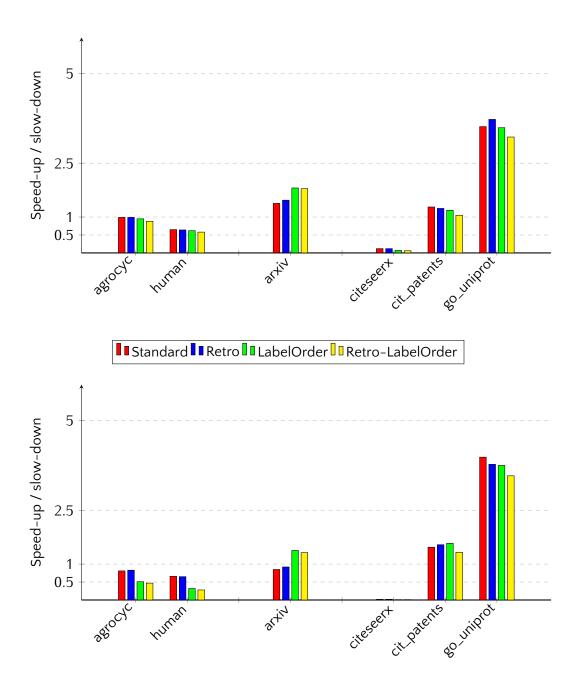

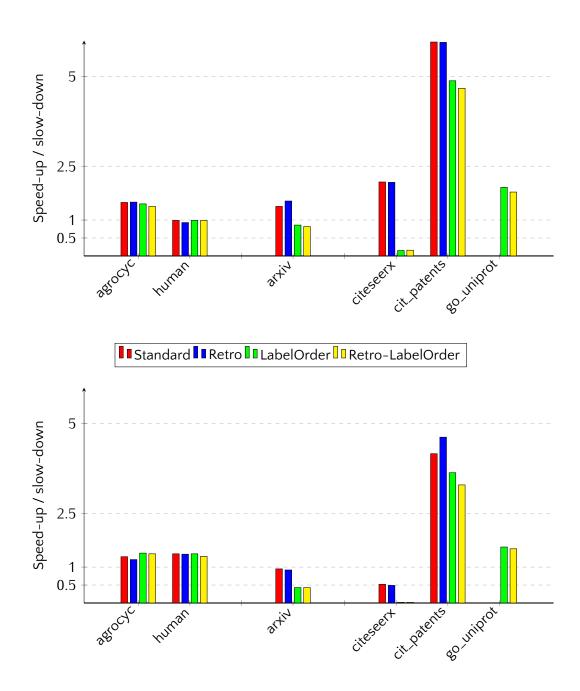

| 5.3     | Evaluation of a prototype: StreamIt               | 82  |

| 5.4     | The path towards an industrial implementation: ΣC | 85  |

| 5.5     | Limits of the current implementation              | 87  |

| 6. Beyo | nd Semi-Regularity                                | 89  |

| 6.1     | Context and goal                                  | 90  |

| 6.2     | State of the art                                  | 91  |

| 6.3     | Graph algorithms                                  | 92  |

| 6.4     | Cost analysis of a partitioning scheme            | 103 |

| 6.5     | The GraphUtilities library                        | 107 |

| Conclus | sion                                              | 121 |

| A fe    | w steps back                                      | 122 |

| Futu    | re directions                                     | 124 |

| Annexe  | S                                                 | 127 |

| Α       | Résumé - Introduction                             | 128 |

| В       | Résumé - Chapitre 1                               | 129 |

| С       | Résumé - Chapitre 2                               | 132 |

| D       | Résumé - Chapitre 3                               | 134 |

| Е       | Résumé - Chapitre 4 | 136 |

|---------|---------------------|-----|

| F       | Résumé - Chapitre 5 | 139 |

| G       | Résumé - Chapitre 6 | 140 |

| Н       | Résumé - Conclusion | 142 |

| Bibliog | graphy              | 147 |

| Aut     | thor references     | 147 |

| Oth     | ner references      | 147 |

| List of | figures             | 159 |

| List of | tables              | 161 |

| List of | algorithms          | 163 |

## Introduction

The wind was not the beginning. There are neither beginnings nor endings to the turning of the Wheel of Time. But it was  $\alpha$  beginning.

R. Jordan - The Eye of the World

#### The Memory-Wall

The science of code optimization, be it automatic through optimizing compilers or done manually by programmers, has seen numerous evolutions since the arrival of the first computers and the associated programming languages. These evolutions have often, if not always, held a close link with evolutions in the hardware on which the code is executed. As such, many changes in the micro-architecture of processor cores have been paired with corresponding modifications in the way code was optimized for these architectures. Compiler techniques such as instruction selection, scheduling and register allocation are some of the most iconic examples of the relationship between computer architecture and code optimization. Some techniques such as vectorization only exist because of the introduction of specific features in a processor's micro-architecture.

The topic of memory communications has been pushing its way into the spotlight of the compiler community for some years. In most if not all modern architectures, memory follows a hierarchical organization ranging from large but distant to small and close by storage. The further away a storage is from a computational core the more time and energy it takes to retrieve data from it. In the past a reduction of the number of communications between the different levels of a memory hierarchy has already been a target as it is usually linked to increased performances. However the current context of hardware evolutions and constraints is pushing both the academic and the industrial world to consider the subject with a renewed focus.

An interesting measure for a given computer architectures is the computation-to-bandwidth ratio. This ratio can be expressed as a number of arithmetic operations per byte loaded from one level of the memory hierarchy to the level below. If a program uses more operations per byte that needs to be loaded than the ratio this indicates that it is *computationally-bound* with respect to this memory level. In the opposite case the program is called *memory-bound*. This is an indication of which architectural element is the current bottle-neck that limits the performance of the program: the computational core or the memory bandwidth.

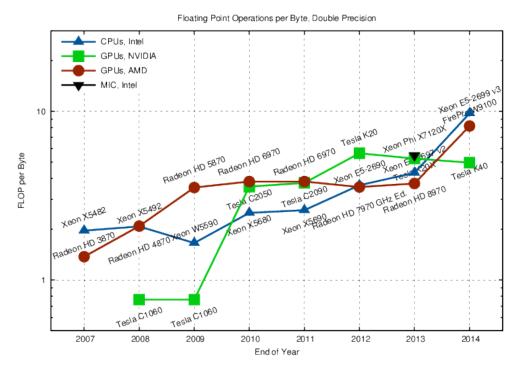

Data extracted from computer architectures that have appeared over the past decade shows a common trend in the evolution of computation-to-bandwidth ratios for both CPUs and GPUs (see Figure I.1). The computation-to-bandwidth ratio is growing which means that more and more existing applications move from being computationally-bound to being memory-bound. This phenomenon is not new and has been called the Memory-Wall when identified during the '90s [WM95; SPN96;

Figure I.1 – Computation-to-bandwidth ratio for various recent architectures<sup>1</sup>

#### McK04; SMCCL11].

An implication of this phenomenon is that the evolution of performances will be limited by the evolution of memory-bandwidth. It appears thus as a necessity to identify ways in which this memory-wall can be broken down or, at the least, ways to extend the time before its influence becomes prohibitive. The paths that are being researched in this respect include the modification of memory interfaces for a faster increase in bandwidths [JED15; Hyb15], the development of novel architectures based on the processor-in-memory concept [Dlu+14] as well as the improvement of bandwidth efficiency of existing software.

Some very recent steps in memory-interfaces have already proven to be able to increase the attainable bandwidths in the near-future by multiple orders of magnitude. This means the memory-wall can be pushed back significantly in its time-frame without being broken down [Rad+15].

In a similar fashion the current projects for novel architectures also promise a change of scenery in the way data is stored and transferred by memory. The grounds

<sup>&</sup>lt;sup>1</sup>Source: www.karlrupp.net/2013/06/cpu-gpu-and-mic-hardware-characteristics-over-time/

for this evolution lie in parallel computations that do not follow the traditional Von Neumann architectural model. Such a change of paradigm means a potential for considerable speed-ups for certain types of computations. The limits however lie in the parts of algorithms that are devoid of inherent parallelism.

The previous observations argue in favor of a continued effort by the compiler community in the search for improvements in bandwidth efficiency. Mainly this implicates that for the transfer of a single datum to a lower-level in the memory hierarchy a maximum amount of computations involving this particular datum should be scheduled before it is discarded again towards a higher level. The underlying concept here is that of *temporal locality*. Traditionally *temporal locality* is optimized through methods that perform some form of rescheduling on the order of execution of an algorithm. A typical example for such methods is loop tiling which can be applied either manually by a programmer or automatically through a compiler.

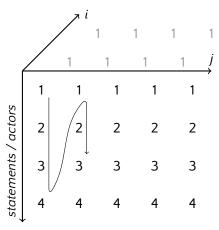

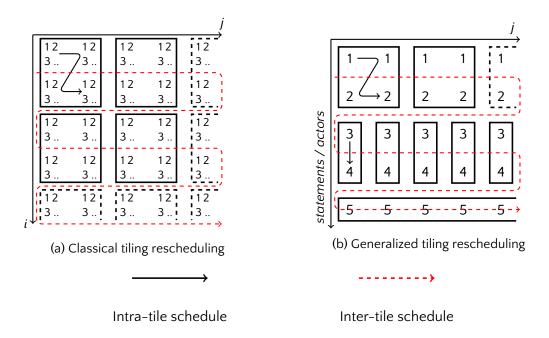

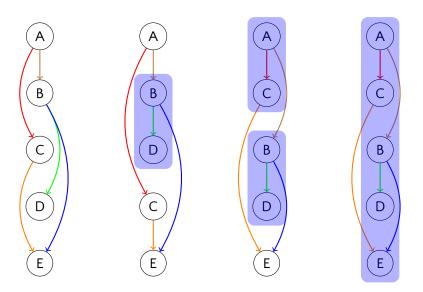

#### Tiling and the need for a communication model

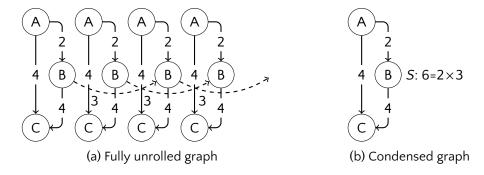

Loop tiling as an optimization technique appeared in the 1980's [Pei86; IT88; Wol89]. The founding concept is to partition the iteration space of a loop nest in regular tiles and to reschedule the execution order of the loop iterations such that all iterations within a given tile are processed together. One of the main difficulties in this process is to compute the correct tile shape and size for a given loop nest. This is a problem that is quite similar in nature to the computation of block sizes for blocked matrix operations [MC69]. However determining the existing data dependencies within the iteration space has become a research subject on its own. Likewise the computation of the optimal tiles for a given dependency scheme remains a source for a great number of publications even if the nature of the loop transformation has remained the same.

Among the limits that exist for current loop tiling techniques we can identify some of those that appear as significant barriers to a more general application of this optimization. A first condition is that tiling only applies to perfect loop nests even if some extensions have been achieved. Furthermore most tiling models only account for situations where all dependencies have distances (*i.e* the amount of iterations between reuses) that can be expressed either as a constant or as an affine function of the induction variables.

A paramount element when evaluating tiling options is the memory for which the tiling is performed. Depending on the characteristics of the target memory (size, granularity, access, ...) a given tile will produce more or less communications with mem-

ory further away from the cores which in turn will influence the final memory bandwidth usage of the tiled code. As an example two cache-memories of the same size may exhibit two completely different behaviors if the sizes of their lines or their associativity differ. Similarly cache-memory does not behave in the same way as registers or off-chip *Dynamic Random Access Memory* (DRAM). In this light a model for memory communications appears to be an important tool without which tile computations fall back to educated guesswork.

When taking a step back to look at the initial motivations behind loop tiling it appears that the identification of parallelism is of an importance comparable to data locality itself. If all incoming dependencies of two separate tiles have been computed and the tiles have no dependencies between them their executions can be done in parallel. This observation makes it possible to draw a link between loop tiling and other examples of optimizations of frequently executed code such as dataflow programs and distributed run-time environments. In all these situations the questions of scheduling and data locality are intertwined and depend heavily on the memory hierarchy on which code is being executed. The whole should be viewed in the context of an amount of hardware parallelism in computer architectures that has been growing considerably over the last decade.

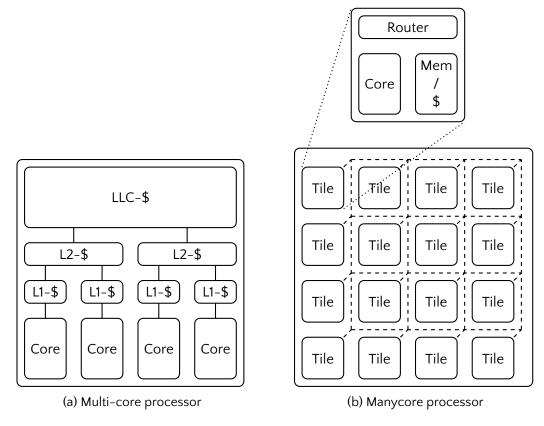

#### The advent of manycore architectures

In a general manner the usage of large distributed and parallel systems has been an exclusivity of high-performance computing. However even basic commercial processors have hit a frequency ceiling and have therefore resorted to an increase in the amount of hardware parallelism. Current top-of-the-line processors showcase up to 20 complex computational cores with the physical size of the chip being the only limit to this number. This type of processors has been called a *multicore processor*. As it has been possible to go from a single core to tens of cores, the next step in this evolution is to go from tens of cores to hundreds or even thousands of cores. Already industrial products and prototypes exist that have taken this direction and have thereby started a first generation of *manycore processors*. The issue of the physical size of the chip is solved by using much simpler core architectures to reduce the surface per core. Some examples of such architectures are the TILE-Gx range by Tilera (now Mellanox)<sup>2</sup>, the

<sup>2</sup>http://www.mellanox.com/page/multi\_core\_overview

MPPA family by Kalray<sup>3</sup> and the Xeon Phi processors by Intel<sup>4</sup>.

Among the main differences between multicore and manycore processors is the communication between the cores. For multicore architectures the general principle is direct communication through shared memory as these architectures usually have a single off-chip memory that is common to all the cores and which is accessed through multiple levels of coherent cache. In the case of manycore architectures memory communications are rarely direct and use an embedded *network-on-chip* that connects all the cores. Memory can be off-chip and accessed through the network-on-chip with caches that are local to some cores. In some cases non-cache memory can also be distributed among the cores thereby forming a *Non-Uniform Memory Access* (NUMA) typed architecture with distant accesses performed through the network-on-chip. Such a memory hierarchy makes it possible to relate a manycore processor to a computational cluster in many aspects. As a result *spatial locality*, a concept that is complimentary to *temporal locality*, encourages the computations involving a given datum to be performed on a single core.

In the context of the *Memory-Wall* a manycore architecture has the advantage of a higher degree of parallelism in the memory communications between on-chip cores. However the off-chip bandwidth must still be shared among all the cores. Furthermore the presence of a network-on-chip as well as the increased complexity of the memory-hierarchy contribute to higher average latencies for memory communications. Because of this both *spatial* and *temporal locality* are of great importance to ensure a correct performance level for computations that run on such architectures. The tiling principle can here be used to ensure the necessary locality but also to provide an adequate level of granularity for scheduling and resource allocation.

#### A high-level framework

Our observation of modern-day hardware characteristics, with the principle of loop tiling in mind suggests, that this existing technique could potentially be of use at a much broader scale than it is today. While it is currently used only on loop nests it would be interesting to see if it could be applied in a more general way to a larger set of loops. There is also much to say for an approach similar to tiling in the optimization of frequently executed code beyond the case of loops. Dataflow programs for example typically can be seen as a set of computations performed by iteration over

<sup>3</sup>http://www.kalray.eu

<sup>4</sup>http://www.intel.com/content/www/us/en/processors/xeon/xeon-phi-detail.html

the available input.

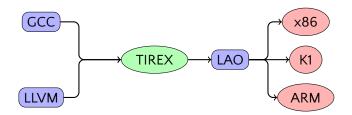

This manuscript's challenge is to expose a coherent vision of such a generalization of the tiling technique applicable in a variety of use-cases. In order to do so, the first point of attention is the study and development of both a communication and memory-cost model in Chapter 1. By defining a single representation for the optimization problems at hand, it is possible to evaluate the memory requirements of a given piece of code as well as the amount of communications that are required throughout the targeted memory hierarchy for an arbitrary scheduling.

For the extension of tiling towards distributed environments such as manycore processors it is also necessary to evaluate the costs and constraints related to the specifics of such platforms. Notably the presence of a network-on-chip requires that its behavior is modeled and parametrized in order to determine the latencies of communications on the network: an important factor when scheduling computations that use a common set of data on separate resources. For the purpose of this study the target platform here was the MPPA chip by Kalray<sup>5</sup> for which a specific modelisation is performed in Chapter 2.

With the theoretical foundations in place, the next step is to create a formal definition for our generalized tiling optimization problem and to propose methods for solving it. This is the subject of Chapter 3. Multiple approaches have been attempted both optimal and approximate with a preference for heuristics that allow to minimize the impact of the optimization on the compilation process. The time required to compute a solution is reduced at the cost of not being optimal.

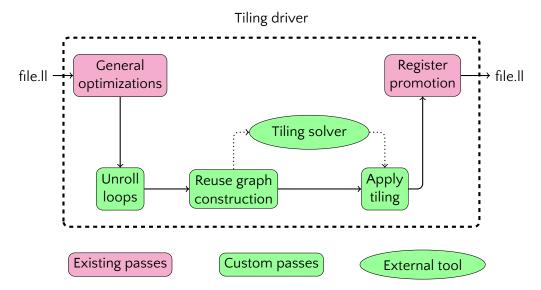

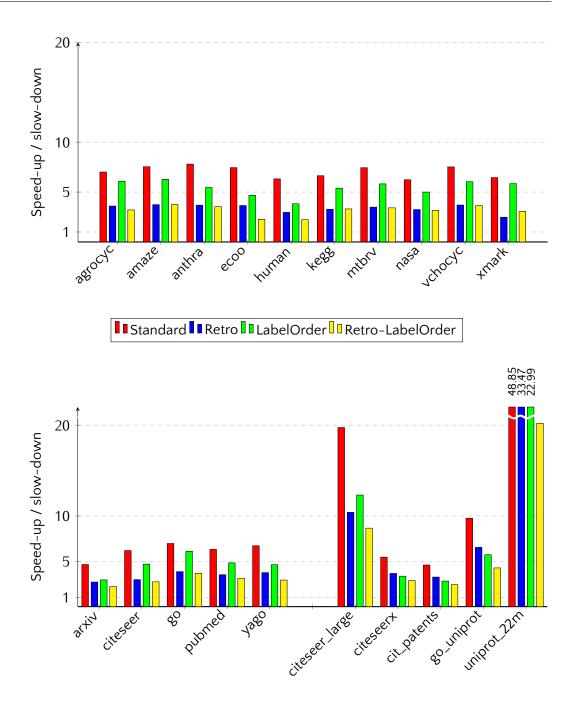

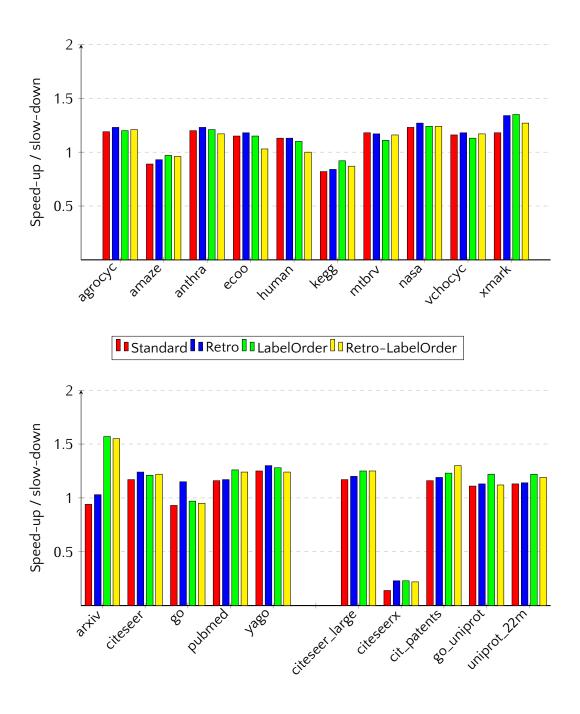

The first application of the generalized tiling method specifically targets loops and tries to reduce the number of load and store instructions. This is also the point where the main differences between generalized tiling and classical tiling appear best. A full detail of the implementation is given in combination with experimental results in Chapter 4. A thorough analysis of the presented results enables us to identify both the strengths and weaknesses of this new approach.

A second application of generalized tiling is presented next in Chapter 5 and targets dataflow code at a higher level of granularity. This also offers the possibility to extend the tiling problem statement with resource allocation in a distributed environment. The experimental evaluation of this generalized tiling in this use-case uses a theoretical model of execution. The first elements of an implementation in a real dataflow

<sup>&</sup>lt;sup>5</sup>The doctoral contract leading to this manuscript was obtained through a CIFRE agreement between Kalray and Inria. The author was a full-time employee of Kalray for the entire duration of his doctoral studies.

environment are also given within the  $\Sigma C^6$  [Gou+11] toolchain.

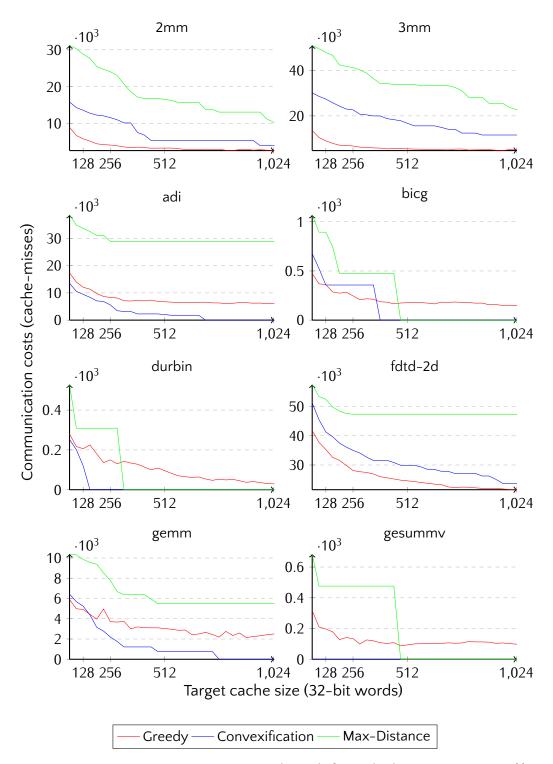

As a final step of this study we try to go beyond the context of code optimization in Chapter 6 by reusing our memory-cost and communication model for the purpose of execution trace analysis. The analysis of traces of the memory operations of a program can be used to identify parts of the code that use significantly more memory-bandwidth than it would with a different scheduling. As execution traces do not exhibit the same kind of regularity as loop dependencies and dataflow graphs their analysis requires us to tackle some new algorithmic challenges in graph partitioning. Again an implementation of these newly developed algorithms is presented together with the associated experimental results and comments.

$<sup>^6\</sup>Sigma C$  is a dataflow extension of C that follows a cyclo-static execution model. It is developed by CEA LIST and was supported on the MPPA processor family.

Chapter 1

# Memory Usage & Operational Intensity

'Thus is our treaty written; thus is agreement made. Thought is the arrow of time; memory never fades. What was asked is given. The price is paid.'

R. Jordan - The Shadow Rising

#### 1.1 Context and goal

The first step in this study of a generalized form of tiling is the construction of an effective model for memory usage and Input-Output (IO) costs.

The memory usage of a given code snippet can be associated with the maximum amount of data throughout the execution that should be simultaneously available. From this point of view it bears a similarity with the notion of the *max-live* measure used in scheduling and register allocation.

In a similar fashion the IO cost of a piece of code represents the amount of memory communications that are performed during its execution. This can then be translated into the characteristic of operational intensity which is the ratio between the number of instructions that are executed and the number of memory communications that the execution of these instructions requires. The operational intensity is specific to a level of the memory-hierarchy. In the case of a standard x86 processor with registers, L1, L2 and LLC caches this means that a program has four different operational intensities:

- A register operational intensity for load / store instructions.

- · An L1 operational intensity for L1 misses that will hit the L2 cache.

- · An L2 operational intensity for L2 misses that will hit the LLC.

- · An LLC operational intensity for LLC misses that will hit off-chip RAM.

Our primary goal is to increase the operational intensity of programs by reducing the amount of memory communications between close-by memory and distant memory. For this purpose we assume from now on that we have a target memory, which is limited in size, containing the data used by the program, and a distant memory of infinite size to which data is sent if the target memory is not large enough. This assumption is valid both for registers, where overflowing data is transferred from and to memory, and for cache memory, where cache misses and updates are transferred from and to a higher level of cache or main memory.

A second important challenge is to be able to perform our optimizations on different types of code, on a diversity of hardware targets as well as on the multiple levels of memory hierarchies. The implies that we need to describe the data dependencies existing within a program in a common representation for all these environments. We also need a representation with an abstraction level high enough to hide the granularity at which the code is viewed (instruction, basic-block, ...). As we want to represent code that executes iteratively it is also necessary for the representation to be identical

Chapter 1 IO complexity

for each iteration. This reduces both the memory size of the representation and the time complexity of algorithms that are applied to it.

Our optimization being a form of tiling, the representation should make it easy to define a tiling solution for the code that is being optimized. And circling back to the memory and IO costs it should be straightforward to translate a tiling solution into the associated measures.

The solution that we propose is inspired by the representation of dataflow programs in the form of a graph of actors and links that transport data from one actor to another. Before diving into the definition of this new representation that we name the *Memory-use graph* of the code we first take a look at the existing state-of-the-art concerning the computation of memory and IO costs.

#### 1.2 State-of-the-art

#### 1.2.1 Cache analysis

The notion of reuse distance or *least-recent use* (LRU) distance was coined by Mattson et al. [Mat+70] in the context of the study of cache usage. It is an effective way to compute the number of cache-misses as a function of the cache size for a given access pattern in the case of an LRU cache and has been used in numerous studies. Similar metrics include the miss rate, the average footprint and the data lifetime. These notions were formalized by Denning in his seminal work on working-set locality for cache analysis [Den68]. They have been extended and formally linked within a unique framework for cache-performance evaluation by Xiang et al. in a *higher-order theory of locality* [Xia+13].

#### 1.2.2 Register pressure

When the register file is the targeted memory, the most well-known and commonly used method is register pressure. It has been the main metric for graph-based register allocation and spilling since the work by Chaitin et al. [Cha+81; Cha82]. Briggs proposed some improvements in his thesis [Bri92] as well as in his work with Cooper and Torczon [BCT94]. The approach taken by Chow and Hennessey for their *priority-based register allocation* [CH90] balances the need to keep register pressure under a given limit while keeping the critical path of execution as short as possible.

#### 1.2.3 IO complexity

Yet another approach to the issue of memory usage and IO cost exists under the form of *IO complexity*. It aims at providing the tightest possible lower-bound on the amount of memory communications that are required for a given algorithm to be executed on target memory and as such it is implementation independent. The first attempts at the computation of such lower-bounds can be attributed to Jia-Wei and Kung [JWK81] who used the mathematical red-blue pebble game to model the inputs and outputs of an algorithm and applied it to a limited set of algorithms. The most recent advances in the topic of IO complexity have been produced by Elango et al. [Ela+15b]. Among other advances they generalized the red-blue pebble game to arbitrary algorithms running on parallel architectures [Ela+14; Ela+15a].

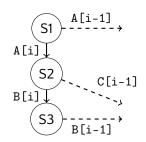

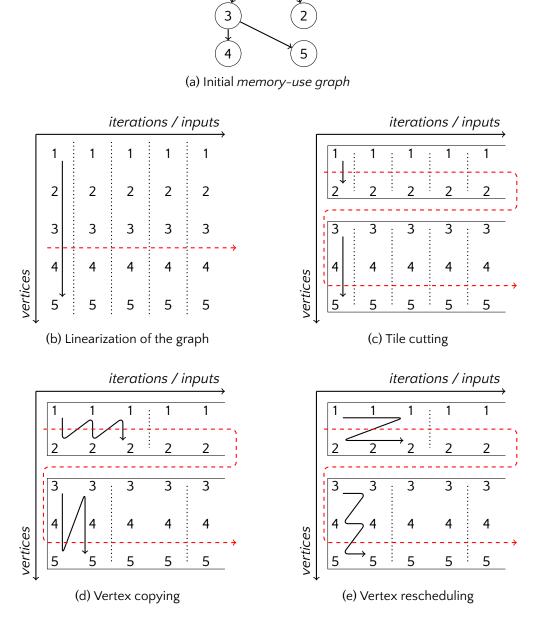

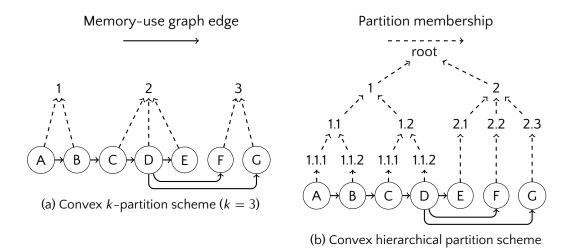

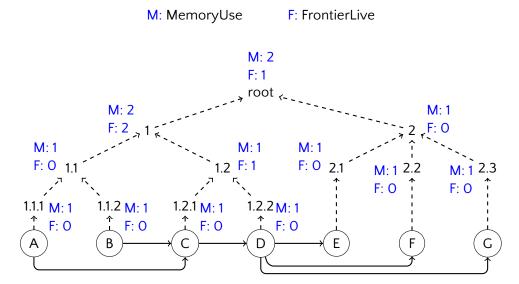

#### 1.3 The memory-use graph

As suggested in the goal statements in Section 1.1 we propose a representation of the memory usage and dependencies of a code snippet inspired by diagrams of dataflow programs. This most important advantage of this approach is that it can easily be applied to the various types of code that we target for optimization. It should be noted that when mentioning dataflow programs we restrict ourselves to static [LM87] and cyclo-static [Bil+95] dataflow languages, a subset of the more general dataflow paradigm. The representation, presented in detail below, is referred to as the *memory-use graph* of the analyzed code. Furthermore, in order to illustrate the choices made for this representation, we use the code presented in Figure 1.1 all along this section.

```

int N, *A;

long long int *B, *C;

/* ... Initializations of N, A, B and C ... */

for (int i = 2; i < N - 2; i++) {

/* S1 */ A[i] = (A[i-2] + A[i-1] + A[i] + A[i+1] + A[i+2]) / 5;

/* S2 */ B[i] = B[i] + A[i] * C[i];

/* S3 */ B[i] = B[i] - (B[i-1] - B[i]) * C[i-1];

}</pre>

```

Figure 1.1 – Example code for the illustration of the memory-use graph

#### 1.3.1 Flow of data in the semi-regular case

At the most basic level a computation, an algorithm, a program is nothing more than the specification of a set of statements to be executed in a specific order. The level of abstraction with which these statements are given can vary over a very wide range and is closely associated with the different types of programming languages that exist. The lowest level of abstraction typically corresponds to the lowest level language (assembly programming), *i.e* a statement representing a single machine instruction, whereas higher levels of abstraction may let a statement correspond to a

Figure 1.2 – Flow of data for a dataflow computation

set of instructions, a basic block or even an entire function. In the case of the example in Figure 1.1 the statements 1, 2 and 3 (S1, S2 and S3) correspond to individual lines of C code. From the point of view of the representation the invariant for all abstraction levels is that statements are the atomic elements.

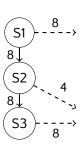

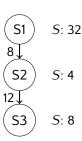

Figure 1.3 – Raw representation of the example code

Statements may take input, produce output or perform intermediate steps. As a result data may be used, modified or produced. This is illustrated in Figure 1.2 (no link with Figure 1.1) and forms the basis of the dataflow programming paradigm. We use the same principle for our *memory-use graph*: nodes represent statements and directed edges between them represent reuses by the target node of data produced by the source node. Following this the example of Figure 1.1 results in three separate nodes as shown in Figure 1.3. Dashed edges are used to represent inter-iteration reuses whereas full edges repre-

sent intra-iteration reuses. Because we have not yet described the graph's semantics, this example should not be interpreted as a correct and exact representation of the code in Figure 1.1. Starting from this point we now dive into the specifics of the *memory-use graph*.

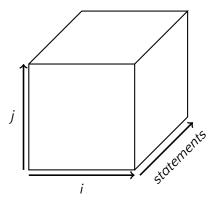

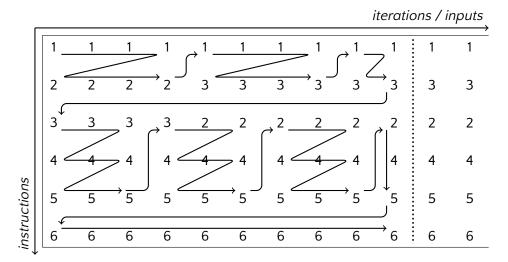

An important observation to make is that in the case of static dataflow languages the entire set of available input is processed by the same computational graph. This means that the same code is applied by iterating over each separate input. For this reason we will characterize the computation as being *semi-regular*: an irregular set of varying statements that are applied in a uniform way over a set of data. From this point of view, the execution of a loop in a more imperative-styled programming paradigm has exactly the same behavior with the different statements of the loop-body being applied over the iteration domain of the loop. Another consequence of the regularity over the iteration domain is that the amount of data that is transmitted between the same two nodes of the *memory-use graph* is identical at each iteration. We can thus annotate each edge with the amount of data that it represents. This is done in Figure 1.4 for each reuse of the example code: arrays A and B contain elements of size 8 whereas array C contains elements of size 4. Again the semantics of the edges being unknown this example should not be seen as an exact representation.

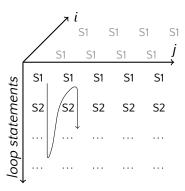

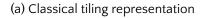

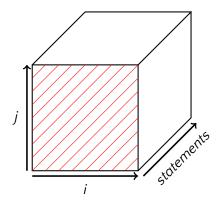

By making a short detour through the world of loop tiling, we can improve our understanding of the above-described semi-regular characteristic by comparing it to the usual representation of loop nests. In the case of classical tiling, each element within the iteration domain of the loop is usually represented by a single point. An iteration of a loop nest of depth k is then associated with coordinates in  $\mathbb{N}^k$  according to the values of the induction variables for this iteration. This correspondence between the loop nest and its representation is shown in Figure 1.5 where each point of the grid represents a single full itera-

Figure 1.4 – Example representation annotated with byte sizes

tion of the loop. A consequence is that this representation is fully *regular* as all elements of the grid are associated with the same code. Our dataflow-based approach

```

for (int i = 0; i < N; i++)

for (int j = 0; j < M; j++)

/* Loop statements */

/* S1 */

/* S2 */

/* ... */

S1, S2 S1, S2 S1, S2 S1, S2 S1, S2

... ... ... ...

S1, S2 S1, S2 S1, S2 S1, S2 S1, S2

... ... ... ...

S1, S2 S1, S2 S1, S2 S1, S2 S1, S2

... ... ... ...

S1, S2 S1, S2 S1, S2 S1, S2 S1, S2

... ... ... ...

S1, S2 S1, S2 S1, S2 S1, S2 S1, S2

... ... ... ...

S1, S2 S1, S2 S1, S2 S1, S2 S1, S2

... ... ... ...

```

Figure 1.5 - Mapping from code to a regular grid for classical loop-tiling

Chapter 1 State data

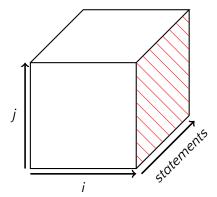

would not showcase this regularity as can be observed in Figure 1.6.

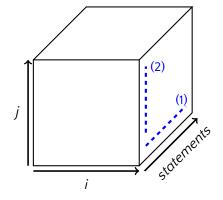

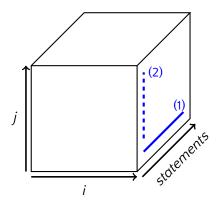

The semi-regularity of the computation implies that it should be possible to represent the data reuses of all iterations with the same *memory-use graph*. However by its definition the graph only contains the statements of a single iteration whereas data reuses often cross multiple iterations. If we want to reflect this fact while keeping the form of the *memory-use graph* more information has to be added to the graph, again inspired by the dataflow programming paradigm.

Figure 1.6 - Semi-regular grid

#### 1.3.2 State data

When provided with a large set of input values, a dataflow program may need to keep specific data between the processing of separate input values. Examples of such values could be counters and accumulator variables that are associated with such stateful processing. The same concept can be applied to the reuse of data between different iterations of a loop.

For the structure of the *memory-use graph* we associate *state information* with each node by providing the size of the state data that should be transmitted from iteration to iteration. Because our goal is only to reduce the amount of IO operations of the analyzed code we choose not to distinguish between separate state data elements that are transmitted by the same node to subsequent iterations. This means that a node in our graph only has a single state data attribute that groups together all the

Figure 1.7 - Construction of state data annotations in a memory-use graph

Figure 1.8 - Example with states

Figure 1.9 - Cross-node reuses

sizes of all state data elements that this node transmits.

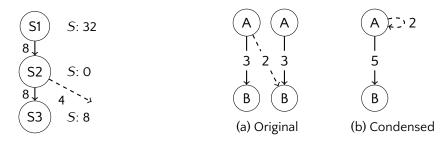

The state data attribute is not necessarily equal to the combined sizes as the data reuse of a specific element may occur in the next iteration or in any other following iteration. In turn this means that a node may need to store several iterations worth of state data if the reuse is not immediate as illustrated in Figure 1.7. The exact amount of memory required is the size of the state date of a single iteration multiplied by the number of iterations between reuses of the data. This state data reuse can then be represented as a loop-back edge within the *memory-use graph* or as an attribute of the node (noted *S*). The effect of this phenomenon on the example representation can be observed in Figure 1.8 on the state data of S1.

In the case where a reuse is performed across multiple iterations, but not within the same node, it can still be described using both state data and intra-iteration reuses. The value is first transported as a state data of the node that produces it to the target iteration. From there a standard reuse within the iteration itself transfers the data to the target node. This transformation is shown in Figure 1.9 and applied to the example in Figure 1.10. Modifying the *memory-use graph* in such a way may introduce cycles which is problematic as we need the graph to be acyclic. Several solutions can be considered:

Figure 1.10 – Condensed example

• Simplifying the graph by considering the nodes within each strongly-connected component as a single super-node. This effectively masks the cycles in all further analyses performed on the *memory-use graph*. However by reducing the number of nodes in the graph this increases the granularity at which the code is considered and as such may decrease the quality of the tiling and indirectly increase the IO cost as well as the associated operational intensity.

• Not considering the reuse for the optimization of memory usage and removing the conflicting edge from the *memory-use graph*. This means that the reuse will in any case contribute to the code's IO cost. Even though this does not increases the granularity of the representation it still increases the IO cost. Furthermore, as the reuse is not included in the graph, this may raise issues when performing tiling because it remains equivalent to a Read-After-Write dependency without being accounted for in our representation. As a result this method for the removal of a cycle in the graph is not considered.

More specific information on the ways in which the state data information is precisely obtained and added to the graphs in the different use-cases is discussed below. For loops this is done in Chapter 4 and for dataflow programs this is detailed in Chapter 5.

Now that edges of the *memory-use graph* are annotated with data sizes and nodes are labeled with state data weights all reuses are taken into account and represented. One element however has still to be considered: the fact that nodes, while being atomic elements in the representation, are not atomic in their execution or their usage of memory.

#### 1.3.3 Internal computational requirements

Because of the abstract notion of statements, a node may represent hundreds or thousands of lines of machine instructions. As such its execution may produce intermediate values that do not appear within our reuse representation but still require memory at some point. In a more general manner a node in the *memory-use graph* represents an instruction as described in Section 1.3.1 and an instruction can be anything from a single machine-instruction to a high-level statement that performs a complex computation on its arguments.

Figure 1.11 – Example with internal computation requirements

Because of this the computation of a single node may require more memory than the sum of the weight of its state data and the size of all incoming reuse edges. For such cases a second attribute is added to each node: the *internal computation requirement*. The value of this attribute is computed by subtracting the state data and the incoming reuses from the total amount of memory required by the nodes execution. For the example code we computed the values for the

internal computation requirement of each node (noted *C*) by writing a naive assembly code equivalent for each statement. The result is presented in Figure 1.11. In a general manner the computation of the exact memory use of a statement is not a focus of this study but an example can be given: when the exact content of the node is known under the form of machine instructions it suffices to count the number of registers that are used. A detailed application of this principle can be found in Chapter 4.

Adding the internal computation requirements to the *memory-use graph* completes its semantics. As a final step we will give a short and more formal definition.

#### 1.3.4 Formal definition of a memory-use graph

For a code snippet containing a set S of statements that are considered to be executed in an atomic fashion, the corresponding *memory-use graph* is a directed-acyclic graph G = (V, E) where:

- $V = \{v \in \mathbb{N}^2\}$

- $\cdot E = \{e \in V \times V \times \mathbb{N}\}$

- $\cdot \exists f: S \twoheadrightarrow V$

- $\cdot \ \forall (u, v, r) \in E$  at most r data is produced in  $\{f^{-1}(u)\}$  and used in  $\{f^{-1}(v)\}$

- $\forall v = (s, i) \in V$  at most s data is available during the computation of  $\{f^{-1}(v)\}$  and should be available for the computation of  $\{f^{-1}(v)\}$  at the next iteration

- $\forall v = (s, i) \in V$  the amount of memory required by the computation of  $\{f^{-1}(v)\}$  is lower than or equal to  $s + i + \max(\ln(v), \operatorname{Out}(v))$ , with  $\ln(v) = \sum_{(i,j,r) \mid j=v} r$  and  $\ln(v) = \sum_{(i,j,r) \mid i=v} r$

#### 1.4 Memory usage of a code

Once the *memory-use graph* of a code is generated, what is the amount of memory required to run the code. Even though we consider that the amount of memory required by the atomic execution of each node of the graph is a known parameter, the handling of several nodes is not straightforward. Multiple questions arise. Has the code already gone through register allocation? Do data objects have yet to be mapped to memory addresses or do we have to take an existing mapping into account? In which order are the nodes executed?

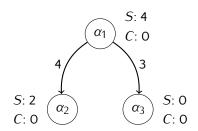

#### 1.4.1 The impact of scheduling

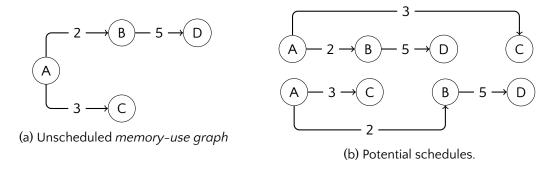

When two statements in a code are linked through a reuse edge between their representative nodes in the *memory-use graph* their order of execution, *i.e* their schedule, is enforced by the direction of the edge. This is true whether they are part of the same iteration or correspond to the same node in two different iterations of the *memory-use graph*. If there is no such edge their schedule is unconstrained. In the case of two statements this is not a major issue. However if multiple statements are involved it becomes much more of an issue. This is of course not a new research question and the topic of scheduling has been a major topic since the advent of compiler research. Our goal here is not to introduce new approaches but instead to merely make the observation that the scheduling of the nodes of the graph, and their multiple instances, may have a significant influence on the associated memory usage.

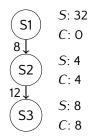

See the example *memory-use graph* in Figure 1.12. Two different schedules are given for the corresponding statements of a single iteration. For the sake of simplicity the state and internal computation requirements are left out. For the first scheduling to be executed the maximum amount of memory necessary to store reused data is achieved at the end of node B and has a value of 3+5=8. At the same time the maximum for the second scheduling is achieved at the end of both nodes A and D and has a value of 3+2=5. Under the hypothesis of an available memory of size 6 the first schedule would generate communications with a distant memory whereas the second would not.

The main consequence of our observation here is that scheduling can influence memory usage. This has direct consequences on our tiling optimization presented in Chapter 3.

Figure 1.12 – An unscheduled memory-use graph and two of its possible schedules

#### 1.4.2 Register pressure & memory mapping

As mentioned in Section 1.3.3, we assume the memory size required for the execution of a specific node of the *memory-use graph* is known. But how is this quantity obtained?

On one hand, if the target is the optimization of register usage it is very likely that a node can be directly linked to one or more machine instructions. This means that we can evaluate the maximum register pressure during the execution of the code that the node represents.

On the other hand, if we want to optimize cache memory usage, a lot depends on whether the variables used within the code have already been assigned to specific memory addresses or not. In the case of such a memory-mapped code it is theoretically possible to count the number of cache lines that are referenced within each node. It is then possible to check if these referenced lines fit into the target cache considering both its size and its associativity. For non-memory-mapped code a similar approach would simply be to compute the amount of data that is accessed by the code's execution and compare it to the total cache size. This would however require the compiler and linker to perform a perfect memory-mapping later on and even then the result could potentially underestimate the real memory usage and IO cost.

Because the goal at this point is not to study the memory-mapping issues in depth, we assume for the moment that the memory use of every node is known when the *memory-use graph* is built. Some additional discussion is necessary when we attempt to extend our tiling approach to execution-trace analysis in Chapter 6 and we can now move on to the main focus of this section: the memory usage model.

#### 1.4.3 A memory usage model

After the discussion about scheduling as well as the memory usage of individual nodes of the *memory-use graph* it should be clear that the model that we are looking for has one main goal: verifying that a given set of nodes subjected to a specified scheduling can be executed within a target memory without requiring any communications with a higher level in the memory hierarchy.

A key fact here is that such a set of nodes may potentially include the same node multiple times when the corresponding piece of code crosses iterations, *i.e* different instances of the same statement.

Evaluating the memory usage of a given set of node instances and schedule is similar to a *max-live* computation. A piece of data is considered to be *live* between

Chapter 1 Only reuse edges

Figure 1.13 - Liveness of edges with respect to the memory usage of a partial schedule

the point of the schedule where it is produced and the point where it is last used. In other words, the edges of the *memory-use graph* actually represent *live ranges*. A particularity is that we only take into account data that flows between nodes belonging to the set of node instances for which we perform our memory usage evaluation. The set may not include all nodes of the *memory-use graph* and because of this edges that have an origin or a target outside the set are not considered to be *live*.

In Figure 1.13 the nodes of a *memory-use graph* are given with their state (S) and internal computation requirements (C). The graph is copied three times in order to represent three iterations. Node duplicates are indexed by the iteration to which each duplicate belongs. The set that is considered for evaluation corresponds to the nodes with a full circle. Following our definition of *live* reuses, only the edges drawn with a full line are considered as opposed to the edges drawn with dashed lines.

To illustrate the effect of scheduling we compute the memory usage of our set assuming two potential schedules: line-by-line and column-by-column.

#### Only reuse edges

At first, we do not consider state sizes and internal computation requirements. We introduce evaluation points between each node of the evaluated schedule. The total usage corresponds to the maximum amount of *live* reuses measured at each of the evaluation points. When applied, this produces two different values for the two proposed schedules:

- 1. Schedule  $B_1 \rightarrow C_1 \rightarrow D_1 \rightarrow B_2 \rightarrow C_2 \rightarrow D_2 \rightarrow B_3 \rightarrow C_3 \rightarrow D_3$ Memory usage  $\max(4, 2, 0, 4, 2, 0, 4, 2) = 4$

- 2. Schedule  $B_1 \to B_2 \to B_3 \to C_1 \to C_2 \to C_3 \to D_1 \to D_2 \to D_3$ Memory usage  $\max(4, 8, 12, 10, 8, 6, 4, 2) = 12$

#### State data

The next step is to include the state data. To do so we only need to extend the liveness principle to the related reuses. In our model this means that state data is equivalent to a *live range* between a node in one iteration and the same node in the next iteration. As state data may actually be the result of consolidated reuses over a distance of multiple, iterations this measure may be a conservative approximation of the real amount of data that is reused. We update the previous computations accordingly without changing the evaluation points. Again we find different usages for both schedules:

- 1. Schedule  $B_1 \to C_1 \to D_1 \to B_2 \to C_2 \to D_2 \to B_3 \to C_3 \to D_3$ Memory usage  $\max(4, 6, 6, 10, 8, 6, 10, 4) = 10$

- 2. Schedule  $B_1 \to B_2 \to B_3 \to C_1 \to C_2 \to C_3 \to D_1 \to D_2 \to D_3$ Memory usage  $\max(4, 8, 12, 14, 12, 6, 6, 4) = 14$

#### Internal computations

The last step is to include internal computation requirements. The memory usage that these represent is local to a node and does not influence edges. As such we need to add evaluation points at each node in the evaluated schedule. The memory use for a single node is considered to be equal to the maximum of the memory use before or after the the node's execution to which we add the internal computation requirement. This brings us to the final update to our memory-use computation:

- 1. Schedule  $B_1 \to C_1 \to D_1 \to B_2 \to C_2 \to D_2 \to B_3 \to C_3 \to D_3$ Memory usage  $\max(7, 4, 8, 6, 6, 6, 13, 10, 12, 8, 8, 6, 13, 10, 12, 4, 4) = 13$

- 2. Schedule  $B_1 \rightarrow B_2 \rightarrow B_3 \rightarrow C_1 \rightarrow C_2 \rightarrow C_3 \rightarrow D_1 \rightarrow D_2 \rightarrow D_3$ Memory usage  $\max(7, 4, 11, 8, 15, 12, 16, 14, 16, 12, 14, 6, 6, 6, 6, 4, 4) = 16$

With the previous example and the associated computations we introduced our memory usage model. We have also shown how this model can lead to a straightforward application on a *memory-use graph* and a (partial) scheduling of its nodes. The next step in the evaluation of a scheduling is its IO cost.

#### 1.5 IO cost of a code

A tiling optimization of a piece of code attempts to reducte the number of IO operations between the different levels of a memory hierarchy through an increased data locality. For this to be possible we should in the first place be able to quantify the number of IO operations required by the code for a given scheduling and tiling. As we have not yet discussed and defined *generalized tiling* (see Chapter 3), we will give and use basic assumptions where necessary.

Because our goal is to target different levels of the memory hierarchy, we first look at some of the differences that may exist between these levels.

#### 1.5.1 Registers are not cache

The major difference between processor registers and cache-memory resides in the manner in which they are accessed. Processor registers must be explicitly loaded with their content through load/store instructions but are the only ones that can be used within computations<sup>1</sup>. Cache memory, on the other hand, is accessed indirectly and IO operations with other levels of cache and distant memory are implicit, but the induced latencies for a cache-miss are much higher than for a cache-to-register load.

Another important difference is that a cache-line is much larger (typically 64 bytes) than a single register or load/store operation (typically 4 or 8 bytes). The result is that a cache-miss can in theory occur at every load or store operation with a new address if a new cache line is accessed each time. In such a case, we would be using only 1/16th or 1/8th of the capacity of each cache line in practice. The influence of this phenomenon can be anything from very extensive to almost non-existent and depends on the memory-mapping of variables combined with a schedule for the code as was already suggested in Section 1.4.2.

<sup>&</sup>lt;sup>1</sup>We do not consider the possibility in x86 architectures to use memory-operands. Replacing such an operation by a load-compute or a compute-store sequence will not change the amount of IO operations and barely influences the general performance. Furthermore other target architectures do not support such a feature.

Because tiling is used on code that executes over a uniform iteration domain of significant size, it is reasonable to make the assumption that the underlying data also exhibits a fair amount of regularity in its organization and memory-mapping (arrays, buffers, ...). Considering this, we assume that cache lines are used in a near optimal fashion in code that is targeted by tiling.

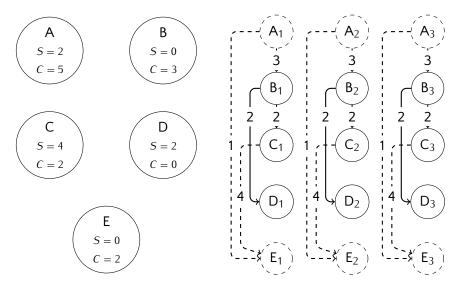

## 1.5.2 Node by node evaluation

Computing the IO cost of the entire code requires us to determine what reuses can be stored within local memory and what data must be transferred to a more-distant memory and thus contributes to the IO cost. Our approach here is to partition the execution of the code into separate pieces. Because the entire execution can be represented by k copies of the *memory-use graph*, k being the number of iterations that the code performs, the partitioning is done on the nodes of these k copies.

For our evaluation of IO the cost to be valid, two criteria are to be verified by the partitioning:

- 1. Each individual partition should admit a scheduling whose memory usage, according to our model, is lower than or equal to the target memory size.

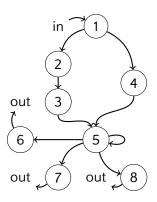

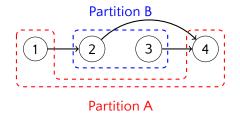

- 2. Each partition should be executable in an atomic fashion. As such there should be no data dependency path that starts in a partition, passes outside of it and then flows back in. Such a path would require code exterior to the partition to be executed to complete the partition, thereby going against the atomic property. A graphical representation of this property is given in Figure 1.14 and it is further discussed in Chapter 6 under the form of convex partitioning of a directed acyclic graph.

(a) Path  $1 \rightarrow 2 \rightarrow 4$  goes from A to B to A: it is a non-convex partitioning.

(b) There is no path from A to B to A or from B to A to B: it is a convex partitioning.

Figure 1.14 - Example and counter-example for convex partitioning

With such a partitioning of the code in hand we can define the IO cost of the code in our model. The first constraint on the partitions imposes that all reuses belonging to a single partition can flow through the target memory and as such do not generate any communications with distant memory. The remaining reuses between partitions are the only ones that generate IO operations that contribute to the cost of the code as a whole.

For each partition we count the amount of data that originates outside of it. This may include state data when the nodes representing the copies of a same node in two consecutive iterations do not belong to the same partition. The amount of data entering a given partition is potentially different from the sum of the weights of all incoming edges. Multiple edges may represent the same data element that is reused by different nodes of the same partition; such duplicates should not be counted in the IO cost computation.

We consider incoming data and thus we only account for load operations in the IO cost of the code. Store operations are not taken into account because a given data element is only produced once. If it is a result that should be kept the associated store will never be removed as it is part of the computation performed by the code. If it is an intermediate result and the scheduling allows it, it is never even written to the more distant memory. In case it can not be kept, it is written to a distant memory before being loaded at least once for a reuse. For these reasons the number of store operations related to reuses is less then the corresponding load operations count. As a consequence the minimization of load operations also directly gives a tighter upper-bound for the number of store operations.

Chapter 2

# Communication Costs in a Manycore Environment

The bird launched itself north and east, straight as an arrow toward Tar Valon. After a moment's thought Ronde prepared another copy on another narrow strip of thin parchment and fastened it to a bird from another coop. That one headed west for she had promised to send duplicates of all of her messages.

R. Jordan - The Fires of Heaven

## 2.1 Context and goal

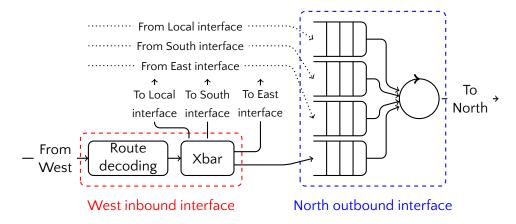

After considering the memory usage of a given code snippet as well as the number of IO operations that are required by its execution, we move on toward a different kind of communications. If we want to apply our tiling method to an environment with distributed resources, communications can go beyond a simple memory hierarchy. For example, it may be necessary to use explicit data communications between the different processors of a distributed system. Or, if we consider the case of manycore processors, these explicit transmissions flow through a Network-on-Chip that link the cores on a single chip. The communications supporting the distribution of computations over different resources require the highest degree of stability in characteristics such as latency and bandwidth. The current chapter aims at providing the necessary theoretical framework to provide this stability.

As the work described in this manuscript was performed during a collaboration with a manycore chip manufacturer, this study of the memory communications beyond the cache-hierarchy is focused on the case of Network-on-Chip-based architectures. The study of traffic behavior as well as its control on Network-on-Chips through Quality-of-Service protocols has been identified as a major issue since the inception of the technology [Mar+09]. For the case of distributed systems beyond manycores, a significant amount of literature exists on the topic of network performance, Quality-of-Service and latency evaluation.

Before looking at what elements and behaviors we want to model and describe, we first need to give some definitions and terminology related to the topic. In no way is this an in-depth survey of all existing Network-on-Chip variants. It should nonetheless allow the reader to clearly understand the context within which our work falls as well as the limits to the theoretical and practical results that will be presented.

After this short introduction, we focus on the presentation of existing network traffic characterizations. Such theoretical models are used both to describe traffic as it is observed on a network, and as a set of constraints that may be forced onto a network flow in order to achieve a desired behavior.

We then move on to the analysis of both the advantages and drawbacks of using a Quality-of-Service regulation on data flows within a Network-on-Chip. Such a regulation can take many different shapes: some rely on back-pressure generated by routers throughout the network, others require to model the behavior of the whole network.

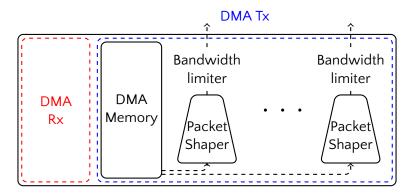

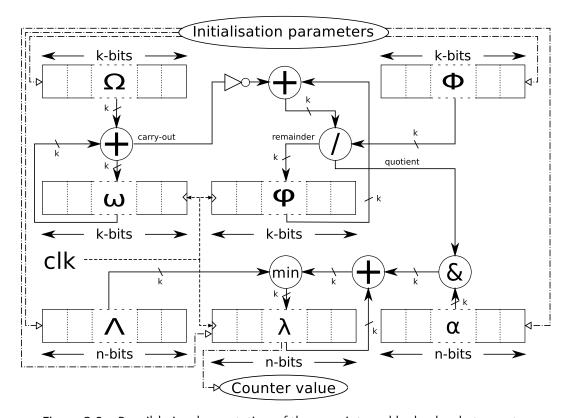

The last part of this chapter reports on a case-study that applies a Quality-of-

Service regime to the MPPA processor family. Because of its architectural specifics, the regulation requires a theoretical network model that is able to compute Quality-of-Service parameters. This work was also published in two separate papers [Din+14b; Din+14a]. A second step is the redesign of the physical bandwidth-limiter that applies the computed parameters at hardware level. The new design from this second step, which is presented in Section 2.5.3, is implemented in the second generation of the MPPA chip family and is the subject of a filed patent.

## 2.2 Architecture of a general-purpose Network-on-Chip

A Network-on-Chip is an infrastructure used by the computations of a manycore processor. In a general manner, it can be seen as a downsized version of the network within a distributed cluster or supercomputer. This is not surprising as the manycore concept is actually based on the idea of adapting the logic behind these larger scale systems to fit into a single chip. The most important elements for our study are:

- 1. The memory architecture for which the Network-on-Chip serves as interconnect

- 2. The topology and routing logic of the network

- 3. The types of traffic that are expected

#### 2.2.1 Memory architecture

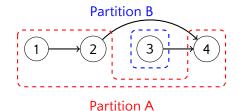

Existing multicore processors use a monolithic memory hierarchy. All cores share at least the same last-level cache. Lower cache levels may be divided into separate units that each serve a subset of the cores. This creates a tree-like shape that is referred to as the memory hierarchy. The different levels and units of this cache hierarchy implement a hardware-based chip-wide cache coherency in the overwhelming majority of such architectures. For manycore processors however, a similar approach would raise significant issues: required surface and power consumption for the coherency logic, exponentially increasing latencies for cache-misses, ...

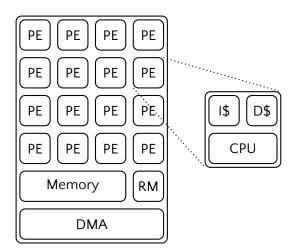

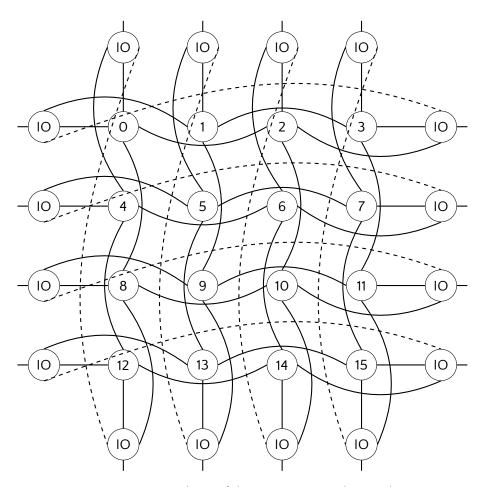

The paths taken by existing manycore architectures, such as the Tile-Gx family [Jag+12] or the MPPA family [Din+14b], differ but a general tendency is to distribute the memory over the numerous cores to create small independent local memories that may better benefit from data locality within parallel computations. The association of a computational core and some local memory creates an element known as a

Figure 2.1 – Memory organizations for multicore and manycore processors

processing tile or processing element. These elementary units are then duplicated to achieve the desired core-count within a manycore processor and they are linked all together by a Network-on-Chip. This approach does not prohibit the implementation of hardware-based cache-coherency but the protocols involved in the process differ from their multicore counterparts because they are distributed by design, as for example directory-based coherency. Yet another alternative is to implement software-based cache-coherency or to forgo cache-coherency entirely. This does however puts a significant burden on the programmer or the run-time environment in order to maintain memory consistency.

The structural differences between the multicore and the manycore approaches are summarized and illustrated in Figure 2.1.

Chapter 2 Routers & routes

#### 2.2.2 Data traffic

As can be deduced from the description of the memory architecture in Section 2.2.1, the Network-on-Chip's main purpose is to ensure the transfer of data between processing elements and potentially to off-chip interfaces such as DRAM ports or Ethernet interfaces. However this single purpose hides a multitude of different data communications that may or may not share common characteristics and constraints.

For example, depending on the architecture chosen for the memory layout, processing tiles may contain only cache memory or also some local memory accessible by the local core. In the latter case, it is entirely possible to allow cores to transfer data between the memory of a distant tile and the local memory. This generates explicit and thereby somewhat predictable data communications as the sequence of a program's execution is known. Cache communications, however, are implicit and unpredictable because their behaviour depends on a multitude of factors.

Cache communications should be treated in such a way as to minimize latency. Explicit communications however may, depending on the use-case, require bandwidth optimization instead. These potentially opposite goals may influence our choices when we want to apply a Quality-of-Service protocol in Section 2.4.

The communications themselves are performed in a packet-switched channel-based fashion. A channel is opened at the source of a data transmission with a given destination and some other parameters. The data that is pushed through a channel is cut into packets of fixed size which are then individually and sequentially sent through the Network-on-Chip. Each packet is prefixed with a header containing elements such as destination, target memory address and other administrative information. In turn a packet can be divided into so-called flits¹which are the atomic transmission elements.

As the network is located on the chip itself, links between nodes are materialized by a parallel set of wires. Usual links are 32 or 64-bit wide. With respect to this fact a *flit* is a data unit equal to the width of a link. *Flits* are also the usual level of granularity at which other elements of the Network-on-Chip function, especially the routers. As can be seen in Figure 2.1 each processing tile of a manycore processor has a core and some local memory or cache but also contains a router. This router is both part of the tile and part of the Network-on-Chip on which the tiles are positioned.

<sup>&</sup>lt;sup>1</sup>The term flit is a contracted form of the expression *Flow control digit*.

#### 2.2.3 Routers & routes

The usage of a Network-on-Chip is a natural evolution of earlier architectures with multiple components that used 1-to-1 links or busses. The increase in the number of elements in the network made the area and energy costs of dedicated 1-to-1 links prohibitive whereas in the case of busses the global available bandwidth has become insufficient thereby forming a performance bottle-neck. As has been the case in the past with computer networks the next step was to introduce switching. Just like this technique has enabled the construction of vast networks with thousands of nodes it has brought the same kind of advantages to manycore architectures.

While switching can either be done in the form of *circuit switching* or *packet-switching* it is the latter one that is predominantly used in computer data networks and it is also the packet-switching method that is used by existing Network-on-Chip architectures. While transiting over the network, data packets need to be routed, an action that is performed by the previously described routers present in each processing tile. In turn this implies the computation of routes for each data packet so it can move from its source to its destination tile through the network topology<sup>2</sup>.

Routers and their implementations in manycore architectures take up various designs as their exact function is heavily dependent on the type of routing on which the network is based. In the case of Network-on-Chips, the most frequently encountered routing methods are:

Virtual Channels The original goal of this technique was to implement virtual *circuit switching* over a packet-switched network. This means allocating resources at each router on the route of a communication before sending data which may guarantee better latency and/or bandwidth performances. The allocated resources include buffer space in the routers and access to the switching fabric leading to the next router. In the case of Network-on-Chips the main advantage compared to *wormhole switching* is to make a better use of resources at each router, especially buffer memory.

Wormhole Switching Wormhole switching can partially be seen as a simplified version of virtual channels, without resource allocation. The term wormhole is used because of the possibility for *flits* to traverse routers without waiting for the other *flits* of the same packet to arrive whenever the next link in the packet's route is not in use. This is in opposition to a *store-and-forward* mechanism. Routers do

<sup>&</sup>lt;sup>2</sup>Network topologies are an entire research topic to themselves that predates the arrival of Network-on-Chip architectures and are not discussed in detail here.

Chapter 2 Network calculus

not contain any logic except for route decoding as routes are determined and encoded in the packet's header before it is emitted.

A logical consequence of having different types of routing and router designs is that modeling the behavior of traffic on the network may be more or less challenging. As the goal of this chapter is to describe a model for Network-on-Chip communications we will focus on a specific architecture later on. Firstly, however, we should have a general view of the types of existing models.

## 2.3 State of the art

## 2.3.1 Describing network traffic

With the basic notions of Network-on-Chips and their architecture stated we now present an oversight of the existing literature on the modeling of communications over such a network. The foremost element in such a model is the traffic itself: data is injected at nodes throughout the network topology but it would be of great help if we could know how it is injected, the rate at which it is done, etc... If we can model such characteristics, it should then be possible to describe the behavior of the traffic when it flows through the different constituents of the Network-on-Chip.

Traffic regulation and its optimization have been explored in the macroscopic case since the first computer networks appeared in the sixties. Initially, the most common issues involved the over-subscription of link capacities, *i.e* too much data needed to be transferred through links with not enough bandwidth. Global source rate adaptation was identified as a convenient way to avoid network congestion and router buffer saturation. The work of Kelly [KMT98] jointly redefined fairness and optimality: a formalization for an optimal distributed method for rate calculation based on the Lagrangian method. Network calculus was initiated by Cruz [Cru91a; Cru91b] in order to compute tight bounds for end-to-end transfer delays in the presence of sporadic traffic bursts, which he named "distortion".

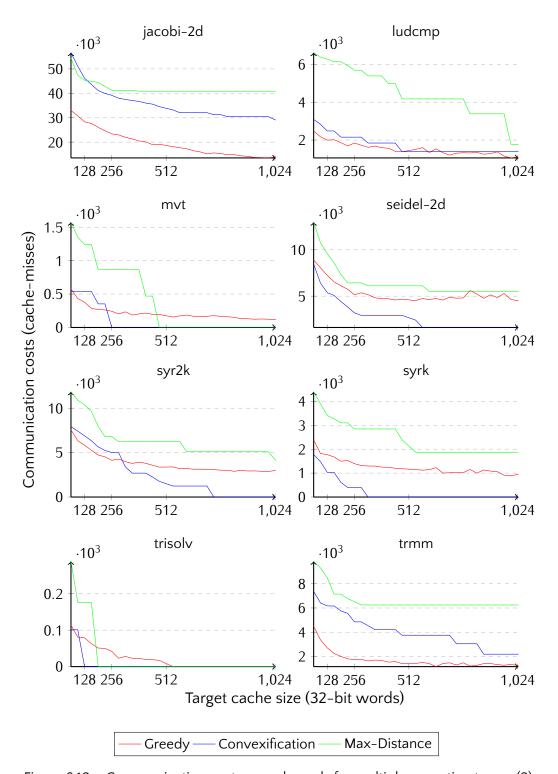

#### 2.3.2 Network calculus