## Exploiting heterogeneous manycores on sequential code

Bharath Narasimha Swamy

### ▶ To cite this version:

Bharath Narasimha Swamy. Exploiting heterogeneous manycores on sequential code. Computer Science [cs]. UNIVERSITE DE RENNES 1, 2015. English. NNT: . tel-01126807

## HAL Id: tel-01126807 https://inria.hal.science/tel-01126807

Submitted on 17 Mar 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^o$  d'ordre : ANNÉE 2015

# THÈSE / UNIVERSITÉ DE RENNES 1 sous le sceau de l'Université Européenne de Bretagne

pour le grade de DOCTEUR DE L'UNIVERSITÉ DE RENNES 1

> Mention : Informatique École doctorale Matisse

> > présentée par

## Bharath NARASIMHA SWAMY

préparée à l'unité de recherche INRIA – Bretagne Atlantique Institut National de Recherche en Informatique et Automatique Composante Universitaire (ISTIC)

Exploiting heterogeneous manycores on sequential code Thèse soutenue à Rennes le 05/03/2015

devant le jury composé de :

Pr Daniel Etiemble

Professeur, Université Paris 11 / Rapporteur

Pr Smail Niar

Professeur, Université de Valenciennes / Rapporteur

Dr Alain Ketterlin

Maître de conférences, Université de Strasbourg /

Examinateur

Dr Erven Rohou

Directeur de recherche, INRIA Rennes / Examinateur

Pr Olivier Sentieys

Professeur, Université de Rennes 1 / Examinateur

Dr André Seznec

Directeur de recherche, INRIA Rennes

Directeur de thèse

## Acknowledgements

I wish to thank Andre, firstly for the opportunity to work in the ALF team for preparing the thesis, and for his guidance and help during the course of work.

I thank Alain who helped in many ways in course of the thesis work.

I thank Pierre for making available his simulator, which is used for experiments in this thesis after extensions.

I thank Erven and Surya for the opportunity to collaborate, summaries of these studies are included in the thesis.

I thank Emmanuel for his help in writing an abstract of the thesis in French.

I thank my colleagues in the ALF team for their help and support.

I thank the members of the jury for the opportunity to defend the thesis.

## Contents

| Ta           | able | of cont  | ents                                                        | 1  |

|--------------|------|----------|-------------------------------------------------------------|----|

| $\mathbf{R}$ | ésum | ié en fr | rançais                                                     | 3  |

| In           | trod | uction   |                                                             | 13 |

| 1            | Bac  | kgrour   | $\mathbf{nd}$                                               | 17 |

|              | 1.1  | Hetero   | ogeneous Many Cores                                         | 17 |

|              |      | 1.1.1    | Improving Sequential Performance on Many Cores              | 21 |

|              | 1.2  | Helper   | Threads                                                     | 25 |

|              |      | 1.2.1    | Issues in applying helper threading to accelerate a sequen- |    |

|              |      |          | tial thread                                                 | 25 |

|              |      | 1.2.2    | Overheads of helper threading on loosely coupled systems .  | 28 |

| 2            | Sta  | te of tl | ne art                                                      | 31 |

|              | 2.1  | Exploi   | ting additional cores for sequential performance            | 31 |

|              |      | 2.1.1    | Using additional cores to run pre-computation based helper  |    |

|              |      |          | threads                                                     | 32 |

|              |      | 2.1.2    | Decoupled LookAhead Processors                              | 36 |

|              |      | 2.1.3    | Using additional cores to emulate hardware structures       | 38 |

|              | 2.2  | Utilizi  | ng small cores                                              | 41 |

|              | 2.3  | Hardw    | vare support for tighter coupling of cores                  | 42 |

|              | 2.4  | Summ     | ary                                                         | 44 |

| 3            | A F  | Iardwa   | re/Software Framework for Helper Threading on Het           | _  |

|              |      |          | s Many Cores                                                | 47 |

|              | 3.1  | _        | ne architecture and Helper construction methodology         | 48 |

|              | 3.2  | Core t   | ethering                                                    | 49 |

|    | 3.3<br>3.4 | -                                                                               | threading with Core-tethering instructions                                                                                                                                                                               | 52<br>55                         |

|----|------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 4  |            |                                                                                 | of Helper Threading on Heterogeneous Many Cores                                                                                                                                                                          | <b>57</b>                        |

|    | 4.1        |                                                                                 | ation Methodology                                                                                                                                                                                                        | 58                               |

|    |            | 4.1.1                                                                           | Static analysis and helper construction                                                                                                                                                                                  | 58                               |

|    |            | 4.1.2                                                                           | Tracing and instruction stream generation                                                                                                                                                                                | 59                               |

|    |            | 4.1.3                                                                           | Trace driven multi-core simulator                                                                                                                                                                                        | 60                               |

|    |            | 4.1.4                                                                           | Benchmarks                                                                                                                                                                                                               | 61                               |

|    |            | 4.1.5                                                                           | Modeling Large and Small Cores                                                                                                                                                                                           | 61                               |

|    | 4.2        | Experi                                                                          | imental Results                                                                                                                                                                                                          | 64                               |

|    |            | 4.2.1                                                                           | Performance of Helper Prefetching on Small Cores                                                                                                                                                                         | 64                               |

|    |            | 4.2.2                                                                           | Performance of Helper Prefetching on In-order Cores                                                                                                                                                                      | 68                               |

|    |            | 4.2.3                                                                           | An alternative design point for memory intensive workloads                                                                                                                                                               | 69                               |

|    | 4.3        | Summ                                                                            | ary                                                                                                                                                                                                                      | 70                               |

| 5  | Oth        | er Cor                                                                          | ntributions                                                                                                                                                                                                              | 73                               |

|    | 5.1        |                                                                                 | h Prediction and Performance of Interpreters                                                                                                                                                                             | 73                               |

|    |            | Бтапсі                                                                          | $\Gamma$                                                                                                                                                                                                                 |                                  |

|    | 0.1        | 5.1.1                                                                           | Experimental Methodology                                                                                                                                                                                                 | 74                               |

|    | 0.1        |                                                                                 | Experimental Methodology                                                                                                                                                                                                 | 74<br>75                         |

|    | 0.1        | 5.1.1                                                                           | Experimental Results                                                                                                                                                                                                     | 74<br>75<br>78                   |

|    | 5.2        | 5.1.1<br>5.1.2<br>5.1.3                                                         | Experimental Results                                                                                                                                                                                                     | 75                               |

|    |            | 5.1.1<br>5.1.2<br>5.1.3                                                         | Experimental Results                                                                                                                                                                                                     | 75                               |

|    |            | 5.1.1<br>5.1.2<br>5.1.3<br>Model                                                | Experimental Results                                                                                                                                                                                                     | 75<br>78                         |

|    |            | 5.1.1<br>5.1.2<br>5.1.3<br>Model<br>core en                                     | Experimental Results                                                                                                                                                                                                     | 75<br>78<br>81                   |

|    |            | 5.1.1<br>5.1.2<br>5.1.3<br>Model<br>core er<br>5.2.1                            | Experimental Results Revisiting conventional wisdom ing the performance of multi-threaded programs in the many- ra Serial Scaling Model Methodology for model construction and validation                                | 75<br>78<br>81<br>82             |

|    |            | 5.1.1<br>5.1.2<br>5.1.3<br>Model<br>core er<br>5.2.1<br>5.2.2                   | Experimental Results                                                                                                                                                                                                     | 75<br>78<br>81<br>82<br>83       |

| Ca |            | 5.1.1<br>5.1.2<br>5.1.3<br>Model<br>core er<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4 | Experimental Results Revisiting conventional wisdom ing the performance of multi-threaded programs in the many- ra Serial Scaling Model Methodology for model construction and validation Sub-linear performance scaling | 75<br>78<br>81<br>82<br>83<br>85 |

## Résumé en français

Dans la dernière décennie, les serveurs et les ordinateurs ont adopté les processeurs multi-coeurs (Chip Multi Processors, CMP) comme modèle d'architecture prédominante, et, plus récemment, même les devices mobiles ont fait le passage à multi-cœurs. En outre, comme la taille des transistors continuent de diminuer, les prévisions de l'industrie sont prometteurs quant à l'intégration de centaines de cœurs sur une seule puce dans un proche avenir.

Cependant, comme le nombre de cœurs augmente, les nouvelles 'application exigent une plus grande hétérogénéité des profils de puissance/performance, et des tailles des coeurs pour atteindre un modèle d'architecture optimisé. Dans un environnement hétérogène avec beaucoup de cœurs (Heterogeneous Many Core, HMC), quelques cœurs grands superscalaires, sont optimisés pour la latence d'exécution tandis que les petits coeurs sont optimisés pour l'exécution de code parallèle tout en étant petits et faiblement consommateurs d'énergie. Ainsi les systèmes HMC peuvent atteindre une efficacité énergétique plus élevé et permettent l'exécution de code à la fois séquentiel et parallèle en comparaison avec les systèmes multi-cœurs symétriques.

Pour être en mesure d'exploiter pleinement les nombreux cœurs disponibles dans les systèmes HMC, l'application doit se prêter à la parallélisation, soit à la décomposition du calcul en plusieurs threads permettant une exécution simultanée sur plusieurs coeurs. Cependant, dans un avenir prévisible, la plus grande partie du code des applications restera séquentiel, et donc difficile à paralléliser ne permettant pas de bénéficier de l'augmentation du nombre de cœurs. Par conséquent, l'amélioration de la performance séquentielle sur les systèmes HMC demeure une priorité. En plus de renforcer traditionnellement le grand coeur , il y a un regain d'intérêt dans l'utilisation des cœurs supplémentaires pour accélérer les performances des différents threads.

Nous proposons que les nombreux petits coeurs dans un système HMC soient utilisés comme coeurs auxilliaires de faible puissance pour accélérer les threads séquentiels qui s'exécutent sur le grand coeur. Pour adapter les mécanismes de threads auxilliaires au système HMC , nous devons considérer les points suivants.

- 1. Le surcoût lié à l'exécution des threads auxilliaires pour des actions telles que thread-spawn et la synchronisation entrainent des surcoûts en raison des latences générées par la communication entre les processeurs via les caches partagés, et également des surcoûts liés au système d'exploitation.

- 2. En raison de la disparité des performances entre le grand et les petits coeurs, on ne sait pas encore si les petits coeurs sont adaptés pour exécuter des threads auxillaires pour faire du prefetching pour un coeur plus puissant.

- 3. Le prefetching par les threads auxilliaires est limité au dernier niveau de cache partagé (L3). Le thread principal entraîne une latence supplémentaire pour accéder aux lignes de cache préalablement chargées même lorsque le prefetching est fait à temps.

Dans cette thèse, nous nous concentrons sur les threads auxilliaires pour les petits /simples coeurs dans les systèmes HMC, pour améliorer la performance des codes séquentiels pour des programmes s'exécutant sur le cœur principal et ayant une utilisation intensive de la mémoire. Tout d'abord, nous développons un cadre matériel / logiciel pour faire tourner efficacement des threads auxilliaires. Nous ajoutons de nouvelles instructions en mode utilisateur comme interface (jouant le rôle d'une sorte de un co-processeur) pour les cœurs auxilliaires sur les systèmes HMC. Ce cadre permet au cœur principal de pouvoir lancer et contrôler directement l'exécution des threads auxillaires, et de transférer efficacement le contexte des applications nécessaire à l'exécution des threads auxilliaires. Ensuite, en utilisant la simulation basée sur des traces d'exécution, nous évaluons la pertinence des petits coeurs à exécuter les threads auxiliaires pour un thread séquentiel fonctionnant sur le coeur principal, qui est plus puissant. Nous constatons que sur un ensemble de programmes ayant une utilisation intensive de la mémoire, les threads auxilliaires s'exécutant sur des cœurs relativement petits, peuvent apporter une accélération significative par rapport à du prefetching hardware simple, et les petits coeurs fournir un bon compromis par rapport à l'utilisation d'un seul cœur puissant pour exécuter le thread auxilliaires. Enfin, un résumé des autres contributions, fait comme un deuxième auteur est inclus. Les études sont (1) la compréhension de l'impact des prédicteurs de branchement faisant partie de l'état de l'art sur la performance des interpréteurs et (2) une estimation de la performance des programmes multi-threads sur des architectures massivement parallèles.

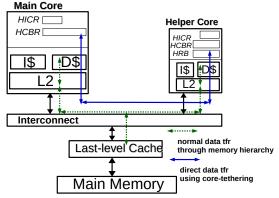

# Un cadre matériel / logiciel pour le thread auxilliaires dans les systèmes HMC

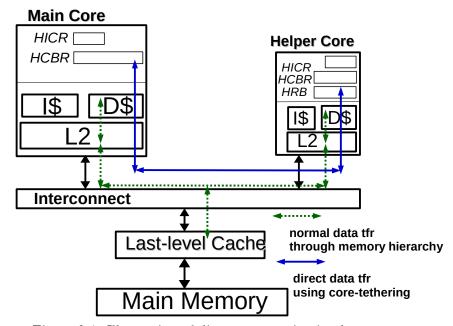

Dans cette thèse, nous présentons "core-tethering", un cadre / matériel et logiciel qui étroitement couples petits et grands processeurs dans un système HMC. Les éléments clés du cadre sont un ensemble de tampons architecturaux qui contiennent des paramètres nécessaires à l'exécution d'aide et de nouvelles instructions pour simplifier l'interaction entre les principaux et auxiliaires cœurs. Ensemble, ils fournissent une interface comme un co-processeur pour petits coeurs dans le système HMC et réduire les coûts de latence d'y accéder pour l'exécution d'aide en utilisant (1) un mécanisme basé sur le matériel pour initier threads auxiliaires et (2) un mécanisme de communication directe entre les cœurs qui contourne la hiérarchie de mémoire (illustré sur la figure Figure 1).

Figure 1: Illustration de la communication directe entre les cœurs.

Helper Control Block Register (HCBR) (HBR), une architecture de type tampon, détient l'action du thread auxillaire et le contexte de l'application nécessaires pour exécuter les actions de l'auxiliaire. Helper Iteration Count Register (HICR) est utilisé pour suivre les progrès dans le thread principal et le thread auxilliaire, et est utilisé lors de la synchronisation du thread auxiliaire.

Trois nouvelles instructions du mode utilisateur sont ajoutés (1) ISHCB - initier écriture du bloc de contrôle de auxiliaire (2) WRHCBR - écrire le registre pour le bloc de contrôle de auxiliaire (3) RDHCBR - lire le registre pour le bloc de contrôle de auxiliaire. Quand le cœur principal exécute l'instruction de ISHCB, contenu de son HCBR sont transférés à la base auxiliaire captif (petite) en utilisant le réseau d'interconnexion, et ont demandé des mesures d'auxiliaire

est lancé.

Helper Request Buffer (HRB), situé sur le petit coeur, détient demandes de ISHCB envoyés par le coeur principale sur l'interconnexion. Lorsque l'action des auxiliaires est SPAWN, il redirige le PC de la petite coeur de la cible-pc dans la demande de ISHCB et commence l'exécution de la fonction auxiliaire. Lorsque l'action de auxiliaire est KILL, l'exécution d'une fonction auxiliaire exécutant sur le petit coeur est terminée, le petit coeur peut maintenant accepter une autre demande de SPAWN. Lorsque l'action de auxiliaire est SYNC, seul le HCBR du petit cœur est rempli.

### Évaluation des threads auxiliaires sur le système HMC

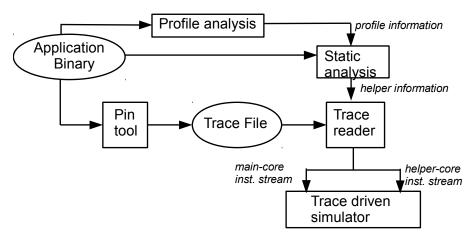

Notre cadre d'évaluation est basé sur des traces d'exécution et comprend trois étapes - analyse statique et construction auxiliaire, de traçage et de génération de liste d'instructions, et de simulation provenant des traces. Un lecteur de trace utilise les informations de l'étape de la construction auxiliaire pour générer des listes d'instructions pour les principaux et auxiliaires coeurs pour l'exécuter sur un simulateur.

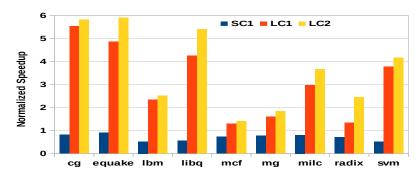

Nous modélisons grands et petits coeurs pour qu'ils exécutent la même ISA. Les paramètres des grandes coeurs sont semblables à processeurs superscalaires (out-of-order) de haute performance (un grand "reorder buffer(ROB)", prédiction agressive de branches, un prédicteur de dépendance et un prefetcher matériel pour le cache L1). Le petit coeur est un processeur avec une faible issue, avec des caches très petits, de petites files d'attente et, une très petite table de prédiction de branchement et aucunes fonctionnalités qui améliorent les performances. Le LargeCore-1 (LC1) modélise un processeur 6-issue avec la taille ROB 128, et le SmallCore-2 (SC2) modélise un processeur 2-issue avec 64 entrées ROB. Le LargeCore-2 (LC2) modélise un processeur beaucoup plus grande avec deux fois la taille du ROB de LC1, tandis que SmallCore-1 (SC1) modèles un processeur encore plus petit avec moitié de la taille de ROB et des ressources d'exécution de SC2.

Nous avons utilisé les programmes des suites standards de référence (SPEC2000, spec2006, NAS, minebench, splash2x), et les applications sélectionnées subissent plus de 10 MPKI (misses par kilo-instruction). Chaque application est simulée pour 500 millions d'instructions après l'avance rapide au delà de la phase d'initialisation, 50B (milliards) des instructions pour SPEC2000 et spec2006, 25B pour NAS, 40B et 10B pour radix et sym-rfe. Différents ensembles d'entrées ont

été utilisés pour le profil et pour la simulation, excepté pour deux applications, radix et svm.

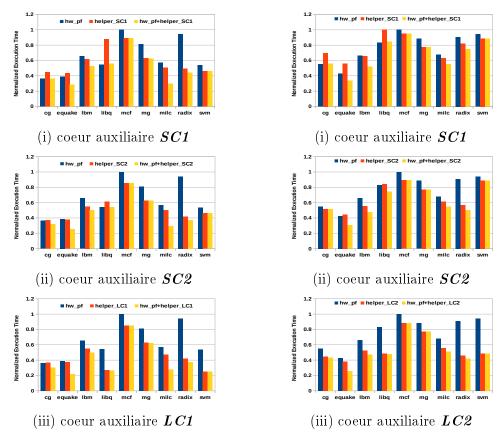

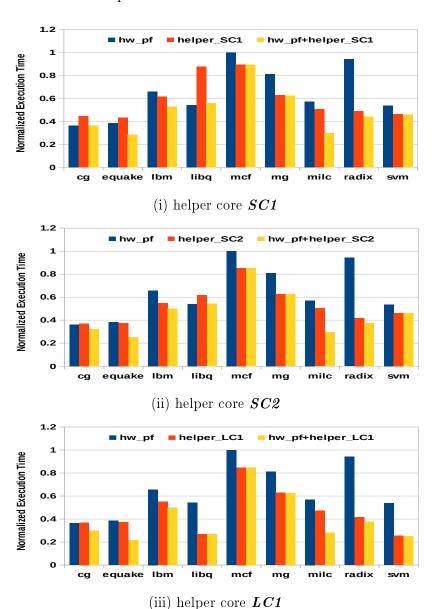

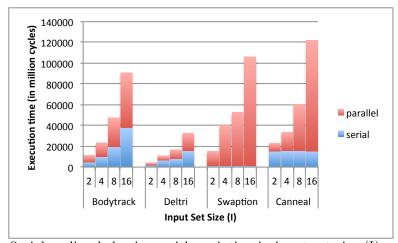

### Performance of Helper Prefetching on Small Cores

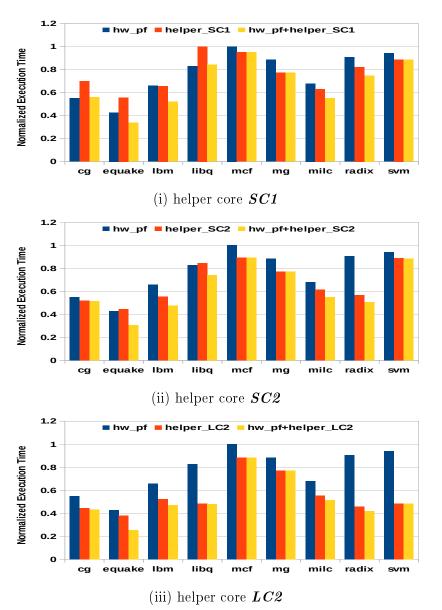

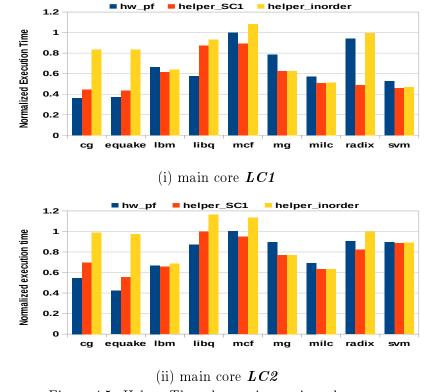

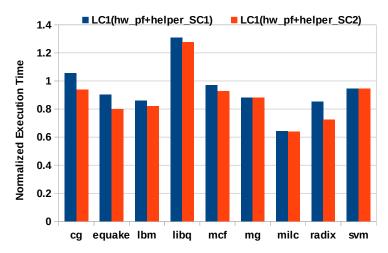

Pour les grands cœurs LC1 et LC2, Figure 2 compare le temps d'exécution (500M instructions) pour la configuration suivante:  $hw\_pf$  - prefetching utilisant un prefetcher matériel pour le cache L1,  $helper\_X$  - prefetching avec l'aide auxiliaire sur un des petits coeurs SC1 ou SC2, ou un grand coeur égale au coeur auxiliaire, et  $hw\_pf+helper\_X$  - combinés prefetching utilisant à la fois prefetcher matériel et un cœur auxiliaire. Temps d'exécution pour chaque configuration est normalisée à la configuration de base sans prefetching auxilliaire et prefetching matériel.

(a) auxiliaires pour le coeur principale LC1 (b) auxiliaires pour le coeur principale LC2Figure 2: Threads auxiliaires dans le système HMC

Prefetching auxiliaire est capable de prefetching pour des applications avec des patterns d'accès séquentiels et irréguliers. Dans l'ensemble, pour la configuration LC1, le prefetching auxiliaire sur de petits coeurs fournit une performance additionnelle moyenne par rapport à hw\_pf seule de 11,3% avec SC1, et 23,2% avec SC2. Pour le plus grand coeur LC2 (plus grande fenêtre d'instruction), nous constatons que le thread auxiliaire sur le petit coeur SC2 surpasse le prefetching matériel seul. Nous voyons aussi un effet synergique pour des patterns d'accès séquentiel où le thread auxiliaire est en avance et charge des lignes de cache dans le cache L3 partagé, et le prefetcher matériel récupère les lignes de cache dans le cache L1 et cache complètement la latence d'accès mémoire.

Nous comparons également l'efficacité de prefetching auxiliaire sur de petits coeurs avec une configuration qui utilise un grand coeur égal pour exécuter des threads auxiliaires. Dans nos benchmarks de référence, à l'exception de deux applications, libquantum et svm, SC2 offre un bon compromis comparé à un grand coeur égal.

#### Autres Contributions

Cette section présente un résumé des autres contributions, comme un deuxième auteur. Les études sont (1) la compréhension de l'impact des prédicteurs de branchement faisant partie de l'état de l'art sur la performance des interpréteurs et (2) une estimation de la performance des programmes multi-threads sur des architectures massivement parallèles.

### Prédiction de branchement et de la performance des Interpreteurs

Malgré la popularité des languages qui sont JIT compilé, tels que Java, les interpreteurs restent largement répandue pour la mise en œuvre des languages de programmation tels que R, Python, Matlab. Les interpreteurs sont beaucoup plus faciles à développer, maintenir, et pour le portage d'applications sur de nouvelles architectures, mais cela se fait au détriment de la performance. Même avec une mise en œuvre efficace de interpreteurs, il y a un ralentissement de 10X dans la vitesse d'exécution par rapport au code natif produit dans un compilateur optimisé.

Le surcoût de la performance des interpreteurs est en raison de l'exécution de la boucle de dispatch qui lit le bytecode, décode, et effectue des mesures appropriées sur la base du bytecode, où la sélection de l'action est généralement mis en œuvre dans une instruction switch. Sur les processeurs haut de gamme, grande issuewidth, avec une exécution out-of-order à haute fréquence, couplé

avec de grands caches de premiers niveaux ont largement atténué la plupart des coûts dans l'exécution des interpreteurs. Mais le saut indirect qui met en oeuvre l'instruction switch reste difficile à prévoir, car il a des centaines de cibles (de un pour chaque niveau opcode bytecode) potentiellement, et la sagesse conventionnelle considère la performance des prédicteurs de branchement sur ce saut indirect comme un obstacle majeur.

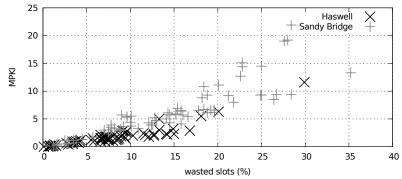

Dans cette étude, nous revisitons les travaux antérieurs sur la prévisibilité des instructions de branchement dans interpreteurs dans trois des derniers processeurs de génération d'Intel, et un état de l'art du prédicteur indirecte ITTAGE, en utilisant des interprètes de python, javascript et cli. Nous trouvons que la précision de prédiction de branchement sur ces interprètes est considérablement améliorée au cours des trois dernières générations de processeurs Intel, et sur le processeur le plus récent appelé Haswell l'exactitude de la prédiction est tel qu'il ne peut plus être considérée comme un obstacle à la performance. Nous constatons également que sur Haswell, la pénalité de mauvaise prédiction ajoute seulement un surcoût limité au temps d'exécution des interpréteurs, en moyenne 7,8% des issues slots sont gaspillées en raison de mauvaises prédictions de branchement. Par conséquent, la sagesse conventionnelle sur le caractère imprévisible des branches indirectes dans la boucle de dispatch, et son impact sur la performance des interpreteurs, est injustifiée

## Modélisation de la performance des programmes multi-thread dans l'ère many-coeurs

Deux modèles précédents, la loi d'Amdahl et Loi de Gustafson, sont largement utilisés pour extrapoler le potentiel de performance d'une application parallèle sur une machine avec un grand nombre de coeurs. La loi d'Amdahl suppose que la taille de l'ensemble des entrées pour une application reste fixe pour une exécution particulière. La loi de Gustafson suppose que la partie relative du calcul parallèle augmente avec la taille des entrées, mais ignore la section séquentielle. Cependant, pour de nombreuses applications, le temps d'exécution de la section séquentielle augmente significativement avec l'augmentation des entrées, mais également un peu avec l'augmentation du nombre de processeurs. Ces modèles de performance ne saisissent pas forcément avec précision la mise à l'échelle de la section séquentielle des applications, et peut donc mener à des estimations optimistes.

Nous construisons un modèle empirique appelé serial scaling model (SSM), pour étudier la mise à l'échelle des applications MT, en fonction de la taille des entrées et du nombre de coeurs. Quand on utilise le modèle SSM, la forme

générale de la durée d'exécution d'une application parallèle peut être représentée comme suit:

$$t(I,P) = c_{seq}I^{as}P^{bs} + c_{par}I^{ap}P^{bp}$$

$$\tag{1}$$

Les six paramètres sont obtenus de manière empirique et représentent le temps d'exécution d'une application parallèle en tenant compte de ses entrées et du nombre de processeurs.  $c_{seq}$ , as and bs sont utilisés pour modéliser le temps d'exécution séquentiel et  $c_{par}$ , ap and bp sont utilisés pour modéliser le temps d'exécution parallèle.  $c_{seq}$  and  $c_{par}$  sont des constantes de la section séquentielle et parallèle qui confèrent à l'amplitude initiale du temps d'exécution. as and ap sont le Input Serial Scaling (ISS) paramètre et le Input Parallel Scaling (IPS) paramètre. bs and bp sont le Processor Serial Scaling paramètre et le Processor Parallel Scaling (PPS) paramètre.

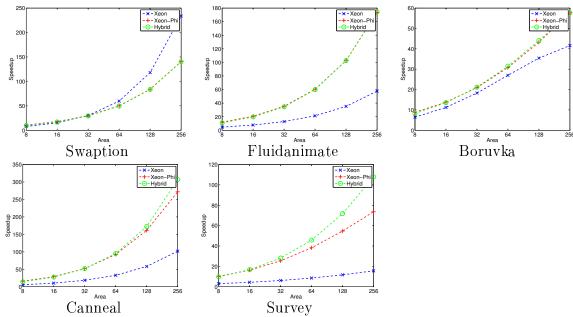

Nous ciblons les programmes qui s'exécutent avec succès sur nos plates-formes matérielles (Xeon (E5645, jusqu'à 24 threads) et le Xeon-Phi (5110P, jusqu'à 240 threads)), et qui ont des entrée qui peuvent être générées avec des facteurs d'échelle connus. Quand on utilise les PMU matériels, l'activité d'une application sur la base du thread est analysée, et le temps passé dans l'exécution de code séquentiel et parallèle i, e.  $t_{seq}(I,P)$  and  $t_{par}(I,P)$  est obtenu en faisant varier le nombre de threads (P), la taille de l'ensemble des entrées (I). Ensuite, l'analyse de régression est réalisée avec la méthode des moindres carrés pour déterminer les six paramètres de SSM qui correspondent le mieux correspondent aux données expérimentales disponibles.

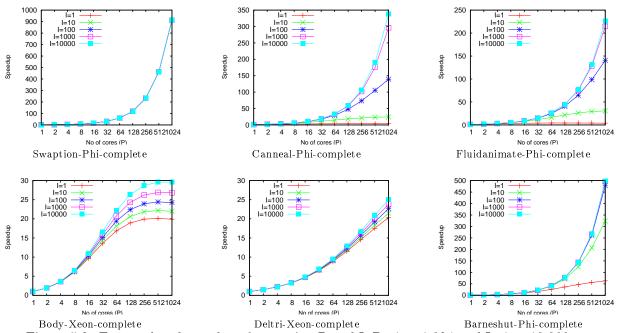

Nous avons étudié les accélérations possibles extrapolées pour quelques applications en faisant varier le nombre de processeurs de 1 à 1024 et en faisant varier la taille du problème de 1 à 10.000. Les applications comme swaptions, barneshut et bodytrack sur Xeon, ont une bonne mise à l'échelle en parallèle, et leur accélération peuvent être encore entre 1024 à 512 pour 1024 coeurs. De nombreuses applications ont une sublinéaire échelle, par exemple canneal, fluidanimate, survey, deltri, sssp et bfs, où l'accélération maximale possible sera comprise entre 512 et 64 avec 1024 coeurs.

Certaines applications, par exemple des swaptions, ont une section séquentielle négligeable et sont hautement évolutives. Certaines applications ont une partie de code séquentiel presque constante et une partie parallèle à croissance rapide pour chaque taille de l'ensemble des entrées, donc de grandes tailles d'entrée fixé sont nécessaires pour amortir la partie sequentielle constante. Dans canneal et fluidanimate (application complète), la section séquentielle est indépendante de

I et P, et la section parallèle passe à l'échelle quasi linéairement avec I et P. L'amélioration significative de l'accélération est obtenue avec une utilisation plus grande de I.

Dans d'autres applications, par exemple deltri, preflow, survey, boruvka, body-track (de applicaiton complète), le code séquentiel passe à l'échelle aussi bien voire un tout petit peu moins bien que le code parallèle. Ces applications ne bénéficient pas forcément des architectures multicoeurs, avec une accélération saturée avec P, malgré l'augmentation de I due à l'impact de la mise à l'échelle du code séquentiel.

### Contributions

Voici les contributions de cette thèse: d'abord, nous développons un cadre matériel / logiciel appelé core-tethering pour permettre l'exécution de threads auxilliaires sur un système HMC (Heterogeneous Many Cores). Le Core-tethering ajoute de nouvelles instructions en mode utilisateur comme interface (jouant le rôle d'une sorte de un co-processeur) pour les cœurs auxilliaires sur les systèmes HMC. Ce cadre permet au cœur principal de pouvoir lancer et contrôler directement l'exécution des threads auxillaires, et de transférer efficacement le contexte des applications nécessaire à l'exécution des threads auxilliaires. Grâce à une association plus étroite entre les coeurs, le core-tethering évite le surcoût de la latence d'accès aux petits coeurs pour l'exécution des threads auxilliaires. Ensuite en utilisant la simulation basée sur des traces d'exécution, nous évaluons la pertinence des petits coeurs à exécuter les threads auxiliaires pour un thread séquentiel fonctionnant sur le coeur principal, qui est plus puissant, que sur un ensemble de programmes ayant une utilisation intensive de la mémoire, nous montrons que les threads auxiliaires fonctionnant sur des cœurs relativement petits permettent une accélération significative des coeurs principaux par rapport au prefetching matériel seul. De plus les petits coeurs permettent un bon compromis par rapport à l'utilisation d'un cœur d'une puissance similaire pour exécuter les threads auxilliaires. Nous montrons également que le prefetching effectué par les threads auxillaires sur les petits cœurs lorsqu'elle est utilisée avec le prefetching matériel, peut fournir une alternative à l'utilisation de cœurs plus grands et puissants pour des applications gourmandes en mémoire.

## Introduction

This thesis work is done in the context of the ERC DAL project [Sez10], which focuses on enhancing single process performance in heterogeneous many-cores (HMC) processor chips that will feature few complex cores and many simple, silicon-area and power effective cores. Specifically, we investigate the use of simple cores in a HMC for executing helper threads to accelerate sequential execution on the complex (main) core.

In the past decade, mainstream server and desktop markets have adopted Chip Multi-Processors (CMP) i.e multi-cores as the predominant architecture template [PDG06]. More recently even the mobile client devices have made the shift to multi-cores. Further as transistor sizes continue to shrink, industry forecasts are promising the integration of hundreds of cores on a single die in the near future.

The move to multi-cores was motivated by the inability to translate additional transistors on chip to performance increases for the single core. Large monolithic processors are difficult to build due to increased hardware complexity and high power requirements [PJS97]. Additionally limitations to exploiting instruction level parallelism (ILP) put a bound on the achievable sequential throughput. Consequently design efforts were redirected towards chip multi processors comprising of identical, complexity effective and power/performance balanced cores to better utilize the available silicon real estate. Single-chip multi-cores provided a high-frequency high-performance processor for inherently sequential applications, and multiple execution engines with improved, low latency interprocessor communication for parallel applications [ONH<sup>+</sup>96]. By utilizing additional transistors on die to improve system performance and throughput, multi-cores served to hide the inability to scale single thread performance.

However, as increasing number of cores are integrated on a single die, application characteristics of emerging workloads are shaping the architecture of next generation many core processors towards increased heterogeneity. Emerging

workloads are expected to contain a mix of sequential and parallel applications, and place varied power/performance demands on the architecture. Simply replicating identical cores does not effectively address the needs of these mixed workloads, and hence Heterogeneous Many Core (HMC) [KFJ+03][SMQP09] designs that mix many simple/small cores with a few complex/large cores are emerging as an architecture template to efficiently execute both parallel and sequential workloads.

Heterogeneity in power/performance profiles and core sizes helps to achieve a workload optimized architecture template. In a HMC, few large cores, typically wide issue superscalar machines, are optimized for execution latency while small cores are optimized for execution parallelism and area/power efficiency. Predominantly sequential workloads requiring high ILP (instruction level parallelism) are mapped to high performance large cores, while the power-efficient and throughput oriented small cores target parallel workloads demanding high TLP (thread level parallelism). In addition, to minimize energy consumption, workloads running on large cores can be migrated down to small cores at run-time based on their resource requirements. Thus HMCs can achieve higher energy efficiency and better support diverse workload characteristics compared to symmetric many-cores.

Despite the widespread prevalence of multi-cores, development of scalable parallel applications has been limited to specific application segments where parallelism is easy to find such as scientific computing, transaction procession, graphics, etc - very few applications in general purpose computing have been successfully parallelized. To be able to fully exploit the many cores available in the HMC architecture, the application has to be amenable to parallelization, i.e decomposition of computation into many threads that can be executed concurrently on different cores. However, in the foreseeable future a majority of applications are still expected to feature significant sequential code sections, either as legacy sequential codes or as difficult to parallelize sections in parallel code and cannot otherwise benefit from increasing the core count. Additionally, even on applications that are parallelized into multiple threads, sequential sections of execution such as critical sections, etc constitute bottlenecks to performance scalability on large number of cores. Consequently, improving sequential performance on HMCs will remain key both for single threaded codes and scalability on parallel codes.

In addition to traditionally strengthening the large core itself, there is a renewed interest in utilizing additional cores to accelerate single thread performance, especially for memory intensive programs. We propose that the many small cores in a HMC be utilized as low-power helper cores to accelerate the

sequential thread running on the large core. Specifically we explore the porting of the helper threading paradigm [DS98][CSK+99] to the HMC architecture template, small cores can be used to run precomputational code and generate prefetch requests on behalf of the main thread. Instead of turning off small cores when sequential(main) threads are mapped to large cores, helper threading allows them to be employed for achieving even higher sequential performance on the main thread.

When using small cores to execute helper threads in a HMC, helper-execution related actions such as thread-spawn and synchronization incur operating system overhead and overheads due to inter-processor communication latencies through the shared caches. In addition, there is a performance disparity between the large and the small cores, and it is not clearly understood if helpers executing on the small cores can provide sufficient lookahead to benefit the main thread running on a much powerful large core. In this thesis, we focus on efficient helper threading on small/simple cores in a HMC processor to improve sequential performance on memory intensive programs running on the large core in a HMC. We propose a hardware/software framework for helper threading that reduces overheads for spawning and controlling helper threads, and thus enables efficient execution of helpers in the HMC. Using trace based simulation and programs from standard benchmark suites, we also study the suitability of using small cores in the HMC for executing helper threads to accelerate the application thread running on a much larger, powerful main core.

### Contributions

The following are the contributions of this thesis: First, we develop a hard-ware/software framework called core-tethering to support efficient helper threading on heterogeneous many-cores. Core-tethering adds new user mode instructions that provide a co-processor like interface to the helper cores in a HMC, allowing a large core to directly initiate and control helper execution, and to efficiently transfer application context needed for execution to the helper core. Through tighter coupling of cores, core-tethering overcomes the latency overheads of accessing the small cores for helper execution. Next, using trace based simulation we evaluate the suitability of small cores to execute helper threads that can prefetch for a sequential thread running on the larger main core. On a set of memory intensive programs from the standard benchmark suites, we show that

helper threads running on a moderately sized small cores can significantly accelerate much larger main cores compared to using a hardware prefetcher alone, and that small cores provide a good trade-off against using an equivalent large core to execute the helper. We also find that helper prefetching on small cores when used together with hardware prefetching, can provide an alternative to growing the core size for achieving higher performance on memory intensive applications.

## Organization of the thesis

This thesis is organized as follows: Chapter 1 provides background information related to Heterogeneous Many Cores architectures, and Helper threading techniques. Chapter 2 presents a survey of prior work on using additional cores for improving sequential performance, and various hardware techniques for closer coupling between cores in loosely coupled systems. Chapter 3 presents a description of core-tethering, the hardware/software framework we propose to support efficient helper threading on heterogeneous many cores. Chapter 4 presents our trace based methodology for simulating helper threading on HMCs and an evaluation of the suitability of small cores to execute helper threads in a HMC. Material from Chapter 3 and Chapter 4 were presented at SBAC-PAD 2014 [SKS14]. Lastly Chapter 5 presents a summary of other contributions, as a second author, to studies in (1) understanding impact of state of the art branch predictors on performance of interpreters and (2) performance estimation of multi-threaded programs on massively parallel many-cores architectures. Material from Chapter 5 are from publications in CGO 2015 [RSS15](to appear) and WAMCA 2014 workshop [NSS14] respectively.

## Chapter 1

## Background

As the number of cores on die increases with the scaling of silicon process technology, the strategy of replicating identical cores does not scale to meet the performance needs of emerging workloads that are a mix of sequential and parallel applications. Heterogeneous Many Cores (HMC) [KFJ<sup>+</sup>03][SMQP09] that mix many simple cores with a few complex cores are emerging as a design alternative that can provide both fast sequential performance for single threaded workloads, and power-efficient execution for parallel workloads. However, on applications that are sequential or contain predominantly sequential sections of code, especially those that are memory bound, increasing core count does not translate into performance. Consequently, there is a renewed interest in techniques such as speculative multithreading and helper threading that can exploit additional cores to deliver performance for sequential code sections.

In this chapter we provide background information related to Heterogeneous Many Cores architectures, and Helper threading techniques. We also discuss issues involved in applying the helper threading technique and the various overheads when helper threading is implemented on loosely coupled systems such as the HMC.

### 1.1 Heterogeneous Many Cores

With the emergence of multi-core architectures, architects have integrated increasing number of cores on-chip. Depending on the target application workloads, and based on whether single thread performance or workload throughput is to be maximized, two typical approaches to grow core count on-chip can be identified.

### 1. Large Core CMP.

In the large core CMP design template approach, architects replicate a small-medium (2-16) number of large cores. Designs of commercial general purpose CMPs such as Opteron [BBSG11] from AMD, Xeon [RTM+10] from Intel, and POWER [SKS+11] from IBM are typical examples of this design template. This design point is targeted at maximizing single thread performance and is best suited to handling a mix of single threaded workloads, or applications with small levels of thread level parallelism, and has been predominantly adopted in the desktop (and laptop) and the mainstream server markets. With SMT support, each core is able to support multiple threads (typically 2 or 4) and consequently designs can be scaled to support applications with moderate levels of thread level parallelism.

#### 2. Small Core CMP.

In the small core CMP design template approach, architects integrate a large (32-64+) number of small cores on-chip. Designs of commerical microprocessors such as TILEPro [TIL] from Tilera, Niagara [KAO05] from SUN microsystems, Xeon-Phi [CE12] from Intel, and GPGPU compute capable graphics processors [MH11][LNOM08] from AMD and NVIDIA are typical examples of this design template. This design point is clearly targeted at applications that have large levels of thread level parallelism and can be easily decomposed into many threads, but is low on single thread performance. This approach has found acceptance in general purpose but specialized throughput oriented application domains such as high performance scientific computing, graphics, and networking tasks that involve packet processing such as intrusion detection, deep packet inspection.

In the third emerging design template called the Heterogeneous Many Core (HMC) [KFJ<sup>+</sup>03][SMQP09], architects make a balanced trade-off between corecount and raw single thread performance. Instead of replicating homogeneous, either only large or only small cores, a few large cores are integrated with many small cores.

Heterogeneity in core size and performance capability allows to achieve areaperformance goals for diverse workloads under fixed power-dissipation constraints. The large cores are complex superscalar processors, and feature high-end microarchitecture design elements such as a deep, high frequency pipeline, large issue width, out of order execution, several functional units, and aggressive and powerful prefetchers, data-dependence and branch prediction. The small cores are simple processors, featuring shallow pipelines and less-aggressive implementations of branch predictors, etc. The large cores target sequential code sections demanding high ILP (instruction level parallelism) and are designed to support fast execution on single threaded applications and performance limiting sequential sections in parallel applications. The small cores target parallel code sections demanding high TLP (thread level parallelism) and are designed to support energy efficient execution for parallel workloads.

HMC is a shared memory architecture template, the cores share memory and private caches are maintained cache coherent using a hardware coherence protocol. Cache hierarchy in a HMC consists of multiple levels of private and shared caches. Each small and large cores have their own private L1 and L2 caches, and share a large last level (L3) cache. The cores share an interconnect fabric for low latency high bandwidth inter-core communication.

In the design of HMC architectures, two templates can be observed in how the large cores and the small cores are differentiated, both in terms of microarchitecture and specialization, to target application needs.

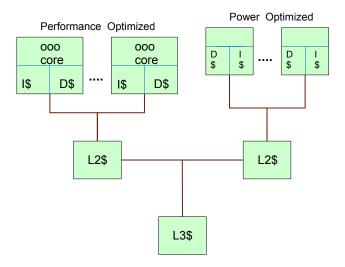

1. Performance Optimized and Power Optimized cores.

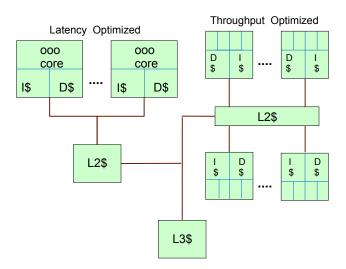

Figure 1.1: HMC Architecture Template - Performance/Power optimized

In this architecture template, cores are differently optimized on the axis of power efficiency. Large performance optimized cores, typically high performance and complex out of order superscalar cores are combined with small power optimized cores, typically in-order or simpler out of order processors. Figure 1.1 shows a schematic illustration of the HMC design template where cores are optimized to trade-off power-performance. In processors that target energy efficiency such as ARM [ARM] and Variable SMP from Nvidia [Nvic], the workload is dynamically migrated between energy efficient (low performance) processors and high performance processors based on the performance needs. Alternately, low power cores can be used to offload and execute parallel code sections of the application in a power efficient manner. For example, the Cell Broadband Engine Architecture microprocessor [CRDI07] from the STI (Sony, Toshiba, IBM) alliance, was cost-effective in executing computationally demanding tasks from a wide range of applications, particularly video processing and graphics rendering for consumer appliances like game consoles.

2. Latency Optimized and Throughput Optimized cores.

Figure 1.2: HMC Architecture Template - Latency/Throughput optimized

In this architecture template, cores are differently optimized to target either providing the fastest execution latency or better execution throughput. Figure 1.2 shows a schematic illustration of the HMC design template where

cores are optimized along the compute latency-throughput axis. Throughput oriented simple cores that can sustain a large number of application threads are integrated with complex latency oriented cores that provide fast execution by employing high frequency, deeply pipelined and out of order execution cores. Applications that expose parallelism are run on the small cores and can benefit from the enormous raw compute capability of these throughput optimized cores. Commercial microprocessors such as the Fusion Accelerated Processing Unit from AMD [FSB+11], Nvidia TegraK1 processor [Nvia] and Integrated CPU/GPU processors from Intel are widely used to offload tasks in domains such as scientific computing, graphics, media and image processing to the small cores. For example, the recently introduced TegraK1 processor offloads computationally intensive computer vision tasks in the automotive domain to the smaller cores of the Kepler based GPU [Nvib].

An orthogonal dimension of heterogeneity in cores is the diversity offered by different ISAs, where processors that execute completely different instruction sets are integrated on the same die. From this perspective, integrated CPU-GPU processors from AMD, Intel and NVIDIA could be considered as having separate ISAs for the large cores based (x86/ARM), and a custom ISA for the small GPU cores. Recently heterogeneous-ISA processors that exploit multiple different ISAs have been shown to be better than same-ISA heterogeneous (micro-architecture based) architectures in both performance and energy savings [VT14]. In this thesis, the target baseline architecture is a single-ISA heterogeneous many cores and is similar to the ARM big.LITTLE template. The focus of our study is the efficient execution of pre-computation based helper threads on small cores to improve sequential performance of memory intensive programs mapped to the large cores.

### 1.1.1 Improving Sequential Performance on Many Cores

HMC architecture targets the needs of a diverse workload that is a mix of serial and parallel applications. Large cores are optimized for execution latency, while simple cores are optimized for execution parallelism and area/power efficiency. When executing a workload with low thread level parallelism, threads are mapped to large cores and benefit from fast sequential execution on the complex microarchitecture. When executing parallel workloads, threads are mapped to the numerous simple cores and realize performance by exploiting the high thread

level parallelism available in the architecture. Additionally when the compute demands are low, threads can be migrated from the large core to energy efficient small cores to achieve greater execution efficiency.

To be able to effectively utilize the many cores in the HMC architecture for performance gains, an application has to be amenable to parallelization, ie decomposition of computation into multiple threads that can be executed concurrently. However, many applications are still expected to feature significant sequential code sections, either due to prevalence of legacy sequential code or due to difficulty in fully parallelizing applications, and therefore improving sequential performance will remain critical to realizing the full performance potential of the HMC architecture template. Here we categorize previous studies in the literature that focus on improving sequential performance in many core architectures.

- 1. Growing core complexity to increase single thread performance.

- Traditionally with every new generation of process technology shrink, architects have relied on increasing core clock frequency, and the use of additional transistors for improved core-IPC, to increase single thread performance. However, clock frequency increases have plateaued because of power dissipation concerns, and increasing IPC remains as the lever to realize higher single thread performance. To improve core-IPC, in addition to widening the execution pipe by increasing the instruction issue width [STR02], recent works have focused on bettering the execution efficiency of the pipeline. By improving branch prediction mechanisms [JL01] [Sez11], and by designing more effective data prefetchers [KKS<sup>+</sup>14] these techniques reduce the amount of cycles wasted in execution when branches mispredict or when memory accesses miss in on-chip caches thereby reducing the average number of cycles required to process an instruction. Further, with the availability of a large number of transistors, architects have proposed specializing few cores in a HMC specifically for the high performance execution of sequential code sections [MSS10].

- 2. Dynamically Merging Simple Cores to improve single thread performance. Many core architecture templates that are designed to target parallel workloads use simple multi-threaded cores in order to achieve maximum execution throughput for a given silicon area size. However, for applications that are only weakly parallelized and hence still feature significant sequential execution phases, performance improvement is more likely achieved by using fewer, but more capable complex cores. In order to improve sequen-

tial performance on throughput oriented many core architectures, architects have proposed techniques that combine two or more simple cores dynamically at runtime to function as a high performance out-of-order core. In [TBS08] Tarjan et al. propose Federation cores, a technique for creating a 2 way out of order superscalar processor by combining two neighboring multithreaded inorder cores. The large register file of the multithreaded core is repurposed to implement out of order structures, also other associative structures are reworked into simpler to implement lookup tables. Core fusion [IKKM07] proposes a reconfigurable CMP architecture that dynamically morphs groups of independent 2 issue out of order cores (upto 4 adjacent cores and their I and D caches) into a more complex and capable larger CPU.

### 3. Utilizing additional cores for single thread performance.

In a many core architecture, when executing sequential code sections, only one core is active while the remaining cores remain idle. Instead of remaining idle, additional cores can be used to accelerate the sequential execution on the active core. Previous works that exploit additional cores for improving single thread performance can be broadly categorized as either thread level speculation or helper threading.

### (a) Thread level speculation

Thread level speculation (TLS) [SCZM05] or speculative multithreading [KT99] aims to exploit parallelism that exists in sequential code sections at a granularity that is much larger than a typical hardware instruction window (of the order of 128 - 256 instructions). In traditional out of order execution processors, the micro data flow engine tracks independent instructions dynamically within a hardware instruction window and initiates parallel execution of multiple independent instructions every cycle. The execution engine uses branch prediction and data dependence prediction to speculate that instructions are independent, dynamically tracks instruction execution for dependence violation and re-executes instructions violating dependence relation to respect sequential semantic of instruction execution. TLS mechanisms similarly exploit speculative parallelism that exist at much larger granularity - such as loop iteration level [WDY+06] or function level [CO98] granularity.

A compiler or profiler marks code sections that can be speculatively executed in parallel, such as multiple iterations of a loop nest, or over-

lapping code following a function call with the execution of the call. At run time, speculative threads are spawned to execute in parallel with the main application thread, and sequential semantic is enforced by hardware i.e. execution is monitored for violation of dependence relations in which case threads are re-executed to respect dependences. Thus additional cores are utilized to execute speculative threads extracted from a sequential code section, and can result in significant speed ups when dependences between threads can be correctly predicated.

#### (b) Helper threading

Helper threading uses a specially constructed speculative thread that executes on an otherwise idle core, in parallel with the main thread without modifying its semantic. The aim of helper thread execution is to accelerate the execution of the main thread by providing performance hints such as direction-prediction for hard to predict branches or by prefetching cache lines that will be referenced by the main thread. The instructions executed by the helper thread themselves do not carry out any of the computation for the main thread, but only provide performance hints. This is in contrast with speculative multithreading where the work done by the additional (speculative) threads are committed to the execution state of the main thread when speculation is validated to be correct. Helper threading is discussed in more detail in Section 1.2.

We study the porting of the helper threading paradigm to the Heterogeneous Many Cores architecture template, i.e the use of small cores as helper cores to benefit sequential applications mapped to the large core. We are interested in improving sequential performance of memory intensive applications that frequently miss in the on-chip cache and spend a large portion of the execution cycles waiting for the memory. While computer architects use prefetching techniques to anticipate future memory access requests, prefetching accurately and sufficiently in advance for applications with complex memory access patterns still remains a challenge. Alternately, helper threading uses small cores to execute backward program slices targeting specific loads/stores to pre-compute memory addresses and generate prefetch requests.

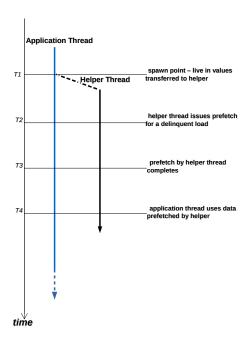

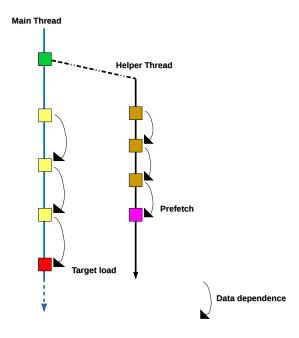

### 1.2 Helper Threads

Helper threading can be considered as a prefetching technique where a specially created pre-compute thread runs ahead of the main thread and initiates future memory accesses for the main thread ahead of time. Figure 1.3a illustrates the working of helper threading based prefetching. The main thread triggers execution of the helper thread by delivering the live in variable needed to initiate helper execution (T1). Once initiated, the helper thread runs concurrently with the main thread, executes precomputation code to prefetch addresses that a targeted load (in the main thread) will request in future(T2,T3). When future memory accesses are initiated sufficiently ahead of time, main thread benefits from the latency hiding effects of a prefetch, ie a demand access by the main thread thread finds the prefetched data in the on-chip cache and avoids the memory access penalty(T4). As illustrated, in figure 1.3b helper executes only the code that is necessary to generate prefetches (back-slice) for the targeted loads/stores.

Memory accesses targeted for prefetching by helper threads are typically difficult to prefetch using traditional prefetchers. Such memory accesses may have unpredictable access patterns or a chain of dependent loads (such as pointer-chasing accesses) and are hence difficult to track by hardware prefetchers. Alternately, they may have complex access patterns that require significant computation to generate future memory accesses and hence incur large overheads when targeted by software prefetching. In a helper thread based prefetch mechanism, the overheads of generating computation are hived off to the precompute code in the helper without incurring performance overheads in the main thread.

# 1.2.1 Issues in applying helper threading to accelerate a sequential thread

1. Identifying target instructions and Generation of helper thread

In order to keep the helper thread running ahead of the main thread, it is

necessary that the helper only execute a limited subset of the instructions

executed by the main thread. Therefore, only a small set of static loads/stores in the main thread that frequently miss in the on-chip cache and

cause most of the cache related stalls - the delinquent loads/stores - are

targeted for helper prefetching. Next, starting from the target load/store,

a back-slice of instructions that participate in target address generation is

### (a) Timeline for Helper Thread Operation

(b) Slicing to construct helper threads

Figure 1.3: Prefetching for an application thread using helper thread

identified. This back-slice along with the instructions required to maintain correct control flow from the pre-computation code in the helper thread. Additionally, loads that are not used later in the helper thread, either to generate address or to maintain control flow, are converted into software prefetches.

Target identification and helper generation techniques can be broadly classified into

### (a) static/offline techniques

Helper threads can be generated statically using offline profile information to guide delinquent selection and precompute slice construction. Here a profile run of the target application collects information on the loads and stores that cause the most cache misses, which is then used by a static analysis phase which performs back-slice construction starting at these target instructions. In [BWC<sup>+</sup>02] Brown et al. used static analysis of program source code in a compiler to generate pre-compute code for the helper. Alternately, in [LWW<sup>+</sup>02] Liao et al. used static analysis directly on the binary to identify the back slice.

### (b) dynamic/runtime techniques.

At runtime, delinquent loads can be identified and helper can be constructed dynamically either using special hardware support or as part of a software dynamic optimization system. In [CTWS01] Collins et al. use a hardware structure known as the Delinquent Load Identification Table to identify delinquent loads, and a Retired Instruction Buffer (RIB) that stores a trace of committed instructions to construct the back-slice. In [LDH+05] Lu et al. implement helper threading within a software dynamic optimization system on an unmodified CMP. Profiling and delinquent load identification are implemented within runtime performance monitoring code, and slice construction and helper generation as part of the JIT compiler.

Helper threading based on statically contructed pre-compute slices are easily adopted with existing hardware architectures, and have found support from microprocessor manufacturers [PSG<sup>+</sup>09][WWW<sup>+</sup>02].

### 2. Maintaining the semantic of the main thread

Helper threads are speculative in nature, they must respect the semantics of sequential execution of the main thread and cannot change its program execution state. To implement helper threading, the processor has to support

a speculative pre-execution model where the results computed in the helper threads are never integrated into the main thread, and any exceptions signaled in the pre-execution context of the helper thread never disrupt the execution of the main thread. In addition, helper threads are not allowed to write to memory locations since a write to memory can potentially change the architectural state of the main thread. Instead store instructions targeted in the helper thread are either converted to prefetches, or localized to a separate memory location within the helper thread.

### 3. Maintaining efficiency of prefetching.

For effective prefetching, the helper threads ideally runs only as far ahead as is adequate to prefetch in time for the main thread. When the helper thread lags behind the main thread, the prefetches it generates are ineffective. When the helper threads runs too far ahead of the main thread, it risks polluting the cache by evicting useful lines that are still needed by the main thread. Therefore during execution, the helper thread synchronizes periodically with the main thread to ensure it is sufficiently ahead of the main thread to be able to launch in time prefetch requests, called the look ahead distance. To implement synchronization, typically for a helper thread targeting a loop region, the main and the helper threads both maintain a counter to track the iteration count they are currently executing. Periodically, the helper thread reads the counter of the main thread and compares it with its own counter. When the helper is too far ahead of the main thread, ie its advance over the main thread is greater than the desired look ahead distance, the helper pauses execution of the precomputation slice and generation of prefetch requests until the main thread makes sufficient progress. When the helper lags the main thread, it resynchronizes its execution state with the main thread, copies over updated values for its live-in variables and restarts execution.

# 1.2.2 Overheads of helper threading on loosely coupled systems

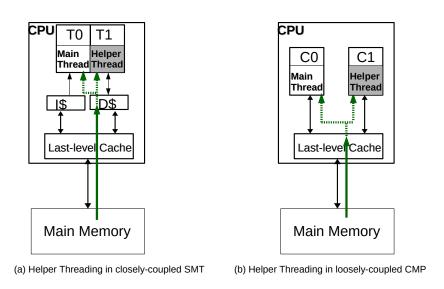

Helper threading was originally proposed as a technique that could utilize unused thread contexts in a SMT machine to speedup serial execution. In a SMT processor, the threads are tightly coupled and share the first level cache, and also execution resources such as functional unit, register file, issue queues, etc. Since the register file is shared, register values from the main thread can be easily

passed to the helper thread as live in variables by using a register to register copy. Fast synchronization is possible since the two threads can communicate through the shared L1 cache. Additionally, the helper thread can prefetch directly into the shared L1 data cache, and a successful hit in the main thread can completely avoid the memory access latency. The main thread and the helper thread are located together on the same core, lesser overheads are incurred during helper initiation and synchronization. However since the main thread shares execution resources with the helper, contention for shared resources can slow down the execution of the main thread. Careful design of the helper is needed to minimize resource requirements. Figure 1.4(a) illustrates helper threading in a tightly coupled SMT machine.

Figure 1.4: Prefetching for SMT and CMP machines

In a loosely coupled system such as the CMP or the HMC, helper threading techniques are extended to harness the unused core for helper execution. Helper threads now get an execution context that does not contend for resources and slow down the main thread. However, helper thread and the main thread are not located on the same core, and hence can only share a lower level in the cache hierarchy. This implies a greater penalty for intra-thread communication and

higher overheads for thread spawn and thread synchronization. Figure 1.4(b) illustrates helper threading in a loosely coupled machine.

On a loosely coupled architecture such as the HMC architecture, significant operating system overhead is incurred in spawning the helper thread. Unlike in a tightly coupled architecture where values can be communicated through a register to register copy with the core, in a loosely coupled machine the main thread has to copy over values that are live-in variables for helper execution. This incurs a significant additional communication overhead during thread initialization.

Communication between the helper thread and the main thread is limited to the shared lower level of cache and incurs large latency penalties. When the helper thread and the main thread synchronize periodically to control helper look ahead for prefetch effectiveness, the value of the progress counter in the main thread is communicated to the helper thread. In addition, live-in values have to be communicated again from the main thread if the helper requires reinitialization to catch up with the main thread. Lastly, the cache lines prefetched by the helper thread reside in a shared lower level cache, and the main thread incurs an additional latency to access the shared cache even when the prefetch is successful.

# Chapter 2

## State of the art

In this thesis, we are studying the porting of helper threading to the emerging HMC template. In the previous chapter, we presented background information related to heterogeneous many cores and the helper threading technique. This chapter presents a survey of the prior work on using multi-cores for improving sequential performance, with a focus mostly on implementations of helper threading. We present a categorization of previous literature based on how the additional cores are utilized, and summarize select relevant papers. The second section highlights specific use cases where a small core is used as helper to a larger core. The third section presents a summary of recent work in hardware support for tighter coupling of cores.

# 2.1 Exploiting additional cores for sequential performance

Before the shift towards multi-cores, utra-wide issue, high frequency processors with large instruction windows were pursued as the design direction to dramatically increase sequential throughput [PPE+97]. In the multi-core era, wide issue processors have not materialized due to design complexity issues [BG04][PJS97], and single core frequencies have largely decreased to accommodate additional cores on chip at the same thermal design points. Instead, increases in sequential performance have been driven by traditional optimizations for IPC. ISA extensions such as SSE/AVX from Intel and NEON from ARM have improved performance on floating point intensive multimedia, scientific, and sig-

nal processing applications. Further, improvements from large on-die caches and increased on die-integration have driven down memory and I/O latency and enhanced performance [CH07].

As an alternative to a monolithic complex core approach to boost single thread performance, research efforts have explored mechanisms to exploit additional on chip resources of a multi-core, both compute (cores/threads) and cache capacity, to improve sequential performance. In this section, we categorize these previous research efforts based on the way in which additional resources are employed to augment the performance of the main sequential thread and present a summary of select relevant papers.

# 2.1.1 Using additional cores to run pre-computation based helper threads

In this approach, traditional slicing based helper threading techniques for SMT processors [CSK+99] are extended to work in a CMP (chip multi-processor) framework. Typically in a CMP processor, when a sequential thread executes on one of the cores, the other cores remain idle and are clock gated to conserve power. In order to boost sequential performance of the main core, the idle cores are utilized to construct and execute helper threads. Unlike in a SMT execution, resources and pipeline stages are not shared between the main thread and the helper thread and hence helper threads can be spawned and executed without concerns of slowing down the main thread.

#### Summary of relevant papers

In [BWC<sup>+</sup>02] Brown et al. first proposed that speculative precomputation can be applied to loosely coupled CMP architectures by using one core to run the main thread and the other cores to execute precomputation code and generate prefetches for the main core. It was demonstrated that despite sharing only the last level L3 cache, speculative precomputation can provide non trivial speedups on memory intensive single threaded workloads. Inter-core resource independence, ie lack of shared resources closer to the core was identified as a major obstacle to fully realize the benefits of helper generated prefetches, and two improvements were proposed to improve performance effectiveness of speculative precomputation on CMPs by reducing the access latency to prefetched cache lines (1) Cache Return Broadcast, when the shared L3 cache services one core's L2 miss, the cache fill is broadcast to all active cores (2) Peer-core L2 Cross-feeding, when one core sees a L2 miss and submits a L3 request, other ac-

tive peer cores snoop on the L3 request and respond with the cache line if it is found in their private L2.

In [LDH+05] Lu et al. present a dynamic optimization system for helper thread based prefetching on CMP systems. A light weight dynamic optimizer runs on the additional core and monitors program performance to identify code regions that have poor memory behavior for optimization using helper threads. The optimizer also identifies delinquent loads and stores within the target region, generates the helper thread and inserts calls to the spawn the helper thread. The execution of the helper threads are interleaved with the dynamic optimization system, thus the helper thread run on an independent processor (different from the main thread) to issue prefetches that bring in data into the shared L2. A software mail box mapped to shared memory is used to communicate values between the main thread and the helper, both during initiation of the helper thread and during the periodic synchronization between the threads. To ensure that the helper thread executes along the same path as the main thread, an asynchronous protocol that avoids cross checking progress of threads is used. After a certain number of iterations (synchronization interval), the helper thread terminates and yields to the dynamic optimization system while the main thread passes updated values of live-in variables and continues execution in the next synchronization interval. This allows the helper to finish within a certain time limit so that tasks in the dynamic optimizer such as phase detection, etc are performed in a timely manner and also ensures that the main thread never waits on the helper for synchronization. When the helper thread is restarted, it compares its progress with the main thread, synchronizes with the main thread if needed and continues execution of precomputation code.

In [SKT05] Song et al. present a compiler framework to automatically construct helper threads for CMPs. Their helper thread methodology works without special hardware support and targeted loops in the program, including techniques to select candidate loops, and to decide which candidate loops are profitable for helper prefetching. They employed a fork-join model based auto-parallelization infrastructure to manage dispatching of helper threads. For synchronization between the threads, communication of live in variables to the helper thread is handled by the parallelization runtime and is allocated in a shared memory region. Compiler generated code inserts checks to verify if the the helper thread is running behind the main thread and terminates execution of the helper thread when the helper trails the main thread in execution. Prefetches issued by the helper thread bring in data to the shared L2 cache, and experimental results showed that their

production compiler working on an unmodified dual-core SPARC microprocessor improved performance on codes suffering large L2 cache miss penalties by upto 22%.