# Software Abstractions for Parallel Architectures Joel Falcou

# ▶ To cite this version:

Joel Falcou. Software Abstractions for Parallel Architectures. Distributed, Parallel, and Cluster Computing [cs.DC]. Universite de Paris 11, 2014. tel-01111708

# HAL Id: tel-01111708 https://inria.hal.science/tel-01111708v1

Submitted on 30 Jan 2015  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. Université Paris Sud Spécialité : INFORMATIQUE

présentée par

# Joel Falcou

pour obtenir:

L'HABILITATION À DIRIGER DES RECHERCHES DE L'UNIVERSITÉ PARIS SUD

Sujet de la thèse:

# Abstractions Logicielles pour Architectures Parallèles Software Abstractions for Parallel Architectures

soutenu le 1er Decembre, 2014

Jury :

| Rapporteurs : | Cole Murray      | Professeur | Université d'Edimburgh       |

|---------------|------------------|------------|------------------------------|

|               | HAINS Gaetan     | Professeur | Université Paris-Est Creteil |

|               | HILL David       | Professeur | Université Blaise Pascal     |

| Examinateurs: | Conchon Sylvain  | Professeur | Université Paris 11          |

|               | McColl Bill      | Professeur | Université de Oxford         |

|               |                  |            | HUAWEI Research Center       |

|               | Etiemble Daniel  | Professeur | Université Paris 11          |

|               | LAMOTTE Jean-Luc | Professeur | Université Paris 6           |

|               | VIALLE Stephane  | Professeur | SUPELEC Metz                 |

|               |                  |            |                              |

Thèse préparée à l'Université Paris-Sud au sein du Laboratoire de Recherche en Informatique (LRI), UMR 8623 CNRS et de l'équipe POSTAL, INRIA Saclay Île-de-France

# Contents

| 1        | Intr | roduction                                | 3 |

|----------|------|------------------------------------------|---|

|          | 1.1  | From Experiments to Simulations          | 3 |

|          | 1.2  | The Free Lunch is Definitively Over      | 4 |

|          | 1.3  | Challenges Addressed in this Document    | 5 |

|          | 1.4  | Habilitation Thesis Overview             | 6 |

| <b>2</b> | Abs  | stractions for Parallel Programming      | 7 |

|          | 2.1  | Motivation                               | 7 |

|          | 2.2  | Performance Centric Abstraction          | 8 |

|          |      | 2.2.1 P-RAM Models                       | 8 |

|          |      | 2.2.2 LOG-P Models                       | 9 |

|          |      | 2.2.3 BSP Models                         | 0 |

|          | 2.3  | Memory Centric Abstraction               | 1 |

|          |      | 2.3.1 HTA                                | 1 |

|          |      | 2.3.2 PGAS Languages                     | 2 |

|          | 2.4  | Pattern Centric Abstraction              | 3 |

|          |      | 2.4.1 Parallel Skeletons                 | 3 |

|          |      | 2.4.2 Futures and Promises               | 6 |

|          | 2.5  | Conclusion                               | 8 |

| 3        | Mo   | dern C++ Design Techniques               | 9 |

|          | 3.1  | Objectives                               | 9 |

|          | 3.2  | Generic Programming                      | 9 |

|          | 3.3  | Active libraries                         | 2 |

|          |      | 3.3.1 Domain Specific Embedded Languages | 3 |

|          |      | 3.3.2 Template Meta-Programming          | 3 |

|          |      | 3.3.3 BOOST.PROTO 2                      | 4 |

|          | 3.4  | Other code generation systems            | 9 |

|          |      | 3.4.1 Delite                             | 9 |

|          |      | 3.4.2 DESOLA                             | 9 |

|          |      | 3.4.3 TOM 2                              | 9 |

|          | 3.5  | Conclusion                               | 0 |

| 4        | The  | BSP++ Library 3                          | 1 |

|          | 4.1  | The BSP++ Library 3                      | 2 |

|          |      | 4.1.1 Objectives                         | 2 |

|          |      | 4.1.2 BSP++ API                          | 2 |

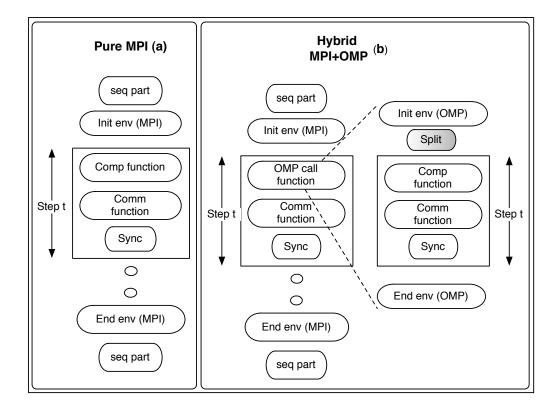

|          |      | 4.1.3 Support for hybrid programming     | 4 |

|          | 4.2  | Benchmarks                               | 5 |

|          |      | 4.2.1 Approximated Model Checking        |   |

|    |                                       | 4.2.2 DNA Sequence Alignment                                                                                                                                                                     | 39              |  |  |  |

|----|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

|    | 4.3                                   | Conclusion                                                                                                                                                                                       | 44              |  |  |  |

| 5  | 5 Toward Architecture-Aware Libraries |                                                                                                                                                                                                  |                 |  |  |  |

| 0  | 5.1                                   | Generative programming                                                                                                                                                                           | <b>47</b><br>47 |  |  |  |

|    | $5.1 \\ 5.2$                          | From <i>DSEL</i> s to Architecture Aware <i>DSEL</i>                                                                                                                                             | 49              |  |  |  |

|    | 5.2<br>5.3                            | AA-DEMRAL and Parallel Programming Abstractions                                                                                                                                                  | $\frac{49}{50}$ |  |  |  |

|    | 5.3                                   | Conclusion                                                                                                                                                                                       | 50<br>53        |  |  |  |

|    | 0.4                                   |                                                                                                                                                                                                  | 00              |  |  |  |

| 6  | 6 BOOST.SIMD                          |                                                                                                                                                                                                  |                 |  |  |  |

|    | 6.1                                   | Motivation                                                                                                                                                                                       | 56              |  |  |  |

|    | 6.2                                   | Basic Abstractions                                                                                                                                                                               | 59              |  |  |  |

|    |                                       | 6.2.1 SIMD register abstraction                                                                                                                                                                  | 59              |  |  |  |

|    |                                       | 6.2.2 Range and Tuple interface                                                                                                                                                                  | 62              |  |  |  |

|    |                                       | 6.2.3 C++ Standard integration                                                                                                                                                                   | 64              |  |  |  |

|    | 6.3                                   | SIMD Specific Abstractions                                                                                                                                                                       | 64              |  |  |  |

|    |                                       | 6.3.1 Predicates abstraction                                                                                                                                                                     | 64              |  |  |  |

|    |                                       | 6.3.2 Shuffling operations                                                                                                                                                                       | 65              |  |  |  |

|    | 6.4                                   | Benchmark                                                                                                                                                                                        | 66              |  |  |  |

|    | 6.5                                   | Conclusion                                                                                                                                                                                       | 68              |  |  |  |

| 7  | The                                   | e Numerical Template Toolbox                                                                                                                                                                     | 69              |  |  |  |

| •  | 7.1                                   | Motivation                                                                                                                                                                                       | 70              |  |  |  |

|    | 7.2                                   | The NT2 Programming Interface                                                                                                                                                                    | 70              |  |  |  |

|    | 1.2                                   | 7.2.1         Basic API                                                                                                                                                                          | 70<br>71        |  |  |  |

|    |                                       | 7.2.2 Indexing and data reshaping                                                                                                                                                                | 71              |  |  |  |

|    |                                       | 7.2.3       Linear Algebra support                                                                                                                                                               | 72              |  |  |  |

|    |                                       | 7.2.4 Compile-time Expression Optimization                                                                                                                                                       | 72              |  |  |  |

|    | 7.3                                   | Implementation                                                                                                                                                                                   | 73              |  |  |  |

|    | 1.5                                   | 7.3.1 Parallel code generation                                                                                                                                                                   | 73              |  |  |  |

|    |                                       | 7.3.2 Support for Asynchronous Skeletons                                                                                                                                                         | 73<br>74        |  |  |  |

|    |                                       | 7.3.2 Support for Asynchronous Skeletons $\dots \dots \dots \dots \dots$<br>7.3.3 Integration in NT <sup>2</sup> $\dots \dots \dots$ | 74<br>75        |  |  |  |

|    | 7.4                                   | Benchmarks                                                                                                                                                                                       |                 |  |  |  |

|    |                                       |                                                                                                                                                                                                  | 77<br>77        |  |  |  |

|    | 7.5                                   | Conclusion                                                                                                                                                                                       | 77              |  |  |  |

| 8  | Cor                                   | clusion and Perspectives                                                                                                                                                                         | 79              |  |  |  |

| Α  | BSI                                   | P++ Benchmarks results                                                                                                                                                                           | 83              |  |  |  |

|    | A.1                                   | APMC Benchmarks                                                                                                                                                                                  | 83              |  |  |  |

|    | A.2                                   | Smith-Waterman Benchmarks                                                                                                                                                                        | 88              |  |  |  |

| В  | Cur                                   | riculum Vitae                                                                                                                                                                                    | 93              |  |  |  |

| Bi | ibliog                                | graphy                                                                                                                                                                                           | 105             |  |  |  |

# Acknowledgments

This thesis is the story of 8 years of research work in various places with many people. It's important to understand that such a body of work can't realistically be done alone. I want to say thanks to every collegues and students that I encountered during those years : Lionel Lacassagne, Claude Tadonki, Tarik Saidani, Adrien Bak, Eric Jourdanneau, Khaled Hamidouche, Pierre Esterie, Alexandre Borghi, Cecile Germain, Sylvain Peyronnet, Thomas Herault, Marc Baboulin, Mikolaj Szydlarski, Sebastian Schaetz.Romain Montagne, Adrien Remy, Amal Khabou, Yushan Wang, Ian Masliah, Lenaic Bagnieres, Florence Laguzet, Dimitrios Chasapsis and Antoine Tran Tan. I also want to thanks people from NumScale for sharing this adventure with me: Mathias Gaunard, Alan Kelly, Charles Pretot, Thierry Mourrain and Guillaume Quintin.

My thanks also go to all my friends from the C++ Community that supported me and my Crazy Frenchman personna : Eric Niebler, Hartmut Kaiser, Bryce Lelbach, Joel de Guzman, Edouard Alligand, Michael Caisse and Andrew Sutton.

I want to express my gratitude to my reviewers – Pr Hill, Pr Hains and Pr Cole – for their precious time spent reading this thesis and for their extremely interesting remarks on my work. A great thanks to Pr Conchon, Pr Vialle, Pr McColl and Pr Lamotte for being part of my committee and for all the advices and discussions we exchanged.

I also want to thank Daniel Etiemble for everything since 2007. Thanks to have put your faith in me and to have been a model for me all those years. I won't probably there if you didn't decide to review my PHD thesis 8 years ago. Thanks again for your trust and support.

Finally, I want to thank my familly, my wife and my children to have been more than supporting during all those years. I love you.

# Chapter 1 Introduction

| Contents |                                       |   |

|----------|---------------------------------------|---|

| 1.1      | From Experiments to Simulations       | 3 |

| 1.2      | The Free Lunch is Definitively Over   | 4 |

| 1.3      | Challenges Addressed in this Document | 5 |

| 1.4      | Habilitation Thesis Overview          | 6 |

|          |                                       |   |

"It is a profound and necessary truth that the deep things in science are not found because they are useful; they are found because it was possible to find them."

— J. Robert Oppenheimer

# **1.1** From Experiments to Simulations

Science has been built for centuries on top of a set of simple rules often called the Scientific Method. The scientific method is a four steps process that structure scientific reasoning. Those steps are usually defined as:

- the **Observation** of the subject of inquiry;

- the formulation of Hypotheses or theory to explain said observations;

- the definition of **Predictions**, including logical deduction from the theory;

- the design and execution of **Experiments** to validate all of the above.

This process has been driving scientific discovery and technological breakthrough for centuries. But as science ventured deeper into the understanding of phenomena which duration and scale were out of reach or for which reproducibility was an issue, the notion of experiments changed. Indeed, if setting up experiments to validate hypothesis on how heat transfers between macroscopic bodies can be made at human scale, how can we experiment the theory on the inner workings of a star, the first femtosecond of the Universe or the monitoring of generations of human beings ? With the advent of computing and computer science, experiments evolved into **Numerical Simulations**. Such simulations are an attempt to model a real-life or hypothetical situation on a computer so that it can be studied to see how the system works. By changing variables in the simulation, predictions may be made about the behavior of the system and reproduce a large variety of settings, thus enabling an iterative refinement of hypotheses. Lately, computer simulations have also been a great tool to process the extremely large dataset that actual experiments can generate [Chen 2014].

Nowadays, numerical simulations running on computers is the most fundamental tool that most sciences – from physics to social science – use as a substitute to experiments when said experiments can not realistically be run with a satisfactory duration, budget or ethical framework. This also means that the accuracy and the speed at which such computer simulations can be done is a crucial factor for the global scientific advancement. If accuracy of the simulation is tied to the field knowledge of scientists, the speed of a simulation is tied to the way one may take advantage of a computer hardware.

# 1.2 The Free Lunch is Definitively Over

For many years, the computing power of a given computer was modeled as a direct derivation of the famous – yet often misquoted – Moore's Law. Moore's law is the observation that, over the history of computing hardware, the number of transistors on integrated circuits doubles approximately every two years [Schaller 1997]. Since its initial definition in 1965, Moore's Law has been proven as accurate, in part because the law is now used in the semiconductor industry to guide long-term planning and to set targets for research and development. For years the self-fulfilling Moore's Law also dictated the increase of computing power of CPUs. A more popular version of Moore's Law, actually stated by David House, is that computing power doubles every 18 months. This phenomenon, often known as the "Free Lunch" following the term coined by Herb Sutter [Sutter 2005], has been true for more than four decades but as been recently been halted.

During the "Free Lunch" era, the computing power of microprocessors has resulted of the continuous increase of clock frequency and from micro-architectural features like super-scalar execution, caches hierarchy, branch predictor or SIMD extensions. However, the so called "Heat Wall" made high frequency unreachable while the benefits from micro-architectural features started showing diminishing returns effects. CPU manufacturers then started designing chips containing multiple computing cores as it was their only solution to the ever growing demand in microprocessor power. The so-called multi-cores then lead the path to many-cores chips containing hundreds of cores with far less micro-architectural features. As **parallelism** grew inside chips, the "Free lunch" was over as the average developers had to willfully manage the complexity of parallel programming if they wanted to use a non trivial amount of performance from their hardware.

# 1.3 Challenges Addressed in this Document

In this context, current research directions usually focus either on how to provide ways for computer scientists to access the latent performance of modern complex parallel systems or on how to actually abstracts away hardware details so development productivity can be increased despite the complexity of parallel programming. In a more formal way, we struggle between **Abstractions**, *i.e* the ability to express parallelism with minimum concerns for implementation details, and **Efficiency**, *i.e* the ability to produce code whose performances can stay on the par with those obtained using low-level technologies. Those two research directions rarely deal with each other, leading to abstractions with interesting properties but no efficient implementation or to efficient tools being under-used due to a lack of proper user-level abstractions. Our work during the past six years focused on exploring how to design tools for parallel programming that provide a high level of abstractions while delivering a high level of performance. In addition to this classical conflict, we wanted to:

- Provide a **Non-Disruptive Technology** by avoiding the design of yet another language and associated ecosystem as we thought that the acceptance of our solutions, especially in industrial contexts, will be easier if our tools do not require changes in the programming infrastructure of our users. We choose to focus on the design of C++ software libraries so that their adoption can be maximal among computer scientists.

- Use **Domain Specific Knowledges** to drive optimizations. If low-level code generation quality is a given, the best opportunities of massive speed-up often lies in a precise choice of algorithms or algorithm's parameters that Domain knowledge may carry.

- Be Architecture Aware, by allowing our software solutions to support or be easily extensible to support upcoming parallel architectures. We first focused on small scale SIMD shared memory systems and moved onto clusters and accelerators.

Our work was then split into three phases:

**Feasibility**: Complex programming models can be implemented using various paradigms ranging from functional to object-oriented programming. Alas, the choice of the proper idiom and the proper language can be non-trivial. We explored if and how modern C++ design strategies like Generic Programming, Generative Programming and Template Meta-programming were able to solve the abstraction vs efficiency conundrum by constructing abstractions with few runtime penalties at

the cost of a more complex development process.

These results notably involved the supervision of Khaled Hamidouche, in collaboration with Daniel Etiemble.

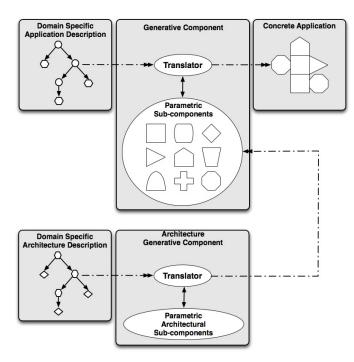

**Extensibility** : Generic and Generative Programming are well known techniques for sequential development but applications to parallel programming suffered for a lack of generality in how the architectural component of the problem was handled. To solve this issue, we investigated an extension of those techniques to exploit architecture knowledge in a way compliant with Generic Programming. By relying on the properties of specific parallel programming models, we proposed a hierarchical version of the usual Generative Programming idiom.

These results notably involved the supervision of Pierre Esterie in collaboration with NumScale SAS.

**Portability** : Once our system was designed to support a wide selection of architectures and domains, we challenged its design by extending its support to different architectures and programming models.

These results notably involved the supervision of Antoine Tran Tan and Ian Masliah in collaboration with Daniel Etiemble, Lionel Lacassagne, Marc Baboulin and NumScale SAS.

### 1.4 Habilitation Thesis Overview

This document is organized as follows. Chapter 2 describes various abstractions for parallel programming. It describes how different approaches have been proposed to scale down the complexity of parallel applications by providing simplified execution and programming models for parallel systems. Chapter 3 presents modern software design principles and how they can help design proper implementation of parallel programming abstractions. Those methods are assessed in Chapter 4 by implementing a C++ BSP library based on generic programming. This implementation show how far we can go in term of both API expressiveness and performances. Based on these preliminary experiments, Chapter 5 depicts our efforts on providing scalable techniques for using architectural informations into the design of efficient libraries in a structured way. Chapter 6 and Chapter 7 shows how this improved design techniques were used into the design of various libraries using different sets of parallel programming abstractions while delivering a high level of performances. We then conclude on the contributions of this work and details some future research directions.

# CHAPTER 2 Abstractions for Parallel Programming

#### Contents

| 2.1 Motivation                                                                                                     | 7 |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|---|--|--|--|

| 2.2 Performance Centric Abstraction                                                                                | 8 |  |  |  |

| 2.2.1 P-RAM Models                                                                                                 | 8 |  |  |  |

| 2.2.2 LOG-P Models                                                                                                 | 9 |  |  |  |

| 2.2.3 BSP Models                                                                                                   | 0 |  |  |  |

| 2.3 Memory Centric Abstraction 1                                                                                   | 1 |  |  |  |

| 2.3.1 HTA                                                                                                          | 1 |  |  |  |

| 2.3.2 PGAS Languages                                                                                               | 2 |  |  |  |

| 2.4 Pattern Centric Abstraction                                                                                    |   |  |  |  |

| 2.4.1 Parallel Skeletons                                                                                           | 3 |  |  |  |

| 2.4.2 Futures and Promises $\ldots \ldots 1$ | 6 |  |  |  |

| 2.5 Conclusion                                                                                                     | 8 |  |  |  |

"It is not only the violin that shapes the violinist, we are all shaped by the tools we train ourselves to use, and in this respect programming languages have a devious influence: they shape our thinking habits." — Edsger W. Dijkstra

# 2.1 Motivation

The design of parallel algorithms is a complex process in which one should find a hardware-agnostic way to express the distribution, scheduling and potential synchronizations of an arbitrary number of sub-tasks applied on an arbitrary amount of data sets. Abstract models of parallel machines and parallel programs have been proposed to simplify the process of designing parallel algorithms. Those limited models willingly omit to take every aspect of parallel machines so that the general form of a program written within the model is simple. We can roughly divide those models in three great families based on the main aspect of parallel systems they focus on.

# 2.2 Performance Centric Abstraction

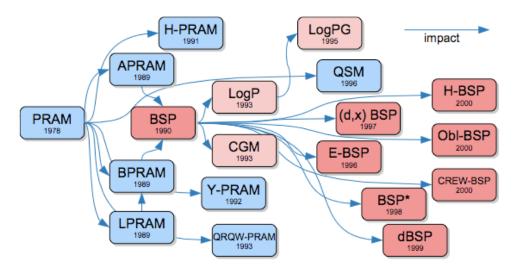

A first class of parallel programming models attempts to simplify the design of parallel programs by constraining valid programs to follow a set of rules tied to a runtime performance model. The objective is to provide a framework in which all valid programs performance can be analytically evaluated before any actual implementation. Even if other models may provide some sort of performance model, it is not usually as central. The relationship between most of these performance centric model is given in figure 2.1.

Figure 2.1: Relationships between performance centric parallel programming models

#### 2.2.1 P-RAM Models

P-RAM [Fortune 1978] is a parallel computing model that is a direct extension of the classic sequential programming model. In the P-RAM model, *P* processors read and write in arbitrary locations of a global shared memory. Using a global clock, they synchronously execute their instructions. Communications between processors is handled by read/write patterns through the shared memory. Conflicts during memory accesses is then resolved using various strategies. The cost model of P-RAM is rather simple as it doesn't take synchronization or communication costs. P-RAM algorithm cost model is often expressed as depending only on the problem size and P-RAM system size.

Various extensions of P-RAM have been proposed:

• Local-memory PRAM (LP-RAM) has been proposed [Aggarwal 1989] as a way to exploit memory hierarchy inside a P-RAM machine. In addition to the global shared memory, each processor contains a private local memory. At each

step, each processor can either read from memory or perform computations. In this model, the concurrent accesses to the global memory are handled via the CREW model (Concurrent Read, Exclusive Write) to limit locking.

- Block-PRAM [Aggarwal 1990] extends LP-RAM by modeling the global memory as a series of blocks. Processors can then transfer data between global and local memory by block of consecutive cells. This block based access has a cost defined as b + l where b is the block size and l the memory access latency, which is a machine dependent parameter. Accesses to block must be non-overlapping and are resolved using the EREW (Exclusive Read, Exclusive Write) model.

- Asynchronous P-RAM [Gibbons 1989] is a P-RAM extension featuring both local and global memory but, contrary to all P-RAM models, allowing asynchronous computation across processors. This model proposes a new instruction to force arbitrary synchronization among a group of processors and adds this synchronization cost to the performance model.

#### 2.2.2 LOG-P Models

The LOG-P model proposed by [Culler 1993] is a model for distributed memory multi-processor machines using peer-to-peer message passing communications. The model models the machine based on a set of four characteristics:

- L: the network latency upper-bound for transmitting a word between two processors;

- *o*: the communication overhead, defined as the time required by a processor to complete a transmission and during which no computations can be performed;

- g: the delay between transmission of successive messages. Inverse of g can then be defined as the system bandwidth;

- *P*: the number of processors in the system.

Note that LOG-P models the network performance but has no informations about the network topology. Moreover, the network is supposed to have a finite capacity so that only L/g messages can be in transit at any given time. If a processor tries to transmit a message under these circumstances, it will be blocked until the network is available again.

#### 2.2.3 BSP Models

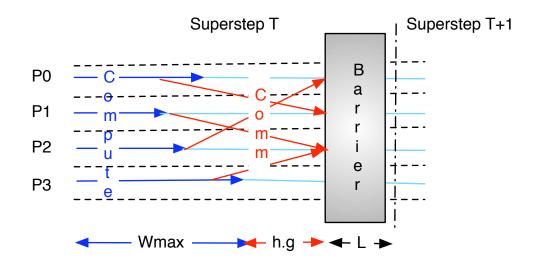

The Bulk Synchronous Parallel Model (BSP) was introduced by [Valiant 1990] as a bridge between the hardware and the software to simplify the development of parallel algorithms. Classically, the BSP model is defined by three components: a machine model, a programming model and a cost model:

Figure 2.2: Principles of the BSP programming model

- The machine model describes a parallel machine as a set of processors linked through a communication medium supporting point-to-point communications and synchronizations. Such machines are described by a set of parameters [Hill 1998]: *P* (number of processors), *r* (processor speed), *g* (communication speed) and *L* (synchronization duration).

- The programming model specifies how a parallel program is structured (Figure 2.2). A BSP program is a sequence of super-steps in which each process performs local computations followed by communications. When all processes reach the synchronization barrier, the next super-step begins.

- The cost model provides an analytical way of estimating the runtime cost of a BSP algorithm. Following this model, the cost of a super-step is determined as the sum of the cost of the longest running local computation, the cost of global communication between the processors, and the cost of the barrier synchronisation at the end of the super-step. The cost of one super-step for *p* processors is expressed as

$$max_{i=1}^{p}(w_{i}) + max_{i=1}^{p}(h_{i}g) + l$$

where  $w_i$  is the cost for the local computation in process i, and  $h_i$  is the number of messages sent or received by process i.

As for P-RAM and LOG-P, various extensions of BSP have been proposed by either increasing the precision of the cost model [Blelloch 1997], by reducing the impact of the synchronization step which is the main limitation of the BSP model [Gonzalez 2000] or extending it to heterogeneous systems [Li 2012]. Various implementations of BSP have been proposed. Table 2.1 gathers information about those implementations.

| Implementation          | Model           | Abstraction | Target   | Architecture     |

|-------------------------|-----------------|-------------|----------|------------------|

|                         |                 | Level       | Language |                  |

| BSPlib[Hill 1998]       | BSP             | Low         | C, C++   | Cluster          |

|                         |                 |             | FORTRAN  |                  |

| BSPonMPI[Suilen 2006]   | BSP             | Low         | C, C++   | Cluster          |

| BSPK[Fahmy 1996]        | Oblivious BSP   | Low         | C, C++   | Cluster          |

|                         | [Gonzalez 2000] |             |          |                  |

| BSPGreen[Goudreau 1999] | BSP             | Low         | C, C++   | Cluster          |

| PUB-BSP[Bonorden 1999]  | BSP             | Medium      | C, C++   | Cluster          |

|                         |                 |             |          | Embedded Systems |

| BSML[Loulergue 2002]    | BSP             | High        | OCaml    | Cluster          |

Table 2.1: Available Implementations of the BSP model

## 2.3 Memory Centric Abstraction

A second class of parallel programming models uses the properties of memory hierarchies and the distribution properties to guide developers in the design of parallel programs. They are often implemented as new languages or existing language extensions due to their interaction with low level memory management or networking systems.

#### 2.3.1 HTA

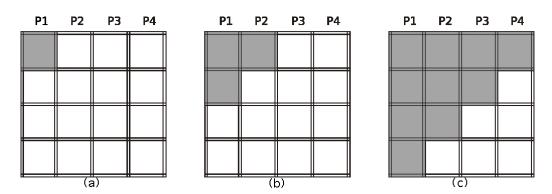

Hierarchically Tiled Arrays or HTA is a parallel data type designed to facilitate the writing of programs based on tiles in object-oriented languages [Bikshandi 2006]. HTA allows to exploit locality as well as to express parallelism with much less effort than other approaches. Implementations of the HTA model have been developed for C++ and MATLAB, with the parallel back-end running on MPI. A C++ version for shared-memory systems based on Intel Threading Building Blocks has been developed. A Hierarchically Tiled Array or HTA is an array that is subdivided into tiles. Each tile can be either a regular array or another HTA, hence the recursive nature of this data type [Brodman 2008]. By leading developers to handle arrays as an explicit or implicit aggregation of tiles, it simplifies the exploitation of locality hints in parallel programs.

Listing 2.1 illustrates a Jacobi computation with HTAs. A and B are HTAs with one level of tiling; there are n tiles at the root of the tiling hierarchy (level 0), each tile holding d + 2 variables (level 1). Variables at index 0 and d + 1 in each tile are

ghost cells. The boundary exchange first updates the ghost cells at index 0, then at index d + 1. The iteration across tiles is implicit in all assignments.

Listing 2.1: Jacobi update C++ implementation using HTA

```

HTA < double, 1 > A(, B;

double S = 0.125;

2

3

while (!converged)

4

5

{

Tuple<1> t1n(1,n), t0n1(0,n-1);

6

Tuple<1> t1d(1,d), t0d1(0,d-1), t0d1(2,d+1);

7

8

// boundary exchange

9

= B(t0n1)[d];

B(t1n)[0]

B(t0n1)[d+1] = B(t1n)[1];

11

stencil computation

11

14

A()[t1d] = S * (B()[t2d1] + B()[t0d1]);

15

16

. . .

17

}

```

In the stencil computation, the region is not specified at tile access and thus all tiles at level 0 are considered in the operation.

#### 2.3.2 PGAS Languages

Partitioned Global Address Space (PGAS) languages [Blagojević 2010] are designed around a memory model in which a global address space is logically partitioned such that a portion of it is local to each processor. Those languages rely on the use of one-sided communications provided by various distributed memory run-times. PGAS abstracts away the notion of communications by providing primitives to build distributed data structures but still requires a SPMD programing style that may limit its applicability. Three PGAS based languages are usually put forward:

#### 2.3.2.1 Co-Array Fortran

Co-Array Fortran [Numrich 1998] supports the ability to refer to the multiple cooperating instances of an SPMD program (known as images) through a new type of array dimension called a co-array. By declaring a variable with such dimension, the user can specify how each image will allocate a copy of the variable. Remote accesses between variables are performed by indexing over this co-array dimension using square brackets instead of the classical parens of Fortran. In addition to this, synchronization primitives are provided to coordinate images.

#### 2.3.2.2 UPC

UPC is a C extension for supporting PGAS-style computation [El-Ghazawi 2003]. Contrary to Co-Array Fortran, UPC relies on automatic distribution of specially typed instances of array following a linear, block cyclic manner. If this makes distribution of works simpler, UPC distributed array suffers from classical C limitations and a task like 2D distribution of a 2D array is tedious. This can be simplified by using UPC PGAS pointer that can point to any shared or global address space while maintaining locality information in the pointer type. Finally, UPC also supports a new loop structure – forall – which allows the distribution of work to workers by following affinity rules.

#### 2.3.2.3 Titanium

Titanium is a PGAS dialect for Java [Yelick 1998]. Titanium adds several features to Java to support multidimensional arrays, iterators, sub-arrays, copying, operator overloading and performance-oriented memory management. The distributions of data and synchronization between SPMD program instances are provided through similar type marking as UPC, allowing the JAVA compiler to statically enforce synchronization.

## 2.4 Pattern Centric Abstraction

Patterns based programming models are based on the observation that parallelism is expressed in the form of a few recurring patterns of computation and communication found in a large number of applications. Different kinds of patterns can be extracted and proposed as composable entities. Pattern abstractions also have the interesting properties to be defined on top of other kind of parallel programming models, *e.g.* pattern rising from BSP algorithms.

#### 2.4.1 Parallel Skeletons

The concept of Parallel Skeletons [Cole 1989] is based on the very definition of Pattern Centric Abstractions. In this model, every application domain has its own specific skeletons – or patterns – that can be leveraged and combined. For example, in computer vision, parallel skeletons mostly involve slicing and distributing regular data while parallel exploration of tree-like structures is common in operational research applications. The main advantage of this parametrization of parallelism is that all low-level, architecture or framework dependent code is hidden from the user, who only has to write sequential code fragments and instantiate skeletons.

Another interesting feature of skeletons is their ability to be nested. If we look at a skeleton as a function taking functions as arguments and producing parallel code, then any instantiated skeleton is eligible as being another skeleton's argument. Skeletons are thus seen as *higher-order functions* in the sense of functional programming. At the user's level, building parallel softwares using algorithmic skeletons boils down to simply combining skeletons and sequential code fragments. Classical skeletons includes:

• The map skeleton encapsulates classical, SIMD style data parallelism. map applies, in parallel, a function f to each element of an array or list-like data

structure. Parallelism is then exploited as the application of f on two distinct elements is done simultaneously. In computer vision, a variant of this skeleton called scm is often found and operates on the whole image, performing the slicing and merging of the input and output image.

- The **pipeline** skeleton models situations in which a sequence of successive tasks are dispatched and run in parallel on a set of processing units. Each task receives its input from its predecessor and sends its result to the next processor in the pipeline, either in a blocking or non-blocking way.

- The farm skeleton [Poldner 2005] handles load balancing in data-parallel context, *i.e.* situations in which a -potentially ordered- list of items has to be processed by a pool of workers following some kind of load-balancing strategy. Each item is dispatched to the first non-busy worker and a result is sent to an implicit collector each time a worker task is completed.

- The par skeleton is a generic ad-hoc skeleton for running N different tasks on a subset of N processing units. No implicit communication is provided and all synchronization or data transfer should be explicitly carried out by the inner tasks. This skeleton is a way to integrate ad-hoc parallelism [Cole 2004] in skeleton-based applications.

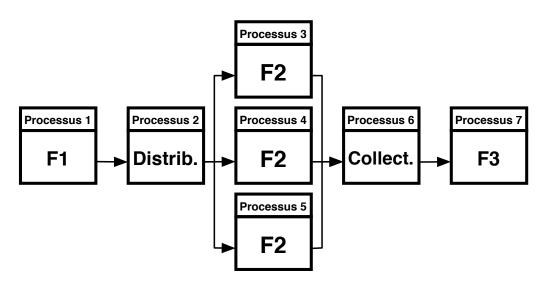

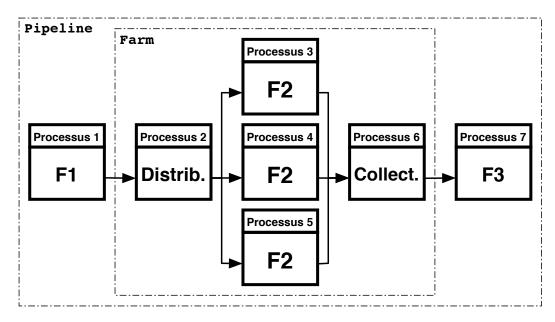

As an example of Skeleton efficiency at capturing parallel applications structure in a compact way, consider the process graph on figure 2.3.

Figure 2.3: A sample process graph

This graph describes an application in which a stream of data are processed by process 1, passed to a distribution process that will send the data to one of the three slave process, gather the results then pass them to the final process. The first level of communications between process 1, 2,6 and 7 is no less than a pipeline. The group of process 2 to 6 can be seen as a farm made of three slaves (fig. 2.4).

Figure 2.4: A sample process graph viewed as nested skeletons

This sample application can then be expressed as a language agnostic, skeletonbased description :

$$pipeline(f_1, farm(3, f_2), f_3)$$

This terse description, backed up by the skeletons semantic, describes the whole application structure and behavior. Note that the distribution and collection process don't appear as they are mere artifact of one potential farm implementation.

A large body of works around Skeletons exists and covers a large selection of domains and languages. As an exhaustive study of the properties of skeleton based tools has been performed in [Gonzalez-Velez 2010], we present here the most influential tools.

- The Edinburgh Skeleton Library [Cole 2004, Benoit 2005b] (eSkel) is a C library based on MPI that provides a set of skeletons including: pipeline, farm, deal, butterfly and haloSwap. It introduced a large number of fundamental skeleton related notions like different types of nesting [Benoit 2005a] (transient or persistent) and attempted at providing a cost model based on process algebra for its skeletons [Benoit 2008].

- The **Pisa Parallel Programming Language** [Bacci 1995] (P3L) provides skeleton constructs that are used to coordinate the parallel or sequential execution of C code. A compiler named Anacleto [Ciarpaglini 1997] is provided and uses implementation templates to compile P3L code on target architectures.

A performance model can then be used to decide program transformations for optimizations. Users can define a P3L module as a properly defined skeleton construct with input and output streams, and other sub-modules or sequential C code. Modules can be nested using the two tier model, where the outer level is composed of task parallel skeletons, while data parallel skeletons may be used in the inner level.

- The Muenster Skeleton Library [Ciechanowicz 2009] (Muesli) is a C++ template library supporting higher order functions, currying, and polymorphic types and uses both MPi and OpenMP to implement both task and data parallel skeletons, using a nesting approach similar to the two tier approach of P3L. In Muesli, C++ templates are used to render skeletons polymorphic, but no type system is enforced. The supported skeletons include Branch & Bound, Divide & Conquer, Farm, Pipe, Filter, reduce, map, permute, zip and their variants. Currently, Muesli supports distributed data structures for arrays, matrices, and sparse matrices.

- Sketo [Matsuzaki 2006] is a C++ skeleton library focusing on parallel data structures as such as: lists, trees, and matrices [Emoto 2007]. The data structures are generic, and operations like map, reduce, scan, zip, shift can be applied in parallel on their contents. SkeTo also uses C++ genericity to implement optimization rules like the skeleton fusion transformation [Matsuzaki 2004], which merges two successive function invocations into a single one, thus decreasing the function call overheads and avoiding the creation of intermediate data structures passed between functions.

- Marrow[Marques 2013] is a C++ parallel skeleton library for heterogeneous, multi-GPU environments relying on OpenCL. Marrow provides a set of classical data and task parallel skeletons including map and pipeline and supports nesting. Marrow automatically generates all the host/device communication and orchestration code, including communications overlap and code generation.

#### 2.4.2 Futures and Promises

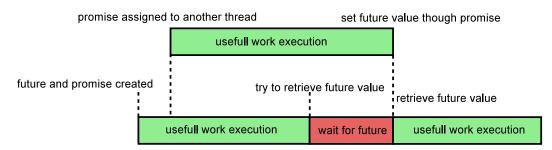

Experience with parallel programming has shown that common synchronization techniques like barriers do not scale well on massively parallel machines [Beckman 2006], with thousands of workers. One would like to use finer grain synchronization, but reasoning about the exact point an operation will complete is virtually impossible in a parallel environment of large scale. An alternative is to use asynchronous programming models, which allow the programmer to write programs where a thread or process can be oblivious to what actions the other threads/processes are doing. However, he should still be able to retrieve the results of concurrent works and produce the correct result. The **Futures and Promises** model is such an asynchronous programming model. A **Future** is a special variable which may or may not have a value at the time that it is referenced in program. A promise is a special construct that is associated with a **Future** and can be used by another thread or process to set the value of the **Future** variable. Usually, the **Future** is used only to read the variable value, while the promise is used to write to the same variable, thus defining a data-flow relation between different threads/processes. The promise construct is often hidden from the programmer. Instead he will have to declare a callable object (function, functor, etc). The library will offer a mechanism to use this callable object to set the **Future** through the promise, after executing the user's callable object. Such is the use of the *async* function in the C++ 11 standard, where the user can issue a function or functor object and retrieve a **Future** object using the *async* call. The *async* will be run by a thread, and the return value of the function or functor will be used to set the **Future** object associated with that *async* call.

An important design decision for any Futures implementation is what happens when a Future is referenced, while its value is not yet available. A common choice is to have the caller block until the Future value is resolved or implicitly try to resolve the Future at the reference time (as with lazy evaluation schemes). Figure 2.5 shows the execution model of the blocking scheme.

Figure 2.5: The Futures execution model of the blocking schematics.

The green color is the time a thread spends doing useful computation, while the red color is the idle time a thread spends on waiting for the result of the Future. This is the scheme used by C++11 and in the Scala Future implementation [Philipp 2012], where the user can set a callable object to be called when the Future will be set, or if the Future throws an exception (failure), using the callback mechanism. This scheme has the benefit that there will be no blocking at any point of the code, allowing true asynchronous execution. The C++11 standard, as most blocking Future implementations, offers the option to ask whether a Future is ready before referencing its value, in order to avoid any blocking if possible.

Other than their asynchronous execution model, Futures offer an easily programmable and expressive user interface that is very close to sequential programming. As a motivation to the reader, we present in Listing 2.2 a Fibonacci function implementation, using the C++ 11 standard threads library [Committee 2011] Future interface.

```

Listing 2.2: A fibonacci implementation using the C++ 11 futures interface

int fibonacci(int n)

{

if(n == 0) return 0;

if(n == 1) return 1;

std::future<int> fib1 = std::async(fibonacci, n-1);

std::future<int> fib2 = std::async(fibonacci, n-2);

return fib1.get() + fib2.get();

}

```

Listing 2.3 also shows the sequential equivalent for comparison.

```

Listing 2.3: Sequential Fibonacci

int fibonacci(int n)

{

if(n == 0) return 0;

if(n == 1) return 1;

return fibonacci(n-1) + fibonacci(n-2);

}

```

The parallel version simply requires the recursive calls to be issued using the *async* function, and the use of the get method on the **Future** objects in order to retrieve the return values of the recursive calls. Note that the call to the get method here is blocking.

### 2.5 Conclusion

Design and exploration of parallel programming models have been a very productive research area for more than thirty years. Various approaches targeted at solving different issues have been proposed and implemented. With respect to our initial goal, the following models appear as strong contender as the basis of new tools' development:

- the BSP model for its ability to provide an analytical cost model that can be used to drive optimizations;

- parallel skeletons which abstraction level and composability could help handling the hierarchical and heterogeneous nature of modern parallel hardware;

- Futures which provide a sound and composable programming model for asynchronous operations

The following chapters will investigate how such models can cooperate and be used as the underlying layer of new tools and how modern development practices can accommodate those models while delivering high performances.

# Chapter 3

# Modern C++ Design Techniques

#### Contents

| 3.1 Obj                           | 3.1 Objectives                     |           |  |  |

|-----------------------------------|------------------------------------|-----------|--|--|

| 3.2 Generic Programming           |                                    |           |  |  |

| 3.3 Act                           | ive libraries                      | <b>22</b> |  |  |

| 3.3.1                             | Domain Specific Embedded Languages | 23        |  |  |

| 3.3.2                             | Template Meta-Programming          | 23        |  |  |

| 3.3.3                             | Boost.Proto                        | 24        |  |  |

| 3.4 Other code generation systems |                                    |           |  |  |

| 3.4.1                             | Delite                             | 29        |  |  |

| 3.4.2                             | DESOLA                             | 29        |  |  |

| 3.4.3                             | ТОМ                                | 29        |  |  |

| 3.5 Con                           | clusion                            | 30        |  |  |

" Within C++, there is a much smaller and cleaner language struggling to get out."

— Bjarne Stroustrup, The Design and Evolution of C++.

# 3.1 Objectives

The previous chapter introduced different parallel programming models, from which we selected a subset amenable to proper implementation. We also noticed that a large number of C++ based implementations of library or tools using those models are available. Some of them use C++ features like generic programming or template meta-programming to achieve high levels of performances or to define intuitive API. This chapter will go over the definition of such modern C++ design techniques and their respective advantages.

# 3.2 Generic Programming

Generic Programming is a programming paradigm for developing efficient, reusable software libraries. Pioneered by Alexander Stepanov and David Musser, Generic Programming obtained its first major success when the Standard Template Library became part of the C++ Standard [Stepanov 1995a]. This process focuses on

finding commonality among similar implementations of the same algorithm, then providing suitable abstractions so that a single, generic algorithm can cover many concrete implementations. This process, called lifting, is repeated until the generic algorithm has reached a suitable level of abstraction, where it provides maximal re-usability while still yielding efficient, concrete implementations. The abstractions themselves are expressed as requirements on the parameters to the generic algorithm.

This notion of requirements are then promoted to first class entities called Concepts [Gregor 2006] that carry the semantic informations about the types requirements, thus providing more than just a generic, reusable implementation, but a better understanding of the problem domain. By building a library API and algorithms on Concepts usually lowers the burden of implementation by requiring the strict minimal set of interfaces from the user defined types, is efficient as runtime checks of interface –as done via dynamic polymorphism– are replaced by simple syntactic verifications and, finally, is far more extensible as new types can be adapted to fit any given Concepts without requiring heavy inheritance.

As an example, consider writing a C++ function that computes the sum of all the elements contained between two memory location (for example, the beginning and the end of an array). To do so in a generic way, we rely on the C++ Concepts of InputIterator. With generic programming, the concrete interface of an InputIterator is irrelevant. The code is written using templates accepting any types and is properly instantiated as long as those types model the correct set of Concepts, regardless of where, when and how they're defined, and whether or not they derive from a common base class or interface.

Iterators in general, and InputIterator in particular, can be thought of as an abstraction of pointers. A type It is said to satisfy the Inputterator Concept if it fulfills the following constraints :

- The type It satisfies CopyConstructible (*i.e.* provides a copy constructor)

- The type It satisfies CopyAssignable (*i.e.* provides a assignment operator)

- The type It satisfies Destructible (*i.e.* provides a destructor)

- The type It satisfies EqualityComparable (*i.e.* provides operator==)

- Given i and j, values of type It&, the following expressions are valid:

- std::iterator\_traits<It>::reference r = \*i;

- It& j = ++i;

- (void)i++;

- bool c = i != j;

Compare this with a traditional object-oriented programming, where iterators would have be design as inheriting from some **Inputterator** interface which would prevent us from using raw pointers as iterators, thus limiting the applicability – and performance – of the function. Listing 3.1 gives a possible generic implementation of our sum function using the **Iterator** Concept.

```

Listing 3.1: C++ generic implementation of sum

template < typename InputIterator >

typename std::iterator_traits<InputIterator>::value_type

sum(Inputterator b, Inputterator e)

ſ

typename std::iterator_traits<InputIterator>::value_type r;

5

6

7

while(b

!= e)

*b++:

9

return r;

10

3

```

Calls of this function can then be performed using raw pointers, iterators extracted from a standard container or any type satisfying the InputIterator Concept, like for example, a user-defined type with the proper interface but which dereferencing operator returns a monotonous series of values instead of extracting data from memory.

Generic Programming and Concepts also provide support for Concept Checking, a practice that allows for a limited support of parametrized types constraints [Siek 2005], simplifying error checking at compile-time. Tools like the Boost Concept Check Library or ConceptGCC compiler implement such mechanisms. Latest developments on Concepts by Sutton et al. [Sutton 2011] brought up a revised Concepts implementation and applied it on the C++ standard library, simplifying the work needed to support Concepts in mainstream C++ compiler. Discussions are still ongoing to decide if and how Concepts will be integrated in the upcoming C++ 17 standard.

Generic Programming has been successfully applied to the design of software tools like:

• The Adobe Generic Image Library: GIL [Parent 2014] is a C++ generic library that allows for writing generic imaging algorithms with performance comparable to hand-writing for a particular image type. The library is designed to be flexible and efficient by using abstract image representations from algorithms on images. It allows for writing code once and having it work for any image type. These image types can then be specified through compile-time or run-time options and policies that helps the library to select and optimize the proper code. Compatibility with standard C++ library components are also provided, thus allowing GIL to be seamlessly integrated into existing code.

- The **Boost Graph Library**: BGL [Siek 2002] aims at applying the concept of Generic Programming to the design of graph oriented algorithms able to operate on a large selection of graph representations (linked list of nodes, adjacency matrix, arrays, etc ...) . By decoupling the algorithm themselves from the internal representation of the graphs, BGL is able to apply a large selection of graphs based algorithms on various, customizable, graph entity using a large variety of graph representations.

- The Standard Template Adaptive Parallel Library (STAPL) is a framework for developing parallel programs in C++ [Buss 2010]. It is designed to work on both shared and distributed memory parallel computers. Its core is a library of ISO Standard C++ components with interfaces similar to the sequential ISO C++ standard library. STAPL includes a run-time system, design rules for extending the provided library code, and optimization tools. STAPL relies on a tiered structure in which parallel containers, parallel algorithms and a supporting run-time system are isolated and allow various levels of users –ranging from standard user to domain expert– to take advantage of large scale parallelism even with complex, non-contiguous data structures.

Note that if properties of values, containers and operations handling those are the most usual Concepts laid by those libraries, few defines Concepts for parallel elements even if these library performs parallel computation.

### 3.3 Active libraries

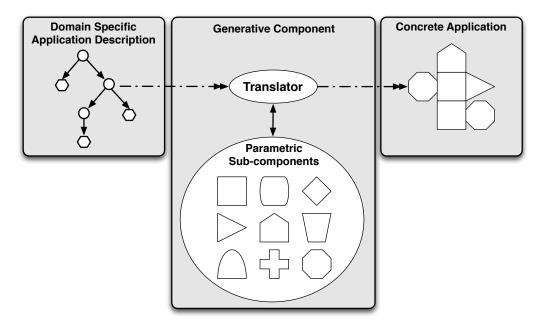

In opposition to classic libraries, Active libraries [Veldhuizen 1998] takes an active role during the compilation phase to generate code. They aim at solving the abstraction/efficiency trade-off problem. They base their approach on defining a set of generative programming methods. These libraries provide domain-specific abstractions through generic components and also define the domain-driven generator to control how these components are optimized. By carrying domain-specific semantic at a high level, this technique enables a semantic analysis of the code before any real code generation process kicks in. Such informations and transformations are then carried on by a meta-language that allows the developer to embed meta-informations. Once the generator finds a solution space in the configuration space, the code generation phase starts resulting on an optimized version of the code. The main approach to design such libraries is to implement them as Domain Specific Embedded Languages (*DSELs*). As they reuse general purpose language features and existing compilers, *DSEL*s are easier to design and implement.

#### 3.3.1 Domain Specific Embedded Languages

By definition, a Domain-Specific Language (DSL) is a computer language specialized to a particular application domain, contrary to a general-purpose language, which is broadly applicable across domains, and lacks specialized features for a particular domain. Domain Specific Embedded Languages (DSELs) are a subclass of DSL that rely on an existing general-purpose language to host it. DSELs then reuse the host language syntax and tool ecosystem to be compiled or interpreted. The compile-time process of generating new code (either inside or outside the current host language) known as **Template Meta-Programming** is then used to ensure performances and correctness.

#### 3.3.2 Template Meta-Programming

C++ template meta-programming [Abrahams 2004] is a technique based on the abuse of the template type system of C++ to perform arbitrary computation at compile time. This properties of template is due to the fact that C++ templates define a Turing-complete sub-language manipulating types and integral constants at compile-time [Unruh 1994]. Due to the fact that template code generation is performed at compile-time, uses constants and supports pattern-matching and recursion thanks to template partial specialization, template can also looked at as a pure functional language [Haeri 2012].

Templates are an interesting technique for generative programming. As templates are Turing-complete, one can design a set of templates meta-programs acting as a DSL compiler run at compile-time and generating temporary C++ code fragment as an output. The resulting temporary source code is then merged with the rest of the source code and finally processed by the classic compilation process. Through this technique, compile-time constants, data structures and complete functions can be manipulated. The execution of meta-programs by the compiler enables the library to implement domain-specific optimizations that lead to a complete domain oriented code generation. Such a technique can be hosted by several languages featuring meta-programming features (incidental or by design) like D [Bright 2014], Haskell [Sheard 2002] and OCaml [Serot 2008].

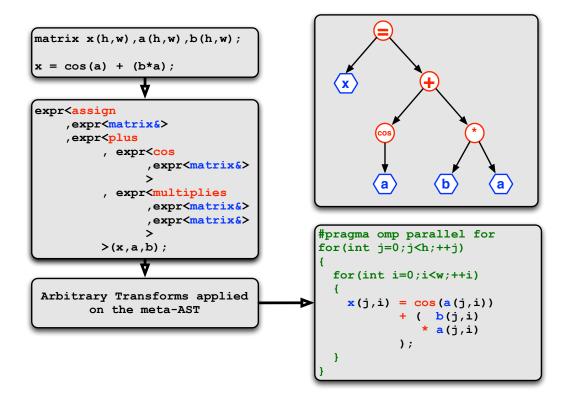

DSELs in C++ use template meta-programming via the Expression Template idiom. Expression Templates [Veldhuizen 1995, Vandevoorde 2002] is a technique implementing a form of delayed evaluation in C++ [Spinellis 2001]. Expression Templates are built around the recursive type composition idiom [Jarvi 1998] that allows the construction, at compile-time, of a type representing the abstract syntax tree of an arbitrary statement. This is done by overloading functions and operators on those types so they return a lightweight object which type represents the current operation in the Abstract Syntax Tree (AST) being built instead of performing any kind of computation. Once reconstructed, this AST can be transformed into

arbitrary code fragments using Template Meta-Programs (see figure 3.1).

Figure 3.1: General principles of *Expression Templates*

#### 3.3.3 BOOST.PROTO

While Expression Templates should not be limited to the sole purpose of removing temporaries and memory allocations from C++ code, few projects actually go further. The complexity of the boilerplate code is usually as big as the actual library code, making such tools hard to maintain and extend. To avoid such a scenario, tools encapsulate the Expression Template technique as reusable frameworks with extended features.

The Portable Expression Template Engine or PETE [Haney 1999] extends the expression template technique and provides an engine to handle user defined types in expression statements. It is used in the POOMA framework [Reynders 1996] that provides a set of C++ classes for writing parallel PDE solvers. With PETE, the user can use the engine and apply transformations at the AST level. PETE presents some limitations and its engine does not allow the user to perform common transformations on the AST as it only evaluates expressions with a bottom-up approach. This engine also lacks of domain specific consideration while manipulating expressions.

To alleviate these shortcomings, Niebler has proposed a C++ compiler construction toolkit for embedded languages called BOOST.PROTO [Niebler 2007]. It allows developers to specify grammars and semantic actions for *DSEL*s and provides a semi-automatic generation of all the template structures needed to perform the AST capture. Simply put, BOOST.PROTO can be seen as a DSEL to design DSELs. Compared to hand-written Expressions Templates-based DSELs, designing a new embedded language with BOOST.PROTO is done at a higher level of abstraction by designing and applying **Transforms** that are functions operating via pattern matching on DSEL statements. In a way, BOOST.PROTO supersedes the normal compiler workflow so that domain-specific code transformations can take place as soon as possible. The main idea behind BOOST.PROTO is the construction of an AST structure through the use of terminals. A BOOST.PROTO terminal represents a leaf of an AST. The use of a terminal in an expression infects the expression and builds a larger BOOST.PROTO expression. These expressions are tied to specific domains as BOOST.PROTO aims at defining *DSELs*. To illustrate the possibilities of the library, we present a simple analytical function DSEL written with BOOST. PROTO.

This DSEL will allow us to evaluate analytical expressions of the following form:

(x\*5 + 2.0\*x - 5)

We will specify the value of x by using the parenthesis operator and it will also triggered the evaluation of the expression like in the following example:

$$(x*5 + 2.0*x - 5)(3.0)$$

BOOST.PROTO can be seen as a compiler in the sense that it provides a similar way to specify your own language. In comparison to classic compilers, the first entry point of the library is the specification of grammar rules. BOOST.PROTO automatically overloads all the operators for the user but some of them may not be relevant for a DSL. This means that it may be possible to create invalid domain expressions. BOOST.PROTO can detect invalid expressions through the use of a BOOST.PROTO grammar. A grammar is defined as a series of valid grammar elements. In our example, we want to allow the use of:

- classical arithmetic operators;

- analytical variables;

- numeric literals.

We then define a grammar that matches these requirements: it is presented in listing 3.2.

```

Listing 3.2: Analytical grammar with BOOST.PROTO

Terminal type discriminator

struct variable_tag {};

3

struct analytical_function

: boost::proto::or_

5

6

<

7

boost::proto::terminal< variable_tag >

8

boost::proto::or_

9

< boost::proto::terminal< int >

, boost::proto::terminal< float >

11

12

boost::proto::terminal< double >

14

, boost::proto::plus<analytical_function,analytical_function>

boost::proto::negate<analytical_function>

16

17

boost::proto::minus<analytical_function,analytical_function>

boost::proto::multiplies<analytical_function,analytical_function>

18

19

boost::proto::divides<analytical_function,analytical_function>

20

>

21

{};

```

At line 7 of listing 3.2, we allow all terminals that hold a variable\_tag. This type enables the discrimination between analytical variables and other terminals. At line 9, we allow numeric literals in our expressions. For this specific case, BOOST.PROTO wraps the literals in terminals. We finally allow the arithmetic operators.

BOOST.PROTO can now construct valid ASTs. These expression trees do not encapsulate any domain semantic for now. The AST type is a raw tree as if it was extracted from the work-flow of a compiler. The library allow us to add domain semantic to an AST through the declaration of a user-defined domain and a user-defined expression class. This process allows the user to merge the domainsemantic information with the raw structure of an expression. The next step consists in specifying the domain for our analytical DSL. This is done by inheriting from proto::domain and linking this domain to an expression generator of a user defined expression type. Listing 3.3 shows the domain declaration.

```

Listing 3.3: Domain definition with BOOST.PROTO

template<typename AST> struct analytical_expression;

struct analytical_domain

boost::proto::generator<analytical_expression>

, analytical_function

}

;

;

```

Once the domain declaration is done, we can now build our analytical\_expression class. We add a specific interface to this class as we want to be able to call the operator() on an expression to evaluate it with a given set of variables. It does not provide the definition of the operator(): we will

see how we evaluate our expression later. At this point, we do not provide any particular behavior to this operator. Listing 3.4 presents the analytical\_expression class that inherits from proto::extends. proto::extends is an expression wrapper that imbues an expression with analytical domain properties.

```

Listing 3.4: User-defined expression type with BOOST.PROTO

template < typename AST >

struct analytical_expression

: boost::proto::extends< AST

, analytical_expression<AST>

, analytical_domain

6

>

7

{

typedef boost::proto::

8

9

extends < AST

, analytical_expression<AST>

, analytical_domain

> extendee:

12

13

14

typedef double result_type;

15

analytical_expression(AST const& ast = AST()) : extendee(ast) {}

16

17

BOOST_PROTO_EXTENDS_USING_ASSIGN(analytical_expression)

18

typedef double result_type;

19

20

result_type operator()(double v0) const;

};

21

```

Now, we need to implement operator() so that BOOST.PROTO can evaluate the value of our analytical expressions. BOOST.PROTO handles that by providing **Transforms** that specify rules that need to be performed when the AST is evaluated. A Transform is a *Callable Object* [Standard 2014] defined in the same way that a BOOST.PROTO grammar. Transform rules can be extended with a semantic action that will describe what happens when a given rule is matched. The library provides a lot of default transforms that we will use in our example. Our transform that evaluates our expression needs to behave differently while walking the AST and encountering its nodes:

- If it is a terminal, we want to extract the corresponding value;

- If it's an operator, we want it to do what the C++ operators does.

To achieve this, we write the evaluate\_ transform that relies on the use of default transforms. proto::when is used here to associate a rule to a specific action. The evaluate\_ transform is presented in listing 3.5.

```

Listing 3.5: The evaluate_ transform

```

```

struct

evaluate_

2

: boost::proto::or_

3

<

4

boost::proto::when

5

< boost::proto::terminal< variable_tag >

6

boost::proto::_state

7

8

boost::proto::when

< boost::proto::terminal< boost::proto::_ >

9

boost::proto::_value

11

>

12

boost::proto::otherwise< boost::proto::_default<evaluate_> >

13

>

{};

14

```

If we want to evaluate an expression like (x+2.0\*x)(3.0), we need to evaluate each node and accumulate the result while we walk the AST. Transforms related to accumulation are common when processing ASTs. BOOST.PROTO provides a clear way to achieve these transforms: the \_state of an AST. In our case, the \_state is used at line 6 to pass the value of the analytical variable through each node and ask each node to evaluate themselves with it (see listing 3.6).

```

Listing 3.6: operator() implementation using evaluate_

result_type operator()(double v0) const

{

evaluate_ callee;

return callee(*this,v0);

}

```

The evaluation of the analytical expression (x + 2.0\*x)(3.0) is performed in the following way.

```

First, the '+' node is evaluated: (x(3.0) + (2.0*x)(3.0))().

Then, the '*' node: (x(3.0) + (2.0*x(3.0)))()

And finally, the terminals evaluation is performed: 3.0 + (2.0*3.0) = 9.0.

```

We notice the use of  $proto::\_$  (line 9) that permits to match any other terminals that are not analytical variables. In this particular case, we directly extract the value of the terminal. Literals will match such a case. At line 12, we simply tell the library to use the default behavior of operators. At the end, we can write analytical expressions that match the correct grammar and evaluate it. This is done by defining terminals and building an expression using them. Listing 3.7 shows how our small analytical DSL in action.

Listing 3.7: Analytical expression in action analytical\_expression < proto::terminal<variable\_tag>::type > const \_x; std::cout << (\_x\*3 + 9.0\*\_x)(2) << "\n"; // Output : 24

## 3.4 Other code generation systems

Several similar ideas can be found in other languages.

#### 3.4.1 Delite

**Delite** [Brown 2011] is a compiler framework and runtime for parallel embedded domain-specific languages from Stanford University PPL. Delite's goal is to enable the rapid construction of high performance, highly productive DSLs. Delite provides several facilities like built-in parallel execution patterns, optimizers for parallel code, code generators for Scala, C++ and CUDA and a heterogeneous runtime for executing DSLs. BOOST.PROTO and its use of Template Meta-Programming could be seen as C++ equivalent to Delite in the sense that it is built on similar sub-systems. The main difference is the fact that Delite has access to information like variables name or dependencies across statements that Template Meta-Programming can not access currently.

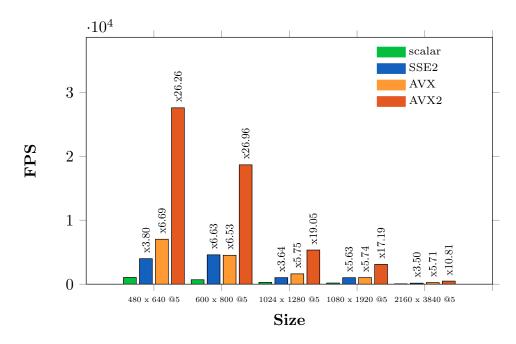

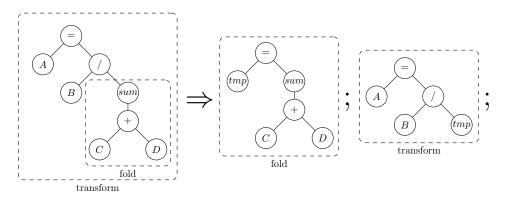

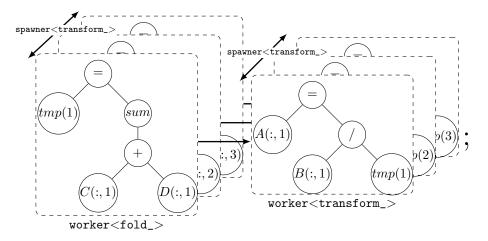

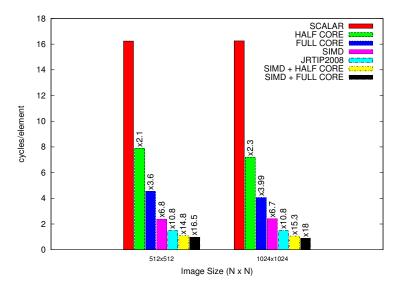

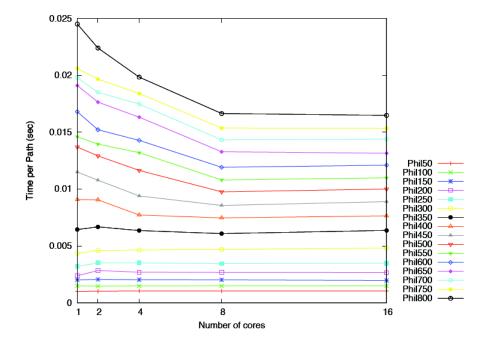

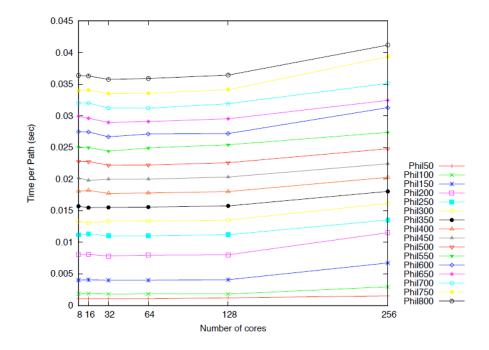

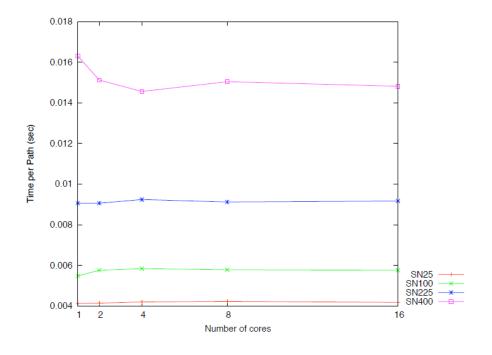

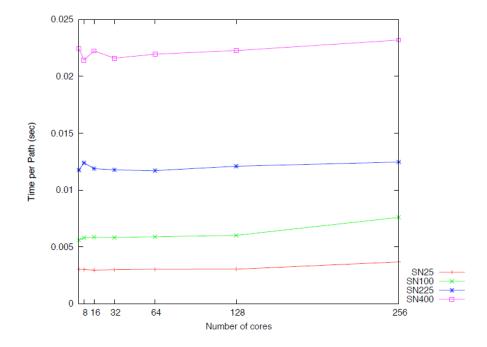

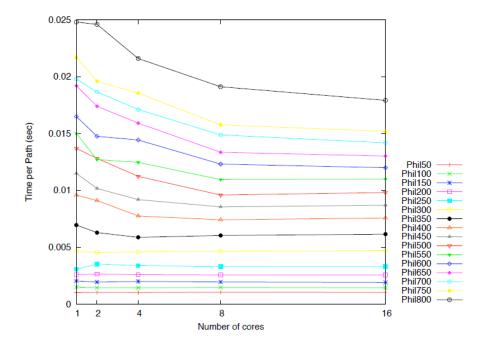

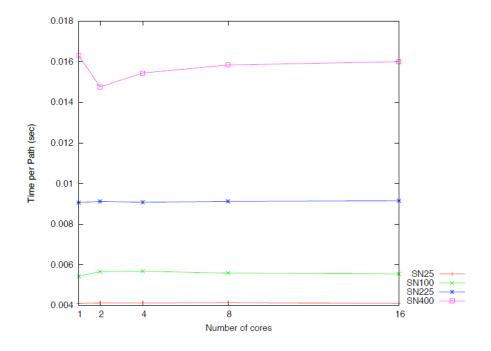

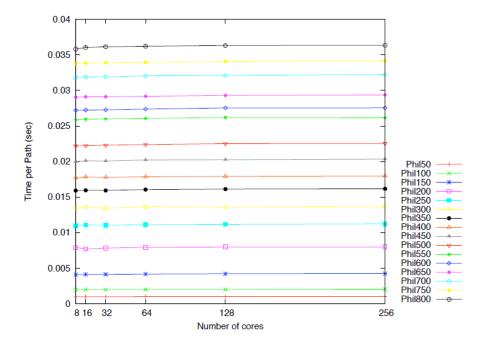

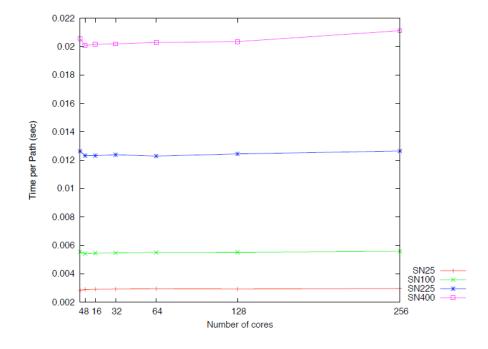

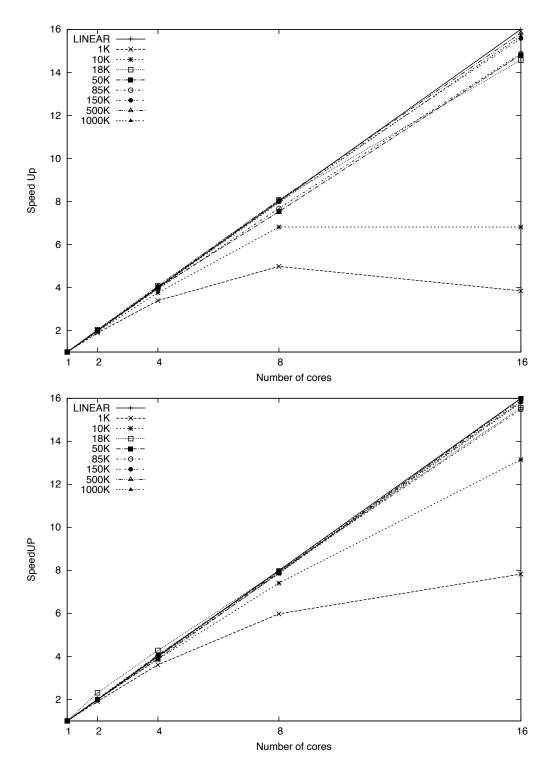

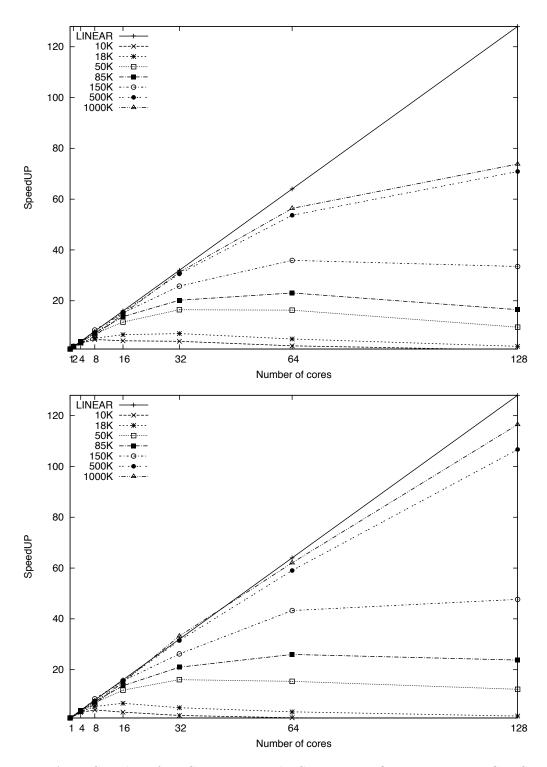

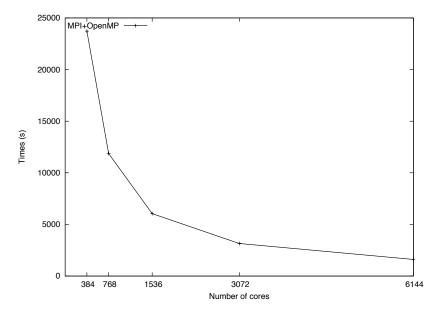

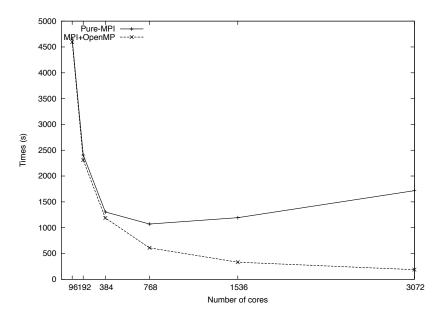

#### 3.4.2 DESOLA