## Low Complexity, Parallel Algorithms, and Scalable Architectures for Real Time Coherent Optical OFDM Systems

Pramod Udupa

### ▶ To cite this version:

Pramod Udupa. Low Complexity, Parallel Algorithms, and Scalable Architectures for Real Time Coherent Optical OFDM Systems. Signal and Image processing. Université de Rennes 1, 2014. English. NNT: . tel-01099824

## HAL Id: tel-01099824 https://inria.hal.science/tel-01099824

Submitted on 8 Jan 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^o$  d'ordre : ANNÉE : 2014

### THÈSE / UNIVERSITÉ DE RENNES 1

sous le sceau de l'Université Européenne de Bretagne

pour le grade de

### DOCTEUR DE L'UNIVERSITÉ DE RENNES 1

Mention: Traitement du Signal et Télécommunications

École doctorale : MATISSE

présentée par

### Pramod UDUPA

préparée à l'unité de recherche : IRISA - UMR 6074 Institut de recherche en informatique et systèmes aléatoires - CAIRN École Nationale Supérieure des Sciences Appliquées et de Technologie

Algorithmes parallèles et architectures évolutives de faible complexité pour systémes optiques OFDM cohérents temps réel

Low Complexity,

Parallel Algorithms

and Scalable Architectures

for Real Time Coherent Optical

OFDM Systems

Composition du jury:

### Lilian BOSSUET

Maître de Conférences HDR, Télécom Saint-Etienne Université Jean Monnet / Examinateur

### Erwan PINCEMIN

Ingénieur, Orange Labs Examinateur

### Michel JEZEQUEL

Professeur, Electronics Department Télécom Bretagne / Examinateur

### **Emmanuel BOUTILLON**

Professeur, Lab-STICC

Université de Bretagne Sud / Rapporteur

### Christophe JEGO

Professeur, IMS, Bordeaux Universités - IPB/ENSEIRB-MATMECA / Rapporteur

### Olivier SENTIEYS

Directeur de Recherche, IRISA/INRIA Université de Rennes 1 / Directeur de thèse

### Laurent BRAMERIE

Ingénieur de Recherche, FOTON, ENSSAT Université de Rennes 1 / Co-directeur de thèse  $oldsymbol{AMMA}^{To,}$  and  $oldsymbol{APPA}$

## Acknowledgements

I wish to express profound gratitude to my thesis director Prof. Olivier Sentieys for guiding me throughout the time span of this work. I am grateful to him for his expert advice and time for thesis discussions and begin available for questions/clarifications at all times. The meetings which I had helped with many aspects of work. His suggestions and comments improved the quality of the thesis report.

I also wish to express my thanks to co-director Mr. Laurent Bramerie for his guidance in the topics related to Optical Communication Systems. His evaluation of ideas from optical systems point of view helped in validation of the work. I am very thankful for many discussions on optical experiments.

I am thankful to my colleague Rémi Pallas for bringing up the real-time FPGA development system and then integrating my architecture implementation on it. It was a very hard job and he was a very good experience working with him for all the three years. I also acknowledge Arnaud Carer for his help in setting up real-time FPGA platform and discussions regarding implementation.

Thanks are also due to faculty members, senior researchers and rest of my colleagues at ENSSAT with whom I mutually shared ideas and had discussions. I am thankful especially to Mme. Nathalie Caradec for her French classes. I would also like to acknowledge the assistance of administrative staff of ENSSAT due to which I had a pleasant work environment. Further I wish to recollect with fondness, the memorable association I developed with my friends Hai, Jérémy, Karthik, Nhan, Rémi, Rengarajan, Stéphane, Vaibhav, Vinh and Vivek.

This thesis has been made possible thanks to the funding by 100 GFLEX project and facilities extended by IRISA/INRIA, including travel assistance to attend conferences, for which I remain grateful.

I wish to express my deep sense of gratitude to my parents for their encouragement in all phases of my academic and professional career that in the first instance enabled me take up doctoral studies. They sharing my goal of acquiring a doctorate only added to my inspiration to complete the doctoral program successfully. I am also grateful to the rest of my family members and friends whose constant support and words of encouragement enabled me to focus on my work.

Last, but not the least, I thank the members of the jury for agreeing to make a critical assessment of the dissertation and suggesting improvements to the thesis that enhanced its quality.

19th June 2014

Pramod UDUPA Lannion, France

## Résumé

Les systèmes de communications optiques à très haut débit sont construits à partir des techniques de pointe pour la détection, la modulation et la compensation de dispersion tels que, la détection cohérente, les modulations multi-porteuses orthogonales (OFDM) et la compensation électronique des dispersions (EDC). La réapparition de la détection cohérente dans les systèmes de communication optique a été rendue notamment possible par les progrès dans les circuits numériques dans les technologies avancées. La détection cohérente possède une meilleure sensibilité pour la détection du signal par rapport aux méthodes de détection directe. Elle permet d'utiliser des transmissions à double polarisation et conserve les informations de phase du signal optique et les transfert dans le domaine électrique. L'utilisation de la modulation OFDM fournit une flexibilité significative et l'utilisation efficace de la bande passante allouée. En raison de la disponibilité des informations de phase dans le domaine numérique, les processeurs DSP de faible coût peuvent être utilisés pour la compensation des dispersions dans le domaine numérique qui rend la solution flexible et reconfigurable. Mais, l'introduction du système CO-OFDM (Coherent-Optical OFDM) à la place de système de IM-DD (Intensity Modulation-Direct Detection) augmente significativement le coût du système avec un plus grand nombre de composants optiques et une quantité plus élevée de ressources électroniques requises pour la réception du signal. À l'heure actuelle, cela rend cette solution uniquement justifiable pour des transmissions à longue portée, même si le nombre de ressources par rapport à un système mono-porteuse à détection cohérente et modulation à quatre états (DP-CO-QPSK). Le choix de l'algorithme et l'optimisation de la précision des calculs en virgule fixe de l'architecture peuvent réduire de façon significative les ressources nécessaires pour la réalisation de systèmes CO-OFDM.

Dans cette thèse, des algorithmes à faible complexité et des architectures parallèles et efficaces sont explorés pour les systèmes CO-OFDM. Tout d'abord, des algorithmes de faible complexité pour la synchronisation et l'estimation du décalage en fréquence en présence d'un canal dispersif sont étudiés. Un nouvel algorithme de synchronisation temporelle à faible complexité qui peut résister à grande quantité de retard dispersif est proposé et comparé par rapport aux propositions antérieures. Ensuite, le problème de la réalisation d'une architecture parallèle à faible coût est étudié et une architecture parallèle générique et évolutive qui peut être utilisée pour réaliser tout type d'algorithme d'auto-corrélation est proposé. Cette architecture est ensuite étendue pour gérer plusieurs échantillons issus du convertisseur analogique/numérique (ADC) en parallèle et fournir une sortie qui suive la fréquence des ADC. L'évolutivité de l'architecture pour un nombre plus élevé de sorties en parallèle et les différents types d'algorithmes d'auto-corrélation sont explorés.

Une approche d'adéquation algorithme-architecture est ensuite appliquée à l'ensemble de la chaîne de l'émetteur-récepteur CO-OFDM. Du côté de l'émetteur, un algorithme IFFT à radix-2² est choisi pour et une architecture parallèle Multipath Delay Commutator (MDC) Feed-forward (FF) est choisie car elle consomme moins de ressources par rapport aux architectures MDC-FF en radix-2/4. Au niveau du récepteur, un algorithme efficace pour l'estimation du Integer CFO est adopté et implémenté de façon optimisée sans l'utilisation de multiplicateurs complexes. Une rÂlduction de la complexité matérielle est obtenue grâce à la conception d'architectures efficaces pour la synchronisation temporelle, la FFT et l'estimation du CFO. Une exploration du compromis entre la précision des calculs en virgule fixe et la complexité du matériel est réalisée pour la chaîne complète de l'émetteur-récepteur, de façon à trouver des points de fonctionnement qui n'affectent pas le taux

d'erreur binaire (TEB) de manière significative. Les algorithmes proposés sont validés à l'aide d'une part d'expériences off-line en utilisant un générateur AWG (arbitrary wave-form generator) à l'émetteur et un oscilloscope numérique à mémoire (DSO) en sortie de la détection cohérente au récepteur, et d'autre part un émetteur-récepteur temps-réel basé sur des plateformes FPGA et des convertisseurs numériques. Le TEB est utilisé pour montrer la validité du système intégré et en donner les performances.

### Abstract

Coherent Optical-OFDM (CO-OFDM) communication system is built on most advanced techniques for detection, modulation and dispersion compensation viz., coherent detection, orthogonal multi-carrier modulation (OFDM) and electronic dispersion compensation (EDC). The re-emergence of coherent detection in optical communication systems was made possible by the advancement in very high rate digital circuits. Coherent detection (CoD) has higher sensitivity for signal detection compared to direct detection (DD) methods. It enables use of dual-polarization transmission and it preserves phase information of optical signal and passes it to electrical domain. The use of OFDM modulation provides significant flexibility and efficient use of allocated bandwidth. Due to availability of phase information in digital domain, low cost digital signal processing (DSP) processors can be used for dispersion compensation in digital domain, which makes the solution flexible and re-configurable. But, the introduction of CO-OFDM system in place of older intensity modulation-direct detection (IM-DD) system significantly increases the cost of the system, i.e. higher number of optical components and higher amount of electronic resources are required for reception of the signal. Due to increase of resources both in optical and electronic domain, it is justifiable for only long-range transmission distances. The choice of algorithm, architecture and fixed-point optimization play a significant role in reduction of electronic resources required for realization of CO-OFDM systems.

In this thesis, low-complexity algorithms and architectures for CO-OFDM systems are explored. First, low-complexity algorithms for estimation of timing and carrier frequency offset (CFO) in dispersive channel are studied. A novel low-complexity timing synchronization algorithm, which can withstand large amount of dispersive delay, is proposed and compared with previous proposals. Then, the problem of realization of low-complexity parallel architecture is studied. A generalized scalable parallel architecture, which can be used to realize any auto-correlation algorithm, is proposed. It is then extended to handle multiple parallel samples from ADC and provide outputs, which can match the input ADC rate. The scalability of the architecture for higher number of parallel outputs and different kinds of auto-correlation algorithms is explored.

An algorithm-architecture approach is then applied to the entire CO-OFDM transceiver chain. At the transmitter side, radix-2<sup>2</sup> algorithm for IFFT is chosen and parallel Multipath Delay Commutator (MDC) Feed-forward (FF) architecture is designed which consumes lesser resources compared to MDC FF architectures of radix-2/4. At the receiver side, efficient algorithm for Integer CFO estimation is adopted and efficiently realized without the use of complex multipliers. Reduction in complexity is achieved due to efficient architectures for timing synchronization, FFT and Integer CFO estimation. Fixed-point analysis for the entire transceiver chain is done to find fixed-point sensitive blocks, which affect bit error rate (BER) significantly. The algorithms proposed are validated using optical experiments by the help of arbitrary waveform generator (AWG) at the transmitter and digital storage oscilloscope (DSO) and Matlab at the receiver. BER plots are used to show the validity of the system built. Hardware implementation of the proposed synchronization algorithm is validated using real-time FPGA platform.

## Contents

| A            | cknov          | wledgements                                                                           | i             |

|--------------|----------------|---------------------------------------------------------------------------------------|---------------|

| $\mathbf{R}$ | ésum           | né                                                                                    | iii           |

| A            | bstra          | net                                                                                   | $\mathbf{v}$  |

| $\mathbf{C}$ | onter          | nts                                                                                   | x             |

| Li           | ist of         | Figures                                                                               | x             |

| Li           | ist of         | Tables                                                                                | xiv           |

| Li           | ist of         | Abbreviations                                                                         | vii           |

| 0            | <b>Rés</b> 0.1 | sumé étendu Système de communications optiques OFDM à détection cohérente             | <b>1</b><br>1 |

|              | 0.2            | Contexte du travail                                                                   | 2             |

|              | 0.3            | Algorithme de synchronisation temporelle à faible complexité pour les systèmes OFDM   | 3             |

|              | 0.4            | Synchronisation temporelle hiérarchique à faible complexité pour les systèmes CO-OFDM | 6             |

|              | 0.5            | Architecture parallèle pour l'auto-corrélation                                        | 8             |

|              |                | 0.5.2 Architecture parallèle complète (FSBP)                                          | 10            |

|              | 0.6            | Architecture parallèle pour les systèmes CO-OFDM                                      | 11            |

|              |                | 0.6.1 Emetteur                                                                        | 11            |

|              |                | 0.6.2 Récepteur                                                                       | 11            |

|              | 0.7            | Experimentations                                                                      | 13            |

|              | 0.8            | Conclusion                                                                            | 16            |

| 1            | Intr           | roduction                                                                             | 19            |

|              | 1.1            | Context of the Work                                                                   | 22            |

|              | 1.2            | Contributions                                                                         | 23            |

|              | 1.3            | Organization of the Thesis                                                            | 24            |

| 2            | CO-            | -OFDM Transceiver System                                                              | 27            |

|              | 2.1            | Introduction                                                                          | 27            |

|              | 2.2            | Single-Mode Optical Fiber (SMF)                                                       | 27            |

CONTENTS vii

|   |     | 2.2.1   | Linear Impairments                                             |

|---|-----|---------|----------------------------------------------------------------|

|   |     | 2.2.2   | Non-Linear Impairments                                         |

|   | 2.3 | Differe | ences between Wireless-OFDM and CO-OFDM Systems                |

|   | 2.4 | Typica  | al CO-OFDM System                                              |

|   |     | 2.4.1   | Coherent Detection                                             |

|   |     | 2.4.2   | OFDM System                                                    |

|   |     | 2.4.3   | Digital Transmitter                                            |

|   |     | 2.4.4   | RF-to-Optical Up Converter                                     |

|   |     | 2.4.5   | Optical-to-RF Down Converter                                   |

|   |     | 2.4.6   | Digital OFDM Receiver                                          |

|   | 2.5 | Compl   | lexity Analysis of the System                                  |

|   |     | 2.5.1   | Digital Transmitter                                            |

|   |     | 2.5.2   | Digital Receiver                                               |

|   |     | 2.5.3   | Time/Frequency Synchronization                                 |

|   |     | 2.5.4   | CFO Compensation                                               |

|   |     | 2.5.5   | FFT                                                            |

|   |     | 2.5.6   | Integer CFO Estimation                                         |

|   |     | 2.5.7   | Channel Estimation and Equalization                            |

|   |     |         | 2.5.7.1 Least Squares (LS)                                     |

|   |     |         | 2.5.7.2 Normalized Least Mean Squares (NLMS)                   |

|   |     | 2.5.8   | CPE Estimation and Compensation                                |

|   |     | 2.5.9   | Demapper                                                       |

|   | 2.6 | Observ  | vations                                                        |

|   | 2.7 | Conclu  | sions                                                          |

|   |     |         |                                                                |

| 3 |     |         | rnchronization in OFDM Systems 50                              |

|   | 3.1 |         | uction                                                         |

|   | 3.2 |         | g Synchronization in Wireless OFDM Systems                     |

|   | 3.3 |         | sed Hierarchical Low-Complexity Synchronizer for Wireless OFDM |

|   |     | •       | os                                                             |

|   |     | 3.3.1   | OFDM System Description                                        |

|   |     |         | Proposed Hierarchical Method                                   |

|   | 0.4 | 3.3.3   | Carrier Frequency Offset (CFO) Estimation                      |

|   | 3.4 |         | ation Results                                                  |

|   |     | 3.4.1   | Parameters                                                     |

|   |     | 3.4.2   | Mean Square Error (MSE) of Timing Estimate                     |

|   |     | 3.4.3   | Mean Square Error (MSE) of CFO Estimate                        |

|   |     | 3.4.4   | Complexity of Calculations                                     |

|   | 3.5 |         | chical Synchronizer Proposed for CO-OFDM System                |

|   | 3.6 |         | ation Results                                                  |

|   |     | 3.6.1   | Parameters                                                     |

|   |     | 3.6.2   | MSE of Timing Estimate                                         |

|   | 6 = | 3.6.3   | MSE of CFO Estimate                                            |

|   | 3.7 |         | For Parallel Timing Synchronization Architecture               |

|   | 3.8 | _       | sed Block Parallel Architecture for Auto-Correlation           |

|   | 3.9 | Partia  | l-Streaming Block-Parallel (PSBP) Architecture 69              |

viii CONTENTS

|   |      | 3.9.1 Proposed PSBP architecture for Schmidl-Cox algorithm (SCA)      | 69  |

|---|------|-----------------------------------------------------------------------|-----|

|   |      | 3.9.2 Proposed PSBP architecture of Minn-Bhargava algorithm (MBA)     | 71  |

|   |      | 3.9.3 Comparison of Architectural Complexity                          | 73  |

|   | 3.10 | Full-Streaming Block-Parallel (FSBP) Architecture                     | 74  |

|   |      | 3.10.1 Proposed FSBP architecture for SCA                             |     |

|   |      | 3.10.2 Proposed FSBP architecture for MBA                             |     |

|   |      | 3.10.3 Comparison of Architectural Complexity                         |     |

|   | 3 11 | Mapping Conjugate Symmetric Correlation onto Proposed PSPB/FSPB ar-   | • • |

|   | 0.11 | chitecture                                                            | 80  |

|   | 3.12 | Conclusions                                                           |     |

|   | 0.12 |                                                                       |     |

| 4 | End  | -to-End Parallel Streaming Architecture for CO-OFDM System            | 81  |

|   | 4.1  | Introduction                                                          | 81  |

|   | 4.2  | A HLS Approach to Designing CO-OFDM System                            | 82  |

|   | 4.3  | Transceiver Algorithms and Frame Structure                            | 83  |

|   |      | 4.3.1 Design of OFDM Parameters                                       | 84  |

|   |      | 4.3.2 Transmitter Algorithm Design                                    |     |

|   |      | 4.3.3 Receiver Algorithm Design                                       |     |

|   | 4.4  | Parallel Transmitter Architecture                                     |     |

|   | 4.5  | Fixed Point Analysis of Transmitter Architecture                      |     |

|   | 4.6  | Parallel Receiver Architecture                                        |     |

|   | 4.7  | Fixed-point Analysis of Receiver Architecture                         |     |

|   | 2    | 4.7.1 Analysis & Choice of Fixed-point Precision                      |     |

|   |      | 4.7.2 Area vs. Precision                                              |     |

|   | 4.8  | Conclusions                                                           |     |

|   | 1.0  | Conclusions                                                           | 101 |

| 5 | Exp  | erimental Validation of CO-OFDM System                                | 107 |

|   | 5.1  | Introduction                                                          | 107 |

|   | 5.2  | Sampling Clock Offset (SCO) Estimation Algorithm                      | 108 |

|   | 5.3  | Electrical Back-to-Back (B2B) Experiment                              | 110 |

|   | 5.4  | Electrical B2B Configuration with RF Amplifier                        | 112 |

|   | 5.5  | Optical B2B Configuration with Homodyne Coherent Detection            | 113 |

|   | 5.6  | Heterodyne Coherent Detection Configuration                           | 116 |

|   | 5.7  | Real-Time FPGA Platform                                               |     |

|   | 5.8  | Performance of the Proposed Timing Synchronization Algorithm on Real- |     |

|   |      | Time FPGA Platform                                                    | 123 |

|   | 5.9  | Future Experiments proposed for Real-Time Platform                    | 124 |

|   | 5.10 | Conclusions                                                           |     |

| c | Com  | alusians and Daranastivas                                             | 196 |

| 6 | 6.1  | clusions and Perspectives  Overview                                   | 126 |

|   |      | Future Work                                                           |     |

|   | 6.2  |                                                                       |     |

|   |      | 6.2.1 Real-time FPGA platform experiments                             |     |

|   |      | 6.2.2 Dual-polarization CO-OFDM System                                |     |

|   | 0.0  | 6.2.3 Time Domain Sampling Clock Offset (SCO) Algorithm               |     |

|   | 6.3  | Scaling to more than 100 Gb/s with MB-CO-OFDM system                  | 128 |

| CONTENTED |    |

|-----------|----|

| CONTENTS  | 12 |

| CONTENTS  | 17 |

| Publications | 130 |

|--------------|-----|

| Bibliography | 131 |

# List of Figures

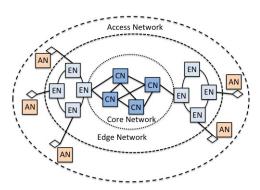

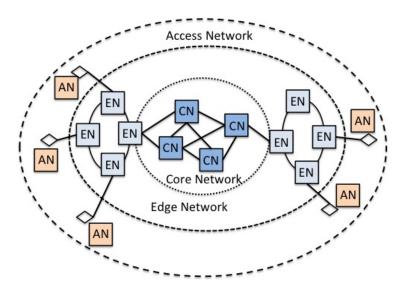

| 1   | Architecture typique d'un réseau optique. CN - Core Node, EN - Edge Node,<br>AN - Access Node                                                                                                                                                                                                                                                                                     | 1        |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

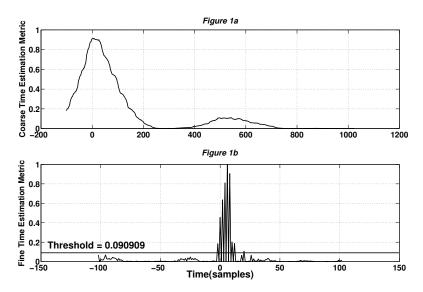

| 2   | Tracé des fonctions de métriques temporelles grossière (a) et fine (b)                                                                                                                                                                                                                                                                                                            | 4        |

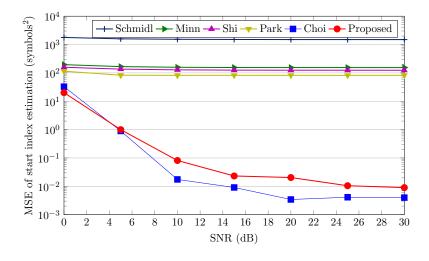

| 3   | MSE de l'estimation temporelle en fonction du SNR dans un canal ISI                                                                                                                                                                                                                                                                                                               | 6        |

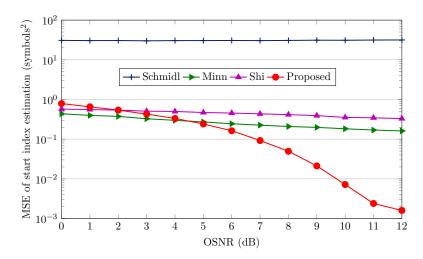

| 4   | MSE de l'estimation temporelle en fonction du OSNR pour des canaux SMS                                                                                                                                                                                                                                                                                                            |          |

|     | et un CFO = $4.75$                                                                                                                                                                                                                                                                                                                                                                | 8        |

| 5   | Architecture PSPB proposée pour le calcul de $P_{mb}$ avec MBA                                                                                                                                                                                                                                                                                                                    | 10       |

| 6   | Architecture parallèle FSPB proposée pour le calcul de $P_{mb}$ avec MBA et $R=4$                                                                                                                                                                                                                                                                                                 | 11       |

| 7   | Configuration hétérodyne à détection cohérente avec une fibre SSMFde 50                                                                                                                                                                                                                                                                                                           |          |

|     | km                                                                                                                                                                                                                                                                                                                                                                                | 15       |

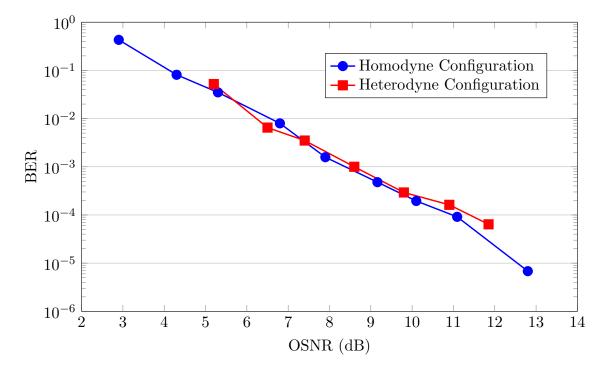

| 8   | BER vs SNR pour un système CO-OFDM simple bande hétérodyne                                                                                                                                                                                                                                                                                                                        | 15       |

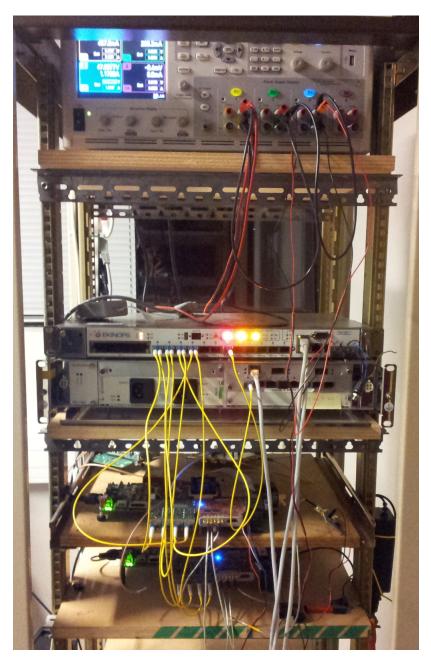

| 9   | Plateforme FPGA temps réel d'émission                                                                                                                                                                                                                                                                                                                                             | 16       |

| 10  | Plateforme FPGA temps réel de réception                                                                                                                                                                                                                                                                                                                                           | 16       |

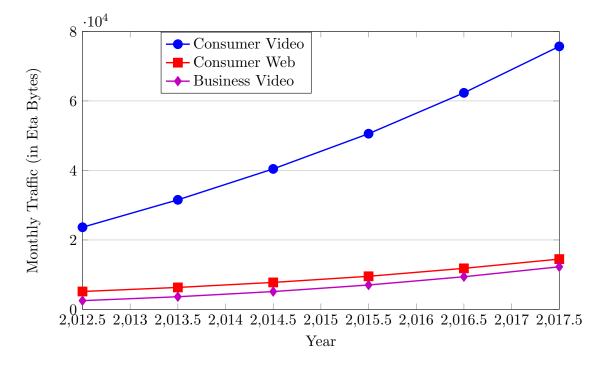

| 1.1 | Cisco Visual Networking Index (VNI) Prediction of growth of internet by Application Type (Updated May 2013). The ordinate units is in Eta Bytes (EB) Total traffic is 2017 is predicted to be three times larger than 2012 [1]                                                                                                                                                    | ).<br>19 |

| 1.2 | Typical Optical Network Architecture, CN - Core Node, EN - Edge Node, AN - Access Node                                                                                                                                                                                                                                                                                            | 20       |

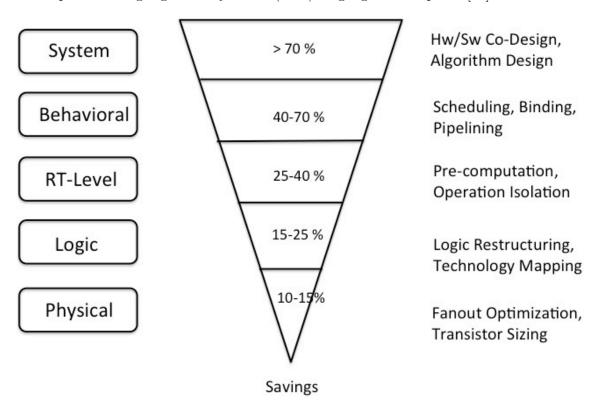

| 1.3 | Power Savings Possible at each stage in Top down VLSI Design Flow                                                                                                                                                                                                                                                                                                                 | 24       |

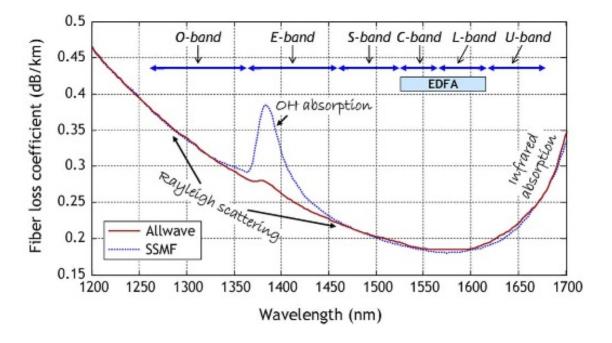

| 2.1 | Fiber loss coefficient vs. different wavelengths for a typical low-loss optical fiber (SSMF) and fiber without the water absorption peak (Allwave). [Reproduced from Essiambre et al.[2]]                                                                                                                                                                                         | 29       |

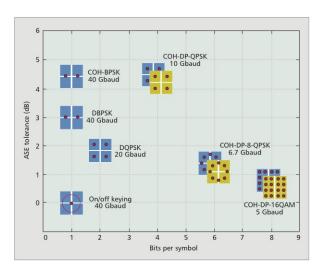

| 2.2 | Tolerance of various phase-amplitude constellations to ASE. Reproduced                                                                                                                                                                                                                                                                                                            |          |

|     | from [3]                                                                                                                                                                                                                                                                                                                                                                          | 33       |

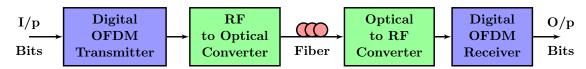

| 2.3 | Single band of a single/dual polarization CO-OFDM system                                                                                                                                                                                                                                                                                                                          | 35       |

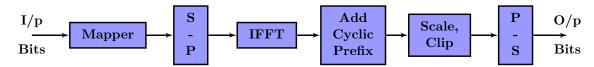

| 2.4 | Digital OFDM Transmitter, S/P - Serial-to-Parallel, P/S - Parallel-to-Serial                                                                                                                                                                                                                                                                                                      | 35       |

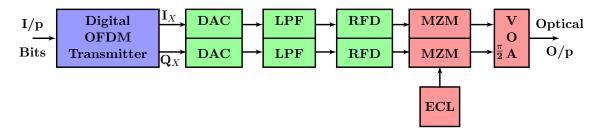

| 2.5 | Single Polarization RF-to-Optical Up Converter. $\mathbf{I}_X$ - Real Part of X-Polarization $\mathbf{Q}_X$ - Imaginary Part of X-Polarization, $\mathbf{DAC}$ - Digital-to-Analog Converter, $\mathbf{LPF}$ - Low Pass Filter, $\mathbf{RFD}$ - RF Driver, $\mathbf{MZM}$ - Mach-Zender Modulator, $\mathbf{ECL}$ - External Cavity LASER, $\mathbf{VOA}$ - Variable Optical Am- | n,       |

|     | plifier.                                                                                                                                                                                                                                                                                                                                                                          | 36       |

|     |                                                                                                                                                                                                                                                                                                                                                                                   |          |

LIST OF FIGURES xi

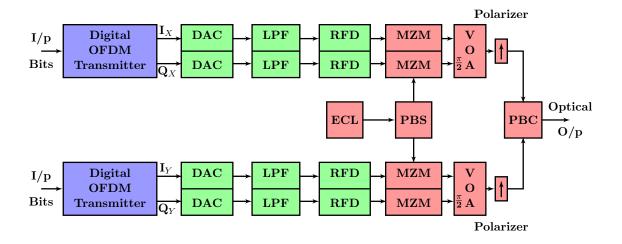

| 2.6  | Dual Polarization RF-to-Optical Up Converter, $I_X$ - Real Part of X-Polarization $\mathbf{Q}_X$ - Imaginary Part of X-Polarization, $\mathbf{I}_Y$ - Real Part of Y-Polarization, $\mathbf{Q}_Y$ - Imaginary Part of Y-Polarization, $\mathbf{DAC}$ - Digital-to-Analog Converter, $\mathbf{LPF}$ - Low Pass Filter, $\mathbf{RFD}$ - RF Driver, $\mathbf{MZM}$ - Mach-Zender Modulator, $\mathbf{ECL}$ - External Cavity LASER, $\mathbf{PBS}$ - Polarization Beam Splitter, $\mathbf{VOA}$ - Variable Optical Amplifier, $\mathbf{PBC}$ - Polarization Beam Combiner. | n,<br>36 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

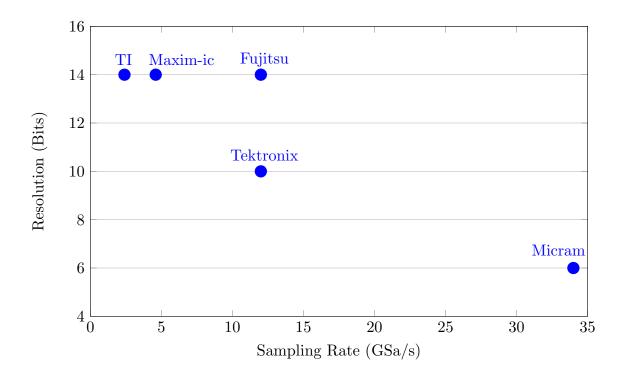

| 2.7  | Resolution vs. Sampling Rate for fastest DAC available. GSa/s - Giga Samples/second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37       |

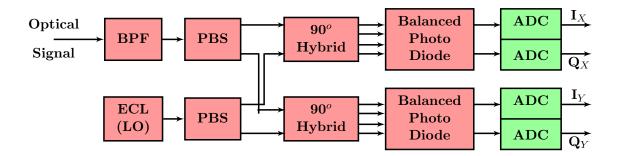

| 2.8  | Optical-to-RF Down Converter. <b>BPF</b> - Band Pass Filter, <b>ECL</b> - External Cavity LASER, <b>LO</b> - Local Oscillator, <b>PBS</b> - Polarization Beam Splitter, <b>ADC</b> - Analog-to-Digital Converter, $\mathbf{I}_X$ - Real Part of X-Polarization, $\mathbf{Q}_X$ - Imaginary Part of X-Polarization, $\mathbf{I}_Y$ - Real Part of Y-Polarization, $\mathbf{Q}_Y$ - Imaginary Part of Y-Polarization                                                                                                                                                       | 38       |

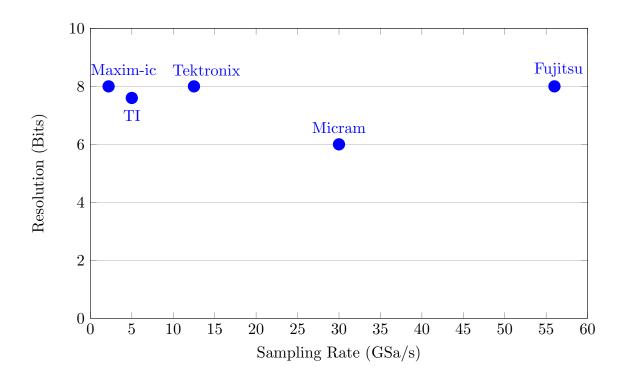

| 2.9  | Resolution vs. Sampling Rate for fastest ADC available. GSa/s - Giga Samples/second.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39       |

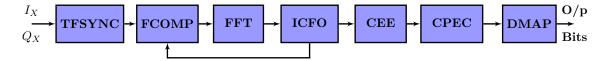

| 2.10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39       |

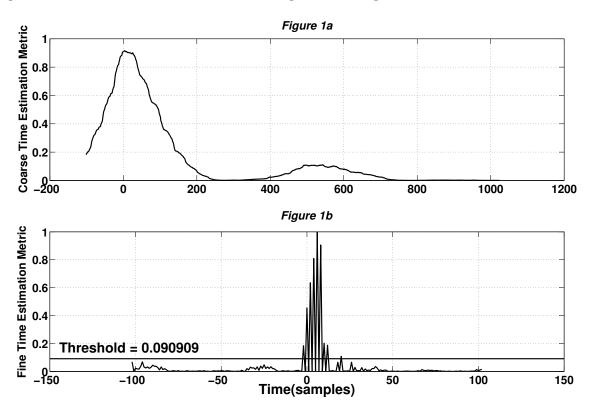

| 3.1  | Plot of Coarse (a) and Fine (b) Timing Metric Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54       |

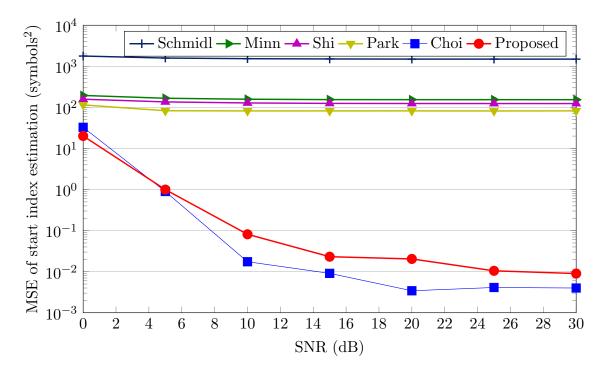

| 3.2  | MSE of Timing Estimation versus SNR in ISI channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58       |

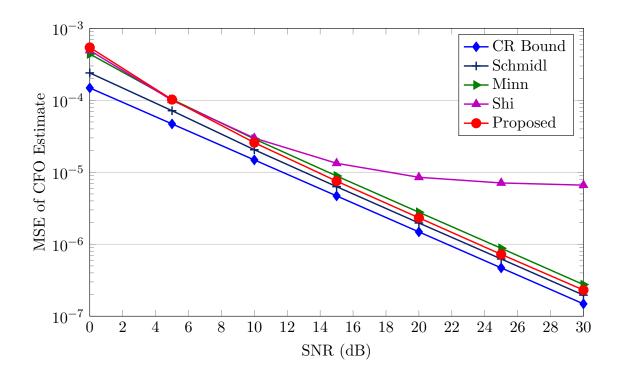

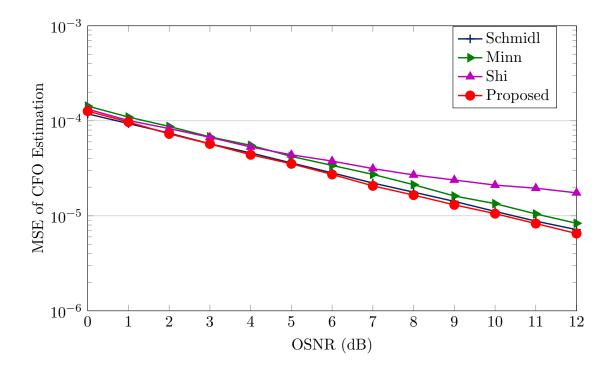

| 3.3  | MSE of CFO Estimation versus SNR in ISI channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59       |

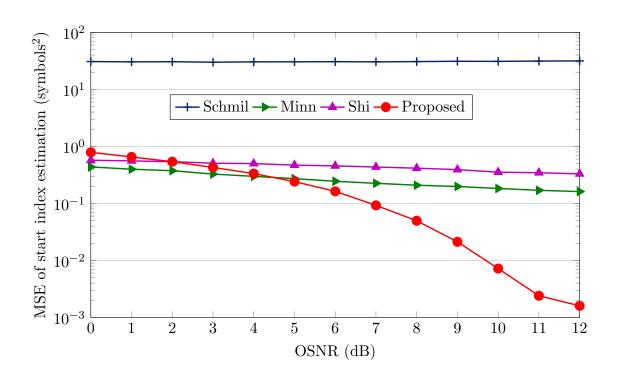

| 3.4  | MSE of Timing Estimation vs. OSNR in SSMF channel with CFO = $0.75$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62       |

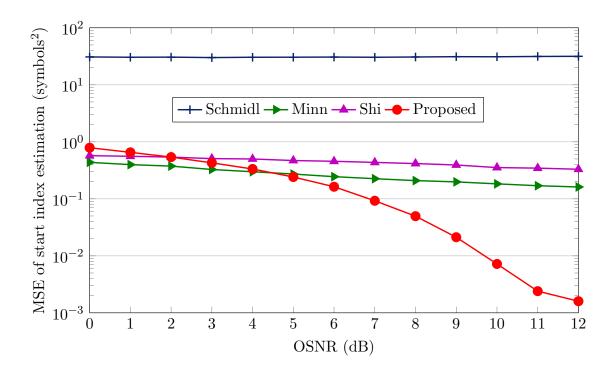

| 3.5  | MSE of Timing Estimation vs. OSNR in SSMF channel with $CFO = 4.75$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63       |

| 3.6  | MSE of CFO Estimation vs. OSNR in SSMF channel for CFO $= 0.75$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 64       |

| 3.7  | Parallel Architecture proposed by Kaneda et. al for Schmidl-Cox Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65       |

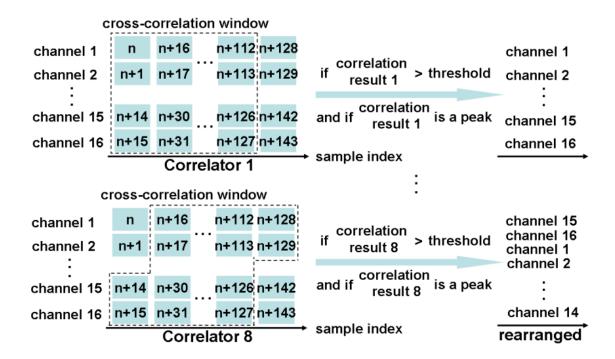

| 3.8  | Parallel Architecture proposed by Chen et. al for cross-correlation operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66       |

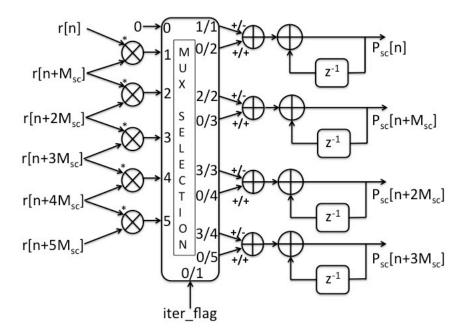

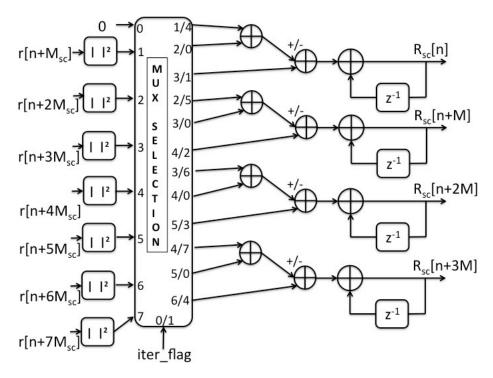

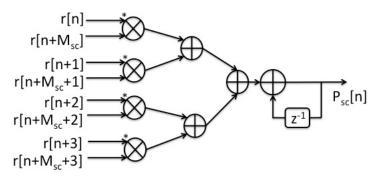

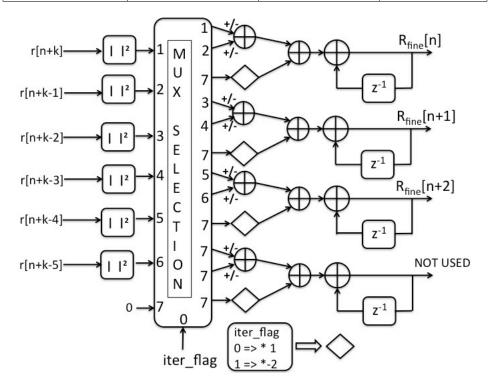

| 3.9  | Proposed $R = 4$ -Parallel PSBP Architecture for $P_{sc}$ calculation in case of SCA. iter_flag = 0 indicates non-iterative computation mode, while iter_flag = 1 indicates iterative computation mode                                                                                                                                                                                                                                                                                                                                                                   | 70       |

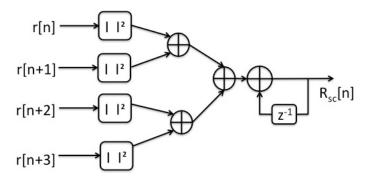

| 3.10 | Proposed $R=4$ -Parallel PSBP Architecture for $R_{sc}$ calculation in case of SCA. iter_flag = 0 indicates non-iterative computation mode, while                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 0.11 | iter_flag = 1 indicates iterative computation mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 70       |

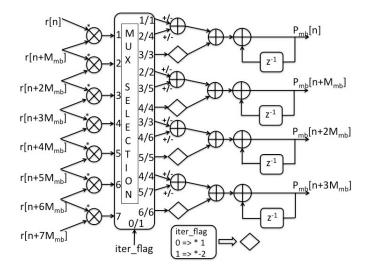

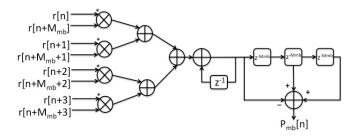

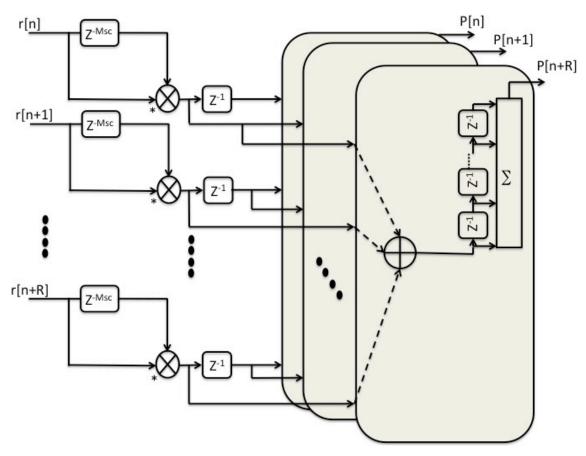

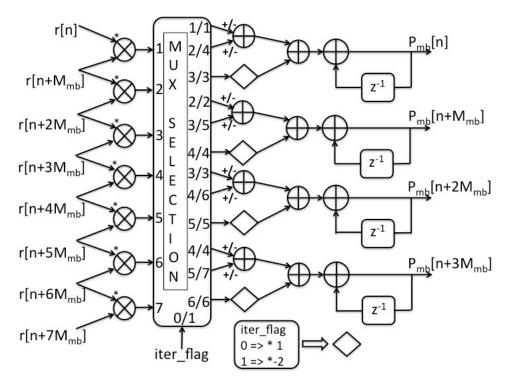

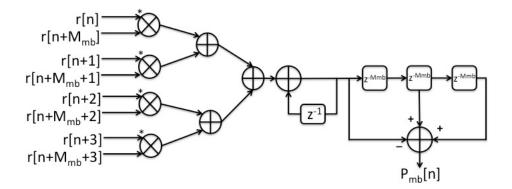

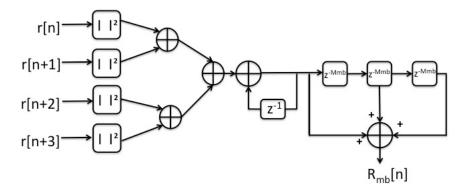

| 3.11 | Proposed PSPB Architecture for calculation of $P_{mb}$ in case of MBA. iter_flag = 0 indicates non-iterative computation mode, while iter_flag = 1 indicates iterative computation mode.                                                                                                                                                                                                                                                                                                                                                                                 | 70       |

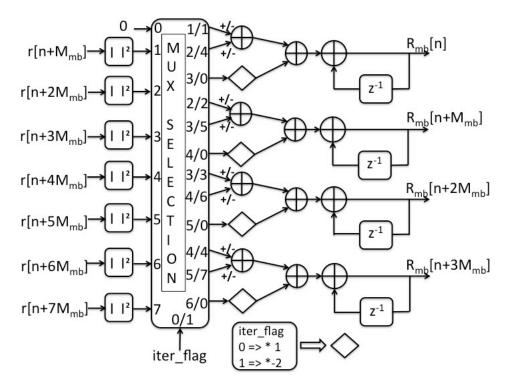

| 3.12 | iterative computation mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 72       |

| 3.13 | iter_flag = 1 indicates iterative computation mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72       |

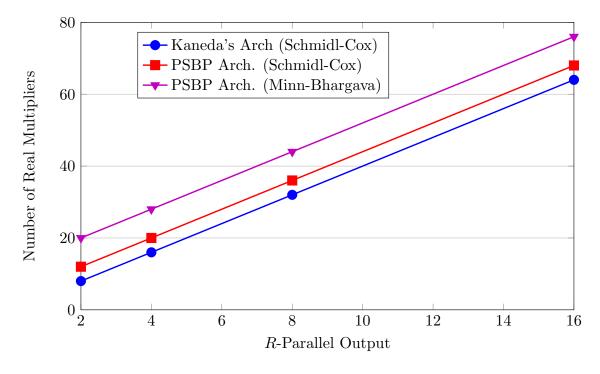

|      | Kaneda's architecture, $M=32$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 73       |

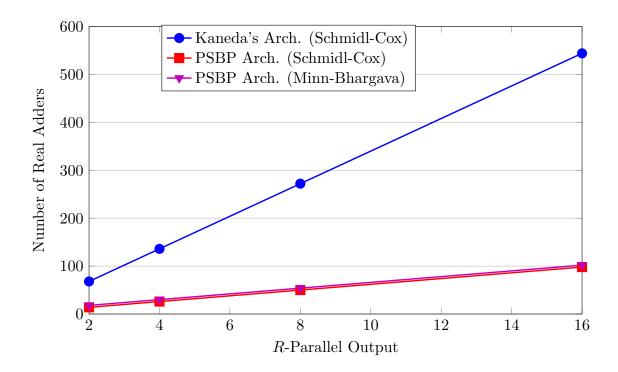

|      | Adder requirement as a function of $R$ -parallel output for PSBP and Kaneda's architecture, $M=32$                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 74       |

| 3.15 | $R=4\mbox{-Parallel}$ Initial Point Auto-Correlation Computation Block for SCA .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75       |

| 3.16 | R = 4-Parallel Initial Point Energy Computation Block for SCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 75       |

xii LIST OF FIGURES

|            | R = 4-Parallel Initial Point Auto-Correlation Computation Block for MBA                                                                          | 76       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | R = 4-Parallel Initial Point Energy Computation Block for MBA                                                                                    | 76       |

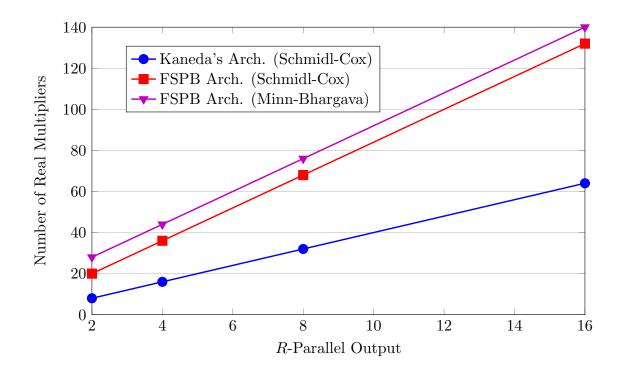

|            | Multiplier requirement as a function of $R$ -parallel output for FSBP and Kaneda's architecture, $M=32$                                          | 77       |

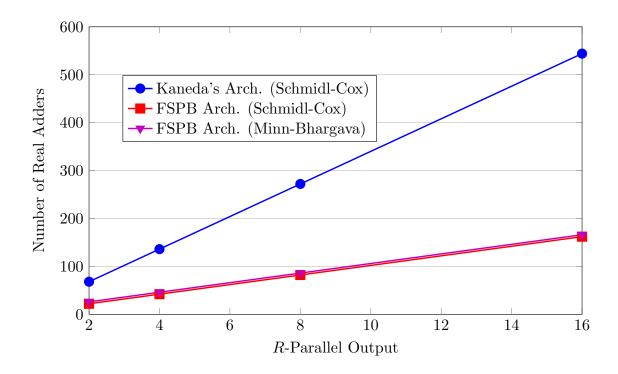

| 3.20       | Adder requirement as a function of $R$ -parallel output for FSBP and Kaneda's architecture, $M=32\ldots\ldots$                                   | 78       |

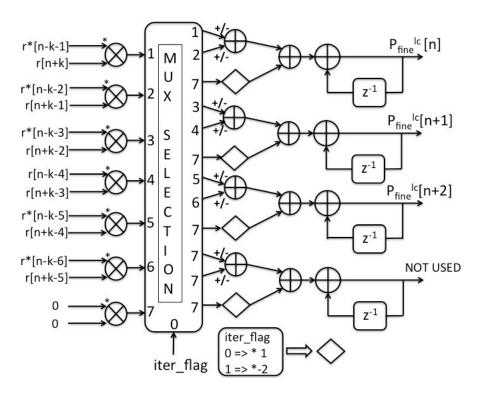

| 3.21       | Parallel conjugate symmetric correlation on $R=4$ PSPB/FSPB architec-                                                                            |          |

|            | ture. iter_flag = 0 for this operation                                                                                                           | 78       |

| 3.22       | Parallel energy calculation on $R=4$ PSPB/FSPB architecture. iter_flag =                                                                         | 79       |

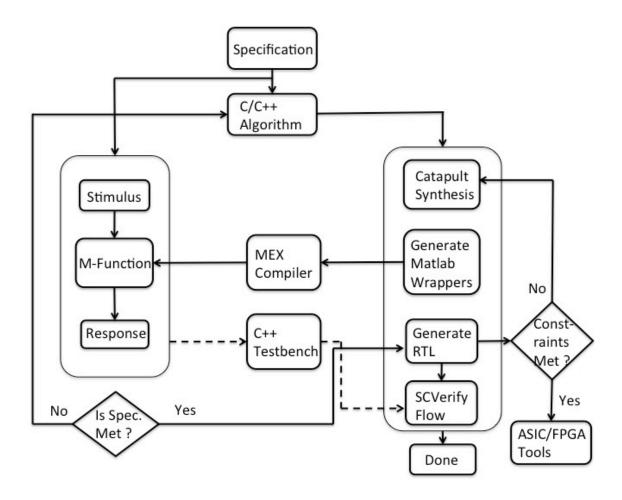

| 4.1        | $\operatorname{HLS}$ Block Diagram of Catapult<br>C synthesis flow and Matlab Integration                                                        | 83       |

| 4.2        | OFDM frame format for single polarization ( $\operatorname{Pol}_X$ ) CO-OFDM system                                                              | 84       |

| 4.3        | OFDM frame format for dual polarization $(Pol_X, Pol_Y)$ CO-OFDM system.                                                                         | 84       |

| 4.4        | IFFT/FFT Architecture of 4-Parallel radix- $2^2$ for $N=256$ , when input is                                                                     |          |

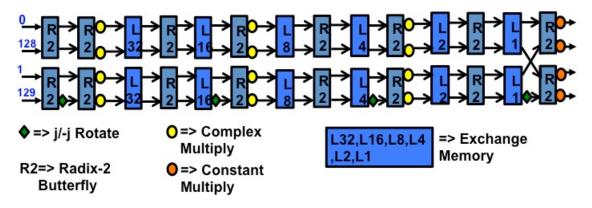

| , _        | given in even and odd index order                                                                                                                | 91       |

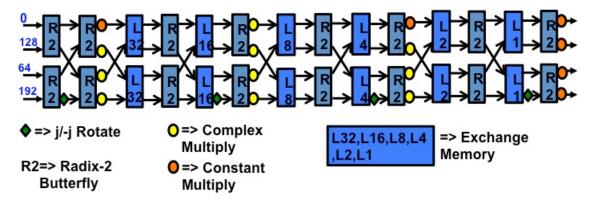

| 4.5        | IFFT/FFT Architecture of 4-Parallel radix- $2^2$ for $N=256$ , when input is                                                                     | 01       |

| 1 G        | given in normal order                                                                                                                            | 91<br>94 |

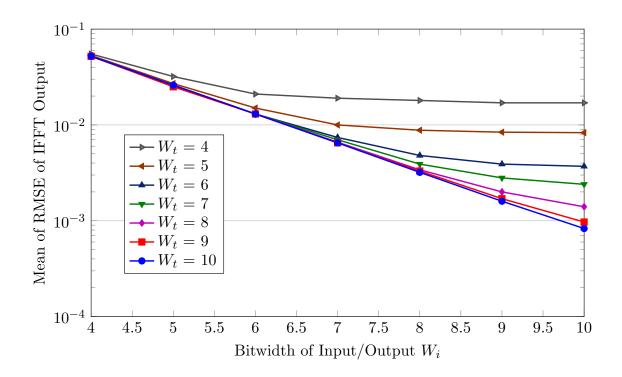

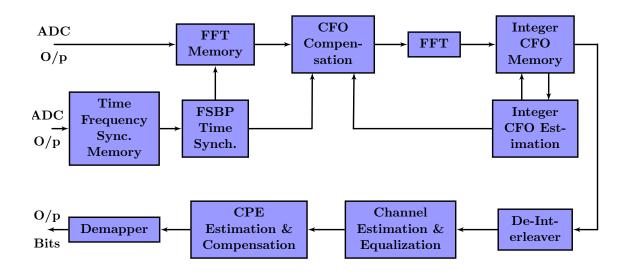

| 4.6<br>4.7 | Plot of Mean of RMSE output of IFFT as function of $W_i$ and $W_t$ Proposed CO-OFDM Receiver Architecture Block Diagram                          | 94<br>95 |

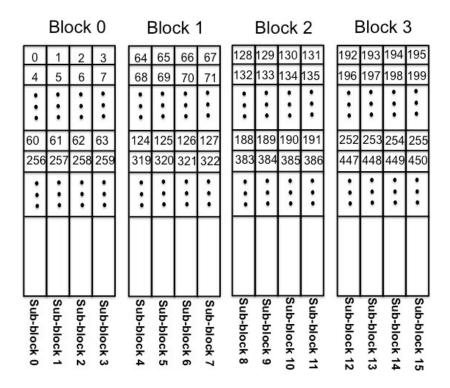

| 4.7        | Data organization in the Synchronization Memory                                                                                                  | 95       |

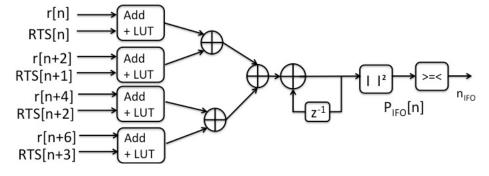

| 4.9        | Parallel Architecture for IFO Estimation                                                                                                         | 96       |

| 4.10       |                                                                                                                                                  | 90       |

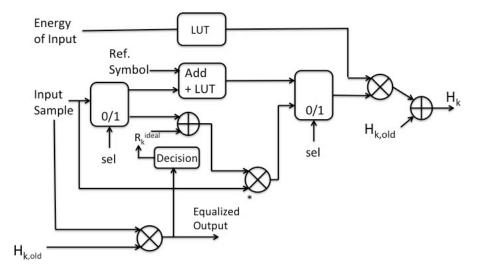

| 4.10       | and NLMS equalizers                                                                                                                              | 98       |

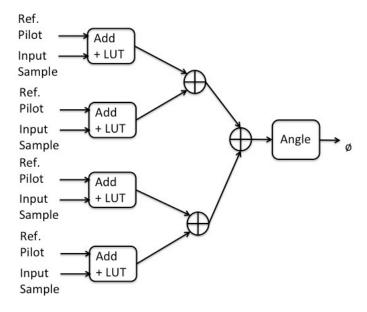

| 4.11       | CPE Estimation Block                                                                                                                             | 98       |

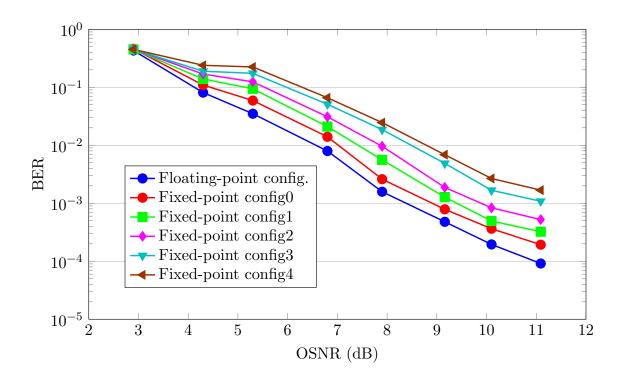

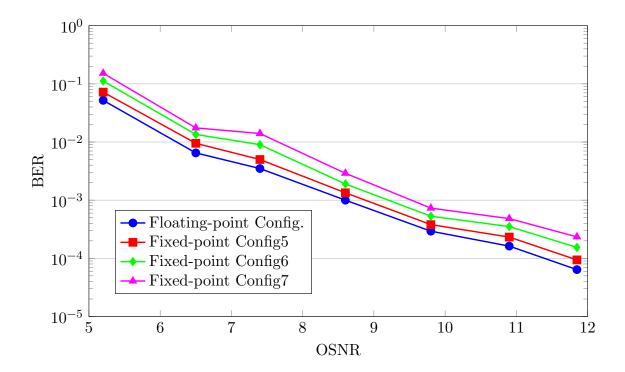

|            | BER vs. OSNR plot for floating-point and various fixed-point configurations                                                                      |          |

|            | in Homodyne setup                                                                                                                                | 100      |

| 4.13       | BER vs. OSNR plot for floating-point and various fixed-point configurations                                                                      |          |

|            | in Heterodyne setup                                                                                                                              | 100      |

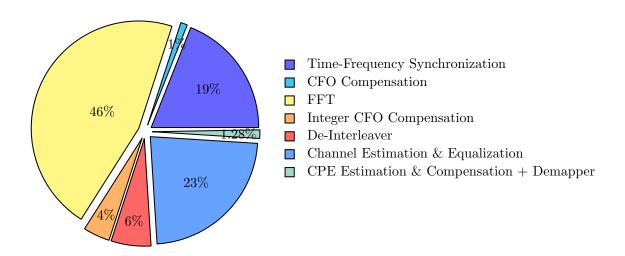

| 4.14       | Pie Chart of area Occupation of all blocks of $R=4$ -Parallel CO-OFDM                                                                            |          |

|            | Receiver (Fixed-point config0)                                                                                                                   | 105      |

| 5.1        | OFDM frame format for single polarization ( $Pol_X$ ) CO-OFDM system                                                                             | 108      |

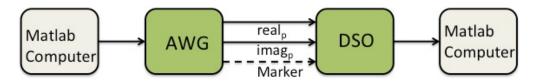

| 5.2        | Configuration of Electrical B2B Experiment. Green blocks indicate analogue                                                                       |          |

|            | blocks                                                                                                                                           |          |

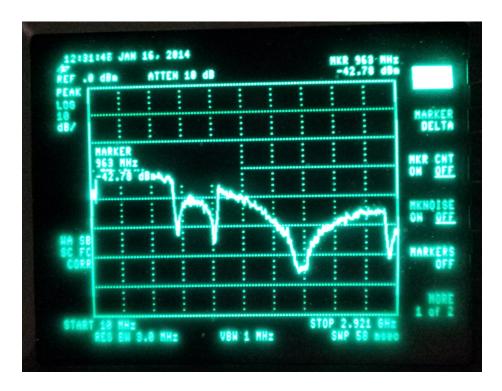

| 5.3        | OFDM Signal Spectrum                                                                                                                             | 111      |

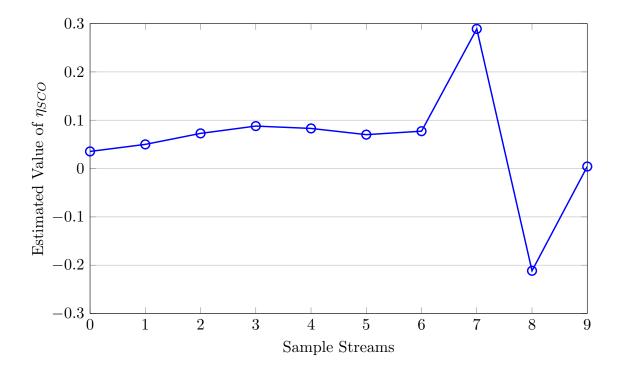

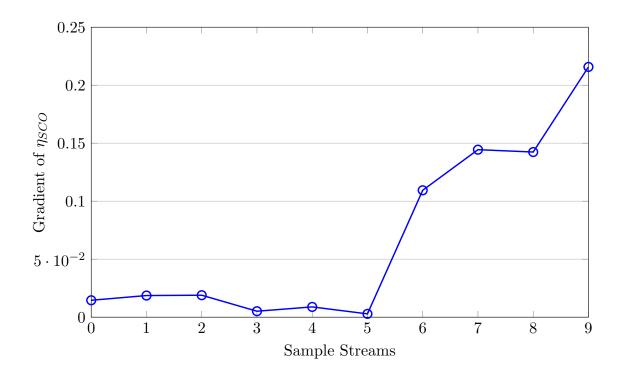

| 5.4        | Estimated Values of $\eta_{SCO}$                                                                                                                 | 111      |

| 5.5        | Gradient of estimated value of $\eta_{SCO}$                                                                                                      |          |

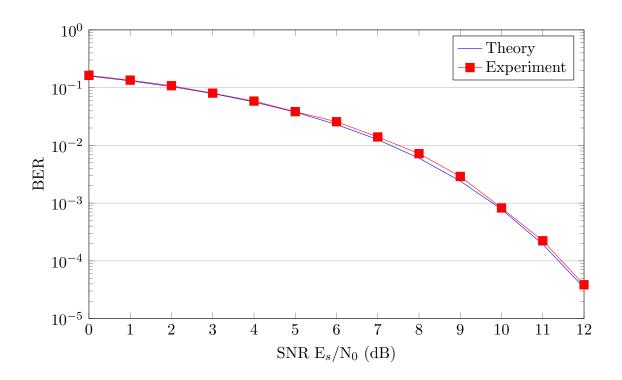

| 5.6        | BER vs SNR for Electrical B2B experiment (Theoretical and Experimental)                                                                          | 113      |

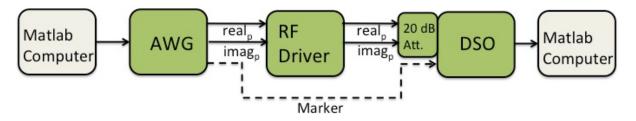

| 5.7        | Configuration of Electrical B2B Experiment with RF Driver. Green blocks                                                                          | 110      |

|            | indicate analogue blocks                                                                                                                         | 113      |

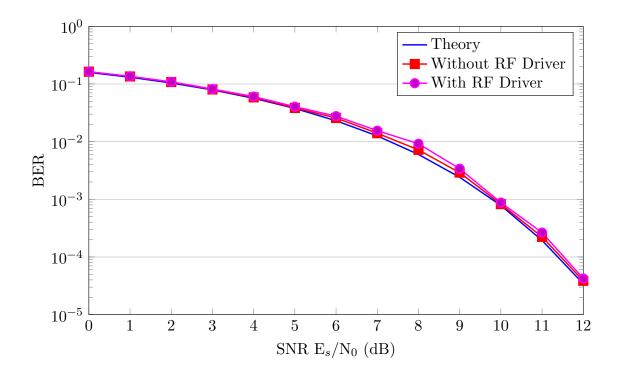

| 5.8        | BER vs SNR for Electrical B2B experiment with RF driver (Theoretical,                                                                            | 111      |

| <b>5</b> O | Experimental with and without RF driver)                                                                                                         | 114      |

| 5.9        | Configuration of Homodyne Coherent Detection. DSP processing is done offline in Matlab. Green blocks indicate analogue blocks. Light Blue blocks |          |

|            | indicate Optical components                                                                                                                      | 114      |

| 5.10       | BER vs SNR for single-band Optical Back-to-Back Experiment                                                                                       |          |

| J. T.      | or or our operous buon to buon inportation                                                                                                       |          |

LIST OF FIGURES xiii

| 5.11 | Configuration of Homodyne Coherent Detection with SMF of 50 km. DSP          |     |

|------|------------------------------------------------------------------------------|-----|

|      | processing is done offline in Matlab. Green blocks indicate analogue blocks. |     |

|      | Light Blue blocks indicate Optical components                                | 117 |

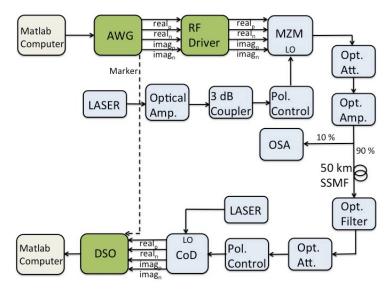

| 5.12 | Configuration of Heterodyne Coherent Detection with standard single mode     |     |

|      | fiber (SSMF) of 50 km. DSP processing is done offline in Matlab. Green       |     |

|      | blocks indicate analogue blocks. Light Blue blocks indicate Optical compo-   |     |

|      | nents                                                                        | 118 |

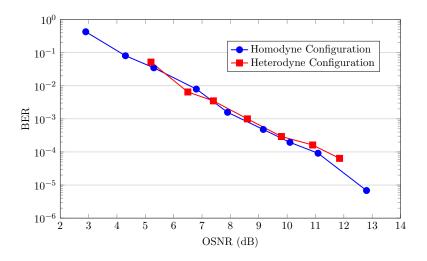

| 5.13 | BER vs SNR for single-band CO-OFDM system for Heterodyne Detection .         | 118 |

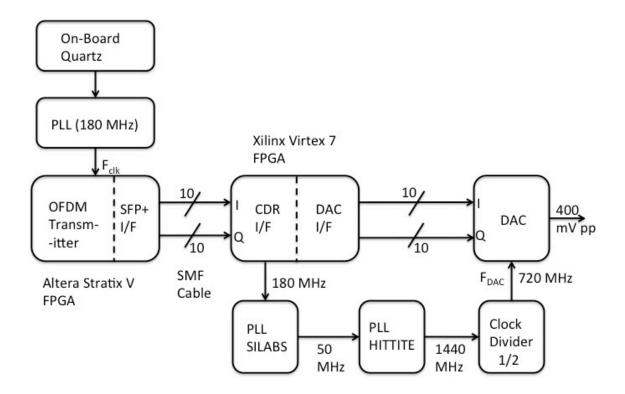

|      | Real-Time FPGA Transmitter Block Diagram. PLL - Phase Locked Loop,           |     |

|      | SFP+ - Enhanced Small Form-factor Pluggable, SMF Cable - Single Mode         |     |

|      | Fiber Cable, I/F - Interface, CDR I/F - Clock Data Recovery Interface,       |     |

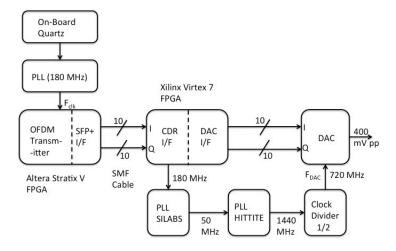

|      | DAC I/F - Digital-to-Analog Converter Interface                              | 119 |

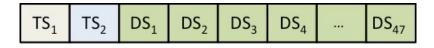

| 5.15 | 100GFLEX Frame Format                                                        |     |

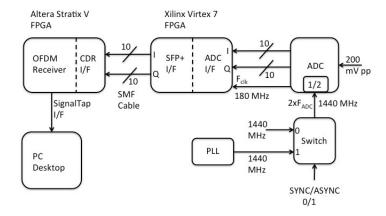

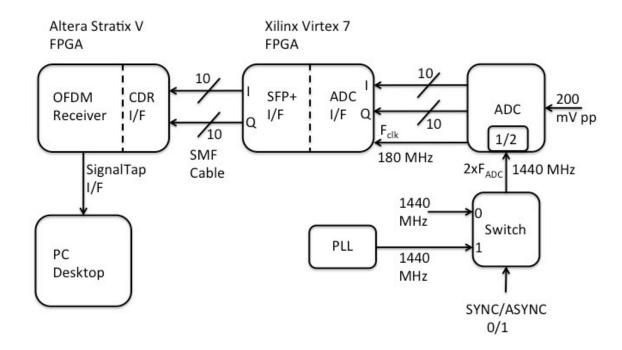

|      | Real-Time FPGA Receiver Block Diagram. ADC - Analog-to-Digital Con-          |     |

|      | verter, I/F - Interface, SFP+ I/F - Enhanced Small Form-factor Pluggable     |     |

|      | Interface, SMF Cable - Single Mode Fiber Cable, CDR I/F - Clock Data         |     |

|      | Recovery Interface, PLL - Phase Locked Loop                                  | 121 |

| 5.17 | Snapshot of Real-Time FPGA Transceiver Platform. The topmost rack            |     |

|      | shows the power supply for the configuration, the second rack is the EKINOPS |     |

|      | Altera FPGA Digital Transceiver, the third rack shows the Xilinx Virtex-7    |     |

|      | FPGA interfaced to DAC board, the bottom most rack shows the other Xil-      |     |

|      | inx Virtex-7 FPGA interfaced to ADC. The yellow cables are single mode       |     |

|      | fiber (SMF) cables to connect using SFP+ interface                           | 122 |

| 5.18 | Altera SignalTap Snapshot of coarse synchronization output. Presence of      |     |

|      | periodic zeros indicate cyclic prefix removal and bigger gap zeros indicate  |     |

|      | the removal of the first training symbol in the output fed into FFT block    | 123 |

| 5.19 | Altera SignalTap Snapshot of coarse synchronization output of OFDM sym-      |     |

|      | bols.Starting from second row, it contains real and imaginary signals alter- |     |

|      | natively. Correctness of the synchronization is verified by observing that   |     |

|      | alternate rows have repeating values indicating correct synchronization is   |     |

|      | achieved                                                                     | 124 |

## List of Tables

| 1    | Nombre d'opérations réelles pour le calcul d'un point de la métrique temporelle                                                                 | 7  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2    | Complexité architecturale en fonction de $R$                                                                                                    | 10 |

| 3    | Complexité architecturale en fonction de $R$                                                                                                    | 11 |

| 4    | Complexité algorithmique pour le calcul de $N$ sorties de la IFFT avec $N{=}256$                                                                | 12 |

| 5    | Complexité algorithmique (auto-corrélation) de notre proposition                                                                                | 12 |

| 6    | Complexité algorithmique de l'estimation CFO entière                                                                                            | 13 |

| 7    | Complexité algorithmique de l'estimation de canal                                                                                               | 14 |

| 8    | Complexité algorithmique de l'estimation et de la compensation CPE                                                                              | 14 |

| 2.1  | DWDM Band Wavelength Range                                                                                                                      | 28 |

| 2.2  | Specifications of commercially available single mode fibers (Corning Fibers)                                                                    | 30 |

| 2.3  | Cost of Optical Transceiver for CO-OFDM, CO-QPSK and IM-DD Systems                                                                              | 40 |

| 2.4  | Algorithmic Complexity in terms of size of IFFT/FFT $N.$                                                                                        | 41 |

| 2.5  | Architectural Complexity of feedforward pipelined IFFT/FFT for 2/4/8-                                                                           |    |

|      | Parallel Outputs as a function of IFFT/FFT size $(N)$ . MDC - Multipath                                                                         |    |

|      | Delay Commutator.                                                                                                                               | 42 |

| 2.6  | Real-time CO-OFDM Transmitter Implementation                                                                                                    | 42 |

| 2.7  | Computational Complexity for CO-OFDM Transmitter                                                                                                | 42 |

| 2.8  | Algorithmic Complexity of Coarse Time Synchronization Algorithms. Calculations count only correlation operation and not the energy calculation. | 43 |

| 2.9  | Architectural Complexity of Coarse Time Synchronization Algorithms                                                                              | 44 |

| 2.10 | ·                                                                                                                                               |    |

|      | number of parallel outputs.                                                                                                                     | 46 |

| 2.11 | Algorithmic/Architectural Complexity for Channel Estimation and Equal-                                                                          |    |

|      | ization. $R$ - number of parallel outputs                                                                                                       | 48 |

| 2.12 |                                                                                                                                                 |    |

|      | sation. $R$ - number of parallel outputs                                                                                                        | 48 |

| 3.1  | Simulation Parameters                                                                                                                           | 57 |

| 3.2  | Number of Real Operations for calculation of a single timing metric point .                                                                     | 60 |

| 3.3  | Simulation Parameters for CO-OFDM System Simulation                                                                                             | 62 |

| 3.4  | Architectural Complexity calculation as a function of $R$ -parallel input/output for SCA                                                        | 71 |

| 3.5  | Architectural Complexity calculation as a function of $R$ -parallel input/output                                                                |    |

|      | for MBA                                                                                                                                         | 73 |

| 3.6  | Architectural Complexity of $P_{sc}$ for FSBP Architecture as a function of                                                                     |    |

|      | R-parallel input/output                                                                                                                         | 75 |

LIST OF TABLES xv

| 3.7   | Architectural Complexity of $P_{mb}$ for FSBP Architecture as a function of                                                                                                                                              | -   |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 9.0   | R-parallel input/output                                                                                                                                                                                                  | 76  |

| 3.8   | Area estimates for 2-Stage Pipelined Adders and Multipliers for 90nm technology node                                                                                                                                     | 77  |

| 3.9   | Area calculation of FSBP (Schmidl-Cox) and Kaneda's architecture at $90nm$ technology node for 5-bit multiplier, 10-bit adder for $R=16$ -Parallel in-                                                                   |     |

| 3.10  | put/output for Schmidl-Cox Algorithm                                                                                                                                                                                     | 79  |

|       | input/output for Schmidl-Cox Algorithm                                                                                                                                                                                   | 79  |

| 3.11  | Conjugate Symmetric Correlation Parallelism Factor achieved on PSPB/FSPE architecture                                                                                                                                    | 80  |

| 4.1   | Calculation of $N_{cyp}$ and $N$ given SMF parameters                                                                                                                                                                    | 85  |

| 4.2   | Algorithmic Complexity for calculation of $N$ output for IFFT size of 256                                                                                                                                                | 86  |

| 4.3   | Algorithmic Complexity (auto-correlation function only) for Proposed Synchronization Algorithm                                                                                                                           | 87  |

| 4.4   | chronization Algorithm                                                                                                                                                                                                   | 88  |

| 4.5   | Algorithmic Complexity for Channel Estimation algorithms                                                                                                                                                                 | 89  |

| 4.6   | Algorithmic Complexity for CPE Compensation                                                                                                                                                                              | 89  |

| 4.7   | Architectural Complexity (normal input order) for full streaming outputs for $N=256$ , with input and output in natural order. Resource count is generated by using SPIRAL tool [4] for radix-2/4/8/16 and using [5] for |     |

|       | $radix-2^2$                                                                                                                                                                                                              | 92  |

| 4.8   | Mean $(\mu)$ and Standard Deviation $(\sigma)$ of RMSE for variation of Bitwidths of inputs/outputs $W_i$ and Twiddle Factor $W_t$                                                                                       | 93  |

| 4.9   | Area Occupied for variation of Bitwidths of inputs/outputs $W_i$ and Twiddle Factor $W_t$                                                                                                                                | 94  |

| 4.10  | Architectural Complexity of Time/Frequency Architecture for $R=4$ -Parallel input/output                                                                                                                                 | 96  |

|       | Look-up table implemented for complex multiplication of conjugate of reference symbol with input $r=a+jb$                                                                                                                | 97  |

|       | Architectural Complexity of IFO Estimation Architecture for $R=4$ -Parallel input                                                                                                                                        | 97  |

|       | Architectural Complexity of Channel Estimator/Equalizer for $R=4$ -Parallel input/output                                                                                                                                 | 97  |

| 4.14  | Architectural Complexity of CPE Estimator and Compensator for $R=4$ -Parallel input/output                                                                                                                               | 99  |

|       | Fixed-point configurations for Homodyne setup                                                                                                                                                                            | 101 |

| 4.16  | BER vs. ONSR for floating-point and various fixed-point configurations in Homodyne setup                                                                                                                                 | 101 |

|       | Fixed-point configurations for Heterodyne setup                                                                                                                                                                          | 102 |

| 4.18  | BER vs. ONSR for floating-point and various fixed-point configurations in                                                                                                                                                |     |

| 4 4 0 | Heterodyne setup                                                                                                                                                                                                         |     |

|       | Area Occupied vs. Bitwidth for Time/Frequency Synchronization block                                                                                                                                                      |     |

|       | Area vs. Bitwidth for CFO Compensation block                                                                                                                                                                             |     |

| 4.21  | Area vs. Bitwidth for FFT block                                                                                                                                                                                          | 103 |

xvi LIST OF TABLES

| 4.22 | Area vs. Bitwidth for Integer CFO Estimation block                                   |

|------|--------------------------------------------------------------------------------------|

| 4.23 | Area vs. Bitwidth for De-interleaver block                                           |

| 4.24 | Area vs. Bitwidth for Channel Estimation & Equalization                              |

| 4.25 | Area vs. Bitwidth for CPE Estimation & Compensation                                  |

| 4.26 | Fixed-Point Allocation and Area for all blocks of the $R=4$ -Parallel Receiver $105$ |

| 5.1  | Parameters of the Electrical B2B Experiment                                          |

| 5.2  | 100GFLEX Frame Format Parameters                                                     |

## List of Abbreviations

**100 GbE** 100 Gigabit Ethernet

ADC Analog to Digital Converter

ASE Amplified Spontaneous Noise

ASIC Application Specific Integrated Circuit

AWG Arbitrary Waveform Generator

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BPF Band Pass Filter

BPSK Binary Phase Shift Keying

CD Chromatic Dispersion

CE Channel Estimation

**CFO** Carrier Frequency Offset

CMZM Complex Mach-Zender Modulator

CO Coherent Optical

CO-DP-QPSK Coherent Optical Dual Polarization QPSK

CO-OFDM Coherent Optical-OFDM

CoD Coherent Detection

CP Cyclic Prefix

**CPE** Common Phase Error

DAC Digital to Analog ConverterDCF Dispersion Compensated Fiber

**DD** Direct Detection

DFT Discrete Fourier TransformDGD Differential Group DelayDP-QPSK Dual Polarization QPSK

DPSK Differential Phase Shift Keying

DSO Digital Storage Oscilloscope

DSP Digital Signal Processing

**DWDM** Dense Wavelength Division Multiplexing

**EB** Eta Bytes  $(10^{18})$

**ECL** External Cavity LASER

**EDC** Electronic Dispersion Compensation

**EDFA** Erbium-Doped Fiber Amplifier

ENOB Effective Number of Bits

EVM Error Vector Magnitude

FEC Forward Error Correction

FFT Fast Fourier Transform

FIR Finite Impulse Response

FPGA Field Programmable Gate Array

**FSF** Frequency Selective Fading

FSM Finite State Machine

FTTH Fiber-to-the-Home

**GB** Giga Bytes  $(10^9)$

GOPS Giga Operations per second

GVD Group Velocity Dispersion

**HLS** High Level Synthesis

ICI Inter Carrier Interference

IDFT Inverse Discrete Fourier Transform

IEEE Institute of Electrical and Electronic

Engineers

IFFT Inverse Fast Fourier Transform

IIR Infinite Impulse Response

IM Intensity Modulation

IM-DD Intensity Modulation-Direct Detection

**ISI** Inter Symbol Interference

ITU International Telecommunication Union

LAN Local Area Network

List of Abbreviations xix

LASER Light Amplification by Stimulated Emission

of Radiation

LD LASER Diode

**LEAF** Large Effective Area Fiber

LMS Least Mean Squares

LO Local Oscillator

LPF Low Pass Filter

LS Least Squares

LTE Long Term Evolution

MAN Metropolitan Area Network

MB Multi-Band

MB-OFDM Multi-band OFDM

MDC Multipath Delay Commutator

MDF Multipath Delay Feedback

MHz Mega Hertz

MIMO Multi Input Multi Output

MLSE Maximum Likelihood Sequence Estimation

MOPS Million of Operations per second

MSE Mean Square Error

MZM Mach-Zender Modulator

N-WDM Nyquist Wavelength Division Multiplexing

NGI CO-OFDM No-Guard Interval CO-OFDM NLMS Normalized Least Mean Square

NRZ Non Return-to-Zero

OBM-OFDM Orthogonal Band Multiplexed OFDM

**OBPF** Optical BPF

OEO Optical-to-Electrical-to-Optical

OFDM Orthogonal Frequency Division Multiplexing

OOK On-Off Keying

OSA Optical Spectrum Analyzer

OSNR Optical Signal to Noise Ratio

PAPR Peak to Average Power Ratio

**PB** Peta Bytes  $(10^{15})$

PBC Polarization Beam Combiner

PBS Polarization Beam Splitter

PCD Polarization Dependent Chromatic

Dispersion

**PD** Photo Diode

PDM Polarization Division Multiplexing

PDM-CO-OFDM Polarization Division Multiplexing-Coherent

Optical-Orthogonal Frequency Division

Multiplexing

PDM-QPSK Polarization Division

Multiplexing-Quadrature Phase Shift Keying

PDR Polarization Diverse Receiver

PMD Polarization Mode Dispersion

PRBS Pseudo Random Bit Sequence

PS Polarization Scrambler

PSCF Pure Silica Core Fiber

PSK Phase Shift Keying

PSP Principle State of Polarization

PSS Primary Synchronization Signal

**QAM** Quadrature Amplitude Modulation

QoS Quality of Service

**QPSK** Quadrature Phase Shift Keying

**RF** Radio Frequency

RGI CO-OFDM Reduced Guard Interval CO-OFDM

RMSE Root Mean Square Error

ROADM Reconfigurable Optical Add Drop

Multiplexer

RS Reed-Solomon

RZ Return-to-Zero

RZ-DQPSK Return-to-Zero Differential Quadratic Phase

Shift Keying

SCO Sampling Clock Offset

SDC Single Path Delay Commutator SDF Single Path Delay Feedback

SNR Signal to Noise Ratio

SOP State of Polarization

List of Abbreviations xxi

SOPMD Second Order PMD

SPM Self Phase Modulation

SQNR Signal Quantization to Noise Ratio

SSMF Standard Single Mode Fiber

$\mathbf{TB}$ Tera Bytes  $(10^{12})$  $\mathbf{TS}$ Training Symbol

ULH Ultra Long Haul

VNI Visual Networking Index VOA Variable Optical Attenuator

WAN Wide Area Network

WDM Wavelength Division Multiplexing

XPM Cross Phase Modulation

**ZF** Zero Forcing

## Chapitre 0

## Résumé étendu

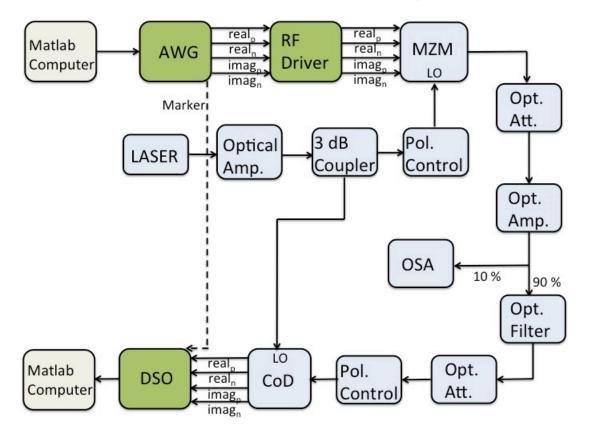

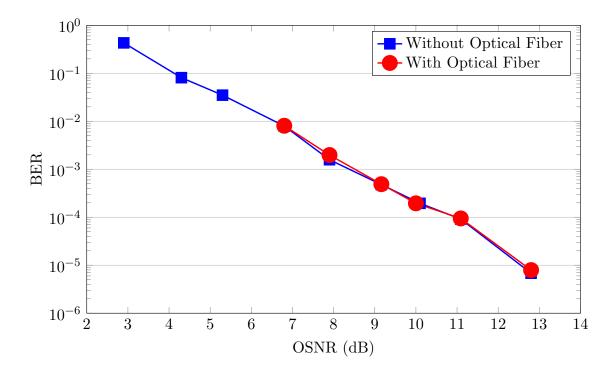

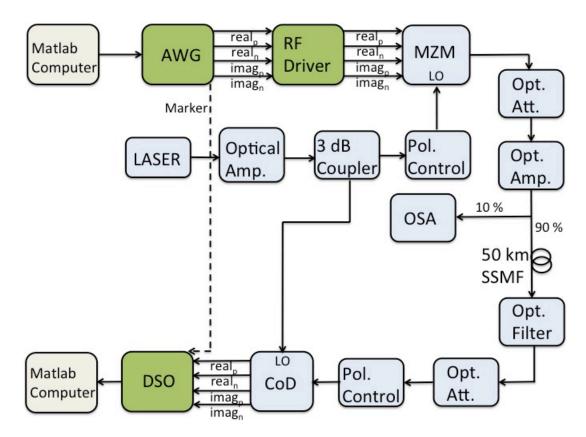

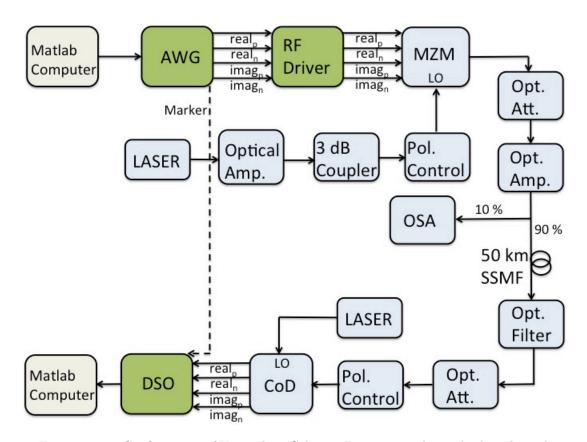

# 0.1 Système de communications optiques OFDM à détection cohérente