### Conception d'architectures d'entrelaceurs parallèles pour les décodeurs de Turbo-Codes et de LDPC

Saeed Ur Reehman

#### ► To cite this version:

Saeed Ur Reehman. Conception d'architectures d'entrelaceurs parallèles pour les décodeurs de Turbo-Codes et de LDPC. Architectures Matérielles [cs.AR]. Université de Bretagne Sud, 2014. Français. NNT: . tel-01096713

### HAL Id: tel-01096713 https://inria.hal.science/tel-01096713

Submitted on 18 Dec 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

THESE / UNIVERSITE DE BRETAGNE-SUD sous le sceau de l'Université européenne de Bretagne pour obtenir le titre de DOCTEUR DE L'UNIVERSITE DE BRETAGNE-SUD Mention : Ecole doctorale SICMA

présentée par Saeed ur REHMAN Préparée au Laboratoire Lab-STICC (UMR n °6285) Université de Bretagne Sud Lorient, France

#### DESIGNING OPTIMIZED PARALLEL INTERLEAVER ARCHITECTURES FOR TURBO AND LDPC DECODERS

#### Thèse soutenue le 24 Septembre, 2014

devant le jury composé de : Emmanuel Casseau (Rennes 1 / ENSSAT) Fabienne Uzel-Nouvel (INSA Rennes) Michel Jezequel (Telecom Bretagne) Christophe Jego (ENSEIRB / IMS) Philippe Coussy (Université de Bretagne Sud / Lab-STICC) Cyrille Chavet (Université de Bretagne Sud / Lab-STICC)

## Acknowledgment

All praises and thanks are for Allah, the Almighty who is the source of all knowledge and wisdom endowed to mankind and to the Holy Prophet Mohammad (Peace Be Upon Him) who showed light of knowledge to the humanity as a whole.

The achievement in this work involves high motivation and supervision of my Ph.D supervisors Philippe COUSSY and Cyrille CHAVET. I am thankful to them for guiding me to complete this thesis as it has been a great privilege working with the researcher of such a caliber. I have learnt a lot from their involvement in my professional as well as personal life. Their originality has triggered and nourished my intellectual maturity which will be beneficial for me forever. Now I can actually sense the beauty behind the research of new approaches. I express my gratefulness to prof. Emmanuel CASSEAU and prof. Fabienne NOUVEL for honoring us by accepting the difficult task of reviewing this thesis.

I would also like to thanks my parents, brothers and wife who motivated and supported me throughout. I would also like to acknowledge all my colleagues at Lab-STICC in France for making my PhD an enjoyable experience. In particular, I'd like to thank my colleague Dr. Awais Hussain SANI for his coordination during my research.

To my friends and family

### **Table of Contents**

| Chapter 1  | INTRODUCTION TO PARALLEL                |    |

|------------|-----------------------------------------|----|

|            | CHITECTURES FOR TURBO AND LDPC CODES    | 3  |

| 1. Introdu | ction                                   | 5  |

| 2. Forward | l Error Correction (FEC) Coding         | 6  |

| 2.1        | Introduction to Turbo Codes             | 7  |

| 2.2        | Introduction to LDPC codes              | 8  |

| 3. Memory  | conflict problem                        | 9  |

| 3.1.       | Memory conflict problem for Turbo Codes | 10 |

| 3.2.       | Memory conflict problem for LDPC Codes  | 11 |

| Chapter 2  | STATE OF THE ART                                       | 11 |

|------------|--------------------------------------------------------|----|

| 1. Introdu | ction                                                  | 17 |

| 2. Avoidin | g conflicts during the code construction               | 17 |

| 3. Solving | conflicts by means of dedicated runtime approaches     | 21 |

| 4. Solving | conflicts with dedicated memory mapping approaches     | 24 |

| 4.1.       | Memory mapping approaches                              | 25 |

| 4.2.       | Architecture for design time memory mapping approaches | 28 |

|            | 4.2.1. In-place memory mapping architecture            |    |

|            | 4.2.2. MRMW architecture                               | 29 |

| 5. Conclus | sion                                                   | 31 |

#### Chapter 3 OPTIMIZED MEMORY MAPPING APPROACH BASED ON NETWORK CUSTOMIZATION

| BASED ON NETWORK CUSTOMIZATION                                    | 33        |

|-------------------------------------------------------------------|-----------|

| 1.Introduction                                                    | 35        |

| 2.Dedicated approach to explore design space of turbo decoder arc | hitecture |

|                                                                   | 35        |

| 2.1.Turbo decoder architecture                                    | 35        |

| 2.2.Proposed design flow                                          | 36        |

| 2.2.1.Shuffled decoding memory issues                             | 37        |

| 2.2.2.Solving memory conflicts                                    | 38        |

| 2.3.Case study: Turbo decoder for LTE                             | 39        |

| 3.Memory mapping approach based on network customization          | 42        |

| 3.1.Proposed Approach                                             | 43        |

| 3.1.1.Memory Mapping with Network Relaxation                      | 43        |

| 3.1.2.Pedagogical Example                                         | 46        |

| 3.2.Experiments and Results                                       |           |

| 3.2.1. Case study for HSPA                                        |           |

| 3.2.2. Case study for LTE                                         | 54        |

| 4.Conclusion                                                      | 55        |

|                                                                   |           |

| <b>OPTIMIZED ARCHITECTURE</b>                                      | 57  |

|--------------------------------------------------------------------|-----|

| 1.Introduction                                                     | 59  |

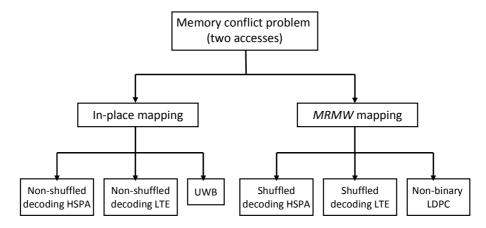

| 2.Two access memory mapping problem                                | 59  |

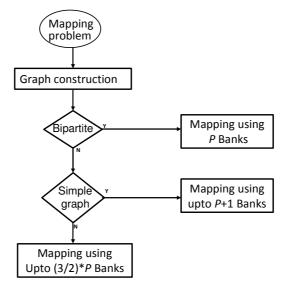

| 2.1.Problem formulation                                            | 60  |

| 3.Design Flow                                                      | 62  |

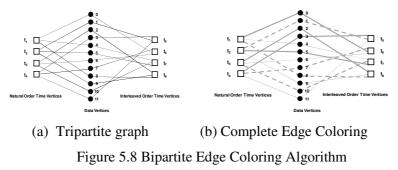

| 3.1.Graph construction                                             | 63  |

| 3.2.Bipartite test                                                 | 64  |

| 3.3.Simple graph test                                              | 66  |

| 3.4. Vizing theorem for edge coloring                              | 67  |

| 3.4.1.Pedagogical Example                                          | 73  |

| 3.5.In-place memory mapping for multigraphs                        | 78  |

| 3.5.1.Modeling                                                     |     |

| 3.5.2.Transformation of bipartite graph into Transportation Matrix |     |

| 3.5.3.Algorithm to find semi 2-factors in Turbo Bipartite Graph    |     |

| 3.5.4.Pedagogical Example                                          | ~ = |

| 4.Experiments and results                                          | 87  |

| 4.1.Case study-1: Shuffled turbo decoders for LTE                  | 87  |

| 4.2.Case study-2: Non-Binary LDPC codes                            |     |

| 4.2.1.Vizing theorem for non-binary LDPC codes                     |     |

| 4.2.2.Results                                                      | 90  |

| 4.3.Case study-3: Shuffled turbo decoding for HSPA                 | 92  |

| 5.Conclusion                                                       | 93  |

# Chapter 5 ON-CHIP IMPLEMENTATION OF MEMORY MAPPING ALGORITHM TO SUPPORT FLEXIBLE DECODER ARCHITECTURE

|                                                       | 95  |

|-------------------------------------------------------|-----|

| 1.Introduction                                        | 97  |

| 2.On-chip implementation of memory mapping algorithms | 97  |

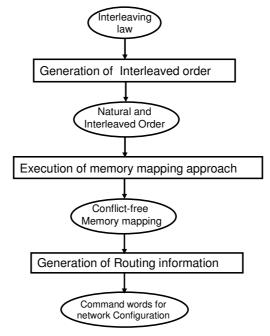

| 2.1.Proposed Design flow                              | 98  |

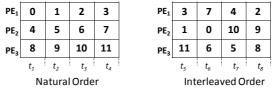

| 2.2. Generation of data access order                  | 99  |

| 2.3.Execution of memory mapping approach              | 104 |

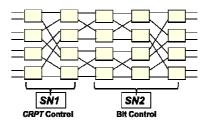

| 2.4.Routing Algorithm                                 | 106 |

| 2.4.1.Example for Routing Algorithm                   | 108 |

| 3.Experiments                                         | 109 |

| 4.Conclusion                                          | 112 |

| Conclusion and Future Perspectives                    | 113 |

| Bibliography                                          | 115 |

| Abbreviations                                         | 123 |

|                                                       |     |

## **List of Figures**

| Figure 1.1 A generic digital communication system                                                 | 5   |

|---------------------------------------------------------------------------------------------------|-----|

| Figure 1. 2. Turbo encoder                                                                        |     |

| Figure 1. 3. Turbo decoder                                                                        |     |

| Figure 1. 4. Taner graph representation of H matrix                                               | 9   |

| Figure 1. 5. Typical Parallel Architecture                                                        |     |

| Figure 1. 6. Data access matrices for turbo codes                                                 |     |

| Figure 1. 7. Memory Conflict Problem in Parallel Turbo Decoder                                    |     |

| Figure 1. 8. Memory Conflict Problem in Partially Parallel LDPC Decoder                           |     |

| Figure 2. 1. Interleaver construction                                                             |     |

| Figure 2. 2. Interleaver matrix                                                                   | 19  |

| Figure 2. 3. Tanner graph formalization of an LDPC H-matrix                                       |     |

| Figure 2. 4. Structured LDPC codes                                                                | 20  |

| Figure 2. 5. Architecture based on LLR Distributor                                                | 21  |

| Figure 2. 6. Architecture based on Double buffer                                                  |     |

| Figure 2. 7. Architecture based on NoC                                                            | 23  |

| Figure 2. 8. Parallel architecture with multistage network                                        | 24  |

| Figure 2. 9. Matrices used in SAGE                                                                | 25  |

| Figure 2. 10. Multiple Read Multiple write (MRMW) approach                                        | 26  |

| Figure 2.11. Me Resulting architecture with additional registers and steering logic for Memo      |     |

| relaxation based approach                                                                         | 27  |

| Figure 2.12. In-place mapping                                                                     | 29  |

| Figure 2.13. Resultant In-place mapping architecture                                              | 29  |

| Figure 2.14. MRMW mapping                                                                         | 30  |

| Figure 2.15. MRMW architecture                                                                    | 30  |

| Figure 3. 1 Decoding Architecture for Turbo Decoders                                              |     |

| Figure 3. 2 Integrated design flow for Turbo decoder architectures exploration                    |     |

| Figure 3. 3 Scheduling for Turbo Decoding                                                         | 39  |

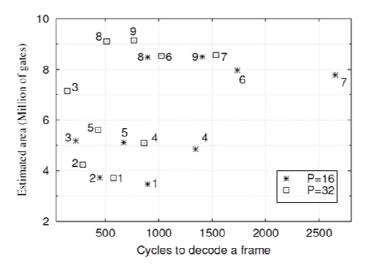

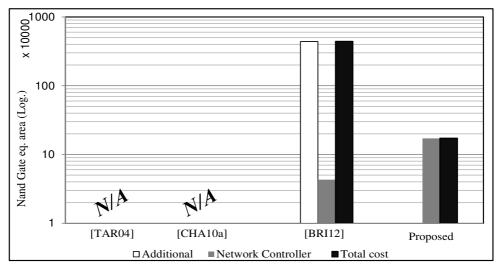

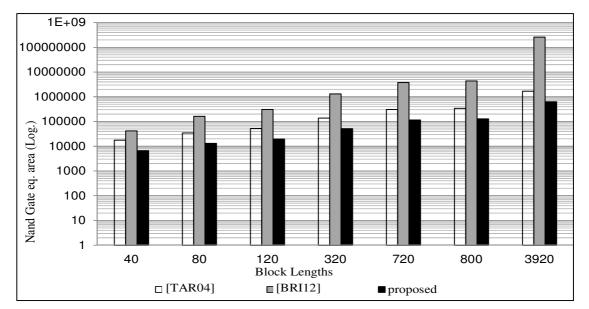

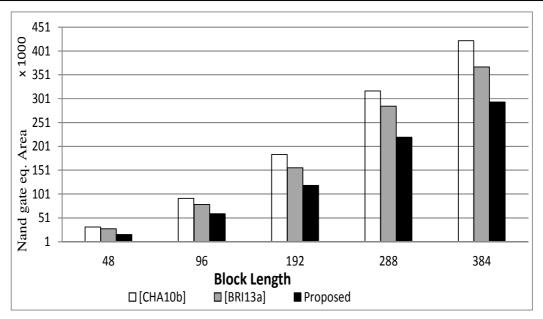

| Figure 3. 4 Area estimations of the considered configurations                                     | 41  |

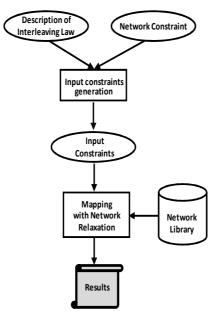

| Figure 3. 5. Proposed Memory Mapping Exploration Flow for Network Relaxation Approach             | 43  |

| Figure 3. 6. Memory Mapping model                                                                 | 44  |

| Figure 3. 7. Mapping algorithm with network relaxation                                            | 45  |

| Figure 3. 8. Network customization                                                                | 46  |

| Figure 3. 9 Barrel shifter                                                                        |     |

| Figure 3. 10 Mapping with BS                                                                      | 47  |

| Figure 3. 11 Network relaxation with BS                                                           |     |

| Figure 3. 12 Network relaxation without any NW constraint                                         | 48  |

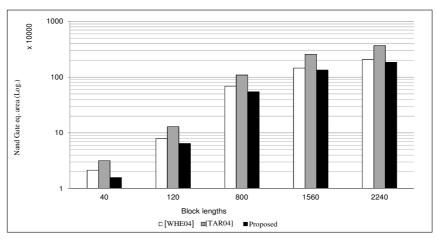

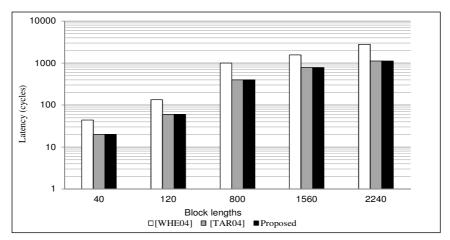

| Figure 3. 13 Comparison of HSPA Network Controllers Areas obtained with state of art approach     | hes |

| and Network Relaxation approach                                                                   |     |

| Figure 3. 14 Comparison of HSPA Network Controllers latencies obtained with state of art approach | hes |

| and Network Relaxation approach                                                                   |     |

| Figure 3. 15. Detailed comparison of HSPA Network Controllers Areas obtained with state of        | art |

| approaches and Network Relaxation approach (L=2240, P=4, Targeted network: Barrel Shifter)        | 50  |

| Figure 3. 16 Detailed comparison of HSPA Network Controllers Areas obtained with state of         | art |

| approaches and Network Relaxation approach (L=800, P=8, Targeted network: Barrel Shifter)         | 51  |

| Figure 3. 17. Detailed comparison of HSPA Network Controllers Areas obtained with state         | of art |

|-------------------------------------------------------------------------------------------------|--------|

| approaches and Network Relaxation approach (L=2240, P=4, No targeted network)                   | 52     |

| Figure 3. 18 Detailed comparison of HSPA Network Controllers Areas obtained with state          | of art |

| approaches and Network Relaxation approach (L=800, P=8, No targeted network)                    | 52     |

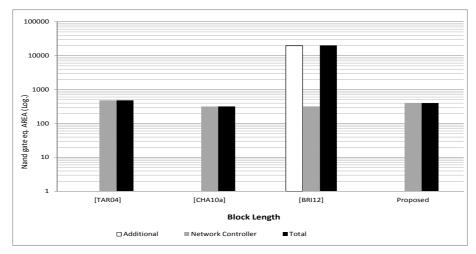

| Figure 3. 19. Comparison of HSPA decoder architecture estimated areas obtained with state       | of art |

| approaches and Network Relaxation approach for different block lengths (P=4)                    |        |

| Figure 3. 20. Comparison of HSPA decoder architecture estimated areas obtained with state       |        |

| approaches and Network Relaxation approach for different block lengths (P=8)                    | 53     |

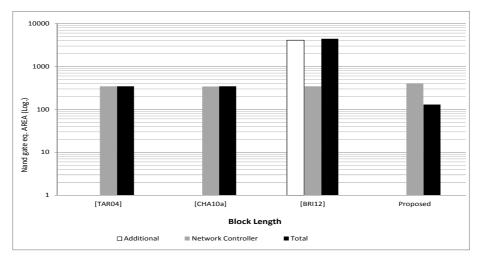

| Figure 3. 21. Parallel architecture with multistage network                                     |        |

| Figure 3. 22. Comparison of LTE decoder architecture estimated areas obtained with state of art |        |

| Approache and Network Relaxation approach for different block lengths (P=4)                     | 55     |

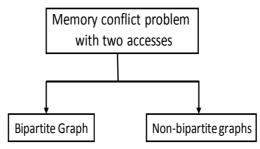

| Figure 4.1 Solution for memory conflict problems                                                | 60     |

| Figure 4.2 Categories in two access problem                                                     | 61     |

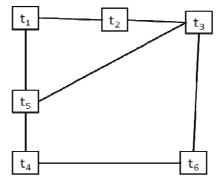

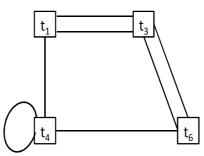

| Figure 4.3 Simple graph                                                                         | 61     |

| Figure 4.4 Multi-graph                                                                          | 62     |

| Figure 4.5 Design flow                                                                          | 63     |

| Figure 4.6 Example of data access matrix with two accesses to each data                         | 64     |

| Figure 4.7 General Graph for edge coloring                                                      | 64     |

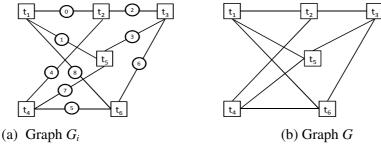

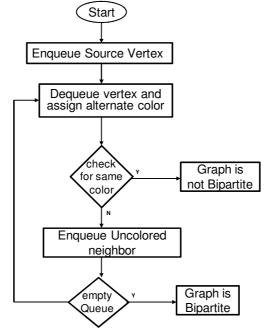

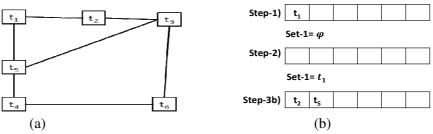

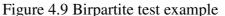

| Figure 4.8 Bipartite test                                                                       | 65     |

| Figure 4.9 Birpartite test example                                                              |        |

| Figure 4.10 Simple Graph test                                                                   | 66     |

| Figure 4.11 Simple graph test example                                                           | 67     |

| Figure 4.12 Edge coloring flow based Vizing theorem (up to <i>P</i> +1 colors)                  | 67     |

| Figure 4.13 Vizing fan                                                                          | 68     |

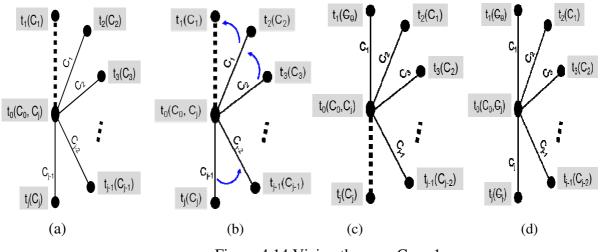

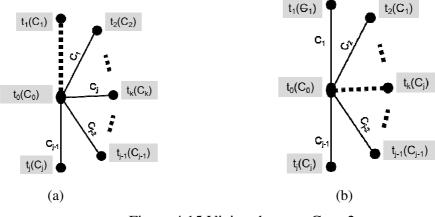

| Figure 4.14 Vizing theorem Case-1                                                               | 70     |

| Figure 4.15 Vizing theorem Case-2                                                               |        |

| Figure 4.16 Vizing theorem Case-2a                                                              |        |

| Figure 4.17 Vizing theorem Condition for Case-2b                                                | 72     |

| Figure 4.18 Vizing theorem Case-2b                                                              | 72     |

| Figure 4.19 Vizing theorem Case-2b final                                                        | 73     |

| Figure 4.20 Example for Vizing theorem                                                          |        |

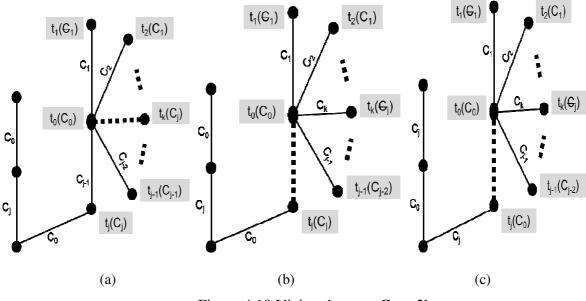

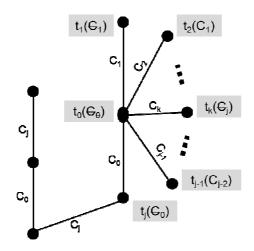

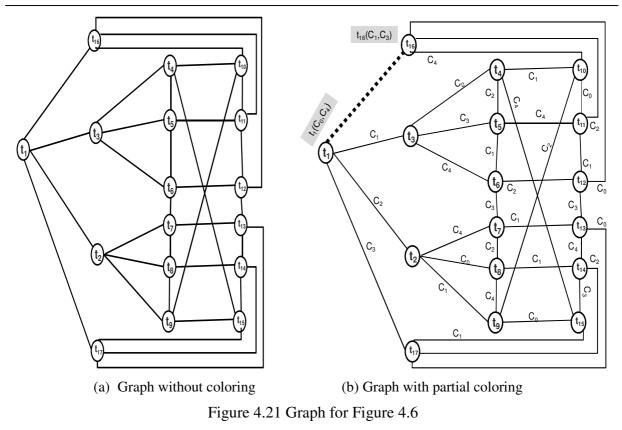

| Figure 4.21 Graph for Figure 4.6                                                                |        |

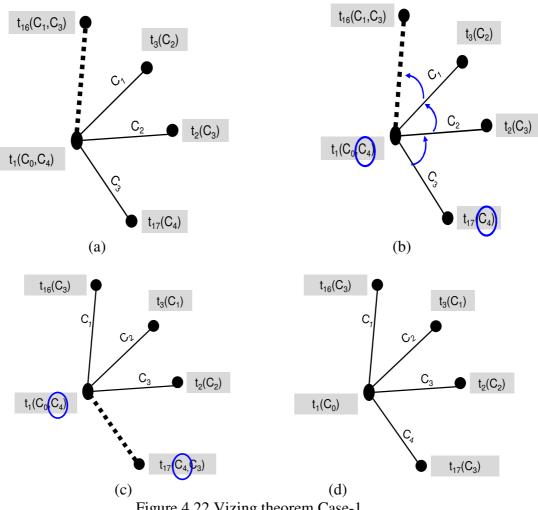

| Figure 4.22 Vizing theorem Case-1                                                               |        |

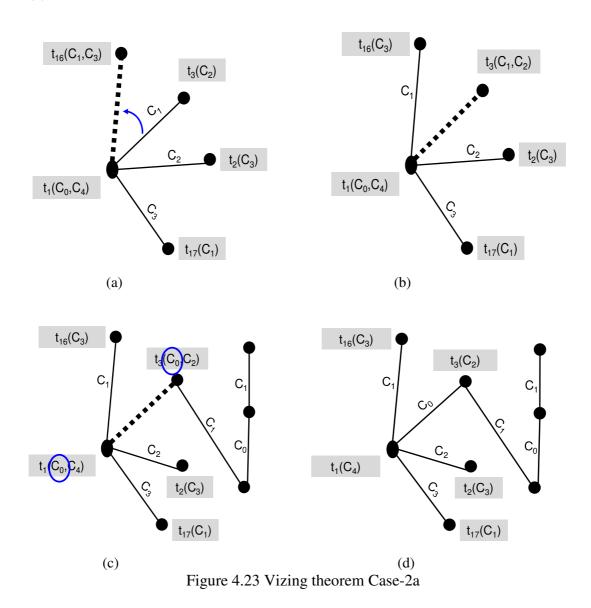

| Figure 4.23 Vizing theorem Case-2a                                                              |        |

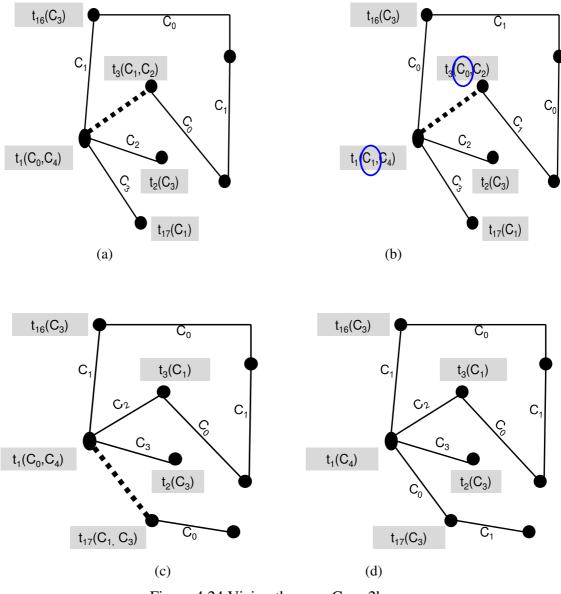

| Figure 4.24 Vizing theorem Case-2b                                                              |        |

| Figure 4.25 Resultant in-place architecture                                                     |        |

| Figure 4.26 Example resulting a multigraph                                                      |        |

| Figure 4.27 Bipartite Graph for example of Figure 4.26                                          |        |

| Figure 4.28 Partitioning algorithm                                                              |        |

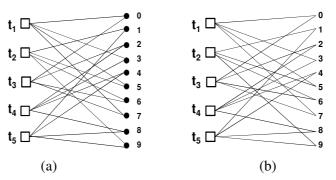

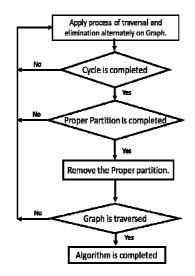

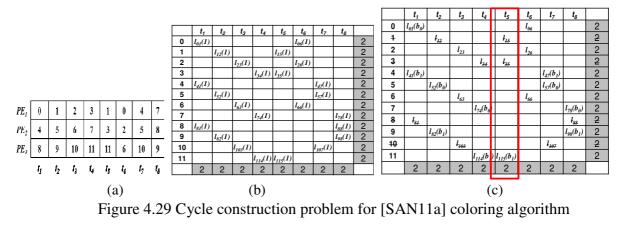

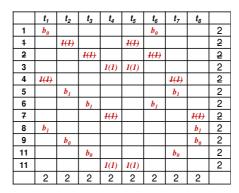

| Figure 4.29 Cycle construction problem for [SAN11a] coloring algorithm                          |        |

| Figure 4.30 Resulting cycle obtained with proposed cycle construction approach                  |        |

| Figure 4.31 Approach based on transportation problem (part-1)                                   |        |

| Figure 4.32 Approach based on transportation problem (part-2)                                   |        |

| Figure 4.33 Mapping based on transportation problem                                             |        |

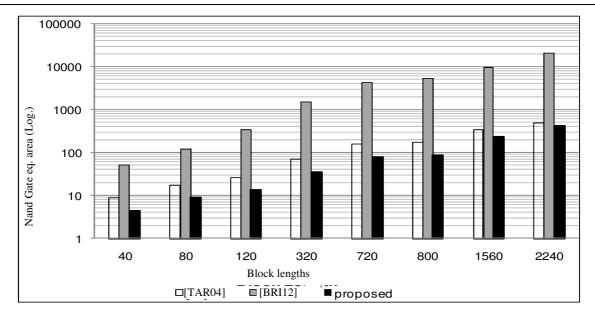

| Figure 4.34 Area comparison for shuffled turbo decoders with P=16                               |        |

| Figure 4.35 Architecture for NB-LDPC                                                            |        |

| Figure 4.36 Data Access Matrix for L = 192 and dc = 6                                           | 89     |

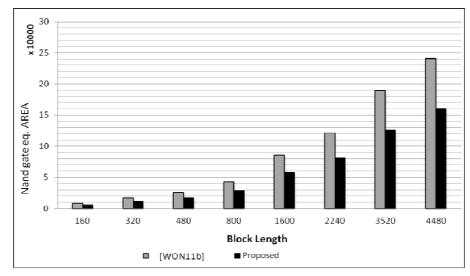

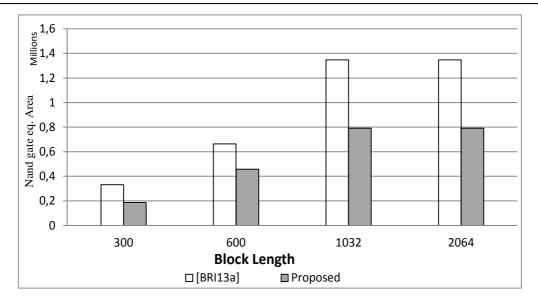

| Figure 4.37 Comparison of NB_LDPC decoder areas obtained with state of art approaches and Vizing |

|--------------------------------------------------------------------------------------------------|

| coloring for different block length ( $P = 6$ )                                                  |

| Figure 4.38 Comparison of NB_LDPC decoder areas obtained with state of art approaches and Vizing |

| coloring for different block length ( $P = 12$ )                                                 |

| Figure 4.39 Area comparison for different block length for HSPA $P = 16$ (best results)          |

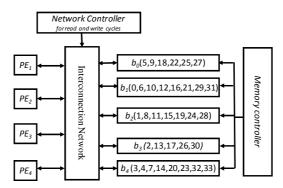

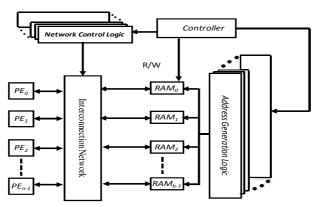

| Figure 5.1 Parallel decoder architecture                                                         |

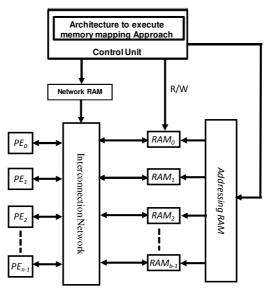

| Figure 5.2 Parallel decoder architecture to embed memory mapping algorithms on chip              |

| Figure 5.3 Embedded conflict free memory mapping flow                                            |

| Figure 5.4 Arrangement of $L = 44$ data into 5*10 matrix                                         |

| Figure 5.5 Matrix after Intra-row Permutation                                                    |

| Figure 5.6 Matrix after Inter-row Permutation                                                    |

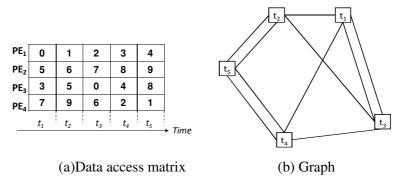

| Figure 5.7 Data access matrix                                                                    |

| Figure 5.8 Bipartite Edge Coloring Algorithm                                                     |

| Figure 5.9 SN1 and SN2 for the routing algorithm 106                                             |

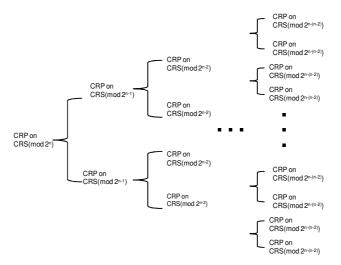

| Figure 5.10 A Complete Residue Partition Tree (CRPT) 107                                         |

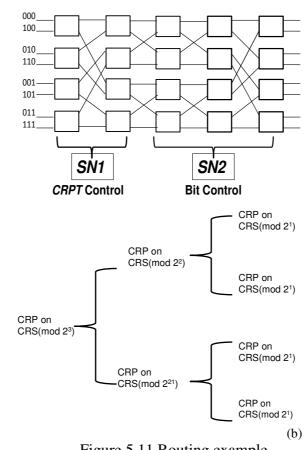

| Figure 5.11 Routing example 108                                                                  |

| Figure 5.12 Example with complete routing tags                                                   |

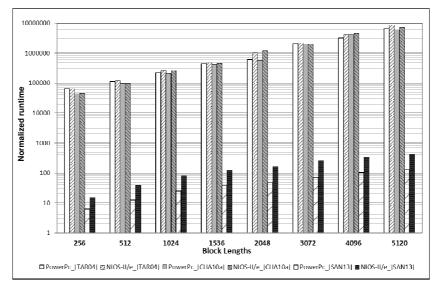

| Figure 5.13 Normalized Run time Values for different embedded processors with PE = 32 110        |

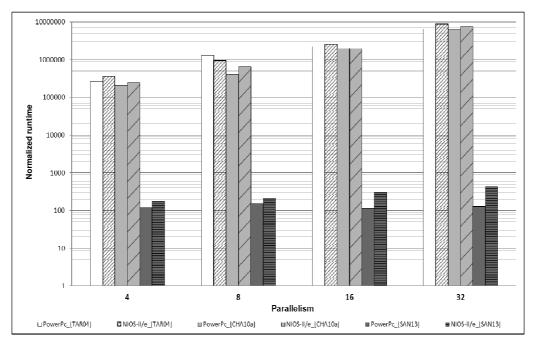

| Figure 5.14 Normalized Run time Values of for different types of parallelism with L=5120 111     |

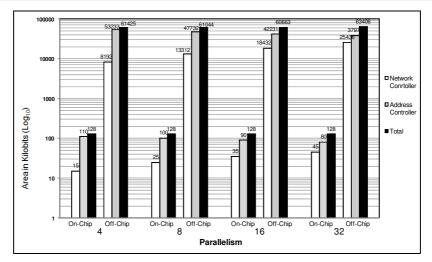

| Figure 5.15 Area Comparison of on-chip and off-chip implementation for different P 112           |

## **List of Tables**

| Table 3. 1. Interconnection network area                                           | 40  |

|------------------------------------------------------------------------------------|-----|

| Table 3. 2. Different configuration to explore the design space for turbo decoding | 4   |

| Table 3. 3. Cost calculation                                                       | 41  |

| Table 3. 4. Permutations after adding network component with BS                    | 47  |

| Table 3. 5. Block lengths supported by BS                                          | 54  |

| Table 4. 1: Different configuration to explore the design space for turbo decoding | 87  |

| Table 5. 1. List of prime number p and associated primitive root v                 | 100 |

| Table 5. 2. Turbo code interleaver parameters                                      | 103 |

## ABSTRACT

We live in the era of high data rate wireless applications (smart-phones, net-books, digital television, mobile broadband devices...) in which advanced technologies are included such as OFDM, MIMO and advanced error correction techniques to reliably transfer data at high rates on wireless networks. Turbo and LDPC codes are two families of codes that are extensively used in current communication standards due to their excellent error correction capabilities. For high throughput performance, decoders are implemented on parallel architectures in which more than one processing elements decode the received data. However, parallel architectures suffer from *memory conflict problem*. It increases latency of memory accesses due to the presence of conflict management mechanisms in communication network and unfortunately decreases system throughput while augmenting system cost.

To tackle memory conflict problem, three different types of approaches are used in literature. In first type of approaches, "architecture friendly" codes are constructed with good error correction capabilities in order to reduce hardware cost. However, these codes originate problem at the channel interleaver. In the second type of approaches, flexible and scalable interconnection network are introduced to handle memory conflicts at run time. However, flexible networks suffer from large silicon area and increased latency. The third type of approaches are design time memory mapping approaches in which the resultant architectures consist of ROM blocks used to store configuration bits. The use of ROM blocks may be sufficient to design parallel architecture that supports single codeword or single application. However, to design hardware architecture that supports complete standard or different applications, ROM based approaches result in huge hardware cost. To reduce hardware cost, optimizations are required to use as less ROMs as possible to support different applications.

In this thesis, we aim to design optimized parallel architectures. For this purpose, we have proposed two different categories of approaches. In the first category, we have proposed two optimized design time off-chip approaches that aim to limit the cost of final decoder architecture targeting the customization of the network and the use of in-place memory architecture.

In the second category, we have introduced a new method in which both runtime and design time approaches are merged to design flexible decoder architecture. For this purpose, we have embedded memory mapping algorithms on-chip in order to execute them at runtime to solve conflict problem. The on-chip implementation replaces the multiple ROM blocks

with a single RAM block to support multiple block lengths and/or to support multiple applications. Different experiments are performed by executing memory mapping approaches on several embedded processors.

# Chapter 1

# INTRODUCTION TO PARALLEL ARCHITECTURES FOR TURBO AND LDPC CODES

| Table of  | Contents                                |    |

|-----------|-----------------------------------------|----|

| 1. Introd | uction                                  | 5  |

| 2. Forwa  | rd Error Correction (FEC) Coding        | 6  |

| 2.1       | Introduction to Turbo Codes             | 7  |

| 2.2       | Introduction to LDPC codes              | 8  |

| 3. Memo   | ry conflict problem                     | 9  |

| 3.1.      | Memory conflict problem for Turbo Codes | 10 |

| 3.2.      | Memory conflict problem for LDPC Codes  | 11 |

In this chapter, error correction codes are discussed. Error correction codes can be classified into two broad categories: convolutional codes and block codes. Parallel hardware architecture is needed to support high throughput. Memory conflict problems which occur in parallel architectures implementation are introduced to highlight the importance of the work presented in this thesis.

#### **1. Introduction**

Wireless communication is undoubtedly one of the major research areas in telecommunication today. Broad progress can be observed in this field in the past decade, although it has been a topic of study since 1960s. The ongoing goal of providing enhanced services seamlessly and effectively continues to drive wireless communications. We have seen the outcomes in the form of cellular systems that have experienced exponential growth over the last decade with billions of customers worldwide. Incorporation of multimedia and value added services in telecommunication have dramatically increased data rate requirements.

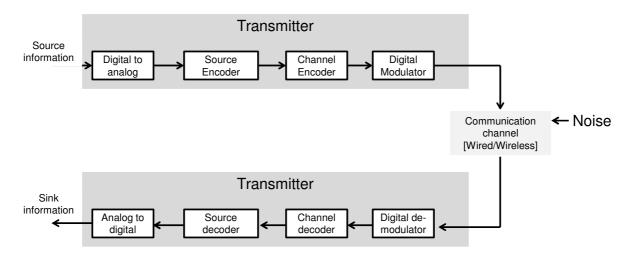

Figure 1.1 A generic digital communication system

A generic digital communication system is shown in Figure 1. 1. The block diagram consists of building blocks each performing a certain well-defined operation on data. The transmitter transforms the signals from information source to the channel. The transmitter consists of blocks namely *Digital to analog converter*, *Source Encoder*, *Channel Encoder and Digital modulator*. *Digital to analog converter* converts the input information source into binary digits (bits), groups them together to form digital messages. *Source Encoder* tries to increase the information content of source symbols by removing the redundant information and encoding the source data using fewer bits than uncoded information. *Channel encoding* can reduce the errors rates at the expense of decoder complexity. Starting from *K* bits the channel encoder provides a codeword *c* of length *N* by adding N - K redundant bits. By means of introduced redundancy, the channel decoder is able to identify errors introduced by channel and correct some of them. *Digital Modulator* is a block that facilitates the transfer of information over a passband channel. In digital modulation, an analog carrier is modulated by a digital bit stream. Based on a particular application and channel condition, different

modulation techniques can be adopted, e.g. Phase Shift Keying (PSK), Frequency Shift Keying (FSK), Amplitude Shift Keying (ASK) and Quadrature Amplitude Modulation (QAM)

The received channel information is transformed by the receiver to the sink information. The receiver consists of several blocks namely *Digital Demodulator, Channel Decoder, Source Decoder and Analog to digital converter. Digital Demodulator* takes the signal received from the Channel and converts it into digital data. *Channel Decoder* receives the decoded data from digital demodulator to detect errors introduced by Channel, corrects them and then it removes the redundant bits and extracts information words of *K* bits. *Source Decoder* performs the reverse operation of *Source Encoder* retrieving the same information as generated by information source along with *Analog to digital conveter*.

The channel encoder and decoder are responsible for the reliable transfer of data for which forward error correction (*FEC*) codes are widely used. *FEC* codes are among the significant parts of the whole system. *FEC* codes are described in the next section.

#### 2. Forward Error Correction (FEC) Coding

We are now moving through the 4<sup>th</sup> generation of wireless communication systems which are expected to achieve high data rates and reliable data transfer. Since error correction is one of the complex and power consuming part of whole transceiver design, therefore extensive research was carried out in the field of channel coding especially Forward Error Correction (FEC). Research in the field of *FEC* codes is aimed to find the best possible error correcting codes allowing high throughput decoding and their efficient VLSI implementation in term of area, speed and power consumption.

*FEC* codes can be classified into two categories: *Block codes* and *Convolutional codes*. *Convolutional codes* are increasingly used in different telecommunication standards due to their simple and efficiently implementable structures. Currently, convolutional codes are part of standards for mobile communication (HSPA [HSP04], LTE [LTE08]) and digital broadcasting (DVB-SH [DVBS08]). Convolutional codes work as a finite state machine which converts continuous stream of bits into continuous stream of coded bits.

In block codes, original information sequence is first divided into different blocks and then each block is independently encoded to generate code-word bits. The encoder must wait for the whole message block before starting the encoding step. However, in convolutional encoder the code-word is transmitted as soon as encoding is started without any wait to obtain the entire message.

Two main error correcting codes families are used in current telecommunication standards. One from convolutional codes called Turbo codes and another from block codes called Low Density Parity Check (LDPC) codes. These two error correcting codes are widely used due to their excellent error correcting capabilities. However, implementation of decoders for these two codes for high data rate applications is a challenging task. In this thesis, we focus on the implementation of both of these codes on parallel architectures.

#### 2.1 Introduction to Turbo codes

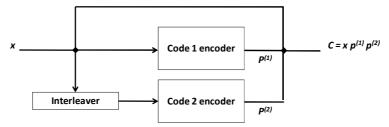

Due to their excellent error correction capabilities, Turbo codes [BER93] are part of most of the current telecommunication standards such as [LTE08] [HSP04] [DVBS08]. They are constructed through the parallel concatenation of two "simple" convolutional codes that share their information during the decoding step. The first convolution encoder encodes the message x in natural (original) order to produce  $p^{(1)}$  parity bits, whereas the second one encodes the message in interleaved order (after passing the original message through interleaver) to generate  $p^{(2)}$  parity bits. The output turbo codeword c is composed of the original message and parallel concatenation of parity bits.

#### Figure 1. 2. Turbo Encoder

The high performances of turbo codes are due to the presence of this pseudo-random interleaver. Interleaving ( $\Pi$ ) is a permutation law that scrambles data to break up neighbourhood-relations. It is a key factor for turbo-codes performances, which vary from one standard to another. The low-complexity iterative decoding algorithm for turbo-decoding makes its hardware implementation possible with the current standards. However, in order to achieve high throughput architectures, we will see that this interleaver generates memory access conflicts when parallel architectures are used.

Figure 1. 3. Turbo Decoder

The turbo decoder receives input values  $Y^{(u)}$ ,  $Y^{(1)}$ ,  $Y^{(2)}$  from the channel (resp. for *x*,  $p^{(1)}$ ,  $p^{(2)}$ ). One complete iteration of turbo decoder is carried out through two half iterations. Firstly *Code 1 Decoder* receives channel values for message bit  $Y^{(u)}$ , first parity bit  $Y^{(1)}$  and deinterleaved extrinsic value from *Code 2 Decoder* to generate extrinsic value. Then, during the second half iteration, *Code 2 Decoder* creates extrinsic value from interleaved message bits, second parity bit  $Y^{(2)}$  and interleaved extrinsic value from *Code 1 Decoder*. The final decision about the message bits is made based on the extrinsic values from the two decoders and channel values for message bits, after a fixed number of decoding iterations.

#### 2.2 Introduction to LDPC codes

Low density parity check Codes (LDPC) are another class of very high performances error correction codes. They are members of the class of Block codes that are used to transmit information reliably through noisy communication channels. Many types of block codes are used in different applications such as Reed-Solomon [AHA], Golay codes [GOL61] or Hamming codes [HAM50]. LDPC codes have already been included in several wireless communication standards such as DVB-S2 and DVB-T2 [DVB08], WiFi (IEEE 802.11n) [WIF08] or WiMAX (IEEE 802.16e) [WIM06].

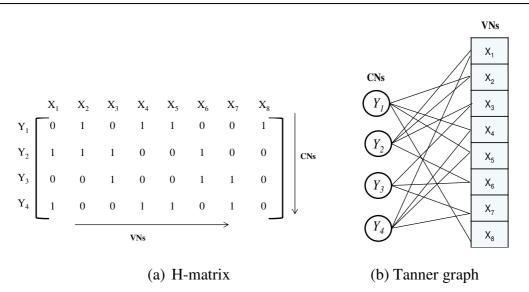

The code is represented with parity check equations. As a pedagogical example, consider a codeword:  $C = [c_1 \ c_2 \ c_3 \ c_4]$  which satisfies the following three parity check equations.

$c_2 \oplus c_3 \oplus c_4 = 0,$   $c_1 \oplus c_2 \oplus c_4 = 0,$  $c_1 \oplus c_3 \oplus c_4 = 0$  In a LDPC code, codeword constraints (or parity check equations) are often expressed in matrix form as follows:

$$\begin{pmatrix} 0 & 1 & 1 & 1 \\ 1 & 1 & 0 & 1 \\ 1 & 0 & 1 & 1 \end{pmatrix} \begin{pmatrix} c_1 \\ c_2 \\ c_3 \\ c_4 \end{pmatrix} = \begin{pmatrix} 0 \\ 0 \\ 0 \end{pmatrix}$$

The above H matrix is an M \* N binary matrix where each row  $M_i$  of H corresponds to a parity check equation whereas each column  $N_j$  associated with codeword bit. A nonzero entry at  $(i, j)^{\text{th}}$  location means that the  $j^{\text{th}}$  codeword bit is included in the  $i^{\text{th}}$  parity check equation. For a codeword  $x \in C$  to be valid, it must satisfy all parity check equations.

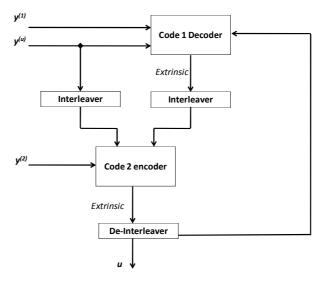

LDPC codes can also be graphically represented as bipartite graph called *Tanner Graphs*. Such graphs depict the association between code (represented by variable nodes *VN*) bit and parity check equation (represented by check nodes *CN*). An edge  $e_{ij}$  connects the  $i^{th}$  check node with  $j^{th}$  variable node, if this variable node is checked by or included in  $i^{th}$  check node. This means that the edges of a Tanner graph are constructed with respect to the H matrix.

Figure 1. 4. Tanner Graph representation of H

Tanner graph is helpful in understanding the decoding process that exchanges messages between CN and VN ( $Mes_{c\rightarrow\nu}$  or  $Mes_{\nu\rightarrow c}$ ) along the edges of these graphs. These decoding algorithms are collectively called message-passing algorithms. They are a type of iterative decoding algorithm in which check nodes and variable nodes iteratively exchange messages until decoding is completed, such as belief-propagation or sum-product decoding [PEA88], min-sum decoding [FOS99] or normalized Min-Sum decoding [CHE02].

#### 3. Memory conflict problem

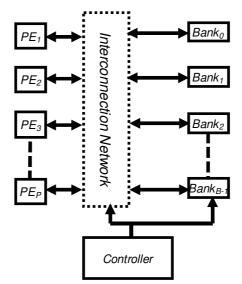

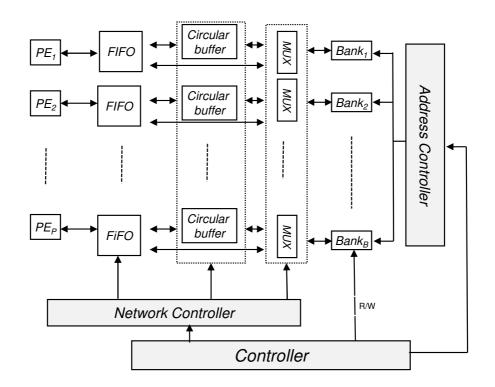

In order to achieve high throughput performance, parallel hardware architectures are needed. The implementation of a typical parallel architecture is shown in Figure 1. 5. In this architecture, P processing elements (PEs) are used to process data elements which are connected to B memory banks through interconnection network, where P = B.

Unfortunately this kind of parallel architectures generates memory access conflicts as soon as several PEs simultaneously try to access to the same memory bank. This problem is also called "*collision problem*" [GIU02]. Memory conflict problem is a major source of concern in designing parallel architectures. The memory conflict problem is explained for turbo and LDPC codes in the two following sub-sections.

Figure 1. 5. Typical Parallel Architecture

#### 3.1. Memory conflict problem for Turbo Codes

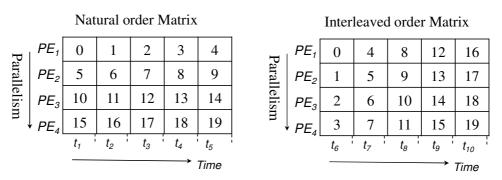

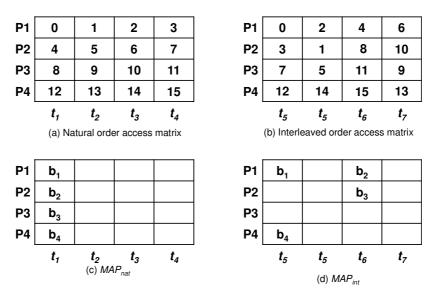

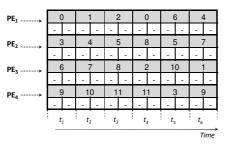

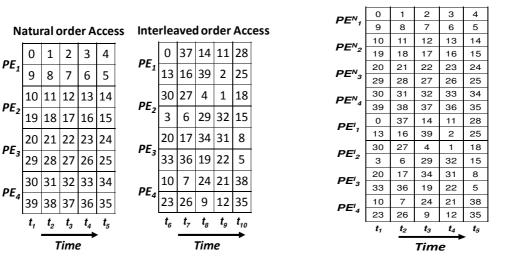

In parallel implementation of turbo codes, different number of processing elements access the data elements from the banks first in the natural order and then in interleaved order. The memory conflict problem for turbo codes is explained here with a pedagogical example. Let us consider L = 20, P = B = 4, M = 5 and T = 10, where L is the number of data elements, B is the number of memory banks, M = L/B is the size of each memory bank and T is the total number of time accesses. The data elements are accessed first in natural order and then in interleaved order shown in Figure 1. 6.

Figure 1. 6. Data access matrices for turbo codes

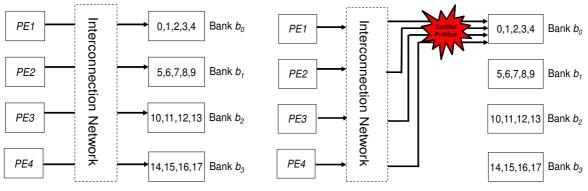

Let us consider that the data elements are stored in the banks in such a manner that all the processing elements always access different memory banks at each time instant in natural order as shown in Figure 1. 7.a e.g. data elements 0,5,10,15 are accessed by the processors in  $t_1$  which are placed in different memory banks i-e  $b_0,b_1,b_2,b_3$  respectively. Unfortunately, due to this memory mapping two or more processing elements need to access one particular memory bank at the same time instance in the interleaved order e.g. data elements 0,1,2,3 are accessed by the PEs in  $t_6$  which are placed in the same memory bank  $b_0$  as shown in Figure 1. 7.b. This issue is called *memory conflict problem* for turbo decoders.

(a) Conflict free natural order Access

Figure 1. 7. Memory Conflict Problem in Parallel Turbo Decoder

#### **3.2.** Memory conflict problem for LDPC Codes

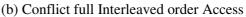

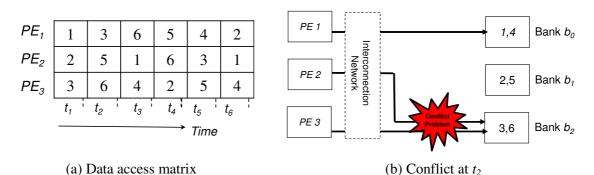

The memory conflict problem for the LDPC codes is different from turbo codes due to the difference in codes construction of these codes. The data access pattern of turbo codes are represented by natural and interleaved order matrices whereas LDPC codes are specified by their *H* matrices and represented by tanner graphs which shows that how data (*variable nodes*) must be processed by the processing elements (*check nodes*) in order to achieve good error correction performances. In order to explain a memory conflict problem in LDPC codes, let us consider L = 6, P = B = 3, M = 2 and T = 6 as shown in data access matrix in Figure 1. 8.a. The data elements stored in bank  $b_0$ , bank  $b_1$  and bank  $b_2$  are (1,4), (2,5) and (3,6) respectively. There is no conflict at time instances  $t_1$  but at  $t_2$  more than two processors want to access the same memory bank. Figure 1. 8.b shows the memory conflict for the time instance  $t_2$ .

Figure 1. 8. Memory Conflict Problem in Partially Parallel LDPC Decoder

Several approaches exist in literature in order to tackle the memory conflict problem. However optimization is needed to design high throughput decoder architectures. The main purpose of this thesis is to optimize the design of parallel architectures focusing on the memory conflict problems (interleavers) in order to reduce the cost for high throughput Turbo and LDPC decoders. The rest of the thesis is organized as follow:

#### Chapter 2

In this chapter, an overview of the state of the art approaches to design parallel hardware architectures for Turbo and LDPC decoders is provided. The state of the art is presented in three different categories. The merits and limitations of each of the approaches are explored.

#### Chapter 3

In this chapter, we present our first approach that aims to limit the cost of final decoder architecture by targeting the customization of the network at the design time (offchip). In the beginning, shuffled and non-shuffled turbo scheduling schemes are explored. Then, the proposed approach based on network relaxation method is described in details. Different experiments are performed for different test cases by using the proposed approach.

#### Chapter 4

In this chapter, our second contribution is presented. This approach is based on inplace memory mapping architectures in order to generate optimized hardware decoders at design time. We propose different algorithms based on Vizing theorem and transportation problem in order to solve memory conflict problem in polynomial time while providing optimized decoders.

#### Chapter 5

Finally, we present an on-chip approach to support multiple standards/applications in order to generate optimized hardware architecture. In order to avoid multiple ROM blocks needed to store controller information, we propose to embed memory mapping approaches on-chip such that complete multiple standards can be supported.

# Chapter 2

## **STATE OF THE ART**

#### **Table of Contents**

| 1. Introduction                                               | 17 |

|---------------------------------------------------------------|----|

| 2. Avoiding conflicts during the code construction            | 17 |

| 3. Solving conflicts by means of dedicated runtime approaches | 21 |

| 4. Solving conflicts with dedicated memory mapping approaches | 24 |

| 4.1. Memory mapping approaches                                | 25 |

| 4.2. Architecture for design time memory mapping approaches   | 28 |

| 4.2.1. In-place memory mapping architecture                   | 28 |

| 4.2.2. <i>MRMW</i> architecture                               |    |

| 5. Conclusion                                                 | 31 |

In this chapter, different state of the art techniques to tackle the memory conflict problem on parallel architectures for Turbo and LDPC codes are presented. The state of the art approaches are divided into three different categories: conflict free interleaving laws, run time conflict resolution and design time conflict resolution. Advantages and disadvantages of each technique are presented in order to motivate our work in this thesis. At the end, we explain the in-place and multiple read multiple write (MRMW) memory mapping architectures.

#### 1. Introduction

Forward error correction codes are used for reliable data transfers between transmitters and receivers. In the associated decoders, parallel architectures are used to achieve high throughput performances. However, these kinds of architectures suffer from memory conflict problem. Many approaches are proposed in literature in order to overcome this issue. In this chapter, different approaches are discussed to implement parallel architectures taking into account the conflict problem for Turbo and LDPC decoders. These approaches can be classified in three categories.

In the first family of approaches, conflict free interleaving laws are defined. The goal is to construct codes with good error correction capabilities, reduced hardware cost and that allow avoiding memory conflicts. In the second family of approaches, conflicts are solved at run time by using flexible and scalable interconnection networks with sufficient path diversity (routing mechanism) and/or buffering techniques to handle memory conflicts. The third family of approaches deals with algorithms that assign data in memory in such a manner that all the processing elements can access memory banks concurrently without any conflict. These approaches which resolve the memory conflict problem at design time are referred as *memory mapping approaches*.

These families are described in detail in the three following sections.

#### 2. Avoiding conflicts during the code construction

In the first category, memory conflict problem is taken into account during code construction. The main source of memory conflicts in Turbo codes comes from the interleaver. Hence, the aim is to develop conflict free interleaving laws with good error correction performance. Conflict free interleaving law provides parallel concurrent accesses to each memory bank without any conflict. An example of such solutions is proposed in [EMM03] in which spatial and temporal permutations are introduced to construct a conflict free interleaver. In order to explain this approach let us consider a block length of 16 data elements arranged row by row into a matrix (*initial matrix*) as shown in Figure2. 1.a. Interleaver leverages on two scrambling techniques: *temporal and spatial permutations*. The *temporal permutation* is obtained by changing the positions of the column in the initial matrix as shown in Figure2. 1.b. For *spatial permutation*, different circular permutations are performed to different columns to obtain the interleaved matrix as shown in Figure2. 1.c. The resultant matrix is a combination of temporal and spatial permutations. Each row is related to

a given processing element and the memory size is represented by the number of columns. The benefit of this approach is also the use of barrel shifter network which controller cost is very low. The Quadratic Permutation Polynomial (QPP) interleaver which is a part of current 3GPP LTE standard [LTE08] is mainly based on this idea.

| 0                     | 1                     | 2  | 3     |

|-----------------------|-----------------------|----|-------|

| 4                     | 5                     | 6  | 7     |

| 8                     | 9                     | 10 | 11    |

| 12                    | 13                    | 14 | 15    |

| <i>C</i> <sub>1</sub> | <i>C</i> <sub>2</sub> | C3 | $C_4$ |

(a) Initial matrix

| 0                     | 2  | 3                     | 1                     |  |

|-----------------------|----|-----------------------|-----------------------|--|

| 4                     | 6  | 7                     | 5                     |  |

| 8                     | 10 | 11                    | 9                     |  |

| 12                    | 14 | 15                    | 13                    |  |

| <b>C</b> <sub>1</sub> | C3 | <i>C</i> <sub>4</sub> | <i>C</i> <sub>2</sub> |  |

(b) *Temporal permutation*

|           | + 4                   | + 3 | <b>+</b> 0 | + 1                   |  |

|-----------|-----------------------|-----|------------|-----------------------|--|

| <b>P1</b> | 4                     | 10  | 3          | 13                    |  |

| <b>P2</b> | 8                     | 14  | 7          | 1                     |  |

| <b>P3</b> | 12                    | 2   | 11         | 5                     |  |

| <b>P4</b> | 0                     | 6   | 15         | 9                     |  |

|           | <b>C</b> <sub>1</sub> | C3  | $C_4$      | <i>C</i> <sub>2</sub> |  |

(c) Spatial permutation

Figure 2. 1. Interleaver construction

QPP interleaver was introduced in [YAN05] which is a *prunable and deterministic interleaver*. A *prunable interleaver* can be modified to obtain the interleaver of shorter length that keeps the error correction capabilities of the original larger interleaver. Prunable interleavers offer scalability in code-word to meet the channel conditions and changing user requirements. In deterministic interleaver, algorithms are used to produce on the fly addresses of interleaved data. The implementation of deterministic interleavers is easy as compared to *random interleavers* in which the addresses are generated randomly and for which dedicated memory (e.g. ROM) is required to store these addressing information. The performance QPP interleaver is near to random interleaver for long frame size whereas for short frame size, QPP interleaver outperforms random interleaver. QPP interleaver is represented by the following equation for a block size *L*:

$$\Pi(x) = (f_1 x^2 + f_2 x) \mod L$$

where x and  $\Pi(x)$  represents the natural and interleaved address respectively and variables  $f_1$ ,  $f_2$  are different for different block lengths as specified in the standard.

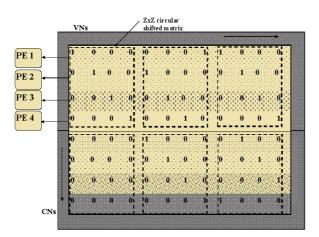

State of the art

In [TAK06], QPP interleaver is proved to be contention-free for every window size that is a factor of interleaver length. However, it is not contention-free for other data rates in which high level parallelisms are used in the decoder.In [BOH07], a new interleaver for turbo codes is proposed. The interleaver is described by using four successive distinct laws and can also be defined using simple matrix S of size  $L \ge L$  where L is the size of the frame. This matrix is composed of k circularly right shifted  $z \ge z$  matrices (like in *LDPC* codes). The amount of shift is denoted by  $\delta(r)$  and it is located at position P(r) of the matrix. In this approach, first the frame with L = k.z elements is interleaved by z-row m-column permutations. Secondly, each group r (where r = [0, k-1]) of z elements is right shifted by  $\delta(r)$ positions. Finally, in the last step the group of z elements is interleaved.

| _ |   |   |   |   |   |   |   |   |   |   |   | _ |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

|   | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

|   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

|   | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|   | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|   | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|   | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|   | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| - | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

|   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

|   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

|   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

|   |   |   |   |   |   |   |   |   | • |   |   |   |

Figure 2. 2. Interleaver matrix

An example of such *S* matrix is shown in Figure 2.6 in which L = 12, k = 3, z = 4, P = [1,0,2] and  $\delta = [1,3,0]$ . This interleaver has good performance and low-complex hardware implementation for high parallelized turbo decoders as compared to 3GPP-LTE interleaver. However, this interleaver is not a part of the current telecommunication standards.

The memory conflict problem for LDPC codes is handled by constructing *structured LDPC* codes [ZHA04] [MAN03]. *LDPC* codes are specified by their *H* matrices (see Figure 2. 3(a)) in which rows are associated to *check nodes* and columns to *variable nodes*. These codes can also be represented by *Tanner graphs* which show how data (*variable nodes*) must be processed by the processing elements (*check nodes*) in order to achieve good error correction performances (see Figure 2. 3(b)).

Figure 2. 3. Tanner graph formalization of an LDPC H-matrix

However, to achieve these excellent error correction capabilities proper construction of the H matrices is required. So H matrix must be constructed such that data transfer between check nodes and variable nodes can be made without any conflict for parallel architecture. In *structured codes*, the H matrix is divided into different blocks of sub-matrices (ZxZ matrices) where each sub-matrix is obtained by permuting rows of the identity matrix as shown in Figure 2.3. The check node processors access the vectors nodes data elements in parallel by using simple interconnection network like *barrel shifter* thanks to the structure of identity matrix in each sub-block.

Structured codes are part of current telecommunication standards such as IEEE 802.11n (WiFi) [WIF08] and IEEE 802.16e (WiMAX) [WIM06]. However, they only support one class of LDPC codes. A general approach to handle memory mapping problem is required to handle various existing and future classes of LDPC codes such as non-binary LDPC codes.

Figure 2. 4. Structured LDPC codes

Moreover, it must be observed that the conflict free data access order in the decoder part of the architecture can be different from the data access order coming from the channel as it is the case in QPP interleaver for example. This issue reports hence the conflict problem on the channel interleaver side.

#### 3. Solving conflicts by means of dedicated runtime approaches

The second family of solutions solves memory access conflict problem by storing the data elements in different memory banks in an arbitrary order and then use additional mechanism (buffering/routing) in the interconnection network to manage conflicts at runtime. These approaches are referred as *run time conflict resolution*. *However, we have* referred these approaches as *time relaxation* methods in this document.

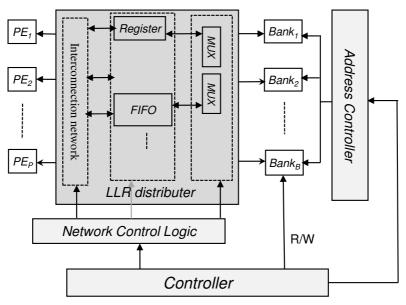

Such approach is presented in [WEH02] in which the data is simply stored in different memory banks without considering conflicting accesses and then additional buffers are used in the interconnection network to manage conflicts at runtime. This approach is based on a *LLR distributor* which is connected with all the *P* processing elements on one side and all the memory banks on the other side, as shown in Figure 2.4. The *LLR distributor* consists of interconnection network, buffers, *FIFOs* and multiplexers. The total cost and the latency of the architecture increases due to the use of buffers, FIFOs and multiplexers to manage conflict.

Figure 2. 5. Architecture based on LLR Distributor

In [WAN11], the authors proposed an approach based on Double-Buffer Contention-Free (DBCF) architecture. The *DBCF* architecture is built around the interleaver between the processors and memory banks. This architecture consists of FIFOs associated with processors, circular buffers, multiplexers and bypass units as shown in Figure 2. 6. The conflicting accesses are routed into a dedicated circular buffer as soon as a conflict is detected. The interest of this approach has been demonstrated by designing an interleaver used in a HSPA+/LTE decoder. However, this architecture is configured on the basis of simulation results analysis in order to handle conflicts.

Figure 2. 6. Architecture based on Double buffer

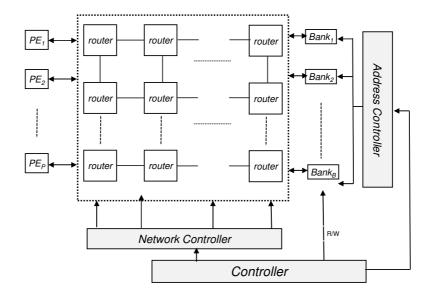

Approaches based on *Network-on-Chip (NoC)* architecture are also proposed to resolve the conflicts on run time. In [NEE05], approaches based on *mesh*, *torus* and *cube* networks are proposed in which routers are used to contain packets for the destination information. However, these approaches suffer from reduced scalability to construct high throughput flexible on-chip communication network. Also, due to complex buffer management architecture to store conflicting data, the router complexity increases significantly with the increase of parallelism.

Another solution based on *NoC* oriented architecture is presented in [MOU07]. In this work (see Figure 2.7), the interconnection network can be configured on-the-fly to compete with any classical interconnection network such as *Butterfly* and *Benes*. *Butterfly network* has two main advantages: firstly, the network has huge scalability as a network of size N can be constructed from two networks of size N/2. Secondly, the packet routing algorithm is very

simple due to the use of destination address bits for selecting output port of router at each stage of the network. The routers stores conflicting packets using FIFOs. However, Butterfly network lacks in path diversity as it provides distinctive path between source and destination.

Figure 2. 7. Architecture based on NoC

Therefore, complex buffering architecture to manage conflicting packets is required which increases cost of the architecture. *Benes network* is the second multistage network studied in [MOU07]. It is constructed by concatenating two Butterfly networks back-to-back. The Benes network has good path diversity as it provides all possible permutations between inputs and outputs. However, this network avoids conflicts between packets, if all the packets have different destinations, which is not the case in turbo decoding. A modified topology and routing algorithm is proposed in this approach to optimize *Benes network* for turbo decoding. Routing algorithm transmits packets which are intended for different router at the same time and registers are used (instead of FIFOs) to store conflicting data. However, pre-processing is required to generate routing information and memory is needed to store router configuration.

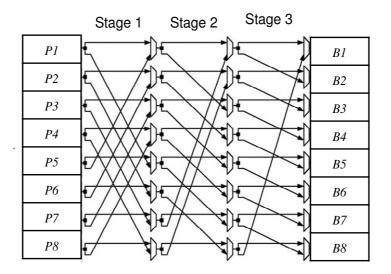

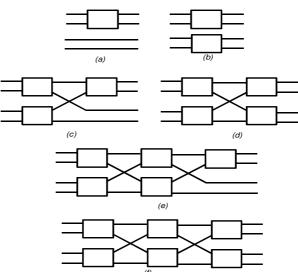

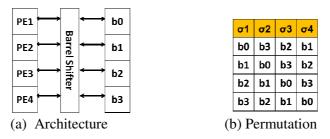

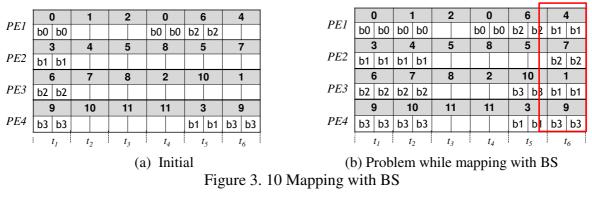

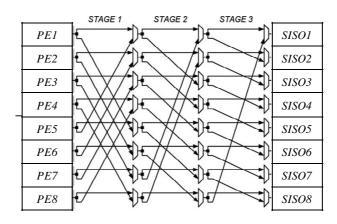

A multistage network based on barrel shifter has been recently proposed for 3GPP LTE System for parallel decoder architecture in [WON10]. The connection between each memory bank and its corresponding processing element is established by shifting each sub block by a given offset due to the permutation characteristics of QPP interleaver used in LTE. The authors have presented a multistage interconnection network based on barrel shifter as shown in Figure 2.8. This figure shows the parallel architecture with multistage interconnection network for P = 8 with three stages. In the proposed network,  $2^i$  bits are needed for shifting data in the stage (3 - i) where  $i = 0 \sim 2$  and the amount of shift in the stage (3 - i) is  $2^i$  locations. So, we can compute that one bit is needed for stage 0, two bits are needed for stage 2 and four bits are needed for stage 3. Therefore, the three stages of the modified barrel shifter require driving seven bits for configuration at each access. Similarly, for P = 4, two stages of modified barrel shifter needs three bits.

Figure 2. 8. Parallel architecture with multistage network

The data between the processor and memory is transferred immediately as the interconnection network has short path delay and simplified network control mechanism. However, the proposed approach can only be applied to QPP interleaver. This approach is not compliant with any other interleaving law.

The presence of interconnection network and buffer management mechanisms to manage conflicts increases hardware cost and latency of decoders which often restricts the implementation of such architectures for practical systems.

# 4. Solving conflicts with dedicated memory mapping approaches

The third family of solutions deal with memory access conflict problem by storing the data elements in different memory banks in such a way that all the processing elements can access to the data without any conflict at each time instance. Different mapping algorithms are proposed in state-of-the-art to perform pre-processing steps in order to determine each data element in the memories. These approach leverage on specific architectures that are presented in the last sub-section.

#### 4.1. Memory mapping approaches

In [BEN04], one of the first algorithms based on simulated annealing meta-heuristic to resolve conflict problem for Turbo and LDPC codes is proposed. This algorithm is always able to find conflict free memory mapping, but the time to calculate the solution cannot be computed statically. Therefore, the computational complexity of the problem inhibits the addition of other constraints into the algorithm such as targeting a dedicated interconnection network.

In [JIN10], an approach based on optimized memory address remapping is presented. In this method certain collision-free exchange rules are defined to complete the simulated annealing procedure much faster than achieved in the traditional method presented in [BEN04] thanks to a reduced number of iterations to complete the annealing procedure . However, this method is also based on a meta-heuristic and the time of completion of the algorithm cannot be predicted.

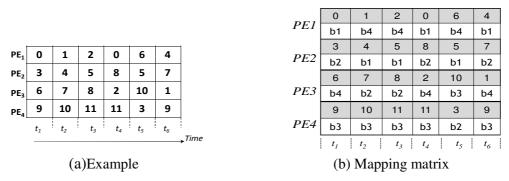

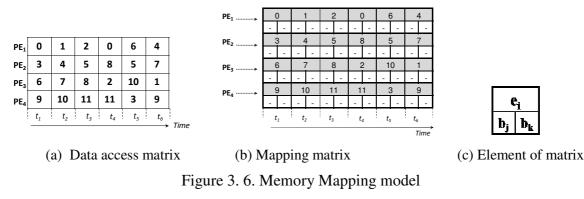

In [CHA10a], a new simplified approach called Static Address Generation Easing (SAGE) is presented. This approach includes additional constraints to determine architecture oriented conflict free memory mapping. In SAGE, two *Mapping Matrices* (*MAP<sub>Nab</sub> MAP<sub>Int</sub>*) are used during algorithm execution to store bank information. These matrices have the same order as the natural and interleaved order matrices as shown in Figure 2.9.

Figure 2. 9. Matrices used in SAGE

There are two constraints to be respected during the execution of the SAGE algorithm in order to find architecture oriented memory mapping. The first constraint is to allocate different memory banks to the cells of each column of the mapping matrices. The second constraint is to respect the targeted interconnection network if supported by the interleaving law. The algorithm is initialized by assigning memory banks to the first column of  $M_{Nat}$  (see Figure 2.8.(c)). Then the entries corresponding to the data in  $M_{int}$  are updated (reported) with this mapping information (see Figure 2.8.(d)). In the next iteration, the most constrained column (i.e. the column with the greater number of assigned cells) is filled and reported in the same manner. This process continues until all the columns of the mapping matrices are filled with mapping information.

The above mentioned approach is limited to turbo-codes and a more generic approach has been proposed in [CHA10b]. This approach is able to solve memory conflict problem also for LDPC codes. It is based on Multiple Read Multiple Write (*MRMW*) mechanism in which each data element  $e_i$  consists of two memory locations: one for read data and the other for write data, as shown in Figure 2.9. For functional correctness, if data is accessed several times, then  $j^{th}$  read access of  $e_i$  must be equal to the  $(j-1)^{th}$  write access of  $e_i$ . The algorithm assigns read and write memory banks to the most constrained column (i.e. the column with high number of data elements already mapped) of the *MAP* matrix. Then the corresponding entries in the other matrix are filled respecting the targeted interconnection network constraints. This process continues until *MAP* matrices are fully filled with targeted network constraints. However, recursion is needed when a conflict is detected. This approach innovates a new way to solve computationally complex problem through multiple read and multiple write mechanism. However, it can use backtracking making time to complete the algorithm unknown.

(a) Mapping matrix

(b) An element of the matrix

Figure 2. 10. Multiple Read Multiple write (MRMW) approach

In [SAN11a], an approach based on Transportation problem modeling is presented. This method finds conflict free memory mapping for Turbo codes with architecture optimization. The mapping problem for turbo codes is transformed as transportation problem. The proposed approach is interesting as it is based on a polynomial time algorithm. However, it works for a subset of cases and can be widely improved as demonstrated in the dedicated section of chapter-4.

In [SAN13], another polynomial time algorithm is presented to reduce the computational complexity to find conflict free mappings. The algorithm is based on two steps. In the first step, a bipartite graph is constructed based on two data access matrices. Then in the second step, a polynomial time bipartite edge coloring algorithm is used to find conflict free memory mapping. This approach can be used to solve memory conflict problem for both Turbo and LDPC codes.

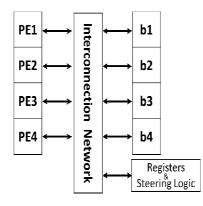

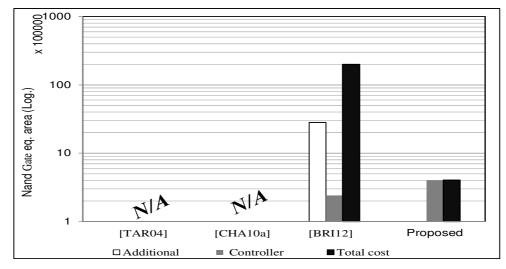

Finally, in [BRI12] [BRI13a] [BRI13b], the authors have presented a memory mapping approach to find conflict-free memory mappings for both Turbo-codes and LDPC codes for any standard respecting targeted interconnection network. This approach is referred as *memory relaxation method* in this thesis. It is based on the idea of adding registers in the memory architecture (and not in the interconnection network) to deal with conflicting data and to respect the targeted interconnection network. However, the cost of the final architecture is increased due the inclusion of registers and their dedicated additional steering logic as shown in Figure 2.11. In this figure, the four processors are connected to four memory banks through a targeted interconnection network. Additional registers and steering logic are required to support the conflict free memory mapping with the targeted network as shown in Figure 2.11. However, if the targeted interleaving law is strongly incompatible with the targeted interconnection network will be high.

Figure 2.11. Resulting architecture with additional registers and steering logic for Memory relaxation based approach

#### 4.2. Architecture for design time memory mapping approaches

All of the previously mentioned memory mapping approaches are either based on inplace memory mapping or multiple read multiple write (MRMW) memory mapping architecture as shown later in this section. We will describe the two kind of architectures in the two next subsections.

#### 4.2.1. In-place memory mapping architecture

The architecture for turbo-like memory conflict problem is known as *in-place memory mapping architecture*. In order to explain in-place architecture, consider a set of L data elements  $\{d_1, d_2, ..., d_L\}$  and a set of P processing elements  $\{PE_1, PE_2, ..., PE_P\}$ . These processors process each of the L data elements two times in T time instances  $\{t_1, t_2, ..., t_T\}$  first in natural order and then in interleaved order, where T = 2L/P. In order to store these L data elements and to achieve parallel processing of data for high throughput, a set of B memory banks  $\{b_1, b_2, ..., b_B\}$  are needed.

#### Mapping problem

We need to store the L data elements in B memory banks in such a way that P processing elements can access B memory banks in parallel for all time instances without any conflict.

For in-place conflict free memory accesses, the two following mapping constraints must be fulfilled:

- All memory banks have to be used only one time at each time instance (conflict free).

- Each data must be mapped in one and only one memory location (*in-place*).

As an example, a matrix in which each data is accessed twice (in natural and interleaved order), is shown in Figure 2.12.a. The resultant mapping of the considered example is shown in Figure 2.12.b by using memory mapping approach [CHA10a] which is based on in-place architecture. In this figure, each data in a column has a mapping cell which shows the memory bank from where a given data is read and written at a given time. It can be seen that every data element is read and written in the same memory bank, e.g. data 0 is read and written back in the same bank  $b_1$ .

Figure 2.12. In-place mapping

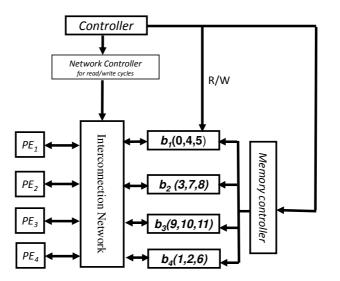

The architecture for resultant mapping can be seen in Figure 2.13 in which the data elements in each bank are shown. The processors read the data from the memory banks without any conflict by using memory controller through an interconnection network which is configured by network controller. The same configuration of a read cycle is also used for the write cycle.

Figure 2.13. Resultant In-place mapping architecture

#### 4.2.2. MRMW architecture

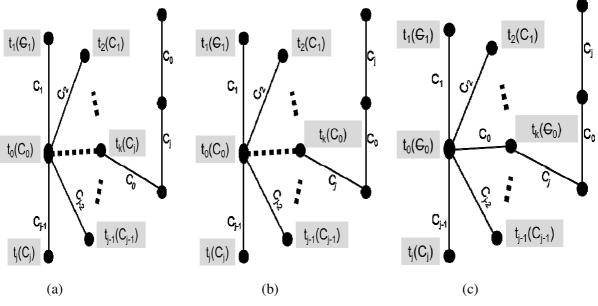

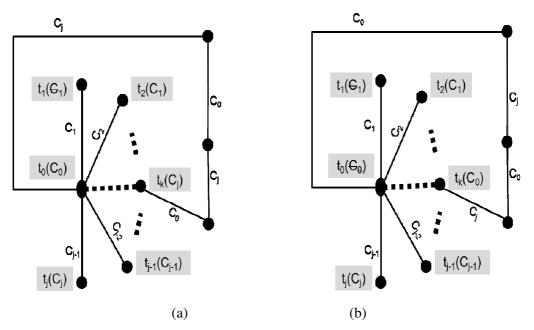

*MRMW* memory mapping architecture is used to solve LDPC-like memory conflict problems. The concept of *MRMW* memory mapping architecture is introduced in [CHA10b]. Then this concept is extended in [SANI13] using polynomial time algorithms to find conflict free memory mapping. In *MRMW* architecture, memory mapping of each data element is done in two memory locations: First location called *read mapping* represents read access to that data element whereas second location called *write mapping* expresses write access of that data element. The aim of *MRMW* architecture is to find memory mapping with optimal number of memory banks.

#### Mapping problem

Store L data in B memory banks in such a manner that P processing elements can access B memory banks at each time instance in parallel for first reading P data and then writing back these P data without any conflict.

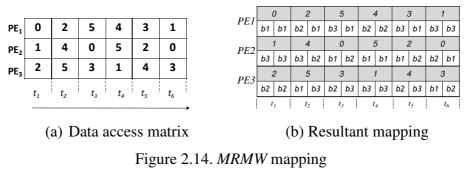

The *MRMW* mapping is shown in Figure 2.14.b for the example in Figure 2.14.a by using [CHA10b]. In this figure data-2 at time instance  $t_2$  is read from bank  $b_2$  and written in a different bank  $b_1$ .

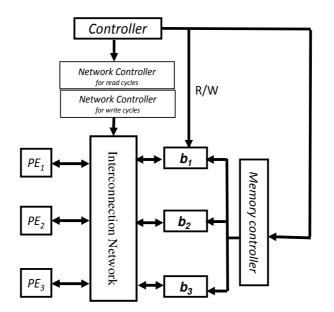

The resultant *MRMW* memory mapping architecture is shown in Figure 2.15. In this architecture the mapping of data elements in the banks is not mentioned because the mapping changes at each cycle according to the mapping shown in Figure 2.14.b. The network configurations for read operations are different from write operation. Therefore, configuration for read as well as write operations are needed which double the network controller cost. Hence, it can be noticed that the in-place mapping architecture could lead to reduce the network controller cost as compared to *MRMW* architecture.

Figure 2.15. MRMW architecture

The *MRMW* architecture is more costly in term of area as compared to in-place memory architectures. Memory conflict problems like shuffled turbo (see chapter-3, section 2.2.2) and LDPC codes are solved using [CHA10b], [SAN11], [SAN13] based on *MRMW* architecture. So, in order to optimize generated architectures, it could be really interesting if in-place memory mapping architecture could be used to solve these problems.

## 5. Conclusion

In this chapter, different approaches to handle memory conflict problem for Turbo and LDPC codes are explained. One solution is to develop an interleaving law taking into account architectural constraints at the time of code construction. However, with this approach the memory mapping problem is only partially solved, and the designers still have to handle conflicts in the final architectures (for some parallelism degrees, block lengths, channel interleaver in telecommunication systems...).

A second technique exists in literature to tackle memory mapping problem at run time. However, the implementation of such architectures requires large hardware cost and latency due to the addition of conflict management mechanisms which limits its use in practical systems.

The third technique is to develop algorithms at design time that assign data in memory banks in such a manner that all processing elements can access their required data concurrently from memory without any conflict. Some of these techniques solve memory mapping problem for any type of interleaving law but results in costly hardware architecture. Others are limited to a subset of applications.

In this thesis, we aim to design optimized parallel hardware architectures to solve memory conflict problems. For this purpose, we propose two categories of complementary approaches. In first category, we propose memory mapping approaches that aim to limit the cost of final decoder architectures by customizing interconnection networks (see chapter 3) and by using in-place memory architectures (see chapter 4). In the second category, we propose to merge both runtime and design time approaches to design flexible decoder architectures. For this purpose, we have embedded polynomial time memory mapping algorithm on-chip along with the interconnection network in order to execute it at runtime to solve conflict problem (see chapter 5).

# Chapter 3

# **OPTIMIZED MEMORY MAPPING APPROACH BASED ON NETWORK CUSTOMIZATION**

### **Table of Contents**

| 1.Introduction                                                             | 35 |

|----------------------------------------------------------------------------|----|

| 2.Dedicated approach to explore design space of turbo decoder architecture | 35 |

| 2.1.Turbo decoder architecture                                             | 35 |

| 2.2.Proposed design flow                                                   | 36 |

| 2.2.1.Shuffled decoding memory issues                                      | 37 |

| 2.2.2.Solving memory conflicts                                             | 38 |

| 2.3.Case study: Turbo decoder for LTE                                      | 39 |

| 3. Memory mapping approach based on network customization                  | 42 |

| 3.1.Proposed Approach                                                      | 43 |

| 3.1.1.Memory Mapping with Network Relaxation                               | 43 |

| 3.1.2.Pedagogical Example                                                  | 46 |

| 3.2.Experiments and Results                                                | 48 |

| 3.2.1.Case study for HSPA                                                  | 49 |

| 3.2.2.Case study for LTE                                                   | 54 |

| 4.Conclusion                                                               | 55 |

This chapter consists of two parts. First, a dedicated approach to explore the design space for parallel turbo decoder architectures is presented in which different configurations based on shuffled and non-shuffled schemes are considered. Then, thanks to the analysis of these experiments, we propose a new approach for conflict free memory mapping based on network customization to generate optimized architectures. This customization can be done by modifying a targeted network with additional network components if needed or by adding components starting from the scratch (directly connected wires). The proposed approach is compared with the state of the art approaches through different test-cases.

# 1. Introduction

In this chapter, we first present a dedicated approach to explore design space for hardware architectures of turbo decoders in order to analyze their hardware complexity. The turbo decoder memory issues are explored and state of the art approaches are used to solve the memory access conflicts in case of shuffled and non-shuffled turbo decoders. We have performed different experiments for a case study of turbo decoders for 3GPP-LTE.

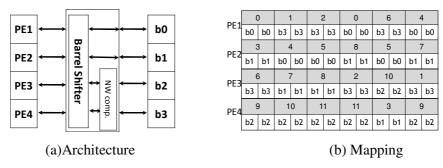

The second part of this chapter is about our proposed memory mapping approach based on network customization. The complexity for a given memory mapping problem depends on the memory and network controller. Unfortunately, none of the existing approaches focused on network controller optimization to design conflict free memory mapping. Our proposal is to introduce a new approach based on finding conflict free memory mapping approaches which gives the degree of freedom in the interconnection network in order to reduce the complexity. In this approach, the interconnection network is customized to find a conflict free memory mapping which generates optimized architectures.

### 2. Dedicated approach to explore design space of turbo decoder architecture

Parallel turbo architecture can be based on different decoding techniques (shuffled, nonshuffled) and different scheduling like backward-forward, butterfly/butterfly-replica, ... (see section 2.3). The impact of these techniques on the hardware complexity and throughput is usually determined at the end of design process after the synthesis process. Thus, the time to market is penalized and the probability of designing an optimized system decreases. In order to tackle this problem, we have introduced a dedicated approach to efficiently explore the design space of parallel turbo decoder architectures. Thanks to this approach, a tradeoff between the hardware complexity can be estimated for the architecture design process. The memory access conflict problem is solved using existing approaches in order to design high throughput architecture for any parallelism and interleaver. However, a penalty in terms of the hardware complexity is expected. This work has been carried out in collaboration with TELECOM Bretagne, Brest-France [SAC12].

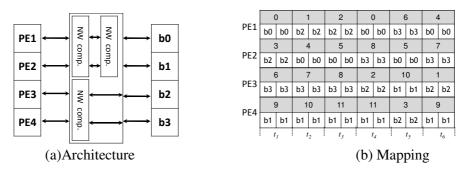

### 2.1. Turbo decoder architecture

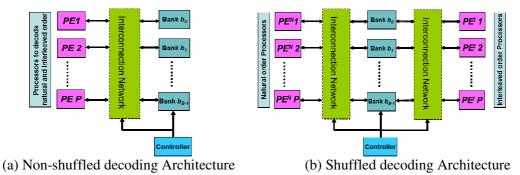

Figure 3. 1 shows the turbo decoder architecture. Through an interconnection network the processing elements (PEs) have access to a set of B memory blocks (single port RAM), allocated to keep the extrinsic information. The controller part consists of Read Only Memories which are used to address each memory block and control signals of the

interconnection network. The controller is also to be designed to address the ROM memories and to generate control signals of the memory blocks. Figure 3. 1(a) shows the architecture for non-shuffled decoding [BER90] in which all the *P* PEs are first assigned to decode the natural order, and then all of them are assigned to the interleaved order. However, as mentioned in [ZHA05], shuffled decoding can also be applied as shown in Figure 3. 1(b). In this case, *P*/2 PEs are used to decode the natural order, while the remaining *P*/2 PEs work on the interleaved order. Let *L* denotes the number of symbols in the received frame. This frame can be divided into *Q* sub-blocks that can be decoded in parallel. Each sub-block is formed by M = L/Qsymbols with Q = P for non-shuffled turbo decoders and Q = P/2 for shuffled turbo decoders.

Figure 3. 1 Decoding Architecture for Turbo Decoders

Let *T* denotes the number of clock cycles where each *PE* performs writing or reading memory access in order to execute one iteration (for a non-shuffled turbo decoder), or a half iteration (for a shuffled turbo decoder). Let *M* represents the size of each memory block. The size of each addressing ROM is  $T^*[log_2(M)]$ . Note that iteration in a shuffled and non-shuffled turbo decoder takes the same time if both turbo decoders have the same sub-block size *M*.

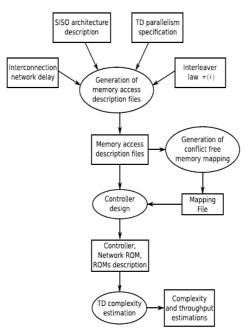

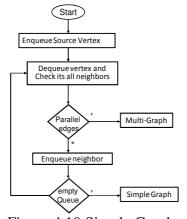

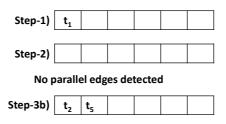

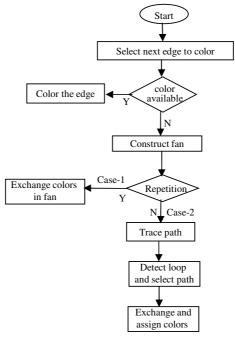

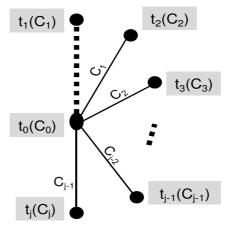

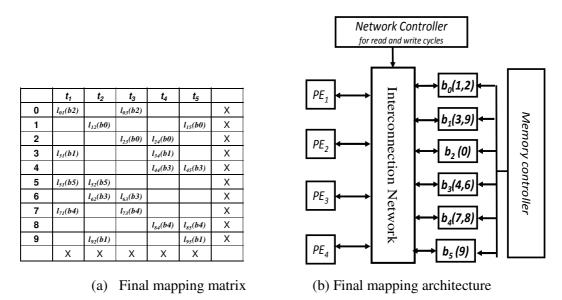

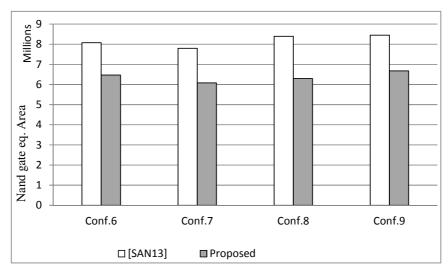

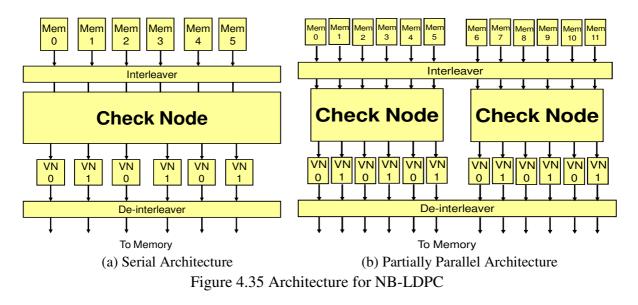

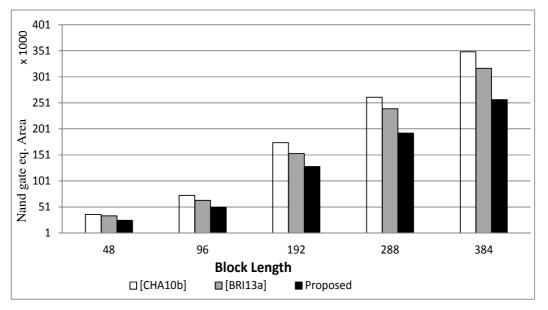

### 2.2. Proposed design flow