# Proving Floating-Point Numerical Programs by Analysis of their Assembly Code

Nguyen Thi Minh Tuyen, Claude Marché

# ▶ To cite this version:

Nguyen Thi Minh Tuyen, Claude Marché. Proving Floating-Point Numerical Programs by Analysis of their Assembly Code. [Research Report] RR-7655, INRIA. 2011, pp.61. inria-00602266

# HAL Id: inria-00602266 https://inria.hal.science/inria-00602266

Submitted on 21 Jun 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

# Proving Floating-Point Numerical Programs by Analysis of their Assembly Code

Thi Minh Tuyen Nguyen — Claude Marché

N° 7655

June 2011

# **Proving Floating-Point Numerical Programs** by Analysis of their Assembly Code

Thi Minh Tuyen Nguyen\* <sup>†</sup>, Claude Marché\*<sup>†</sup>

Thème : Programmation, vérification et preuves Équipes-Projets PROVAL

Rapport de recherche n° 7655 — June 2011 — 58 pages

**Abstract:** We present an approach for proving behavioral properties of numerical programs by analyzing their compiled assembly code. We focus on the issues and traps that may arise on floatingpoint computations. Direct analysis of the assembly code allows to accurately take into account architecture- or compiler-dependent features such as the possible use of extended precision registers.

The approach is implemented on top of the generic Why platform for deductive verification, which allows us to perform experiments where proofs are discharged by combining several back-end automatic provers.

Key-words: Formal Specification, Proof, assembly code, floating-point computations

\* INRIA Saclay - Île-de-France, F-91893

<sup>†</sup> Lab. de Recherche en Informatique, Univ Paris-Sud, CNRS, Orsay, F-91405

Centre de recherche INRIA Saclay – Île-de-France Parc Orsay Université 4, rue Jacques Monod, 91893 ORSAY Cedex Téléphone : +33 1 72 92 59 00

# Preuve de programmes avec calculs en virgule flottante par analyse de leur code assembleur

**Résumé :** Nous décrivons une nouvelle approche pour prouver des propriétés du comportement des programmes numériques en analysant leur code assembleur compilé. Nous mettons l'accent sur les enjeux et les pièges qui peuvent survenir lors des calculs en virgule flottante. L'analyse directe du code assembleur permet de prendre en compte de façon précise l'architecture et le compilateur, par exemple l'utilisation de registres en précision flottante étendue.

Un prototype est implanté au-dessus de la plate-forme générique Why plate-forme pour la vérification déductive. Nous présentons des expérimentations où les preuves sont effectuées par une combinaison de plusieurs prouveurs automatiques.

Mots-clés : Spécification formelle, Preuve, assembleur, calculs en virgule flottante

# Contents

| 1 | Intr           | Introduction 6                                                                                                     |  |  |  |

|---|----------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2 | c background 8 |                                                                                                                    |  |  |  |

|   | 2.1            | Assembly language                                                                                                  |  |  |  |

|   |                | 2.1.1         Operands         8                                                                                   |  |  |  |

|   |                | 2.1.2         Instruction Naming         9                                                                         |  |  |  |

|   |                | 2.1.2       Instruction real-purpose instructions       9         2.1.3       General-purpose instructions       9 |  |  |  |

|   |                | 2.1.4       Assembler directives       10                                                                          |  |  |  |

|   | 2.2            | Inline assembly   10                                                                                               |  |  |  |

|   | 2.2            | 2.2.1       Simple Inline Statement       10                                                                       |  |  |  |

|   |                | 2.2.1       Simple infine Statement       10         2.2.2       Extended Inline Statements       10               |  |  |  |

|   | 22             |                                                                                                                    |  |  |  |

|   | 2.3            | Why: a software verification platform    11                                                                        |  |  |  |

|   | 2.4            | Frama-C and the ACSL specification language                                                                        |  |  |  |

| 3 | Case           | e of Simple programs 12                                                                                            |  |  |  |

|   | 3.1            | Overview of the approach                                                                                           |  |  |  |

|   | 3.2            | Definition of the class of "simple" C programs                                                                     |  |  |  |

|   | 3.3            | Translation to Why                                                                                                 |  |  |  |

|   |                | 3.3.1 Translation of 32-bit integers                                                                               |  |  |  |

|   |                | 3.3.2 Translation of operands                                                                                      |  |  |  |

|   |                | 3.3.3 Translation of instructions                                                                                  |  |  |  |

|   |                | 3.3.4 Translation of a sequence of instructions                                                                    |  |  |  |

|   | 3.4            | Annotations                                                                                                        |  |  |  |

|   |                | 3.4.1 Types of annotations interpreted                                                                             |  |  |  |

|   |                | 3.4.2 Preprocessing: keeps annotations in assembly code                                                            |  |  |  |

|   |                | 3.4.3 Translation of annotations in assembly to Why                                                                |  |  |  |

|   | 3.5            | Examples                                                                                                           |  |  |  |

|   | 5.5            |                                                                                                                    |  |  |  |

| 4 |                | ting-point programs 22                                                                                             |  |  |  |

|   | 4.1            | Definition of programs                                                                                             |  |  |  |

|   | 4.2            | Assembly with floating-point arithmetic                                                                            |  |  |  |

|   |                | 4.2.1 SSE/SSE2                                                                                                     |  |  |  |

|   |                | 4.2.2 x87 Floating-point Unit                                                                                      |  |  |  |

|   |                | 4.2.3 FMA 25                                                                                                       |  |  |  |

|   | 4.3            | Examples of the chapter                                                                                            |  |  |  |

|   |                | 4.3.1 Double rounding example                                                                                      |  |  |  |

|   |                | 4.3.2 Example: Architecture dependent Overflow                                                                     |  |  |  |

|   | 4.4            | Translation to Why                                                                                                 |  |  |  |

|   |                | 4.4.1 Abstract functions                                                                                           |  |  |  |

|   |                | 4.4.2 When constants is referenced by %rip                                                                         |  |  |  |

|   |                | 4.4.3 Rewrite the translation of general-purpose instructions                                                      |  |  |  |

|   |                | 4.4.4       Translation of SSE/SSE2 instructions       32                                                          |  |  |  |

|   |                | 4.4.5 x87 Floating-point Unit                                                                                      |  |  |  |

|   |                | $\tau$ ,                                            |  |  |  |

|                                |     |                                                                                  | 34 |  |

|--------------------------------|-----|----------------------------------------------------------------------------------|----|--|

|                                |     | 4.4.7 Translation of annotations to Why in presence of floating-point arithmetic | 35 |  |

|                                | 4.5 | Results of examples of the chapter                                               | 35 |  |

|                                |     | 1 1                                                                              | 35 |  |

|                                |     |                                                                                  | 36 |  |

| 5                              | Han | dling Conditional and loops                                                      | 37 |  |

|                                | 5.1 | Definition of programs treated                                                   | 37 |  |

|                                | 5.2 |                                                                                  | 37 |  |

|                                | 5.3 |                                                                                  | 41 |  |

|                                | 5.4 | •                                                                                | 43 |  |

|                                |     |                                                                                  | 43 |  |

| 6 Handling Arrays and Pointers |     | dling Arrays and Pointers                                                        | 45 |  |

| U                              |     |                                                                                  |    |  |

|                                | 0.1 |                                                                                  | 45 |  |

|                                | 6.2 | 5 1                                                                              | 45 |  |

|                                |     | 6.2.1 Representation of memory in Why                                            | 45 |  |

|                                |     | 6.2.2 Definition of memory model                                                 | 49 |  |

|                                |     | 6.2.3 Translation of instructions and operands to Why                            | 49 |  |

|                                |     |                                                                                  | 53 |  |

|                                | 6.3 |                                                                                  | 53 |  |

|                                |     | -                                                                                | 53 |  |

| 7                              | Con | clusion                                                                          | 56 |  |

# **List of Figures**

| 3.1 | Step-by-step from C program to WHY proof obligations           |

|-----|----------------------------------------------------------------|

| 3.2 | A simple program                                               |

| 3.3 | Assembly code of the example of Figure 3.2                     |

| 3.4 | Translation of a function in assembly to Why 18                |

| 3.5 | Why program of Figure 3.3         20                           |

| 3.6 | Result of Figure 3.5 program    21                             |

| 4.1 | FPU data registers                                             |

| 4.2 | Illustration of vfmaddsd instruction 26                        |

| 4.3 | Illustration of VFNMADDSS instruction                          |

| 4.4 | A simple floating-point program                                |

| 4.5 | Assembly code in SSE mode and x87 mode of Figure 4.4 example   |

| 4.6 | Optimized versus non-optimized assembly of overflow example 28 |

| 4.7 | Illustration of the stack with instruction <i>fldl</i>         |

| 4.8 | Result of Figure 4.4 program    36                             |

| 5.1 | Example with <i>if</i>                                         |

| 5.2 | Assembly code of program in Figure 5.1                         |

| 5.3 | CFG of Program in Figure 5.1                                   |

| 5.4 | Program with loop statement                                    |

| 5.5 | CFG of Program in Figure 5.4                                   |

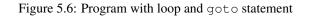

| 5.6 | Program with loop and goto statement 40                        |

| 5.7 | CFG of Program in Figure 5.6                                   |

| 5.8 | Avionics program                                               |

| 6.1 | An example containing array as global value                    |

| 6.2 | Memory model                                                   |

| 6.3 | C code of a program with arrays defined as local variables     |

| 6.4 | Assembly code of Figure 6.3                                    |

| 6.5 | Scalar product: annotated code                                 |

6

# Chapter 1 Introduction

The C language is the first choice for embedded systems or critical software from domains such as simulation of physical systems, control-command programs in transportation, etc. For such systems, floating-point (FP for short) computations are involved and precision of calculations is an important issue. The IEEE-754 standard [1] enforces a precise definition on how the basic arithmetic operations (+, -, \*, /, and also absolute value, square root, etc.) must be computed on given FP format (32 bits, 64 bits, etc.) and w.r.t a given rounding mode. This standard is currently supported by most of the processor chips. However, this does not imply that a given C program must produce exactly the same results whatever is the compiler and the underlying architecture. There are several possible reasons, e.g. the x87 floating-point unit (FPU) uses 80-bit internal floating-point registers, or the compiler may optimize the assembly code be changing the order of operations. Such issues have been extensively analyzed by D. Monniaux [23]. A small example that illustrates such an issue is as follows.

```

double doublerounding() {

double x = 1.0;

double y = 0x1p-53 + 0x1p-64;

double z = x + y;

return z;

}

```

If computations follows the IEEE-754 standard, the result should be  $1.0 + 2^{-52}$ , but if compiled using the x87 FPU, a *double rounding* happens and the result is 1.0. The latter compilation does not *strictly* follows the standard<sup>1</sup>.

In the context of static verification, FP computations have been considered in part. In analysis based on the abstract interpretation framework, support for FP computations is proposed in tools like Fluctuat [15] and Astrée [14]. Generally speaking, FP arithmetic has been formalized since 1989 to formally prove hardware components or algorithms [11, 20, 25].

However, there are very few attempts to analyze FP programs in the so-called *extended static checking* techniques, or *deductive verification* techniques, where verification is typically performed by producing proof obligations, which are formulas to be shown valid using theorem provers. In this context, complex behavioral properties are formally specified, using specification languages such as JML [9] for Java, ACSL [5] for C, Spec#[4] for C#. The support for floating-point computations in such approaches is poorly studied. In 2006, Leavens [22] enumerates a set of possible traps when one attempts to specify FP programs. In 2007, Boldo and Filliâtre [6] propose both a specification language to specify FP programs and an approach to generate proof obligations to be proved in the Coq proof assistant. In 2010, Ayad and Marché [2] extended this to the support of special values and to the use of automated theorem provers. However, the former approaches assume that the compiler strictly follows the IEEE-754 standard. In other words, on the example above they can prove that the result is  $1 + 2^{-52}$ .

<sup>&</sup>lt;sup>1</sup>The term *strict* here refers to the -fp-model strict or /fp:strict options on C compilers, or the strictfp keyword of Java, which explicitly require the compilation to strictly conform to the standard.

In 2010, Boldo and Nguyen [7, 8] proposed a deductive verification approach which is compiler and architecture *independent*, is the sense that the behavioral properties that can be proved valid on a FP program are true whatever does the compiler (up to some extent). On the same example, the only property that can be proved is that the result is between 1 and  $1 + 2^{-52}$ . In this paper, we propose an approach which is compiler and architecture *dependent*: the requirements are proved valid with respect to the assembly code generated by the compiler. At the level of the assembly, all architecturedependent information is known, such as the precision of each operation.

In Chapter 2, we present the necessary background needed on assembly code on one hand, and on the Why platform on the other hand. Chapter 3 first considers a reduced class of "simple" C programs to present the main principles of our approach. Chapter 4 then specifically focuses on floating-point computation and how the specificities of the compiler and architecture are taken into account. Chapter 5 presents how we deal with programs containing conditional statements and loops, that is when the assembly code contains jump statements. Chapter 6 considers the case of programs involving arrays, for which we need to change our so-called memory model. Chapter 7 concludes with comparisons to related works and perspectives.

# Chapter 2

# **Basic background**

An assembly language is a low-level programming language. It is directly influenced by the instruction set and architecture of the processor.

A program written in assembly language consists of a series of statements.

GNU Assembler, commonly known as GAS, is the default back-end of GCC and it is a part of the GNU Binutils package. By default, on the x86 and x86-64 architecture, it uses the AT&T assembler syntax. We uses GCC to generate assembly code, only AT&T syntax will be used in this document.

# 2.1 Assembly language

## 2.1.1 Operands

An operand in assembly language may be a register, a memory reference or a constant.

Registers are preceded by '%'. For example: the EAX register is specified as %eax

Memory references Memory references in AT&T syntax has the following form: section:disp(base, index, scale)

where base and index are the optional 32-bit base and index registers, disp is the optional displacement, and scale, taking the values 1, 2, 4, 8, and multiplies index to calculate the address of the operand. If there is no scale specified, it takes 1. section specifies the optional section register for memory operand.

For example, in AT&T syntax:

- -4 (%rbp): base is '%rbp'; disp is '-4'. index, scale are both missing.

- foo(, %eax, 4): index is '%eax'; scale is '4'; disp is 'foo'. All others fields are missing.

In this model, we suppose that there is no section, this means that there is only one section in the memory.

The x86-64 architectures add an RIP (instruction pointer relative) addressing. This addressing mode is specified by using '*rip*' as a base register. Only constant offsets are valid. For example, in AT&T syntax:

- 1234 (%rip) points to the address 1234 bytes past the end of the current instruction.

- symbol (%rip) points to the symbol in RIP relative way [17].

Immediate operands are preceded by '\$'. For example: \$1, \$12

# 2.1.2 Instruction Naming

In AT&T syntax, instruction mnemonics are suffixed with one character modifiers which specify the size of operands. The letter 'b', 'w', 'l', and 'q' specify byte, word, long and quadruple words operands. If no suffix is specified, GAS will try to fill in the missing suffix based on the destination register operand.

# 2.1.3 General-purpose instructions

Assembly language statements are entered one per line in the source file. All the assembly language statements use the same format:

[label] mnemonic [operands] [comment]

The fields in the square brackets are optional in some statements.

In this section, we only talk about the general-purpose instructions, floating-point instructions does not include.

Also note that the order of source operands and destination operand is reversed in AT&T syntax. This means that source operand is on the left-hand side.

#### Data transfer instructions

The *mov* instruction uses to transfer data from source operand to destination operand. It requires two operands and has the syntax:

## mov source, destination

The data is copied from source to destination and the source operand remains unchanged. Both operands should be of the same size. The *mov* instruction can take one of the following five forms:

- mov register, register

- mov immediate, register

- mov immediate, memory

- mov register, memory

- mov memory, register

#### **Binary Arithmetic Instructions**

**INC and DEC Instructions** These instructions can be used to either increment or decrement the operands by one. The inc (INCrement) instruction adds one to its operand and the dec (DECrement) instruction subtracts one from its operand. Both instructions require a single operand. The operand can be either in a register or in memory. It does not make sense to use an immediate operand such as inc 55 or dec 109. The general format of these instructions is

$inc \ destination$

# dec destination

where destination may be an 8-, 16- or 32-bit operand.

# **ADD/SUB/MUL/DIV Instructions**

The following instructions make a binary calculation. They can be used to add/sub/mul/div two 8-, 16- or 32-bit operands.

| add source, destination | destination = destination + source |

|-------------------------|------------------------------------|

| sub source, destination | destination = destination - source |

| mul source, destination | destination = destination * source |

| div source, destination | destination = destination / source |

## **CMP Instructions**

The cmp (CoMPare) instruction is used to compare two operands (equal, not equal, and so on). The cmp instruction performs the same operation as the sub except that the result of subtraction is not saved. Thus, cmp does not disturb the source and destination operands. The cmp instruction is typically used in conjunction with a conditional jump instruction for decision making [13, 24].

# 2.1.4 Assembler directives

Here are some assembler directives we will see in our examples.

#### .comm symbol, length

.comm declares a common symbol named symbol. When linking, a common symbol in one object file may be merged with a defined or common symbol of the same name in another object file. If *ld* does not see a definition for the symbol – just one or more common symbols – then it will allocate length bytes of uninitialized memory. length must be an absolute expression. If *ld* sees multiple common symbols with the same name, and they do not all have the same size, it will allocate space using the largest size.

## .globl symbol, .global symbol

.global makes the symbol visible to *ld*. If you define symbol in your partial program, its value is made available to other partial programs that are linked with it. Otherwise, symbol takes its attributes from a symbol of the same name from another file linked into the same program. Both spellings ('.globl' and '.global') are accepted, for compatibility with other assemblers.

#### .cfi\_startproc

.*cfi\_startproc* is used at the beginning of each function that should have an entry in *.eh\_frame*. It initializes some internal data structures.

#### .cfi\_endproc

.*cfi\_endproc* is used at the end of a function where it closes its unwind entry previously opened by .*cfi\_startproc*, and emits it to .*eh\_frame* [17].

# 2.2 Inline assembly

## 2.2.1 Simple Inline Statement

The form of a basic inline statement is:

asm("assembly code");

For example: asm("move %eax, %ebx");

# 2.2.2 Extended Inline Statements

In basic inline assembly, we had only instructions. In extended assembly, we can also specify the operands. The format of the asm statement consists of four components below:

asm ( assembly template : outputs /\* optional \*/ : inputs /\* optional \*/ : clobber list /\* optional \*/ );

where each component is separated by a colon (:). The last three components are optional.

RR nº 7655

Assembly template consists of the assembly language statements to be inserted into the C code. This may be a single instruction or a sequence of instructions.

**Outputs** specify the output operands for the assembly code. The format specifying each operand is "=option-constraint"

where option-constraint may be

- r register operand constraint

- m memory operand constraint

- rm register or memory

- ri register or immediate

- g general

**Inputs** are specified in the same why, except for the = sign.

Clobber list is the list of registers modified by the assembly instructions

The operands specified in the output and input parts are assigned sequence numbers 0, 1, 2.... For example: asm( "movl 0, 1, 1"

```

:"=r"(sum)/*output */

:"r"(number1)/*input */);

```

The C variables *sum* and *number1* are both mapped to registers. In assembly code statement, *sum* is identified by %0 and *number1* by %1.

We can put the keyword volatile after asm if our Assembly statement must execute where it is put. Its form is

asm volatile (...: ...: ....)

# **2.3** Why: a software verification platform

Why is a generic platform for deductive verification [19]. It is generic on the front-end side since it is an intermediate language for higher-level like C or Java. It is generic on the side of output since it can produce proof obligations for different provers.

In the input language of Why, one can define a pure model in the logic world by declaring abstract sort names, declaring logic symbols operating on these sorts and posing first-order axioms to axiomatize the behavior of these symbols. Equality and both integer and real arithmetic are built-in in the logic. One can then declare a set of *references* which are mutable variables denoting logic values. Finally, one can define procedures which can modify these references. The body of such a procedure is made of statements in a while-style language. Procedures are also equipped with preand post-conditions. The Why VC generator then produces the necessary VCs to ensures that the body respects the post-condition.

One can alternatively just *declare* procedures by only giving pre- and post-conditions, but also declaring the set of modified references. This feature allows to declare how the atomic operations on a given data type behave. We use this feature extensively in the remaining.

# 2.4 Frama-C and the ACSL specification language

Frama-C is a framework for static analysis of C source code. Its architecture is modular: a kernel is provided which performs parsing and typing of source code, to which analyzers can plug-in. The parser is able to parse formal annotations given as a special kind of comments. The formal language of these annotations is ACSL [5]. Examples of such annotations will come along this paper.

# Chapter 3

# **Case of Simple programs**

In this chapter we describe the main principles of our approach, on a reduced class of C programs called "simple", described below.

# **3.1** Overview of the approach

Our approach for proving a C source via analyzing its assembly is made in several steps illustrated on Figure 3.1. The figure in the left hand-side is all steps to prove a program with assembly code. The one in the right hand-side instantiates these steps concretely for the proof of some program foo.c.

In C program, all annotations are put in comments. When gcc generates assembly code, these annotations will be ignored. As we need them to prove the program, a preprocessing step is needed. This step puts all annotations into inline assembly in order to keep them in assembly code. This is detailed in Section 3.4.

Once preprocessing is done, another C file is generated. The regular GNU compiler gcc is called with option -S to generate assembly code from this C file.

The translation from assembly to Why is implemented in a our own modified version of the GNU assembler as. This step generates a file containing proof obligations in Why. These obligations are then attempted to be proved by automatic provers.

| C program + A         | CSL annotations | fo       | 0.C                  |

|-----------------------|-----------------|----------|----------------------|

| ad-hoc preprocessing  |                 |          | ./inlineasm foo.c    |

| C program + i         | nline assembly  | foo_ir   | uline.c              |

| regular C compilation |                 |          | gcc -S foo_inline.c  |

| Assemb                | ly code         | foo_ii   | ↓<br>nline.s         |

| modified assembler    |                 |          | ./as-new foo_inline. |

| Proof obligat         | ions in WHY     | foo_inli | ine.why              |

| proof                 |                 |          | gwhy foo_inline.why  |

| Automati              | c provers       | Automati | č provers            |

|                       |                 |          |                      |

Figure 3.1: Step-by-step from C program to WHY proof obligations

S

```

/*@ requires n >= 0 && n < 100; */

int f(int n){

int tmp = 100 - n;

//@ assert tmp > 0;

//@ assert tmp <= 100;

return tmp;

}</pre>

```

Figure 3.2: A simple program

# 3.2 Definition of the class of "simple" C programs

Simple C programs considered in this chapter are made of a set of functions definitions, specified with ACSL-style annotations, which satisfies these restrictions:

- The only data type is the type int which is assumed to denote 32-bit 2-complement integers. In particular there are no float types, no arrays and no pointers.

- · There are no global variables but only local variables and arguments of the functions

- The body of any function is restricted to a sequence of assignments, i.e. there is no compound instructions: no loop statements of any kind, no if and no switch statements and no goto.

- The allowed expressions are the arithmetic expressions plus the functions calls.

This class of programs is simple for us because the corresponding assembly codes contain only general-purpose instructions, neither jump instructions nor any floating-point instructions.

**Example 3.1 (A simple example)** This small example (Figure 3.2) has a function int f(int n) that returns the value of 100 - n. It is found in the documentation of ACSL [5]. The precondition of this function is  $0 \le n < 100$ . We have two assertions in the body of the function. These are tmp > 0 and  $tmp \ge 100$ .

The assembly code of this program (See Figure 3.3) is generated by the default option of gcc. There are only three basic instructions to use: transfer data with mov instruction, subtract instruction and instructions for returning from a function.

The function **f** in assembly code is defined as a global symbol with its type is **@function**(line 3–4). This means that this function is visible in other files. A label **f** begins this function. The body of this function is between two directives **.cfi\_startproc** and **.cfi\_endproc**.

As one can see, ACSL annotations appear between **#APP** and **#NO\_APP** in assembly code. All the lines between **#APP** and **#NO\_APP** are indeed ignored by the GNU assembler. We use this feature for putting annotations, this is described in Section 3.4.

# **3.3** Translation to Why

Now we will detail the translation of assembly code to Why. We present firstly how to translate operands to Why. Secondly, we will talk about how to translate instructions to Why. Finally, it is the translation of annotations.

# 3.3.1 Translation of 32-bit integers

Why only have unbounded mathematical integers built-in. Thus, 32-bits integers must be defined in Why. We follow here the same technique as what is done in the Jessie plug-in of Frama-C.

The type *int32* is an abstract type for an 32-bit integer.

```

.file

"simple.c"

1

2

.text

.globl f

3

f, @function

4

.type

f :

5

.LFB0:

6

7

.cfi_startproc

8

. . . .

9

movl

\% edi, -20(\% rbp)

10

#APP

# 2 "simple.c" 1

11

/*requires #int#-20(%rbp)# >= 0 && #int#-20(%rbp)# < 100;*/

12

# 0 "" 2

13

#NO_APP

14

-20(\% rbp), %eax

movl

15

$100, %edx

movl

16

movl

%edx, %ecx

17

%eax, %ecx

subl

18

19

movl

% ecx, % eax

20

movl

\%eax, -4(\%rbp)

21

#APP

# 4 "simple.c" 1

22

/* assert #int#-4(%rbp)# > 0;*/

23

# 0 "" 2

24

# 5 "simple.c" 1

25

/* assert #int#-4(%rbp)# <= 100;*/

26

# 0 "" 2

27

#NO_APP

28

-4(\% rbp), %eax

movl

29

leave

30

31

.cfi_def_cfa 7, 8

32

ret

33

.cfi_endproc

34

. . . .

```

Figure 3.3: Assembly code of the example of Figure 3.2

```

type int32

logic integer_of_int32: int32 -> int

```

*integer\_of\_int32* returns an integer value from an *int32*.

We need a predicate *is\_int32* which verifies whether an integer is in the range of 32-bit word or not.

predicate is\_int32(x: int) = -2147483648 < x and x < 2147483647

We have an axiom

axiom int32\_coerce: forall x:int32, is\_int32(integer\_of\_int32(x))

Although the 8- and 16- integers are considered here for simplicity, they could be handled similarly, as it is in Jessie.

## **3.3.2** Translation of operands

We want to translate operands of kind register or memory reference into Why variables. To do so, we make the following hypothesis:

**Assumption 3.2 (Separate Assumption)** On a simple C program, the compiler generates an assembly code where syntactically distinct memory references denote disjoint memory locations.

For example, we assume that in any assembly code, the memory references -16(\$rbp) and -8(\$rax) are disjoint. Of course there is not reason that this is true in general, but we claim that for the "simple" C programs considered here, and our GNU compiler, this is true. Note that in Chapter 6, this assumption will not be made anymore.

The Separation Assumption allows us to translate each memory reference into a Why variable whose name is syntactically derived from it.

For the simplicity, we ignore the size of the register. This means that <code>%ax</code>, <code>%eax</code> and <code>%rax</code> has the same name \_rax. Once we have this, we do not need to cast from <code>%ax</code> to <code>%eax</code> <code>%rax</code> and otherwise.

The following abstract type and logic function will be used in this section:

type register

Each register or memory reference used as an operand will be declared as a variable with type register.

logic sel\_int32: register -> int32

The logic function *sel\_int32* returns an 32-bit integer from a *register*.

We distinguish two types of operands as follows:

- Immediate operand: begins by '\$'. There is not any declaration here because this operand is a constant. What we do is to delete the prefix '\$'.

- Registers and memory references: We denote by op the variable in Why corresponding to the operand. Each register or memory reference will have a unique name in Why. In this document, we name the register or memory reference by replacing all special character (()+-%.) by '\_'.

Example:  $-4(\% rbp) = -4\_rbp\_$ . The variable in Why to declare for this operand is *parameter* \_4\_rbp\_: register ref

We denote

- $\llbracket imm \rrbracket_{int32} = imm$

- $[reg]_{int32} = (integer_of_int32 (sel_int32 !reg))$

- $[mem]_{int32} = (integer_of_int32 (sel_int32 !mem))$

## 3.3.3 Translation of instructions

The move instructions and addition/subtraction/multiplication/division instructions are translated thank to the following abstract function in Why program:

```

parameter set_int32_no_check: imm:int -> dest: register ref ->

{ }

unit writes dest

{ integer_of_int32(sel_int32(dest)) = imm }

```

This abstract function will set an 32-bit integer to a register without verifying if this value is overflow or not.

```

parameter set_int32: imm:int -> dest: register ref ->

{ is_int32(imm) }

unit writes dest

{ integer_of_int32(sel_int32(dest)) = imm }

```

The post-condition of set\_int32 is the same as set\_int32\_no\_check. We denote by

- [ ins  $]_i$  the Why translation of an instruction *ins*,

- op the Why interpretation of op as a left-value

- $[\![op]\!]_r$  the Why interpretation of *op* as a right value

Instructions in assembly code are interpreted to Why as follows:

Note that leave and ret are instructions in assembly language but they do not have any translation here.

As specified in the documentation, *src* of the instruction *movl* is either a constant, a register or a memory reference in 32 bits. Therefore, we do not need to verify if it is overflow or not. However, for addition/subtraction/multiplication instructions, we need to assure that this computation does not overflow.

The case of division cannot be handled as other operations since the divisor must be check nonnull. We thus use

```

\llbracket \text{divl src, dest } \rrbracket_i = \text{div\_int32 } \llbracket src \rrbracket_{int32} \text{ dest}

\llbracket \text{idivl src, dest } \rrbracket_i = \text{div\_int32 } \llbracket src \rrbracket_{int32} \text{ dest}

with the special Why parameters:

```

```

parameter div_int32: imm: int32 -> dest: register ref ->

{

imm <> 0

and

is_int32(computer_div(integer_of_int32(sel_int32(dest),imm)))

}

unit writes dest

{

integer_of_int32(sel_int32(dest)) =

computer_div(integer_of_int32(sel_int32(dest)),imm)

}

```

The function computer\_div is defined in Why standard library and denotes the integer division which rounds the result towards 0, which corresponds to the usual convention for division in C and other programming languages.

## **3.3.4** Translation of a sequence of instructions

A function in assembly code is a sequence of instructions. All we have until now is the interpretation of each separate instruction. What we need is how to assure that the state at a instruction corresponds to a state in Why. This will be presented in Theorem 3.3.

**Theorem 3.3** Let S be one state in assembly program,  $\overline{S}$  be the state in Why corresponding to S,  $R(S,\overline{S})$  be the relation between S and  $\overline{S}$ .

$\forall S, \overline{S}, i: R(S, \overline{S}) \land (S, i \Rightarrow S') \land (\overline{S}, \llbracket i \rrbracket \Rightarrow \overline{S'}) \longrightarrow R(S', \overline{S'})$

# 3.4 Annotations

# 3.4.1 Types of annotations interpreted

The annotations mentioned in this section are:

- · preconditions

- · post-conditions

- assertions

Normally, when assembly code is generated, all the comments in C after // or between /\* and \*/ will be eliminated. The annotations are thus disappeared in assembly code. In order to keep these annotations in assembly code, we need a pre-processing step which will be presented in 3.4.2.

Note that in this document, both ACSL annotations and Why annotations are authorize. This is the reason why we don't use Frama-C plugin.

# 3.4.2 Preprocessing: keeps annotations in assembly code

The goal of this step is to create a new C file which contains inline assembly in order to have annotations in the assembly file generated. The idea is that we put all annotations in inline assembly statements.

This step follows several steps:

- Firstly we detect all the variables in the program and their types. We use an array to store these variables.

- With assertion: if the assertion is in  $n^{th}$  line, we only need to find global variables, function parameters and local variables (in the function containing this assertion) declared before line n.

- With precondition and post-condition: function parameters may be needed in this kind of annotation. Therefore, we have to get all function parameters and their type. Then put the annotations after the function declaration (more precisely, after '{').

- Replace variables in annotation: Each time we meet a variable in annotation, we will replace it by "#type#argument#" where *type* is the type of variable, *argument* has format '%' + *order number*. The syntax of inline assembly was mentioned in Chapter 2.

- Put the annotation replaced in inline assembly statement.

By using this syntax of inline assembly, we are able to have directly the memory reference/register corresponding to the variable when compiling. For example, an annotation in ACSL :

/\*@ requires n >= 0 && n < 100;\*/

is put in inline assembly as the following format:

$\begin{array}{cccc} \text{f:} & \longrightarrow & \text{let f()} = \\ .\text{cfi\_startproc} & & \\ & /*@ \ \text{requires } P; \ */ & \longrightarrow & \text{assumes } \{\llbracket P \rrbracket_{annot} \}; \\ & (\text{body of the function f)} & \longrightarrow & \llbracket (\text{body of the function f)} \rrbracket_i \\ & /*@ \ \text{ensures } Q; \ */ & \longrightarrow & \text{assert } \{\llbracket Q \rrbracket_{annot} \}; \\ & \text{leave} & & \text{void} \\ & \text{ret} \\ .\text{cfi\_endproc} & & parameter \ f: \ unit \ -> \\ & \{ \llbracket P \rrbracket_{annot} \} \ unit \ \text{writes } w \ \{ \llbracket Q \rrbracket_{annot} \} \end{array}$

Figure 3.4: Translation of a function in assembly to Why

asm volatile("/\*requires #int#%0# >= 0 &&

#int#%1# < 100;\*/"::"X"(n),"X"(n));</pre>

"%0", "%1" are replaced by the memory reference of the variable n.

This inline assembly will then be translated in assembly code as follows:

/\*requires #int#-20(%rbp)# >= 0 && #int#-20(%rbp)# < 100;\*/

It is not easy to know exactly type of a memory reference/register in assembly code. Here, thank to inline assembly, we have both memory reference/register and type of variable in C.

This preprocessing step will deplace precondition and put it after the declaration of the function, other words, put it after ". The post-condition will move to the line before return value. Once this is done, we have memory reference/register of the variables in both pre- and post-condition and even the one of the abstract variable \result.

In a program, we have many return and it will be a bad idea if we put each post-condition before each return. We add a new variable res with the type is the type of the returned value. We analyze the code source C and replace each return v; by {res = v; goto Lres;}. At the end of the program, before ", we put Lres: return res;. If there is a post-condition, put it between the Lres: and return res;

In Why, each function will have a Why interface with the input and output are registers (as they are input and output of a function in assembly language). However, maybe the variables of the annotation are memory reference. This is the reason why we need to match memory references with input/output registers. To do this, we create an array and find only in the **mov** instructions all the operands and match the input register and the memory reference. When creating the function interface, we simply replace the memory reference in precondition and post-condition by the corresponding register.

# 3.4.3 Translation of annotations in assembly to Why

Now we have annotations in assembly file. The question is how to translate these annotation to Why? We already know that all inline assembly are put between #APP and #NO\_APP, it is thus easy to identify where annotations are in assembly code.

We denote by  $[\![A]\!]_{annot}$  the translation of an annotation to Why and

$[v]_{int32@} = integer_of_int32 (sel_int32 (v))$

Assume that we have a function with preconditions, post-conditions and assertions. The translation of this function in assembly to Why is illustrated in Figure 3.4. As we see in this figure, the post-condition becomes an assertion in Why.

For each function with pre- and post-condition, we define an interface of function in Why (See Figure 3.4) where w is is a set of variables modified in the function.

The translation of annotations to Why is described in the table below:

| $\llbracket A ==> B \rrbracket_{annot}$        | = | $\llbracket A \rrbracket_{annot} \rightarrow \llbracket B \rrbracket_{annot}$      |

|------------------------------------------------|---|------------------------------------------------------------------------------------|

| $\llbracket A == B \rrbracket_{annot}$         | = | $\llbracket A \rrbracket_{annot} = \llbracket B \rrbracket_{annot}$                |

| $\llbracket A \&\& \& B \rrbracket_{annot}$    | = | $\llbracket A \rrbracket_{annot}$ and $\llbracket B \rrbracket_{annot}$            |

| $\llbracket A \mid \mid B \rrbracket_{annot}$  | = | $\llbracket A \rrbracket_{annot}$ or $\llbracket B \rrbracket_{annot}$             |

| $\llbracket !A \rrbracket_{annot}$             | = | not( $\llbracket A \rrbracket_{annot}$ )                                           |

| [[#int#v#]] <sub>annot</sub>                   | = | $\llbracket v \rrbracket_{int32@}$                                                 |

| $[\abs(#int#v#)]_{annot}$                      | = | abs_int([[#int#v#]] <sub>annot</sub> )                                             |

| $\llbracket e_1 \ op \ e_2 \rrbracket_{annot}$ | = | $[\![e_1]\!]_{annot} op [\![e_2]\!]_{annot}$ where $op \in \{+,-,*,/\}$            |

| $\llbracket e_1 \ op \ e_2 \rrbracket_{annot}$ | = | $[e_1]_{annot} op [e_2]_{annot}$ where $op \in \{>, <, >=, <=, !=\}$               |

| $[\![\forall 	au i; P]\!]_{annot}$             | = | forall $i: \llbracket \tau \rrbracket_{annot}$ . $\llbracket P \rrbracket_{annot}$ |

| $[\![ exists \ 	au \ i; P ]\!]_{annot}$        | = | exists $i: \llbracket \tau \rrbracket_{annot}$ . $\llbracket P \rrbracket_{annot}$ |

| $\llbracket integer \rrbracket_{annot}$        | = | int                                                                                |

# 3.5 Examples

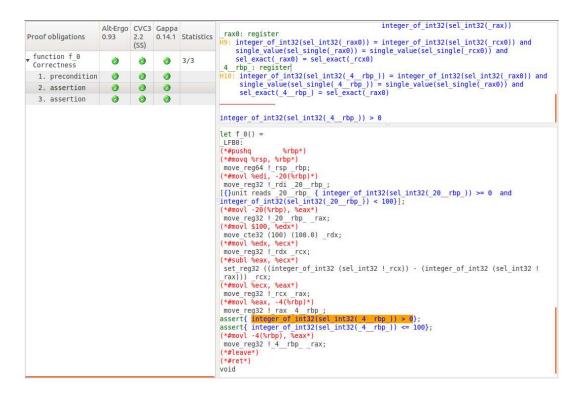

Figure 3.5 is the Why program of the assembly code in Example 3.1. The result of this Why program is in Figure 3.6.

```

parameter f_parameter: _: unit->

{integer_of_int32(sel_int32(_rdi)) >= 0 and

integer_of_int32(sel_int32(_rdi)) < 100}

unit reads _rdi

{true}

let f_0() =

_LFB0:

(*#pushq

%rbp *)

(*#movq %rsp, %rbp*)

move_reg64 !_rsp _rbp;

(*#movl %edi, -20(%rbp)*)

move_reg32 !_rdi _20__rbp_;

[{}unit reads _20_rbp_ { integer_of_int32(sel_int32(_20_rbp_)) >= 0

and

integer_of_int32(sel_int32(_20__rbp_)) < 100}];

(*#movl -20(\%rbp), \%eax*)

move_reg32 !_20__rbp_ _rax;

(*#movl $100, %edx*)

move_cte32 (100) (100.0) _rdx;

(*#movl %edx, %ecx*)

move_reg32 !_rdx _rcx;

(*#subl %eax, %ecx*)

set_reg32 ((integer_of_int32 (sel_int32 !_rcx))

- (integer_of_int32 (sel_int32 !_rax))) _rcx;

(*#movl %ecx, %eax*)

move_reg32 !_rcx _rax;

(*#movl \ \%eax, -4(\%rbp)*)

move_reg32 !_rax _4__rbp_;

assert { integer_of_int32(sel_int32(_4_rbp_)) > 0};

assert{ integer_of_int32(sel_int32(_4__rbp_)) <= 100};

(*#movl -4(\%rbp), \%eax*)

move_reg32 !_4_rbp_ _rax;

(*#leave *)

(*#ret *)

void

```

Figure 3.5: Why program of Figure 3.3

Figure 3.6: Result of Figure 3.5 program

# Chapter 4

# **Floating-point programs**

Chapter 3 talks about the translation of the program containing only 32-bit integer type. In this chapter, we will extend it with the computation in both integer and floating-point. There are some points we need to rewrite in order to make it true in both integer and floating-point computation.

# 4.1 Definition of programs

This chapter is an extension of the previous one. The programs concerned are the one support for both int, long, float and double. Certainly, the annotations can contain variables with those type. An interesting point of this chapter is that we will show the different results obtained by compiling a floating-point program with different mode of compiler and architecture.

# 4.2 Assembly with floating-point arithmetic

Before entering to the translation, we give some basic knowledge about the different modes: SSE/SSE2, x87 and FMA and their instructions.

# 4.2.1 SSE/SSE2

Intel MMX (MultiMedia eXtensions) technology introduced single-instruction multiple-data (SIMD) capacity into the IA-32 architecture, with the 64-bit mmx registers, 64-bit packed integer data types, and instructions that allowed SIMD operations to be performed on packed integers. SSE extensions expand the SIMD execution model by adding facilities for handling packed and scalar single-precision floating-point value contained in 128-bit registers.

SSE2 is a major enhancement to SSE. It adds new maths instructions for double-precision (64-bit) floating-point and also extends mmx instructions to operate on 128-bit xmm registers.

#### **Data Transfer Instruction**

| movsd xmm1 xmm2/m64 | Move scalar double-precision floating-point value from xmm1 reg-   |

|---------------------|--------------------------------------------------------------------|

|                     | ister to xmm2/m64                                                  |

| movsd xmm2/m64 xmm1 | Move scalar double-precision floating-point value from xmm2/m64    |

|                     | to xmm1 register                                                   |

| movss xmm1 xmm2/m32 | Move scalar single-precision floating-point value from xmm1 regis- |

|                     | ter to xmm2/m632                                                   |

| movss xmm2/m32 xmm1 | Move scalar single-precision floating-point value from xmm2/m32    |

|                     | to xmm1 register                                                   |

|                     |                                                                    |

These instructions move a scalar double-precision (single-precision) floating-point value from the source operand (first operand) to the destination operand (second operand). The source and destination operands can be xmm registers or 64-bit (32-bit) memory locations.

#### **Packed Arithmetic Instructions**

| addsd xmm2/m64, xmm1 | Add the low double-precision floating-point value from xmm2/m64 to xmm1                                                   |

|----------------------|---------------------------------------------------------------------------------------------------------------------------|

| addss xmm2/m32, xmm1 | Add the low single-precision floating-point value from xmm2/m32 to xmm1                                                   |

| subsd xmm2/m64, xmm1 | Subtracts the low double-precision floating-point values in xmm2/mem64 from xmm1                                          |

| subss xmm2/m32, xmm1 | Subtracts the low single-precision floating-point values in xmm2/mem32 from xmm1                                          |

| mulsd xmm2/m64, xmm1 | Multiply the low double-precision floating-point value in xmm2/mem64 by low double-precision floating-point value in xmm1 |

| mulss xmm2/m32, xmm1 | Multiply the low single-precision floating-point value in xmm2/mem32 by low single-precision floating-point value in xmm1 |

| divsd xmm2/m64, xmm1 | Divide low double-precision floating-point value in $xmml$ by low                                                         |

|                      | double-precision floating-point value in xmm2/mem64                                                                       |

| divss xmm2/m32, xmm1 | Divide low single-precision floating-point value in xmm1 by low single-precision floating-point value in xmm2/mem32       |

#### **Comparison Instructions**

comisd xmm2/m64, xmm1 comiss xmm2/m32, xmm1 ucomisd xmm2/m64, xmm1 ucomiss xmm2/m32, xmm1

comisd and comiss compare the double-precision (single-precision) floating-point values in the low quadwords (doublewords) of first operand and second operand, and sets the ZF, PF, and CF flags in the EFLAGS register according to the result (unordered, greater than, less than, or equal). The OF, SF and AF flags in the EFLAGS register are set to 0. In our model, we consider that there is no difference between ucomiss/ucomisd and comiss/comisd.

# **Conversion Instructions**

## 4.2.2 x87 Floating-point Unit

The x87 floating-point unit (FPU) instructions are executed by the processor's x87 FPU. These instructions operate on floating-point, integer and binary-coded decimal(BCD) operands.

# **FPU registers**

This FPU provides several registers. These registers are divided into three groups: data registers, control and status registers, and pointer registers.

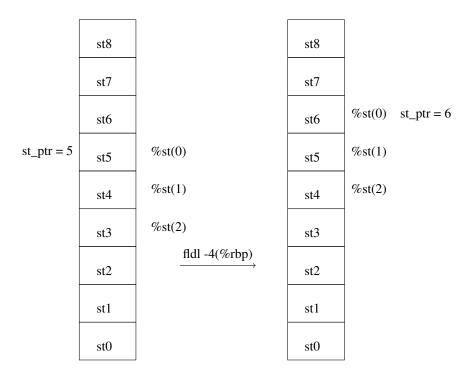

The FPU has 8 floating-point registers to hold the floating-point operands. These registers supply the necessary operands to the floating-point instructions. Unlike the processor's general-purpose registers such as the eax and ebx registers, these registers are organized as a register stack. In addition, we can access these registers individually using st0, st1, and so on.

Since these registers are organized as a register stack, these names are not statically assigned. That is, st0 does not refer to a specific register. It refers to whichever register is acting as the top-of-stack (TOS) register. The next register is referred to as st1, and so on; the last register as st7. There is a 3-bit top-of-stack pointer in the status register to identify the TOS register.

Each data register can hold an extended-precision floating-point number. This format uses 80 bits as opposed to single-precision (32 bits) or double-precision (64 bits) formats. The rationale is that these registers typically hold intermediate results and using the extended format improves the accuracy of the final result.

|     | sign | exponent | mantissa |

|-----|------|----------|----------|

| ST7 |      |          |          |

| ST6 |      |          |          |

| ST5 |      |          |          |

| ST4 |      |          |          |

| ST3 |      |          |          |

| ST2 |      |          |          |

| ST1 |      |          |          |

| ST0 |      |          |          |

Figure 4.1: FPU data registers

# x87 FPU instructions

Most floating-point instructions requires one or two operands, located on the x87 FPU data-register stack or in memory. When an operand is located in a data register, is is referenced relative to the st(0) register, rather than by a physical register name. Often the st(0) is an implied operand.

These instructions are divided into the following groups: data transfer, load constants, and FPU control instructions.

**Data Transfer Instructions** The data transfer instructions perform the following operations:

- Load a floating-point, integer, or packed BCD operand from memory into the st (0) register.

- Store the value in an st (0) register to memory in floating-point, integer, or packed BCD format.

- Move values between registers in the x87 FPU register stack.

**Load Constant Instructions** The following instructions push commonly used constants onto the top st(0) of the x87 FPU register stack:

| fldz   | Load +0.0        |

|--------|------------------|

| fld1   | Load +1.0        |

| fldpi  | Load $\pi$       |

| fld12t | Load $log_2 10$  |

| fldl2e | Load $log_2 e$   |

| fld1g2 | Load $log_{10}2$ |

| fldln2 | Load $log_e 2$   |

**Basic Arithmetic Instructions** These are the floating-point instructions perform basic arithmetic operations on floating-point numbers:

| fiadd          | Add integer to floating point                                                 |

|----------------|-------------------------------------------------------------------------------|

| fsub/fsubp     | Subtract floating point                                                       |

| fisub          | Subtract integer from floating point                                          |

| fsubr/fsubrp   | Reverse subtract floating point                                               |

| fisubr         | Reverse subtract floating point from integer                                  |

| fmul/fmulp     | Multiply floating point                                                       |

| fimul          | Multiply integer by floating point                                            |

| fdiv/fdivp     | Divide floating point                                                         |

| fidiv          | Divide floating point by integer                                              |

| fdivr/fdivrp   | Reverse divide                                                                |

| fidivr         | Reverse divide integer by floating point                                      |

| fabs           | Absolute value                                                                |

| fchs           | Change sign                                                                   |

| The add subtra | ct multiply and divide instructions operate on the following types of operate |

The add, subtract, multiply and divide instructions operate on the following types of operands:

25

- Two x87 FPU data registers

- An x87 FPU data register and a floating-point or integer value in memory

Reverse versions of the subtract (fsubr) and divide (fdivr) instructions enable efficient coding. For example, the following options are available with the fsub and fsubr instructions for operating on values in a specified x87 FPU data register st(i) and the st(0) register: fsub:

$\begin{array}{c} \mathrm{st}(0) \leftarrow \mathrm{st}(0) - \mathrm{st}(i)\\ \mathrm{st}(i) \leftarrow \mathrm{st}(i) - \mathrm{st}(0)\\ \texttt{fsubr:}\\ \mathrm{st}(0) \leftarrow \mathrm{st}(i) - \mathrm{st}(0)\\ \mathrm{st}(i) \leftarrow \mathrm{st}(0) - \mathrm{st}(i) \end{array}$

The pop versions of the add, subtract, multiply, and divide instructions offer the option of popping the x87 FPU register stack following the arithmetic operation. These instructions operate on values in the st(i) and st(0) registers, store the result in the st(i) register, and pop the st(0) register.

# 4.2.3 FMA

gcc uses AVX instructions when generating assembly code with option -mfma4. Before talking about FMA instructions we will present some AVX instructions.

#### AVX arithmetic instructions

| vaddss xmm3/mem32, xmm2, xmm1 | Add Scalar Single-Precision Floating-Point      |

|-------------------------------|-------------------------------------------------|

| vaddsd xmm3/mem64, xmm2, xmm1 | Add Scalar Double-Precision Floating-Point      |

|                               |                                                 |

| vsubss xmm3/mem32, xmm2, xmm1 | Subtract Scalar Single-Precision Floating-Point |

| vsubsd xmm3/mem64, xmm2, xmm1 | Subtract Scalar Double-Precision Floating-Point |

|                               | -                                               |

| vmulss xmm3/mem32, xmm2, xmm1 | Multiply Scalar Single-Precision Floating-Point |

| vmulsd xmm3/mem64, xmm2, xmm1 | Multiply Scalar Double-Precision Floating-Point |

| vdivss xmm3/mem32, xmm2, xmm1 | Divide Scalar Single-Precision Floating-Point   |

| vdivsd xmm3/mem64, xmm2, xmm1 | Divide Scalar Double-Precision Floating-Point   |

The first source operand is an xmm register and the second source operand is either an xmm register or a 64-bit memory location. The destination is a third xmm register. Bits [127:64] of the first source operand are copied to bits [127:64] of the destination. Bits [255:128] of the ymm register that corresponds to the destination are cleared.

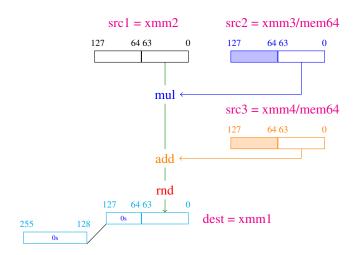

Figure 4.2: Illustration of vfmaddsd instruction

#### **FMA instructions**

Now both AMD and Intel have specifications for FMA. In this document, FMA instructions are generated (thanks to gcc) by FMA4, specified by AMD.

| vfmaddss src3, src2, src1, dest  | $dest = src1^* src2 + src3$ | Multiply and Add Scalar Single-        |  |  |

|----------------------------------|-----------------------------|----------------------------------------|--|--|

|                                  |                             | Precision Floating-Point               |  |  |

| vfmaddsd src3, src2, src1, dest  | $dest = src1^* src2 + src3$ | Multiply and Add Scalar Double-        |  |  |

|                                  |                             | Precision Floating-Point               |  |  |

| vfmsubss src3, src2, src1, dest  | $dest = src1^* src2 - src3$ | Multiply and Subtract Scalar Single-   |  |  |

|                                  |                             | Precision Floating-Point               |  |  |

| vfmsubsd src3, src2, src1, dest  | $dest = src1^* src2 - src3$ | Multiply and Subtract Scalar Double-   |  |  |

|                                  |                             | Precision Floating-Point               |  |  |

| vfnmaddss src3, src2, src1, dest | dest = -(src1* src2) + src3 | Negative Multiply and Add Scalar       |  |  |

|                                  |                             | Single-Precision Floating-Point        |  |  |

| vfnmaddsd src3, src2, src1, dest | dest = -(src1* src2) + src3 | Negative Multiply and Add Scalar       |  |  |

|                                  |                             | <b>Double-Precision Floating-Point</b> |  |  |

| vfnmsubss src2, src2, src1, dest | dest = -(src1* src2) - src3 | Negative Multiply and Subtract Scalar  |  |  |

|                                  |                             | Single-Precision Floating-Point        |  |  |

| vfnmsubsd src3, src2, src1, dest | dest = -(src1* src2) - src3 | Negative Multiply and Subtract Scalar  |  |  |

|                                  |                             | Double-Precision Floating-Point        |  |  |

The implement of vfmaddsd is presented in Figure 4.2. The destination is an xmm register. When the result is written to the destination xmm register, the upper quadword of the destination register (bits 64 - 127) and the upper 128-bits of the corresponding ymm register are cleared to zeros. The intermediate product is not rounded; the infinitely precise product is used in the addition. The result of the addition is rounded.

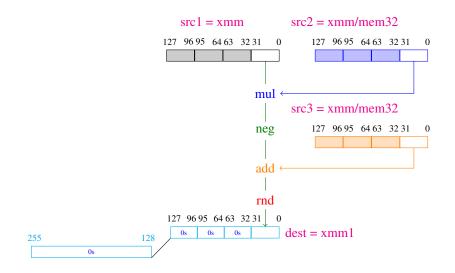

The implementation of vfnmaddss is in Figure 4.3. The destination is always an xmm register. When the result is written to the destination xmm register, the upper three doublewords of the destination register (bits 32 - 127) and the upper 128-bits of the corresponding ymm register are cleared to zeros.

The intermediate products are not rounded; the infinitely precise products are used in the addition. The results of the addition are rounded.

Figure 4.3: Illustration of VFNMADDSS instruction

```

double doublerounding(){

double x = 1.0;

double y = 0x1p-53 + 0x1p-64;

double z = x + y;

//@ assert z == x;

return z;

}

```

Figure 4.4: A simple floating-point program

# 4.3 Examples of the chapter

Two following examples are used for illustrating the translation of floating-point instruction to Why. Their proofs will be presented at the end of this chapter.

# 4.3.1 Double rounding example

This example do the calculation of two *double* values. The goal of this example is to show that the result depends on the architecture and the choice of compiler options. More precisely, with the strict IEEE-754 standard (default option of *gcc*), the returned value of the function *doublerounding()* is  $1 + 2^{-52}$ . When it is compiled on IA32 architecture – the computation on *double* are performed in the long double type inside x87 unit – the result is 1. We insert an assertion //@ assert z == x which will be true in SSE case and won't be proved in x87 case.

We show here a piece of assembly code which shows the difference in these two modes (See Figure 4.5).

On the left hand-side of Figure 4.5, instructions on 64 bits (movabs, movq, movsd, addsd) are used. Thus, all the calculations are in 64 bits (SSE mode). On the right hand-side, the intermediate value are stored in x87 register (80-bit registers) and then it is rounded to 64-bit value (line 5–7). This is called *double rounding* and its value is different from the direct one (SSE mode).

SSE

```

movabsq $4607182418800017408, %rax

1

i movabsq $4607182418800017408, %rax

2

mova

\% rax, -16(\% rbp)

2 movq

\% rax, -16(\% rbp)

movabsq $4368493837572636672, %rax

3 movabsq $4368493837572636672, %rax

3

\% rax, -8(\% rbp)

\% rax, -8(\% rbp)

4 movq

4 movq

5 movsd

-16(\% rbp), % xmm0

5 fldl

-16(\% rbp)

6 addsd

6 faddl

-8(\% rbp), \% xmm0

-8(\% rbp)

\%xmm0, -24(%rbp)

7 movsd

7 fstpl

-24(\% rbp)

```

x87

**Ontimized** level 1

Figure 4.5: Assembly code in SSE mode and x87 mode of Figure 4.4 example

# 4.3.2 Example: Architecture dependent Overflow

Monniaux [23] considers the following program to illustrate differences between architectures with respect to overflows.

```

double foo() {

double v = 1e308;

double y = v * v;

return y/v;

}

```

No optimization

Excerpts of the generated assembly code are shown on Fig. 4.6. The left part corresponds to non-optimized x87 code (precisely, gcc -mfpmath=387 -00) whereas the right part is optimized (-01).

|    | no optim |                                     |    | Optimized, level 1 |                     |  |  |

|----|----------|-------------------------------------|----|--------------------|---------------------|--|--|

| 1  | movabsq  | \$9214871658872686752, % <b>rax</b> | 1  | fldl               | .LC0(%rip)          |  |  |

| 2  | movq     | % rax, $-8(%$ rbp)                  | 2  | fld                | %st(0)              |  |  |

| 3  | fldl     | -8(% <b>rbp</b> )                   | 3  | fmul               | %st(1), %st         |  |  |

| 4  | fmull    | -8(% <b>rbp</b> )                   | 4  | fdivp              | %st, %st(1)         |  |  |

| 5  | fstpl    | -16(% rbp)                          | 5  | fstpl              | -8(% rsp)           |  |  |

| 6  | fldl     | -16(% rbp)                          | 6  | movsd              | -8(% rsp), $% xmm0$ |  |  |

| 7  | fdivl    | -8(% rbp)                           | 7  |                    |                     |  |  |

| 8  | fstpl    | -24(% rbp)                          | 8  | .LC0:              |                     |  |  |

| 9  | movsd    | -24(% rbp), %xmm0                   | 9  | .long              | 2246822048          |  |  |

| 10 |          |                                     | 10 | .long              | 2145504499          |  |  |

Figure 4.6: Optimized versus non-optimized assembly of overflow example

# 4.4 Translation to Why

# 4.4.1 Abstract functions

An integer in 64 bits has type int 64. Like int 32, we define two following logic functions for it:

```

type int64

logic sel_int64: register -> int64

logic integer_of_int64: int64 -> int

predicate is_int64(x: int) =

-9223372036854775808 < x and x < 9223372036854775807</pre>

```

#### We also have an axiom

axiom int64\_coerce: forall x:int64, is\_int64(integer\_of\_int64(x))

In order to get a floating-point value from a register, we need some following logic functions:

logic sel\_single : register -> single logic sel\_double : register -> double logic sel\_80 : register -> binary80 logic sel\_exact : register -> real

The logic functions sel\_single, sel\_double, sel\_80 and sel\_exact return a single, double, binary80 value and exact value, respectively, from a register.

We also need to set a floating-point value to a register. To do that, we need the following parameter functions:

```

parameter set_single_no_check: a:real -> aexact:real -> b:register ref ->

{}

unit writes b

{single_value(sel_single(b)) = a

and

sel_exact(b) = aexact}

parameter set_single: a:real -> aexact:real -> b:register ref ->

{no_overflow_single(\nearest_even,a)}

unit writes b

{single_value(sel_single(b)) = round_single(nearest_even,a)

and

sel_exact(b) = aexact}

```

Each parameter has three arguments: the real value, the exact value and the register to store. Setting a single has two cases:

- Case 1: We don't need to check if the input value is overflow or not. We use it when transferring data from src to dest in the movss instructions. Pay attention that in this case, the value a is not rounded because we already know that it is a 32-bit FP number.

- Case 2: We have to check the input value. This parameter is used when we set a value of a computation (addition, subtraction, etc.) to a register.

We do similarly with double and 80-bit FP value.

```

parameter set_double_no_check: a:real -> aexact:real -> b:register ref ->

{ }

unit writes b

{double_value(sel_double(b)) = a

and

sel_exact(b) = aexact}

parameter set_double: a:real -> aexact:real -> b:register ref ->

{no_overflow_double(\nearest_even, a)}

unit writes b

{double_value(sel_double(b)) = round_double(nearest_even, a)

and

sel_exact(b) = aexact}

parameter set_80_no_check: a:real -> aexact:real -> b:register ref ->

{ }

unit writes b

{binary80_value(sel_binary80(b)) = a

and

sel_exact(b) = aexact}

parameter set_80: a:real -> aexact:real -> b:register ref ->

```

```

{no_overflow_binary80(\nearest_even,a)}

unit writes b

{binary80_value(sel_binary80(b)) = round_binary80(nearest_even,a)

and

sel_exact(b) = aexact}

```

Division is a special case. We need to assure that the denominator is not equal to 0. Different from div, with divr, the numerator and the denominator are reversed.

```

parameter div_single: a:register -> b:register -> c:register ref ->

{single_value(sel_single(a))<>0

and

no_overflow_single(nearest_even,

single_value(sel_single(b))/single_value(sel_single(a)))}

unit writes c

{single_value(sel_single(c)) = round_single(nearest_even,

single_value(sel_single(b))/single_value(sel_single(a)))

and

sel_exact(c) = sel_exact(b)/sel_exact(a) }

parameter div_double: a:register -> b:register -> c:register ref ->

{double_value(sel_double(a))<>0

and

no_overflow_double(nearest_even,

double_value(sel_double(b))/double_value(sel_double(a)))}

unit writes c

{double_value(sel_double(c)) = round_double(nearest_even,

double_value(sel_double(b))/double_value(sel_double(a)))

and

sel_exact(c) = sel_exact(b)/sel_exact(a) }

parameter div_80: a:real -> aexact:real -> b:register ref ->

{a<>0

and

no_overflow_binary80(nearest_even, binary80_value(sel_80(b))/a)}

unit writes b

{binary80_value(sel_80(b)) = round_binary80(nearest_even,

binary80_value(sel_80(b@))/a)

and

sel_exact(b) = sel_exact(b@)/aexact}

parameter divr_80: a:real -> aexact:real-> b:register ref ->

{binary80_value(sel_80(b)) <>0

and

no_overflow_binary80(nearest_even,

a/binary80_value(sel_80(b)))}

unit writes b

{binary80_value(sel_80(b)) = round_binary80(nearest_even,

a/binary80_value(sel_80(b@)))

and

sel_exact(b) = aexact/sel_exact(b0) }

```

where round\_single(mode, value), round\_double(mode, value), round\_binary80(mode, value) have already defined in Why library floats\_common.why.

In assembly language, there are instructions which transfer data from src to dest and we know only their size but we do not know the type of the data. For example, movl is a data transfer instruction but we do not know if it transfer a 32-bit integer or a 32-bit FP number(float type in C). Our idea is that we define a parameter move\_cte32 which copies at the same time an integer value , a single value and its exact value to dest and a parameter move\_cte64 which copies an integer value, a double value and its exact value to dest.

```

parameter move_cte32:a:int-> b:real->bexact:real->c:register ref->

{ }

unit writes c

{

integer_of_int32(sel_int32(c)) = a

and

single_value(sel_single(c)) = b

and

sel_exact(c) = bexact

}

parameter move_cte64:a:int->b:real->bexact:real->c:register ref->

unit writes c

{

integer_of_int64(sel_int64(c)) = a

and

double_value(sel_doule(c)) = b

and

sel_exact(c) = bexact

}

```

We denote by  $[opr]_{int32}, [opr]_{single}, [opr]_{double}$  and  $[opr]_{binary80}$  the interpretation of an operand that return an integer value, a real in 32 bits, 64 bits and 80 bits respectively from a *register*.

We denote by *opr* and operand being register or memory reference. The translation of operands is specified as follows:

| $[\![opr]\!]_{int32}$                                                             | = | <pre>(integer_of_int32 (sel_int32 !opr))</pre>                                         |

|-----------------------------------------------------------------------------------|---|----------------------------------------------------------------------------------------|

| $\llbracket opr \rrbracket_{int64}$                                               | = | (integer_of_int64 (sel_int64 !opr))                                                    |

| $\llbracket opr \rrbracket_{single}$                                              | = | <pre>(single_value (sel_single !opr))</pre>                                            |

| $\llbracket opr \rrbracket_{double}$                                              | = | (double_value (sel_double !opr))                                                       |

| $[opr]_{binary80}$                                                                | = | (binary80_value (sel_80 !opr))                                                         |

| $\llbracket opr \rrbracket_{exact}$                                               | = | ((sel_exact !opr)                                                                      |

|                                                                                   |   |                                                                                        |

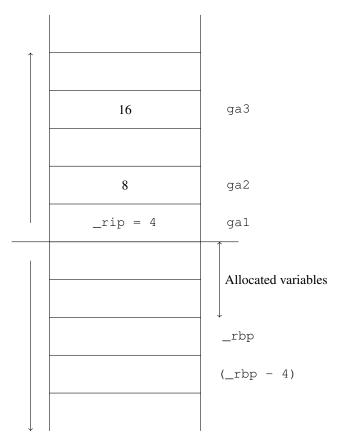

|                                                                                   |   |                                                                                        |