# Conception d'un générateur d'intergiciels temps réel embarqués dans l'automobile.

Karim Dahmen

## ▶ To cite this version:

Karim Dahmen. Conception d'un générateur d'intergiciels temps réel embarqués dans l'automobile.. [Stage] 2007. inria-00586813

# HAL Id: inria-00586813 https://inria.hal.science/inria-00586813

Submitted on 18 Apr 2011

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# RÉPUBLIQUE TUNISIENNE MINISTÈRE DE L'ENSEIGNEMENT SUPÉRIEUR, DE LA RECHERCHE SCIENTIFIQUE ET DE LA TECHNOLOGIE UNIVERSITÉ DE TUNIS EL MANAR

# INSTITUT SUPÉRIEUR D'INFORMATIQUE

# MÉMOIRE DE PROJET DE FIN D'ÉTUDES

Présenté en vue de l'obtention du

Diplôme National d'Ingénieur en Informatique Spécialité : Génie du Logiciel et des Systèmes d'Information

Par

#### **Karim DAHMEN**

# CONCEPTION D'UN GÉNÉRATEUR D'INTERGICIELS TEMPS RÉEL EMBARQUÉS DANS L'AUTOMOBILE

Organisme d'accueil

#### **LORIA - INRIA Lorraine**

Laboratoire Lorrain de recherche en Informatique et ses Applications - UMR 7503.

Encadrants à l'établissement : Françoise SIMONOT-LION - Professeur

Xavier REBEUF - Maître de conférence

Encadrant à l'ISI : Adel KHALFALLAH - Maître de conférence

Année universitaire: 2006-2007

## Généralités

#### Institution

ISI – Institut Supérieur d'Informatique – Université de Tunis El Manar

2, Abou Raihane Bayroumi – L'Ariana 2080 – Tunisie – (www.isim.rnu.tn).

# Organisme d'accueil

*LORIA – INRIA Lorraine* – Laboratoire lorrain de Recherche en Informatique et ses Applications.

UMR 7503 – Équipe TRIO – Bâtiment C – Campus scientifique – B.P. 239 – 54506 Vandoeuvre lès Nancy Cedex – France – (www.loria.fr/equipes/TRIO/).

# Encadrants de l'organisme d'accueil

*Xavier REBEUF* – Maître de conférence à l'École Nationale Supérieure d'Électricité et de Mécanique – INPL – (Xavier.Rebeuf@loria.fr).

*Françoise SIMONOT-LION* – Responsable de l'équipe – Professeur à l'École Nationale Supérieure des Mines de Nancy – INPL– (simonot@loria.fr).

# Répondant de l'institution

Adel KHALFALLAH - Maître de conférence à l'Institut Supérieur d'Informatique – Université de Tunis El Manar – (Adel.Khalfallah@fst.mu.tn).

#### Durée

**4.**½ **mois**, du 02 février au 10 juin 2007.

# Table des matières

| Reme         | rciements                                                             | 3   |

|--------------|-----------------------------------------------------------------------|-----|

| <b>Table</b> | des illustrations                                                     | 3   |

| Liste o      | des tableaux                                                          | 4   |

| Glossa       | aire                                                                  | 4   |

|              |                                                                       |     |

| I Int        | troduction généraletroduction générale                                |     |

| I - 1        | Objectifs du document                                                 | 10  |

| I - 2        | Conditions de réalisation du stage                                    | 11  |

| II Ca        | ndre de référence et problématique                                    | 14  |

| II - 1       | Un sujet, un stage, un mémoire                                        |     |

| II - 2       | Problématique et objectifs du projet                                  |     |

| II - 3       | Notre vision du système                                               |     |

| II - 4       | Plan du mémoire                                                       |     |

| III Co       | ontexte des systèmes temps réel embarqués dans l'automobile           | 20  |

| III - 1      | Introduction : Application, système informatique, environnement       |     |

|              | Qualité de service et contextes temporels des systèmes temps réel     |     |

|              | Du temps réel embarqué au temps réel embarqué appliqué à l'automobile |     |

|              | Méthodologie de développement logiciel dans l'automobile              |     |

|              | La distribution dans l'automobile                                     |     |

|              | Une architecture cible abstraite                                      |     |

|              | De l'intergiciel à l'intergiciel temps réel appliqué à l'automobile   |     |

|              | Dimensionnement temps réel de l'architecture cible abstraite          |     |

|              | Conclusion sur le contexte                                            |     |

| IV Ré        | ealisation                                                            | 64  |

|              | Méthode et contraintes du processus de développement                  |     |

|              | Spécification générale                                                |     |

|              | Modélisation UML                                                      |     |

| IV - 4       | Le générateur de code                                                 | 81  |

|              | L'intergiciel                                                         |     |

|              | Développement et déploiement                                          |     |

|              | 11                                                                    | 108 |

| V Co         | onclusion et perspectives                                             | 110 |

|              | Les résultats du projet                                               |     |

| V - 2        |                                                                       |     |

|              | Perspectives                                                          |     |

|              | nnexes                                                                |     |

|              | Bibliographie                                                         |     |

#### Remerciements

Je remercie tout d'abord les membres du jury qui me font honneur en jugeant ce travail.

Ce mémoire de projet de fin d'études d'ingénieur en informatique est le fruit d'un travail mené au sein de l'équipe *Temps Réel et InterOpérabilité* (TRIO) du laboratoire lorrain de recherche en Informatique et ses applications (LORIA) dirigée par le Professeur **Françoise Simonot-Lion**, à qui je voudrais exprimer toute ma gratitude pour sa confiance et les moyens techniques et scientifiques qu'elle a mise à ma disposition et sans qui ce travail n'aurait jamais été envisageable...« شكراً ».

Je tiens à exprimer mes plus sincères remerciements à mon tuteur Monsieur **Xavier Rebeuf**, maître de conférence à l'École Nationale Supérieure d'Électricité et de Mécanique de Nancy, pour avoir encadré ce travail de fin d'études. Sa disponibilité, ses conseils éclairés et son soutien m'ont été d'une aide inestimable et ont largement contribué à ma formation. Je n'oublierais certainement jamais cette extraordinaire collaboration...« большое спасибо ».

Je souhaite également remercier Monsieur Adel Khalfallah, maître de conférence à l'institut supérieur d'Informatique et mon maître de stage, et qu'il trouve ici l'expression de mon indéfectible reconnaissance pour cette merveilleuse opportunité qu'il ma offerte, en me permettant d'intégrer cette équipe. Sans oublier toutes ces années où il a été mon professeur à l'ISI, et pendant lesquelles il a si bien su nous transmettre sa rigueur scientifique et certainement le goût de la perfection... « un grand merci ».

Enfin, je remercie sincèrement tous les membres de l'équipe, pour leur chaleureux accueil et pour les bons moments passés ensemble et la bonne ambiance qu'ils entretiennent au sein de TRIO ...« *grazie a tutti* ».

Je dédie ce travail à ma mère Natalia et à ma sœur Anissa pour leur indéfectible soutien, les marques d'amour et les sacrifices dont elles ne se sont jamais départies ... « я вас люблю »... Un grand merci à mon ami Achraf ... Clin d'œil particulier à ma chère Alevtina.

Regretter ce que l'on aime est un bien,... [Jean de La Bruyère] Et Bien ... À tous ceux que j'ai perdu et qu'aujourd'hui je regrette.

# **Table des illustrations**

| Figure 1 : Méthodologie de construction de l'intergiciel                        | 18  |

|---------------------------------------------------------------------------------|-----|

| Figure 2 : Logo du projet GenIETeR                                              | 18  |

| Figure 3 : Application temps réel.                                              | 20  |

| Figure 4 : Un système Temps Réel - Interaction procédé contrôleur               | 23  |

| Figure 5 : Architecture générale d'une application temps réel monoprocesseur    | 27  |

| Figure 6 : Les systèmes d'exploitation temps réel.                              | 28  |

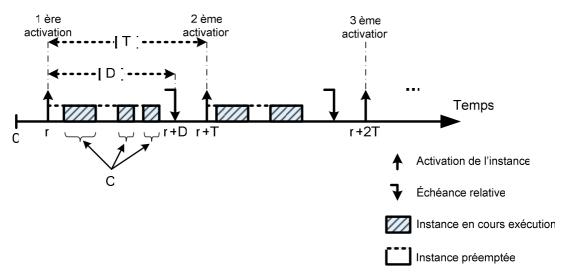

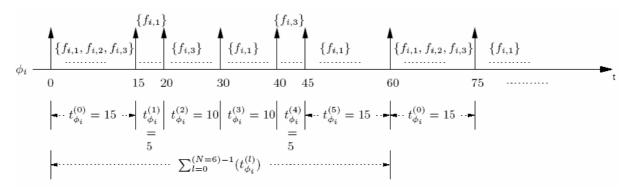

| Figure 7 : Modélisation d'une tâche périodique                                  |     |

| Figure 8 : Enfouissement d'un contrôleur d'injection diesel de Scania. [MRTC05] | 35  |

| Figure 9 : De l'électricité à l'électronique dans l'automobile. [PSA07]         |     |

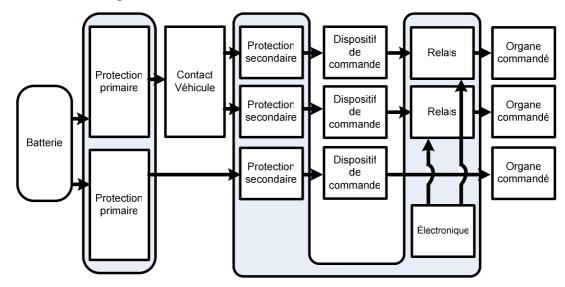

| Figure 10 : Architecture conventionnelle. [ETR05]                               |     |

| Figure 11 : Architecture centralisée. [ETR05]                                   |     |

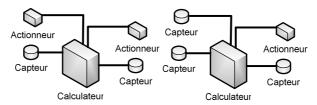

| Figure 12 : Architecture faiblement distribuée.                                 |     |

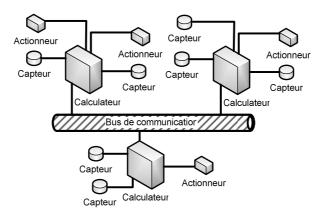

| Figure 13 : Architecture multi-calculateurs                                     |     |

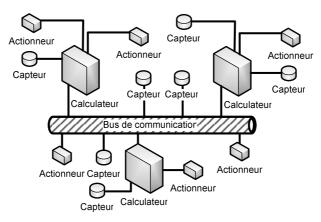

| Figure 14 : Architecture fortement distribuée.                                  |     |

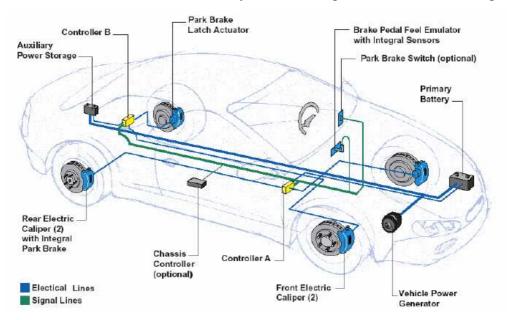

| Figure 15 : Exemple d'un système embarqué de contrôle de freinage [MRTC05]      |     |

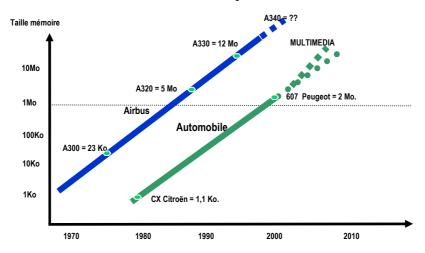

| Figure 16: Augmentation de la taille du code. [PSA07]                           |     |

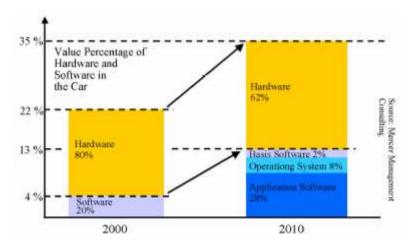

| Figure 17 : Croissance de l'importance du logiciel dans l'automobile. [HAR04]   |     |

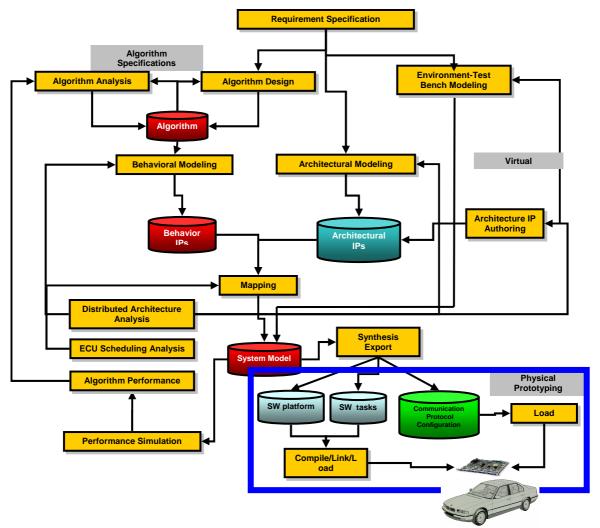

| Figure 18: Flot de conception logicielle global. [ALB02]                        |     |

| Figure 19 : Intervenants et rôles dans le processus de réalisation logicielle   |     |

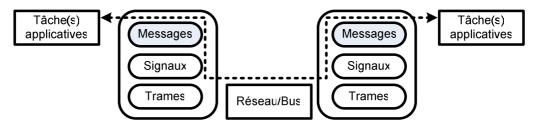

| Figure 20: Modèle d'interaction distante ente 2 tâches.                         |     |

| Figure 21: Une abstraction de l'architecture cible.                             |     |

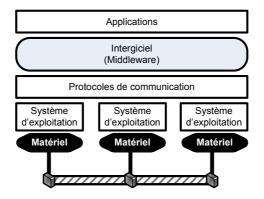

| Figure 22 : (a, b) Couche intergiciel dans l'organisation d'un système.         |     |

| Figure 23: Couche intergiciel dans l'organisation d'un système distribué        |     |

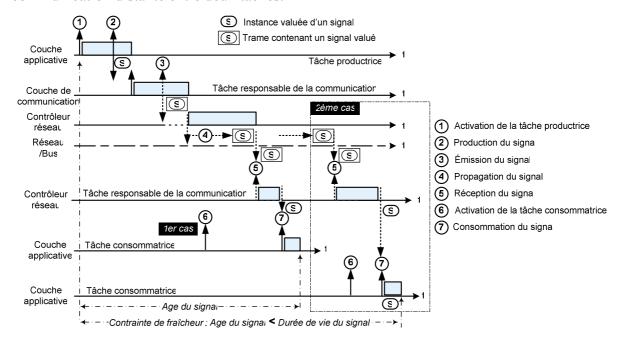

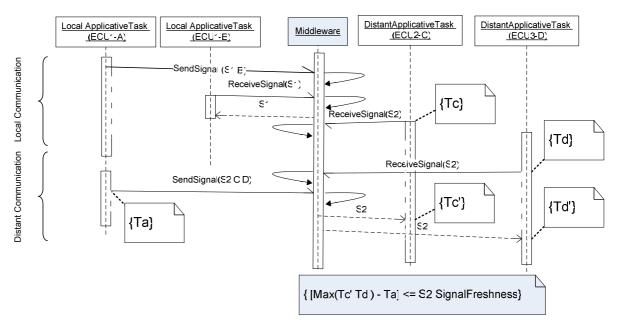

| Figure 24 : Contrainte de fraîcheur d'un signal (exécutif préemptif).           |     |

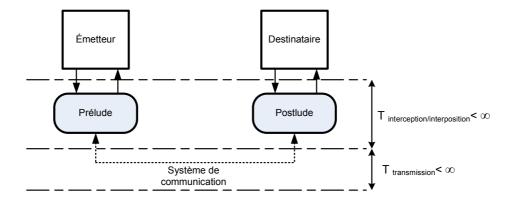

| Figure 25: Modèle logiciel d'Interception/Interposition.                        |     |

| Figure 26: Temps de bout en bout                                                |     |

| Figure 27 : Situation de la conception générique dans 2TUP. [ROQ03]             |     |

|                                                                                 |     |

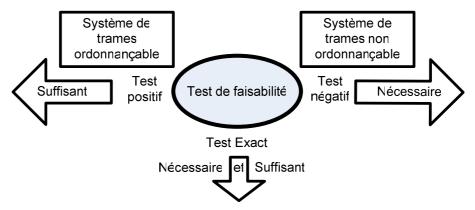

| Figure 28 : Synoptique des différents résultats d'un test d'ordonnançabilité.   |     |

| Figure 29: Diagramme des cas d'utilisation.                                     |     |

| Figure 30 : Diagramme de séquences (utilisation de l'intergiciel)               |     |

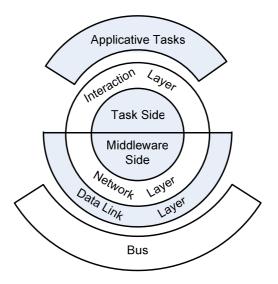

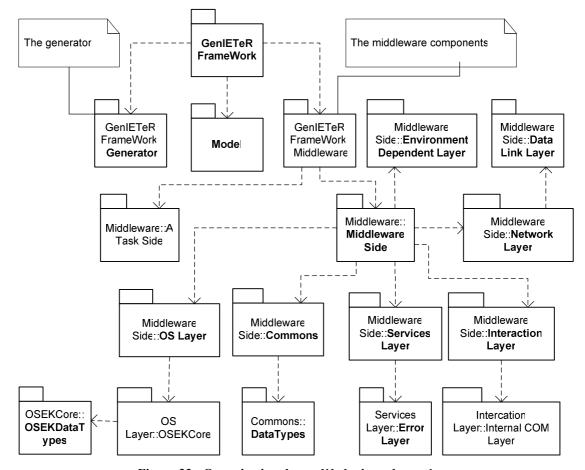

| Figure 31: Organisation en couches de l'intergiciel.                            |     |

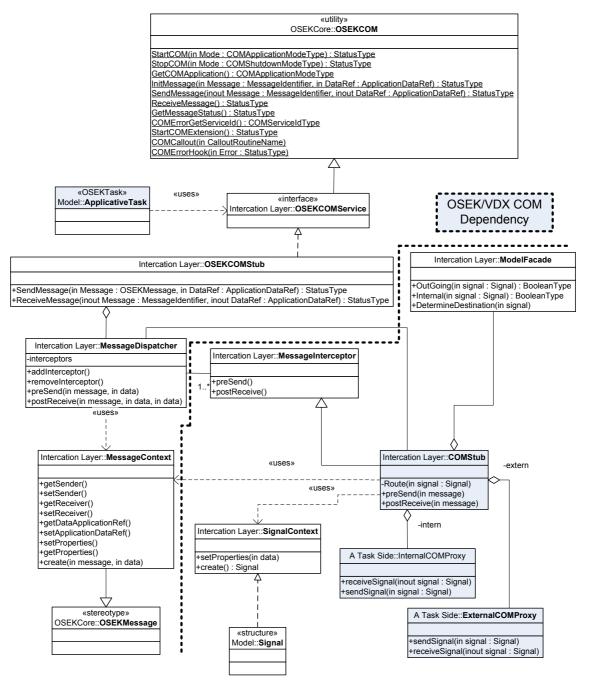

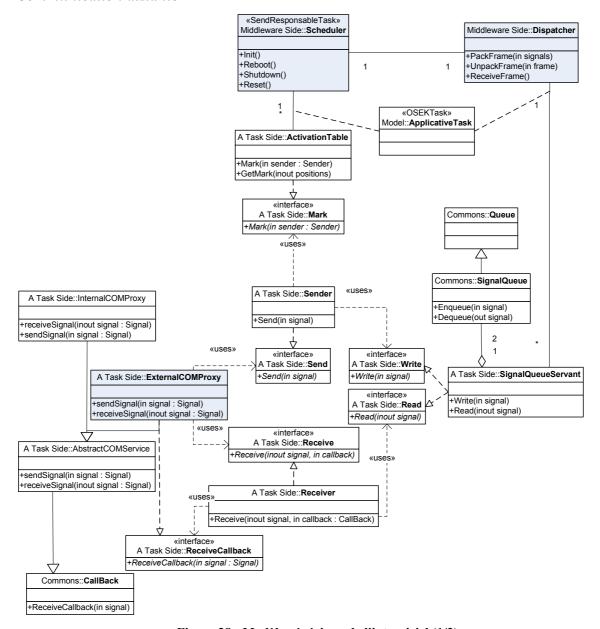

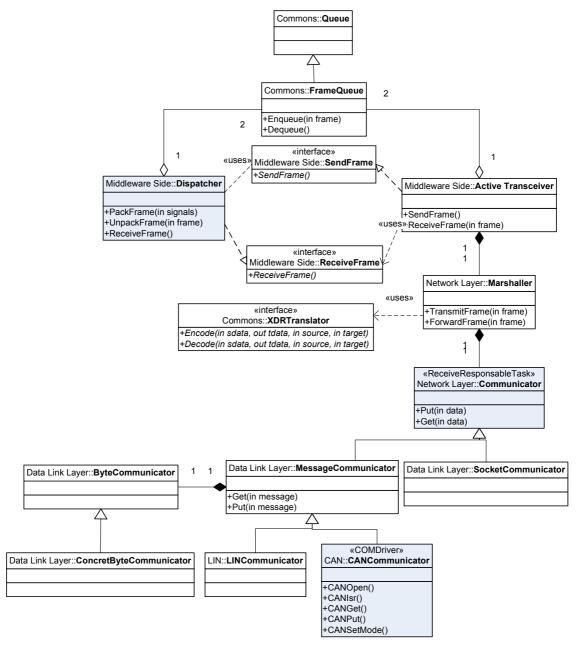

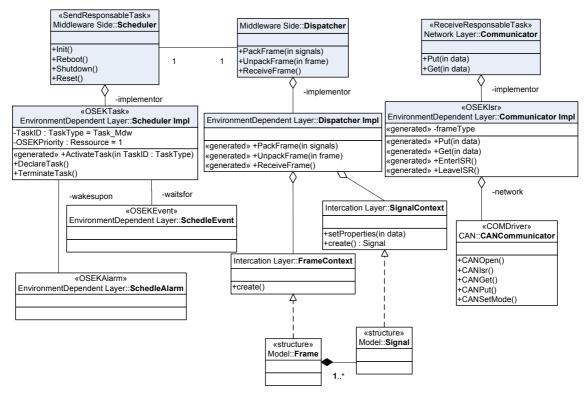

| Figure 32 : Organisation du modèle logique du système.                          |     |

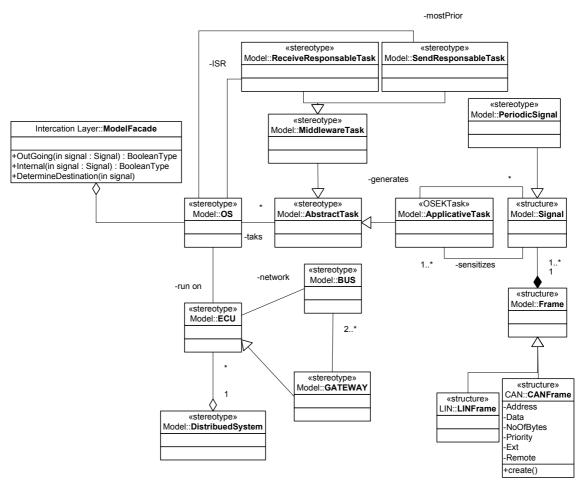

| Figure 33 : Modèle structurel.                                                  |     |

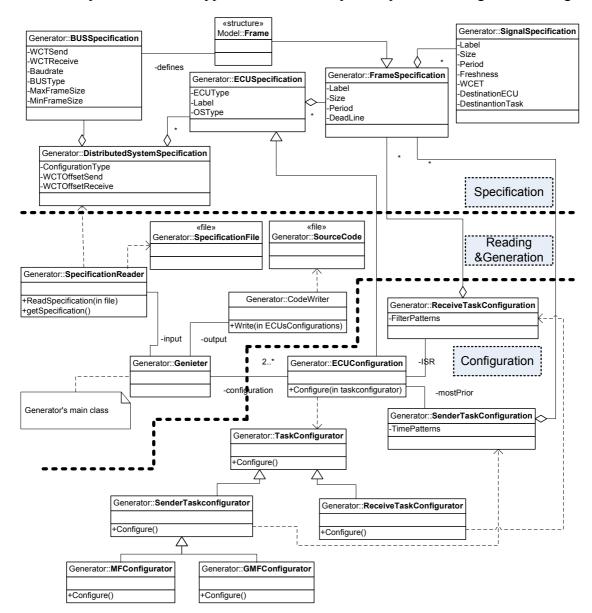

| Figure 34 : Diagramme de classes du générateur.                                 |     |

| Figure 35: Illustration d'une tâche configurée en GMF. [RSM06]                  |     |

| Figure 36 : Taxonomie des structures de données du système.                     |     |

| Figure 37 : Modèle d'interaction tâches applicatives/intergiciel.               |     |

| Figure 38 : Modèle générique de l'intergiciel (1/2)                             |     |

| Figure 39 : Modèle générique de l'intergiciel (2/2)                             |     |

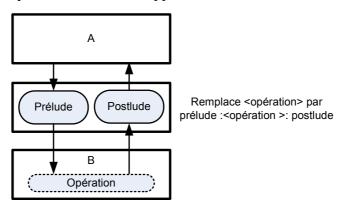

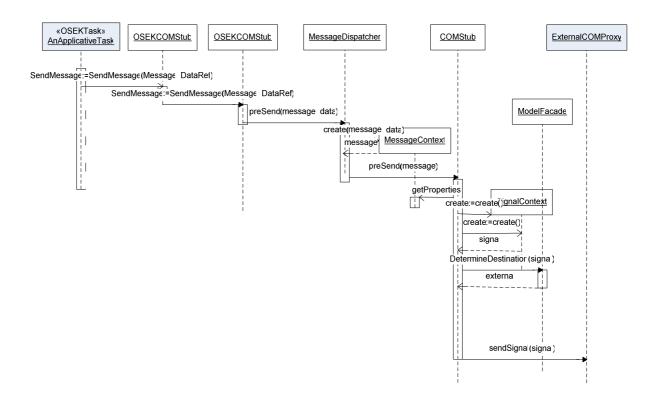

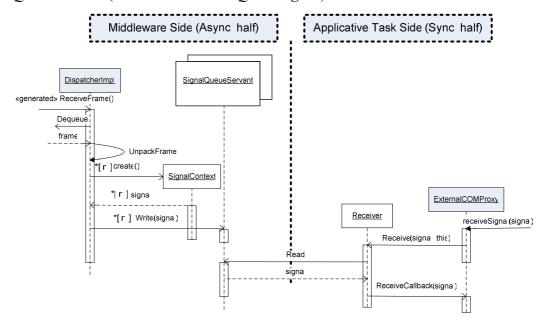

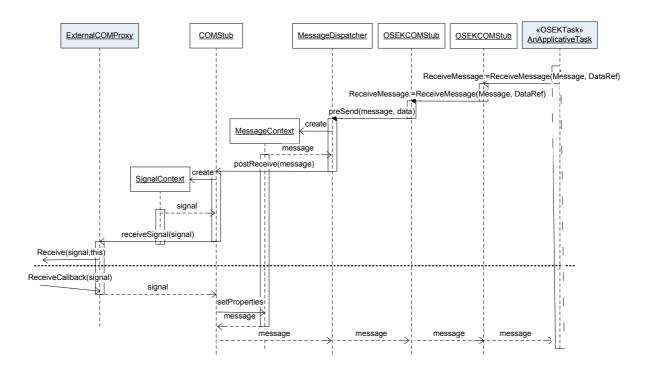

| Figure 40 : Diagramme de séquence du mécanisme de prélude (1/3)                 |     |

| Figure 41 : Diagramme de séquence du mécanisme de prélude (2/3)                 |     |

| Figure 42 : Diagramme de séquence du mécanisme de prélude (3/3)                 |     |

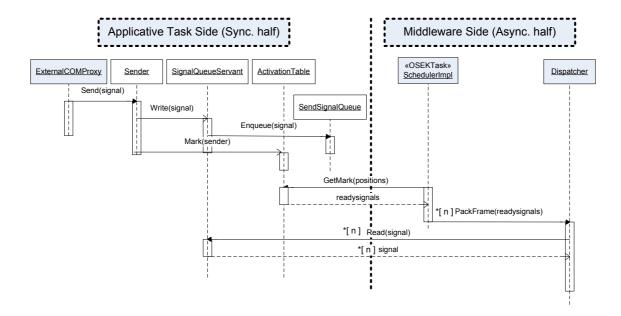

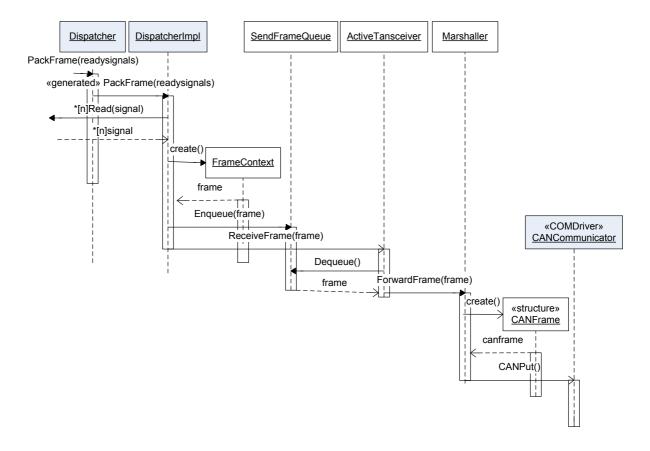

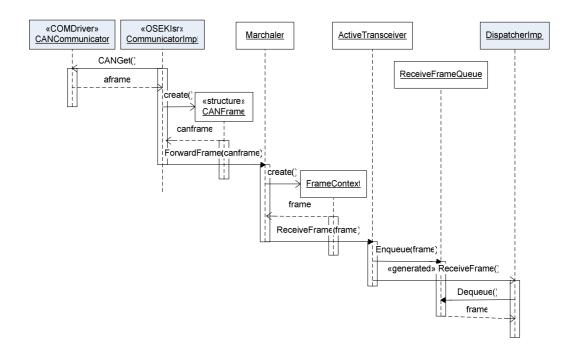

| Figure 43 : Diagramme de séquence du mécanisme de postlude (1/3)                |     |

| Figure 44 : Diagramme de séquence du mécanisme de postlude (2/3).               |     |

| Figure 45 : Diagramme de séquence du mécanisme de postlude (3/3)                |     |

| Figure 46 : Ebauche du modèle fonctionnel pour la communication locale.         |     |

| Figure 47 : Modèle de tâches de l'intergiciel                                   |     |

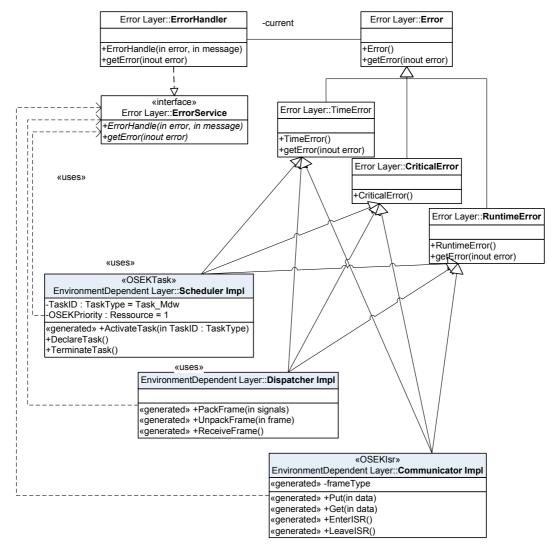

| Figure 48 : Modèle de gestion d'erreur pour l'intergiciel.                      |     |

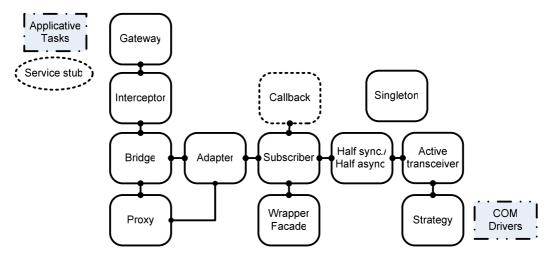

| Figure 49 : Organisation des design patterns dans l'intergiciel                 |     |

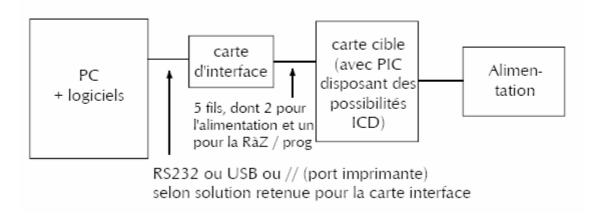

| Figure 50 : Programmation et déboguage in situ pour PIC. [MOREN]                |     |

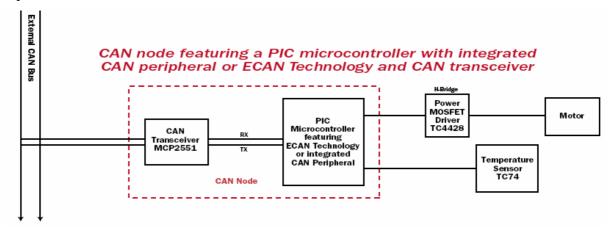

| Figure 51 : Solution d'architecture pour le développement sur CAN. [WCANS]      |     |

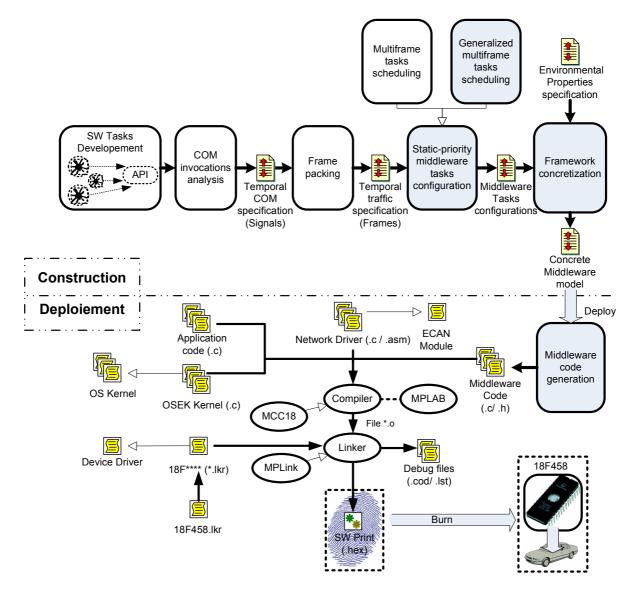

| Figure 52 : La méthodologie de développement globale.                           |     |

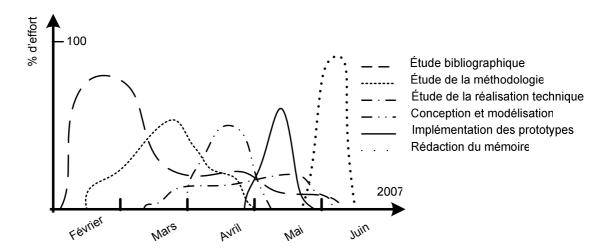

| Figure 53 : Courbe d'efforts impartis au projet.                                |     |

| Figure 54 : Passerelle distribuée. [WVECT]                                      | 118 |

#### Liste des tableaux

| Tableau 1 : Classification des réseaux multipléxé dans l'automobile. [ETR05] | . 47 |

|------------------------------------------------------------------------------|------|

| Tableau 2 : Preuve de la limite du temps de bout en bout                     | 62   |

| Tableau 3 · Structure et nomenclature de la spécification du trafic          | 70   |

# Glossaire

- [1] Système temps réel embarqué: C'est tout d'abord un système dont le comportement dépend, non seulement de l'exactitude des traitements effectués, mais également du temps où les résultats de ces traitements sont produits. Il est dit « temps réel » parce que ses actions logicielles dirigent les activités d'un processus en cours d'exécution. Si de plus, il est physiquement intégré à l'environnement qu'il contrôle et qu'il est soumis aux mêmes contraintes physiques (température, pression, etc.) que son environnement, il est alors dit « embarqué ».

- [2] Système réparti : On peut employer le terme de système réparti ou distribué lorsque le système dispose d'un ensemble d'entités communicantes, installées sur une architecture de processeurs reliés par un réseau de communication, dans le but de résoudre en coopération une fonctionnalité applicative commune.

- [3] Intergiciel: Un intergiciel (Middleware) désigne un logiciel présent sur un noeud d'un système réparti et servant d'intermédiaire de communication entre des applications complexes, distribuées sur un réseau d'échange d'informations. Il offre pour cela les abstractions d'un modèle de distribution des services de haut niveau liés aux besoins de communication de ces composants applicatifs présents sur ce nœud.

- [4] Composant logiciel ou applicatif: La définition qu'on pourrait retenir pour un composant logiciel se base principalement sur la deuxième phrase de celle donnée par [SZYP98]: «Un composant logiciel est une unité de composition spécifiant, par contrats, ses interfaces

(fournies et requises) et ses dépendances explicites aux contextes. Un composant logiciel peut être déployé indépendamment et peut être sujet de composition par un tiers pour la conception d'applications logicielles». Nous utilisons le terme composant logiciel par analogie avec les composants utilisés dans l'industrie de l'électronique. Contrairement au contexte des CBSE [BEL01] (Component-Based Software Engineering) nous n'en retiendrons que les notions liées à sa faculté d'adaptation. Nous ferons alors le rapprochement avec le terme «composant logiciel réutilisable» pour dire que c'est une entité logicielle capable de résoudre un même problème dans des contextes différents. Paradoxalement, c'est un composant avec peu de dépendance.

[5] CAN: Control Area Network [CAN] est un bus multiplexé/réseau de terrain à faibles coûts. C'est d'une part, un réseau de terrain à moyens débits respectant le modèle d'interconnexion des systèmes ouverts OSI [WOSI] de l'ISO (ISO 7498) et qui est particulièrement adapté à un fonctionnement dans un environnement critique et géographiquement limité. D'autre part, c'est un protocole de communication série qui supporte des systèmes temps réel avec un haut niveau de fiabilité.

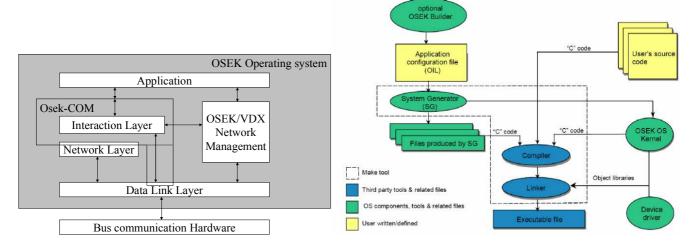

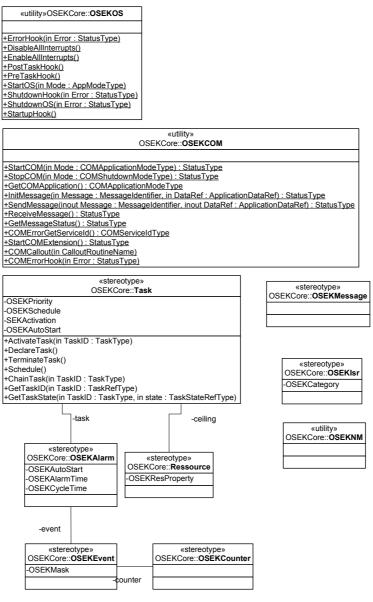

[6] OSEK/VDX OS: OSEK/VDX (cf. Annexe 1) est un système d'exploitation standard [WOSEK] dans l'industrie automobile européenne. Il est spécialement adapté aux applications temps réel embarquées qui exigent une utilisation minimale de la mémoire et du temps d'une unité centrale.

[7] Design patterns: Un patron de conception est un concept destiné à résoudre les problèmes récurrents du génie logiciel suivant le paradigme objet. Les patrons de conception décrivent des solutions standards pour répondre à des problèmes d'architecture et de conception des logiciels par une formalisation de bonnes pratiques, ce qui signifie que l'on privilégie les solutions éprouvées (un patron de conception n'est considéré comme « prouvé » qu'une fois qu'il a été utilisé avec succès au moins dans trois cas).

[8] Frame packing: Techniques et algorithmes [TIN95, TIN93] de validation d'une collection d'objets (dans notre cas, un ensemble de tâches et/ou de trames) reposant sur des critères analytiques ou des heuristiques (contraintes temporelles) pour conclure à la construction d'une séquence d'ordonnancement (ou configuration ordonnancée) de cet ensemble et à sa faisabilité. L'utilisation de ces méthodes se justifie dès lors que l'on souhaite ordonnancer des applications fortement couplées (forte utilisation de ressources et de synchronisations). En effet, la construction d'une séquence d'ordonnancement permet de s'assurer du respect des

contraintes temporelles pendant sa construction et donc de valider simultanément la séquence produite puisque celle-ci sera utilisée telle quelle dans un séquenceur (dispositif d'analyse). Ces algorithmes [SAND00] sont une adaptation des algorithmes de *bin packing* visant à trouver l'arrangement optimal (ou un arrangement) le plus économique possible (économie des ressources matérielles) pour cette séquence.

- [9] Modèle de répartition: Un modèle de répartition est un ensemble de définitions d'interactions entre des entités abstraites, associées à une projection de ces entités sur les noeuds d'un système réparti.

- [10] Générateur de code : Un générateur de code est un programme qui partant d'une configuration donnée produit du code ad hoc (spécifique) optimisé pour cette configuration. En d'autres termes, la génération permet de généraliser les bonnes pratiques capitalisées et met à disposition des développeurs les éléments nécessaires aux développements additionnels. Les développements complémentaires sont réalisés indépendamment du code généré et non pas sur les éléments générés garantissant ainsi la possibilité de re-générer certains éléments lors de l'apparition de nouvelles bonnes pratiques.

- [11] *Intergiciel générique*: Un intergiciel générique est un intergiciel dans lequel certains modules sont rendus indépendants du choix de la structuration d'une répartition particulière, et réalisés sous une forme réutilisable. L'adaptation ou la personnalisation est alors obtenue en concrétisant ces modules génériques avec des composants de personnalisation.

- [12] *Intergiciel configurable ou adaptable*: Un intergiciel est dit configurable lorsque les composants qu'il intègre peuvent être choisis et adaptés leur comportement en fonction des besoins de l'application et des fonctionnalités offertes par l'environnement.

# I Introduction générale

Les récentes controverses sur certains des incidents survenus sur des véhicules équipés de régulateurs de vitesse (le *pédalgate* Renault entre autres) dont la vocation est d'éviter aux conducteurs de confondre frein et embrayage (seule hypothèse avancée à ce jour par Renault pour justifier les nombreux accidents) ont beaucoup défrayé la chronique. Le manque de moyen d'urgence donné au conducteur indépendamment de tout système électronique pour lui permettre de reprendre le contrôle de son véhicule en cas de dysfonctionnement, est un fait. À qui attribuer la responsabilité : au constructeur ou au conducteur ?

En d'autres termes la loi de Murphy s'applique aussi à l'électronique, « *tout ce qui peut potentiellement dysfonctionner dysfonctionnera* » [WREN], et cela s'applique nécessairement à l'industrie automobile comme aux autres industries.

Conscients que les dysfonctionnements électroniques existent, et que la vie de leurs clients dépend de la qualité de leurs produits, les constructeurs concentrent tous leurs efforts sur l'amélioration de la sécurité des véhicules. Et par conséquent, améliorent leurs procédés de conception et de fabrication, tout en réduisant les coûts et les délais.

Parce que ce genre de système est appelé « système réactif », il est soumis à des contraintes temporelles fortes (temps de réponse borné, fréquence d'échantillonnage d'un signal, etc.), spécifiées lors de la conception. La vérification de celles-ci avant utilisation est nécessaire pour la validation du système. La criticité de ces systèmes se traduit alors, non seulement par leur fiabilité, mais également par leur rigoureuse réactivité.

Un autre objectif poursuivi par les constructeurs est celui d'offrir aux utilisateurs un plus grand confort d'utilisation, ainsi que des services nouveaux. Tout ceci nécessite la mise en place de plateformes de développement performantes, qui traitent d'une part des aspects fonctionnels, et d'autre part des aspects opérationnels de construction. C'est ce second point qui nous intéresse dans le présent mémoire. La validation opérationnelle d'une application sous-entend la nécessité de procéder à des vérifications temporelles quantitatives. La sécurité nécessite que l'on puisse garantir qu'entre toute évolution du procédé et la commande produite en réaction par le système, s'écoulera une durée limité.

En d'autres termes, il s'agit de garantir que le temps de réponse de l'Informatique soit, au moins, aussi rapide que le procédé qu'elle contrôle. Cette propriété doit être garantie avant et après la mise en exploitation de l'application. L'application concernée consiste en un ensemble de tâches, chacune d'elles ayant vocation à traiter une information reçue du procédé

(la réception de l'information pouvant être assimilée à l'évènement) ou à réagir à un évènement spécifique. L'application est donc exposée comme un ensemble d'activités, décrites par des tâches, qui doivent s'exécuter de manière répétitive tout au long de la vie de l'application. Par ailleurs, celle-ci s'exécute sur une architecture souvent dédiée, qui peut être monoprocesseur, multiprocesseur ou répartie. Dans ce mémoire, nous considérerons des systèmes distribués monoprocesseur. L'exécution des tâches doit donc être répartie entre les différents processeurs (ou sites dans la terminologie des systèmes distribués) du système pour réaliser les activités de l'application concernée.

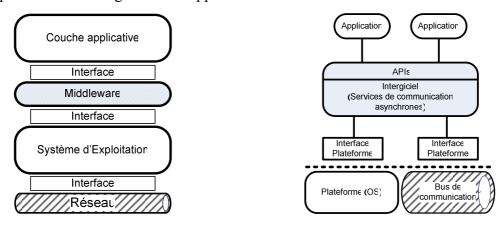

Ainsi, le développement d'applications distribuées temps réel nécessite aujourd'hui l'introduction de paradigmes existants d'origines diverses (notamment issus du génie du logiciel). De manière très classique, la répartition de l'architecture est à la charge d'une couche logicielle spécifique appelée intergiciel [3] (*Middleware*). Pour ne pas alourdir notre présentation, nous parlerons dans cette introduction de plateforme ou d'intergiciel, en gardant en mémoire le caractère plus ou moins étendu que peuvent revêtir ces notions. La notion la plus ancienne, celle de plateforme, désigne un ensemble de logiciels dont l'objectif est de servir de fondation au développement et au fonctionnement de nouvelles applications. La notion d'intergiciel est, elle, beaucoup plus récente et désigne plus particulièrement un ensemble de services réalisés entre le système d'exploitation et l'application. Parmi les intergiciels les plus populaires ces dernières années, l'on peut citer les intergiciels orientés communication, notamment ceux basés sur la norme CORBA [OMG02]. Toutefois, peu d'entre eux permettent de garantir une qualité de service temporelle.

Les intergiciels rendent les applications réparties indépendantes d'un environnement particulier, mais au prix d'une surcharge de l'architecture logicielle de ces applications. Ils masquent ainsi une partie de la complexité de la programmation répartie en permettant à un développeur de manipuler de la même manière des entités locales et distantes. De plus, la spécificité vient ici du fait que l'objectif premier (voire même unique) de l'intergiciel est de garantir le respect des contraintes temporelles induites par le procédé.

La détermination des fonctions fondamentales de l'intergiciel et leur isolement dans des modules indépendants permet également de rendre celui-ci adaptable à des besoins et à des environnements variés par assemblage de « briques logicielles » [4] encapsulant des mécanismes prédéfinis. Cet assemblage est effectué au moyen de générateurs plus ou moins automatisés, qui réalisent les abstractions d'un modèle de répartition et permettent aux tâches applicatives d'interagir. Selon la nature et la richesse des « briques » fournies, on pourra parler de « kit de développement » ou de « canevas » (*framework*).

Des architectures d'intergiciels génériques [11] ont été par ailleurs proposées, introduisant la notion de paramétrisation. À partir de ces architectures d'intergiciels génériques, nous pouvons retenir un certain nombre de fonctions communes de communication, mais néanmoins dépendant d'un choix de modèle de communication: une communication asynchrone orientée messages entre tâches, inspiré de celui des MOMs (*Message-Oriented Middlewares*). Il est alors possible de mettre en oeuvre ces fonctions sous forme d'une couche neutre. Cette couche neutre est ensuite dotée de services, qui sont une façade offrant une interface standard à toutes les couches applicatives. La séparation entre couche neutre et noyau de l'intergiciel permet de découpler, tout en garantissant le respect des contraintes temporelles fournies par les exigences opérationnelles, les deux aspects architecturaux : une facette applicative présentée aux applicatifs de l'utilisateur, et une facette protocolaire présentée aux réseaux.

Par garantir, il faut concevoir ; pour concevoir, il faut formaliser. Il est donc nécessaire de modéliser l'application, et dans le cas qui nous occupe, c'est une modélisation temporelle de l'application qui s'impose. Une telle modélisation est utilisée depuis très longtemps dans la littérature, et les travaux (qui nous intéressent) qui s'appuient sur une modélisation souvent appelée « modélisation de Liu Layland » [LAY73]. Il s'agit de proposer une abstraction temporelle de fonctionnement de l'application. Une application consiste en un ensemble de tâches, chacune de ces tâches est décrite à l'aide de paramètres temporels qui peuvent indiquer (le cas échéant) l'instant de création de la tâche, sa période (s'il s'agit d'une tâche de contrôle, par essence même périodique), son délai critique (qui quantifie la « durée adaptée » entre la création d'une instance et sa terminaison), et sa durée. Parmi tous ces paramètres, les trois premiers sont issus du cahier des charges, et dépendent du concepteur de l'application. Mais le dernier dépend directement du code de la tâche. Comme il est difficile (voire même dénué de sens) de déterminer une durée d'exécution unique et exacte, nous travaillons en fait avec un majorant de la durée (WCET, Worst Case Execution Time). Mais cette approche « pire cas » masque la réalité des choses. Quand les variations de durées sont dues à l'indéterminisme de la gestion de la mémoire par exemple, il est difficile de faire autrement. Mais cette vue de durée unique masque également les variations liées au code lui-même. Les études réalisées en masquant les communications distantes sont alors d'une part surcontraintes (particulièrement dans le cas où le protocole de communication est pris en compte) et d'autre part incapables de décrire le fonctionnement réel de l'application. Alors, comment modéliser et construire un générateur d'intergiciel temps réel embarqués dans l'automobile?

... Et c'est ainsi que commence ce mémoire...

## I - 1 Objectifs du document

La réalisation de ce générateur d'intergiciels temps réel embarqués dans l'automobile intervient dans le cadre du stage du projet de fin d'études pour l'obtention du diplôme d'ingénieur en génie du logiciel et des systèmes d'information. Ce sujet m'a valu un déplacement à Nancy (France) et une entrée au Laboratoire Lorrain de Recherche en Informatique et ses Applications pour un séjour de plus de quatre mois. Le document que vous avez entre les mains se veut être un mémoire et le rapport témoin de ce stage. Ce mémoire est destiné à l'honorable jury chargé de l'évaluation du stage, ainsi qu'aux encadrants de l'organisme qui y retrouveront les acquis et le résumé de mes activités pour le sujet qui me fût confié.

Il s'adresse par ailleurs aux concepteurs et développeurs qui me relaieront, et qui peut-être y trouveront un intérêt, ou à tout autre personne qui s'intéresserait à ce sujet.

A ces personnes, je souhaite une bonne lecture.

Le stage touchant à sa fin, j'ai voulu et j'ai le devoir de réaliser le présent document à l'échelle d'un rapport de mes réalisations durant toute la période du stage. Et d'autre part le considérer comme un témoignage des compétences et connaissances acquises lors de cette nouvelle expérience professionnelle. Une expérience au sein d'un laboratoire de recherche en Informatique qui, s'est révélé extrêmement instructive.

Voici, les principaux objectifs de ce document :

- Comprendre les enjeux des missions qui m'ont été confiées,

- Synthétiser les concepts théoriques que j'ai pu appréhender durant ce stage au travers de l'étude bibliographique,

- Montrer comment j'ai résolu les situations délicates en y confrontant mes acquis théoriques,

- Présenter les réalisations effectuées et la méthodologie de mise en oeuvre de ce système applicatif,

- Procéder à une analyse des fonctionnalités requises pour l'utilisation de notre système applicatif et en présenter les conclusions,

- Décrire les principales fonctions et les scénarii de transactions du système applicatif,

- Déterminer les exigences du système applicatif, les objectifs généraux et les critères de réussite qui permettront d'assurer son bon fonctionnement et de juger de l'avancement du projet,

- Déterminer les conditions et les contraintes opérationnelles reliées au système défini afin d'évaluer les délais de déploiement,

- Présenter les réalisations que j'ai pus effectuer durant ce stage,

- Mettre en exergue mes appréciations pour ce stage et ceux de mes répondants, ainsi que les conclusions de mon travail,

- Faire le point de mes nouvelles connaissances sur le métier qui régit le secteur d'activité de l'organisme qui a bien voulu m'ouvrir ses portes,

- Prouver en quoi le stage a réussit à développer mes compétences (rigueur, esprit d'équipe, créativité, gestion de projet),

- Prouver l'utilité de mon choix pour ce stage,

- Faire le tour de cette expérience qui m'a fait découvrir les prémisses de la recherche scientifique et qui n'a fait que renforcer mes motivations pour un avenir de chercheur.

# I - 2 Conditions de réalisation du stage

C'est pour toute la période de ces quatre mois et demi, au sein du LORIA, que j'ai pu confronter les compétences techniques du génie logiciel acquises durant ma formation académique à l'Institut Supérieur d'Informatique, à la réalité d'un environnement où la rigueur, l'esprit d'équipe et l'innovation doivent rallier l'esprit de recherche, afin de faire avancer la science.

# I - 2 - 1 Présentation de l'organisme d'accueil : le LORIA

Le , Laboratoire Lorrain de Recherche en Informatique et ses Applications, est une Unité Mixte de Recherche - UMR 7503 - commune à plusieurs établissements partenaires :

- CNRS Centre National de Recherche Scientifique,

- INRIA Institut National de Recherche en Informatique et en Automatique,

- **INPL** Institut National Polytechnique de Lorraine,

- **UHP** Université Henri Poincaré Nancy 1,

- NANCY 2 Université Nancy 2.

#### I - 2 - 2 Identité du LORIA

La création de cette unité a été officialisée le 19 décembre 1997 par la signature du contrat quadriennal avec le ministère de l'éducation nationale, de la recherche et de la technologie et par une convention entre les cinq partenaires. Cette unité, renouvelée en 2001, succède ainsi au CRIN (Centre de Recherche en Informatique de Nancy), et associe les équipes communes entre celui-ci et l'Unité de Recherche INRIA Lorraine.

Le LORIA est un Laboratoire de plus de 450 personnes parmi lesquelles :

- cent cinquante chercheurs et enseignants-chercheurs,

- un tiers de doctorants et post doctorants,

- des ingénieurs, techniciens et personnels administratifs,

organisés en équipes de recherche et services de soutien à la recherche.

C'est aussi chaque année :

- Une trentaine de chercheurs étrangers invités,

- Des coopérations internationales avec des pays des cinq continents,

- Une quarantaine de contrats industriels.

Les missions du LORIA sont essentiellement :

- La recherche fondamentale et appliquée au niveau international dans le domaine des sciences et technologies de l'information et de la communication,

- La **formation par la recherche** en partenariat avec les universités lorraines,

- Le transfert technologique par le biais de partenariats industriels et au travers de la création d'entreprises.

# I - 2 - 3 Identité de l'équipe d'accueil : TRIO, the Dream Team

TRIO (Temps Réel et InterOpérabilité) est l'une des équipes de recherche du LORIA, son objectif premier est le développement par l'innovation des techniques et des méthodes pour la conception, la validation et l'optimisation des applications distribuées temps réel. Pour se faire, ses travaux sont structurés selon deux axes complémentaires :

- La spécification de mécanismes exécutifs (protocoles, ordonnanceurs, intergiciels, ...) offrant des services et une qualité de service garantissant le respect des contraintes de sûreté de fonctionnement, en particulier des contraintes de temps ; ceci intègre la détection de fautes, la signalisation de fautes et la tolérance aux fautes.

- La modélisation, l'analyse et l'évaluation d'applications temps réel distribuées en vue d'exploiter les modèles pour des activités de validation et /ou de configuration automatique de tout ou partie des applications.

Les problématiques à résoudre proviennent principalement de trois caractéristiques des applications ciblées :

Il s'agit de systèmes à événements discrets intégrant des caractéristiques temporelles (performances du matériel support, propriétés temporelles); ceci accroît la complexité de leur modélisation et de leur analyse. Aussi, une partie des objectifs de recherche consiste à maîtriser cette complexité en faisant un compromis entre précision d'un modèle et son exploitabilité.

- L'environnement de ces systèmes peut être cause de perturbations. Les travaux doivent en particulier prendre en compte l'impact d'un environnement incertain (par exemple, l'influence des perturbations électromagnétiques sur le support matériel des applications) sur le respect des propriétés requises. Des approches stochastiques doivent, alors, être mises en oeuvre.

- Enfin, la caractéristique principale des travaux repose sur le fait qu'ils traitent de temps physique continu.

Les trois axes mentionnés ci-dessus contribuent à couvrir l'ensemble des activités allant de la résolution de problèmes théoriques (modélisation et analyse de systèmes temporisés à événements discrets) à leur mise en oeuvre en applications industrielles à échelle réelle, et en particulier dans des systèmes électroniques embarqués dans le domaine de l'automobile. Certains résultats ont conduit à des prototypes et à des collaborations fructueuses avec l'industrie automobile.

L'équipe-projet TRIO maintient des relations à la fois avec des institutions académiques et des partenaires industriels, en France aussi bien qu'à l'étranger :

- National Laboratory of Industrial Control Technology of Zhejiang University.

- MOSIC team, Université de Tunis El Manar Tunisie.

- Anatoly Manita.

- Joël Goossens, Université Libre de Bruxelles Belgique.

- Kottering University.

Elle collabore activement dans des projets et des programmes aussi bien européens que nationaux au travers de contrats conclus avec ses partenaires :

- Programme européen : NNE 2001-00825, REMPLI.

- Projets nationaux : ANR PREDIT Project SCARLET, ARA SSIA SAFE NECS.

- Action régionale : QSL Operation TT\_SAFETY Evaluation of the Safety of Systems

Distributed onto a TDMA-Based Network and Subject to "Agressive Environment".

L'équipe TRIO a monté, en 2001, une équipe de recherche technologique en coopération avec le groupe PSA Peugeot-Citroën, CARAMELS (CAractérisation des Réseaux embarqués dans l'Automobile et Mécanismes En Ligne pour leur Sûreté) supportée par le ministère de la recherche. La thématique traitée concerne l'évaluation des caractéristiques de sûreté de fonctionnement des architectures de communications supportant les applications embarquées X-by-Wire dans l'automobile.

# II Cadre de référence et problématique

## II - 1 Un sujet, un stage, un mémoire

Le contexte de notre travail émane directement des propositions de la méthodologie présentée dans la thèse [RSM06], et qui concerne le développement d'un intergiciel à embarquer [1] dans l'automobile. En raison de l'impact que peut avoir un intergiciel [3] sur le bon fonctionnement des fonctions automobiles réparties, et en particulier sur le respect des contraintes temporelles imposées aux échanges entre ces fonctions, l'auteur propose la construction d'un intergiciel devant fournir des services de communication asynchrone au niveau applicatif. Cette construction repose sur une génération d'intergiciels « légers » (rapide et peu encombrant) et adaptés [12] à un type d'application, et ce par assemblage automatisé de composants prédéfinis, optimisant ainsi la consommation des ressources.

Les objectifs traités dans ces travaux sont :

- Offrir un ensemble de services de communication distante permettant aux entités applicatives d'effectuer des échanges entre elles tout en garantissant le respect des propriétés liées à la criticité du système globale;

- Cacher la distribution, en ce que les services de communication fournis doivent être indépendants de la localisation des intervenants dans les échanges;

- Garantir une qualité de service temporelle, où le respect de toutes les contraintes temporelles soit assuré.

Ces objectifs fournissent deux axes importants qui ont été explorés :

- D'une part, l'intergiciel sera un logiciel de plus dans chaque ECU provoquant un encombrement logiciel dont il est impératif d'étudier l'impact;

- D'autre part, la garantie du respect des contraintes impose à l'intergiciel un comportement totalement déterministe.

La méthodologie proposée traite alors de l'implémentation et la configuration d'un intergiciel automobile optimal. En ce qui concerne l'implémentation de cet intergiciel, la définition d'un ensemble optimal d'entités, dans le sens où il est adapté aux propriétés du support d'exécution, a été faite pour qu'elles puissent être capables de représenter l'intergiciel sur chaque ECU cible avec une moindre utilisation de ressources (par *frame packing* [8]). Le volet suivant, la configuration de l'intergiciel, essaye d'attribuer des paramètres au système de manière à ce que les contraintes temporelles et fonctionnelles imposées soient respectées.

Par conséquent, la thèse ouvrait le champ à une perspective immédiate d'une implémentation sur une plateforme réelle. Ce travail, qui nous a été proposé et que nous nous

sommes approprié dans le cadre du stage de notre projet de fin d'études, a pour objectif de vérifier l'implémentabilité de l'approche proposée, de quantifier l'influence de l'architecture logicielle basée sur des *design patterns* sur la performance de l'intergiciel et d'évaluer la possibilité d'automatiser l'implémentation de l'empreinte d'un intergiciel sur chaque ECU.

# II - 2 Problématique et objectifs du projet

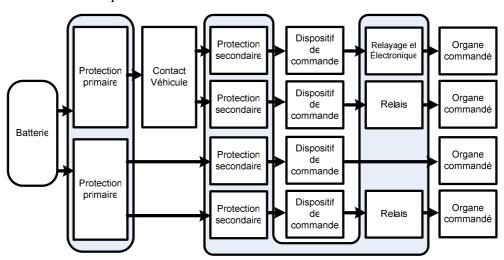

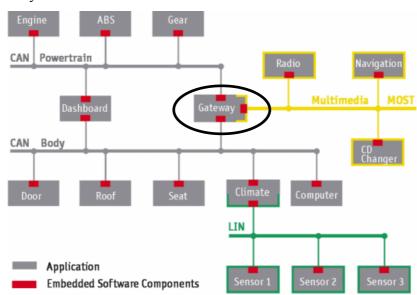

Un véhicule est traversé de part et d'autre par des faisceaux de fils électrique afin de transmettre énergie et informations à l'ensemble des différents organes électriques (des calculateurs ou des unités de contrôle électroniques, ou leur acronyme anglais ECU: *Electronic Control Unit*, ou des capteurs, etc.) composant le système. L'augmentation croissante des fonctions dans l'automobile fût à l'origine de l'accroissement considérable du nombre des liaisons filaires, et par conséquent, a augmenté le poids des véhicules ainsi que leurs coûts. Une mutation de ces liaisons vers des réseaux multiplexés permet de limiter ces contraintes tout en introduisant d'autres difficultés à surmonter, comme le dimensionnement temps réel et la réactivité.

Certes l'introduction des réseaux permet de réduire la quantité de liaisons filaires reliant les nombreux organes d'un véhicule, mais rajoute une autre caractéristique à ces systèmes : la distribution [2]. Par ailleurs, cette situation provoque des modèles de répartition [9] spécifiques à chaque système.

L'interaction des différents programmes participant à un système distribué pose également des problèmes algorithmiques particuliers. L'hétérogénéité des architectures matérielles et logicielles au sein d'un système réparti rend nécessaire la mise en oeuvre de composants d'adaptation : la répartition est une source de complexité qui s'ajoute aux problèmes propres à une application temps réel.

Historiquement, il incombait aux développeurs d'applications de résoudre eux-mêmes les problèmes liés à la répartition : fiabilisation des communications, algorithmes répartis, hétérogénéité des environnements, etc. En particulier, ils devaient programmer directement le matériel de communication de chaque machine, s'assurer de la coordination entre composants, et choisir une représentation de l'information commune acceptée par tous les participants.

Pour faciliter la conception et le développement d'applications réparties, des modèles de répartition ont été proposés, c'est-à-dire des ensembles d'abstractions permettant de spécifier les interactions entre composants suivant leur organisation logique et leur déploiement, plutôt qu'en termes de moyens techniques utilisés pour transporter l'information de l'un à l'autre.

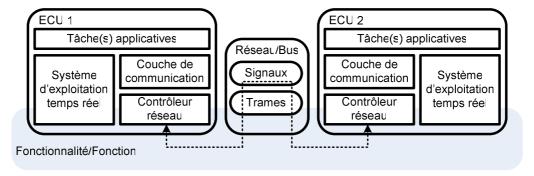

L'utilisation de modèles de répartition, mis en oeuvre par des intergiciels (*Middlewares*), permet donc aux développeurs de se concentrer sur les aspects fonctionnels de l'application. Elle affranchit le programmeur de certaines contraintes, telles que la gestion de la communication entre noeuds, ou l'hétérogénéité des architectures matérielles et logicielles.

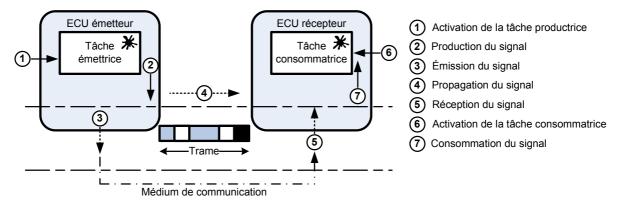

Entre les organes de l'automobile, les échanges se font par des signaux au niveau applicatif et par des trames au niveau du protocole réseau. Par exemple, certaines applications utilisent des intergiciels basés sur le passage de messages (MOM, *Message-Oriented Middlewares*), d'autres les objets distants (ORB, *Object Request Broker*) ou la mémoire partagée répartie.

Les intergiciels suppriment la dépendance d'une application répartie vis-à-vis d'un environnement matériel et d'un système d'exploitation, mais introduisent en contrepartie un encombrement supplémentaire. Cette situation constitue le paradoxe de l'intergiciel

Cependant, les exigences en temps réel, la variété des modèles de répartition et des intergiciels introduit une nouvelle problématique.

De plus, le fort besoin en prévisibilité (et par conséquent le déterminisme) des systèmes temps réel embarqués dans l'automobile, du fait de leur criticité, implique impérativement que les comportements des applications développées soient connus au départ et ne changent pas au cours de la vie du système.

Il paraît donc inenvisageable d'utiliser des intergiciels « génériques » [11] (spécifiés une seule fois et instanciés à la demande) car de surcroît, à défaut de disposer des ressources matérielles suffisantes, l'optimisation est primordial.

Les deux caractéristiques des systèmes temps réel embarquées, de prévisibilité et de limitation de ressource, rendent possible l'utilisation des techniques de validation hors-ligne dites *tests d'ordonnançabilités* sur le comportement de ces systèmes distribués pour en valider les contraintes temporelles tels qu'elles sont imposées par le cahier des charges.

Ces tests permettront de statuer, non seulement sur la faisabilité des applications, mais aussi de déterminer une configuration des échanges entre les entités du réseau. Ils concluent sur l'aptitude, d'une part, de l'architecture matérielle à supporter des exigences d'utilisations optimales des ressources en terme de consommation de bande passante, et d'autre part celle d'un intergiciel (exigences de qualité de service) et à s'assurer de la faisabilité de la communication distante, et à conclure quant à la sûreté de l'application temps réel.

Comme nous l'avons précédemment fait remarquer, [RSM06] a défraîchi le terrain en répondant à :

Comment spécifier une architecture d'implémentation ? (quels sont les composants logiciels et comment interagissent-ils entre eux);  Comment construire une configuration qui respecte les contraintes ? (configuration de messagerie, déploiement des composants logiciels au sein des tâches, configuration des tâches).

La méthodologie qu'il propose est basée sur l'utilisation de schémas d'assemblage [7] de composants conçus dans un même langage, mais l'ingénierie de conception des applications logicielles à base de composants logiciels [4] est ainsi née du besoin de faciliter, au maximum, la réutilisation du code, ce qui permet de concevoir des applications robustes, réduites, légers (peu encombrant) et très rapidement.

L'idée de développer des applications par utilisation, assemblage ou réutilisation de composant est ancienne, mais les débuts de sa mise en pratique à grande échelle sont récents. Le formalisme de programmation par objets est déjà au coeur des possibilités actuelles dans ce domaine (architectures logicielles génériques ou extensibles : *frameworks*, architectures pour l'interopérabilité : CORBA [OMG02], COM/OLE, composants répartis : *JAVA Beans*, contrôles Active/X), mais la prises en comptes du temps réel parmi les propriétés nécessaires de tels composants n'est pas encore usuelle.

Une barrière technologique s'oppose cependant à l'émergence de tels intergiciels : l'automatisation de leur construction par assemblage adapté à la configuration du support d'exécution et du modèle de répartition en minimisant la surcharge introduite par l'exécution des composants constituants l'intergiciel. Et le tout pour le temps réel.

L'objectif du stage est de mettre en oeuvre de telles techniques pour la génération de code [10] d'intergiciels de communication embarqués pour l'automobile. Plus précisément, cette approche doit permettre de concevoir un générateur d'un ensemble de tâches implémentant cette couche de communication pour un type d'application donné. Pour cela, elle prend en compte l'ensemble des événements requis et offerts par l'application tout en assurant la qualité de service requise par cette dernière (propriétés temps réel, garanties de convergence des exécutions) et minimisant la surcharge due à l'exécution de l'intergiciel.

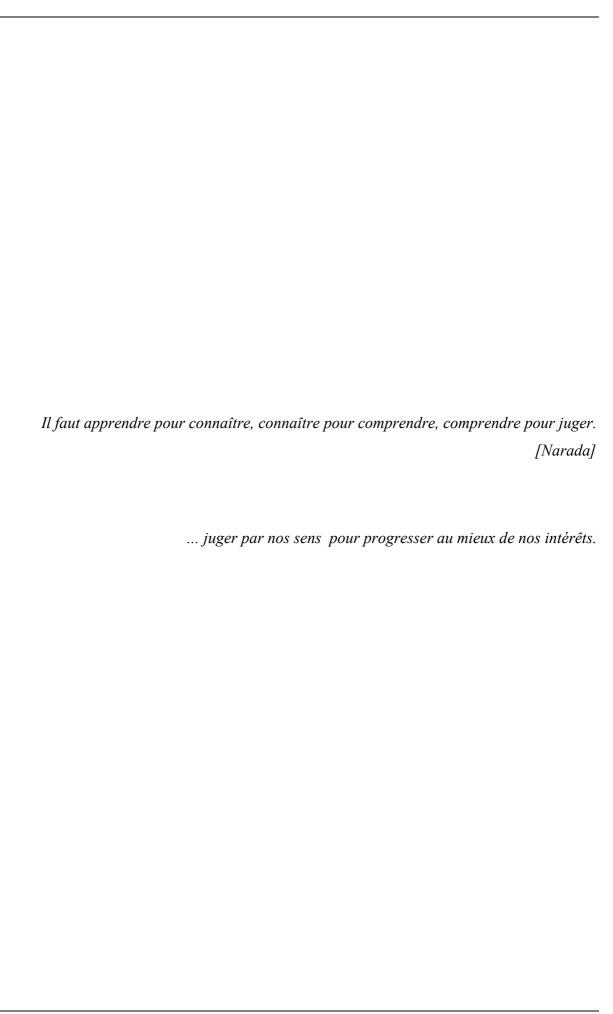

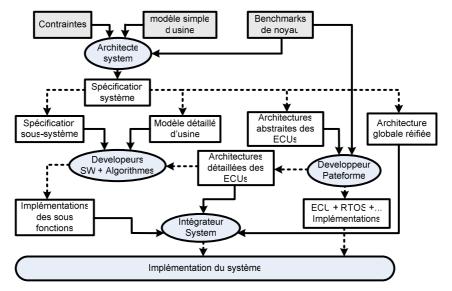

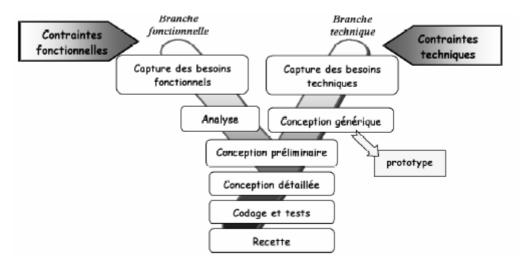

Le processus de réalisation, illustré par la Figure 1, que nous suivrons est : partant d'une spécification temporelle donnée des interactions entre entités applicatives (trafic des signaux et messagerie des trames, *Temporal traffic specification*), il devra générer un intergiciel (*Concrete Middleware model*) spécifiquement configuré à l'environnement (*Environmental properties specification*) sur lequel il sera déployé.

Figure 1 : Méthodologie de construction de l'intergiciel.

De plus, le résultat généré (une empreinte logiciel personnalisé) devra être exploitable sur une plateforme temps réel de démonstration.

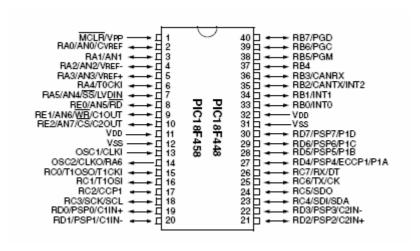

Technologiquement parlant, notre réalisation devrait rejoindre les hypothèses des models théoriques de [RSM06], à savoir :

- Les ECUs sont munis d'OSEK/VDX OS [6];

- Ces ECUs sont connectés à même réseau (local) de communication CAN [5];

# II - 3 Notre vision du système

Le nom que nous avons retenu pour identifier le système logiciel est « GenIETeR » en référence à l'acronyme de « GÉNérateur d'Intergiciels Embarqués Temps Réel » d'une part. Et d'autre part, faisant référence à la consonance que pourrait donner ce même acronyme avec le substantif « géniteur » et qui exprimerait le fait que le générateur serait le géniteur des empreintes logicielles cibles qu'il produirait. Ce plus indéniable a eu l'agrément du répondant du laboratoire, et représentait notre système comme le géniteur d'une longue lignée d'applications.

Figure 2 : Logo du projet GenIETeR.

Le logo ayant pour intérêt d'exprimer une empreinte logicielle générée pour un environnement cible particulier.

#### II - 4 Plan du mémoire

La suite de ce mémoire est organisée en deux parties :

#### Contexte de la distribution des systèmes temps réel embarqués dans l'automobile

La première partie est consacrée à l'étude théorique du contexte des systèmes temps réel, en passant en revue les modèles et les architectures qui les caractérisent. Nous introduisons, par la suite, le dimensionnement temps réel des applications embarqués dans l'automobile en mettant en exergue les contraintes temporelles imposées à leurs constructions. En second lieu, nous nous intéresserons à la distribution dans l'électronique des véhicules ainsi qu'aux exigences conséquentes de maîtrise des méthodologies de développement logiciel.

Ensuite, nous dégagerons la notion de modèle de répartition dans les architectures distribuées dans le domaine automobile, et nous motiverons la nécessité de recourir aux intergiciels. La section suivante situera alors notre problématique par rapport aux intergiciels existants. Elle dégagera les axes pertinents de ces projets par rapport aux besoins que nous avons identifiés. En conclusion, nous terminerons par la proposition d'une architecture d'intergiciel innovante, qui permet à un générateur de produire des instances d'intergiciels configurés et adaptés conformément au modèle de répartition de la solution à la quelle ils sont destinés

## Réalisation

La seconde partie de ce mémoire présente une synthèse des contributions de l'étude dont émane notre travail. Nous y retracerons les éléments ayant motivés nos choix pour la démarche de réalisation que nous avons suivi dans la construction d'une conception générique, et nous dégageons les aspects innovants de notre projet.

À la suite, nous ferons le tour du périmètre fonctionnel de notre solution générique, indépendamment du choix de tout modèle de répartition, pour ensuite présenter notre conception des mécanismes de base et des patrons de conception que nous avons retenue pour faciliter la réalisation de notre intergiciel par assemblage et configuration de composants au travers d'un générateur.

En dernier lieu, nous décrirons notre développement logiciel et les choix technologiques adoptés pour construire les prototypes de notre solution.

Le mémoire s'achèvera alors en rappelant les réalisations essentielles de notre travail et les perspectives ouvertes par l'architecture que nous proposons.

# III Contexte des systèmes temps réel embarqués dans l'automobile

#### III - 1 Introduction: Application, système informatique, environnement

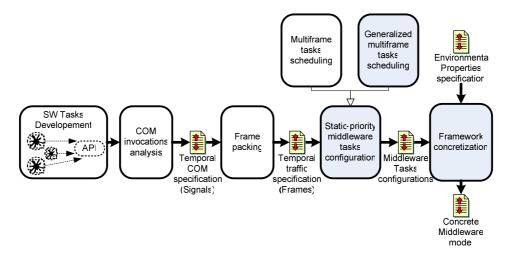

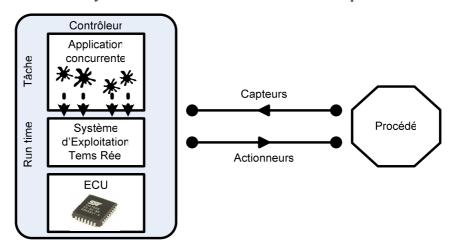

Une *application* est composée d'un *système informatique* (Lorsqu'il n'y aura pas de confusion possible nous l'appellerons simplement système) et d'un *environnement* physique avec lequel il interagit. Le système est composé d'un *calculateur* et d'un ensemble de programmes qu'il doit exécuter appelé *Applicatif* (cf. Figure 3).

Le système informatique, considéré par l'automaticien comme un simple maillon du système automatisé constitue l'unique centre d'intérêt de l'informaticien. L'environnement est défini comme l'ensemble de tous les éléments physiques qui sont extérieurs au système informatique et qui sont en interaction avec lui. La frontière entre l'environnement et le système informatique est parfois difficile à établir, c'est pourquoi nous avons choisi ici de considérer que l'ensemble des composants physiques qui peuvent être programmés (microprocesseurs, bus de communication, mémoire, interface E/S, etc.) fait partie du système informatique, alors que tous les composants physiques non-programmables constituent l'environnement. Il représente, du point de vue de l'automaticien, l'ensemble des éléments qui constituent le processus discrétisé à l'exception des convertisseurs analogique-numérique et numérique-analogique.

Figure 3: Application temps réel.

#### III - 1 - 1 Définitions et taxinomie

Chaque système informatique(isé) possède ses propres spécificités, étroitement dépendantes de son domaine d'utilisation. Toutefois, nous pouvons regrouper les applications informatiques parmi les trois catégories suivantes [ELL97], que la bibliographie qualifie de :

- Transformationnelles: toutes les applications permettant d'élaborer un résultat à partir de données connues et disponibles à l'initialisation de l'application. Leur traitement effectif est de plus non contraint dans la durée. Les applications de calcul scientifique ou de gestion de bases de données sont des exemples représentatifs de cette catégorie d'application;

- Interactives: toutes les applications permettant de fournir des résultats en fonction de données produites par l'environnement du système (essentiellement par l'interaction avec les utilisateurs), dans un délai de production satisfaisant au vue de contraintes aussi bien fonctionnelles, que non fonctionnelles. Parmi ces applications, les progiciels de bureautique sont certainement les plus connus ou les logiciels qu'on qualifie d'aide à un cœur de métier particulier;

- *Réactives*: toutes les applications dont les résultats sont entièrement liés à l'environnement dans lequel elles évoluent. De plus, la dynamique de cet environnement conditionne les instants de production de ces résultats.

Cette dernière catégorie est souvent assimilée aux systèmes temps réel puisque d'une part, elle suggère par le terme réactif, les paradigmes essentiels aux systèmes temps réel. Parmi les caractéristiques des systèmes réactifs [HAL93], il convient de souligner les suivantes :

- La concurrence : L'évolution du système se fait de façon concurrente avec son environnement. Il est naturel de voir un tel système comme un ensemble de composants parallèles qui coopèrent pour réaliser la tâche assignée au système entier. Ainsi, le système comprend au moins deux types de processus coopérants qui assurent d'une part l'échange des donnes et d'autre part le traitement de celles-ci ;

- Les contraintes temporelles: Les systèmes réactifs sont soumis à des contraintes temporelles fortes (temps de réponse borné, fréquence d'échantillonnage d'un signal, etc.), spécifiées lors de la conception. La vérification de celles-ci avant utilisation est nécessaire pour la validation du système. On parle dans ce cas de systèmes temps réel;

- La sûreté: Du fait de leurs divers rôles critiques (par exemple, le contrôle d'une centrale nucléaire ou bien celui du train d'atterrissage d'un avion) impliquant des enjeux importants aussi bien en vies humaines qu'en termes économiques, il est primordial d'éviter tout risque de dysfonctionnement. La sûreté de fonctionnement devient de fait une question essentielle pour ces systèmes. Cela entraîne un besoin de

méthodes de développement qui intègrent des outils et techniques adéquates pour la vérification et l'analyse ;

- Le déterminisme. C'est une propriété fortement souhaitée dans les systèmes temps réel. Elle facilite la prédiction sur les comportements d'un système. Elle permet aussi de reproduire des comportements d'un système dans l'optique, par exemple, de mettre en évidence des erreurs susceptibles de survenir lors d'une exécution de celui-ci;

- La maintenance. Les systèmes réactifs sont parfois embarqués (dits aussi enfouis de façon équivalente dans le reste de ce mémoire), posant ainsi quelques difficultés pour les modifier après la réalisation. Dans ce cas, une stratégie prédictive de maintenance, basée sur des modèles a priori, peut jouer un rôle important dans le choix d'une structure de système facile à modifier. Les systèmes embarqués sont surtout caractérisés par des contraintes matérielles (ressources limitées en espace mémoire et puissance de calcul);

- La répartition. Ce sont souvent des systèmes géographiquement distribués pour diverses raisons : la délocalisation des éléments d'un système (capteurs chargés de récupérer les entrées, actionneurs responsables de la production des sorties, processeurs servant de support d'exécution), le gain de performance grâce à l'utilisation de plusieurs calculateurs pour améliorer les temps de réponse des systèmes, la tolérance aux fautes à travers la duplication de certaines parties d'un système. Nous reviendrons plus loin en détail sur ce type système et qui bien sûr nous intéresse ici.

L'interactivité et le temps et d'autre part l'émergence de l'informatisation du contrôle de procédés de plus en plus complexes contribue à une utilisation en forte croissance de ce type de systèmes. Les domaines concernés vont des chaînes de production aux transports aériens en passant par des robots de plus en plus perfectionnés, tels que les modules d'exploration planétaire, l'aide à la conduite automobile ou aux applications multimédia contraintes par le temps. Si le caractère réactif prédomine dans ces exemples, la criticité du temps est autant importante pour ces systèmes. En effet, alors que le retard de quelques millisecondes ou la perte d'une trame vidéo sur un réseau ne nuira qu'au confort d'un utilisateur, le retard de la décision de redresser les roues d'une voiture lors d'un tête-à-queue peut provoquer une catastrophe sur le plan humain ainsi que des pertes financières considérables et surtout l'image de marque du constructeur.

Par référence à ces caractéristiques, la conception des systèmes réactifs temps réel distribués requiert des méthodologies suffisamment élaborées pour répondre aux exigences d'une mise en œuvre fiable. Pour toutes ces raisons, il est nécessaire de s'assurer du bien saisi

des notions qui régissent ce domaine du temps réel. Ce que nous tenterons de présenter dans la suite de ce mémoire

# III - 1 - 2 Les systèmes réactifs temps réel

Il existe de nombreuses définitions des systèmes temps réel [STA88, CNR88] qui évoquent les caractéristiques précitées au paragraphe précédent. Nous citerons la définition donnée par [AD92] qui introduit les notions de critères temporels :

« Système de traitement de l'information ayant pour but de commander un environnement imposé en respectant les contraintes de temps et de débit (temps de réponse à un stimulus, taux de perte d'information toléré par entrée) qui sont imposées à ses interfaces avec cet environnement».

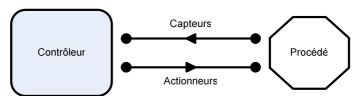

Cette définition met en évidence deux éléments distincts : une ou plusieurs entités physiques constituant le procédé, dont le rôle est d'agir et de détecter, et un contrôle informatique, nommé contrôleur ou application temps réel qui est le décideur des actions (ou réactions) du procédé. Le contrôleur reçoit des informations sur l'environnement du procédé à l'aide de capteurs et commande les changements d'état du procédé via des actionneurs. La Figure 4 donne un aperçu des interactions qui existent entre procédé et contrôleur d'un système temps réel.

Figure 4 : Un système Temps Réel - Interaction procédé contrôleur.

#### III - 1 - 3 Application temps réel et applications concurrentes

Pour gérer la dynamique des périphériques (ou interfaces) du procédé et de son environnement, il est donc nécessaire de développer des techniques logicielles permettant de traiter les informations issues des capteurs sur l'unité de calcul pour produire les actions adéquates sur les actionneurs. Pour cela, citons le principe des applications concurrentes dont nous pouvons trouver une définition dans [BW90] :

«La programmation concurrente est le nom donné aux techniques et notations de programmation pour exprimer le potentiel parallèle et résoudre les problèmes inhérents de synchronisation et de communication. L'implémentation du parallélisme est un problème des systèmes informatiques (logiciel ou matériel) qui est avant tout indépendant de la programmation concurrente. La programmation concurrente est importante puisqu'elle permet de faire abstraction de l'étude du parallélisme sans être confronté aux détails de l'implémentation».

Cette approche est particulièrement prometteuse en ce qu'elle permet d'augmenter la puissance d'expressivité et de réduire le coût de développement par rapport à une application fonctionnant sans parallélisme. Toutefois, l'utilisation des applications concurrentes n'est pas sans inconvénients. En effet, il devient nécessaire de fournir un moteur d'exécution (*Runtime* est un programme ou une bibliothèque qui permet l'exécution d'un autre programme) ou noyau temps réel pour superviser l'exécution sur l'unité de calcul des différentes tâches du système.

#### III - 1 - 4 Notion de tâche

La multiplicité des capteurs et des actionneurs introduit implicitement, du point de vue logiciel, l'utilisation de différentes tâches permettant de les piloter. Ce sont des programmes (flot de contrôle propre, distinct) séquentiels dédiés au traitement d'un des composants du système temps réel (aussi bien d'un point de vue fonctionnel que structurel). Par exemple un programme temps réel peut être constitué d'une collection de tâches telles que :

- Des exécutions périodiques de mesures de différentes grandeurs physiques (pression, température, accélération, etc.). Ces valeurs peuvent être comparées à des valeurs de consignes liées au cahier des charges du procédé;

- Des traitements à intervalles réguliers ou programmés ;

- Des traitements en réaction à des évènements internes ou externes ; dans ce cas les tâches doivent être capables d'accepter et de traiter en accord avec la dynamique du système les requêtes associées à ces évènements.

Ainsi nous pouvons caractériser une application temps réel d'application multitâches.

#### III - 1 - 5 Interactions entre les tâches

Les tâches, dont les comportements sont séquentiels, peuvent interagir entre elles pour assurer le bon fonctionnement global de l'application que le système pilote. Il est donc nécessaire de fournir parallèlement à ces tâches des moyens de communication et de synchronisation permettant de gérer tous les problèmes liés aux accès à des ressources communes, comme par exemple les périphériques (terminaux, imprimantes, etc.), ou l'exécution des tâches ordonnées par des critères de précédence. Ces critères de précédence des tâches sont pour la plupart issus, soit d'un désir d'échange de données entre deux tâches, soit de la volonté de synchroniser deux tâches pour que la suite de leur exécution s'effectue en parallèle par un mécanisme de rendez-vous. Dans le premier cas, on identifie une tâche

émettrice et une tâche réceptrice. Nous parlons de tâches indépendantes lorsque l'application n'utilise ni ressources critiques, ni synchronisation.

# III - 1 - 6 Architecture matérielle d'une application temps réel

Nous appelons *architecture matérielle*, l'ensemble des composants physiques qu'il est nécessaire d'ajouter à un processus pour réaliser l'application temps réel. L'architecture matérielle est donc composée d'un calculateur, de capteurs et d'actionneurs.

# Le calculateur : Microprocesseurs, microcontrôleurs

Un *microprocesseur* est composé d'un CPU (*Central Processing Unit*) et d'unités de communication pour communiquer avec des périphériques externes ou d'autres microprocesseurs. Le CPU est une machine séquentielle constituée généralement d'un *séquenceur d'instruction* (SI), d'une *unité de traitement* (UT) et d'une *mémoire*. Les dernières générations de microprocesseurs peuvent aussi intégrer une *unité de calcul flottant* (FPU) dont le but étant d'accélérer considérablement certains calculs mathématiques (multiplication, division, sinus, arrondi, etc.).

Un *microcontrôleur* est un microprocesseur intégrant un certain nombre d'interfaces supplémentaires (mémoires, timers, PIO : *Parallel Input Output*, décodeurs d'adresse, etc.). Ces nombreuses entrées-sorties garantissent un interfaçage aisé avec un environnement extérieur tout en nécessitant un minimum de circuits périphériques ce qui les rend particulièrement bien adaptés aux applications temps réel embarquées. Du fait de leur forte intégration en périphérique (certains microcontrôleurs vont jusqu'à intégrer des fonctions spécialisées dans la commande des moteurs), les microcontrôleurs sont souvent moins puissants que les microprocesseurs; le CPU qu'ils intègrent est généralement en retard d'une ou même de deux générations.

Dans la suite du document, nous utiliserons le terme de ECU (*Electronic Control Unit*) pour désigner indifféremment un microprocesseur ou un microcontrôleur pourvu qu'il soit doté d'une architecture logicielle.

#### Le capteur

Le capteur est un dispositif conçu pour mesurer une grandeur physique (température, pression, accélération, etc.) en la convertissant en une tension ou un courant électrique. Le signal électrique issu d'un capteur est un signal continu qui doit être discrétisé pour pouvoir être traité par le calculateur. Cette discrétisation ou numérisation est réalisée par un circuit appelé, Convertisseur Analogique-Numérique (C.A.N).

#### Actionneur

Un actionneur est un dispositif qui convertit un signal électrique en un phénomène physique (moteur, vérin électrique, voyant, haut-parleur, etc.) censé modifier l'état courant du processus. Le signal de commande fourni par le calculateur est un signal numérique qu'il faut convertir en signal électrique analogique à l'aide d'un Convertisseur Numérique Analogique (C.N.A).

#### Environnement d'exécution

Nous avons vu précédemment qu'un classement des systèmes temps réel pourrait être fait selon leurs caractéristiques. D'un autre point de vue, matériel cette fois, les systèmes temps réel peuvent être classés selon leur couplage avec des éléments matériels avec lesquels ils interagissent. Ainsi, l'application concurrente et le système d'exploitation qui lui est associé peuvent se trouver :

- Soit directement dans le procédé contrôlé : c'est ce que l'on a appelé des systèmes embarqués (embedded systems). Le procédé est souvent très spécialisé et fortement dépendant du calculateur. Les exemples de systèmes embarqués sont nombreux : contrôle d'injection automobile, stabilisation d'avion, électroménager, etc. C'est le domaine des systèmes spécifiques intégrant des logiciels sécurisés optimisés en encombrement et en temps de réponse ;

- Soit le calculateur est détaché du procédé : c'est souvent le cas lorsque le procédé ne peut être physiquement couplé avec le système ou dans le cas général des contrôle/commandes de processus industriels. Dans ce cas, les applications utilisent généralement des calculateurs industriels munis de systèmes d'exploitation standard ou des automates programmables industriels, comme par exemple dans les chaînes de montage industrielles.

Ayant introduit la notion de calculateur ou de processeur, nous distinguons trois grandes catégories d'architecture matérielle pour les Systèmes Temps Réel en fonction de leur richesse en terme de nombre de cartes d'entrée/sortie, de mémoires, de processeurs et de la présence de réseaux.

L'architecture monoprocesseur : un unique processeur exécute toutes les tâches de l'application concurrente. Dans ce cas, la notion de parallélisme n'a plus vraiment de sens puisque le temps processeur est partagé entre toutes les tâches. Nous parlons plutôt de pseudo-parallélisme ou d'entrelacement des exécutions. En effet, le parallélisme des tâches semble réel à l'échelle de l'utilisateur mais le traitement sur l'unique processeur s'opère de façon séquentielle.

- L'architecture multiprocesseurs : l'exécution de toutes les tâches est ici répartie sur plus de deux processeurs partageant une unique mémoire centrale. La coopération entre tâches se fait par partage des informations placées en mémoire. Donc ici, le traitement est réellement parallélisé.

- L'architecture distribuée : c'est le cas des architectures multiprocesseurs ne partageant pas de mémoire centrale. Ces processeurs sont reliés entre eux par l'intermédiaire de réseaux permettant d'assurer les communications entre les différentes tâches. La coopération se fait ici par communication par réseau ou par bus.

Pour le contexte de ce mémoire, nous retiendrons de cette taxonomie des différentes formes que peuvent prendre les systèmes temps réel, le cas des architectures distribuées monoprocesseur. La figure ci-dessous montre plus particulièrement l'architecture monoprocesseur d'un tel système en affinant l'interaction entre le procédé et le contrôleur.

Figure 5 : Architecture générale d'une application temps réel monoprocesseur.

## III - 1 - 7 Architecture logicielle d'une application temps réel

Avant de passer à l'architecture logicielle, il est intéressant de dire que si cette architecture matérielle permet de mettre en avant les qualités réactive de ces systèmes, il n'en va pas de même pour la seconde notion primordiale : le temps. Il est vital pour le procédé de pouvoir garantir que le traitement des différents évènements interviendra dans des délais adaptés à l'évolution du procédé. Pour cela, il est nécessaire d'associer à un système réactif des contrôles temporels. Ceux-ci doivent évaluer la vitesse de réaction du système de contrôle. Deux approches peuvent être envisagées : l'approche synchrone et l'approche asynchrone. Dans le premier cas, le respect des délais est implicite. Dans le deuxième cas, il devra être contrôlé. De plus, il sera nécessaire de se placer dans un environnement d'exécution adapté, qui sera fourni par un noyau temps réel ou exécutif temps réel, proposant des routines temporelles spécifiques.

Nous pouvons maintenant décomposer l'architecture logicielle d'un système temps réel en deux couches. La première, consiste en une application concurrente composée d'un ensemble de tâches comme nous l'avons cité plus haut. Nous utilisons également le terme d'application multi-tâches. La deuxième, de plus bas niveau, joue le rôle d'un système d'exploitation minimal chargé de faire le lien entre le procédé physique et l'application multitâches. Ce système d'exploitation, appelé exécutif temps réel, est de par la considération de l'asynchronisme (quantification du retard entre l'occurrence d'un évènement et la terminaison de l'exécution de la tâche qui lui est associée), dirigé par les évènements, ceux-ci pouvant provenir de différentes sources :

- Du procédé physique par l'intermédiaire d'interruptions matérielles associées à chaque évènement;

- Du temps : chaque système est muni d'une horloge temps réel pouvant générer des interruptions ;

- De l'application multi-tâches lorsque par exemple l'exécution d'une tâche est conditionnée par l'exécution d'autres tâches. Dans ce cas il faut que l'exécutif retarde l'exécution de cette tâche pour permettre au préalable au processeur d'exécuter les autres.

# III - 1 - 8 Le rôle de l'exécutif temps réel

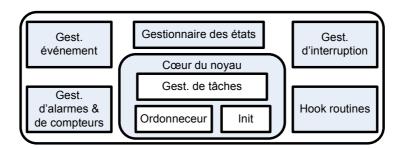

L'exécutif temps réel a pour rôle de décrire les conditions événementielles d'exécution des tâches de même que les conditions de préemption (réquisition du processeur à une tâche et sa mise en attente forcée) et de reprise d'exécution sur le processeur. On appelle donc exécutif temps réel, la partie du système d'exploitation chargée de gérer l'exécution des tâches conformément aux contraintes exprimées. Cet exécutif est constitué d'une base communément appelée ordonnanceur, encapsulé par des niveaux qui offrent aux tâches les services requis pour leurs synchronisations, communications, temporisations, etc.

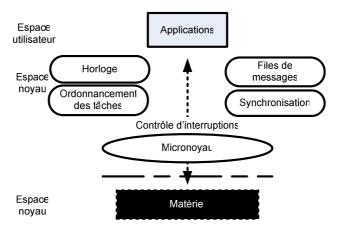

Figure 6 : Les systèmes d'exploitation temps réel.

L'exécutif temps réel propose différents services et garanties facilitant l'exécution et la communication des tâches. Ces services appelés primitives temps réel peuvent être directement utilisés dans les tâches et sont de différentes natures :

- Gestion des tâches ;

- Gestion des ressources partagées ;

- Gestion des communications entre tâches ;

- Gestion du temps ;

- Gestion des interruptions et de la mémoire, etc.

#### Gestion des communications entre tâches

Il existe principalement deux types de communications entre tâches. La première dite asynchrone utilise le concept de boîte aux lettres. Ce dernier est fondé sur l'utilisation d'un tampon d'échange de données : une tâche émettrice dépose chaque donnée dans ce tampon qui les gère en mode FIFO; la tâche réceptrice, lorsqu'elle a besoin de la donné, doit soit se mettre en attente si le tampon est vide, soit recueillir la donnée la plus ancienne. La deuxième forme de communication est dite synchrone et est la plupart du temps utilisée par les langages synchrones. Elle utilise la méthode du rendez-vous qui permet à deux tâches de se synchroniser à un instant précis de leur exécution pour s'exécuter par la suite de façon conjointe.

#### Gestion des interruptions et de la mémoire

La gestion des interruptions doit permettre de prendre en compte toutes les sollicitations matérielles et logicielles. On utilise pour cela un service de routines d'interruption (ou ISR pour *Interruption Service Routine*) permettant d'associer un traitement à chaque exécution. La durée de chaque routine doit être la plus courte possible puisque les routines s'exécutent de manière atomique (les interruptions sont masquées durant leurs exécutions). La gestion de la mémoire peut être faite suivant deux modèles : soit l'exécutif et les tâches ont chacun une zone de mémoire réservée, soit chaque tâche ainsi que l'exécutif possèdent une zone mémoire séparée et protégée.

Toutes ces fonctions de l'exécutif temps réel existent sous forme de primitives ou routines élémentaires dont la plupart possèdent des bribes atomiques, c'est-à-dire ne pouvant pas être interrompues par la gestion des interruptions matérielles. Ces portions ininterruptibles engendrent des retards dans la gestion des évènements qu'ils soient logiciels ou matériels. Pour assurer un service optimal aux traitements des tâches, il faut réduire ces portions au minimum. C'est justement l'un des critères d'évaluation des exécutifs temps réel du marché

(ou RTOS pour *Real Time Operating System*), ce qui les différentie des systèmes d'exploitation classiques. Les RTOS ou les systèmes à micronoyau temps réel assurent ainsi une borne temporelle pour chacune des primitives temps réel qu'elles proposent. Parmi ces RTOS, nous pouvons citer par exemple OSEK/VDX, Vxworks, RTEMS, Lynx OS, Linux RT.

Nous reviendrons en détails sur notre choix pour l'exécutif OSEK/VDX dans la section consacrée à la réalisation.

# III - 1 - 9 Les systèmes à micronoyau

L'objectif principal des systèmes à micronoyau est de maîtriser la complexité croissante du système d'exploitation en les rendant synthétiques et homogènes. La première caractéristique des systèmes à micronoyau est la taille réduite de leur code (de quelques kilos octets à quelques centaines de kilos octets). Cette réduction de taille du noyau a pour conséquence directe la limitation des services proposés qui sont complétés par des couches transversales de service (au sens programme fournissant des services) sous forme de modules ou de librairies. Actuellement, presque seuls les systèmes d'exploitation temps réel sont à micronoyau et pour la plupart d'entre eux, les programmes applicatifs temps réel sont chargés dans l'espace noyau. Il n'y a donc aucun transfert de données entre espace utilisateur et espace noyau pour accéder aux fonctionnalités du système d'exploitation et donc une minimisation du temps d'exécution due aux nombreuses transmissions de données vers le micronoyau.

Le fait que les applicatifs temps réel résident dans l'espace noyau (cf. Figure 6) permet de les « rapprocher du matériel », améliorant ainsi grandement les performances en termes de temps de réponse. Toutefois, l'inconvénient majeur de cette approche réside dans l'impossibilité de tirer profit des services uniquement accessibles dans l'espace utilisateur tels que la protection de la mémoire (les erreurs de segmentation qui protègent le système d'exploitation et les autres applications des problèmes d'adressage), d'user de primitives d'allocation dynamique de mémoire et l'utilisation de *drivers* matériels spécifiquement dédiés à l'espace utilisateur.

#### III - 1 - 10 Quantification du temps

L'architecture logicielle des applications temps réel permet d'identifier le traitement d'un évènement à une tâche. Nous avons vu que ce traitement doit intervenir dans des délais appropriés. Il faut donc être à même de vérifier que les contraintes temporelles soient bien