# ACOTES Project: Advanced Compiler Technologies for Embedded Streaming

Harm Munk, Eduard Ayguadé, Cédric Bastoul, Paul J. Carpenter, Zbigniew Chamski, Albert Cohen, Marco Cornero, Philippe Dumont, Marc Duranton, Mohammed Fellahi, et al.

# ▶ To cite this version:

Harm Munk, Eduard Ayguadé, Cédric Bastoul, Paul J. Carpenter, Zbigniew Chamski, et al.. ACOTES Project: Advanced Compiler Technologies for Embedded Streaming. International Journal of Parallel Programming, 2011, 39 (3), pp.397-450. 10.1007/s10766-010-0132-7. inria-00551083

# HAL Id: inria-00551083 https://inria.hal.science/inria-00551083

Submitted on 2 Jan 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# ACOTES Project: Advanced Compiler Technologies for Embedded Streaming

Harm Munk,<sup>1</sup> Eduard Ayguadé,<sup>5</sup> Cédric Bastoul,<sup>3</sup> Paul Carpenter,<sup>5</sup> Zbigniew Chamski,<sup>1</sup> Albert Cohen,<sup>3</sup> Marco Cornero,<sup>4</sup> Philippe Dumont,<sup>13</sup> Marc Duranton,<sup>1</sup> Mohammed Fellahi,<sup>3</sup> Roger Ferrer,<sup>5</sup> Razya Ladelsky,<sup>2</sup> Menno Lindwer,<sup>6</sup> Xavier Martorell,<sup>5</sup> Cupertino Miranda,<sup>3</sup> Dorit Nuzman,<sup>2</sup> Andrea Ornstein,<sup>4</sup> Antoniu Pop,<sup>7</sup> Sebastian Pop,<sup>8</sup> Louis-Noël Pouchet,<sup>3</sup> Alex Ramírez,<sup>5</sup> David Ródenas,<sup>5</sup> Erven Rohou,<sup>4</sup> Ira Rosen,<sup>2</sup> Uzi Shvadron,<sup>2</sup> Konrad Trifunović,<sup>3</sup> Ayal Zaks<sup>2</sup>

- <sup>1</sup> NXP Semiconductors, The Netherlands

- $^2\,$  IBM Haifa Research Laboratories, Israel

- $^{3}\,$  Alchemy Group, INRIA Saclay and LRI, Paris-Sud 11 University, France

- <sup>4</sup> STMicroelectronics, Cornaredo (MI), Italy

- <sup>5</sup> Universitat Politècnica de Catalunya, Spain

- $^{\rm 6}\,$  Silicon Hive, Eindhoven, The Netherlands

- <sup>7</sup> Centre de Recherche en Informatique, MINES ParisTech, France

- $^{8}\,$  Compiler Performance Engineering, Advanced Micro Devices, Austin, Texas

Streaming applications are built of data-driven, computational components, consuming and producing unbounded data streams. Streaming oriented systems have become dominant in a wide range of domains, including embedded applications and DSPs. However, programming efficiently for streaming architectures is a challenging task, having to carefully partition the computation and map it to processes in a way that best matches the underlying streaming architecture, taking into account the distributed resources (memory, processing, real-time requirements) and communication overheads (processing and delay).

These challenges have led to a number of suggested solutions, whose goal is to improve the programmer's productivity in developing applications that process massive streams of data on programmable, parallel embedded architectures. StreamIt is one such example. Another more recent approach is that developed by the ACOTES project (Advanced Compiler Technologies for Embedded Streaming). The ACOTES approach for streaming applications consists of compiler-assisted mapping of streaming tasks to highly parallel systems in order to maximize cost-effectiveness, both in terms of energy and in terms of design effort. The analysis and transformation techniques automate large parts of the partitioning and mapping process, based on the properties of the application domain, on the quantitative information about the target systems, and on programmer directives.

This paper presents the outcomes of the ACOTES project, a 3-year collaborative work of industrial (NXP, ST, IBM, Silicon Hive, NOKIA) and academic (UPC, INRIA, MINES ParisTech) partners, and advocates the use of Advanced Compiler Technologies that we developed to support Embedded Streaming.

#### 1. INTRODUCTION

Streaming applications which dominantly process large amounts of data have increasing demands for processing power. This demand stems from several requirements: on the one hand, the amount of processing per data element increases because of higher quality requirements of the result (e.g. video processing). On the other hand, the amount of data per unit of time also increases (e.g. higher communication speeds in wireless networks). This, in fact, calls for higher silicon efficiency, a demand that was met up to a few years ago by designing Application Specific Integrated Circuits (ASICs). The time to design such ASICs is, however, proportional to the complexity of the ASIC; as the complexity of the ASIC grows exponentially, their design becomes economically infeasible. Designers have thus shifted their focus toward programmable platforms, thereby potentially amortizing the design cost across several applications, or even application domains. Programmable platforms have traditionally been unable to meet the high throughput requirements: they

were mostly designed for general purpose computation and offering limited parallelism opportunities.

Several recent architectures do expose parallelism to the application programmer. This, however, shifts the problem of managing complexity partly from the hardware designer to the software application developer. Exploiting available parallelism optimally requires intimate knowledge of both the application and the target platform. Automating the extraction of parallelism from sequential algorithmic descriptions has proven to be an extremely complex task in general.

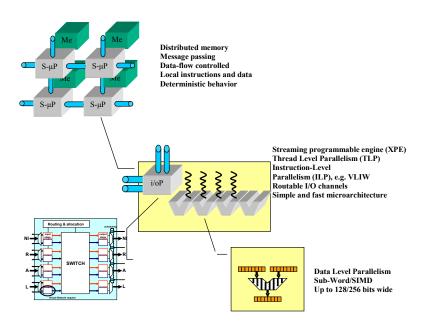

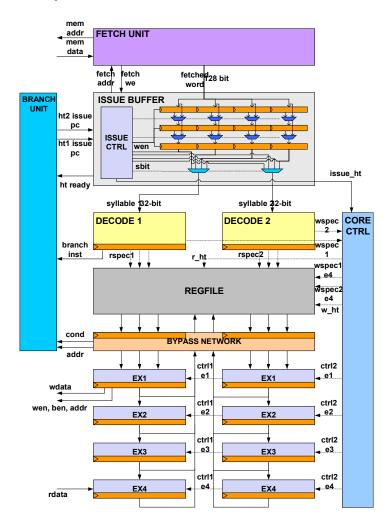

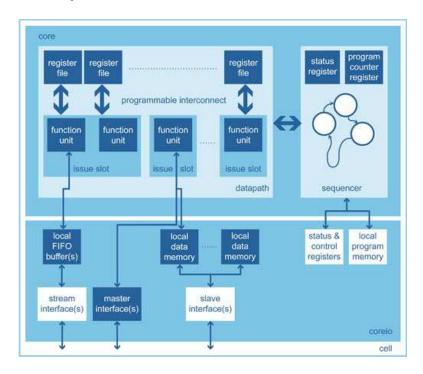

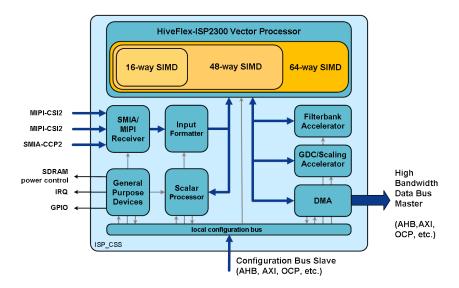

In 2006, IBM, Philips (later: NXP Semiconductors), STMicroelectronics, NOKIA, INRIA and UPC initiated the ACOTES project to advance the support of application programmers in parallelising applications on highly parallel architectures. They were later joined by Silicon Hive and MINES ParisTech. The ACOTES project concentrates on developing tools to assist the application programmer in achieving optimal parallelism. From the outset we decided to use a mainstream language (C), an existing compiler framework (the GNU Compiler Collection - GCC), focus on the data streaming application domain, and target three distinct state-of-the-art multicore architectures (Cell Broadband Engine, xSTream processor, and Ne-XVP). This way we were able to concentrate our efforts on support for parallelization across several levels. Data streaming applications typically contain potential for both coarse-grain task-level parallelism across threads, fine-grain data-level parallelism residing inside nested loops of SIMD-like computations, and also memory-level parallelism to optimize data transfers.

# 1.1. Applications

The ACOTES project focuses on the data-streaming application domain. In this paper we present experimental results using three applications from this domain: FM-radio, H264 and Gamma-correction. The project, however, uses several additional streaming applications to drive the developments in the project.

#### **FMradio**

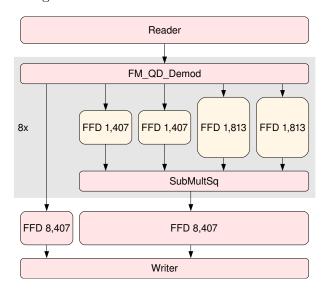

The FM-radio application was extracted and adapted from the GNU Radio project <sup>(1)</sup>. It contains about 500 lines of code. The application receives an input stream, applies a number of filters to it, and finally writes an output stream. Several of the filters apply the same

transformation with different configuration parameters. The structure of the filters is shown in Figure 1. The FFD filter is the most time consuming one.

Fig. 1. FMradio filters structure

#### H.264

The H.264 application is part of the MPEG-4 standard <sup>(2)</sup>. It consists of a video and audio coder and decoder, achieving high levels of compression for improved transmission and storage of streaming media files. We study a subset of its internal algorithms to demonstrate the vectorization capabilities introduced in GCC.

#### Gamma Correction

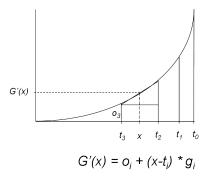

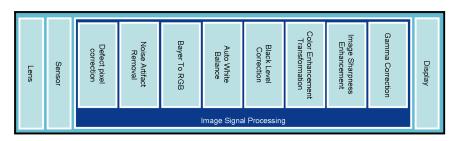

The Gamma correction algorithm is one of the last phases in a typical image processing pipeline. It features a triply nested loop scanning over the pixels of a 2D image. For each pixel, it searches through an array of thresholds until it finds the threshold interval (plotted along the X-axis of Figure 2) within which the color value  $\mathbf{x}$  lies. The new pixel value is inferred from the offset, gradient and threshold of the interval. The signal processing flow is depicted in Figure 3.

Fig. 2. Gamma correction filter

Fig. 3. Image signal processing algorithm pipeline

The current customer requirement from the Gamma correction algorithm calls for pixel throughtput of about 4 cycles-per-pixel for the whole image signal processing pipeline. A straightforward scalar implementation of Gamma correction takes 154 cycles per pixel. This application illustrates the potential of outer-loop vectorization, developed within ACOTES.

# 1.2. Compiler Structure

GCC, the GNU Compiler Collection is a compiler framework supporting several mainstream programming languages as well as a large array of target processors. The framework is actively maintained by the GCC project of the Free Software Foundation, supervised by the GCC steering committee. The project consists of a mainstream development part, which results in regular releases, and several development parts often dubbed development branches. The mainstream

development is closely supervised by the GCC steering committee delegating responsibilities to leading developers. Results from development branches are incorporated into the mainstream only after scrutiny and approval by designated maintainers. This setup allows for the simultaneous development of a production quality compiler and a set of new, experimental prototypes.

The structure of GCC itself is that of a traditional compiler: a front-end for language parsing and semantics checking, a "middle-end" for target-independent optimisations, and a back-end for code generation and target-specific optimisations. It is this combination of support for mainstream languages and targets, industrial mainstream quality, the ability to experiment freely in parallel to the main line of development without interference, a vibrant supporting community and its adoption by a vast number of users that makes GCC an ideal choice for a project such as ACOTES.

# 1.3. ACOTES Project Structure

The ACOTES project is divided into a set of subtopics:

- Abstract Streaming Machine. In order to target several distinct architectures, we developed an abstract machine model that captures the streaming characteristics of the platforms in a common model called the Abstract Streaming Machine, or ASM.

- Streaming Programming Model. Starting from the C-language, we developed a number of extensions that express parallelism opportunities in the source, collectively referred to as the Streaming Programming Model, or SPM. As an extra requirement, these language extensions had to be neutral with respect to the core C language: the pragma mechanism is ideal for this purpose. This decision, however, surfaced a shortcoming of GCC, which is not very well suited for experimenting with front-end transformations. This prompted the project to turn to Mercurium (3) as a source-to-source prototyping tool for implementing the SPM.

- Middle-end optimisations. Streaming applications are characterized by nested loops of computations. Considerable performance improvements can be gained by applying optimisations to these loops. The project concentrated its effort on the polyhedral model for high-level loop optimisations in the middle-end.

- Back-end optimisations. Modern architectures often contain SIMD-like instructions, also called vector instructions. As these

instructions are target specific, opportunities for applying them are detected in the back-end of the compiler.

7

Code generation. Code generation is typically specific to each architecture; in the ACOTES project, we therefore decided to concentrate our effort on common back-end algorithms and on common back-end formats.

Apart from the technical topics, the project has a separate activity to disseminate its results, part of which is maintaining contact with the GCC and HiPEAC network of excellence communities.

This article describes the design and implementation of the ACOTES tool-chain. Section 2 describes related work. Sections 3 and 4 respectively present the Abstract Streaming Machine (compilation target) and the Streaming Programming Model (extensions to the ISO-C language). Section 5 presents the automatic loop nest optimisations and vectorisation, and the interaction between them. Section 6 describes the target platforms and the code generation phase of the compiler for these architectures. Section 7 presents some experimental results, and Section 8 concludes.

#### 2. RELATED WORK

The ACOTES project takes a holistic approach to parallel streamprogramming, spanning over the whole flow of compilation down to the runtime system. It has connections with a large number of related work. This section compares our approach with the most closely related results in the field of high-performance embedded computing.

StreamIt is a long running project with a publicly available compiler and benchmark suite. The StreamIt <sup>(4)</sup> language imposes a hierarchical structure on the program composed of filters, pipelines, split-join operators and feedback loops. It requires the developer to structure the program into separate work functions per filter, in contrast to using pragmas which maintain the original structure of the code. The StreamIt compiler <sup>(5)</sup> targets the Raw Architecture Workstation, symmetric and heterogeneous multicore architectures, and clusters of workstations, where aggressive task-level optimizations are performed automatically <sup>(6)</sup>. StreamIt does not employ a generic machine model like the ACOTES ASM, and the ACOTES SPM is much more expressive than the cyclostatic data-flow model of computation underlying StreamIt <sup>(7)</sup>, while still facilitating compilation-time task-level optimizations <sup>(8,9)</sup>. Compared to StreamIt, our ap-

proach involves a tight coupling of task- and loop-level optimizations, enabling more relevant decisions about synchronization adaptation, communication, multi-level exploitation of parallelism and locality. The optimization strategy relies on iterative search which helps us find interesting tradeoffs inaccessible to partitioned compilation flows separating these problems into different representations and passes <sup>(10)</sup>. We will illustrate this design on the interplay between task-level and loop-level optimizations, including automatic vectorization.

Sequoia is a well known data parallel language exploiting the structure of data-centric algorithms <sup>(11)</sup>. It severely restricts the model of computation to hierarchical fork-join parallel sections, but allows the programmer to state data affinity to portions of iteration space. For each hardware platform, the application programmer must supply a mapping that takes the "abstract" hierarchy defined in the application, and assigns pieces of it onto specific hardware. This approach requires more effort from the application providers and requires them to learn the memory characteristics of each hardware platform, but it is certainly a pragmatic solution that could be added as an optional feature to the ACOTES programming model.

The new specification of OpenMP <sup>(12,13)</sup>, version 3.0, supports task parallelism using the new task directive. This directive specifies that the serial code within it can be executed by another thread inside the scope of a parallel region. In OpenMP, every time the task directive is reached a new task is created to execute its body. In the ACOTES SPM, all the inner tasks are created once when the taskgroup directive is reached, and a value is sent on each input stream each time the task directive is reached. This is a form of synchronization that does not exist in the OpenMP 3.0 proposal. However, there are other proposals for OpenMP that add synchronization between threads. Gonzalez et al. (14,15) propose three new directives: PRED, SUCC and NAME. The NAME directive labels a worksharing, and this label can be used by PRED and SUCC directives to specify synchronization. Another approach using annotated C is Cell Superscalar (CellSs) (16), which uses a task directive to express what are the inputs and outputs at a function level. Each time the function is called, a new task is created and the runtime system takes care of the possible dependencies it may have with other tasks.

StarPU features a stream-oriented model of computation, but focuses on the dynamic sheduling aspects and does not involve any language extension <sup>(17)</sup>. Based on multi-versioned kernels, it automates the dynamic balancing and mapping of tasks and data over

heterogeneous, accelerator-centric parallel architectures. It would be an interesting target for GCC and the ACOTES runtime system.

StreamRoller <sup>(6)</sup> is a stream compiler for the Cell Broadband Engine, which uses the SGMS algorithm to split stateless kernels, partition the graph, and schedule it statically. Task fission and fusion are translated into an Integer Linear Programming (ILP) problem, which is solved using the commercial CPLEX solver <sup>(18)</sup>.

Gedae is a proprietary graphical programming environment for streaming signal processing applications in the defense industry. Unlike ACOTES, the developer specifies the mapping of the program onto the target, and the compiler generates the executable according to this mapping  $^{(19)}$ .

We selected GNU Radio as our motivating example <sup>(1)</sup>. It is a framework developed in C++ and Python. GNU Radio allows to express graphs of filters and connections described using Python. Filters are usually constructed as C++ classes. GNU Radio comes with its own task scheduler and the system can be deployed on multiple architectures, including even FPGAs. GNU Radio provides more than 100 different basic blocks that can be combined to achieve the goal of the application. New blocks may be added to add new functionality. Both StreamIt and GNU Radio are designed for signal processing applications, and require the program to be written specifically in terms of streaming blocks.

#### 3. ASM

The Abstract Streaming Machine <sup>(20,21)</sup> is the compiler's description of the target multiprocessor system. The ASM defines the search space for the compiler's partitioning and allocation algorithm by specifying the system topology and performance characteristics, and providing constraints on the mapping such as allowed memory sizes.

We have implemented the ASM in a coarse-grain simulator, which estimates the performance of a candidate mapping on the given target without iterative compilation and execution on a real platform. In addition to improving the speed of the compiler, the simulator allowed us to initiate work on the search algorithm before the compiler's transformation infrastructure is complete, and is repeatable because there are no experimental errors.

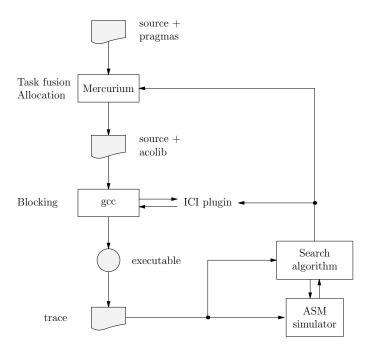

Figure 4 shows the structure of the ACOTES compiler, including the ASM simulator. The compilation flow is iterative: a heuristic search determines a candidate mapping which is compiled using Mer-

Fig. 4. The feedback loop of the ACOTES compiler: a heuristic search algorithm controls Mercurium and GCC.

curium <sup>(3)</sup> and GCC. The mapping is provided to GCC through a plugin using the Interactive Compilation Interface (ICI) <sup>(22)</sup>.

#### 3.1. The ASM machine model

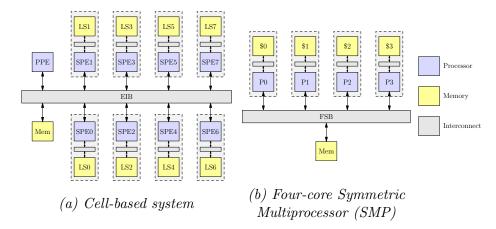

The topology of the target platform is given by an unstructured bipartite graph H=(V,E) where  $V=P\cup M\cup I$  is the set of vertices, a disjoint union of processors, P, and memories, M, in one partition and interconnects, I, in the other. The edges, E, serve only to define the topology. Figure 5 shows two example targets: (a) a Cell Broadband Engine, and (b) a four-core shared memory machine. Each processor, interconnect, and memory is defined using the parameters summarized in Figures 6, 7 and 8, described in detail below. Figure 6 and 7 give the machine descriptions for the example targets, measured on Cell and estimated for a 4-processor SMP. The ASM defines the machine characteristics that are visible to software, including the ACOlib runtime, so it may not exactly match the underlying physical hardware. For example, the Operating System in a

Fig. 5. Topology of two example targets for the ASM

Playstation 3<sup>TM</sup>makes only six SPEs available to software, and the mapping from virtual to physical core is not known. We assume that any processors available to the stream program will not be timeshared with other applications while the stream program is running.

Each processor is defined using the parameters in Figure 6. The ASM supplements the back-end compiler machine description: the details of the processor ISA and micro-architecture are not duplicated in the ASM. The addressSpace and hasIO parameters provide constraints on valid mappings. The former defines the local address space of the processor, i.e., which memories are directly accessible through ordinary load-store instructions, and where they appear in virtual memory; it is used to place stream buffers. The latter defines which processors can perform system IO, and is a simple way to ensure that tasks needing system IO are mapped to appropriate processors.

Each memory is defined using the parameters in Figure 7. The latency and bandwidth figures may be used by the compiler to refine the estimate of the execution time of each task. The memory sizes are used to determine where to place communications buffers, and provide constraints on loop blocking factors.

Each interconnect is defined using the parameters shown in Figure 8. The graph topology is given by the elements parameter, which lists the processors and memories that are adjacent to the bus. Each interconnect is modelled as a bus with multiple channels, which has been shown to be a good approximation of the performance observed

| Parameter         | Type      | Description                       | Cell        | SMP         |

|-------------------|-----------|-----------------------------------|-------------|-------------|

| name              | String    | Unique name in platform names-    | 'SPEn'      | 'CPUn'      |

|                   |           | pace                              |             |             |

| clockRate         | Fixed pt. | Clock rate, in GHz                | 3.2         | 2.4         |

| hasIO             | Bool      | True if the processor can per-    | False       | True        |

|                   |           | form IO                           |             |             |

| addressSpace      | List      | List of the physical memories in  | [('LSn',0)] | [('Mem',0)] |

|                   |           | the system that are addressable   |             |             |

|                   |           | by this processor and their vir-  |             |             |

|                   |           | tual address                      |             |             |

| pushAcqCost       | Int       | Cost, in cycles, of acquiring a   | 448         | 20          |

|                   |           | producer buffer (before waiting)  |             |             |

| pushSendFixedCost | Int       | Fixed cost, in cycles, of pushing | 1104        | 50          |

|                   |           | a block (before waiting)          |             |             |

| pushSendUnit      | Int       | Number of bytes per push trans-   | 16384       | 0           |

|                   |           | fer unit                          |             |             |

| pushSendUnitCost  | Int       | Incremental cost, in cycles, to   | 352         | 0           |

|                   |           | push pushUnit bytes               |             |             |

| popAcqFixedCost   | Int       | Fixed cost, in cycles, of popping | 317         | 50          |

|                   |           | a block (before waiting)          |             |             |

| popAcqUnit        | Int       | Number of bytes per pop trans-    | 16384       | 0           |

|                   |           | fer unit                          |             |             |

| popAcqUnitCost    | Int       | Incremental cost, in cycles, to   | 0           | 0           |

|                   |           | pop popUnit bytes                 |             |             |

| popDiscCost       | Int       | Cost, in cycles, of discarding a  | 189         | 20          |

|                   |           | consumer buffer (before waiting)  |             |             |

Fig. 6. Definition of a processor

| Parameter | Type      | Description                       | Cell   | SMP        |

|-----------|-----------|-----------------------------------|--------|------------|

| name      | String    | Unique name in platform namespace | 'LSn'  | 'Mem'      |

| size      | Int       | Size, in bytes                    | 262144 | 2147483648 |

| clockRate | Fixed pt. | Clock rate, in GHz                | 3.2    | 0.4        |

| latency   | Int       | Access latency, in cycles         | 2      | 4          |

| bandwidth | Int       | Bandwidth, in bytes/cycle         | 128    | 8          |

Fig. 7. Definition of a memory

in practice when the processors and memories on a single link are equidistant <sup>(23)</sup>. Each bus has a single unbounded queue to hold the messages ready to be transmitted, and one or more channels on which to transmit them. Streams are statically allocated onto buses, but the choice of channel is made at runtime. The <code>interfaceDuplex</code> parameter defines for each processor or memory whether it can simultaneously read and write on different channels. The bandwidth

| Parameter        | Type      | Description                        | Cell        | SMP          |

|------------------|-----------|------------------------------------|-------------|--------------|

| name             | String    | Unique name in platform            | 'EIB'       | 'FSB'        |

|                  |           | namespace                          |             |              |

| clockRate        | Fixed pt. | Clock rate, in GHz                 | 1.6         | 0.4          |

| elements         | [String]  | List of names of the elements      | ['PPE',     | ['CPUO',     |

|                  |           | (processors and memories) on       | 'SPEO',,    | , 'CPU3']    |

|                  |           | the bus                            | 'SPE7']     |              |

| interfaceDuplex  | [Bool]    | If the bus has more than one       | [True, ···, | [False, ···, |

|                  |           | channel, then define for each      | True]       | False]       |

|                  |           | processor whether it can trans-    |             |              |

|                  |           | mit and receive simultaneously     |             |              |

|                  |           | on different channels              |             |              |

| interfaceRouting | [Enum]    | Define the routing type for        | [None, ···, | [None,,      |

|                  |           | each processor: storeAndFor-       | None]       | None]        |

|                  |           | ward, cutThrough, or None          |             |              |

| startLatency     | Int       | Start latency, $L$ cycles          | 80          | 0            |

| startCost        | Int       | Start cost of the channel, $S$ cy- | 0           | 0            |

|                  |           | cles                               |             |              |

| bandwidthPerCh   | Int       | Bandwidth per channel, $B$         | 16          | 16           |

|                  |           | bytes/cycle                        |             |              |

| finishCost       | Int       | Finish cost, $F$ cycles            | 0           | 0            |

| numChannels      | Int       | Number of channels on the bus      | 3           | 1            |

| multiplexable    | Int       | False for a hardware FIFO          | True        | True         |

|                  |           | that supports only one stream      |             |              |

Fig. 8. Definition of an interconnect

and latency of each channel is controlled using four parameters: the start latency (L), start cost (S), bandwidth (B) and finish cost (F). The latency of transferring a message of size n bytes is given by  $L+S+\lceil\frac{n}{B}\rceil$  and the cost incurred on the link is  $S+\lceil\frac{n}{B}\rceil+F$ . This is a natural model for distributed memory machines, and is equivalent to the assumption of cache-to-cache transfers on shared memory machines.

The ASM simulator assumes that the only significant traffic on an interconnect is the transfer of messages related to streams. Hence each processor should have some private memory — either a local store or a cache. If it is a local store, the compiler must allocate the stream buffers in this local store <sup>(24)</sup>. If it is a cache, the ASM assumes that it is sufficiently effective so that the cache miss traffic on the interconnect is low.

Hardware routing is controlled using the interfaceRouting parameter, which defines for each processor whether it can route messages from this interconnect onto another interconnect that it is ad-

jacent to. Each entry can take the value storeAndForward (receive a complete message and check its integrity before forwarding it down the route), cutThrough (start forwarding a message before it is complete, increases throughput at the expenses of reliability), or None (no routing capability).

# 3.2. The ASM program model in the simulator

The coarse-grain simulator models the stream program as a directed graph G = (T, S) where T is the set of vertices representing tasks and S is the set of edges representing streams. The graph does not have to be acyclic, but it must be connected (simulation of a single streaming application).

Note that a task may have irregular data-dependent behaviour. We therefore divide tasks into *subtasks*, which are the basic unit of sequencing. A subtask pops a fixed number of elements from each input stream and pushes a fixed number of elements into each output stream. In detail, the work function for a subtask is divided into three consecutive phases: first, the acquire phase calls Iport\_acquire or Oport\_acquire for each stream to obtain the next set of full input buffers and empty output buffers. Second, the processing phase works locally on these buffers, and is modelled using a fixed or normally-distributed processing time. Finally, the release phase calls Iport\_pop to discard the input buffers, and calls Oport\_push to send the output buffers, releasing the buffers in the same order they were acquired. This three-stage model is not a fundamental requirement of the ASM, and was introduced as a convenience in the implementation of the simulator; the ACOTES compiler generates subtasks of this form.

Streams are defined by the size of each element, the location and the length of the distinct producer and consumer buffers (distributed memory) or the single shared buffer (shared memory). These buffers do not have to be the same length. Streams are point-to-point, so each stream has exactly one producer task and one consumer task, but those tasks may access the same stream from more than one subtask (precise semantics and examples will be presented in the next section).

#### 3.3. Definition and sequencing of irregular tasks

The coarse-grain simulator uses the sequential semantics of the SPM program to control the sequencing of subtasks in the stream program. A task is controlled by its *subtask tree*, which is built up from

subtasks, If nodes and While nodes. Each If or While node is associated with a similar statement in the sequential program.

When the simulator executes in the trace-driven mode, the executable is instrumented to record the outcome each time a control statement is executed. A control statement is an if or while statement in the original SPM program that controls one or more subtask trees. The resulting sequence of outcomes is known as a control variable, and takes the values 1 or 0 for an if statement, or the nonnegative iteration count for a while statement. When the simulator is used in the trace-driven mode, the program model is driven by the set of control variables taken from the trace.

The set of control variables may be reused with a different partition or allocation. It usually cannot be reused with a different blocking factor, or after compiler transformations such as loop interchange or distribution, because of these transformation's impact on branch outcome statistics.

## 4. SPM AND THE FRONT-END COMPILER

The Streaming Programming Model (SPM) designed in the context of the ACOTES project is implemented using extensions to the C language. It consists of a set of *pragmas* extending the serial code semantics. The main requirements of the SPM are: to be easy to learn, easy to use and reuse, and to support task and data parallelism. We think that OpenMP <sup>(12)</sup> can therefore serve as a good basis to develop our SPM: OpenMP can be learned, applied, and tested incrementally, which is convenient for new programmers in the streaming field.

#### 4.1. Elements in the SPM

The SPM adds three basic elements to OpenMP: streaming tasks, streams, and ports. These elements are enclosed into a taskgroup compound abstraction. Applications are represented in SPM as multiple tasks connected via point-to-point data streams. Each task may be viewed as an independent process with all its data being private. Communication and synchronization among tasks happen only via streams. A stream is directed, and we refer to its two end points (ports from now on) from the point of view of the task, so that the producer has an output port to generate data into the stream, and the consumer has an input port to read data from the stream. The two ends are permanently connected together. The consumer task

blocks when it tries to read from an empty input stream, and the producer blocks when it tries to write to a full output stream.

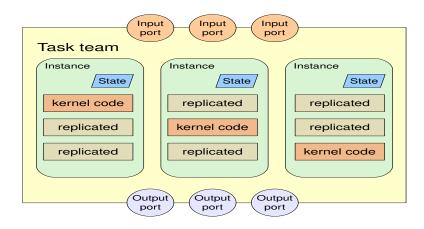

Using the scheme described above, task parallelism is supported in a traditional way with the addition of having communication channels between tasks. Data parallelism is supported through the ability of replicating a task into a number of instances, allowing to run each instance in a different core on disjoint input and/or output data.

There are several distinctions between the execution model of the SPM and that of OpenMP, namely:

- In the SPM, streaming tasks are created all at once when a taskgroup is entered. This is contrary to OpenMP where a thread creates each task in a parallel region upon encountering it dynamically.

- Tasks in SPM are permanent, meaning that they are alive while there is input data for them to process. This implies the automatic generation of an implicit loop: while (there-is-input-data) { ... }, enclosing the code in the body of the task, contrary to what is done in OpenMP. Only when the input streams are known to have no more data, can the task finish. A taskgroup ends when all its tasks have finished.

- Contrary to OpenMP which supports shared data, data accessed by a task must be either private or acquired through an input stream of the task. The SPM defines specific situations where global data can be accessed through a well-defined interface.

#### 4.2. Streaming execution model

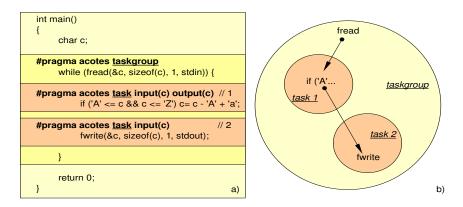

An SPM program start executing serially as a single process. Upon entering a taskgroup, tasks are created and the program starts processing data in streams. Figure 9a shows a simple example, which converts an input stream read from stdin to lower case, and then writes the resulting stream to stdout. Figure 9b shows the scheme of tasks built using the SPM pragmas. As can be observed in the drawing, the taskgroup is used as a container for the annotated tasks. Arrows represent streams along the direction in which data circulates.

Observe that extra clauses are attached to the SPM task pragmas to express data transfers through the streams. The clauses *input* and *output* receive one variable for each input and output stream that should be established, respectively. A task can receive input

Fig. 9. Example program (a), and representation of tasks (b)

data either from its taskgroup or from a previous task having the same variable designated as output. A task can send output data either to a subsequent task having the same variable designated as input, or to its taskgroup. This way, the taskgroup itself serves as an environment, used when there is no previous or subsequent task having the corresponding variable as output or input.

The SPM also supports the exploitation of data parallelism. In the streaming context, this implies processing chunks of data taken from streams in parallel. This is accomplished by replicating an SPM task into multiple instances (collectively called a team), where each instance processes a distinct set of input data chunks. Figure 10 depicts the execution of a team consisting of three instances. Tasks can have many inputs and many outputs. When splitting a task into a team of instances, each input stream can be split so that data chunks are distributed among the instances, or it can be replicated so that all instances will receive all data chunks. The team contribute to the output streams as a single task, where each output chunk is generated by a single instance at every task iteration. The runtime system implements this intertwined contribution by keeping track of which instance is the leader at every iteration. See in Figure 10 how the complete kernel code (updating state and contributing output) is executed by a single instance at a time, while the code needed only for updating the state of each instance is executed in a replicated wav.

Fig. 10. Representation of a team of tasks

# 4.3. Front-end compiler and runtime library (ACOlib)

The transformations outlined above are implemented in the *Mercurium C Compiler* <sup>(3,21)</sup>, which is a source-to-source compiler, generating C code. We use Mercurium to translate the full set of SPM pragmas and clauses into calls to a runtime library which supports task and stream management. The resulting C output is then compiled with GCC, and linked with the runtime library to obtain the final binary file.

The initial approach for a runtime system in the ACOTES project was to implement a simple library (ACOlib) supporting the functionality needed for tasking and streams. We developed an implementation of ACOlib for generic SMP environments, but designed it in such a way that the library could also work with possibly distributed memory architectures and local stores.

ACOlib supports streaming execution in SMP environments, as shown in Figure 11a which depicts a snippet of the code generated for the taskgroup example presented in Figure 9a. Observe how two tasks are initialized, their ports created and connected, and then they are started. The two tasks are alive while the taskgroup reads characters from the file and sends them to  $Task\ 1$ . Figure 11b shows the code resulting from the transformation of  $Task\ 1$  of the same example. This task reads characters from its input port, processes

them, and writes the result onto its output port. The task will remain alive as long as there are characters available in its input stream.

```

void task1_outline(task_t __task)

task t task1:

task_init(&task1, task1_outline, 0)

task t task2:

trace_instance_begin();

task init(&task2 task2 outline 0):

char c;

iport_acquire(0, 1);

task_oport(task0, 0, sizeof(char), 1, 1);

oport_acquire(1, 1);

task iport(task1, 0, sizeof(char), 1, 0 + 1, (void *) 0, 0);

while (task_allopen())

task oport(task1, 1, sizeof(char), 1, 1);

task_iport(task2, 0, sizeof(char), 1, 0 + 1, (void *) 0, 0);

memcpy(&c, iport_peek(0), sizeof (char));

port_connect(task1, 1, task2, 0);

if ('A' <= c && c <= 'Z')

port connect(task0, 0, task1, 0):

c = c - 'A' + 'a':

task_start(task1);

memcpy(oport_peek(1), &c, sizeof(char));

task_start(task2);

while (fread(&c, sizeof (c), 1, stdin)) {

iport pop(0, 1):

oport_acquire(0, 1);

memcpy(oport_peek(0), &c, sizeof(char));

oport push(1, 1);

iport_acquire(0, 1):

oport_push(0, 1);

oport_acquire(1, 1);

task_wait(task2);

task close():

task wait(task1):

b) Task 1

a) Taskgroup

```

Fig. 11. Code generated from the taskgroup example

## 4.4. Integration in OpenMP and GCC

Inspired by the full set of SPM pragmas and their support by Mercurium and ACOlib, we also developed a reduced version especially designed as a minimal extension <sup>(9)</sup> of the OpenMP3.0 standard <sup>(12)</sup>. This approach leverages the knowledge of OpenMP thereby improving the learning curve while preserving, to a certain extent, the semantic of the SPM pragmas. The additional compiler support required by this extension is implemented directly in GCC and its runtime library libGOMP.

In order to provide stream programming support in OpenMP, the minimal necessary extension is to allow the use of lastprivate clauses on task constructs, without changing the existing semantic of the lastprivate clause. The semantic of firstprivate and lastprivate clauses is very close to SPM's input and output clauses. The firstprivate clause corresponds to data that is consumed by the task (flows in), while the lastprivate clause corresponds to data that is produced by the task (flows out). The explicit knowledge about data flow between tasks helps the compiler's static analysis and facilitates generating stream communication between tasks.

To illustrate the OpenMP extension as well as the similarity of this approach with the SPM, we propose in Figure 12 an implementation of the example code of Figure 9a using OpenMP3.0 extended annotations. We implemented this support for streams in GCC's lib-

Fig. 12. Implementation of the example of Figure 9a using OpenMP extended annotations.

GOMP runtime library  $^{(25)}$ , which also simplifies the toolchain by removing the dependence on the source to source *Mercurium C Compiler*.

#### 4.5. MSF: Multicore Streaming Framework

The ACOlib runtime library developed to support tasks and streams was implemented for generic SMP environments, i.e. with shared memory. In order to apply our streaming framework to distributed memory architectures such as that of the Cell/B.E., we are making use of an underlying Multicore Streaming Framework (MSF). On one hand, MSF provides efficient support for code management, as the code that the tasks execute is preloaded in advance of its execution. And on the other hand, it provides efficient support for data transfers between tasks, which may be running on the same or on different processors, as well as with shared or distributed memory.

The abstraction layer implementing such data transfers resembles that of ACOlib, offering stream-based communication.

The use of MSF in ACOTES augments the general tool-chain of ACOTES which starts with Mercurium translating SPM pragmas into ACOlib calls. Instead, for the Cell/B.E., it makes direct use of MSF facilities for setting up tasks in remote processors and establishing stream communications among them. Furthermore, MSF also provides the runtime management and scheduling of task executions according to available data in the heterogenous and distributed environment of the Cell/B.E.

MSF provides a generic programming model for parallel platforms and an API for programming directly using its facilities. Although its first implementation is on the Cell/B.E., MSF can be implemented on any programmable platform. Tasks can be directed to various processors based on their processing characteristics. On the Cell/B.E the target processors are either PPEs or SPEs. The tasks are then compiled by a back-end compiler that deals with standard sequential code, and vectorization can be applied to achieve better performance on the target processor. Once available on a specific platform the same front-end compilation techniques can be performed independently of the underlined architecture. Using the information provided by the ASM, applications can be optimized for each platform by changing runtime parameters that are used by MSF.

# 4.6. Silicon Hive's ISO-C Language Extensions, underpinning SPM

Silicon Hive, one of the ACOTES partners, had already developed and used an in-house C-compiler (HiveCC) prior to the project. In the course of the project, Silicon Hive adapted HiveCC to the developing insights of the project, providing feedback to the other partners. By using the blocking communication ports of ACOTES, we realized that synchronization (i.e. the blocking behaviour) and data communication should take place at different granularities. This allows the compiler to expose parallelism between communication and computation. This resulted in ISO-C language extensions for synchronisation, as discussed below. We illustrate these synchronisation mechanisms in the context of the Gamma correction algorithm (introduced in Section 1.1). In this context, we also make use of other language extensions, such as: attributes, built-in types, function inlining, operator overloading, and register structures, as illustrated in Figure 13 (for reference, the unoptimized version, which is used as an input to the ACOTES auto-vectorizer is shown in Figure 19).

```

HIVE_TERNARY_OPERATOR( ?, OP_vec_mux

, tvec, tflags, tvec, tvec)

HIVE_BINARY_OPERATOR ( >>, OP_vec_asrrnd

, tvec, tvec, tvec )

( >, static inline, isp_vec_gt_c

HIVE_BINARY_CALL

, tflags, tvec, int )

#define LINESZV LINESZ/VECSZ

SYNC_WITH(0) tvec MEM(VMEM) inBuf[2*LINESZV];

SYNC_WITH(1) tvec MEM(VMEM) outBuf[2*LINESZV];

// Initialize correction coefficients:

int ta[SN]=\{...\}, oa[SN]=\{...\}, ga[SN]=\{...\};

// double buffering; pre-fetch & sync with buf 1:

signal_inputFormatter() SYNC(0);

for( line=0; line<LINES_PER_FRAME; line++ ) {</pre>

int buf=line&1; // determine buffer

// double buffering; pre-fetch next line:

signal_inputFormatter() SYNC(0);

\ensuremath{//} double buffering; wait for current line:

wait_inputFormatter() SYNC(0);

for( c=0; c<LINESZV; c++ ) {</pre>

tvec x = inBuf[buf*LINESZV+c];

int t=thrh[0], o=offs[0], g=grad[0];

for( i=0; i<SN-1; i++ ) {</pre>

tflags flag = x>ta[i]; // overloaded '>'

// overloaded vector '?' operator:

o = flag ? o : OP_vec_clone(oa[i+1]);

g = flag ? g : OP_vec_clone(ga[i+1]);

t = flag ? t : OP_vec_clone(ta[i+1]);

pragma hivecc unroll

// overloaded vector '>>' operator:

outBuf[buf*LINESZV+c] = o+(x-t)*g>>SCALE;

pragma hivecc unroll=6, pipelining=0

// Signal output buffer full, sync with output buf.

signal_DMA() SYNC(1);

// Wait until DMA finished previous line.

if(line) wait_DMA() SYNC(1);

```

Fig. 13. Gamma-correction kernel optimized with Silicon-Hive's SPM

HiveCC supports several pragmas by which the programmer can steer the compiler to reveal parallelism. HiveCC also provides builtin preprocessor definitions which enable the programmer to develop code independent of the underlying system architecture.

Taken together, these language extensions are needed to efficiently implement SPM on Silicon Hive processors.

Type attributes specify aspects of variables such as location, access routes, and synchronization with volatile operations. Expression attributes allow the user to specify the relative timing of associated statements, aliasing relations between variables, and the mapping of code on specific function units. MEM and SYNC\_WITH in Figure 13 are example for such attributes. These define input/output as mapped on a specific memory and with which side-effect statements their accesses need to be synchronized.

Built-in Types allow HiveCC to generate non-ISO-C operations on non-ISO-C types. These types result from processors being defined with datapaths of arbitrary width (i.e. not restricted to the widths of ISO-C datatypes). The additional types are available as signed or unsigned integers of processor-defined width and vectors with processor-defined numbers of elements and element widths. If the associated operators have been overloaded (see below), these types may be used in arithmetic expressions. In the optimized Gamma correction algorithm in Figure 13, pixel colour components are mapped onto the vector type tvec. In the case of ISP2300 this is a vector of 32 elements, each element being 16 bits wide.

Custom Operations can be called as intrinsic functions, which is needed when the overloading mechanism cannot distinguish operations based on signature alone. In fact, all operations defined on Silicon Hive processors may be called as intrinsic functions. Besides intrinsics for regular and custom operations, HiveCC also provides a number of Pseudo Operations. These operations are interpreted by the simulator, which provides cycle counts and more.

Operator Overloading allows the programmer to assign normal operator symbols to functions, including intrinsic functions for specific processor operators. HiveCC supports overloading of unary, binary, ternary, and assignment signatures. The optimized Gamma correction code provides three examples of overloading (see Figure 13). By applying overloading to inline functions, the programmer can develop machine-independent code without loss of performance. This is illustrated in the following code example:

inline static tvec fmux(tvec c,tvec t,tvec e) {

```

# if HAS_mux

return( OP_mux(c,t,e) );

# else

return c?t:e;

}

HIVE_TERNARY_CALL(?,static,fmux,tvec,tvec,tvec)

```

Register Structures are an extension to the ISO-C register qualifier. By adding this qualifier to a newly defined type, the programmer indicates that all elements of the type are to be mapped onto registers.

In addition to the direct mapping of tasks to hardware synchronizations and communications, HiveCC revisits the SPM for the static interleaving of tasks. In a very wide VLIW context, multiple tasks may be statically scheduled and parallelized over multiple issue slots, converting task-level parallelism into instruction-level parallelism. Unlike the dynamic scheduling of a conventional task pipeline, load balancing and communication/computation overlapping needs to be performed statically by the compiler. A specific syntax is introduced to let the programmer expose such opportunities, and to fine-tune register pressure and resource usage. Inspired by these challenges, the ACOTES project also developed related techniques to optimize code size of nested software pipelined loops vs. memory usage and register pressure <sup>(26)</sup>.

In conclusion, the new synchronisation mechanism is needed to allow data to be communicated at pixel granularity, while synchronisation takes place at line granularity (for instance). This way, rather than keeping all volatile loads and stores together, the programmer is free to communicate data when it becomes available (streaming) and the compiler is free to schedule the resulting loads and stores within the constraints imposed by the synchronisation mechanism, exposing maximal parallelism.

Notice that other type attributes and built-in types are needed in this context, because they allow the compiler to reason about the many different non-ISO-C datatypes that embedded processors may support. Lastly, the overloading mechanism supports the programmer in reasoning about his code, which is particularly important when communication and computation need to be alternated.

#### 5. COMPILER MIDDLE-END AND LOOP-LEVEL OPTIMIZATIONS

Through the SPM, the programmer exposes much of the pipeline and data parallelism in stream computations. Recall that the goal of the ACOTES project is to minimize the burden of manually adapting a stream computing program to a new architecture. This adaptation is partly managed by the runtime system for the SPM, and partly by the compiler middle-end. Program transformations are indeed necessary to adjust the synchronization grain, and to tune the exploitation of the architecture's memory hierarchy w.r.t. the temporal and spatial locality of the streaming program. One typically splits such transformations into task-level and loop-level optimizations. Both address parallelism, locality and specialization, but generally at different levels (the levels of the memory hierarchy and the levels of parallelism in the target). In the following, we focus on loop-level optimizations, although our design is extensible to task-level optimizations such as static task pipelining, fusion and blocking (5). Such an extension requires an adequate intermediate representation of the task-level data flow; this work is still in progress, based on Feautrier's proposal to extend the polyhedral representation to the full network of tasks (8). We will conclude this section with the study of some tradeoffs between the exploitation of thread-level parallelism, fine-grain SIMD parallelism (e.g., vectors) and memory locality. Those tradeoffs are particularly important when optimizing a streaming application for multiple levels of parallelism, and considering power efficiency and compute density metrics.

#### 5.1. Loop-Nest Optimizations

Loop nest optimizations are important compiler transformations to fully exploit the features of a given architecture. Current compiler techniques using syntax-based representations and hard-wired pattern matching techniques are not able to provide peak performance on complex architectures with multiple on-chip processing units.

In order to enable long and complex sequences of program transformations, we rely on a powerful algebraic program representation called the *polyhedral model*, where a sequence of transformations is represented as a single affine mapping function.

In scientific and engineering applications, most of the execution time is spent in nested loops. The *polyhedral model* views a dynamic instance (iteration) of each program statement as an integer point

in a well defined subspace called *polyhedron*. Basing on this representation a dependence graph is built, which represents dependences among pairs of statement execution instances (iterations in loops).

The polyhedral model is classically applicable to *static control parts* (SCoP), that is loop nests in which the data access functions and loop bounds are affine combinations of enclosing loop iteration variables and *global parameters*.

# Polyhedral representation of programs

Each dynamic instance of a statement S is denoted by a pair  $(S, \mathbf{i})$ , where  $\mathbf{i}$  is iteration vector which contains values for the loop indices of the enclosing loops, from outermost to innermost. If loop bounds are affine expressions of outer loop indices and global parameters (usually, symbolic constants representing problem size) then the set of all iteration vectors associated with statement S can be represented by polytope  $\mathcal{D}_S$  which is called the *iteration domain* of statement S. Let  $\mathbf{g}$  be the vector of global parameters (a.k.a. structural parameters). Let  $\mathbf{D}_S$  denote the matrix collecting affine loop bound constraints, the iteration domain set  $\mathcal{D}_S$  is defined by

$$\mathcal{D}_S = \left\{ \mathbf{i} \mid D_S \times \left( \mathbf{i} | \mathbf{g} | 1 \right)^t \ge \mathbf{0} \right\}$$

#### Polyhedral dependences

Dependences in a SCoP are represented as a Dependence Graph (DG). DG is directed multigraph DG = (V, E) where each vertex represent a statement and each edge  $e^{S_i \to S_j} \in E$  from  $S_i$  to  $S_j$  represents a dependence polyhedron from dynamic instance of  $S_i$  to dynamic instance of  $S_j$ . The dependence polyhedron is a subset of the cartesian product of iteration domains  $\mathcal{D}_{S_i}$  and  $\mathcal{D}_{S_j}$ . Dependence polyhedron for edge e is denoted as  $\mathcal{P}_e$ .

#### Access functions

For each statement S, we define two sets  $\mathcal{W}_S$  and  $\mathcal{R}_S$  of (M, f) pairs, each pair representing a reference to variable M being written or read in statement S; f is the access function mapping iterations in  $\mathcal{D}_S$  to memory locations in M. f is a function of loop iterators and global parameters. The access function f is defined by a matrix F such that

$$f(\mathbf{i}) = \mathbf{F} \times (\mathbf{i}|\mathbf{g}|1)^t$$

.

Subscript function returns a vector whose dimensionality is equal to the dimensionality of an array M.

# Scheduling function

Iteration domains define exactly the set of executed dynamic instances for each statement. However, this algebraic structure does not describe the order in which each statement instance has to be executed with respect to other statement instances (10). A convenient way to express the execution order for each statement instance is to give each instance an execution date. It is obviously impractical to define all dates explicitly because the number of instances may be either very large or unknown at compile time. An appropriate solution is to define, for each statement S, a scheduling function  $\theta_S$  mapping instances of S to multidimensional timestamps (vectors). For tractability reasons, we restrict these functions to be affine, and we will use matrix operations on homogeneous coordinates (additional dimension equal to the constant 1) to represent affine functions. For the sake of transformation composition or search space exploration  $^{(27)}$ ,  $\theta_S$  is often broken into dedicated blocks: a matrix  $A^S$  operating on iteration vectors, a vector  $\beta^S$  for static (multidimensional) statement ordering, and a matrix  $\Gamma^S$  to parameterize the schedule and to model pipelining:

$$\Theta_{S} = \begin{bmatrix} 0 & \cdots & 0 & 0 & \cdots & 0 & \beta_{0}^{S} \\ A_{1,1}^{S} & \cdots & A_{1,d^{S}}^{S} & \Gamma_{1,1}^{S} & \cdots & \Gamma_{1,d_{\mathbf{g}}}^{S} & 0 \\ 0 & \cdots & 0 & 0 & \cdots & 0 & \beta_{1}^{S} \\ A_{2,1}^{S} & \cdots & A_{2,d^{S}}^{S} & \Gamma_{2,1}^{S} & \cdots & \Gamma_{2,d_{\mathbf{g}}}^{S} & 0 \\ \vdots & \ddots & \vdots & \vdots & \ddots & \vdots & \vdots \\ A_{d^{S},1}^{S} & \cdots & A_{d^{S},d^{S}}^{S} & \Gamma_{d^{S},1}^{S} & \cdots & \Gamma_{d^{S},d_{\mathbf{g}}}^{S} & 0 \\ 0 & \cdots & 0 & 0 & \cdots & 0 & \beta_{d^{S}}^{S} \end{bmatrix}$$

$$heta_S(\mathbf{i}_S) = \Theta_S imes egin{pmatrix} \mathbf{i}_S \\ \mathbf{g} \\ 1 \end{pmatrix}$$

As an example we will consider the pseudocode in Figure 18a. The loop kernel is composed of three statements:  $S_1$ ,  $S_2$  and  $S_3$ . The iteration domains for statements  $S_1$  and  $S_2$  are the following:

$$D^{S_1} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ -1 & 1 & 0 & -1 \end{bmatrix} \begin{array}{c} 0 \le i \\ i \le M - 1 \end{bmatrix}$$

$$D^{S_2} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ -1 & 0 & 1 & 0 & -1 \\ 0 & 1 & 0 & 0 & 0 \\ 0 & -1 & 0 & 1 & -1 \end{bmatrix} \begin{array}{c} 0 \le i \\ i \le M - 1 \\ 0 \le j \\ j \le K - 1 \end{array}$$

(domain of  $S_3$  is the same as that of  $S_2$ ). Domain of statement  $S_1$  has single iterator dimension (corresponding to iteration variable i), and two parameter dimensions (corresponding to M and K. Domain of statement  $S_2$  has two iterator dimensions (corresponding to iteration variables i and j). There are no array data access function for statement  $S_1$  because it does not access any array. Data access functions for statement  $S_2$  are the following:

$$\mathcal{W}^{S_2} = \left\{ \right\}$$

$$\mathcal{R}^{S_2} = \left\{ \begin{pmatrix} \|x\|, [1\ 1|0\ 0|0] \end{pmatrix}, \begin{cases} x[i+j] \\ (\|c\|, [0\ 1|0\ 0|0] \end{pmatrix}, \end{cases} c[j]$$

There are no write accesses in statement  $S_2$ , while there are two read data accesses: one from array  $\mathbf{x}$  and other from array  $\mathbf{c}$ . Original(corresponding to original input code) scheduling functions for statement  $S_1$  and  $S_2$  are given:

$$A^{S_{2}} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}$$

$$A^{S_{1}} = \begin{bmatrix} 1 \end{bmatrix} \qquad \beta^{S_{2}} = \begin{bmatrix} 0 & 1 & 0 \end{bmatrix}^{t}$$

$$\beta^{S_{1}} = \begin{bmatrix} 0 & 0 \end{bmatrix}^{t}$$

$$\Gamma^{S_{1}} = \begin{bmatrix} 0 & 0 \end{bmatrix}$$

i.e.  $\Theta^{S_{1}} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ 0 & 0 & 0 \end{bmatrix}$

i.e.  $\Theta^{S_{2}} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 0 \end{bmatrix}$

note that  $\Gamma^{S_1}$  and  $\Gamma^{S_2}$  are all zeros, since the schedule does not depend on global parameters.  $A^{S_1}$  and  $A^{S_2}$  are identity matrices.

Program optimization in polyhedral model is usually done in three steps: (1) static analysis of input program resulting in algebraic representation of static control loop nests and construction of dependence graph, (2) transformations of polyhedral abstraction (based on linear algebra and integer linear programming machinery) without touching syntax representation of original program (3) code generation (going back into syntax representation). Note that step (3) is done only once: all transformations (sequences) operate on polyhedral (algebraic) representation.

The following table lists the main loop transformations that we can freely compose and parameterize in our framework; see Allen and Kennedy <sup>(28)</sup> for reference on those transformations and Girbal et al. <sup>(27)</sup> for details on the encoding and composition invariants:

| Transformation name                      | Matrices involved |

|------------------------------------------|-------------------|

| Interchange, skewing (unimodular)        | A                 |

| Strip-mining, tiling                     | $D, \Theta$       |

| Pipelining (multidimensional)            | $\beta$           |

| Parametric pipelining (multidimensional) | Γ                 |

| Reversal (unimodular)                    | Α, Γ              |

| Motion, fusion, fission (distribution)   | $\beta$           |

| Privatization, contraction               | F                 |

Considerable advances in dependence analysis, optimization and parallelization heuristics, and code generation proved that polyhedral model is scalable enough to be used in industrial tools. Yet, the problem of devising the optimal transformation sequences for optimizing locality and enabling parallelism is still a topic of considerable ongoing research efforts.

There are two approaches to optimizing programs using polyhedral model: static analytical modelling and iterative optimization. The former builds an analytical model and tries to statically predict the best possible loop transformation. Iterative optimization takes a feedback-directed approach, building different versions of the input program by applying different optimizations and choosing the one that gives the best performance gains. Those two approaches are complementary: analytical modelling can miss the best optimization opportunity but takes just a one pass to complete. On contrary, iterative optimization might search for the best optimization but the search space might be huge, taking many iterations to complete, a challenge for its adoption in production compilers.

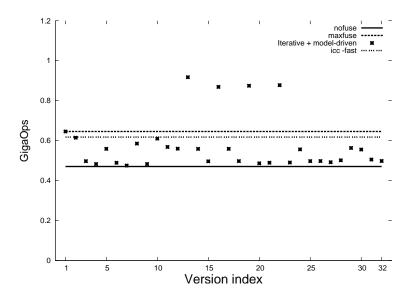

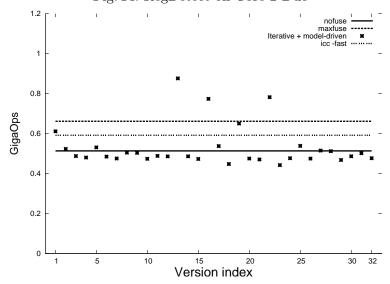

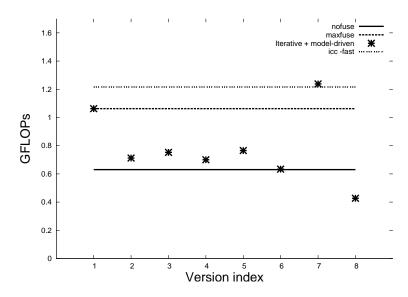

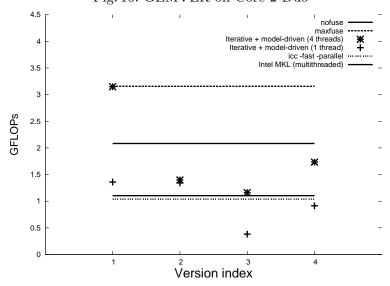

Our approach combines an analytical model and an iterative, feedback-directed approach. We rely on the loop tiling framework of Bondughula et al. <sup>(29)</sup>, and on the associated tool Pluto, to extract blocked/tiled loop nests that exhibit one or more parallel loop levels. This framework includes a heuristic to select the shapes of the tiles, to maximize coarse grain parallelism while minimizing communication. This heuristic happens to behave consistently well on our benchmarks. However, another heuristic is proposed to deal with the combinatorics of loop fusion/distribution, and this one is not robust enough to achieve good performance on a wide variety of benchmarks and on multiple architectures. We thus replaced the fusion/distribution heuristic with an iterative search approach, building a search space of feasible, unique transformations before looking for a proper tiling scheme with Bondughula's heuristic. The iterative search is adapted from the more general technique of Pouchet et al. (10), with new invariants enabling to focus the search space on more relevant transformations (for the practicality of the iterative search). Our results on 2 UTDSP and 2 BLAS2 benchmark are reported in Figures 14, 15, 16, 17, considering two different quadcore general-purpose processors, Intel Core 2 Duo Q6600 and AMD Phenom 9850. Those results demonstrate (1) the potential of our loop-nest optimizer compared to the state-of-the-art (Intel's compiler), and (2) the wide performance differences among the different transformation sequences explored by the iterative search method.

#### 5.2. Vectorization

Vectorization is the process of converting scalar source code into code that operates on vectors of data elements, making use of SIMD (vector) instructions. Automatic vectorization by a compiler typically focuses on loops, where occurrences of an instruction across different loop iterations operate on different data elements. It can be seen as a downstream stage of the loop nest optimizer, where the selection of target-dependent instructions and access patterns come into play. Vectorization is known to be one of the most effective ways to exploit fine-grain data-level parallelism, and is especially important for streaming architectures because their processing units typically contain vector (SIMD) units (see Section 7) to take advantage of the abundant data-level parallelism available in streaming applications (see Section 1.1). Vectorization has therefore been identified as one of the key compiler optimizations to be addressed in the project.

Fig. 14. RegDetect on Core 2 Duo

Fig. 15. RegDetect on Phenom

Fig. 16. GEMVER on Core 2 Duo

Fig. 17. Doitgen on Core 2 Duo

The auto-vectorizer available since GCC 4.0 <sup>(30)</sup> is capable of vectorizing inner-most loops with memory references of unit or power-of-two strides, that may or may not be aligned, and that may include multiple data-types and type conversions, reductions, and other special idioms. The two main enhancements that were missing and were identified as important for the streaming domain are a cost-model, and the capability to vectorize outer-loops. One of the most important goals of the cost model, beyond facilitating informed decision making by the vectorizer, was to be part of an interface to exchange data and guidance with the high-level loop optimizer. This is described in detail in Section 5.3. The rest of this section focuses on the in-place outer-loop vectorization capability we developed.

Outer loop vectorization refers to vectorizing a level of a loop nest other than the inner-most, which can be beneficial if the outer loop exhibits greater data-level parallelism and locality than the inner-most loop. Figure 18c shows the result of vectorizing the outer i loop of the loop nest in Figure 18a, assuming Vector Length VL=4 and M divisible by 4. Notice that the innermost j loop continues to advance in steps of 1 (compared to 4 in the case of innermost loop vectorization depicted in Figure 18b), computing 4 results for 4 successive i iterations simultaneously.

```

for (i=0; i<M; i++){for (i=0; i<M; i++){}}

for (vi=0; vi<M; vi+=4){

vs[0:3] = \{0,0,0,0\}

vs[0:3] = \{0,0,0,0\}

for (j=0; j<K; j++){ for (vj=0; vj<K; vj+=4){ for (j=0; j<K; j++){

s += x[i+j] * c[j]

vc = c[vj:vj+3]

vc = {c[j],c[j],c[j],c[j]}

vs[0:3] +=

vs[0:3] +=

x[i+vj:i+vj+3] * vc

x[vi+j:vi+3+j] * vc

S3: y[i] = s

vy[vi:vi+3] = vs[0:3]

(a) Scalar

(b) Inner-loop vectorized

(c) Outer-loop vectorized

```

Fig. 18. FIR-filter Vectorization

Outer-loops may have longer iteration counts, smaller strides, more efficient computation constructs, lower initialization and finalization overheads than those in innermost loops, as well as greater potential for promoting vector register reuse, thereby allowing us to leverage the many vector-registers often available in streaming architectures.

As mentioned above, data-streaming applications are dominated by nested loops of SIMD-like computations. The high-level datareuse carried by the outer-loops in these loop nests can be detected

and exploited only if operating at the level of the outer-loop. For this reason we have implemented an in-place vectorization approach that directly vectorizes the outer-loop  $^{(31-36)}$ , instead of the traditional approach of interchanging an outer-loop with the inner-most loop, followed by vectorizing it at the inner-most position  $^{(28)}$ . The cost model we developed is capable of guiding the compiler which of these two alternatives is expected to be more profitable (as exaplined in the following Section).

Operating directly on the level of the outer-loop allows detecting high-level data reuse opportunities that are carried by the outer-loop. as well as fine grained data reuse opportunities related to the handing of alignment. We developed an optimization tapping such opportunities, incorporated within the outer-loop vectorizer. This optimization detects situations in which the misalignment of a vector load in a nested inner-loop is not invariant in the inner-loop (which happens e.g. if the inner-loop stride S is smaller than the Vector Length (VL)), yet the different misalignments across consecutive inner-loop iterations repeat themselves to form a cyclic group of VL/S distinct misalignments (if S divides VL). This is the case in the example in Figure 18c where S=1 and VL=4. In this case we can achieve fixed misalignment by unrolling the inner-loop by VL/S. Fixed misalignment across iterations can be vectorized much more efficiently, as the misalignment (and in turn, the permutation masks to extract the desired data) can be computed once before the loop (instead of in each iteration). Moreover, each such cyclic group of loads exhibits a high rate of overlap in the data that is being fetched, and can be optimized by removing redundant loads from the unrolled iteration.

Note, however, that such unrolling may result in high register pressure, which on some architectures may result in register spilling, incurring high overhead that masks away the above benefits. For this reason, depending on the required unrolling factor, this optimization may not be suitable for architectures with too few vector registers, but is especially appropriate for streaming architectures, that often include a relatively large number of vector registers (e.g. 128 in the Cell SPE).

We evaluated these techniques on multimedia benchmarks. Our implementation of in-place outer-loop vectorization achieves speedup factors of 2.92x on average across this set of benchmarks, compared to 1.21x achieved by innermost loop vectorization. Outer-loop vectorization provides superior speedups for most benchmarks due to smaller strides and/or larger outer-loop-counts than those in the

inner-loop, and/or by avoiding a reduction-epilog penalty. The optimization for fixed misalignment and data reuse using unrolling is capable of further boosting the performance obtained by outer-loop vectorization, to achieve an average speedup factor of  $4.98 \times$  (for detailed results see  $^{(36)}$ ).

These techniques are also applicable to the main computation kernels in the streaming applications described in Section 1, namely Gamma-correction and H.264 (in FMradio the inner-most loops are the best choice for vectorization).

#### Gamma correction

The complete Gamma-correction algorithm we used for this evaluation is shown in Figure 19. As the reader will notice, the algo-

```

volatile int inBuf[LINESZ]; // global arrays

volatile int outBuf[LINESZ];

// Initialize correction coefficients:

int ta[SN]={...}, oa[SN]={...}, ga[SN]={...};

for( line=0; line<LINES_PER_FRAME; line++ ) {</pre>

signal_inputFormatter(); // Line buffer empty

wait_inputFormatter(); // Processor stalled,

// until line buffer is full.

for( c=0; c<LINESZ; c++ ) {</pre>

int x = inBuf[c];

int t=thrh[0], o=offs[0], g=grad[0];

// Search for correction interval:

for( i=0; i<SN-1; i++ ) {

int flag = x>ta[i];

// Found interval; set pixel coeffs:

o = flag ? o : oa[i+1];

g = flag ? g : ga[i+1];

t = flag ? t : ta[i+1]; }

// Calculate output:

outBuf[c] = o + asrrnd((x-t)*g,SCALE );}

// Line output buffer full; Signal&wait for DMA.

signal_DMA();

wait_DMA(); } // Stalled until DMA is ready.

```

Fig. 19. Gamma-correction algorithm

rithm continues searching after the interval has been found, but will no longer update the three coefficients. Thus, the algorithm is predictable and more amenable to vectorization. Vectorizing the outer-loop that scans over pixels in a row (the c loop), is most effectively

done when the inner-most loop (that searches through the array of thresholds, i loop in the Figure) is completely unrolled (this means that the pixel-loop becomes the inner-most loop in the nest, and so regular inner-loop vectorization can be applied), achieveing an improvement factor of  $1.81 \times /10.15 \times$  over the sequential version on PowerPC970/Cell-SPU respectively. The super-linear speedup on the Cell-SPU (the Vectorization Factor is 4) is due to the heavy penalty for branches on the SPU (which the vectorizer converts into conditional vector operations) and the data-rotate overhead for operating on scalar data in vector registers (which is avoided when the code is vectorized). Outer-loop vectorization can be used if the inner-most loop is not completely unrolled, e.g. if its loop-count is unknown at compile time or too large to completely unroll. In the particular case at hand however the inner-most loop-count (SN-1) is a compile-time known constant 3.

As a point of comparison, we note that these optimizations can be expressed using Silicon Hive's SPM (as described in Section 4.6). A manually optimized implementation of Gamma correction for the ISP2300 is shown in Figure 13. It applies these optimizations (vectorization, loop unrolling) and others (software pipelining with double buffering and explicit synchronization) achieves a 200-fold acceleration, bringing performance up to 0.76 cycles/pixel. Vectorization is expressed using overloaded comparison and conditional operators and by making the pixel loop iterate over vectors of pixels rather than a single pixel, achieving a 30× improvement factor - close to the theoretical speedup factor VF = 32. While the data-level parallelism exploited by the compiler using GCC auto-vectorization is comparable to the one achieved manually using Silicon Hive's SPM, the other optimizations that the latter applies are not yet supported by the ACOTES toolchain. In Gamma-correction these further increase data-level parallelism by a factor of 3 on the ISP2300.

## H.264

The main computation kernel in H.264 consists of two modes: vertical and horizontal. The first mode has a consecutive access-pattern in the inner-most loop, and an outer-loop that scans through different rows. Here only inner-loop vecorization is applicable, and it obtains a  $5.2\times$  to  $7.6\times$  performance improvement on PowerPC970/Cell-SPU respectively. The second mode has a consecutive access-pattern in the outer-loop and a row-size stride in the inner-loop. In-place outer-loop vectorization is applied here and achieves a  $10\times$  to  $11\times$  performance

improvement on PowerPC970/Cell-SPU respectively. The alternative of first interchanging the two loops in the nest and then applying inner-loop vectorization (rather than vectorizing the outer-loop in-place) achieves a speedup of  $6.8\times$  to  $11\times$  on PowerPC970/Cell-SPU. In-place outer-loop vectorization is better on PowerPC970 than the interchange based approach due to improved locality (which the Cell-SPU is less sensitive to as it does not have a cache). Reasoning about such tradeoffs and selecting between these alternatives is the role of the cost-model presented in the next section.

## 5.3. Interaction Between Loop-Nest Optimizations and Vectorization

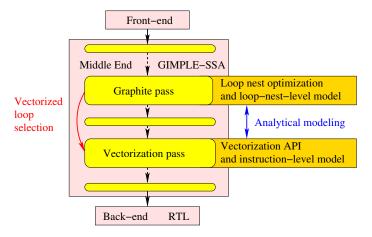

Vectorization involves low-level, target-specific considerations and transformations, which currently exclude it from being part of the polyhedral framework. In this section, we make a first step in this direction, building a performance model for automatic vectorization integrating seamlessly within the polyhedral representation <sup>(37)</sup>. Figure 20 summarizes this integration step in the context of the GCC compilation flow. We address a key adaptation problem when porting a streaming application to a new target architecture; it facilitates educated decision making on how to best apply loop transformations while considering the subsequent effects of vectorization.

Fig. 20. GCC compilation flow

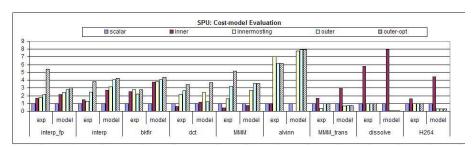

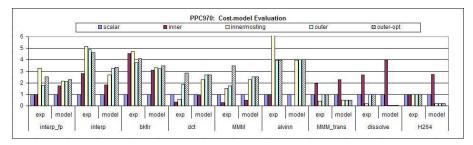

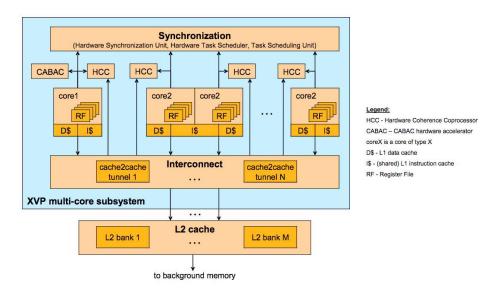

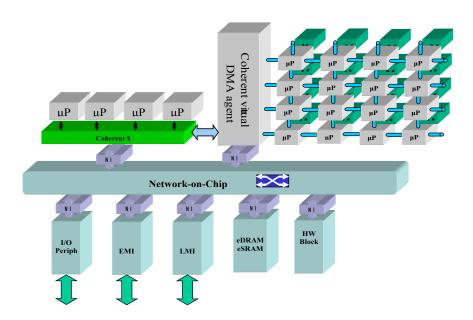

To apply vectorization to a loop-nest profitably, an intelligent decision needs to be made as there are often several alternatives to