## A Software Implementation of ECM for NFS

Alexander Kruppa

#### ▶ To cite this version:

Alexander Kruppa. A Software Implementation of ECM for NFS. [Research Report] RR-7041, INRIA. 2009. inria-00419094

## HAL Id: inria-00419094 https://inria.hal.science/inria-00419094

Submitted on 22 Sep 2009

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

## A Software Implementation of ECM for NFS

Alexander Kruppa

## N° 7041

Septembre 2009

## A Software Implementation of ECM for NFS

#### Alexander Kruppa

Thème : Algorithmique, calcul certifié et cryptographie Équipe-Projet CACAO

Rapport de recherche n° 7041 — Septembre 2009 — 39 pages

**Abstract:** The Elliptic Curve Method (ECM) of factorization can be used in the relation collection phase of the Number Field Sieve (NFS) to help identify smooth integers. This requires rapidly finding small prime factors for a large number of composites, each of a few machine words in size. We present a software implementation of ECM that is optimized for high throughput operation and compare it with recently proposed hardware implementations of ECM.

Key-words: Integer factoring, Elliptic Curves, Number Field Sieve

# Une implémentation d'ECM pour le crible algébrique

**Résumé :** L'algorithme ECM de factorisation d'entier est utilisé dans le crible algébrique (Number Field Sieve, NFS) pour identifier les relations friables. Cela nécessite de trouver rapidement des petits facteurs premiers dans un grand nombre d'entiers, chacun faisant quelques mots-machine. Nous présentons une implémentation logicielle d'ECM qui est optimisée pour ce cas précis et la comparons á des implémentations récentes en matériel.

Mots-clés: factorisation des entiers, courbes elliptiques, crible algébrique

#### 1 Introduction

The sieving step of the Number Field Sieve [15] identifies integer pairs (a,b) with  $a \perp b$  such that the values of two homogeneous polynomials  $F_i(a,b)$ ,  $i \in \{1,2\}$ , are both smooth, where the sieving parameters are chosen according to the smoothness criterion. Typically the two polynomials each have a "factor base bound"  $\mathfrak{B}_i$ , a "large prime bound"  $\mathfrak{L}_i$ , and a permissible maximum number of large primes  $k_i$  associated with them, so that  $F_i(a,b)$  is considered smooth if it contains only prime factors up to  $\mathfrak{B}_i$  except for up to  $k_i$  prime factors greater than  $\mathfrak{B}_i$ , but none exceeding  $\mathfrak{L}_i$ . For example, for the factorization of the RSA-155 challenge number [5] (a hard integer of 512-bit) the values  $\mathfrak{B}=2^{24}$ ,  $\mathfrak{L}=10^9$  and k=2 were used for both polynomials. Kleinjung [14] gives an estimate for the cost of factoring a 1024-bit RSA key based on the parameters  $\mathfrak{B}_1=1.1\cdot 10^9$ ,  $\mathfrak{B}_2=3\cdot 10^8$ , and  $\mathfrak{L}_1=\mathfrak{L}_2=2^{42}$  with  $k_1=5$  and  $k_2=4$ .

The contribution of the factor base primes to each polynomial value  $F_i(a, b)$  for a set of (a, b) pairs is approximated with a sieving procedure, which estimates roughly what the size of the polynomial values will be after factor base primes have been divided out. If these estimates for a particular (a, b) pair are small enough that both  $F_i(a, b)$  values might be smooth, the polynomial values are computed, the factor base primes are divided out, and the two cofactors  $c_i$  are tested to see if they satisfy the smoothness criterion.

If only one large prime is permitted, no factoring needs to be carried out at all for the large primes: if  $c_i > \mathcal{L}_i$  for either i, this (a, b) pair is discarded. Since generally  $\mathcal{L}_i < \mathfrak{B}_i^2$  and all prime factors below  $\mathfrak{B}_i$  have been removed, a cofactor  $c_i \leq \mathcal{L}_i$  is necessarily prime and need not be factored.

If up to two large primes are permitted, and the cofactor  $c_i$  is composite and therefore greater than the large prime bound but below  $\mathfrak{L}_i^2$  (or a suitably chosen threshold somewhat less then  $\mathfrak{L}_i^2$ ), it is factored. Since the prime factors in  $c_i$  are bounded below by  $\mathfrak{B}_i$ , and  $\mathfrak{L}_i$  is typically less than  $\mathfrak{B}_i^{1.5}$ , the factors can be expected not to be very much smaller than the square root of the composite number. This way the advantage of special purpose factoring algorithms when small divisors (compared to the composite size) are present does not come into great effect, and general purpose factoring algorithms like SQUFOF or MPQS perform well. In previous implementations of QS and NFS, various algorithms for factoring composites of two prime factors have been used, including SQUFOF and Pollard-Rho in [9, chapter 3.6], and P-1, SQUFOF, and Pollard-Rho in [4, §3].

If more than two large primes are allowed, the advantage of special purpose factoring algorithms pays off. Given a composite cofactor  $c_i > \mathcal{L}_i^2$ , we know that it can be smooth only if it has at least three prime factors, of which at least one must be less than  $c_i^{1/3}$ . If it has no such small factor, the cofactor is not smooth, and its factorization is not actually required, as this (a,b) pair will be discarded. Hence an early-abort strategy can be employed that uses special-purpose factoring algorithms until either a factor is found and the new cofactor can be tested for smoothness, or after a number of factoring attempts have failed, the cofactor may be assumed to be not smooth with high probability so that this (a,b) pair can be discarded.

Suitable candidates for factoring algorithms for this purpose are the P-1 method, the P+1 method, and the Elliptic Curve Method (ECM). All have in common that a prime factor p is found if the order of some group defined over

$\mathbb{F}_p$  is itself smooth. A beneficial property is that for ECM, and to a lesser extent for P+1, parameters can be chosen so that the group order has known small factors, making it more likely smooth. This is particularly effective if the prime factor to be found, and hence the group order, is small.

Although the P–1 and P+1 methods by themselves have a relatively poor asymptotic algebraic complexity in  $O(\sqrt{p})$  (assuming an asymptotically fast stage 2 as described in [23] for example), they find surprisingly many primes in far less time, making them useful as a first quick try to eliminate easy cases before ECM begins. In fact, P–1 and P+1 may be viewed as being equivalent to less expensive ECM attempts (but also less effective, due to fewer known factors in the group order).

Another well-known special-purpose factoring algorithm is Pollard's "Rho" method [25] which looks for a collision modulo p in an iterated pseudo-random function modulo N, where p is a prime factor of N we hope to find. When choosing no less than  $\sqrt{2\log(2)n} + 0.28$  integers uniformly at random from [1,n], the probability of choosing at least one integer more than once is at least 0.5, well known as the Birthday Paradox which states that in a group of only 23 people, two share a birthday with more than 50% probability. For the Rho method, the expected number of iterations to find a prime factor p is in  $O(\sqrt{p})$ , and in case of Pollard's original algorithm, the average number of iterations for primes p around p is close to p is close to p where each iteration takes three modular squarings and a modular multiplication, for an average of p 130000 modular multiplications when counting squarings as multiplications. Brent [2] gives an improved iteration which reduces the number of multiplications by about 25% on average. We will see that a combination of p-1, p-1, and ECM does better on average.

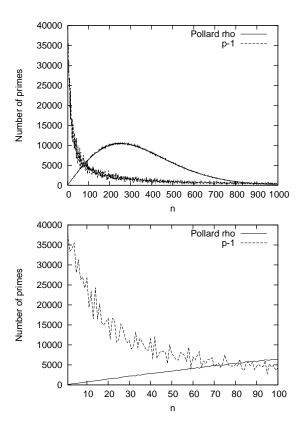

Furthermore, trying the Pollard-Rho method with only a low number of iterations before moving on to other factoring algorithms has a negligible probability of success — among the 4798396 primes in  $[2^{30},2^{30}+10^8]$ , only 3483 are found with at most 1000 iterations of the original Pollard-Rho algorithm with pseudo-random map  $x\mapsto x^2+1$  and starting value  $x_0=2$ . For P–1, there are 1087179 primes p in the same range where the largest prime factor of p-1 does not exceed 1000, and exponentiating by the product of all primes and prime powers up to B requires only  $B/\log(2)+O\left(\sqrt{B}\right)\approx 1.44B$  squarings, compared to 4 multiplications per iteration for the original Pollard-Rho algorithm. By using a stage 2 for P–1, its advantage increases further. Figure 1 shows the distribution of the largest prime factor of p-1 and the required number of Pollard-Rho iterations for finding p, respectively, for primes p in  $[2^{30},2^{30}+10^8]$ . The distribution of the largest prime factor of p+1 is identical to that of p-1, up to statistical noise. We conclude that unlike P–1 and P+1, the Pollard-Rho method is not suitable for removing "easy pickings."

This research report describes an implementation of trial division for composites of a few machine words, as well as the P-1, P+1, and Elliptic Curve Method of factorization for small composites of one or two machine words, aimed at factoring cofactors as occur during the sieving phase of the Number Field Sieve.

Figure 1: Number of primes p in  $\left[2^{30},2^{30}+10^{8}\right]$  where the largest prime factor of p-1, respectively the number of Pollard-Rho iterations to find p, is in  $\left[100n,100n+99\right],\ n\in\mathbb{N}$ . The left graph shows  $0\leq n\leq 1000$ , the right graph shows a zoom on  $0\leq n\leq 100$ .

#### 2 Trial Division

Before factoring of the non-sieved cofactor of the polynomial values into large primes can commence, the cofactor needs to be determined by dividing out all the factor base primes. For medium size factor base primes, say larger than a few hundred or a few thousand, a sieving technique ("re-sieving") can be used again that stores the primes when re-sieving hits a location previously marked as "likely smooth." For large factor base primes, say larger than a few ten thousand, the number of hits in the sieve area is small enough that the primes can be stored during the initial sieving process itself. For the smallest primes, however, re-sieving is inefficient, and a trial division technique should be used. This Section examines a fast trial division routine, based on ideas by Montgomery and Granlund [13] [21], that precomputes several values per candidate prime divisor to speed up the process.

#### 2.1 Trial division algorithm

Given many composite integers  $N_i, \ 0 \le i < n$ , we want to determine which primes from some set  $P = \{p_j, 0 \le j < k\}$  of small odd primes divide each  $N_i$ . We assume  $n \gg k$ . Each  $N_i$  is a multi-word integer of up to  $\ell+1$  words,  $N_i = \sum_{j=0}^\ell n_{i,j}\beta^j$ , where  $\beta$  is the machine word base (e.g.,  $\beta = 2^{32}$  or  $\beta = 2^{64}$ ) and  $\ell$  is on the order of "a few," say  $\ell \le 4$ . For each prime  $p \in P$ , we precompute  $w_j = \beta^j \mod p$  for  $1 \le j \le \ell$ ,  $p_{\text{inv}} = p^{-1} \pmod{\beta}$  and  $p_{\text{lim}} = \left\lfloor \frac{\beta-1}{p} \right\rfloor$ .

Consider a particular integer  $N = \sum_{j=0}^{\ell} n_j \beta^j$ , and a particular prime  $p \in P$ . The algorithm first does a semi-reduction modulo p to obtain a singleword integer congruent to  $N \pmod{p}$ , then tests this single-word integer for divisibility by p.

To do so, we compute  $r = n_0 + \sum_{j=1}^{\ell} n_j w_j \leq (\beta - 1)(\ell(p-1) + 1)$ . To simplify the next steps, we require  $p < \sqrt{\frac{\beta}{\ell}}$ . Even for  $\beta = 2^{32}$ ,  $\ell = 4$ , this gives p < 32768 which is easily sufficient for trial division in NFS.

With this bound on p, we have  $r < (\beta - 1)(\sqrt{\beta \ell} - \ell + 1)$ . We then decompose r into  $r = r_1\beta + r_0$ , where  $0 \le r_0 < \beta$ . This implies  $r_1 < \sqrt{\beta \ell}$ , and  $r_1w_1 \le r_1(p-1) < \sqrt{\beta \ell} \left(\sqrt{\frac{\beta}{\ell}} - 1\right) = \beta - \sqrt{\beta \ell}$ .

The algorithm then does another reduction step by  $s = r_1w_1 + r_0$ . We would like  $s = s_1\beta + s_0 < 2\beta - p$ , so that a final reduction step  $t = s_0 + s_1w_1 < \beta$  produces a one-word result. Since  $r_1(p-1) < \beta - \sqrt{\beta\ell}$ ,  $s < 2\beta - \sqrt{\beta\ell} - 1 < 2\beta - p$ . Since  $s_1$  is either 0 or 1, the multiplication and addition in  $s_0 + s_1w_1$  is really just a conditional addition.

Now we have a one-word integer t which is divisible by p if and only if N is. To determine whether  $p \mid t$ , we use the idea from [13, §9] to compute  $u = tp^{-1} \mod \beta$ , using the precomputed  $p_{\text{inv}} = p^{-1} \pmod \beta$ . If  $p \mid t, t/p$  is an integer  $< \beta$  and so the modular arithmetic mod  $\beta$  must produce the correct u = t/p. There are  $\left\lfloor \frac{\beta-1}{p} + 1 \right\rfloor$  multiples of p (including 0) less than  $\beta$ , under division by p these map to the integers  $\left[0,\ldots,\left\lfloor \frac{\beta-1}{p} \right\rfloor\right]$ . Since p is coprime to  $\beta$ , multiplication by  $p^{-1} \pmod \beta$  is a bijective map, so all non-multiples of p must map to the remaining integers  $\left[\left\lfloor \frac{\beta-1}{p} \right\rfloor + 1, \beta - 1\right]$ . Hence the test for divisibility

can be done by a one-word multiplication by the precomputed constant  $p_{\text{inv}}$ , and one comparison to the precomputed constant  $p_{\text{lim}} = \left| \frac{\beta - 1}{p} \right|$ .

#### 2.2 Implementation

The algorithm is quite simple to implement on an x86 CPU, which offers the two-word product of two one-word arguments by a single MUL instruction. It might run as shown in Algorithm 1, where  $x_1$ ,  $x_0$  are registers that temporarily hold two-word products. A pair of registers holding a two-word value  $r_1\beta + r_0$  is written as  $r_1:r_0$ . The values  $r_{0,1}$ ,  $s_{0,1}$ , and  $t_0$  can all use the same registers, written  $r_{0,1}$  here. The loop over j should be unrolled.

```

Input: Length \ell

N = \sum_{i=0}^{\ell} n_i \beta^i, \ 0 \le n_i < \beta

Odd prime p < \sqrt{\frac{\beta}{\ell}}

w_j = \beta^j \mod p \text{ for } 1 \le j \le \ell

p_{\text{inv}} = p^{-1} \mod \beta

p_{\text{lim}} = \left\lfloor \frac{\beta - 1}{p} \right\rfloor

Output: 1 if p \mid N, 0 otherwise

r_0 := n_0;

r_1 := 0;

for 1 \le j \le \ell do

x_1 : x_0 = n_j \cdot w_j;

r_1 : r_0 = r_1 : r_0 + x_1 : x_0;

x_0 = r_1 \cdot w_1;

r_0 = (r_0 + x_0) \mod \beta;

if last \ addition \ set \ carry \ flag \ then

r_0 = (r_0 + w_1) \mod \beta;

r_0 = r_0 \cdot p_{\text{inv}};

if r_0 \le p_{lim} \ then

return \ 1;

else

return \ 0;

Algorithm \ 1: Pseudo-code for trial division of numbers of up to \(\ell + 1\) words.

```

This code uses  $\ell$  multiplications of two words to a two-word product. These multiplications are independent of one another, so they can overlap on a CPU with pipelined multiplier. On an Athlon64, Opteron, and Phenom CPUs, a multiplication can start every 2 clock cycles, the low word of the product is available after 4 clock cycles, the high word after 5 clock cycles. Thus in case of  $\ell=4$ , the latency for the first 4 products and building their sum should be 12 cycles. The two remaining multiplies, the additions and conditional moves should be possible in about 11 cycles, giving a theoretical total count of about 23 clock cycles for trial dividing a 5 word integer by a small prime. Data movement from cache may introduce additional latency.

#### 2.3 Use in NFS

Given a sieve region of size s with every d-th entry a sieve report, trial dividing by the prime p for all sieve reports has cost O(s/d), while resieving has cost

O(rs/p), where r is the number of roots modulo p the sieved polynomial has. Hence whether trial division or resieving is preferable will depend on  $\frac{p}{dr}$ , where those p with  $\frac{p}{dr} < c$  for some threshold c should use trial division.

As primes are divided out of N, the number of words in N may decrease, making the following trial division faster. It might be worthwhile to try to reduce the size of N as quickly as possible. The probability that a prime p divides N may be estimated as r/p, the size decrease as  $\log(p)$ , so the probability that trial division by p will decrease the number of words in N may be estimated as being proportional to  $r\log(p)/p$ . For trial division, the candidate divisors p can be sorted so that this estimate is decreasing. This probability estimate does not take into account the fact that N, being a sieve report, is likely smooth, and under this condition the probability that p divides N increases by Bayes' theorem, more so for larger p than for small ones.

#### 2.4 Testing several primes at once

Algorithm 1 reduces the input number to a one-word integer which is congruent to  $N\pmod{p}$ , then tests divisibility by p of that one-word integer. It is possible to do the reduction step for composite candidate divisors q, then test divisibility of the resulting one-word integer for all  $p\mid q$ . This way, for integers consisting of several words, the expensive reduction needs to be done only once for each q, the relatively cheap divisibility test for each p. This is attractive if the bound  $q<\sqrt{\beta/\ell}$  is not too small. With  $w=2^{64}$ ,  $\ell=4$ , we can use q<2147483648, which allows for several small primes in q. For integers N with a larger number of words, it may be worthwhile to introduce an additional reduction step (for example, using Montgomery's REDC for a right-to-left reduction) to relax the bound on q to, e.g.,  $q< w/\ell$ , so that the number of primes in q can be doubled at the cost of only two additional multiplies. In NFS, if the primes found by re-sieving have been divided out already before trial division begins, the  $N_i$  may not be large enough to make this approach worthwhile.

#### 2.5 Performance of trial division

To measure the performance of the trial division code, we divide  $10^7$  consecutive integers of  $1, \ldots, 5$  words by the first n = 256, 512, 1024, and 2048 odd primes on a 2 GHz AMD Phenom CPU, see Figure 2. The higher timings per trial division for n = 256 are due to the additional cost of dividing out found divisors, which has a greater relative contribution for smaller primes which divide more frequently. The timing for  $\ell = 4, n = 2048$  is close to the predicted 23 clock cycles. The sudden increase for n = 2048 in the case of N with one word is due to caching: with 7 stored values  $(p, p_{\text{inv}}, p_{\text{lim}}, w_{1,\dots,4})$  of 8 bytes each, n = 2048has a table of precomputed values of size 112kB, which exceeds the level-1 data cache size of 64kB of the Phenom. For large sets of candidate primes, the sequential passes through the precomputed data cause frequent misses in the level-1 cache, and the trial divisions for N of only one word are fast enough that transfer rate from the level-2 cache limits the execution. This could be avoided by computing fewer  $w_i$  constants (i.e., choosing a smaller  $\ell$ ) if the N are known to be small, or storing the  $w_i$  in separate arrays rather than interleaved, so that the  $w_i$  for larger i do not occupy cache while the N processed are small. Since the value of p is not actually needed during the trial division, it is possible to

|      | Number of words in $N$ |             |             |                 |                  |  |

|------|------------------------|-------------|-------------|-----------------|------------------|--|

| n    | 1                      | 2           | 3           | 4               | 5                |  |

| 256  | 6.8 (2.6)              | 15.3 (6.0)  | 20.8 (8.1)  | 27.5 (10.7)     | 32.4 (12.6)      |  |

| 512  | 11.3 (2.2)             | 28.2 (5.5)  | 38.8 (7.6)  | $52.0\ (10.2)$  | $61.32 \ (12.0)$ |  |

| 1024 | 21.3(2.1)              | 54.9 (5.4)  | 75.9(7.4)   | $102.0\ (10.0)$ | 120.7 (11.8)     |  |

| 2048 | 85.4 (4.1)             | 108.4 (5.3) | 149.8 (7.3) | 200.8 (9.8)     | 237.8 (11.6)     |  |

Figure 2: Time in seconds for trial division of  $10^7$  consecutive integers by the first n odd primes on a 2 GHz AMD Phenom CPU. Time per trial divison in nanoseconds in parentheses.

avoid storing it and recomputing it, e.g., from  $p_{\text{inv}}$  when it needs to be reported as a divisor.

#### 3 Modular arithmetic

The modular arithmetic operations are relatively inexpensive when moduli and residues of only a few machine words are considered, and should be implemented in a way that lets the compiler perform in-lining of simple arithmetic functions to avoid unnecessary function call overhead and data movement between registers, memory and stack due to the calling conventions of the language and architecture. Many simple arithmetic operations can be implemented easily and efficiently using assembly language, but are cumbersome to write in pure C code, especially if multi-word products or carry propagation are involved. The GNU C compiler offers a very flexible method of injecting assembly code into C programs, with an interface that tells the compiler all constraints on input and output data of the assembly block so that it can perform optimization on the code surrounding the assembly statements. By defining some commonly used arithmetic operations in assembly, much of the modular arithmetic can be written in C, letting the compiler handle register allocation and data movement. The resulting code is usually not optimal, but quite useable. For the most timecritical operations, writing hand-optimized assembly code offers an additional speed improvement.

For the present work, modular arithmetic for moduli of 1 machine word and of 2 machine words with the two most significant bits zero is implemented. Implementation of arithmetic for moduli of 3 machine words is in progress.

#### 3.1 Assembly support

To give an example of an elementary function that is implemented with the help of some assembly code, we examine modular addition with a modulus of 1 machine word. This is among the most simple operations possible, but useful as an example.

Let a "reduced residue" with respect to a positive modulus m mean an integer representative  $0 \le r < m$  of the residue class  $r \pmod{m}$ . Modular addition of

two reduced residues can be defined as

$$(a+b) \bmod m = \begin{cases} a+b-m & \text{if } a+b-m \ge 0 \\ a+b & \text{otherwise.} \end{cases}$$

If any modulus  $m < \beta$  is permitted, where  $\beta$  is the machine word base, then the problem that a+b might overflow the machine word arises. One could test for this case, then test if  $a+b \ge m$ , and subtract m if either is true, but this necessitates two tests. With a slight rearrangement, we can do with one:

```

1  r := a + b;

2  s := a - m;

3  t := s + b;

4  if last addition set carry flag then

5     r := t;

```

All arithmetic in this code is assumed modulo the word base  $\beta$ , i.e., the integers in r, s, and t are reduced residues modulo  $\beta$ . In line 2, since a is reduced modulo m, the subtraction a-m necessarily produces a borrow, so that  $s=a-m+\beta$ . In line 3, if  $s+b<\beta$ , then this addition does not produce a carry, and  $t=a+b-m+\beta<\beta$ , i.e., a+b-m<0. If  $s+b\geq\beta$ , the addition does produce a carry, and  $0\leq t=s+b-\beta=a+b-m$ . Hence t is the proper result if and only if a carry occurs in line 3, to make up for the borrow of line 2. Lines 1 and 2 are independent and can be executed in parallel, leading to a dependent chain of length 3. We require a< m for correctness, if  $b\geq m$ , the result still satisfies  $r\equiv a+b\pmod{m}$  and r< b, but not necessarily r< m.

The implementation in C with a GCC x86 assembly block shown below. The value of s, shown separately for clarity above, is stored in t here.

The computation of the initial t and r are done in C, to give the compiler some scheduling freedom. Since C does not provide direct access to the carry flag, the addition t := t + b and the following conditional assignment are done in assembly. The constraints on the data passed to the assembly block state that the values of r and t must reside in registers ("r") since the target of the conditional move instruction cmove must be a register, and at least one of source or target of the addition instruction add must be a register. We allow the variable b to be passed in a register, in memory or as an immediate operand ("g", "general" constraint, for  $x86\_64$  the correct constraint is "rme" since immediate constants are only 32 bit wide), which is the source operand to the add instruction. The "+" modifier tells that the values in r and t will be modified, and the "&" modifier tells that t may be modified before the end of the assembly block and thus no

other input variable should be passed in the register assigned to t, even if their values are known to be identical. Finally, "cc" tells the compiler that the values of the flags register may change. These constraints provide the information the compiler needs to be able to use the assembly block correctly, while leaving enough flexibility that it can optimize register allocation and data movement, compared to, e.g., compilers that require all parameters to assembly blocks in a fixed set of registers.

An alternative solution is to compute r := b - (m - a) and adding m if the outer subtraction produced a borrow. However, this requires a conditional addition rather than a conditional move.

Similar to the modular addition, various functions such as modular subtraction and multiplication for one and two-word moduli, two-word addition, subtraction, multiplication and binary shift, and division with a two-word dividend (used, for example, for preparing a residue for use with REDC modular reduction with a two-word modulus, see 3.2) are written as functions with assembly support. As optimization effort progresses, more time-critical functions currently written in C with assembly macros will be replaced by dedicated assembly code.

#### 3.2 Modular reduction with REDC

Montgomery presented in [17] a method for fast modular reduction. Given an integer  $0 \le a < \beta m$ , for odd modulus m of one machine word and machine word base  $\beta$  (here assumed a power of 2), and a precomputed constant  $m_{\text{inv}} = -m^{-1} \mod \beta$ , it computes an integer  $0 \le r < m$  which satisfies  $r\beta \equiv a \pmod{m}$ . It does so by computing the minimal non-negative tm such that  $a + tm \equiv 0 \pmod{\beta}$ , to make use of the fact that division by  $\beta$  is very inexpensive. Since  $t < \beta$ ,  $(a + tm)/\beta < 2m$ , and at most one final subtraction of m ensures r < m. He calls the algorithm that carries out this reduction "REDC," shown in Algorithm 2.

```

Input: m, the modulus \beta, the word base a < \beta m, integer to reduce m_{\text{inv}} < \beta such that mm_{\text{inv}} \equiv -1 \pmod{\beta}

Output: r < m with r\beta \equiv a \pmod{m}

t := a \cdot m_{\text{inv}} \mod{\beta}; r := (a + t \cdot m)/\beta; if r \geq m then r := r - m;

```

**Algorithm 2**: Algorithm REDC for modular reduction with one-word modulus. All variables take non-negative integer values.

The reduced residue output by this algorithm is not in the same residue class mod m as the input, but the residue class gets multiplied by  $\beta^{-1} \pmod{m}$  in the process. To prevent accumulating powers of  $\beta^{-1} \pmod{m}$  and having unequal powers of  $\beta$  when, e.g., adding or comparing residues, any residue modulo m is converted to Montgomery representation first, by multiplying it by  $\beta$  and reducing (without REDC) modulo m, i.e., the Montgomery representation of a

residue  $a\pmod{m}$  is  $a\beta\pmod{m}$ . This way, if two residues in Montgomery representation  $a\beta\pmod{m}$  and  $b\beta\pmod{m}$  are multiplied and reduced via REDC, then REDC $(a\beta b\beta)\equiv ab\beta\pmod{m}$  is the product in Montgomery representation. This ensures the exponent of  $\beta$  in the residues always stays 1, and so allows addition, subtraction, and equality tests of residues in Montgomery representation. Since  $\beta\perp m$ , we also have  $a\beta\equiv 0\pmod{m}$  if and only if  $a\equiv 0\pmod{m}$ , and  $\gcd(a\beta,m)=\gcd(a,m)$ . Since  $\beta=2^{32}$  or  $2^{64}$  is an integer square, the Jacobi symbol satisfies  $\binom{a\beta}{m}=\binom{a}{m}$ .

For moduli m of more than one machine word, say  $m<\beta^k$ , a product of

For moduli m of more than one machine word, say  $m < \beta^k$ , a product of two reduced residues may exceed  $\beta$ , but is below  $m\beta^k$ . The reduction can be carried out in two ways: one essentially performs the one-word REDC reduction k times, performing  $O(k^2)$  one-word multiplies, the other replaces arithmetic modulo  $\beta$  in REDC by arithmetic modulo  $\beta^k$ , performing O(1) k-word multiplications. In either case, a full reduction with (repeated one-word or a single multi-word) REDC divides the residue class of the output by  $\beta^k$ , and the conversion to Montgomery representation must multiply by  $\beta^k$  accordingly. The former method has lower overhead and is preferable for small moduli, the latter can use asymptotically fast multiplication algorithms if the modulus is large. As in our application the moduli are quite small, no more than two machine words, we use the former method.

Before modular arithmetic with REDC for a particular m can begin, the constant  $m_{\rm inv}$  needs to be computed. If  $\beta$  is a power of 2, Hensel lifting makes this computation very fast. To speed it up further, we try to guess an approximation to  $m_{\rm inv}$  so that a few least significant bits are correct, thus saving a few Newton iterations. The square of any odd integer is congruent to 1 (mod 8), so  $m_{\rm inv} \equiv m \pmod{8}$ . The fourth bit of  $m_{\rm inv}$  is equal to the binary exclusive-or of the second, third, and fourth bit of m, but on many microprocessors an alternative suggestion from Montgomery [22] is slightly faster: (3m) XOR 2 gives the low 5 bits of  $m_{\rm inv}$  correctly. Each Newton iteration  $x \mapsto 2x - x^2m$  doubles the number of correct bits, so that with either approximation, 3 iterations for  $\beta = 2^{32}$  or 4 for  $\beta = 2^{64}$  suffice.

Converting residues out of Montgomery representation can be performed quickly with REDC, but converting them to Montgomery representation requires another modular reduction algorithm. If such conversions are to be done frequently, it pays to precompute  $\ell = \beta^2 \mod m$ , so that REDC( $a\ell$ ) =  $a\beta \mod m$  allows using REDC for the purpose.

In some cases, the final conditional subtraction of m in REDC can be omitted. If a < m, then  $a + tm < m\beta$  since  $t < \beta$ , so  $r = (a + tm)/\beta < m$  which can be used when converting residues out of Montgomery form, or when division by a power of 2 modulo m is desired.

#### 3.3 Modular inverse

To compute a modular inverse  $r \equiv a^{-1} \pmod{m}$  for a given reduced residue a and odd modulus m with  $a \perp m$ , we use a binary extended Euclidean algorithm. Modular inverses are used at the beginning of stage 2 for the P–1 algorithm, and for initialisation of stage 1 of ECM (except for a select few curves which have simple enough parameters that they can be initialised using only division by small constants). Our code for a modular inverse takes about  $0.5\mu$ s for one-word moduli, which in case of P–1 with small  $B_1$  and  $B_2$  parameters accounts

for several percent of the total run-time, showing that some optimization effort is warranted for this function.

The extended Euclidean algorithm solves

$$ar + ms = \gcd(a, m)$$

for given a, m by initialising  $e_0 = 0, f_0 = 1, g_0 = m$  and  $e_1 = 1, f_1 = 0, g_1 = a$ , and computing sequences  $e_i, f_i$  and  $g_i$  that maintain

$$ae_i + mf_i = q_i \tag{1}$$

where  $\gcd(a,m) \mid g_i$  and the  $g_i$  are strictly decreasing until  $g_i = 0$ . The original Euclidean algorithm uses  $g_i = g_{i-2} \mod g_{i-1}$ , that is, in each step we write  $g_i = g_{i-2} - g_{i-1} \lfloor \frac{g_{i-2}}{g_{i-1}} \rfloor$  and likewise  $e_i = e_{i-2} - e_{i-1} \lfloor \frac{g_{i-2}}{g_{i-1}} \rfloor$  and  $f_i = f_{i-2} - f_{i-1} \lfloor \frac{g_{i-2}}{g_{i-1}} \rfloor$ , so that equation (1) holds for each i. If n is the smallest i such that  $g_i = 0$ , then  $g_{n-1} = \gcd(a,m)$ ,  $s = f_{n-1}$ , and  $r = e_{n-1}$ . Since we only want the value of  $r = e_{n-1}$ , we don't need to compute the  $f_i$  values. We can write  $u = e_{i-1}, v = e_i, x = g_{i-1}, y = g_i$  and for i = 1 initialise u = 0, v = 1, x = m, and y = a. Then each iteration  $i \mapsto i+1$  is computed by

$$(u, v, x, y) := (v, u - |x/y|v, y, x - |x/y|y).$$

At the first iteration where y = 0, we have r = u and x = 1 if a and m were indeed coprime.

A problem with this algorithm is the costly computation of  $\lfloor x/y \rfloor$  as integer division is usually slow. The binary extended Euclidean algorithm avoids this problem by using only subtraction and division by powers of 2. Our implementation is inspired by code written by Robert Harley for the ECCp-97 challenge and is shown in Algorithm 3. The updates maintain  $ua \equiv -x2^t \pmod{m}$  and  $va \equiv y2^t \pmod{m}$  so that when y=1, we have  $r=v2^{-t}=a^{-1} \pmod{m}$ .

```

Input: Odd modulus m

Reduced residue a \pmod{m}

Output: Reduced residue r \pmod{m} with ar \equiv 1 \pmod{m}, or failure if

\gcd(a,m) > 1

if a = 0 then

return failure;

/* 2^{t} || a */

t := \operatorname{Val}_2(a);

u := 0; v := 1; x := m; y := a/2^t;

while x \neq y do

/* 2^{\ell} || x - y */

\ell := \operatorname{Val}_2(x - y);

if x < y then

(u, v, x, y, t) := (u2^{\ell}, u + v, x, (y - x)/2^{\ell}, t + \ell);

else

(u, v, x, y, t) := (u + v, v2^{\ell}, (x - y)/2^{\ell}, y, t + \ell);

if y \neq 1 then

return failure;

r := v2^{-t} \bmod m;

Algorithm 3: Binary extended GCD algorithm.

```

In each step we subtract the smaller of x, y from the larger, so they are decreasing and non-negative. Neither can become zero as that implies x = y

in the previous iteration, which terminates the loop. Since both are odd at the beginning of each iteration, their difference is even, so one value decreases by at least a factor of 2, and the number of iterations is at most  $\log_2(am)$ . In each iteration, uy + vx = m, and since x and y are positive,  $u, v \leq m$  so that no overflow occurs with fixed-precision arithmetic.

To perform the modular division  $r = v/2^{t_i}$ , we can use REDC. While  $t \ge \log_2(\beta)$ , we replace v := REDC(v) and  $t := t - \log_2(\beta)$ . Then, if t > 0, we perform a variable-width REDC to divide by  $2^t$  rather than by  $\beta$  by computing  $r = (v + ((v m_{\text{inv}}) \mod 2^t) m)/2^t$  with  $m m_{\text{inv}} \equiv -1 \pmod{\beta}$ . Since v < m, we don't need a final subtraction in these REDC.

If the residue a whose inverse we want is given in Montgomery representation  $a\beta^k \mod m$  with k-word modulus m, we can use REDC 2k times to compute  $a\beta^{-k} \mod m$ , then compute the modular inverse to obtain the inverse of a in Montgomery representation:  $a^{-1}\beta^k \equiv \left(a\beta^{-k}\right)^{-1} \pmod{m}$ . This can be simplified by using the fact that the binary extended GCD computes  $v = a^{-1}2^t$ . If we know beforehand that  $t \geq \log_2 \beta$ , we can skip divisions by  $\beta$  via REDC both before and after the binary extended GCD. Let the function t(x,y) give the value of t at the end of Algorithm 3 for coprime inputs x,y. It satisfies

$$t(x,y) = \begin{cases} 0 & \text{if } x = y \text{ (implies } x = y = 1), \\ t(x/2,y) + 1 & \text{if } x \neq y, \ 2 \mid x, \\ t(x-y,y) & \text{if } x > y, \ 2 \nmid x, \\ t(y,x) & \text{if } x < y, \ 2 \nmid x. \end{cases}$$

Assuming y odd, case 3 is always followed by case 2, and we can substitute case 3 by t(x,y) = t((x-y)/2,y) + 1. We compare the decrease of the sum x+y and the increase of t. In case 2,  $(x+y) \mapsto x/2 + y > (x+y)/2$ , and t increases by 1. In the substituted case 3,  $(x+y) \mapsto (x+y)/2$ , and t increases by 1. We see that whenever x+y decreases, t increases, and whenever t increases by 1, x+y drops by at most half, until x+y=2. Hence  $t(x,y) \ge \log_2(x+y) - 1$ , and therefore  $t(x,y) \ge \log_2(y)$ , since x>0.

Thus in case of k-word moduli  $\beta^{k-1} < m < \beta^k$ , we have  $t(x,m) \ge (k-1)\log_2(\beta)$  for any positive x, so using  $a\beta^{-1} \pmod m$  as input to the binary extended GCD is sufficient to ensure that at the end we get  $a^{-1}\beta \equiv v2^{-t} \pmod m$ , or  $a^{-1}\beta^k \equiv v2^{-t+(k-1)\log_2(\beta)} \pmod m$  and the desired result  $a^{-1}\beta^k$  can be obtained from  $v2^{-t}$  with a division by  $2^{t-(k-1)\log_2(\beta)}$  via REDC.

#### 3.4 Modular division by small integers

Initialisation of P+1 and ECM involves division of residues by small integers such as 3, 5, 7, 11, 13 or 37. These can be carried out quickly by use of dedicated functions. To compute  $r \equiv ad^{-1} \pmod{m}$  for a reduced residue a with  $d \perp m$ , we first compute t = a + km, with k such that  $t \equiv 0 \pmod{d}$ , i.e.,  $k = a \left( -m^{-1} \right) \pmod{d}$ , where  $-m^{-1} \pmod{d}$  is determined by look-up in a precomputed table for the d-1 possible values of  $m \pmod{d}$ .

For one-word moduli, the resulting integer t can be divided by d via multiplication by the precomputed constant  $d_{\text{inv}} \equiv d^{-1} \pmod{\beta}$ . Since  $t/d < m < \beta$  is an integer, the result  $r = td_{\text{inv}} \mod{\beta}$  produces the correct reduced residue r. This implies that computing t modulo  $\beta$  is sufficient.

For two-word moduli, we can choose an algorithm depending on whether m and d are large enough that t may overflow two machine words or not. In either case, we may write  $t = t_1\beta + t_0$  with  $0 \le t_0 < \beta$ ,  $0 \le t_1 < d\beta$  and  $r = r_1\beta + r_0$  with  $0 \le r_0, r_1 < \beta$ , and can compute  $r_0 = t_0 d_{\text{inv}} \mod \beta$ .

If t does not overflow, we may write  $t = t'' + t'd\beta$ ,  $0 \le t'' < d\beta$ , where  $d \mid t''$ . Then  $r = t/d = t'\beta + t''/d$  with  $t''/d < \beta$ , so we can compute  $r_1 = \lfloor t_1/d \rfloor$ . The truncating division by the invariant d can be implemented by the methods of [13]. An advantage of this approach is that the computation of the low word  $r_0$  from  $t_0$  is independent of the computation of the high word  $r_1$  from  $t_1$ .

If t may overflow two machine words, we can compute  $r_0$  as before, and use that  $t - dr_0$  is divisible by  $d\beta$ , so we may write  $r_1\beta + r_0 \equiv t/d \pmod{\beta^2}$  as  $r_1 \equiv (t - dr_0)/\beta \cdot d_{\text{inv}} \pmod{\beta}$ .

## 4 P-1 algorithm

The P-1 algorithm is described, for example, in [23]. We recapitulate some elementary facts here. The first stage of P-1 computes

$$x_1 = x_0^e \mod N$$

for some starting value  $x_0 \not\equiv 0, \pm 1 \pmod{N}$  and a highly composite integer exponent e. By Fermat's little theorem, if  $p-1 \mid e$  for any  $p \mid N$ , then  $x_1 \equiv 1 \pmod{p}$  and  $p \mid \gcd(x_1-1,N)$ . This condition is sufficient but not necessary: it is enough (and necessary) that  $\operatorname{ord}_p(x_0) \mid e$ , where  $\operatorname{ord}_p(x_0)$  is the order of  $x_0$  in  $\mathbb{F}_p^*$ . To maximise the probability that  $\operatorname{ord}_p(x_0) \mid e$  for a given size of e, we could choose e to contain all primes and prime powers that divide  $\operatorname{ord}_p(x_0)$  with probability better than some bound  $1/B_1$ . One typically assumes that a prime power  $q^k$  divides  $\operatorname{ord}_p(x_0)$  with probability  $q^{-k}$ , so that e is taken as the product of all primes and prime powers not exceeding  $B_1$ , or  $e = \operatorname{lcm}(1, 2, 3, 4, \ldots, B_1)$ .

The value of e is precomputed and passed to the P-1 stage 1 routine, which basically consists only of a modular exponentiation, a subtraction and a gcd. The base  $x_0$  for the exponentiation is chosen as 2; in a left-to-right binary powering ladder, this requires only squarings and doublings, where the latter can be performed quickly with an addition instead of a multiplication by  $x_0$ .

To reduce the probability that all prime factors of N (i.e., N itself) are found simultaneously and reported as a divisor at the end of stage 1, only the odd part of e is processed at first, and then the factors of 2 in e one at a time by successive squarings. After each one we check if the new residue is 1 (mod N), indicating that all prime factors of N have been found now, and if so, revert to the previous value, to use it for the gcd. If not the same power of 2 divides  $\operatorname{ord}_p(x_0)$  exactly for all primes  $p \mid N$ , then this will discover a proper factor. This backtracking scheme is simple but satisfactorily effective: Among  $10^6$  composite numbers that occurred during an sieving experiment of the RSA155 number, each composite being of up to 86 bits and with prime factors larger than  $2^{24}$ , only 48 had the input number reported as the factor in P-1 stage 1 with  $B_1 = 500$ . Without the backtracking scheme (i.e., processing the full exponentiation by e, then taking a GCD), 879 input numbers are reported as factors instead.

The second stage of P-1 can use exactly the same implementation as the second stage of P+1, by passing  $X_1 = x_1 + x_1^{-1}$  to the stage 2 algorithm.

The stage 2 algorithm for ECM is very similar as well, and they are described together in Section 7.

#### 4.1 P-1 stage 1 performance

Table 1 compares the performance of the P–1 stage 1 implementation for different  $B_1$  values and modulus sizes on AMD Phenom and Intel Core 2 CPUs.

|       | Core 2 |                    | Phenom |                    |  |

|-------|--------|--------------------|--------|--------------------|--|

| $B_1$ | 1 word | 2  words  -2  bits | 1 word | 2  words  -2  bits |  |

| 100   | 3.15   | 6.24               | 2.49   | 4.59               |  |

| 200   | 5.38   | 12.2               | 4.12   | 8.26               |  |

| 300   | 7.28   | 17.2               | 5.51   | 11.3               |  |

| 400   | 9.23   | 22.2               | 6.92   | 14.5               |  |

| 500   | 11.4   | 27.8               | 8.49   | 18.0               |  |

| 600   | 13.2   | 32.7               | 9.83   | 21.0               |  |

| 700   | 15.4   | 38.2               | 11.4   | 24.4               |  |

| 800   | 17.2   | 43.1               | 12.7   | 27.5               |  |

| 900   | 19.4   | 48.5               | 14.2   | 30.9               |  |

| 1000  | 21.4   | 53.8               | 15.7   | 34.1               |  |

Table 1: Time in microseconds for P-1 stage 1 with different  $B_1$  values on 2.146 GHz Intel Core 2 and 2 GHz AMD Phenom CPUs.

## 5 P+1 algorithm

The P+1 algorithm is described in detail in [23]. We recapitulate the basic algorithm here.

The first stage of P+1 computes  $x_1=V_e(x_0) \bmod N$ , where  $x_0\in \mathbb{Z}/N\mathbb{Z}$  is a parameter,  $V_n(x)$  is a degree-n Chebyshev polynomial defined by  $V_n(x+x^{-1})=x^n+x^{-n}$ , and e is a highly composite integer chosen as for the P-1 method. These Chebyshev polynomials satisfy  $V_0(x)=2$ ,  $V_1(x)=x$ ,  $V_{-n}(x)=V_n(x)$ ,  $V_{mn}(x)=V_m(V_n(x))$ , and  $V_{m+n}(x)=V_m(x)V_n(x)-V_{m-n}(x)$ .

$V_{mn}(x) = V_m(V_n(x))$ , and  $V_{m+n}(x) = V_m(x)V_n(x) - V_{m-n}(x)$ . We test for a factor by taking  $\gcd(x_1 - 2, N)$ . If there is a prime p such that  $p \mid N$  and  $p - \left(\frac{\Delta}{p}\right) \mid e$ , where  $\Delta = x_0^2 - 4$  and  $\left(\frac{\Delta}{p}\right)$  is the Legendre symbol, then  $p \mid \gcd(x_1 - 2, N)$ .

Since  $V_{n-m}$  is required for computing  $V_{n+m}$ , these polynomials cannot be evaluated with a simple binary addition chain as in the case of the exponentiation in stage 1 of P-1. Instead, an addition chain needs to be used that contains n-m whenever the sum n+m is formed from n and m. These chains are described in Section 5.1.

The required addition chain for the stage 1 multiplier e is precomputed and stored as compressed byte code, see Section 5.2.

As for P-1, a backtracking scheme is used to avoid finding all factors of N and thus reporting the input number as the factor found. Since factors of 2 in e can easily be handled by  $V_{2n}(x) = V_2(V_n(x)) = V_n(x)^2 - 2$ , they need not be stored in the pre-computed addition chain, and can be processed one at a time. Similarly as in stage 1 of P-1, we remember the previous residue, process one

factor of 2 of e, and if the result is 2 (mod N), meaning that all factors of N have been found, we revert to the previous residue to take the GCD with N. Using the same  $10^6$  composite inputs as for P-1, P+1 with  $B_1 = 500$  reports 117 input numbers as factors with backtracking, and 1527 without.

If stage 1 of P+1 is unsuccessful, we can try to find a factor yet by running stage 2, using as input the output  $x_1$  of stage 1. Our stage 2 is identical for P-1 and P+1, and very similar for ECM, and is described in Section 7.

#### 5.1 Lucas chains

Montgomery shows in [19] how to generate addition chains  $a_0, a_1, \ldots, a_\ell$  with  $a_0 = 1$  and length  $\ell$  such that for any  $0 < i \le \ell$ , there exist  $0 \le s, t < i$  such that  $a_i = a_s + a_t$  and  $a_s - a_t$  is either zero, or is also present in the chain. He calls such chains "Lucas chains." For example, the addition chain 1, 2, 4, 5 is not a Lucas chain since the last term 5 can be generated only from 4 + 1, but 4 - 1 = 3 is not in the chain. The addition chain 1, 2, 3, 5, however, is a Lucas chain. For any positive integer n, L(n) denotes the length of an optimal (i.e., shortest possible) Lucas chain that ends in n.

A simple but generally non-optimal way of generating such chains uses the reduction  $(n,n-1)\mapsto (\lceil n/2\rceil,\lceil n/2\rceil-1)$ . We can compute  $V_n(x)$  and  $V_{n-1}(x)$  from  $V_{\lceil n/2\rceil}(x),\,V_{\lceil n/2\rceil-1}(x),\,V_1(x)=x,$  and  $V_0(x)=2$ . In the case of n even, we use  $V_n(x)=V_{\lceil n/2\rceil}(x)^2-V_0(x),$  and  $V_{n-1}(x)=V_{\lceil n/2\rceil-1}(x)V_{\lceil n/2\rceil-1}(x)-V_1(x)$  and in the case of n odd, we use  $V_n=V_{\lceil n/2\rceil}(x)V_{\lceil n/2\rceil-1}(x)-V_1(x).$  and  $V_{n-1}(x)=V_{\lceil n/2\rceil-1}(x)^2-V_0(x)$  The resulting chain allows processing the multiplier left-to-right one bit at a time, and thus is called binary chain by Montgomery. Each bit in the multiplier adds two terms to the addition chain, except that when processing the final bit, only one of the two values needs to be computed, and if the two most significant bits (MSB) are  $10_b$ , the above rule would compute  $V_2(x)$  twice of which one should be skipped. Any trailing zero bits can be handled by  $V_{2n}(x)=V_n(x)^2-V_0(x)$  at the cost of 1 multiplication each. The length  $L_b(n2^k)$  for the binary Lucas chain for a number  $n2^k$  with n odd is therefore  $2\lfloor \log_2(n)\rfloor -1+k$  if the two MSB are  $10_b$ , or  $2\lfloor \log_2(n)\rfloor +k$  if n=1 or the two MSB are  $11_b$ . Examples are in Table 2. It lists the binary chain, the length  $L_b(n)$  of the binary chain, an optimal chain, and the length L(n) of an optimal chain, for odd n up to 15.

| n             | Binary chain         | $L_b(n)$ | Optimal chain     | L(n) |

|---------------|----------------------|----------|-------------------|------|

| $3 = 11_b$    | 1, 2, 3              | 2        | 1, 2, 3           | 2    |

| $5 = 101_b$   | 1, 2, 3, 5           | 3        | 1, 2, 3, 5        | 3    |

| $7 = 111_b$   | 1, 2, 3, 4, 7        | 4        | 1, 2, 3, 4, 7     | 4    |

| $9 = 1001_b$  | 1, 2, 3, 4, 5, 9     | 5        | 1, 2, 3, 6, 9     | 4    |

| $11 = 1011_b$ | 1, 2, 3, 5, 6, 11    | 5        | 1, 2, 3, 5, 6, 11 | 5    |

| $13 = 1101_b$ | 1, 2, 3, 4, 6, 7, 13 | 6        | 1, 2, 3, 5, 8, 13 | 5    |

| $15 = 1111_b$ | 1, 2, 3, 4, 7, 8, 15 | 6        | 1, 2, 3, 6, 9, 15 | 5    |

Table 2: Binary and optimal Lucas chains for small odd values n

The binary chain is very easy to implement, but produces non-optimal Lucas chains except for very small multipliers. The smallest positive integer where the binary method does not produce an optimal chain is 9, and the smallest such

prime is 13. Montgomery shows that if n is a prime but not a Fibonacci prime, an optimal Lucas chain for n has length  $L(n) \ge r$  with r minimal such that  $n \le F_{r+2} - F_{r-3}$ , where  $F_k$  is the k-th Fibonacci number. Since  $F_k = (\phi^k - \phi^{-k})/\sqrt{5}$  where  $\phi = (1 + \sqrt{5})/2$  is the Golden Ratio, this suggests that if this bound is tight, for large n an optimal chain for n should be about 28% shorter than the binary chain.

In a Lucas chain  $a_0, a_1, \ldots, a_\ell$  of length  $\ell$ , a doubling step  $a_{k+1} = 2a_k$ causes all  $a_i$  with  $k \leq i \leq \ell$  to be multiples of  $a_k$ , and all these terms  $a_i$  are formed using sums and differences only of terms  $a_i, k < j \le \ell$ , see [19]. Such a doubling step corresponds to a concatenation of Lucas chains. For composite  $n = n_1 \cdot n_2$ , a Lucas chain can be made by concatenating the chains of its factors. E.g., for n = 15, we could multiply every entry in the chain 1, 2, 3, 5 by 3 and append it do the chain 1, 2, 3 (omitting the repeated entry 3) to form the Lucas chain 1, 2, 3, 6, 9, 15. Since any Lucas chain starts with 1, 2, every concatenation introduces one doubling step, and every doubling step leads to a chain that is the concatenation of two Lucas chains. Chains that are not the concatenation of other chains (i.e., that contain no doubling step other than 1,2) are called simple chains. For prime n, only simple chains exist. In the case of binary Lucas chains, the concatenated chain is never longer than the chain for the composite value and usually shorter, so that forming a concatenated Lucas chain from chains of the prime factors of n (if known) is always advisable. The same is not true for optimal chains, as shown below.

Optimal chains can be found by exhaustive search for a chosen maximal length  $l_{\text{max}}$  and maximal end-value  $n_{\text{max}}$ . For odd  $n \geq 3$ , a Lucas chain for n always starts with 1,2,3 since a doubling step 2,4 would produce only even values in the remainder of the chain. In the exhaustive search, the Lucas chain  $a_0, \ldots, a_k$  can be extended recursively if  $k < \ell_{\text{max}}$  and  $a_k < n_{\text{max}}$  by adding an element  $a_{k+1} > a_k$  such that the resulting sequence is still a Lucas chain, i.e., satisfying that there are  $0 \leq i, j \leq k$  such that either  $a_{k+1} = 2a_i$ , or  $a_{k+1} = a_i + a_j$  and  $a_i - a_j$  is present in the chain. For each chain so created, we check in a table of best known lengths whether the length k+1 is smaller than the previously known shortest length for reaching  $a_{k+1}$ , and if so, update it to k+1 and store the current chain as the best known for reaching  $a_{k+1}$ . By trying all possible chain expansions, we are certain to find an optimal chain for every  $n \leq n_{\text{max}}$ . This recursive search is very time consuming due to a large number of combinations to try. To reach a worthwhile search depth, the possible chain extensions can be restricted. The last step of an optimal chain is always  $a_l = a_{\ell-1} + a_{\ell-2}$  as otherwise one or both of  $a_{\ell-1}, a_{\ell-2}$  are obsolete, so the table of best known lengths needs to be checked and updated only after such an addition step, and the final recursion level of the search needs to consider only this addition step. Any doubling step  $a_{k+1} = 2a_k$  causes the chain to become the equivalent of a concatenated chain, so during the recursive chain expansion, doubling steps need not be considered. Instead the recursive search produces only the optimal lengths of simple chains. Then for all possible pairs  $3 \leq m \leq n \leq \sqrt{n_{\text{max}}}$ , the length of the chain for mn is updated with the sum of the lengths of chains for m and n, if the latter is shorter. This is repeated until no more improvements occur. After the first pass, the optimal lengths of chains for all n where n has at most two prime factors are known. After the second pass, for all n that contain at most three primes, etc., until after at most  $O(\log(n_{\text{max}}))$  passes optimal lengths for all values are known. Using this

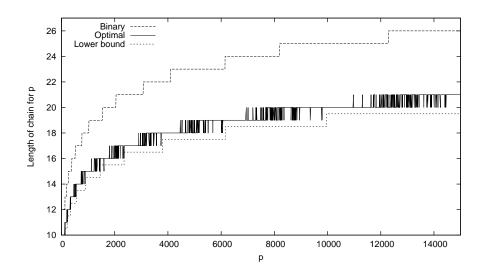

Figure 3: Length of binary and optimal Lucas chains for odd primes p in [100, 15000], and a lower bound on the length for primes that are not Fibonacci primes. The graph for the bound is set 0.5 lower to make it visible. The Fibonacci prime 1597 is seen to undershoot this lower bound.

search method, the minimal lengths of Lucas chains for primes 100 < n < 10000 have been determined, shown in Figure 3. It compares the length of the binary Lucas chain, the optimal Lucas chain and the lower bound on the length of Lucas chains for primes that aren't Fibonacci primes. This lower bound is quite tight, in the examined data L(n) does not exceed it by more than 1. The Fibonacci prime 1597 visibly undershoots this lower bound (as does the smaller Fibonacci prime 233, but it is difficult to see in the graph).

The exhaustive search method is extremely slow and useless for producing addition chains for P+1 or ECM if large  $B_1$  values are desired. Montgomery [19] suggests the algorithm "PRAC," which produces Lucas chains based on GCD chains, noting that a subtractive GCD algorithm for n, r with n > r and  $n \perp r$ always produces a valid Lucas chain for n. However, the resulting Lucas chain has length equal to the sum of the partial quotients in the continued fraction expansion of n/(n-r), and if a large partial quotient appears, the resulting Lucas chain is unreasonably long. He fixes this problem by introducing additional rules for reduction in the GCD chain (rather than just replacing the larger of the two partial remainders by their absolute difference as in a purely subtractive GCD chain) to avoid situations where the quotient of the partial remainders deviates too far from the Golden Ratio, yet satisfying the conditions for a Lucas chain. The great advantage is that PRAC usually produces very good chains and does so rapidly. This way it is feasible to try a few different suitable r for a given n, and for n in the range of interest for P+1 and ECM, one usually discovers an optimal chain this way.

It remains the problem of choosing a suitable  $r \perp n$  to start the GCD chain, hoping to find a (near) optimal chain. Montgomery suggests trying  $r = n - \lfloor n/c \rfloor$  for several irrational c such that the continued fraction expansion of c has small

partial quotients. This way, the partial fraction expansion of n/(n-r) starts with small partial quotients as well. Good choices are the golden Ratio  $c_0 = \phi$ , whose partial quotients all are 1, or numbers with partial quotients all 1 except for one or two 2 among the first 10 partial quotients. The resulting large number of multipliers is not a problem if the Lucas chains are precomputed, but in cases where they are computed on-the-fly during stage 1 of P+1 or ECM, a smaller set of multipliers should be used, say, only those with at most one 2 among the first ten partial quotients.

Even with a large set of  $c_i$  values to try, PRAC in the form given by Montgomery cannot always obtain an optimal chain. The smallest example is n=751 which has two Lucas chains of optimal length L(751)=14:

1, 2, 3, 5, 7, 12, 19, 24, 43, 67, 110, 177, 287, 464, 751 and

1, 2, 3, 5, 8, 13, 21, 34, 55, 68, 123, 191, 314, 437, 751.

Both chains involve an addition step that references a difference that occurred 5 steps before the new term: for the former sequence in the step  $a_8 = 43 =$  $a_7 + a_6 = 24 + 19$ , with difference  $a_7 - a_6 = 5 = a_3$ , and for the latter sequence in the step  $a_{10} = 123 = a_9 + a_8 = 68 + 55$ , with difference  $a_9 - a_8 = 13 = a_5$ . The original PRAC algorithm does not have any rule that allows utilizing a difference that occurred more than 4 steps before the new term and so cannot find either of these two chains. Another, similar case is n = 1087. For primes below 10000, I found 40 cases where PRAC did not find an optimal chain. For the purpose of generating Lucas chains for P+1 and ECM, these missed opportunities at optimal chains are of no great consequence. When using P+1 and ECM as a factoring subroutine in NFS, the  $B_1$  value is often less than 751 so that such cases do not occur at all, and if a greater  $B_1$  should be used, they occur so rarely that adding more rules to PRAC so that optimal chains are found for all primes below  $B_1$  would increase the code complexity of our P+1 or ECM stage 1, which implements each PRAC rule (see Section 5.2), for little gain. For our implementation, this was not deemed worthwhile. For the purpose of finding optimal Lucas chains rapidly, it would be interesting to augment PRAC with a suitable rule for the required addition step  $a_k = a_{k-1} + a_{k-2}$  with  $a_{k-1} - a_{k-2} = a_{k-5}$ , and testing which primes remain such that the modified PRAC cannot find optimal chains.

For composite n=pq, we trivially have  $L(n) \leq L(p) + L(q)$ , since we can concatenate the chain for p and the chain for q. In some cases, a shorter chain for the composite n exists than for the concatenated chains of its factors. The smallest example is  $1219 = 23 \cdot 53$  which has

```

1, 2, 3, 4, 7, 11, 18, 29, 47, 76, 123, 170, 293, 463, 756, 1219

```

as an optimal chain of length 15, while an optimal chain for 23 is 1, 2, 3, 4, 5, 9, 14, 23 of length 7, and for 53 is 1, 2, 3, 5, 6, 7, 13, 20, 33, 53 of length 9.

#### 5.2 Byte code and compression

In implementations of P+1 or ECM such as in GMP-ECM [29] that typically operates on numbers of hundreds to ten-thousands of digits, or in the ECM implementation of Prime95 [28] that operates on number of up to several million digits, the cost of generating good Lucas chains on-the-fly during stage 1 is mostly negligible, except for P+1 on relatively small numbers of only a few hundred digits. However, in an implementation of ECM and especially P+1 designed for numbers of only a few machine words, the on-the-fly generation of Lucas chains would take an inacceptable part of the total run-time. Since in our application of using P+1 and ECM as a factoring sub-routine in NFS, identical stage 1 parameters are used many times over again, it is possible to pre-compute optimized Lucas chains and process the stored chain during P+1 or ECM stage 1.

This raises the question how the chain should be stored. Since the PRAC algorithm repeatedly applies one of nine rules to produce a Lucas chain for a given input, an obvious method is to store the sequence of PRAC rules to apply. The precomputation outputs a sequence of bytes where each byte stores the index of the PRAC rule to use, or one of two extra indices for the initial doubling resp. the final addition that is common to all (near-)optimal Lucas chains. This way, a byte code is generated that can be processed by an interpreter to carry out the stage 1 computations for P+1 or ECM. For each prime to include in stage 1, the corresponding byte code is simply appended to the byte code, which results in a (long) concatenated Lucas chain for the product of all stage 1 primes. If primes are to be included whose product is known to have a better simple Lucas chain than the concatenation of the chains for the individual primes, then their product should be passed to the byte-code generating function.

The byte code generated by PRAC is highly repetitive. For example, byte codes for the PRAC chains for the primes 101, 103, 107, and 109 are

$\begin{array}{lll} 101: & 10,3,3,0,3,3,0,5,3,3,3,11 \\ 103: & 10,3,0,3,3,0,3,3,0,4,3,11 \\ 107: & 10,3,0,3,3,0,3,0,4,3,3,3,11 \\ 109: & 10,3,0,3,0,1,1,3,11 \end{array}$

It is beneficial to reduce redundancy in the byte code to speed up stage 1. The byte code interpreter that executes stage 1 must fetch a code byte, then call the program code that carries out the arithmetic operations that implement the PRAC rule indicated by the code; thus there is a cost associated with each code byte. If the interpreter uses a computed jump to the code implementing each PRAC rule, there is also a branch misprediction each time a code byte is different from the previous one, as current microprocessors typically predict computed jumps as going to the same address as they did the previous time. Some PRAC rules frequently occur together, such as rule 3 follwed by rule 0, so that merging them may lead to simplifications in the arithmetic. In particular, rules 11 (end of a simple chain) and 10 (start of a new simple chain) always appear together, except at the very start and at the very end of the byte code.

These issues are addressed by byte code compression. A simple static dictionary coder greedily translates frequently observed patterns into new codes. The byte code interpreter implements merged rules accordingly. For example, the byte code sequence "3, 0" (for an addition follwed by a swap of variable

contents) occurs very frequently and may be translated to a new code, say 12, and the interpreter performs a merged addition and swap. The codes "11, 10" always occur as a pair and can be substituted except at the very start and the very end of the bytecode, but these two occurrences can be hard-coded into the interpreter, so they do not need to be considered individually at all.

Since we often can choose among several different Lucas chains of equal length for a given stage 1 prime by using different multipliers in PRAC, we can pick one that leads to the simplest compressed code by compressing each candidate chain, and choosing the one that has the smallest number of code bytes and code byte changes.

For comparison, without any compression or effort to reduce the number of code bytes or code changes when choosing PRAC multipliers, the byte code for a stage 1 with  $B_1=500$  consists of 1487 code bytes and 1357 code changes, whereas even with the simple substitution rules described above and careful choice of PRAC multipliers to minimize the number of code bytes and code changes, only 554 code bytes with 435 code changes remain.

#### 5.3 P+1 stage 1 performance

Table 3 compares the performance of the P+1 stage 1 implementation for different  $B_1$  values and modulus sizes on AMD Phenom and Intel Core 2 CPUs.

|       | Core 2 |                    | ${ m Phenom}$ |                    |

|-------|--------|--------------------|---------------|--------------------|

| $B_1$ | 1 word | 2  words  -2  bits | 1 word        | 2  words  -2  bits |

| 100   | 4.04   | 8.44               | 3.45          | 6.30               |

| 200   | 7.50   | 17.3               | 6.32          | 12.3               |

| 300   | 10.3   | 24.6               | 8.69          | 17.2               |

| 400   | 13.4   | 32.5               | 11.2          | 22.3               |

| 500   | 16.6   | 40.7               | 14.0          | 27.9               |

| 600   | 19.5   | 48.0               | 16.4          | 32.8               |

| 700   | 22.8   | 56.6               | 19.1          | 38.5               |

| 800   | 25.7   | 64.0               | 21.5          | 43.5               |

| 900   | 28.9   | 72.4               | 24.2          | 48.9               |

| 1000  | 32.0   | 80.4               | 26.7          | 54.2               |

Table 3: Time in microseconds for P+1 stage 1 with different  $B_1$  values on 2.146 GHz Intel Core 2 and 2 GHz AMD Phenom CPUs, using precomputed Lucas chains stored as compressed byte code.

For comparison, without using byte code compression or choosing the PRAC multipliers to minimize byte code length and number of code changes, on Core 2, P+1 stage 1 with 1 word and  $B_1 = 500$  takes  $20.4 \mu s$  and so is about 22% slower, and with 2 words takes  $50.4 \mu s$  and so is about 24% slower.

## 6 ECM algorithm

The Elliptic Curve Method of factorization was introduced by H. W. Lenstra in 1987 [16]. Whereas P-1 works in the group  $\mathbb{F}_p^*$  of order p-1 and P+1 in a subgroup of  $\mathbb{F}_{p^2}^*$  of order p-1 or p+1, ECM works in the Mordell-Weil group of points on an elliptic curve defined over  $\mathbb{F}_p$ . By Hasse's theorem, the number

of points and therefore the order of the Mordell-Weil group of an elliptic curve over  $\mathbb{F}_p$  is in  $[p+1-2\sqrt{p},p+1+2\sqrt{p}]$ . The number of points on a particular curve depends on both the curve parameters and the field. ECM finds a prime factor p of N if the curve over  $F_p$  has smooth order; the advantage of ECM over previous algorithms such as P-1 and P+1 (which always work in a group of order p-1 or p+1) is that many different curves can be tried, until one with sufficiently smooth order comes along.

Any elliptic curve E over a field K of characteristic neither 2 nor 3 can be defined by the Weierstraß equation

$$y^2 = x^3 + ax + b. (2)$$

This equation defines an elliptic curve if and only if the discriminant  $4a^3 + 27b^2$  does not vanish. The set of points on E consists of the solutions  $(x, y) \in K^2$  of (2), plus the point at infinity  $\mathcal{O}$ .

The group addition law of two points on the curve is defined geometrically by putting a straight line through the two points (or, if the points are identical, the tangent of the curve in that point), taking the line's intersection point with the curve and mirroring it at the x-axis. Since the curve is symmetric around the x-axis, the mirrored point is on the curve, and is the result. If the straight line is vertical, no intersection point exists; in this case the point at infinity is taken as the result. The point at infinity is identity element of the group, adding it to any point results in the same point. The inverse of a point is the point mirrored at the x-axis. This addition law on the points of an elliptic curve defines an Abelian group, see for example [26].

The Weierstraß form of elliptic curves can be used for implementing ECM, but requires a costly modular inverse in the computation of point additions. Montgomery [18] proposes an alternative form of elliptic curve equation in projective coordinates so that its addition law avoids modular inverses, while still keeping the number of required multiplications low. His curves are of form

$$BY^{2}Z = X(X^{2} + AXZ + Z^{2}), (3)$$

with points  $(X:Y:Z) \in K^3$  satisfying (3), where X,Y,Z are not all zero. Two points are identical if  $(X_2:Y_2:Z_2)=(kX_1:kY_1:kZ_1)$  for some  $k \in K, k \neq 0$ . The point at infinity is  $\mathcal{O}=(0:1:0)$ .

Not all elliptic curves over finite fields can be brought into form (3), but we may restrict our ECM implementation to use only these curves. Montgomery describes an addition law for curves of this form. Given two distinct points  $P_1$  and  $P_2$ , we can compute the X and Z-coordinates of  $P_1 + P_2$  from the X and Z-coordinates of  $P_1$ ,  $P_2$  and  $P_1 - P_2$ . Similarly, we can compute the X and Z-coordinates of P and the curve parameters. Surprisingly, the Y-coordinate is not needed in these computations, and can be ignored entirely when using curves in Montgomery form for ECM, and points are commonly written as only (X :: Z) with Y-coordinate omitted. The details of the addition law are found in [18, 10.3.1] or [20, 2.3].

This addition law requires that in order to form the sum of two points, their difference is known or zero. This is reminiscent of the P+1 method where we need  $V_{m-n}(x)$  to compute  $V_{m+n}(x)$  from  $V_m(x)$  and  $V_n(x)$ , and the same Lucas chains used to compute  $V_k(x)$  for integer k in P+1 can be used to compute the multiple kP of a point P on a curve in Montgomery form in ECM.

#### 6.1 ECM stage 1

In stage 1 of ECM, we choose a suitable curve E of form (3) defined over  $\mathbb{Z}/N\mathbb{Z}$ , where N is the integer we wish to factor. Naturally N is composite, so  $\mathbb{Z}/N\mathbb{Z}$  is a ring but not a field, but this has little consequence for the arithmetic of the curve as the only operation that could fail is inversion of a ring element, and an unsuccessful inversion of a non-zero element in  $\mathbb{Z}/N\mathbb{Z}$  reveals a proper factor of N which is the exact purpose of ECM. We often consider the curve  $E_p$  for a prime  $p \mid N$ , which is the curve E reduced modulo p, i.e., E over the field  $\mathbb{F}_p$ .

We then choose a point  $P_0$  on E and compute  $P_1 = e \cdot P_0$  for a highly composite integer e, usually taken to be divisible by all primes and prime powers up to a suitably chosen value  $B_1$ , i.e.,  $e = \text{lcm}(1, 2, 3, 4, \dots, B_1)$ . We hope that for some prime factor p of N, the order of  $P_0$  on  $E_p$  is  $B_1$ -smooth (and thus divides e), since then the point  $P_1$  on  $E_p$  will be the point at infinity (0 :: 0) so that  $P_1$  has Z-coordinate  $P_1$ 0 (mod  $P_2$ 1) and  $P_2$ 2 (gcd( $P_2$ 1).

To find a point  $P_0$  on E over  $\mathbb{Z}/N\mathbb{Z}$ , we choose a point of E over  $\mathbb{Q}$  and map it to  $\mathbb{Z}/N\mathbb{Z}$ . The point over  $\mathbb{Q}$  must not be a torsion point, or  $P_0$  will have identical order on  $E_p$  for all  $p \mid N$  so that  $P_1$  is the point at infinity either for all  $E_p$  or for none, producing only the trivial factorizations N or 1.

By careful selection of the curve E we can ensure that number of points of  $E_p$  is a multiple of 12 or 16, significantly increasing the probability that the order of  $P_0$  is smooth. The choice of E is described in Section 6.2.

The computation of  $P_1 = e \cdot P_0$  on E is carried out by use of pre-computed Lucas chains, similarly as in the P+1 algorithm. The selection of near-optimal Lucas chains for ECM is described in Section 6.3.

If stage 1 of ECM is unsuccessful, we try stage 2 where we hope to find a prime p such that the order of  $P_0$  on  $E_p$  factors into primes and prime powers up to  $B_1$ , except for one bigger (but not too much bigger) prime q. Our stage 2 is very similar for P-1, P+1, and ECM and is described in Section 7.

#### 6.2 Choice of curve

In a letter to Richard Brent, Hiromi Suyama [27] showed that curves of form (3) over  $\mathbb{F}_p$  always have group order divisible by 4, and also showed a parametrization that ensures that the group order is divisible by 12, which Brent describes in [3]. This parametrization generates an infinite family of curves over  $\mathbb{Q}$  which can be used to generate a large number of distinct curves modulo N. For a given integer parameter  $\sigma \neq 0, 1, 3, 5$ , let

$$u = \sigma^2 - 5, v = 4\sigma,$$

$X_0 = u^3, Z_0 = v^3 \text{ and } A = \frac{(v-u)^3(3u+v)}{4u^3v} - 2.$  (4)

Then the point  $(X_0 :: Z_0)$  is on the curve (3) with parameter A. The same parametrization is used by GMP-ECM [29, 1] and Prime95 [28].

Montgomery showed in his thesis [20] how to choose curves of form 3 such that the curve over  $\mathbb{Q}$  has a torsion subgroup of order 12 or 16, leading to group order divisible by 12 or 16, respectively, when the curve is mapped to  $\mathbb{F}_p$  for almost all p.

For curves with rational torsion group of order 12 he uses

$$t^{2} = \frac{u^{2} - 12}{4u}, a = \frac{t^{2} - 1}{t^{2} + 3}$$

$$X_{0} = 3a^{2} + 1, Z_{0} = 4a \text{ and } A = \frac{-3a^{4} - 6a^{2} + 1}{4a^{3}},$$

(5)

where  $u^3-12u$  is a rational square. The solutions of  $v^2=u^3-12u$  form an elliptic curve of rank 1 and 2-torsion over  $\mathbb{Q}$ , with generator (-2,4) and 2-torsion point (0,0). However, adding the torsion point or not seems to produce isomorphic curves for ECM, so we ignore it. Hence for a given integer parameter k>1 we can compute suitable values of u and v by computing  $k\cdot (-2,4)$  on  $v^2=u^3-12u$ . We can then let t=v/(2u). This produces an infinite family of curves over  $\mathbb{Q}$ .

Curves with torsion 16 and positive rank over  $\mathbb{Q}$  are more difficult to generate, see [20, 6.2] for details. We currently implement only one such curve with  $X_0 = 8$ ,  $Z_0 = 15$ , and A = 54721/14400.

These parametrizations ensure that the group order is divisible by 12 or 16, respectively, but the resulting group order of the curve over  $\mathbb{F}_p$  does not behave like an integer chosen uniformly at random from the integers that are multiples of 12 or 16, respectively, in the Hasse interval around p. In particular, the average valuation of 2 in the group order for curves with rational torsion 12 is 11/3, slightly higher than 10/3 for curves in Brent-Suyama parametrization (which have rational torsion 6), making them somewhat more likely to find factors.

Very small  $\sigma$ -values for the Brent-Suyama parametrization lead to curves with simple rationals for the point coordinate and curve parameter, and very small k-values for Montgomery's parametrization for curves with rational torsion 12 lead to simple rationals for a, see Table 4. These rationals can be mapped to  $\mathbb{Z}/N\mathbb{Z}$  easily, as the denominators are highly composite integers so that the required divisions modulo N can be done by the methods of Section 3.4 and a few multiplications.

When factoring cofactors after the sieving step of NFS into large primes, only very few curves are required on average since the primes to be found are relatively small, and with an early-abort strategy, only the first few curves work on larger composites where arithmetic is more expensive. In spite of the small number of curves with such simple rationals as curve parameters, it is useful to implement them as special cases.

Table 4: Some elliptic curves chosen by the Brent-Suyama parametrization with group order divisible by 12, and by Montgomery's parametrization with rational torsion group of order 12.

#### 6.3 Lucas chains for ECM

In principle, Lucas chains for ECM can be chosen exactly as for P+1. However, a subtle difference exists: in P+1, the cost of a doubling  $V_{2n}(x) = V_n(x)^2 - 2$  is identical to that of an addition  $V_{m+n}(x) = V_m(x)V_n(x) - V_{m-n}$  if  $V_{m-n}$  is

known and a squaring is taken to have the same cost as a multiplication. This way, the cost of a Lucas chain depends only on its length.

In ECM, the cost of a point doubling usually differs from the cost of an addition of distinct points. In the addition rules given by Montgomery, a doubling takes 5 modular multiplications of which 2 are squarings, whereas an addition of distinct points takes 6 modular multiplications of which again 2 are squarings.

These different costs can be taken into account when choosing Lucas chains. For example, to multiply a point by 7, we can choose between the chains 1, 2, 3, 5, 7 or 1, 2, 3, 4, 7 of equal length. In the former, all additions except for the initial doubling 1, 2 are additions of distinct values. In the latter, we can produce 4 by doubling 2, so that this Lucas chain would save 1 modular multiplication in the elliptic curve arithmetic.

When generating Lucas chains with PRAC using several multipliers, we can choose the best chain not according to its length but by the cost of the arithmetic performed in each PRAC rule that is used to build the chain.

The speedup in practice is relatively small: with two-word modulus, ECM stage 1 with  $B_1 = 500$  is about 1% faster when counting the cost of a doubling as 5/6 of the count of an addition when choosing Lucas chains. Still, this improvement is so simple to implement that it may be considered worthwhile.

As for P+1, the precomputed addition chains are stored as byte code that describes a sequence of PRAC rules to apply. Code compression may be used to reduce the overhead in the byte code interpreter, but since the elliptic curve arithmetic is more expensive than in the case of P+1, the relative speedup gained by compression is much smaller.

#### 6.4 ECM stage 1 performance

Table 5 compares the performance of the ECM stage 1 implementation for different  $B_1$  values and modulus sizes on AMD Phenom and Intel Core 2 CPUs.

|       | Core 2 |                    | Phenom |                    |

|-------|--------|--------------------|--------|--------------------|

| $B_1$ | 1 word | 2  words  -2  bits | 1 word | 2  words  -2  bits |

| 100   | 11.8   | 35.6               | 9.33   | 24.4               |

| 200   | 24.5   | 77.9               | 19.4   | 52.6               |

| 300   | 35.3   | 113                | 27.8   | 76.0               |

| 400   | 46.7   | 151                | 36.6   | 101                |

| 500   | 58.7   | 190                | 46.2   | 127                |

| 600   | 69.6   | 226                | 54.6   | 151                |

| 700   | 82.3   | 266                | 64.5   | 178                |

| 800   | 93.6   | 302                | 72.4   | 202                |

| 900   | 105    | 342                | 82.5   | 229                |

| 1000  | 117    | 381                | 92.0   | 255                |

Table 5: Time in microseconds for ECM stage 1 with different  $B_1$  values on 2.146 GHz Core 2 and 2 GHz AMD Phenom CPUs

## 7 Stage 2 for P-1, P+1, and ECM