# A Multistandard Simultaneous Reception Front-End Architecture

Ioan Burciu, Guillaume Villemaud, Jacques Verdier, Matthieu Gautier

## ▶ To cite this version:

Ioan Burciu, Guillaume Villemaud, Jacques Verdier, Matthieu Gautier. A Multistandard Simultaneous Reception Front-End Architecture. COST2100 Pervasive Mobile & Ambient Wireless Communications, Oct 2008, Lille, France. inria-00412106

# HAL Id: inria-00412106 https://inria.hal.science/inria-00412106v1

Submitted on 27 Nov 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# EUROPEAN COOPERATION IN THE FIELD OF SCIENTIFIC AND TECHNICAL RESEARCH

COST 2100 TD(08)658 Lille, France 2008/Oct/06-08

| <br>      |  |

|-----------|--|

|           |  |

| EURO-COST |  |

SOURCE: CITI, Centre d'Innovarion en Telecom et Intégration de services,

INSA Lyon,

France

## A Multistandard Simultaneous Reception Front-End Architecture

Ioan Burciu, Guillaume Villemaud, Jacques Verdier, Matthieu Gautier CITI/INRIA 21, avenue Jean Capelle 69621 Villeurbanne

France

Phone: + 39-051 20 93 817

Fax: + 39-051 20 93 540

Email: <u>ioan.burciu@insa-lyon.fr</u>

Abstract—In this paper, we address the architecture of multistandard simultaneous reception receivers and we aim to reduce the complexity of the analog front-end. To this end we propose an architecture using the double orthogonal translation technique in order to multiplex two signals received on different frequency bands. A study case concerning the simultaneous reception of 802.11g and UMTS signals is developed in this article. Theoretical and simulation results show that this type of multiplexing does not significantly influence the evolution of the signal to noise ratio of the signals.

#### I. INTRODUCTION

NOWADAYS the market presents a real interest in the development of telecommunication networks based on radiofrequency systems. Along with the already existing ones, new standards (WiFi, WiMax or the 3G standards) allow the operators to offer new and better services in terms of speed, quality and availability. Consequently, in order to handle this important diversity of telecommunication techniques, there is a growing interest in developing new frontend architectures capable of processing several standards.

For the multistandards research domain we can distinguish two different categories of receivers: non-simultaneous receivers using switching techniques [1][2][3][4][5] and simultaneous receiving receivers. The state of the art of the multistandard simultaneous reception architectures uses the front-end stack-up technique - each chain being dedicated to the reception of only one standard. Nonetheless, this architecture is characterized by some inconveniences such as the bad complexity-performance trade-off, but also the price and the physical size.

The goal of the architecture proposed in this paper, subject of a patent pending [6], is to answer a multistandard simultaneous reception need generated by the ambient or sensor network domain, while also not being restricted to that alone. In order to answer to this need we chose to study the simultaneous reception of an 802.11g signal and a UMTS signal using only one front-end.

The structure assessed in this article implements a novel and innovating multistandard simultaneous receiving architecture using a single front-end. Moreover, the baseband signal has the same bandwidth as the one of the state of the art front-end stack-up structure. This architecture uses the double orthogonal translation technique [8][9] in order to multiplex the two standards signals by completely overlapping their spectrums at a intermediate frequency. After the second IQ translation the baseband signals are digitized, and then are processed by a signal processing block that separately demultiplexes the baseband component of the two standards. A key point of this structure is the orthogonal mismatches of the translation blocks, which can be meanwhile digitally mitigated by a proper signal processing [10][11][12]. In addition, the image frequency impairment is no longer a problem as each of the standards occupies the image band of the other.

This paper consists of three parts. Following this introduction, section II describes the double IQ principle, along with the implantation of this technique in a novel

multistandard front-end architecture, based on orthogonal multiplexing of its two input branches. The last section details the implementation of such a receiver by specifying its functionality and by presenting some significant simulation results. Finally, conclusions of this study are drawn and the follow-up to this work is provided.

#### II. MULTI-BAND RECEIVER USING A DOUBLE IQ STRUCTURE

#### A. The double IQ technique

In wireless telecommunications, the integration of IQ baseband translation structures in the receiver chain has become a common procedure. The simple IQ architecture is usually used in the receiver front-end design in order to reduce the bandwidth of baseband signals treated by the ADC.

Meanwhile, this orthogonal frequency translation technique is also used to eliminate the image frequency default during the translation steps of heterodyne front-end architectures [9], [10]. The image frequency rejection technique consists in using two orthogonal frequency translations of the signal. In order to realize this double translation, three IQ translation blocks are needed. After the double orthogonal translation, a signal processing block uses the four baseband signals to eliminate the image frequency signal. This type of image rejection structure relies on the advantage of orthogonalizing the useful signal  $s_u(t)$  and the signal occupying its image frequency band  $s_{Im}(t)$ . Even though the spectrums of the two signals are completely overlapped after the first frequency translation, this orthogonalization allows the baseband processing to theoretically eliminate the image frequency component while reconstructing the useful one.

This paper assesses the use of the double orthogonal translation technique to develop a multi-standard simultaneous reception front-end. In fact, the main idea refers to a technique allowing the reconstruction, in the baseband domain, of the signal from the image band. This technique relies on a signal processing parallel to that dedicated to the reconstruction of the useful signal. If the image band of the useful signal is occupied by a second useful signal, we can consider that this type of structure can simultaneously treat the two useful signals. In order to fulfill this image band condition a clever choice has to be made concerning the frequency of the local oscillator used during the first orthogonal frequency translation.

In order to realize a theoretical study of this type of multistandard reception dedicated double IQ structure, the useful components  $s_1(t)$  and  $s_2(t)$  of the input s(t) are considered as RF domain signals. Therefore these signals can be modeled by the following:

$$s_1(t) = I_1(t)\cos(2\pi f_1 t) + Q_1(t)\sin(2\pi f_1 t),$$

(1)

$$s_2(t) = I_2(t)\cos(2\pi f_2 t) + Q_2(t)\sin(2\pi f_2 t),$$

(2)

where  $\{I_k(t)+jQ_k(t), k=(1,2)\}$  are their baseband complex envelope.

Each of the three IQ translation structures multiplies the input signals by two 90° shifted signals provided by the frequency synthesizers. The first IQ block frequency

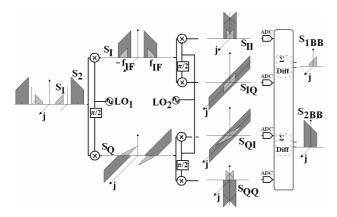

Fig. 1 Spectral evolution of the signals in a double IQ structure

translation multiplies the input signal s(t) with two 90° shifted sinusoids, generated by a local oscillator having a frequency  $f_{LOI}=(f_I+f_2)/2$ . This choice of the oscillator frequency fulfils the image band condition: each of the two signals must occupy the image frequency band of the other before the first orthogonal frequency translation.

By taking into account this oscillator's frequency condition, the two output signals of the first IQ translation structure  $s_I(t)$  and  $s_O(t)$  can be defined by:

$$\begin{split} s_I(t) &= LP[\cos(2\pi\!f_{LOI}t)s(t)] \\ &= [I_1(t) + I_2(t)] \frac{\cos(2\pi\!f_{I\!F}t)}{2} + [Q_1(t) - Q_2(t)] \frac{\sin(2\pi\!f_{I\!F}t)}{2} \\ s_Q(t) &= LP[\sin(2\pi\!f_{LOI}t)s(t)] \\ &= [I_1(t) - I_2(t)] \frac{\sin(2\pi\!f_{I\!F}t)}{2} + [Q_1(t) + Q_2(t)] \frac{\cos(2\pi\!f_{I\!F}t)}{2} \\ \text{where } \ LP[.] \ \ \text{stands for low-pass filter and where the} \end{split}$$

where LP[.] stands for low-pass filter and where the intermediate frequency  $f_{IF} = f_{I} - f_{LOI} = f_{LOI} - f_2$ . These equations highlight the overlapping of the useful spectrum and the image band spectrum after the intermediate frequency translation, as shown in  $Fig.\ I$ .

In the second IQ frequency translation step, each of the two signals  $s_I(t)$  and  $s_Q(t)$  are separately multiplied by two 90° shifted sinusoids. As the frequency of the local oscillators is chosen to be  $f_{LO2}=f_{IF}$ , the four output signals of this second IQ translation block are translated in the baseband domain and are given by the equations:

$$\begin{split} s_{II}\left(t\right) &= LP\left[\cos(2\pi f_{IF}\,t)\,s_{I}\left(t\right)\right] = \frac{I_{1}(t)}{4} + \frac{I_{2}(t)}{4}\,,\,\,(5)\\ s_{IQ}\left(t\right) &= LP\left[\sin(2\pi f_{IF}\,t)\,s_{I}\left(t\right)\right] = \frac{Q_{1}(t)}{4} - \frac{Q_{2}(t)}{4}\,,\,\,(6)\\ s_{QI}\left(t\right) &= LP\left[\cos(2\pi f_{IF}\,t)\,s_{Q}\left(t\right)\right] = \frac{Q_{1}(t)}{4} + \frac{Q_{2}(t)}{4}\,,\,\,(7)\\ s_{QQ}\left(t\right) &= LP\left[\sin(2\pi f_{IF}\,t)\,s_{Q}\left(t\right)\right] = \frac{I_{1}(t)}{4} - \frac{I_{2}(t)}{4}\,.\,\,(8) \end{split}$$

The four output signals contain the multiplexed baseband translated information of the two RF components  $s_I(t)$  and  $s_2(t)$ . For a mono-standard image rejection front-end architecture, only the useful component  $s_u(t)$  is interesting and therefore reconstructed by a single signal processing. But both of the baseband translated information can be separately demultiplexed by two dedicated signal processing, detailed by:

$$s_{1BB}(t) = s_{II}(t) + s_{QQ}(t) + j[s_{QI}(t) - s_{IQ}(t)], (9)$$

$$s_{2BB}(t) = s_{II}(t) - s_{QQ}(t) + j[s_{IQ}(t) + s_{QI}(t)]. (10)$$

Each of these series of operations reconstructs one of the two components while eliminating the other. In fact, by developing (9) and (10) using (5), (6), (7) and (8), we obtain:  $\{s_{kBB}(t)=I_k(t)+jQ_k(t), k=(1,2)\}$ , the same baseband characterizations as those of the RF input signals  $s_I(t)$  and  $s_2(t)$ .

Usually, for the mono-standard image rejection architecture, only one of the treatment techniques is implemented in the analog domain so that only two signals have to be digitized instead of four in the case of a digital signal processing. But, if we wish to realize simultaneously the two dedicated signal processing, the four baseband signals have to be digitalized and then used to do the demultiplaxation step in the digital domain.

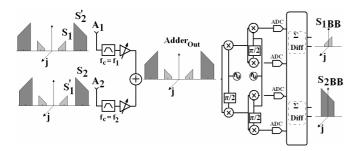

### B. Theoretical consideration on the implantation of multiband double IQ architecture

All the studies presenting the integration of the double IQ technique use this method in order to cancel the image frequency default in a mono-standard reception front-end. Here we propose implement it in a novel multistandard simultaneous reception front-end architecture (Fig.2). The input stages of the front-end are parallelized, each branch being dedicated to the processing of only one frequency band. This way, the signal from the two different frequency bands can be separately received by a dedicated antenna, filtered and amplified by dedicated RF filters and LNAs respectively. Another key element of this structure is the power control realized in parallel for the two signals. As it will be shown below this parallel power control step allows a better rejection complementary standard during the digital of demodulation. Once the signals are properly filtered and amplified, an addition step process the two signal in order to generate the input signal of the double IQ structure. After the double IQ frequency translation the four baseband signals are digitized and the two dedicated signal processing demultiplex the two useful signals.

As presented in the previous section, the double IQ technique allows, for ideal orthogonal mismatches conditions, a theoretically perfect rejection of the image band while reconstructing the useful signal. For the receivers using heterodyne process, the image rejection ratio is the ratio of the intermediate frequency signal level produced by the desired input signal to that produced by the image band signal. For a double IQ structure, the image rejection ratio (IRR) depends on the gain and phase mismatches between the two branches of the IQ translation structures, and especially on the mismatches of the first one as the frequency translation is generally the highest. The orthogonal mismatches are caused by design and layout defaults such as different line length between the two branches and non identical mixers, which generate phase and respectively gain mismatches [12]. Supposing that the first IQ stage has a gain mismatch  $\Delta A$  and a phase mismatch  $\Delta \theta$ , the final IRR can be modeled by the equation below [11].

Fig. 2 Multiband simultaneous reception architecture using the double IQ structure

$$IRR(dB) = 10 \log \left[ \frac{1 + (1 + \Delta A)^2 + 2(1 + \Delta A)\cos(\Delta \theta)}{1 + (1 + \Delta A)^2 - 2(1 + \Delta A)\cos(\Delta \theta)} \right]$$

(11)

For a receiver implementing this kind of architecture, the image band rejection is accomplished through a combination between the front-end's input elements: antenna, external RF filter, LNA (Low Noise Amplifier) on one hand, and the image rejection technique achieved by the double-conversion configuration on the other hand. The state of the art front-end's input elements can realize an image frequency rejection of up to 40 dB depending on the choice of the intermediate frequency.

In order to provide sufficiently high image rejection to meet, for example, the WLAN 802.11g standard, an IRR of at least 80 dB is needed. In order to achieve this 80 dB IRR it is shown [11] that only 0.01 dB gain mismatch and 0.1 degrees of phase mismatch are allowed for each of the IQ blocks—this way, the remaining 40 dB of IRR are realized using the image rejection technique.

This high degree of matching is not achievable using only good design and layout techniques, additional digital signal treatment techniques have to be employed in order to achieve this performance. One of these techniques has been developed in the digital domain using an LMS (Least mean square) algorithm [11]. The results show an image rejection ratio due to the front-end architecture reaching up to 70 dB. Therefore we can assume that the total IRR of a classical double IQ image rejection receiver reaches 110 dB. This level of image rejection allows the elimination of the external band-pass filter from the receiver's design.

In comparison to the single antenna double IQ image rejection architecture, for the multiband architecture assessed here, the addition of the parallel branches' outputs generates supplementary parasitic signals that can degrade the final SNR (Signal to Noise Ratio) of the two useful signals. Each of the two antennas receives a signal made of two components –  $s_I(t)+s_2(t)$  for the  $A_I$  antenna and  $s'_I(t)+s_2(t)$  for the  $A_2$  antenna, where  $s_I(t)$  and  $s'_I(t)$  are the same transmitted signals after two different propagation channels, as well as  $s_2(t)$  and  $s'_2(t)$ . The parasitic components  $s'_2(t)$  and  $s'_I(t)$  are filtered by the input stage of each dedicated branch - antenna, RF band filter, LNA - but even when attenuated like this, these components have to be taken into account while studying the

useful signals' SNR evolution.

In fact, the output signal of the adder is mainly composed of four components:

$$Adde_{out}(t) = G_1 \cdot s_1(t) + G_2 \cdot s_2(t) + G_1 \cdot s_1'(t) + G_2 \cdot s_2'(t)$$

(12)

where the coefficients  $G_1$ ,  $G_2$ ,  $G'_1$  and  $G'_2$  are the gains that the two input parallel branches of the receiver induce to each of the four components.

In order to evaluate the SNR evolution of the useful signal  $s_{IBB}(t)$  after the demultiplexing stage, the evolution of the parasitic signals  $s'_{I}(t)$ ,  $s_{2}(t)$  and  $s'_{2}(t)$  compared to that of the useful signal  $s_{I}(t)$  have to be taken into account:

- The  $s'_2(t)$  signal is attenuated by the input blocks of the branch dedicated to the treatment of  $s_1(t)$ . The state of the art of the antennas, of the RF band filters and of the LNA can generate a 40 dB rejection of  $s'_2(t)$  for an architecture such as that of Fig. 2. In addition to these 40 dB of initial rejection, the double IQ structure, along with the LMS digital processing, will achieve up to 70 dB of signal rejection from the image band of the useful signal. This means a rejection of up to 110 dB of the parasitic signal  $s'_2(t)$ .

- The  $s_2(t)$  signal undergoes up to 70 dB of rejection compared to the useful signal  $s_I(t)$ . This rejection is generated by the double IQ structure, similar to that of  $s'_2(t)$  as the two signals occupy the same frequency band after the addition of the two branches. In addition to this rejection, another element to be taken into account, when studying the influence of  $s_2(t)$ on the SNR of  $s_I(t)$ , is the dedicated power control stage. In fact the worst case scenario is when  $s_1(t)$  is at its lowest power level and the parasitic signal  $s_2(t)$  is at its highest. This means that this is the case when  $s_2(t)$  has its highest effect on the degradation of the useful signal. In this case, the power control will amplify  $s_1(t)$  compared to  $s_2(t)$  before the addition step, which means that the influence of the parasitic signal on the useful signal is decreased. The state of the art of the power controls [14] can provide up to 35 dB between minimum and maximum amplification. Therefore, for the worst case scenario, it can be considered that the  $s_2(t)$  signal undergoes a 105 dB rejection compared to the useful signal  $s_1(t)$ .

- The  $s'_I(t)$  signal, along with  $s_2(t)$ , is one of the two components of the radiofrequency signal received by the  $A_2$  antenna. This signal doesn't undergo a rejection due to the double IQ structure as it occupies the same frequency band as the useful signal after the addition step. The only supplementary rejection that  $s'_I(t)$  will undergo compared to the useful signal  $s_I(t)$  is realized by the input elements of the front-end. In fact, as this signal is received by the branch dedicated to  $s_2(t)$ , the input elements will realize an attenuation of up to 40 dB. As  $s'_I(t)$  and the useful signal  $s_I(t)$  are not received by the same antenna, even if they are generated by the same transmitter, a phase shift and a gain shift between the two appears during the hertzian transmission.

For an AWGN (Additive White Gaussian Noise) transmission channel, the phase shift between the two signals can go from 0 to 360 degrees, but the gain shift can be ignored. For this case, where the two signals  $s'_I(t)$  and  $s_I(t)$  have the same power level at the input of the front-end, the 40 dB of attenuation of the parasitic signal  $s'_I(t)$  achieved before the addition step assures a 40 dB SNR of the useful signal  $s_I(t)$  in the baseband domain after the digital signal processing. This SNR level insures a very good reception quality.

In the case of a multipath channel, where the gain shift as well as the phase shift can not be ignored, a new solution can be implemented. It consists in using a digitally controlled RF phase shifter that will cancel the phase shift between  $s'_I(t)$  and  $s_I(t)$  before the addition step. This way  $s'_I(t)$  is no more a parasite, but a useful component during the digital signal processing that reconstructs the  $s_I(t)$  signal. This solution will be developed in a future document.

Considering all this arguments concerning the additional parasitic components, it can be considered that the SNR evolution of the useful signal is the same as that of a signal treated by a classic mono-standard receiver. Therefore the single front-end multistandard simultaneous reception structure presents similar performance as a front-end stack up structure.

Meanwhile, a complexity comparison study reveals that the single front-end structure is less complex, much more compact and presents a higher on-chip integration level. The number of components is smaller because of the use of a single local oscillator for the first frequency translation compared to the two dedicated oscillators of the front-end stack-up receiver. Furthermore, the greatest advantage of the single front-end receiver is the elimination of the image rejection RF filters. In fact these external components, used to mitigate the impact of the image band signal, can not be integrated on-chip. In the proposed architecture, these components are replaced by a cheaper, on-chip and especially more flexible signal treatment. In the following section, a validation of the theoretical result will be presented.

#### III. IMPLEMENTATION AND PERFORMANCE

The high image rejection multistandard receiver using a double IQ front-end architecture allows the simultaneous reception of two different frequency bands. In order to validate the theoretical study, a first implementation was made and simulated using the ADS software (Advanced Design System) provided by Agilent Technologies [13]. The selection of the standards used for this implementation was influenced by their complexity and their deployment as well as by their complementarities in terms of range. These parameters, along with a direct utility of such a structure in the sensor network domain, directed our choice towards the 802.11g and the WCDMA-FDD standards. Regarding this choice, an important point that should be underlined is the implementation constraints imposed by the standards dynamics, but especially by those of the WCDMA-FDD. These dynamics constraints make this standards choice implementation the most delicate.

In order to realize a good performance comparison between the multistandard single frond-end receiver and the front-ends stack-up, the blocks used during the simulation have the same

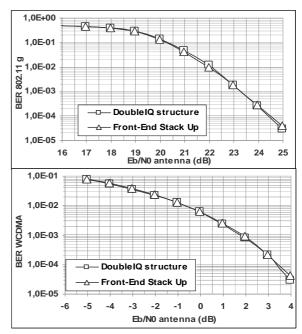

Fig. 3 802.11g and WCDMA BER evolution during multistandards simultaneous reception using two types of receivers: the classical front-end stack-up and the multistandards single front-end receiver

TABLE I

METRICS USED FOR THE SIMULATION OF THE MULTISTANDARD SINGLE

FRONT-END RECEIVER

| Symbol           | SI UNIT | VALUE |

|------------------|---------|-------|

| NF               | dB      | 6     |

| IIP3             | dBm     | -12   |

| Maximal Gain AGC | dB      | 25    |

| Minimal Gain AGC | dB      | -10   |

typical metrics (gain, noise figure, 1 dB compression point, third order interception point) for both cases. By taking into account all these metrics, a global characterization of the multistandard single front-end receiver is made (*Table 1*).

During this study, it will be considered that the metrics of the blocks used by the two parallel input branches are similar and therefore the performance offered by the front-end for the two standards are identical in terms of noise figure, gain and third order intercept point.

The first results (*Fig.3*) represent the evolution of the two standards BER (Bit Error Rate) depending on their SNR level at the antenna. This BER evolution was observed using both the multistandard single front-end and the front-end stack-up structures as receivers. The wireless transmission channel was chosen to be AWGN while the translation blocks are considered to be ideal in terms of IQ mismatch. During the simulation of the reception of one of the standards the antenna power level of the complementary standard is set to the maximum level so that its parasitic influence is the highest.

Under these conditions the two standards BER evolutions are almost identical for both types of receivers. In fact, using the multistandard single front-end receiver allows the complete rejection of one of the standards during the digital final signal processing as the IQ mismatches are ignored for the moment.

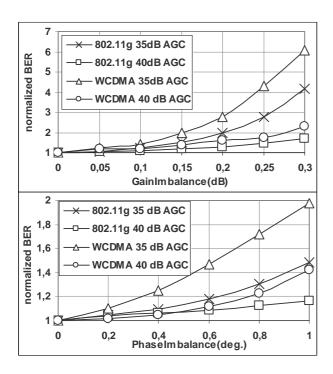

Fig. 4 802.11g and WCDMA BER evolution versus gain and phase imbalance of the IQ translation blocks. Two series are dedicated to each BER evolution for an AGC gain dynamics of 35 and respectively 40 dB

The theoretical study underlines the importance of the IQ mismatches for the performance of a receiver using a double orthogonal translation. Indeed, for this type of receiver, it is necessary to realize a good rejection of the image frequency band, which is occupied by the complementary standard. In fact, this rejection relies on two different methods: the gain control realized in the RF domain and the image band rejection realized by the IQ structure, depending on the IQ mismatches. In order to estimate the impact of the orthogonal mismatches on the evolution of the two standards BER a second set of simulations are realized. The metrics of the receiver used during these simulations are the same as those presented in Table 1, except for the gain dynamics of the AGC which take two different values of 35 dB and 40 dB. Concerning the power level of the signals at the antenna, while testing the influence of the IQ mismatches on the BER of one of the standards, the power level of the complementary standard is maximal. Meanwhile, the power level of the concerned standard is at its reference level (the minimum power level that ensures a certain service quality). For our study case, the concerned standard power level leads to a 10<sup>-3</sup> level of BER, when considering ideal IQ mismatch conditions.

For each standard, two normalized BER evolution are presented in *Fig. 4*, for an AGC gain dynamics of 35 and respectively 40 dB. Depending on the AGC dynamics the complementary signal will be attenuated by a certain amount at the input of the antenna compared to the useful signal. Another rejection step is then realized by the IQ structure, but this one is dependent of the orthogonal mismatches.

Results show that the BER performance of the receiver depends on one hand of the AGC gain dynamics and on the other hand on the orthogonal IQ mismatches. For an AGC gain dynamics varying from the state of the art 35 dB to 40 dB, the

BER can triple for the same power levels and mismatch configuration. It can also be observed that, under significant orthogonal mismatches conditions, the influence of the complementary standard (at its maximum power level) on the useful one's SNR leads to a BER six times higher.

The graphs of Fig. 4 rely on simulations of the multistandard receiver architecture which does not integrate the digital signal processing (LMS) dedicated to the mitigation of the orthogonal mismatches [11]. The use of these signal processing techniques reduces the final influence of the complementary signal on the useful one's SNR. It can be considered that the final orthogonal mismatches are reduced to an equivalent level of 0.01 dB of gain mismatch and 0.1 degrees of phase mismatch, corresponding to a 70 dB rejection of the complementary signal from the image frequency band. For these levels of orthogonal mismatches, the influence of the complementary standard on the useful one can be ignored as it can be observed on the results shown in Fig. 4. Therefore the theoretical study concerning the rejection of the parasitic signals presented in section II is validated here.

#### IV. CONCLUSIONS

In this article, a novel multistandard simultaneous reception architecture was presented. Expected performance of its implementation has been presented for a particular study case - simultaneous reception of two signals using the 802.11g and UMTS standards. Compared to the stack-up dedicated frontends structure, this architecture uses an innovating double IQ multiplexing technique in order to use a unique front-end to receive both standards. In addition to the complexity decrease offered by the use of a single front-end, the signal processed by the analog part of the receiver presets an excellent spectral efficiency as the two standards spectrums are overlapped after the first IQ stage. Knowing that the power consumption of the analog part of the receiver is directly dependent on the bandwidth of the signal, the excellent complexity-powerperformance trade-off becomes obvious. Despite the use of a demultiplexing block in the digital domain, the power consumption of the receiver is lower compared to that of the actual state of the art. The key point of this structure is the rejection of the complementary standard during the demultiplexing stage. As a matter of fact, the rejection level depends of the orthogonal mismatches of the frequency translation blocks; a complete study of their influence has been presented.

The issues that still have to be addressed turn around the implementation of a digital processing used to mitigate the IQ impairments. Another interesting idea concerns a possible multi-antenna multistandard simultaneous reception technique using the principles of the architecture assessed in this article.

#### REFERENCES

- D. Evans, D. Raynes and A. Payne, "Development and Simulation of a Multi-standard MIMO Transceiver (Report style)", FLOWS WP4 program, Deliverable Number: D20, IST-2001-32125, Nov. 2004.

- [2] S-G Lee, N.-S. Kim, S.-M. Oh, J.-K. Choi and S.-C. Kim, "A Dual-Band Receiver Architecture For PCS and IMT-2000", Proc. 2nd IEEE Asia-Pacific Conference on ASICs, pp.235 238, Aug. 2000.

- [3] B. McFarland, A. Shor and A. Tabatabaei, "A 2.4 & 5 GHz Dual Band 802.11 WLAN Supporting Data Rates to 108 MB/s", IEEE Gallium Arsenide Integrate Circuit Symposium, pp.1-14, Oct. 2002.

- [4] D. Belot, B. Bonhoure, D. Saias and N. Bertholet, "A DCS1800/GSM900 RF to Digital fully Integrated Receiver in SiGe 0.35um BiCMOS", Proc. 2001 BIPOLAR/BiCMOS Circuits and Technology Meeting, pp. 86 – 89, Oct. 2001.

- [5] K. Rampmeier, B. Agarwal, P. Mudge, D. Yates and T. Robinson, "A Versatile Receiver IC Supporting WCDMA, CDMA and AMPS Cellular Handset Applications", *Proc. IEEE Radio Frequency Integrated Circuits Symposium*, pp. 21 – 24, May 2001.

- [6] I. Burciu, G. Villemaud and J. Verdier, "Technique d'orthogonalisation permettant la réduction de l'occupation spectrale pendant le traitement simultané de deux signaux indépendants (Patent style)", INPI Patent Request 0856328, Sept, 2008.

- [7] C. Van Der Burgt, "Multi-band receiver and method associated therewith (Patent style)", U.S. Patent 7120406, June 11, 2004.

- [8] I. Mak, S.-P. U and R. P. Martins, Analog-Baseband Architecture and Circuits for Multistandard and Low Voltage Wireless Transceivers (Book style). New York: Springer, 2007.

- [9] J. C. Rudell, J.-J. Ou, T. B. Cho, G. Chien, F. Brianti, J. A. Weldon, and P. R. Gray, "A 1.9GHz Wide-Band IF Double Conversion CMOS Integrated Receiver for Cordless Telephone Applications", *IEEE Journal of Solid-State Circuits*, vol. 32, no. 12, pp. 2071-2088, Dec. 1997

- [10] J. C. Rudell, "Frequency Translation Techniques for High-Integration High-Selectivity Multi-Standard Wireless Communication Systems (Thesis or Dissertation style)," Ph.D. dissertation, Dept. Electrical Engineering and Computer Sciences, Berkeley Univ., 2000.

- [11] E. Çetin, İ. Kale and R. C. S. Morling, "Adaptive self-calibrating image rejection receiver", *IEEE Communications Society*, vol.5, pp. 2731 – 2735, June 2004.

- [12] S. Traverso, M. Ariaudo, I. Fijalkow, J-L Gautier and C. Lereau, "Decision Directed Channel Estimation and High I/Q Imbalance Compensation in OFDM Receivers", IEEE Transactions on Communications, Feb. 2008.

- [13] www.agilent.com.

- [14] J. Xiao, I. Mehr and J. Silva-Martinez, "A High Dynamic Range CMOS Variable Gain Amplifier for Mobile DTV Tuner", *IEEE Journal of Solid-State Circuits*, vol. 42, no. 2, pp. 298-301, Feb. 2007.