# Fences in Weak Memory Models

Alglave Jade, Luc Maranget

# ▶ To cite this version:

Alglave Jade, Luc Maranget. Fences in Weak Memory Models. [Research Report] RR-7010, INRIA. 2009. inria-00408568

# HAL Id: inria-00408568 https://inria.hal.science/inria-00408568

Submitted on 3 Aug 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

# Fences in Weak Memory Models

Jade Alglave — Luc Maranget

# N° 7010

Juillet 2009

INSTITUT NATIONAL

DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

# Fences in Weak Memory Models

Jade Alglave, Luc Maranget

Thème : Équipe-Projet Moscova

Rapport de recherche n° 7010 — Juillet 2009 — 39 pages

**Abstract:** We present here an axiomatic framework, implemented in the Coq proof assistant, for defining weak memory models in terms of several parameters: local reorderings of reads and writes, and visibility of inter and intra processor communications through memory. In this context, we provide formal definition of weak memory models induced by architectures, illustrated by definitions of SC and Sparc TSO. Moreover, we define a comparison over architectures, an architecture  $A_1$  being weaker than another one  $A_2$  when  $A_1$  allows more behaviours than  $A_2$ . In addition, we provide a characterisation of behaviours allowed by  $A_1$  which are also valid on  $A_2$ . By that means, we provide a simple characterisation of SC and TSO behaviours on any weaker architecture. We also provide an abstract notion of what should be the action and placement of fences to restore a given model from a weaker one.

Key-words: Weak Memory Models, Fences

Centre de recherche INRIA Paris - Rocquencourt Domaine de Voluceau, Rocquencourt, BP 105, 78153 Le Chesnay Cedex Téléphone : +33 1 39 63 55 11 — Télécopie : +33 1 39 63 53 30

# Une étude de l'action des barrières au sein de modèles de mémoire relâchés

**Résumé :** Nous proposons un environnement générique, implémenté au sein de l'assistant de preuve Coq, pour définir des modèles de mémoire relâchés en fonction de plusieurs paramètres: réordonnancements de lectures et écritures, et visibilités des communications via la mémoire. Dans ce contexte, nous fournissons une définition formelle d'un modèle de mémoire induit par une architecture, que nous illustrons par les définitions de SC et Sparc TSO. Par ailleurs, nous définissons une notion de comparaison de deux architectures, une architecture  $A_1$  étant considérée plus faible qu'une architecture  $A_2$  si  $A_1$  autorise plus de comportements que  $A_2$ . De plus, nous fournissons une caractérisation des comportements autorisés par  $A_1$  qui sont également valides au sein de  $A_2$ , ce qui nous permet de donner une caractérisation simple de SC et TSO sur des architectures plus faibles. Nous fournissons également une formalisation du pouvoir et du placement des barrières mémoires pour restaurer un modèle donné depuis un modèle plus faible.

Mots-clés : Modèles de mémoires relâchés, Barrières

# Contents

| 1           | Intr                                                                                                                       | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                                                                                           |

|-------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| _           | 1.1                                                                                                                        | An axiomatic generic model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                                                                                                           |

|             | 1.2                                                                                                                        | Study of barriers power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5                                                                                                                           |

|             | 1.3                                                                                                                        | Case study: a Power model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                                                                                                           |

|             |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Ŭ                                                                                                                           |

| <b>2</b>    | $\mathbf{Des}$                                                                                                             | cription of the model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>5</b>                                                                                                                    |

|             | 2.1                                                                                                                        | Axiomatisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                                                                                                           |

|             |                                                                                                                            | 2.1.1 Basic objects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5                                                                                                                           |

|             |                                                                                                                            | 2.1.2 Execution witnesses $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                                                                                                           |

|             |                                                                                                                            | 2.1.3 Architectures $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8                                                                                                                           |

|             |                                                                                                                            | 2.1.4 Validity of an execution with respect to an architecture .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                                                                                                                           |

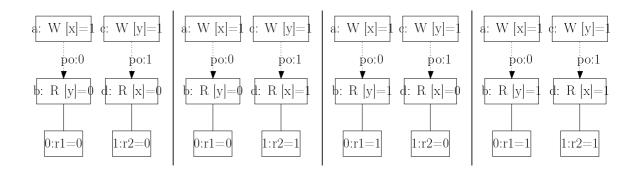

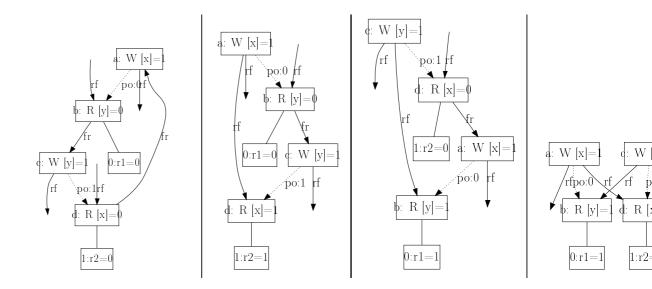

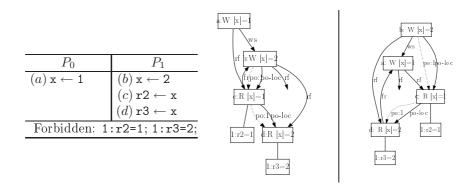

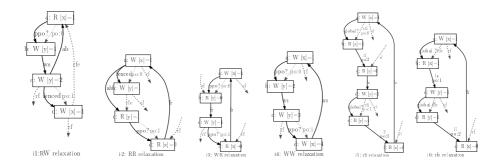

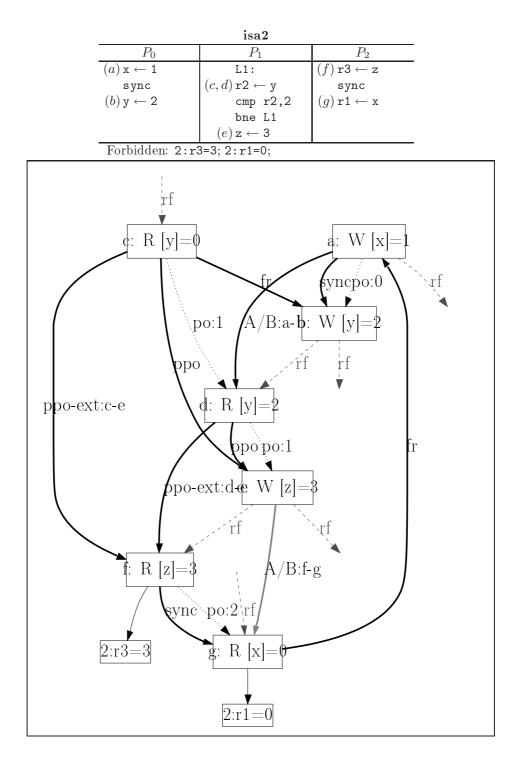

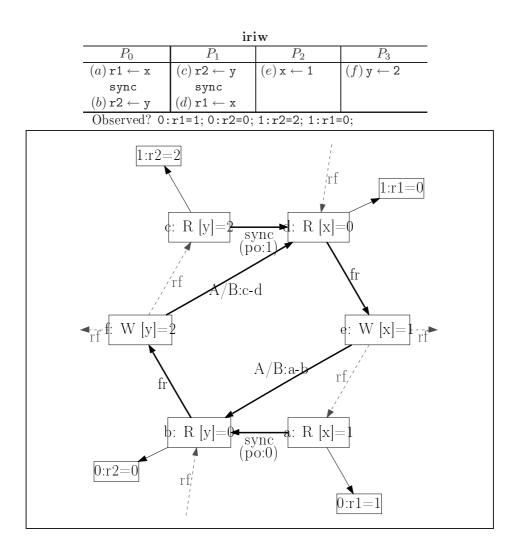

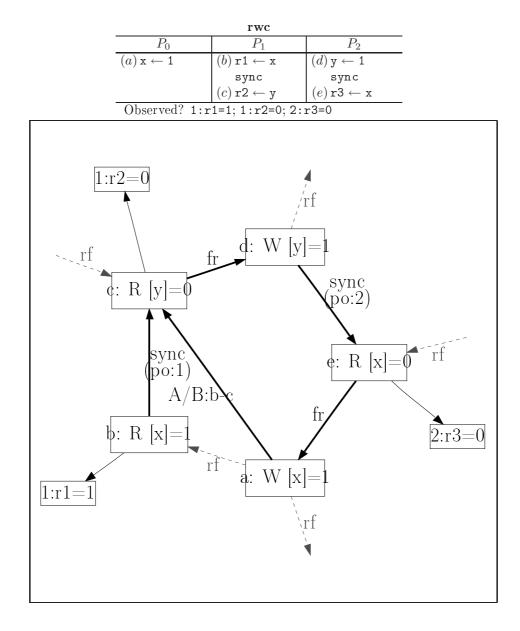

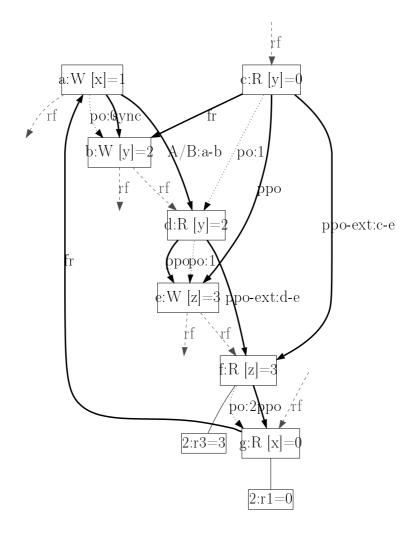

|             |                                                                                                                            | 2.1.5 Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10                                                                                                                          |

|             | 2.2                                                                                                                        | Comparison of architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12                                                                                                                          |

|             |                                                                                                                            | 2.2.1 Making validity monotonous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13                                                                                                                          |

|             |                                                                                                                            | 2.2.2 Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13                                                                                                                          |

|             | 2.3                                                                                                                        | Equivalence with native models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14                                                                                                                          |

|             |                                                                                                                            | 2.3.1 Sc is SC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14                                                                                                                          |

|             |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14                                                                                                                          |

|             | 2.4                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15                                                                                                                          |

|             |                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15                                                                                                                          |

|             |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15                                                                                                                          |

|             |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16                                                                                                                          |

|             |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                             |

| 9           | Com                                                                                                                        | antiag of banning 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                             |

| 3           |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                                                                                                                          |

| 3           | 3.1                                                                                                                        | Barriers guarantee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                                                                                          |

| 3           |                                                                                                                            | Barriers guarantee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                             |

| 3<br>4      | 3.1<br>3.2                                                                                                                 | Barriers guarantee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                                                                                          |

|             | 3.1<br>3.2                                                                                                                 | Barriers guarantee    Image: Considering a weaker guarantee    Image: Considering a weaker guarantee    Image: Considering a weaker guarantee      e study: a Power model    Image: Considering a weaker guarantee    Image: Considering a weaker guarantee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19<br>20                                                                                                                    |

|             | 3.1<br>3.2<br>Cas                                                                                                          | Barriers guarantee       1         Considering a weaker guarantee       2         e study: a Power model       2         Complete event structures and execution witnesses       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19<br>20<br>21                                                                                                              |

|             | 3.1<br>3.2<br><b>Cas</b><br>4.1                                                                                            | Barriers guarantee       1         Considering a weaker guarantee       2         e study: a Power model       2         Complete event structures and execution witnesses       2         Globality of rfmaps       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19<br>20<br>21<br>22                                                                                                        |

|             | 3.1<br>3.2<br><b>Cas</b><br>4.1<br>4.2                                                                                     | Barriers guarantee       1         Considering a weaker guarantee       2         e study: a Power model       2         Complete event structures and execution witnesses       2         Globality of rfmaps       2         Preserved program order <i>ppo</i> 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19<br>20<br>21<br>22<br>24                                                                                                  |

|             | 3.1<br>3.2<br><b>Cas</b><br>4.1<br>4.2<br>4.3                                                                              | Barriers guarantee       Image: Study: a Power model       Ima | 19<br>20<br>21<br>22<br>24<br>24                                                                                            |

| 4           | 3.1<br>3.2<br><b>Cas</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5                                                                | Barriers guarantee       1         Considering a weaker guarantee       2         e study: a Power model       2         Complete event structures and execution witnesses       2         Globality of rfmaps       2         Preserved program order ppo       2         Values do not come out of thin air       2         Cumulative memory barriers       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19<br>20<br>21<br>22<br>24<br>24<br>25<br>27                                                                                |

|             | 3.1<br>3.2<br><b>Cas</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br><b>Bar</b>                                                  | Barriers guarantee       1         Considering a weaker guarantee       2         e study: a Power model       2         Complete event structures and execution witnesses       2         Globality of rfmaps       2         Preserved program order ppo       2         Values do not come out of thin air       2         Cumulative memory barriers       2         cier experiments       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>21</b><br>222<br>24<br>224<br>225<br>227<br><b>28</b>                                                                    |

| 4           | 3.1<br>3.2<br><b>Cass</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br><b>Bar</b><br>5.1                                          | Barriers guarantee       1         Considering a weaker guarantee       2         e study: a Power model       2         Complete event structures and execution witnesses       2         Globality of rfmaps       2         Preserved program order <i>ppo</i> 2         Values do not come out of thin air       2         cumulative memory barriers       2         cier experiments       2         Official tests       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19<br>20<br>21<br>22<br>24<br>24<br>25<br>27<br>28<br>28                                                                    |

| 4           | 3.1<br>3.2<br><b>Cas</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br><b>Bar</b>                                                  | Barriers guarantee       1         Considering a weaker guarantee       2         considering a weaker guarantee       2         e study: a Power model       2         Complete event structures and execution witnesses       2         Globality of rfmaps       2         Preserved program order <i>ppo</i> 2         Values do not come out of thin air       2         cumulative memory barriers       2         cier experiments       2         Official tests       2         Classical tests       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>21</b><br>222<br>24<br>224<br>225<br>227<br><b>28</b>                                                                    |

| 4           | 3.1<br>3.2<br><b>Cas</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br><b>Bar</b><br>5.1<br>5.2<br>5.3                             | Barriers guarantee       1         Considering a weaker guarantee       2         Considering a weaker guarantee       2         e study: a Power model       2         Complete event structures and execution witnesses       2         Globality of rfmaps       2         Preserved program order <i>ppo</i> 2         Values do not come out of thin air       2         Cumulative memory barriers       2         cier experiments       2         Official tests       2         Experiments       2         Experiments       2         Experiments       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19<br>20<br>21<br>22<br>24<br>24<br>25<br>27<br>28<br>28<br>31<br>31                                                        |

| 4           | 3.1<br>3.2<br><b>Cas</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br><b>Bar</b><br>5.1<br>5.2<br>5.3<br><b>Tow</b>               | Barriers guarantee       1         Considering a weaker guarantee       2         Considering a weaker guarantee       2         e study: a Power model       2         Complete event structures and execution witnesses       2         Globality of rfmaps       2         Preserved program order <i>ppo</i> 2         Values do not come out of thin air       2         Cumulative memory barriers       2         classical tests       2         Classical tests       2         ards a stronger model       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19<br>20<br>21<br>22<br>24<br>24<br>25<br>27<br>28<br>31<br>31<br>31<br>34                                                  |

| 4           | 3.1<br>3.2<br><b>Cas</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br><b>Bar</b><br>5.1<br>5.2<br>5.3<br><b>Tow</b><br>6.1        | Barriers guarantee1Considering a weaker guarantee2Considering a weaker guarantee2e study: a Power model2Complete event structures and execution witnesses2Globality of rfmaps2Preserved program order $ppo$ 2Values do not come out of thin air2Cumulative memory barriers2rier experiments2Official tests2Classical tests2Experiments2ards a stronger model3Extension $\stackrel{\text{ppo-ext}}{\rightarrow}$ 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19         20         21         22         24         25         27         28         31         34         34            |