## Syntax and Semantics of the Clock Constraint Specification Language (CCSL)

Charles André

#### ▶ To cite this version:

Charles André. Syntax and Semantics of the Clock Constraint Specification Language (CCSL). [Research Report] RR-6925, 2009, pp.34. inria-00384077v1

## HAL Id: inria-00384077 https://inria.hal.science/inria-00384077v1

Submitted on 14 May 2009 (v1), last revised 15 Jun 2009 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

## Syntax and Semantics of the Clock Constraint Specification Language (CCSL)

Charles André

N° 6925

May 2009

Thème COM

apport de recherche

### Syntax and Semantics of the Clock Constraint Specification Language (CCSL)

Charles André\*

Thème COM — Systèmes communicants Projet Aoste

Rapport de recherche n° 6925 — May 2009 — 34 pages

**Abstract:** The UML Profile for Modeling and Analysis of Real-Time and Embedded (MARTE) systems has recently been adopted by the OMG. Its Time Model extends the informal and simplistic Simple Time package proposed by UML2 and offers a broad range of capabilities required to model real-time systems. The MARTE OMG specification introduces a Time Structure inspired from Time models of the concurrency theory and proposes a new clock constraint specification language (CCSL) to specify, within the context of UML, logical and chronometric time constraints.

This report specifies the syntax and a formal semantics of a subset of CCSL, called *kernel* CCSL. This semantics is to be the reference semantics of CCSL.

**Key-words:** CCSL, syntax, semantics, time constraints, UML

<sup>\*</sup> Université de Nice Sophia Antipolis

# Syntaxe et sémantique du langage de spécification des contraintes d'horloges (CCSL)

Résumé: Le profil UML pour la Modélisation et l'Analyse des systèmes Temps Réel et Embarqués (MARTE) a été récemment adopté par l'OMG. Son modèle de Temps étend le modèle simpliste défini dans le paquetage "Simple Time" de la spécification UML2 et offre des possibilités adaptées aux systèmes temps réel. La spécification OMG MARTE introduit uns Structure de Temps (Time Structure) inspirée des modèles de temps de la théorie du parallélisme et propose un langage de spécification de contraintes d'horloges appelé CCSL. Ce langage permet de spécifier dans le cadre d'UML, des contraintes aussi bien de temps chronométrique que de temps logique.

Ce rapport définit la syntaxe et la sémantique d'un sous-ensemble noyau de CCSL. La sémantique donnée servira de référence.

Mots-clés: CCSL, syntaxe, sémantique, contraintes temporelles, UML

#### 1 Introduction

The Unified Modeling Language (UML) is a widely accepted language for system modeling (structural and behavioral aspects). However, when time plays a central role in the system behavior, UML is inadequate. Its model of time, called Simple Time, is too simple to address, for instance, real-time system time requirements. In its Common Behavior chapter, the UML specification [1] explicitly says that system modeling that demand advanced time concepts "will use a more sophisticated model of time provided by an appropriate profile". The UML Profile for Modeling and Analysis of Real-Time and Embedded' systems [2] (MARTE), is such a profile.

MARTE introduces a rich model of time (Chapter 9: Time Modeling) that supports dense and discrete time, chronometric and logical time, simple and multiple time references. In MARTE, a *Clock* is a model element giving access to the model time structure. When using the MARTE time model, several—interdependent— clocks are generally defined in a model. Clock mutual dependence can be specified with a dedicated language, called *Clock Constraint Specification Language* (CCSL). CCSL is defined in annex C3 of the UML specification. The syntax of CCSL is non normative and its semantics is informal (English description).

This report defines a formal semantics for a subset of CCSL, called Kernel Clock Constraint Language (abbreviated as KCCL). This semantics is to be the reference semantics of CCSL. It is applied to execute timed UML models in software environment like TIMESQUARE [3]. TIMESQUARE is a collection of plug-ins developed by the project team AOSTE to apply the MARTE time model, to specify clock constraints and to analyze them<sup>1</sup>. CCSL can also be used with non-UML models to specify constraints on event occurrences.

This report is organized as follows. Section 2 presents the meta-models: a simplified version of the MARTE time model (Sec 2.1) and the kernel clock constraint language (Sec. 2.2). Section 3 introduces the syntax of KCCL. A concise symbolic notation, inspired by processus algebra, is also proposed. A *structural operational semantics* of KCCL is then defined in Section 4. A KCCL specification is transformed into a set of logical constraints. Section 5 describes how to solve these constraints with a BDD-based Boolean solver. Different policies to select a solution from the many possible ones are then discussed. Finally, we conclude with existing success applications of CCSL and its forthcoming developments.

#### 2 Metamodels

#### 2.1 Time Model

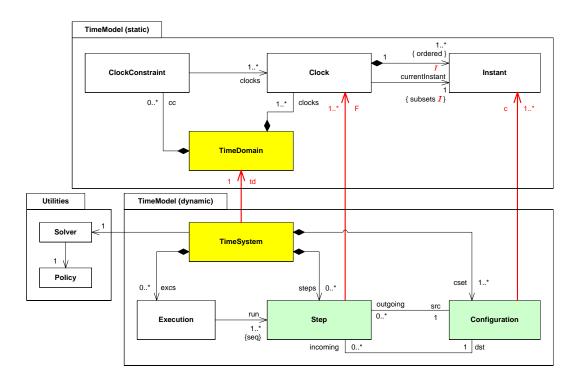

We have defined the *Time Model* part of the UML profile for "Modeling and Analysis of Real-Time and Embedded" systems [2], (MARTE). Figure 1 shows a simplified version of the MARTE Time meta-model. For a detailed description the reader is urged to refer to the MARTE specification.

$<sup>^{1}\</sup>mathrm{TimeS}_{\mathrm{QUARE}}$  is available at http://www-sop.inria.fr/aoste/dev/time\_square.

4 C. Andre

#### 2.1.1 Static view

The upper part of the figure represents the static model elements and their relationships. A  $Time\ Domain\ consists$  of one or many clocks. Each clock clk owns an ordered set of instants  $\mathcal{I}_{clk}$ . One of these instants is distinguished as the  $current\ instant$  of the clock.

The instants of the clocks are *a priori* independent. However, in most applications there exist dependence relationships between pairs of instants. Three instant relations have been introduced in MARTE: coincidence (denoted  $\equiv$ ), precedence (denoted  $\preccurlyeq$ ), and exclusion (denoted #). A fourth relation, the strict precedence (denoted  $\prec$ ), is derived from the others ( $\prec \triangleq \prec \backslash \equiv$ ). These instant relations are more conveniently expressed by clock constraints, which are the topic of this report. Thus, a time domain also owns a (usually not empty) set of clock constraints.

#### 2.1.2 Dynamic view

A time domain with its sets of clocks and clock constraints specifies a *time system*. A temporal evolution—*i.e.*, one execution of the time system or *run*—is a kind of non-sequential process [4] whose events are clock tickings. Thus, in a first approximation, a temporal evolution is a partially ordered set of instants. In fact, because of our coincidence relation, the partial ordering is not on instants but on sets of coincident instants [5].

A configuration is a set of coexisting instants, i.e., a slice of the occurrence net [6] representing a run. Of course, since the instants of a clock are strictly ordered, a configuration cannot contain two instants of the same clock. When a clock ticks (the current instant of the clock moves to the next instant of this clock), the configuration changes. Several clocks can fire<sup>2</sup> simultaneously. A set of simultaneous clock firings is called a step. A particular execution of a time system (run) is a partially ordered set of steps.

The issue is to compute runs that meet all the clock constraints imposed in the time domain. This is done by a *constraint solver* applying a given *policy*.

Remark: The reader may wonder why considering the notion of simultaneous firings intead of concurrent firings. Concurrency, such as defined in the General net Theory (C.A. Petri), is a kind of independence relation (absence of causal ordering). In this theory, coincidence is a very strong relation that relates two events occurring at one space-time point (one place, one instant). Of course, two coincident events are not concurrent because they are tighly dependent. In fact, the two events are a unique event. In our approach of time, clock ticks—changes in the current instant of a clock—play the role of events (or more precisely, event occurrences). The idea to define a step as a set of concurrent clock firings is not adequate because this precludes coincident clock firings. For us, coincidence is not the unification of two instants: coincident instants keep their individuality, they are only forced to occur jointly. This constraint is not necessarily a causal condition. Most of the time, it is a mere design choice. That is the reason why we have adopted another adjective: simultaneous. A step (simultaneous clock firings) contains coincident firings that must be fired

<sup>&</sup>lt;sup>2</sup>another word to say that the clock ticks.

Figure 1: Static and Dynamic views of Time

altogether, and possible concurrent firings. Simultaneity is a central concept in synchronous reactive modeling. Since covering the concept of instants of synchronous reactive models is also part of the MARTE time model objectives, we have adopted the concept of simultaneous firings.

#### 2.2 Clock constraints

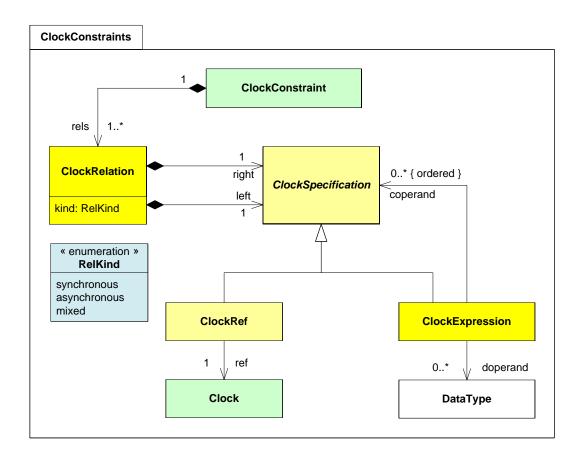

Figure 2: Clock constraint meta-model

The clock constraints of a time domain are specified in CCSL (Clock Constraint Specification Language). We have introduced this language in the MARTE specification. It is a non normative specification, and its semantics has only been given in an informal way (English specification). Beyond the MARTE specification, we have given a concrete syntax and a formal semantics to CCSL. A kernel CCSL, called Kernel Clock Constraint Language (KCCL) has also been defined. Using the primitives provided by this kernel, complex constraints can be elaborated. Another advantage of having a kernel is that it is sufficient to define the semantics of the kernel primitives to give the semantics of any CCSL specification.

The abstract syntax of CCSL is given in Fig. 2. A clock constraint consists of at least one clock relation. A clock relation relates two clock specifications. A clock specification can be either a simple reference to a clock or a clock expression. A clock expression refers to one or more clock specifications and possibly to additional operands. The attribute kind of a clock relation indicates if the relation is based on the coincidence relation (synchronous), the precedence relation (asynchronous), or a combination of both (mixed).

The meta-model in Fig. 2 is a simplified version. To describe the semantics of the clock constraints, we needs a more detailed meta-model (Fig. 3). The additional model elements will be explained when used.

Figure 3: (Kernel) Clock constraint full meta-model

The names of the clock relations and the clock expressions used in KCCL are defined in the enumerations CRelKind and CEOpKind. Attributes and operations have been added to the meta-model classes. They have been introduced to make the semantic rules easier. They will be explained when used for the first time in the semantics rules. The type BinaryWord is

detailed in Annex A. For now, the reader has only to know that a binary word is a, possibly infinite, sequence of bits (0 or 1).

#### 3 Syntax of the kernel CCSL

This section defines the syntax of the kernel clock constraint language on a set of clocks  $\mathcal{C}$  (denoted KCCL  $_{\mathcal{C}}$ , or simply KCCL when  $\mathcal{C}$  is understood). With the primitive constructs provided by the kernel, new constructs can be derived and proposed in libraries. For the sake of conciseness, we use a symbolic notation for the kernel operators and constructs. There also exists a concrete textual syntax given in Table 6. The reader should not focus on this concrete syntax since CCSL specifications are usually given interactively through dialog boxes offered by TIMESQUARE.

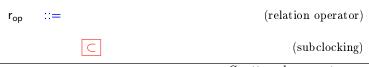

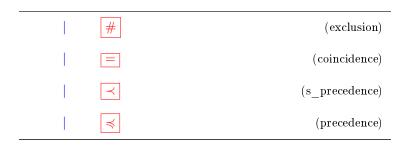

#### 3.1 Kernel relations and expressions

#### 3.1.1 Notation

In what follows, grammatical rules are given in the BNF notation. ::= means "is defined by"; | means "or"; non terminal symbols are written in a sans-serif font (e.g., CC, natural). Terminal symbols are in red fonts (e.g., |, | |).

Table 1: Constraints and relations

| (clock constraint)       |                | ::= | СС |

|--------------------------|----------------|-----|----|

| (parallel composition)   | CC   CR        |     |    |

|                          | CR             |     |    |

| (conditional constraint) | CR if bool     |     |    |

| $({ m clock\ relation})$ |                | ::= | CR |

|                          | $CS\ r_op\ CS$ |     |    |

| 01:11                    |                |     |    |

Continued on next page

Table 2: Relation operators

Continued on next page

Table 3: Clock specifications

```

CS

(clock specification)

clock

(clock reference)

CE

CE

(clock expression)

bool? CE: CE

(conditional expression)

clock

(clock reference)

! 1

(force)

! 0

(inhibit)

CE<sup>natural</sup>

(await)

CE > CE

(s sample)

CE > CE

(sample)

CE / CE

(upto)

CE • CE

(concat)

CE + CE

(union)

CE * CE

(inter)

CE(naturalSequence) → CE

(defer)

CE V CE

(sup)

CE ∧ CE

(inf)

```

The non terminal clock is an identifier referencing a clock of  $\mathcal{C}$ . bool stands for a Boolean expression. natural is an integer expression evaluating to a non negative integer value. natural Sequence is a sequence of natural.

Recursion The clock attribute is Recursive is a Boolean set to true for clock defined by a relation of the form clock CE • clock, where clock denotes the same clock on both sides of the clock relation. In this case, the property staticDef is set to CE. The following OCL constraint holds:

```

context Clock

inv:    if self.isRecursive then

```

```

self.staticDef->notEmpty() and

self = self.staticDef.implicitClock

else

self.staticDef->isEmpty()

endif

```

#### 3.2 Simple KCCL

The above syntax allows nested clock expressions. In order to make the specification of the semantics of KCCL easier, we propose now a simpler syntax forbidding nested clock expressions. This entails no loss of generality because nested clock expressions are replaced by clock definitions, one per clock expression. The new syntax in given in Tables 4 and 5. The non-terminals are similar to the ones used in the original syntax, prefixed by an 'S', short for Simple. The clock relation "clock definition" is a simple clock relation which associates a clock with a simple clock expression. Of course,  $\mathcal C$  includes the newly introduced clocks. Notice that in Simple KCCL, a clock relation applies to two clock references instead of two clock specifications.

An OCL constraint is also added to the meta-model in Fig. 3:

Table 4: Simple constraints and relations

Continued on next page

SCE (simple clock expression) bool? clock: clock (conditional expression) clock (clock reference) ! 1 (force) ! 0 (inhibit) clock natural (await) clock ¥ clock (s sample) clock ≥ clock (sample) clock f clock (upto) clock • clock (concat) clock + clock (union) clock \* clock (inter) clock(naturalSequence) → clock (defer) clock ∨ clock (sup) clock ∧ clock (inf)

Table 5: Simple clock expressions

#### 3.3 Transformation KCCL to Simple KCCL

This transformation is specified by conditional rewriting rules of two kinds: clock constraint rewriting rules (denoted  $\rightarrow$ ), and clock specification rewriting rules (denoted  $\rightarrow$ ).

$$\to : \mathsf{CC} \to Set(\mathsf{SCR}) \tag{1}$$

$$\rightarrow$$

: CS  $\rightarrow$  clock  $\times$   $Set(SCR)$  (2)

In both rules,  $Set(\mathsf{SCR})$  is the set of simple clock relations to be substituted to the left-hand side term. In the second rule, the clock result is a reference to a clock. As shown in the kernel clock constraint meta-model (Fig. 3), this clock is either a given clock (ref property of a  $\mathsf{ClockRef}$ ) or an implicit clock, created during the transformation and attached to a clock expression.

#### 3.3.1 Clock relation transformations

$$\frac{cr \twoheadrightarrow scrs}{cr \text{ if } \beta \to \beta ? scrs : \emptyset} \quad \text{( cond. rel. transf. )} \tag{3}$$

In rule 3, the conditional operator is applied to sets:  $\beta$ ? scrs:  $\emptyset$  is scrs (a set of simple clock relations) if  $\beta = 1$ , and the empty set otherwise.

$$\frac{cs_1 \twoheadrightarrow c_1, cds_1}{cs_2 \twoheadrightarrow c_2, cds_2}$$

$$\frac{cs_2 \twoheadrightarrow c_2, cds_2}{cs_1 \mathsf{r_{op}}\ cs_2 \rightarrow \{c_1 \mathsf{r_{op}}\ c_2\} \cup cds_1 \cup cds_2}$$

(rel. transf. ) (4)

$cds_1$  ( $cds_2$ , respectively) is a set of clock definitions generated while transforming clock specification  $cs_1$  ( $cs_2$ , respectively).

#### 3.3.2 Clock expression transformations

$$c woheadrightarrow c, \emptyset$$

(clock ref. transf.) (5)

Rule 5 applies when the clock specification is a ClockRef (meta-model Fig. 3). In this case, there is no actual change.

0-ary clock expression transformations:

$$! \ 1 \rightarrow c = \text{new clock}, \{c \triangleq ! 1\} \quad \text{(clock forcing transf.)}$$

(6)

$$! \ 0 \rightarrow c = \text{new clock}, \{c \triangleq ! 0\} \quad \text{(clock inhib. transf.)}$$

(7)

Unary clock expression transformation:

$$\frac{ce_1 \twoheadrightarrow c_1, cds_1}{ce^{\hat{}} n \twoheadrightarrow c = \text{new clock}, \{c \stackrel{\triangle}{=} c_1 \hat{} n\} \cup cds_1} \quad \text{(await transf.)}$$

Binary clock expression transformations:

$$\frac{ce_1 \twoheadrightarrow c_1, cds_1}{ce_2 \twoheadrightarrow c_2, cds_2} \qquad \qquad \text{(bin. expr. transf.)}$$

$$\frac{ce_1 \ \mathsf{e}_{\mathsf{op2}} \ ce_2 \twoheadrightarrow c = \mathrm{new \ clock}, \{c \ \triangleq \ c_1 \ \mathsf{e}_{\mathsf{op2}} \ c_2\} \cup cds_1 \cup cds_2}$$

The binary clock expression operators  $e_{op2}$  are  $\begin{align*}{l} \begin{align*}{l} \begin{align$

$Conditional\ clock\ specification\ transformation:$

$$cs_1 \rightarrow c_1, cds_1 cs_2 \rightarrow c_2, cds_2$$

$$\beta ? cs_1 : cs_2 \rightarrow c = \text{new clock}, \{c \triangleq \beta ? c_1 : c_2\} \cup (\beta ? cds_1 : cds_2)$$

(cond. spec. transf.)

#### 3.4 Example of transformation

Let  $(a + b) \notin c \equiv d$  be a KCCL specification consisting of one clock relation only. Given clocks are a, b, c, and d. Rule 4 applies and demands the transformation of the two clock specifications  $(a + b) \notin c$  and d. Now, rule 9 applied to  $(a + b) \notin c$  creates a clock  $c_1$ , and requires transformations of clock expressions a + b on the one hand, and c on the other hand.

The transformation of a + b can be written as:

$$\frac{a \to a, \emptyset}{b \to b, \emptyset}$$

$$\frac{a + b \to c_2 = \text{new clock}, \left\{ c_2 \stackrel{\triangle}{=} a + b \right\}}{}$$

(11)

The transformation of c is trivial:

$$c \to c, \emptyset$$

(12)

From Eqs. 11 and 12, we can complete the transformation of  $(a + b) \notin c$ :

$$\frac{a+b \twoheadrightarrow c_2, \left\{c_2 \stackrel{\triangle}{=} a+b\right\}}{c \twoheadrightarrow c, \emptyset} \\

\frac{c \twoheadrightarrow c, \emptyset}{a+b \twoheadrightarrow c_1, \left\{c_1 \stackrel{\triangle}{=} c_2 \not c\right\} \cup \left\{c_2 \stackrel{\triangle}{=} a+b\right\}} \tag{13}$$

The transformation of the right-hand side of the relation is also trivial:

$$d \rightarrow d, \emptyset$$

(14)

Taking account of Eq. 13 and Eq. 14, the result of the transformation of the initial relation is:

$$\{c_1 \equiv d\} \cup \{c_1 \triangleq c_2 \not c, c_2 \triangleq a+b\}$$

Hence, the equivalent simple KCCL specification is

$$c_2 \stackrel{\triangle}{=} a + b \mid c_1 \stackrel{\triangle}{=} c_2 \not\downarrow c \mid c_1 \stackrel{\blacksquare}{=} d$$

#### 3.5 Summary

Table 6 gathers the elements of simple KCCL syntax along with their textual forms. In this table c is a clock reference (either a given clock or an implicit clock generated during the transformation).

Ref. Textual syntax Notation Comments Relations c1 isSubClockOf c2 R1 $c_1 \subset c_2$ c1 # c2 R2#  $c_2$ c1 = c2R3R4c1 strictly precedes c2  $\prec c_2$ R5c1 precedes c2R6c clockDef e Internal use (for simple KCCL) r if b R.7r if br:relation, b: Boolean Expressions E1force ! 1 ! 0 E2inhibit E3await n c  $c^n$ n: natural number, n > 0E4c1 strictly sampled c2 $c_1 \ \ c_2$  ${\rm c1}$  sampled  ${\rm c2}$ E5 $c_1 \triangleleft c_2$ E6c1 upto c2 $c_1 \not = c_2$ E7c1 followedBy c2  $c_1 \bullet c_2$ c1 clockUnion c2 E8  $c_1 + c_2$ c1 clockInter c2E9  $c_1 * c_2$ E10 c1 deferred c2 for ns  $c_1(ns) \leadsto c_2$ ns: sequence of non-0 natural numbers E11 c1 lub c2  $c_1 \lor c_2$  $c1 \hspace{0.1cm} \textcolor{red}{\textbf{glb}} \hspace{0.1cm} c2$ E12 $c_1 \wedge c_2$

Table 6: Syntax of the Simple Kernel Clock Constraint Language

#### 4 Semantics

if b then c1 else c2

E13

The suggestion of representing temporal evolutions as non-sequential processes (Section 2.1) is not effective: they are infinite structures and they hide choices (conflicts). Instead, we propose to give KCCL an operational structural semantics that allows the effective construction of temporal evolutions. Note that we consider only clocks with a discrete set of instants.

$b ? c_1 : c_2$

b: Boolean

#### 4.1 Clock Model

A Clock Model  $\mathcal{M} = \langle \mathcal{C}, \mathcal{S} \rangle$  consists of a finite set of discrete clocks  $\mathcal{C}$ , constrained by a  $\text{KCCL}_{\mathcal{C}}$  specification  $\mathcal{S}$ . A clock model is a TimeDomain of the TimeModel (Fig 1), whose constraints are specified in CCSL.

A clock model is static, the next subsection deals with the dynamics of this model.

#### 4.2 Time System

A Time System  $TS = \langle C, S \rangle$ ,  $\chi^0$  consists of a Clock Model  $\mathcal{M} = \langle C, S \rangle$ , along with an initial configuration  $\chi^0$ .

A configuration  $\chi$  of  $\mathcal{TS}$  is a tuple of natural numbers  $\chi: \mathcal{C} \to \mathbb{N}$ , where for any clock  $c \in \mathcal{C}$ ,  $\chi(c)$  is the current instant of clock c. The initial configuration  $\chi^0$  is such that  $(\forall c \in \mathcal{C})\chi^0(c) = 0$ .

A run r of  $\mathcal{TS}$  is a, generally infinite, sequence of steps:  $r = F_1.F_2.\cdots.F_n.\cdots$ , where  $F_k \subset \mathcal{C}$  for all k.

$F \subset \mathcal{C}$  is fireable in  $\langle \mathcal{C}, \mathcal{S} \rangle$  at  $\chi$ , if the firing of every clock in F satisfies the clock constraint  $\mathcal{S}$  at  $\chi$ . This is denoted by  $\langle \mathcal{C}, \mathcal{S} \rangle$ ,  $\chi \xrightarrow{F}$ . The firing of F leads to a new configuration  $\chi'$  and possibly new clock constraints  $\mathcal{S}'$ , denoted as shown in Eq. 15.

$$\langle \mathcal{C}, \mathcal{S} \rangle, \chi \xrightarrow{F} \langle \mathcal{C}, \mathcal{S}' \rangle, \chi'$$

(15)

In the new configuration, the current index of every fired clocks is incremented by 1 (Eq. 16).

$$\chi'(c) = \begin{cases} \chi(c) + 1 & \text{if } c \in F, \\ \chi(c) & \text{otherwise.} \end{cases}$$

(16)

The change in S is explained later.

A run r can be rewritten as

$$\langle \mathcal{C}, \mathcal{S}^{0} \rangle, \chi^{0} \xrightarrow{F_{1}} \langle \mathcal{C}, \mathcal{S}^{1} \rangle, \chi^{1} \xrightarrow{F_{1}} \cdots \langle \mathcal{C}, \mathcal{S}^{n-1} \rangle, \chi^{n-1} \xrightarrow{F_{n}} \langle \mathcal{C}, \mathcal{S}^{n} \rangle, \chi^{n} \cdots$$

where  $\mathcal{S}^{0} = \mathcal{S}$

The semantics of a clock constraint  $\mathcal{S}$  expressed in  $\mathrm{KCCL}_{\mathcal{C}}$  is given as a Boolean expression on  $\mathscr{C}$ , a set of Boolean variables in bijection with  $\mathcal{C}$ .

let

$$\pi: \mathcal{C} \to \mathscr{C}$$

bijection, and  $[\![]\!]: \mathrm{KCCL}_{\mathcal{C}} \to \mathscr{B}_{\mathscr{C}}$  (18)

[ ] is defined by structural rewriting rules. For convenience, we denote  $\pi(c)$  by c, for all c in C. c = 1 means that c is fireable in  $\langle C, S \rangle$  at  $\chi$ . More generally,

$$(\forall f: \mathscr{C} \to \{0, 1\}) \langle \mathcal{C}, \mathcal{S} \rangle, \chi \xrightarrow{|f|} \Leftrightarrow \llbracket \mathcal{S} \rrbracket (f) = 1$$

(19)

In Eq. 19, f is a valuation of  $\mathscr{C}$ ,  $[\![\mathcal{S}]\!](f) = 1$  says that  $[\![\mathcal{S}]\!]$  evaluates to 1 for the valuation f, and  $|f| \triangleq \{c \in \mathcal{C} \mid f(\pi(c)) = 1\}$ . The symbol  $\triangleq$  means "is defined by".

The next two subsections detail structural transformations from  $KCCL_{\mathcal{C}}$  to Boolean expressions on  $\mathscr{C}$  (i.e.,  $\mathscr{B}_{\mathscr{C}}$ ). In Boolean expressions, we use operators  $\Rightarrow$  (implication), =

$C. \ And r\acute{e}$

(equality), # (exclusion), and ite( , , ) (if ... then ... else ...) such that for any Boolean expression  $t_1, t_2, t_3$ :

$$\begin{split} t_1 &\Rightarrow t_2 \Leftrightarrow \neg t_1 \wedge t_2 \\ t_1 &= t_2 \Leftrightarrow (t_1 \wedge t_2) \vee (\neg t_1 \wedge \neg t_2) \\ t_1 &\# t_2 \Leftrightarrow \neg t_1 \vee \neg t_2 \\ \mathrm{ite}(t_1, t_2, t_3) \Leftrightarrow (t_1 \wedge t_2) \vee (\neg t_1 \wedge t_3) \end{split}$$

A first rule is given right now. This rule expresses the composition of clock relations.

$$\llbracket \mathsf{SCR}_1 \mid \mathsf{SCR}_2 \rrbracket = \llbracket \mathsf{SCR}_1 \rrbracket \wedge \llbracket \mathsf{SCR}_2 \rrbracket \quad \text{( paral )} \tag{20}$$

#### 4.3 Clock relations

#### 4.3.1 Conditional clock relation

$$[\![\mathsf{SCR}\ \mathsf{if}\ \beta]\!] = (\beta \Rightarrow [\![\mathsf{SCR}]\!]) \quad (\mathsf{rcond}\ ) \tag{21}$$

#### 4.3.2 Index-independent clock relations

Sub-clocking

Recall that  $c = b_c(c) = [c]$ .

Clock exclusion

$$\begin{bmatrix} c_1 & \# & c_2 \end{bmatrix} = (\mathsf{c}_1 \# \mathsf{c}_2) \quad \text{(excl)}$$

Clock equality

$$\llbracket c_1 \sqsubseteq c_2 \rrbracket = (\mathsf{c}_1 = \mathsf{c}_2) \quad \text{(coinc)}$$

#### 4.3.3 Index-dependent clock relations

Let  $\delta \triangleq \chi(c_1) - \chi(c_2)$ .

$Clock\ strict\ precedence$

$$\frac{\beta \triangleq (\delta = 0)}{\llbracket c_1 \, \middle| \, c_2 \rrbracket = (\beta \Rightarrow \neg c_2)} \quad \text{(sprec)}$$

Invariant:  $\delta \geqslant 0$

Clock non-strict precedence

$$\frac{\beta \triangleq (\delta = 0)}{\left\| c_1 \bowtie c_2 \right\| = \left(\beta \Rightarrow (c_1 \Rightarrow c_2)\right)} \quad \text{(prec)}$$

Invariant:  $\delta \geqslant 0$ Clock definition

$$c \triangleq SCE = (c = [SCE]) \quad (clockDefinition)$$

(27)

#### 4.4 Clock expressions

During a run, clock expressions may change. So, we introduce conditional rewriting rules for clock expressions. A rewriting is expressed as  $SCE \to SCE'$  where SCE' replaces SCE after a firing which meets the condition. As shown in Fig. 3, Sec. 2.2, an expression may own a binary word bw. In this case, the rewriting rule takes the form  $SCE, w \to SCE', w'$  where binary words are written if needed.

A simple clock expression has an associated  $implicit\ clock$  (Fig. 3). In the rules below, c stands for the clock associated with the current clock expression.

**0** and **1** are two predefined clocks. The former never ticks, the latter always ticks.

#### 4.4.1 Conditional clock expression

$$[\![\beta] ? c_1 : c_2]\!] = ite(\beta, c_1, c_2) \quad (econd)$$

(28)

#### 4.4.2 Terminating clock expressions

Forcing

$$[\![!1]\!] = 1 \quad \text{(force)} \tag{29}$$

$$!1 \rightarrow \mathbf{0}$$

(RWforce) (30)

Inhibition

$$[\![!0]\!] = 0 \quad \text{(inhib)} \tag{31}$$

$$!0$$

→  $0$  (RWinhib) (32)

Awaiting

$$\frac{\beta \triangleq (n=1)}{\llbracket c_1 \hat{\ } n \rrbracket = (\beta \wedge c_1)} \quad \text{( await )}$$

$$\frac{c_1 \in F}{c_1 \hat{1} \to \mathbf{0}} \quad \text{(RWawait1)} \tag{34}$$

$$\frac{c_1 \in F \quad n > 1}{c_1 \quad n \rightarrow c_1 \quad (n-1)} \quad \text{(RWawait2)}$$

$Strict\ sampling$

$$\llbracket c_1 \setminus c_2 \rrbracket = 0 \quad \text{(ssampl)} \tag{36}$$

$$\frac{c_1 \in F}{c_1 \wr c_2 \to c_2 \hat{1}} \quad (\text{RWssampl1}) \tag{37}$$

$$\frac{c_1 \not\in F}{c_1 \wr c_2 \to c_1 \wr c_2} \quad \text{(RWssampl2)}$$

Non strict sampling

$$\llbracket c_1 \setminus c_2 \rrbracket = (\mathsf{c}_1 \land \mathsf{c}_2) \quad (\mathsf{sampl}) \tag{39}$$

$$\frac{c_1 \in F \quad c_2 \in F}{c_1 \setminus c_2 \to \mathbf{0}} \quad (\text{RWsampl1}) \tag{40}$$

INRIA

$$\frac{c_1 \in F \quad c_2 \notin F}{c_1 \bowtie c_2 \to c_1 \choose 1} \quad (\text{RWsampl2})$$

$$\tag{41}$$

Preemption

$$\llbracket c_1 \not \downarrow c_2 \rrbracket = (\mathsf{c}_1 \land \neg \mathsf{c}_2) \quad (\text{ upto }) \tag{42}$$

$$\frac{c_2 \in F}{c_1 \not \downarrow c_2 \to \mathbf{0}} \quad (\text{RWupto}) \tag{43}$$

#### 4.4.3 Non-terminating index-independent clock expressions

$Clock\ reference$

$$[\![c]\!] = \mathsf{C} \quad (\mathsf{ref}) \tag{44}$$

$$[\![ \mathbf{1} ]\!] = 1 \quad \text{( always )} \tag{45}$$

$$[\![ \mathbf{0} ]\!] = 0$$

(never) (46)

$Clock\ concatenation$

$$\llbracket c_1 \bullet c_2 \rrbracket = \mathsf{c}_1 \quad \text{(concat)} \tag{47}$$

$$\frac{c_1 \to \mathbf{0}}{c_1 \bullet c \to c.staticDef \bullet c} \quad (\text{RWrecur})$$

$Clock\ union$

$C. \ Andr\'e$

$$[c_1 + c_2] = (c_1 \vee c_2)$$

(union) (50)

Clock intersection

$$\llbracket c_1 * c_2 \rrbracket = (\mathsf{c}_1 \wedge \mathsf{c}_2) \quad \text{(inter)} \tag{51}$$

Clock delay

$$\frac{\beta \triangleq (bw = 1.w)}{\llbracket c_1(ns) \leadsto c_2 \rrbracket = (\beta \land c_2)} \quad \text{(defer)}$$

$$\frac{c_1 \not\in F \quad c_2 \in F \quad b \in \{0, 1\}}{c_1(ns) \leadsto c_2, b.w \to c_1(ns) \leadsto c_2, w} \quad \text{(RWdefer1)}$$

$$\frac{c_1 \in F \quad c_2 \not\in F \quad h \in \mathbb{N}^*}{c_1(h.s) \leadsto c_2, w \to c_1(s) \leadsto c_2, w + (0^{h-1}.1)} \tag{RWdefer2}$$

$$\frac{c_1 \in F \ c_2 \in F \ b \in \{0,1\} \ h \in \mathbb{N}^*}{c_1(h.s) \leadsto c_2, b.w \to c_1(s) \leadsto c_2, w + (0^{h-1}.1)}$$

(RWdefer3)

#### 4.4.4 Non-terminating index-dependent clock expressions

Fastest of slower clocks

$$\beta_{1} \triangleq (\chi(c_{1}) = \chi(c))$$

$$\beta_{2} \triangleq (\chi(c_{2}) = \chi(c))$$

$$[c_{1} \lor c_{2}] = ((\beta_{1} \Rightarrow c_{1}) \land (\beta_{2} \Rightarrow c_{2}))$$

(sup)

Invariant:  $\chi(c) = \min\{\chi(c_1), \chi(c_2)\}\$ and  $\beta_1 \vee \beta_2 = 1$

$Slowest\ of\ faster\ clocks$

$$\begin{array}{c} \beta_1 \triangleq (\chi(c) = \chi(c_1)) \\ \beta_2 \triangleq (\chi(c) = \chi(c_2)) \\ \hline \llbracket c_1 \wedge c_2 \rrbracket = \left( (\beta_1 \Rightarrow c_1) \vee (\beta_2 \Rightarrow c_2) \right) \end{array} \tag{57}$$

Invariant:  $\chi(c) = \max\{\chi(c_1), \chi(c_2)\}$  and  $\beta_1 \vee \beta_2 = 1$

#### 5 Effective computation of Steps

In the previous section, a  $KCCL_{\mathcal{C}}$  specification  $\mathcal{S}$  has been transformed into a Boolean expression  $[\![\mathcal{S}]\!]$ . Now, we explain how to determine a set of clocks F to fire for a given configuration  $\chi$ .

We proceed in steps:

- 1. (implicit) construction of the logically correct solutions of  $[\![S]\!]$ . This is performed by a BDD-based solver;

- 2. choose one of these solutions according to the adopted policy;

- 3. effectively fire the clocks in F and update the state accordingly.

Step 1 is deterministic but usually yields several solutions. Step 2 makes a selection that can be non-deterministic. Step 3 applies the rewriting rules of the semantics, so that the clock system move to a new state.

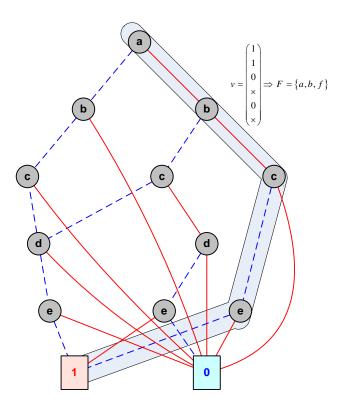

To illustrate this process, we consider a simple case, used as a running example.

#### 5.1 Logical solutions

#### 5.1.1 Example

Given  $\mathcal{C} = \{a, b, c, d, e, f\}$ , we consider the following Boolean expression

$$[S] = (d \Rightarrow b)|(b \Rightarrow a)|(c = e)|(c \Rightarrow a)|(b\#c)$$

(58)

So,  $\llbracket \mathcal{S} \rrbracket = (\neg d \lor b) \land (\neg b \lor a) \land ((c \land e) \lor (\neg c \land \neg e)) \land (\neg c \lor a) \land (\neg b \lor \neg c)$ . Note that f is not effectively used in  $\llbracket \mathcal{S} \rrbracket$ .

#### 5.1.2 Set of solutions

Let  $\mathscr{V}$  the kernel of the Boolean expression [S] defined in Eq. 59

$$\mathcal{V} \triangleq \{v : \mathcal{C} \to \{0, 1\} | \, \mathbb{S} \, \mathbb{I}(v) = 1\} \tag{59}$$

**Example**: taking the variable ordering a, b, c, d, e, f  $\mathscr{V} = \{110-0-, 10101-, -0000-\}$  using don't care values, or explicitly  $\mathscr{V} = \{110000, 110001, 110100, 110101, 101010, 101011, 000000, 000001, 100000, 100001\}$

#### 5.1.3 Auxiliary sets

With any valuation  $v \in \mathcal{V}$ , we associate a subset |v| of  $\mathcal{C}$ —subset of fireable clocks at  $\chi$ —such that

$$|v| \triangleq \{c \in \mathcal{C} \mid v(\pi(c)) = 1\} \text{ where } \pi : \mathcal{C} \to \mathscr{C} \text{ is bijective}$$

(60)

**Example**: for v = 110001,  $|v| = \{a, b, f\}$ .

The set of fireable subsets of clocks at  $\chi$  is  $\mathcal{F}$  defined in Eq. 61.

$$\mathcal{F} \triangleq \{ |v| \mid v \in \mathcal{V} \} \tag{61}$$

**Example** :  $\mathcal{F} = \{\{a,b\}, \{a,b,f\}, \{a,b,d\}, \{a,b,d,f\}, \{a,c,e\}, \{a,c,e,f\}, \emptyset, \{f\}, \{a\}, \{a,f\}\}\}.$

We also introduce the set of fireable subsets of clocks including a given clock:

$$\mathcal{F}^c \triangleq \left\{ F \in \mathcal{F} \mid c \in F \right\} \text{ for } c \in \mathcal{C}$$

(62)

**Example** :  $\mathcal{F}^b = \{\{a,b\}, \{a,b,f\}, \{a,b,d\}, \{a,b,d,f\}\}.$

#### 5.2 Subsets of clocks

#### 5.2.1 Sets of enabled/disabled clocks

Given a time system  $\langle \mathcal{C}, \mathcal{S} \rangle$ ,  $\chi$ , the subset of disabled clocks  $D \subseteq \mathcal{C}$ , and the subset of enabled clocks  $E \subseteq \mathcal{C}$  at  $\chi$  are such that

$$D = \{ c \in \mathcal{C} \mid \mathcal{F}^c = \emptyset \}$$

(63)

$$E = \mathcal{C} \setminus D \tag{64}$$

**Example** :  $D = \emptyset$ ;  $E = \{a, b, c, d, e, f\}$

#### 5.2.2 Required clocks

Given a clock  $c \in \mathcal{C}$ , a clock c' is said to be required for c in  $\langle \mathcal{C}, \mathcal{S} \rangle$  at  $\chi$  if for any solution, c in the solution implies c' in the same solution. c requires c' at  $\chi$  is denoted  $c \to_{\chi} c'$

$$(c \to_{\chi} c') \Leftrightarrow \left(\mathcal{F}^c \subseteq \mathcal{F}^{c'}\right) \tag{65}$$

**Example**:  $b \to_{\chi} a$  because  $\mathcal{F}^b = \{110000, 110001, 110100, 110101\}; \mathcal{F}^a = \{110000, 110001, 110100, 110101, 101010, 101011, 100000, 100001\}, hence <math>\mathcal{F}^b \subset \mathcal{F}^a$ . Other cases:  $d \to_{\chi} b, c \to_{\chi} a, d \to_{\chi} a, e \to_{\chi} a, c \to_{\chi} e, e \to_{\chi} c$ .

#### 5.2.3 Set of fired clocks

All the clocks in E are not necessarily simultaneously fireable. For instance b and c are in E, but there is no valuation v such that v(b) = v(c) = 1 (no wonder since b and c have been specified exclusive).

This raises the issue of choosing a *consistent* subset F of E. By consistent we mean:

- $1. \ F \ {\rm contains \ only \ simultaneously \ fireable \ clocks};$

- 2. if c is in F then all its required clocks are also in F.

In mathematical terms:

$$F$$

is a consistent set iff  $F \in \mathcal{F}$  (66)

$$(c \in F) \land (c \to_{\gamma} c') \Rightarrow (c' \in F) \tag{67}$$

This consistency criterium makes room for possibly many solutions. Several policies are predefined:

**minimal:** F is consistent and minimal:  $\forall F' \in \mathcal{F}, F \subseteq F'$ .

**maximal:** F is consistent and maximal:  $\forall F' \in \mathcal{F}, F' \subseteq F$ .

**randomCausal:** choose any c in E, and then build F that contains c, all its required clocks, and no other clocks (Given  $c \in E$ ,  $F = \{c\} \cup \{c' \in E \mid c \to_{\chi} c'\}$ ).

The last policy is called randomCausal because one enabled clock c is selected at random, and then other enabled clocks are added if they are causally linked to c (i.e., involved with c in Boolean expressions like  $c \Rightarrow c'$  or c = c', for some c'). A different random policy is proposed later.

${\bf Example} \quad : \ possible \ fireable \ sets \ are$

**minimal**  $\{a\}$  or  $\{f\}$ .

**maximal**  $\{a, b, d, f\}$  or  $\{a, c, e, f\}$ .

randomCausal for

$$a: F = \{a\}$$

$$b: F = \{a, b\}$$

$$c: F = \{a, c, e\}$$

$$d: F = \{a, b, d\}$$

$$e: F = \{a, c, e\}$$

$$f: F = \{f\}.$$

Note that the minimal and maximal solutions are not necessarily unique.

#### 5.3 Solver implementation

We use a BDD-based solver (see Annex B for a short introduction to BDDs). Let S be the BDD that represents [S].

#### 5.3.1 Computation of the sets of enabled/disabled clocks

For any  $c \in \mathcal{C}$ ,  $\mathcal{F}^c = \emptyset$  means that c never appears in any solution v in its positive form (i.e., where v(c) = 1). In terms of BDD this is expressed as "the cofactor of c in S is 0", where 0 is the void BDD. Remind that the cofactor of c in S (denoted  $S_c$ ) is obtained by substituting 1 for each occurrence of c in S.

$$(\forall c \in \mathcal{C})c \in D \Leftrightarrow \mathsf{S_c} = 0 \tag{68}$$

Algorithm 1 computes the sets D and E:

#### **Algorithm 1** Computation of E and D: ComputeSets(S)

```

Require: S is a BDD

Ensure: E is the set of enabled clocks and D the set of disabled clocks.

D \leftarrow \emptyset

E \leftarrow \emptyset

for all c \in \mathcal{C} do

if S_c = 0 then

D \leftarrow D \cup \{c\}

else

E \leftarrow E \cup \{c\}

end if

end for

return D,E

```

**Example**: No cofactor is 0, therefore D is empty and  $E = \{a, b, c, d, e, f\}$ .

#### 5.3.2 Computation of required clocks

Given a clock c, as explained above, the cofactor  $S_c$  represents the set  $\mathcal{F}^c$ . c required c' at  $\chi$  implies that for any solution v in  $\mathcal{F}^c$ , v(c')=1, or equivalently, there is no v in  $\mathcal{F}^c$  where v(c')=0. In terms of BDD, this property can be stated as " $S_c \wedge \neg c'=0$ ". Hence, algorithm 2:

**Example** : ComputeReq(e, E, S) returns  $\{e, a, c\}$ .

#### 5.3.3 Computation of a random fireable subset of clocks

Choosing a random subset of fireable clocks is just taking a random solution in  $\mathcal{F}$ . This can be done by a traversal of the BDD S and making a random choice between the 0-edge and the 1-edge, when both are possible.

#### **Algorithm 2** Computation of the required set of c at $\chi$ : ComputeReq(c, E, S)

```

Require: c is a clock, E the set of enabled clocks, S is the BDD

Ensure: The result is the required set of c at \chi.

R \leftarrow \{c\}

for all c' \in E do

if c \neq c' then

if S_c \land \neg c' = 0 then

R \leftarrow R \cup \{c'\}

end if

end for

return R

```

#### **Algorithm 3** Variant of the BDD's AnySat: RandomSat(u)

```

Require: u an internal node of a ROBDD and u \neq 0 { Recursive function modifying the

global array v }

if u = 1 then

return {Terminal node 1 reached}

\mathbf{else}

if u.high = 0 then

v(u.var) \leftarrow 0

\mathsf{RandomSat}(u.low)

else

if u.low = 0 then

v(u.var) \leftarrow 1

RandomSat(u.high)

else {both successors are possible}

if Toss() then

v(u.var) \leftarrow 1

RandomSat(u.high)

else

v(u.var) \leftarrow 0

RandomSat(u.low)

end if

end if

end if

end if

```

Algorithm RandomSat (Alg. 3) is an adaptation of the AnySat function provided by BDD environments. The terminal nodes of the ROBDD are written in bold fonts (0 and 1), while the bit values 0, 1 are written in normal font. Toss() is a function returning true or false equiprobably. The idea is to find a path from the top of the ROBDD to the terminal 1.

The reader should note that it is impossible for u.high and u.low to be both equal to  $\mathbf{0}$  in a (non  $\mathbf{0}$ ) ROBDD. This traversal algorithm is linear in the depth of the RBDD (O(|u|)).

**Example**: Let  $\times$  stand for the *don't care* bit value (0 or 1). Assume the variable ordering is a < b < c < d < e < f. RandomSat(S) sets v to one of the following solutions:  $(110 \times 0 \times)$ ,  $(10101 \times)$ ,  $(10000 \times)$ ,  $(00000 \times)$ .

Algorithm ComputeRandom (Alg. 4) returns a fireable subset of C. S = 0 is the trivial case when no clocks are fireable.

```

Algorithm 4 Computation of a random fireable set at \chi: ComputeRandom(S)

```

```

Require: S the ROBDD

Ensure: The result is the random fireable set at \chi.

R \leftarrow \emptyset

if S \neq 0 then

v \in \{0,1,\times\}^n \leftarrow \times^n \{\times \text{ stands for the } don't \ care \ \text{truth value} \}

RandomSat(S) \{\text{side-effect: modifies } v\}

for all c \in \mathcal{C} do

Let c' = \pi(c)

if (v(c') = 1) or (v(c') = x) and (v(c') = x)

```

This algorithm based on RandomSat(), which is linear in the depth of S, is far less expansive than Algorithm ComputeReq (Alg. 2). RandomSat(S) lets some variables free (don't care value). These variables are then arbitrarily set to eiher 0 or 1. A variant taking the substitution by 0 systematically, would not be adequate because it could discard causal solutions. For instance, changing  $(110\times0\times)$ ,  $(10101\times)$ ,  $(10000\times)$ ,  $(000000\times)$  respectively to (110000), (101010), (100000), (000000), never fires  $\{a,b,d\}$ , a solution which reflects the constraints  $d\Rightarrow b$  and  $b\Rightarrow a$ . Even worse, f is never fired.

RandomSat is more general and less complex than ComputeReq, but it does not restrict solutions to causally dependent clock firings. It is up to the user to choose the most appropriate algorithm.

Figure 4: ROBDD and a possible traversal

**Example**: Figure 4 is the ROBDD for the example. The variable ordering is a < b < c < d < e < f. Note that there is no node labeled f because f is not constrained in the specification. A traversal of the ROBDD has been shaded on the picture. For this path, RandomSat() has set v to  $(110 \times 0 \times)$ , and ComputeRandom() has chosen the firing set  $F_1 = \{a, b, f\}$ .  $F_2 = \{a, b\}$ ,  $F_3 = \{a, b, d\}$ ,  $F_2 = \{a, b, d, f\}$  might have been chosen as well.

Note that the left-most path in Figure 4 yields  $v = (00000 \times)$ , so that the firing set can be empty. This may be useful to model "stuttering". If this kind of behavior is unwanted, a solution consists in imposing that for each step, one clock at least fires. This can be done by adding a Boolean expression that is disjunction of all the Boolean variables:  $S \leftarrow S \land V_{c \in \mathscr{C}} c$ .

#### 6 Conclusion

This report has described the syntax and the semantics of a kernel CCSL. The underlying formal models are the  $Clock\ Model$  and the  $Time\ System$ . The Clock Model  $\mathcal M$  is a structure that consists of a finite set of discrete clocks  $\mathcal C$  and a clock constraint specifications  $\mathcal S$  written in CCSL (or more precisely in a subset of CCSL: KCCL). The Time System consists of a Clock model and a current  $configuration\ \chi$ , which indicates the index of the current instant of each clock. A Time System changes its state by  $firing\ clocks$ . A set of fired clocks is named a step. The dynamics of a Time model is represented by runs, which are sequences of steps. Of course, all firings must respect the clock constraints  $\mathcal S$ . A structural transformation of the KCCL specifications into a semantically equivalent Boolean expression has been given and illustrated on a simple example. This transformation is fully deterministic. Using a BDD-based Boolean solver, a set of fireable clocks is computed. Generally, this solution is not unique. Various policies are available to select one solution.

Clock constraints rely on three basic relations between pairs of instants:  $precedence \prec$ , exclusion #, and  $coincidence \equiv$ . The first two are classical in models such as Petri nets. They express asynchronous dependency. The third relation departs from usual concurrency models and it corresponds to synchronous dependency, a concept borrowed from synchronous reactive models. A clock constraint imposes (infinitely) many instant relations. The parallel composition of clock constraints, interpreted as a conjunction of constraints, allows the specification of complex time constraints. This has been illustrated in several papers under different aspects:

- Time model in the UML profile MARTE. This model has been defined to support both "chronometric" time and logical time. CCSL has been introduced in Annex C3 of the MARTE specification. The paper entitled "Modeling Time(s)" [5], presented at MoDELS'07, describes these two forms of time and introduced the concept of clock constraints.

- Modeling of time constraints with application to the automotive domain. Logical time is suitable for modeling complex synchronization among events. This has been illustrated on a *knock detection and control* system [7]. Another paper analyzes the end-to-end timing constraints in an ABS system [8].

- Relation with other formal models A paper [9] presented at ISORC'09, compares the CCSL approach to (Time) Petri nets and the synchronous language Signal.

- Improving the semantics of models. Standards, like AADL, have a semantics generally given in natural languages. This may give rise to ambiguity or even worse to inconsistency. CCSL has been used as a pivot language to make the semantics of the AADL communications more formal [10, 11].

- CCSL and formal verification. CCSL specifications, which rely on a formal semantics, are amenable to formal analysis. This has been illustrated on the formal verification of an Esterel program [12] (LCTES'09).

Even though CCSL appears to be very expressive, the version presented in this report is too crude a version to be easily extensible by the users. An ongoing research focuses attention on a parameterized version, offering possibilities to define new clock expressions and clock constraints as reusable modules in libraries. Last but not least, CCSL is supported by a software environment called TimeSquare, which can be downloaded on the project WEB site (http://www.inria.fr/sophia/aoste/dev/time\_square).

#### References

- [1] OMG. Unified Modeling Language, Superstructure, November 2007. Version 2.1.2 formal/2007-11-02.

- [2] The ProMARTE Consortium. *UML Profile for MARTE*, beta 2. Object Management Group, June 2008. OMG document number: ptc/08-06-08.

- [3] C. André and F. Mallet. Modèle de temps de marte et ccsl. In J-C. Rault, editor, *Actes de NEPTUNE 2009*, volume 89. GL&IS, Juin 2009.

- [4] C. Fernández. Non-sequential processes. In W. Brauer, W. Reisig, and G. Rozenberg, editors, Petri Nets: Central Models and their Properties, volume 254 of Lecture Notes in Computer Science, pages 95–115. Springer-Verlag, Sept. 1986.

- [5] C. André, F. Mallet, and R. de Simone. Modeling time(s). In G. Engels, B. Opdyke, D. C. Schmidt, and F. Weil, editors, MoDELS, volume 4735 of Lecture Notes in Computer Science, pages 559–573. Springer, 2007.

- [6] W. Reisig. *Petri nets: an introduction*. Monograph on Theoretical Computer Science. Springer, Berlin, 1985.

- [7] M-A. Peraldi-Frati C. André, F. Mallet. A multiform approach to real-time system modeling: Application to an automotive system. Technical Report RR-2007-14, I3S, Sophia-Antipolis, (F), April 2007. http://www.i3s.unice.fr/%7Emh/RR/2007/RR-07.14-C. ANDRE.pdf.

- [8] Frédéric Mallet, Marie-Agnès Peraldi-Frati, and Charles André. Marte CCSL and East-ADL2 timing requirements. Research Report 6781, INRIA, 12 2008.

- [9] Frédéric Mallet and Charles André. UML/MARTE CCSL, signal and petri nets. Research Report 6545, INRIA, 05 2008.

- [10] Charles André, Frédéric Mallet, and Robert de Simone. Modeling of immediate vs. delayed data communications: from AADL to UML marte. In FDL, pages 249–254. ECSI, September 2007.

$C. \ Andr\'e$

[11] Frédéric Mallet, Robert de Simone, and Laurent Rioux. Event-triggered vs. time-triggered communications with UML Marte. In *FDL*, pages 154–159. IEEE, September 2008.

[12] Charles André and Frédéric Mallet. Combining CCSL and Esterel to specify and verify time requirements. Research Report 6839, INRIA, 02 2009. published in the proceedings of LCTES'09.

#### A Binary Words

#### A.1 Finite/infinite binary words

**Definition A.1** (Set of bit values).  $\mathbb{B} = \{0, 1\}$ .

**Definition A.2** (Finite binary word). A finite binary word is a word of  $(0+1)^*$ .

**Definition A.3** (Infinite binary word). An *infinite binary word* is a word of  $(0+1)^{\omega}$ .

**Definition A.4** (Periodic binary word). A *periodic binary word* is an infinite binary word defined by the following grammar:

$$w ::= u (v)^{\omega}$$

$$u ::= \varepsilon \mid 0 \mid 1 \mid 0 \bullet u \mid 1 \bullet u$$

$$v ::= 0 \mid 1 \mid 0 \bullet v \mid 1 \bullet v$$

u is called the *prefix* of w, v is the *period* of w, and  $(v)^{\omega} = \lim_{n} v^{n}$  denotes the infinite repetition of v.  $\varepsilon$  is the empty binary word. In order to avoid confusion between parentheses denoting periodic binary words and usual parentheses, the former are colored red. The associated  $\omega$  symbol is also red.

For convenience, we adopt a power notion for repeated bits:

$$b^{n} = b \bullet b^{n-1} \quad (b \in \mathbb{B}, n \in \mathbb{N}^{*})$$

$$(69)$$

$$b^0 \triangleq \varepsilon \tag{70}$$

A periodic binary word with an empty prefix is called a *strictly periodic binary word*  $(w = (v)^{\omega})$ .

A periodic binary word has infinitely many representations:

Let

$$b \in \mathbb{B}, u, v \in \mathbb{B}^*, u \bullet b (v \bullet b)^{\omega} = u (b \bullet v)^{\omega}$$

(71)

Notation A.1 (Length of a binary word). |w| denotes the length of the binary word w.

Notation A.2.  $|w|_b$  denotes the number of bits set to  $b \in \mathbb{B}$  in the binary word w.

Notation A.3. w[k] denotes the  $k^{th}$  bit of the binary word w.

Notation A.4. w[k..l] denotes the (sub) binary word from w starting at the  $k^{\text{th}}$  bit upto the  $l^{\text{th}}$  bit included.

Notation A.5. w[k..] denotes the (sub) binary word from w starting at the  $k^{th}$  bit. Possibly infinite.

#### A.2 Operations on binary words

**Definition A.5** (Number of 1 upto k).  $w \downarrow k$  denotes the number of 1 upto the k<sup>th</sup> bit included in the binary word w.

$$w \downarrow k \triangleq |w[1..k]|_1$$

Let  $k \in \mathbb{N}^*, b \in \mathbb{B}, w$  a binary word

$$w \downarrow 0 \triangleq 0 \tag{72}$$

$$b \bullet w \downarrow k = b + (w \downarrow (k-1)) \tag{73}$$

**Definition A.6** (Index of the  $k^{\text{th}}$  one).  $w \uparrow k$  denotes the index of the  $k^{\text{th}}$  one in the binary word w.

$$w \uparrow k \triangleq j \in \mathbb{N}^*$$

such that  $w[j] = 1 \land (w \downarrow j = k)$

Let  $k \in \mathbb{N}^*, w$  a binary word

$$w \uparrow 0 \triangleq 0 \tag{74}$$

$$w \uparrow k \triangleq \omega \text{ if } |w|_1 < k \tag{75}$$

$$(1 \bullet w) \uparrow k = 1 + w \uparrow (k - 1) \tag{76}$$

$$(0 \bullet w) \uparrow k = 1 + w \uparrow k \tag{77}$$

**Definition A.7** (Binary word composition). For any two binary words  $w_1$  and  $w_2$ , the binary word composition ( $\circ$  operator) is defined as follows:

$$(0 \bullet w_1) \circ w_2 = 0 \bullet (w_1 \circ w_2)$$

$$(1 \bullet w_1) \circ (b \bullet w_2) = b \bullet (w_1 \circ w_2) \text{ (for } b \in \mathbb{B})$$

$$(0 \bullet w_1) \circ \varepsilon = 0 \bullet (w_1 \circ \varepsilon)$$

$$(1 \bullet w_1) \circ \varepsilon = \varepsilon$$

$$\varepsilon \circ w_2 = \varepsilon$$

Properties:

$$|w_1 \circ w_2| = \min\{|w_1|, w_1 \uparrow (|w_2| + 1) - 1\}$$

(78)

**Definition A.8** (Binary word union). For any two binary words  $w_1$  and  $w_2$ , the binary word addition (+ operator) is defined as follows:

$$(b_1 \bullet w_1) + (b_2 \bullet w_2) = (b_1 \text{ or } b_2) \bullet (w_1 + w_2)$$

$$\varepsilon + w = w$$

$$w + \varepsilon = w$$

$$\varepsilon + \varepsilon = \varepsilon$$

#### B Binary Decision Diagram

**Definition B.1** (BDD). A Binary Decision Diagram (BDD) is a rooted, directed acyclic graph with

- one or more terminal nodes of out-degree 0 labeled 0 or 1, and

- a set of internal nodes u of out-degree 2. The successors of u are u.low and u.high. The Boolean variable u.var is associated with u.

**Definition B.2** (OBDD). An Ordered BDD (OBDD) is a BDD such that on all paths the variables respect a given linear order  $x_1 < x_2 < \cdots < x_n$ .

**Definition B.3** (ROBDD). A Reduced OBDD (ROBDD) is an OBDD such that

• (uniqueness) no two distinct nodes u and v have the same variable name and low-and high-successor, i.e.,

$$(u.var = v.var) \land (u.low = v.low) \land (u.high = v.high) \Rightarrow u = v$$

• (non-redundant tests) no internal node has identical low- and high-successor, i.e.,

$$u.low \neq u.high$$

A ROBDD can represent any Boolean function. Each node u defines a Boolean expression  $t^u$  such that

$$t^0 = 0$$

$t^1 = 1$

$t^u = \text{if } u \text{ then } t^{u.high} \text{ else } t^{u.low}$

Given a variable ordering  $x_1 < x_2 < \dots < x_n$ , with each node u of the ROBDD, we associate the function f that maps  $(b_1, b_2, \dots, b_n) \in \mathbb{B}^n$  to the truth value of  $t^u[b_1/x_1, b_2/x_2, \dots, x_n/b_n]$ .

**Theorem B.1** (Canonicity of ROBDD). For any function  $f : \mathbb{B}^n \to \mathbb{B}$  there is exactly one ROBDD u with variable ordering  $x_1 < x_2 < \cdots < x_n$  such that  $f^u = f(x_1, \cdots, x_n)$ .

$C. \ Andr\'e$

## Contents

| 1 | Introduction                    |                                                                                                                |          |  |  |  |  |

|---|---------------------------------|----------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

| 2 | Met 2.1 2.2                     | camodels Time Model                                                                                            |          |  |  |  |  |

| 3 | Synt 3.1 3.2 3.3 3.4 3.5        | Simple KCCL                                                                                                    | 11<br>13 |  |  |  |  |

| 4 | Sem<br>4.1<br>4.2<br>4.3<br>4.4 | Clock Model                                                                                                    | 15<br>16 |  |  |  |  |

| 5 | Effe<br>5.1<br>5.2<br>5.3       | ctive computation of Steps         Logical solutions          Subsets of clocks          Solver implementation | 22       |  |  |  |  |

| 6 | Con                             | nclusion 2                                                                                                     |          |  |  |  |  |

| A | A.1                             | ary Words Finite/infinite binary words                                                                         |          |  |  |  |  |

| В | Bina                            | ary Decision Diagram                                                                                           | 33       |  |  |  |  |

#### Unité de recherche INRIA Sophia Antipolis 2004, route des Lucioles - BP 93 - 06902 Sophia Antipolis Cedex (France)

Unité de recherche INRIA Futurs : Parc Club Orsay Université - ZAC des Vignes

4, rue Jacques Monod - 91893 ORSAY Cedex (France)

Unité de recherche INRIA Lorraine : LORIA, Technopôle de Nancy-Brabois - Campus scientifique

615, rue du Jardin Botanique - BP 101 - 54602 Villers-lès-Nancy Cedex (France)

Unité de recherche INRIA Rennes : IRISA, Campus universitaire de Beaulieu - 35042 Rennes Cedex (France)

Unité de recherche INRIA Rhône-Alpes : 655, avenue de l'Europe - 38334 Montbonnot Saint-Ismier (France)

Unité de recherche INRIA Rocquencourt : Domaine de Voluceau - Rocquencourt - BP 105 - 78153 Le Chesnay Cedex (France)