# Mapping pipeline skeletons onto heterogeneous platforms.

Anne Benoit, Yves Robert

#### ▶ To cite this version:

Anne Benoit, Yves Robert. Mapping pipeline skeletons onto heterogeneous platforms.. [Research Report] Laboratoire de l'informatique du parallélisme. 2007, 2+31p. hal-02101753

# HAL Id: hal-02101753

https://hal-lara.archives-ouvertes.fr/hal-02101753

Submitted on 17 Apr 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Mapping pipeline skeletons onto heterogeneous platforms

#### Anne Benoit and Yves Robert

LIP, ENS Lyon, 46 Allée d'Italie, 69364 Lyon Cedex 07, France UMR 5668 - CNRS - ENS Lyon - UCB Lyon - INRIA {Anne.Benoit|Yves.Robert}@ens-lyon.fr

January 2007

LIP Research Report RR-2007-05. Updated version of RR-2006-40.

#### Abstract

Mapping applications onto parallel platforms is a challenging problem, that becomes even more difficult when platforms are heterogeneous –nowadays a standard assumption. A high-level approach to parallel programming not only eases the application developer's task, but it also provides additional information which can help realize an efficient mapping of the application.

In this paper, we discuss the mapping of pipeline skeletons onto different types of platforms: Fully Homogeneous platforms with identical processors and interconnection links; Communication Homogeneous platforms, with identical links but different speed processors; and finally, Fully Heterogeneous platforms. We assume that a pipeline stage must be mapped on a single processor, and we establish new theoretical complexity results for different mapping policies: a mapping can be required to be one-to-one (a processor is assigned at most one stage), or interval-based (a processor is assigned an interval of consecutive stages), or fully general. In particular, we show that determining the optimal interval-based mapping is NP-hard for Communication Homogeneous platfors, and this result assesses the complexity of the well-known chains-to-chains problem for different-speed processors. We provide several efficient polynomial heuristics for the most important policy/platform combination, namely interval-based mappings on Communication Homogeneous platforms. These heuristics are compared to the optimal result provided by the formulation of the problem in terms of the solution of an integer linear program, for small problem instances.

#### 1 Introduction

Mapping applications onto parallel platforms is a difficult challenge. Several scheduling and load-balancing techniques have been developed for homogeneous architectures (see [29] for a survey) but the advent of heterogeneous clusters has rendered the mapping problem even more difficult. Typically, such clusters are composed of different-speed processors interconnected either by plain Ethernet (the low-end version) or by a high-speed switch (the high-end counterpart), and they constitute the experimental platform of choice in most academic or industry research departments.

In this context of heterogeneous platforms, a structured programming approach rules out many of the problems which the low-level parallel application developer is usually confronted to, such as deadlocks or process starvation. Moreover, many real applications draw from a range of well-known solution paradigms, such as pipelined or farmed computations. High-level approaches based on algorithmic skeletons [12, 27] identify such patterns and seeks to make it easy for an application developer to tailor such a paradigm to a specific problem. A library of skeletons is provided to the programmer, who can rely on these already coded patterns to express the communication scheme within its own application. Moreover, the use of a particular skeleton carries with it considerable information about implied scheduling dependencies, which we believe can help to address the complex problem of mapping a distributed application onto a heterogeneous platform.

In this paper, we therefore consider applications that can be expressed as algorithmic skeletons, and we focus on the pipeline skeleton, which is one of the most widely used. In such applications, a series of tasks enter the input stage and progress from stage to stage until the final result is computed. Each stage has its own communication and computation requirements: it reads an input file from the previous stage, processes the data and outputs a result to the next stage. For each task, initial data is input to the first stage, and final results are output from the last stage. The pipeline operates in synchronous mode: after some latency due to the initialization delay, a new task is completed every period. The period is defined as the longest cycle-time to operate a stage, and is the inverse of the throughput that can be achieved.

The problem of mapping pipeline skeletons onto parallel platforms has received some attention, and we survey related work in Section 7. In particular, Subhlok and Vondran [32, 33] have dealt with this problem on homogeneous platforms. In this paper, we extend their work and target heterogeneous clusters. Our main goal is to assess the additional complexity induced by the heterogeneity of processors, and/or of communication links. As in [32], we aim at deriving optimal mappings, i.e. mappings which minimize the period, or equivalently maximize the throughput, of the system. Each pipeline stage can be seen as a sequential procedure which may perform disc accesses or write data in the memory for each task. This data may be reused from one task to another, and thus the rule of the game is always to process the tasks in a sequential order within a stage. Moreover, due to the possible local memory accesses, a given stage must be mapped onto a single processor: we cannot process half of the tasks on a processor and the remaining tasks on another without exchanging intra-stage information, which might be costly and difficult to implement.

In this paper, we focus on pipeline skeletons and thus we enforce the rule that a given stage is mapped onto a single processor. In other words, a processor that is assigned a stage will execute the operations required by this stage (input, computation and output) for all the tasks fed into the pipeline. The optimization problem can be stated informally as follows: which stage to assign to which processor? We consider several variants, in which we require the mapping to be one-to-one (a processor is assigned at most one stage), or interval-based (a processor is assigned an interval of consecutive stages), or fully general.

In addition to these three mapping categories, we target three different platform types. First, Fully Homogeneous platforms have identical processors and interconnection links. Next, Communication Homogeneous platforms, with identical links but different speed processors, introduce a first degree of heterogeneity. Finally, Fully Heterogeneous platforms constitute the most difficult instance, with different speed processors and different capacity links. The main objective of the paper is to assess the complexity of each mapping variant onto each platform type. We establish several new complexity results for this important optimization problem, and we derive efficient polynomial heuristics for interval-based mappings onto Communication Homogeneous platforms. These heuristics are compared through simulation; moreover, their absolute performance is assessed owing to the formulation of the problem in terms of an integer linear program, whose solution returns the optimal result for small problem instances.

An interesting consequence of one of the new complexity results proved in this paper (see Section 3.2.2) is the following. Given an array of n elements  $a_1, a_2, \ldots, a_n$ , the well-known chainsto-chains problem is to partition the array into p intervals whose element sums are well balanced (technically, the aim is to minimize the largest sum of the elements of any interval). This problem has been extensively studied in the literature (see the pioneering papers [11, 17, 25] and the survey [26]). It amounts to load-balance n computations whose ordering must be preserved (hence the restriction to intervals) onto p identical processors. The advent of heterogeneous clusters naturally leads to the following generalization: can we partition the n elements into p intervals whose element sums match p prescribed values (the processor speeds) as closely as possible. The NP-hardness of this important extension of the chains-to-chains problem is established in Section 3.2.2.

The rest of the paper is organized as follows. Section 2 is devoted to a detailed presentation of the target optimization problems. Next in Section 3 we proceed to the complexity results. In Section 4 we introduce several polynomial heuristics to solve the mapping problem. These heuristics are compared through simulations, whose results are analyzed in Section 5. Section 6 introduces the linear formulation of the problem and assesses the absolute performance of the heuristics when the optimal solution can be found. Section 7 is devoted to an overview of related work. Finally, we state some concluding remarks in Section 8.

### 2 Framework

We outline in this section the characteristics of the applicative framework, as well as the model for the target platform. Next we detail the objective function, chosen as the maximum period of a processor to execute all the pipeline stages assigned to it.

Figure 1: The application pipeline.

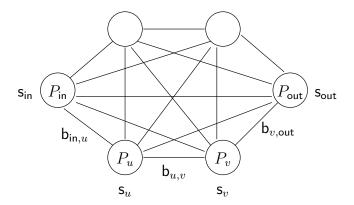

Figure 2: The target platform.

#### 2.1 Applicative framework

We consider a pipeline of n stages  $S_k$ ,  $1 \le k \le n$ , as illustrated on Figure 1. Tasks are fed into the pipeline and processed from stage to stage, until they exit the pipeline after the last stage.

The k-th stage  $S_k$  receives an input from the previous stage, of size  $\delta_{k-1}$ , performs a number of  $w_k$  computations, and outputs data of size  $\delta_k$  to the next stage. The first stage  $S_1$  receives an input of size  $\delta_0$  from the outside world, while the last stage  $S_n$  returns the result, of size  $\delta_n$ , to the outside world.

# 2.2 Target platform

We target a heterogeneous platform (see Figure 2), with p processors  $P_u$ ,  $1 \le u \le p$ , fully interconnected as a (virtual) clique. There is a bidirectional link  $link_{u,v}: P_u \to P_v$  between any processor pair  $P_u$  and  $P_v$ , of bandwidth  $b_{u,v}$ . Note that we do not need to have a physical link between any processor pair. Instead, we may have a switch, or even a path composed of several physical links, to interconnect  $P_u$  and  $P_v$ ; in the latter case we would retain the bandwidth of the slowest link in the path for the value of  $b_{u,v}$ .

Communications contention is taken care of by enforcing the *one-port* model [9, 10]. In this model, a given processor can be involved in a single communication at any time-step, either a send or a receive. However, independent communications between distinct processor pairs can take place simultaneously. The one-port model seems to fit the performance of some current MPI implementations, which serialize asynchronous MPI sends as soon as message sizes exceed a few megabytes [28].

In the most general case, we have fully heterogeneous platforms, with different processors speeds and link capacities. The speed of processor  $P_u$  is denoted as  $s_u$ , and it takes  $X/s_u$  time-units for  $P_u$  to execute X floating point operations. We also enforce a linear cost model for communications, hence it takes  $X/b_{u,v}$  time-units to send (resp. receive) a message of size X to (resp. from)  $P_v$ . We classify below particular cases which are important, both from a theoretical and practical perspective:

**Fully Homogeneous**— These platforms have identical processors  $(s_u = s)$  and links  $(b_{u,v} = b)$ . They represent typical parallel machines.

Communication Homogeneous— These platforms have different-speed processors ( $s_u \neq s_v$ ) interconnected by links of same capacities ( $b_{u,v} = b$ ). They correspond to networks of workstations with plain TCP/IP interconnects or other LANs.

Fully Heterogeneous— These are the most general, fully heterogeneous architectures, with  $s_u \neq s_v$  and  $b_{u,v} \neq b_{u',v'}$ . Hierarchical platforms made up with several clusters interconnected by slower backbone links can be modeled this way.

Finally, we assume that two special additional processors  $P_{in}$  and  $P_{out}$  are devoted to input/output data. Initially, the input data for each task resides on  $P_{in}$ , while all results must be returned to and stored in  $P_{out}$ . Of course we may have a single processor acting as the interface for the computations, i.e.  $P_{in} = P_{out}$ .

#### 2.3 Mapping problem

The general mapping problem consists in assigning application stages to platform processors. However, some constraints can be added to the mapping to ease the implementation of the application, for instance by imposing to map a single stage onto each processor. Different instances of the mapping problem are discussed below.

#### 2.3.1 One-to-one Mapping

Assume temporarily, for the sake of simplicity, that each stage  $S_k$  of the application pipeline is mapped onto a distinct processor  $P_{\mathsf{alloc}(k)}$  (which is possible only if  $n \leq p$ ). For convenience, we create two fictitious stages  $S_0$  and  $S_{n+1}$ , and we assign  $S_0$  to  $P_{\mathsf{in}}$  and  $S_{n+1}$  to  $P_{\mathsf{out}}$ .

What is the period of  $P_{\mathsf{alloc}(k)}$ , i.e. the minimum delay between the processing of two consecutive tasks? To answer this question, we need to know which processors the previous and next stages are assigned to. Let  $t = \mathsf{alloc}(k-1)$ ,  $u = \mathsf{alloc}(k)$  and  $v = \mathsf{alloc}(k+1)$ .  $P_u$  needs  $\delta_{k-1}/\mathsf{b}_{t,u}$  to receive the input data from  $P_t$ ,  $\mathsf{w}_k/\mathsf{s}_u$  to process it, and  $\delta_k/\mathsf{b}_{u,v}$  to send the result to  $P_v$ , hence a cycle-time of  $\delta_{k-1}/\mathsf{b}_{t,u}+\mathsf{w}_k/\mathsf{s}_u+\delta_k/\mathsf{b}_{u,v}$  for  $P_u$ . The period achieved with the mapping is the maximum of the cycle-times of the processors, this corresponds to the rate at which the pipeline can be activated.

In this simple instance, the optimization problem can be stated as follows: determine a one-to-one allocation function alloc:  $[1,n] \to [1,p]$  (augmented with  $\mathsf{alloc}(0) = \mathsf{in}$  and  $\mathsf{alloc}(n+1) = \mathsf{out}$ ) such that

$$T_{\mathsf{period}} = \max_{1 \le k \le n} \left\{ \frac{\delta_{k-1}}{\mathsf{b}_{\mathsf{alloc}(k-1),\mathsf{alloc}(k)}} + \frac{\mathsf{w}_k}{\mathsf{s}_{\mathsf{alloc}(k)}} + \frac{\delta_k}{\mathsf{b}_{\mathsf{alloc}(k),\mathsf{alloc}(k+1)}} \right\} \tag{1}$$

is minimized. We denote by ONE-TO-ONE MAPPING the previous optimization problem.

#### 2.3.2 Interval Mapping

However, one-to-one mappings may be unduly restrictive. A natural extension is to search for interval mappings, i.e. allocation functions where each participating processor is assigned an interval of consecutive stages. Intuitively, assigning several consecutive tasks to the same processors will increase their computational load, but may well dramatically decrease communication requirements. In fact, the best interval mapping may turn out to be a one-to-one mapping, or instead may enroll only a very small number of fast computing processors interconnected by high-speed links.

Interval mappings constitute a natural and useful generalization of one-to-one mappings (not to speak of situations where p < n, where interval mappings are mandatory). A major objective of this paper is to assess the performance of general interval mappings as opposed to pure one-to-one allocations.

For the sake of completeness, we formally write the optimization problem associated to interval mappings. We need to express that the intervals achieve a partition of the original set of stages  $S_1$  to  $S_n$ . We search for a partition of [1..n] into m intervals  $I_j = [d_j, e_j]$  such that  $d_j \leq e_j$  for  $1 \leq j \leq m$ ,  $d_1 = 1$ ,  $d_{j+1} = e_j + 1$  for  $1 \leq j \leq m - 1$  and  $e_m = n$ . Interval  $I_j$  is mapped onto processor  $P_{\mathsf{alloc}(j)}$ , and the period is expressed as

$$T_{\mathsf{period}} = \max_{1 \le j \le m} \left\{ \frac{\delta_{d_j - 1}}{\mathsf{b}_{\mathsf{alloc}(j - 1), \mathsf{alloc}(j)}} + \frac{\sum_{i = d_j}^{e_j} \mathsf{w}_i}{\mathsf{s}_{\mathsf{alloc}(j)}} + \frac{\delta_{e_j}}{\mathsf{b}_{\mathsf{alloc}(j), \mathsf{alloc}(j + 1)}} \right\} \tag{2}$$

Here, we assume that  $\mathsf{alloc}(0) = \mathsf{in}$  and  $\mathsf{alloc}(m+1) = \mathsf{out}$ . The optimization problem Interval Mapping is to determine the best mapping, over all possible partitions into intervals, and over all processor assignments.

#### 2.3.3 General Mapping

The most general mappings may be more complicated than interval-based mappings: a processor  $P_u$  can be assigned any subset of stages.

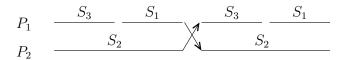

Let us consider the following example with n=3 stages and p=2 processors. We also use a third processor  $P_0=P_{\mathsf{in}}=P_{\mathsf{out}}$  for input/output, with no processing capacity  $(\mathsf{s}_0=0)$ .

If the platform is Fully Homogeneous, let us consider a case in which the second stage requires two times more computation than the other stages:  $w_1 = w_3 = 1$  and  $w_2 = 2$ , and where the communications are negligible ( $\delta_i = 0$ ). The platform parameters (s, b) are set to 1. An interval-based mapping needs to map either the two first stages or the two last ones on a same processor, which will have a cycle time of 1 + 2 = 3 (computations of the two stages). An intuitive solution would however be to map the first and third stages on one processor, and the second stage alone, relaxing the interval constraint, hoping to reach a cycle time of 2 for both processors (with a good load-balancing), which will work in parallel. Figure 3 illustrates such a mapping, and the desired behavior of the application.

Figure 3: Example of general mapping.

During a cycle,  $P_1$  processes a task for  $S_3$  and then a task for  $S_1$  (communications from/to  $P_0$  can be neglected), while  $P_2$  processes a task for  $S_2$ . Communications occur between each cycle, when  $P_1$  sends output from  $S_1$  and  $P_2$  sends output from  $S_2$ .

However, we always assumed in this paper that a stage is implemented in a static and synchronous way, using the one-port model, which is a realistic hypothesis on the implementation of the application. With such a model, if  $P_1$  starts to send the output from  $S_1$ , it will be blocked until  $P_2$  completes the receive, while  $P_2$  is sending its own output before receiving the next task for  $S_2$ . This leads to a deadlock with a straightforward implementation.

The solution would be to create a process for each stage, and map the independent processes on processors, possibly several processes on a single processor. In order to obtain asynchronous communications, each process should run three threads, one for input, one for computation and one for output. Each thread knows where to expect its input from, and where to redirect its output to, so it can post asynchronous messages and poll for completion. When an input is completed, it hands over the data to the computation thread, and so on. Overall, the computation advances asynchronously, in a greedy fashion: each action is executed as soon as it is ready. Computations and communications are preemptive. On each processor and at any time step, several processes share the CPU for computations related to different stages, and several communications take place simultaneously and share the bandwidth (of the link and/or the network card). This scheme requires as many communication buffers as there are stages/processes assigned to the processor.

With such an implementation, we would like to define the cycle-time of a processor by the time needed to execute one instance of each of its stages, and the period as the maximum of the processor cycle-times. If  $P_u$  handles the set of stages  $\mathsf{stages}(u)$ , and  $\mathsf{stage}\ i$  is mapped on processor  $\mathsf{alloc}(i)$ , the period is defined by:

$$T_{\mathsf{period}} = \max_{1 \le u \le p} \left\{ \sum_{i \in \mathsf{stages}(u)} \left( \Delta^{u}_{\mathsf{alloc}(i-1)} \frac{\delta_{i-1}}{\mathsf{b}_{\mathsf{alloc}(i-1),u}} + \frac{\mathsf{w}_{i}}{\mathsf{s}_{u}} + \Delta^{\mathsf{alloc}(i+1)}_{u} \frac{\delta_{i}}{\mathsf{b}_{u,\mathsf{alloc}(i+1)}} \right) \right\} \tag{3}$$

where  $\Delta_u^v = 1$  if  $u \neq v$  and 0 otherwise. In equation (3), we pay the input communication for a stage  $S_i$  only if stage  $S_{i-1}$  is not mapped on the same processor (and similarly for the output communication).

However, it is very difficult to assess whether the above period will actually be achieved in a real-life implementation. Delays may occur due to the dependency paths ( $P_u$  sending data to  $P_v$  that returns it to  $P_u$ , and the like), leading to idle times (waiting on polling). Races may occur and slow down, say, two simultaneous communications involving non-disjoint processor pairs. Finally, control overhead and cost of switching processes may prove very high. At least an optimistic view is that the achieved period will be only slightly larger than the above theoretical bound, but this would require to be validated experimentally.

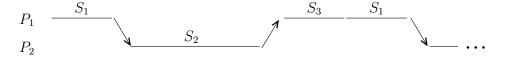

If we restrict ourselves to the one-port model, and consider the 3-stages example again with the first and third stages mapped on the first processor, the straightforward implementation leads to a period of 4 because  $P_1$  always wait for a task to go through  $S_2$  on  $P_2$  before it goes through  $P_3$ . This leads to the execution scheme of Figure 4.

Figure 4: Example of general mapping with the one-port model.

In this execution scheme, we enforced a natural rule that is implied by a non-preemptive implementation. Let  $S_i(k)$  denote the processing in stage  $S_i$  for the incoming task number k. Then, if  $S_i$  and  $S_j$  are two stages assigned to  $P_u$  with i < j, then  $P_u$  executes  $S_j(k)$  before  $S_i(k+1)$ . With this rule, the cycle-time of a processor is the duration of the path that goes from the input of its first stage all the way to the output of its last stage. Let us define first(u) and last(u) as the first and last index, respectively, which are assigned to  $P_u$ .

$$\mathsf{cycle\text{-}time}(P_u) = \frac{\delta_{\mathsf{first}(u)-1}}{\mathsf{b}_{\mathsf{alloc}(\mathsf{first}(u)-1),u}} + \sum_{i=\mathsf{first}(u)}^{\mathsf{last}(u)} \left( \frac{\mathsf{w}_i}{\mathsf{s}_{\mathsf{alloc}(i)}} + \Delta_{\mathsf{alloc}(i)}^{\mathsf{alloc}(i+1)} \frac{\delta_i}{\mathsf{b}_{\mathsf{alloc}(i),\mathsf{alloc}(i+1)}} \right) \tag{4}$$

$$T_{\mathsf{period}} = \max_{1 < u < p} \mathsf{cycle-time}(P_u) \tag{5}$$

In equation (4), we always pay the first communication and the last one, by definition of first(u) and last(u), but we need to take care that some consecutive stages might be mapped onto the same processor.

Obviously, this period is longer than the one obtained with equation (3), but with these assumptions, we know how to implement the application in a natural way, and we can ensure that this (longer) period will be achieved. All actions can be organized (scheduled statically) and the period can be characterized analytically. This allows us to avoid the complex dynamic scheme.

In this case, it does not seem very interesting to map non consecutive stages on a same processor, because it has to wait for the processing of the intermediate stages, which leads to idle time. Actually, we will see in Section 3 that interval-based mappings are always as good as general mappings on *Communication Homogeneous* platforms. We still consider the general optimization problem, since general mappings may outperform interval-based ones in some particular cases, even with the definition of the period of equation (5).

Consider the following example with n=3 stages and p=2 processors. The target architecture is characterized by  $s_1=b_{0,2}=b_{1,2}=1$  and  $s_2=b_{0,1}=10$ . As for the application, we have  $\delta_0=\delta_3=w_2=10$  and  $\delta_1=\delta_2=w_1=w_3=1$ . If we map  $\mathcal{S}_2$  on  $P_1$ , then  $T_{\mathsf{period}}\geq \frac{w_2}{s_1}=10$ . If we map  $\mathcal{S}_1$  on  $P_2$ , then  $T_{\mathsf{period}}\geq \frac{\delta_0}{b_{0,2}}=10$ . Similarly, if we map  $\mathcal{S}_3$  on  $P_2$ , then  $T_{\mathsf{period}}\geq \frac{\delta_3}{b_{0,2}}=10$ . There exists a single mapping whose period is smaller than 10: indeed, we can map  $\mathcal{S}_1$  and  $\mathcal{S}_3$  on  $P_1$  and  $\mathcal{S}_2$  on  $P_2$ , and the period becomes

$$T_{\text{period}} = \frac{\delta_0}{b_{0,1}} + \frac{w_1}{s_1} + \frac{\delta_1}{b_{1,2}} + \frac{w_2}{s_2} + \frac{\delta_2}{b_{1,2}} + \frac{w_3}{s_1} + \frac{\delta_3}{b_{0,1}} = 7$$

(6)

In equation (6), we have computed the length of the cycle that  $P_1$  repeats for every incoming task:

- read data for task number k from  $P_{in}$

- compute  $S_1(k)$ , i.e. stage 1 for that task

- send data to  $P_2$ , wait for  $P_2$  to process it (stage  $S_2(k)$ ) and to return the results

- compute stage  $S_3(k)$ , send output data to  $P_{\text{out}}$

- proceed to task number k+1 and repeat entire cycle, starting with input data for  $S_1(k+1)$  Because the operation of  $P_2$  is entirely included into that of  $P_1$ ,  $P_1$  has the longest cycle-time, thereby defining the period. This is how we derived that  $T_{period} = 7$  in the example, in full accordance to equations (4) and (5).

This little example shows that general mappings may be superior to interval-based mappings, and provides a motivation to study the corresponding optimization problem, denoted as GENERAL MAPPING.

In this paper, we mostly concentrate on interval-based mappings, because they realize the best trade-off between efficiency and simplicity. One-to-one mappings are not general enough, in particular when resources are in limited number, or when communications have a higher cost. General

|                    | Fully Homogeneous                   | Comm. Homogeneous        | Fully Heterogeneous |

|--------------------|-------------------------------------|--------------------------|---------------------|

| One-to-one Mapping | polynomial (bin. search)            | polynomial (bin. search) | NP-complete         |

| Interval Mapping   | polynomial (dyn. prog [32, 33])     | NP-complete              | NP-complete         |

| General Mapping    | same complexity as Interval Mapping |                          | NP-complete         |

Table 1: Complexity results for the different instances of the mapping problem.

mappings require important changes in the model and its implementation, and may be too complex to deal with efficiently for the application programmer. We still address the complexity of all mapping problems, including general mappings, but for practical developments we limit ourselves to one-to-one and interval-based mappings. Also, we privilege *Communication Homogeneous* platforms, which are the most representative of current experimental architectures.

# 3 Complexity results

To the best of our knowledge, this work is the first to study the complexity of the various mapping strategies (One-to-one Mapping, Interval Mapping and General Mapping), for each of the different platform categories (Fully Homogeneous, Communication Homogeneous and Fully Heterogeneous). Table 1 summarizes all our new results.

For Fully Homogeneous or Communication Homogeneous platforms, determining the optimal One-to-one Mapping can be achieved through a binary search over possible periods, invoking a greedy algorithm at each step. The problem surprisingly turns out to be NP-hard for Fully Heterogeneous platforms. The binary search algorithm for One-to-one Mapping is outlined in Section 3.1.

The Interval Mapping problem is more complex to deal with. For *Fully Homogeneous* platforms (see Section 3.2.1), we simply recall the optimal dynamic programming algorithm of Subhlok and Vondran [32, 33]. For *Communication Homogeneous* platforms (see Section 3.2.2), the problem turns out to be NP-hard. Quite interestingly, this result is a consequence of the fact that the natural extension of the chains-to-chains problem [26] to different-speed processors is NP-hard. Furthermore, in Section 3.2.3, we also prove the nice theoretical result that interval-based mappings are dominant for *Communication Homogeneous* platforms: no need to consider general mappings for such platforms, we can restrict the search to interval-based mappings.

Finally, all three optimization problems are NP-hard for *Fully Heterogeneous* platforms. The proof of these results is provided in Section 3.3.

## 3.1 One-to-one Mapping

**Theorem 1.** For Fully Homogeneous and Communication Homogeneous platforms, the optimal One-to-one Mapping can be determined in polynomial time.

**Proof.** We provide a constructive proof: we outline a binary-search algorithm that iterates until the optimal period is found. At each step, a greedy algorithm is used to assign stages to processors in a one-to-one fashion. The greedy algorithm succeeds if and only if the period is feasible. If the algorithm does succeed, we decrease the target period, otherwise we increase it, and then proceed to the next step. For theory-oriented readers, we easily check that the number of steps is indeed polynomial in the problem size: in a word, we use a binary search over an interval whose length can

be bounded by the maximum values of the application/platform parameters, hence a number of steps proportional to the logarithm of this value, which in turn is the encoding size of the problem. For more practice-oriented readers, only a few seconds are needed to obtain the period with a precision of  $10^{-4}$  for a reasonable problem size. See for instance the practical experiments reported in Section 5.

Let us now describe the most interesting part of the procedure, namely the greedy assignment algorithm for a prescribed value  $T_{period}$  of the achievable period. Recall that there are n stages to map onto  $p \ge n$  processors in a one-to-one fashion. Also, we target Communication Homogeneous platforms with different-speed processors  $(s_u \ne s_v)$  but with links of same capacities  $(b_{u,v} = b)$ .

First we retain only the fastest n processors, which we rename  $P_1, P_2, \ldots, P_n$  such that  $s_1 \leq s_2 \leq \ldots \leq s_n$ . Then we consider the processors in the order  $P_1$  to  $P_n$ , i.e. from the slowest to the fastest, and greedily assign them any free (non already assigned) task that they can process within the period. Algorithm 1 details the procedure.

```

procedure Greedy Assignment

begin

Work with fastest n processors, numbered P_1 to P_n, where s_1 \leq s_2 \leq \ldots \leq s_n

Mark all stages S_1 to S_n as free

for u = 1 to n do

Pick up any free stage S_k s.t. \delta_{k-1}/b + w_k/s_u + \delta_k/b \leq T_{\text{period}}

Assign S_k to P_u. Mark S_k as already assigned

If no stage found return "failure"

end

end

```

**Algorithm 1**: Greedy assignment algorithm for a given period  $T_{period}$ .

The proof that the greedy algorithm returns a solution if and only if there exists a solution of period  $T_{\text{period}}$  is done by a simple exchange argument. Indeed, consider a valid one-to-one assignment of period  $T_{\text{period}}$ , denoted A, and assume that it has assigned stage  $S_{k_1}$  to  $P_1$ . Note first that the greedy algorithm will indeed find a stage to assign to  $P_1$  and cannot fail, since  $S_{k_1}$  can be chosen. If the choice of the greedy algorithm is actually  $S_{k_1}$ , we proceed by induction with  $P_2$ . If the greedy algorithm has selected another stage  $S_{k_2}$  for  $P_1$ , we find which processor, say  $P_u$ , has been assigned this stage in the valid assignment A. Then we exchange the assignments of  $P_1$  and  $P_u$  in A. Because  $P_u$  is faster than  $P_1$ , which could process  $S_{k_1}$  in time in the assignment A,  $P_u$  can process  $S_{k_1}$  in time too. Because  $S_{k_2}$  has been mapped on  $P_1$  by the greedy algorithm,  $P_1$  can process  $S_{k_1}$  in time. So the exchange is valid, we can consider the new assignment A which is valid and which did the same assignment on  $P_1$  than the greedy algorithm. The proof proceeds by induction with  $P_2$  as before. We point out that the complexity of the greedy algorithm is bounded by  $O(n^2)$ , because of the two loops over processors and stages.

#### 3.2 Interval Mapping

#### 3.2.1 Fully Homogeneous platforms

**Proposition 1.** For Fully Homogeneous platforms, the optimal Interval Mapping can be determined in polynomial time.

**Proof.** This result is due to Subhlock and Vondran[32, 33]. We briefly outline a variant of their dynamic programming algorithm that returns the optimal period. Consider an application with n stages  $S_1$  to  $S_n$  to be mapped onto a fully-homogeneous platform composed of p (identical) processors. Let s and b respectively denote the processor speed and the link bandwidth.

We compute recursively the value of c(i, j, k), which is the optimal period that can be achieved by any interval-based mapping of stages  $S_i$  to  $S_j$  using exactly k processors. The goal is to determine

$$\min_{1 \le k \le p} c(1, n, k)$$

The recurrence relation can be expressed as

$$c(i,j,k) = \min_{\begin{subarray}{c} q+r=k\\ 1 \leq q \leq k-1\\ 1 < r < k-1 \end{subarray}} \left\{ \min_{i \leq \ell \leq j-1} \left\{ \max\left(c(i,\ell,q),c(\ell+1,j,r)\right) \right\} \right\}$$

with the initialization

$$c(i, j, 1) = \frac{\delta_{i-1}}{\mathsf{b}} + \frac{\sum_{k=i}^{j} \mathsf{w}_k}{\mathsf{s}} + \frac{\delta_j}{\mathsf{b}}$$

$$c(i, j, k) = +\infty \text{ if } k > j - i + 1$$

The recurrence is easy to justify: to compute c(i, j, k), we search over all possible partitionings into two subintervals, using every possible number of processors for each interval. The complexity of this dynamic programming algorithm is bounded by  $O(n^3p^2)$ .

It is not possible to extend the previous dynamic programming algorithm to deal with Communication Homogeneous platforms. This is because the algorithm intrinsically relies on identical processors in the recurrence computation. Different-speed processors would execute sub-intervals with different cycle-times. Because of this additional difficulty, the INTERVAL MAPPING problem for Communication Homogeneous platforms seems to be very combinatorial: we prove that it is NP-hard below (Section 3.2.2. Furthermore we prove that interval-based mappings are dominant for such platforms (Section 3.2.3), which means that there exist interval-based mappings which are optimal among all possible general mappings (hence the entry titled same complexity in Table 1).

# 3.2.2 NP-completeness of the Interval Mapping problem for $Communication\ Homogeneous\ platforms$

**Theorem 2.** For Communication Homogeneous platforms, the (decision problem associated to the) Interval Mapping optimization problem is NP-complete.

Theorem 2 is a consequence of Theorem 3 which assesses the complexity of the heterogeneous 1D partitioning problem. We introduce this problem and prove Theorem 3 before returning to the proof of Theorem 2.

Given an array of n elements  $a_1, a_2, \ldots, a_n$ , the 1D partitioning problem, also known as the chains-to-chains problem, is to partition the array into p intervals whose element sums are almost identical. More precisely, we search for a partition of [1..n] into p consecutive intervals  $\mathcal{I}_1, \mathcal{I}_2, \ldots, \mathcal{I}_p$

, where  $\mathcal{I}_k = [d_k, e_k]$  and  $d_k \le e_k$  for  $1 \le k \le p$ ,  $d_1 = 1$ ,  $d_{k+1} = e_k + 1$  for  $1 \le k \le p - 1$  and  $e_p = n$ . The objective is to minimize

$$\max_{1 \le k \le p} \sum_{i \in \mathcal{I}_k} a_i = \max_{1 \le k \le p} \sum_{i = d_k}^{e_k} a_i.$$

This problem has been extensively studied in the literature because it has various applications. In particular, it amounts to load-balance n computations whose ordering must be preserved (hence the restriction to intervals) onto p identical processors. Then each  $a_i$  corresponds to the execution time of the i-th task, and the sum of the elements in interval  $\mathcal{I}_k$  is the load of the processor which  $\mathcal{I}_k$  is assigned to. Several algorithms and heuristics have been proposed to solve this load-balancing problem, including [11, 20, 17, 21, 25]. We refer the reader to the survey paper by Pinar and Aykanat [26] for a detailed overview and comparison of the literature.

The advent of heterogeneous clusters leads to the following generalization of the 1D partitioning problem: the goal is to partition the n elements into p intervals whose element sums match p prescribed values (the processor speeds) as closely as possible. Let  $s_1, s_2, \ldots, s_p$  denote these values. We search for a partition of [1..n] into p intervals  $\mathcal{I}_k = [d_k, e_k]$  and for a permutation  $\sigma$  of  $\{1, 2, \ldots, p\}$ , with the objective to minimize:

$$\max_{1 \le k \le p} \frac{\sum_{i \in \mathcal{I}_k} a_i}{\mathsf{s}_{\sigma(k)}}.$$

Another way to express the problem is that intervals are now weighted by the  $s_i$  values, while we had  $s_i = 1$  for the homogeneous version. Can we extend the efficient algorithms described in [26] to solve the heterogeneous 1D partitioning problem, Hetero-1D-Partition for short? In fact, the problem seems combinatorial, because of the search over all possible permutations to weight the intervals. Indeed, we prove the NP-completeness of (the decision problem associated to) Hetero-1D-Partition.

**Definition 1** (HETERO-1D-PARTITION-DEC). Given n elements  $a_1, a_2, \ldots, a_n$ , p values  $s_1, s_2, \ldots, s_p$  and a bound K, can we find a partition of [1..n] into p intervals  $\mathcal{I}_1, \mathcal{I}_2, \ldots, \mathcal{I}_p$ , with  $\mathcal{I}_k = [d_k, e_k]$  and  $d_k \leq e_k$  for  $1 \leq k \leq p$ ,  $d_1 = 1$ ,  $d_{k+1} = e_k + 1$  for  $1 \leq k \leq p - 1$  and  $e_p = n$ , and a permutation  $\sigma$  of  $\{1, 2, \ldots, p\}$ , such that

$$\max_{1 \le k \le p} \frac{\sum_{i \in \mathcal{I}_k} a_i}{\mathbf{s}_{\sigma(k)}} \le K \quad ?$$

**Theorem 3.** The Hetero-1D-Partition-Dec problem is NP-complete.

**Proof.** The HETERO-1D-PARTITION-DEC problem clearly belongs to the class NP: given a solution, it is easy to verify in polynomial time that the partition into p intervals is valid and that the maximum sum of the elements in a given interval does divided by the corresponding s value does not exceed the bound K. To establish the completeness, we use a reduction from NUMERICAL MATCHING WITH TARGET SUMS (NMWTS), which is NP-complete in the strong sense [16]. We consider an instance  $\mathfrak{I}_1$  of NMWTS: given 3m numbers  $x_1, x_2, \ldots, x_m, y_1, y_2, \ldots, y_m$  and  $z_1, z_2, \ldots, z_m$ , does there exist two permutations  $\sigma_1$  and  $\sigma_2$  of  $\{1, 2, \ldots, m\}$ , such that  $x_i + y_{\sigma_1(i)} = z_{\sigma_2(i)}$  for  $1 \leq i \leq m$ ? Because NMWTS is NP-complete in the strong sense, we can encode the 3m numbers in unary and assume that the size of  $\mathfrak{I}_1$  is O(m+M), where  $M = \max_i \{x_i, y_i, z_i\}$ . We also assume that  $\sum_{i=1}^m x_i + \sum_{i=1}^m y_i = \sum_{i=1}^m z_i$ , otherwise  $\mathfrak{I}_1$  cannot have a solution.

We build the following instance  $\mathfrak{I}_2$  of HETERO-1D-PARTITION-DEC (we use the formulation in terms of task weights and processor speeds which is more intuitive):

• We define n = (M+3)m tasks, whose weights are outlined below:

$$A_1 \quad \underbrace{111...1}_{M} \quad C \quad D \quad | \quad A_2 \quad \underbrace{111...1}_{M} \quad C \quad D \quad | \quad \dots \quad | \quad A_m \quad \underbrace{111...1}_{M} \quad C \quad D$$

Here, B=2M, C=5M, D=7M, and  $A_i=B+x_i$  for  $1 \le i \le m$ . To define the  $a_i$  formally for  $1 \le i \le n$ , let N=M+3. We have for  $1 \le i \le m$ :

$$\begin{cases} a_{(i-1)N+1} = A_i = B + x_i \\ a_{(i-1)N+j} = 1 \text{ for } 2 \le j \le M+1 \\ a_{iN-1} = C \\ a_{iN} = D \end{cases}$$

• For the number of processors (and intervals), we choose p = 3m. As for the speeds, we let  $s_i$  be the speed of processor  $P_i$  where, for  $1 \le i \le m$ :

$$\begin{cases} \mathbf{s}_i = B + z_i \\ \mathbf{s}_{m+i} = C + M - y_i \\ \mathbf{s}_{2m+i} = D \end{cases}$$

Finally, we ask whether there exists a solution matching the bound K = 1. Clearly, the size of  $\mathfrak{I}_2$  is polynomial in the size of  $\mathfrak{I}_1$ . We now show that instance  $\mathfrak{I}_1$  has a solution if and only if instance  $\mathfrak{I}_2$  does.

Suppose first that  $\mathfrak{I}_1$  has a solution, with permutations  $\sigma_1$  and  $\sigma_2$  such that  $x_i + y_{\sigma_1(i)} = z_{\sigma_2(i)}$ . For  $1 \leq i \leq m$ :

- We map each task  $A_i$  and the following  $y_{\sigma_1(i)}$  tasks of weight 1 onto processor  $P_{\sigma_2(i)}$ .

- We map the following  $M y_{\sigma_1(i)}$  tasks of weight 1 and the next task, of weight C, onto processor  $P_{m+\sigma_1(i)}$ .

- We map the next task, of weight D, onto the processor  $P_{2m+i}$ .

We do have a valid partition of all the tasks into p = 3m intervals. For  $1 \le i \le m$ , the load and speed of the processors are indeed equal:

- The load of  $P_{\sigma_2(i)}$  is  $A_i + y_{\sigma_1(i)} = B + x_i + y_{\sigma_1(i)}$  and its speed is  $B + z_{\sigma_2(i)}$ .

- The load of  $P_{m+\sigma_1(i)}$  is  $M-y_{\sigma_1(i)}+C$ , which is equal to its speed.

- The load and speed of  $P_{2m+i}$  are both D.

The mapping does achieve the bound K=1, hence a solution to  $\mathfrak{I}_1$ .

Suppose now that  $\mathfrak{I}_2$  has a solution, i.e. a mapping matching the bound K=1. We first observe that  $s_i < s_{m+j} < s_{2m+k} = D$  for  $1 \le i, j, k \le m$ . Indeed  $s_i = B + z_i \le B + M = 3M$ ,  $5M \leq s_{m+j} = C + M - y_j \leq 6M$  and D = 7M. Hence each of the m tasks of weight D must be assigned to a processor of speed D, and it is the only task assigned to this processor. These msingleton assignments divide the set of tasks into m intervals, namely the set of tasks before the first task of weight D, and the m-1 sets of tasks lying between two consecutive tasks of weight D. The total weight of each of these m intervals is  $A_i + M + C > B + M + C = 10M$ , while the largest speed of the 2m remaining processors is 6M. Therefore each of them must be assigned to at least 2 processors each. However, there remains only 2m available processors, hence each interval is assigned exactly 2 processors.

Consider such an interval  $A_i$  111...1 C with M tasks of weight 1, and let  $P_{i_1}$  and  $P_{i_2}$  be the two processors assigned to this interval. Tasks  $A_i$  and C are not assigned to the same processor (otherwise the whole interval would). So  $P_{i_1}$  receives task  $A_i$  and  $h_i$  tasks of weight 1 while  $P_{i_2}$ receives  $M - h_i$  tasks of weight 1 and task C. The weight of  $P_{i_2}$  is  $M - h + C \ge C = 5M$  while  $s_i \leq 3M$  for  $1 \leq i \leq m$ . Hence  $P_{i_1}$  must be some  $P_i$ ,  $1 \leq i \leq m$  while  $P_{i_2}$  must be some  $P_{m+j}$ ,  $1 \le j \le m$ . Because this holds true on each interval, this defines two permutations  $\sigma_2(i)$  and  $\sigma_1(i)$ such that  $P_{i_1} = P_{\sigma_2(i)}$  and  $P_{i_2} = P_{\sigma_1(i)}$ . Because the bound K = 1 is achieved, we have:

- $A_i + h_i = B + x_i + h_i \le B + z_{\sigma_2(i)}$

- $\bullet \quad M h_i + C \le C + M y_{\sigma_1(i)}$ Therefore  $y_{\sigma_1(i)} \leq h_i$  and  $x_i + h_i \leq z_{\sigma_2(i)}$ , and

$$\sum_{i=1}^{m} x_i + \sum_{i=1}^{m} y_i \le \sum_{i=1}^{m} x_i + \sum_{i=1}^{m} h_i \le \sum_{i=1}^{m} z_i$$

By hypothesis,  $\sum_{i=1}^{m} x_i + \sum_{i=1}^{m} y_i = \sum_{i=1}^{m} z_i$ , hence all inequalities are tight, and in particular  $\sum_{i=1}^{m} x_i + \sum_{i=1}^{m} h_i = \sum_{i=1}^{m} z_i$ . We can deduce that  $\sum_{i=1}^{m} y_i = \sum_{i=1}^{m} h_i = \sum_{i=1}^{m} z_i - \sum_{i=1}^{m} x_i$ , and since  $y_{\sigma_1(i)} \leq h_i$  for all i, we have  $x_i = 0$ .

have  $y_{\sigma_1(i)} = h_i$  for all i.

Similarly, we deduce that  $x_i + h_i = z_{\sigma_2(i)}$  for all i, and therefore  $x_i + y_{\sigma_1(i)} = z_{\sigma_2(i)}$ .

Altogether, we have found a solution for  $\mathfrak{I}_1$ , which concludes the proof.

Back to the proof of Theorem 2. Obviously, the Interval Mapping optimization problem belongs to the class NP. Any instance of the HETERO-1D-PARTITION problem with n tasks  $a_i$ , p processor speeds  $s_i$  and bound K can be converted into an instance of the INTERVAL MAPPING problem with n stages of weight  $w_i = a_i$ , letting all communication costs  $\delta_i = 0$ , targeting a Communication Homogeneous platform with the same p processors and homogeneous links of bandwidth b = 1, and trying to achieve a period not greater than K. This concludes the proof.

#### Dominance of interval mappings for Communication Homogeneous platforms

**Theorem 4.** For Communication Homogeneous platforms, interval-based mappings are dominant.

**Proof.** Consider an application with n stages  $S_1$  to  $S_n$  to be mapped onto a communicationhomogeneous platform composed of p processors  $P_1$  to  $P_p$ . The speed of  $P_i$  is  $s_i$ , and all links have same bandwidth b. Consider an optimal mapping for this application. If this mapping is intervalbased, we are done. Otherwise, there exist processors which are not assigned a single interval of stages. Let  $i_1$  be the index of the first stage  $S_{i_1}$  that is mapped onto such a processor, say  $P_u$ , and let  $i_2$  be the last index such that the interval  $[i_1, i_2]$  is mapped on  $P_u$ . Stages  $S_1$  to  $S_{i_1-1}$  are mapped by intervals onto other processors.

Rather than going on formally, let us illustrate the algorithm through the following example, where we have  $i_1 = 6$ ,  $i_2 = 7$  and u = 4:

The idea is to transform the mapping so that  $P_4$  will be assigned a single interval, without increasing the cycle-time of any processor. Recall that we use equations (4) and (5) to compute the period of a general mapping. There are two cases to consider:

- If the speed of  $P_4$  is larger than (or at least equal to) the speed of  $P_5$ ,  $P_6$  and  $P_7$ , then we assign stages  $S_8$  to  $S_{12}$  to  $P_4$ . This will indeed decrease its cycle-time, because these stages are processed in shorter time and no more communication is paid in between. Then we iterate the transformation with  $i_2 = 15$ .

- Otherwise, choose the fastest processor among  $P_4$ ,  $P_5$ ,  $P_6$  and  $P_7$ . Assume that it is  $P_6$ . Then  $P_6$  is assigned the extra stages  $S_{11}$  to  $S_{15}$ , and all the other subsequent stages that were assigned to  $P_4$ . Because the communications are homogeneous, nothing is changed in the price paid by the following communications between  $P_4$  and other processors that now go between  $P_6$  and these processors. The cycle-time of  $P_4$  has been reduced since we removed stages from it. The cycle-time of  $P_6$  has not increased the period of the new mapping compared to the initial mapping. To see this, note that its first assigned stage first(6) is the same. If its last assigned stage was already assigned to it before the transformation (last(6)), then its cycle-time has decreased (because some stages are processed faster in between) or is unchanged. If its last assigned stage was originally assigned to  $P_4$  (last(4)), then its new cycle-time is smaller than the old cycle-time of  $P_4$  since first(6) > first(4) and some stages are eventually processed faster between first(6) and last(4). In both cases, we safely increase the value of  $i_1$  and proceed to the next transformation, without increasing the period of the mapping.

After a finite number of such transformations, we obtain an interval-based mapping, whose period does not exceed the period of the original mapping, which concludes the proof.  $\Box$

#### 3.3 Fully Heterogeneous platforms

**Theorem 5.** For Fully Heterogeneous platforms, the (decision problems associated to the) three mapping strategies (ONE-TO-ONE MAPPING, INTERVAL MAPPING and GENERAL MAPPING) are all NP-complete.

We build the following instance  $\mathcal{I}_2$  of our mapping problem (note that the same instance will work out for the three variants One-to-one Mapping, Interval Mapping and General Mapping):

• For the application: n = 2m - 1 stages which for convenience we denote as

$$ightarrow \mathcal{S}_1

ightarrow \mathcal{S}_1'

ightarrow \mathcal{S}_2

ightarrow \mathcal{S}_2'

ightarrow \ldots

ightarrow \mathcal{S}_{m-1}

ightarrow \mathcal{S}_{m-1}'

ightarrow \mathcal{S}_m

ightarrow$$

For each stage  $S_i$  or  $S_i'$  we set  $\delta_i = w_i = 1$  (as well as  $\delta_0 = \delta_n = 1$ ), so that the application is perfectly homogeneous.

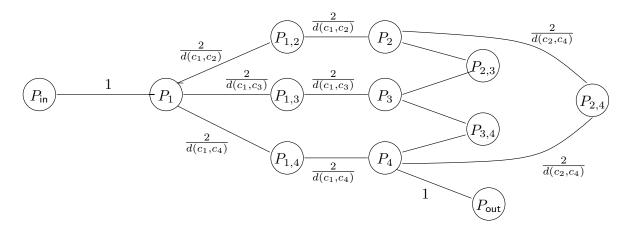

- For the platform (see Figure 5):

- we use  $p = m + {m \choose 2}$  processors which for convenience we denote as  $P_i$ ,  $1 \le i \le m$  and  $P_{i,j}$ ,  $1 \le i < j \le m$ . We also use an input processor  $P_{\text{in}}$  and an output processor  $P_{\text{out}}$ . The speed of each processor  $P_i$  or  $P_{ij}$  has the same value  $s = \frac{1}{2K}$  (note that we have a computation-homogeneous platform), except for  $P_{\text{in}}$  and  $P_{\text{out}}$  whose speed is 0.

- the communication links shown on Figure 5 have a larger bandwidth than the others, and are referred to as fast links. More precisely,  $b_{P_{\text{in}},P_1} = b_{P_m,P_{\text{out}}} = 1$ , and  $b_{P_i,P_{ij}} = b_{P_{ij},P_j} = \frac{2}{d(c_i,c_j)}$  for  $1 \le i < j \le m$ . All the other links have a very small bandwidth  $b = \frac{1}{5K}$  and are referred to as slow links. The intuitive idea is that slow links are too slow to be used for the mapping.

Finally, we ask whether there exists a solution with period 3K. Clearly, the size of  $\mathcal{I}_2$  is polynomial (and even linear) in the size of  $\mathcal{I}_1$ . We now show that instance  $\mathcal{I}_1$  has a solution if and only if instance  $\mathcal{I}_2$  does.

Suppose first that  $\mathcal{I}_1$  has a solution. We map stage  $\mathcal{S}_i$  onto  $P_{\pi(i)}$  for  $1 \leq i \leq m$ , and stage  $\mathcal{S}_i'$  onto processor  $P_{\pi(i),\pi(i+1)}$  for  $1 \leq i \leq m-1$ . The cycle-time of  $P_1$  is  $1+2K+\frac{d(c_{\pi(1)},c_{\pi(2)})}{2} \leq 1+2K+\frac{K}{2} \leq 3K$ . Quite similarly, the cycle-time of  $P_m$  is smaller than 3K. For  $2 \leq i \leq m-1$ , the cycle-time of  $P_{\pi(i)}$  is  $\frac{d(c_{\pi(i)},c_{\pi(i)})}{2} + 2K + \frac{d(c_{\pi(i)},c_{\pi(i+1)})}{2} \leq 3K$ . Finally, for  $1 \leq i \leq m-1$ , the cycle-time of  $P_{\pi(i),\pi(i+1)}$  is  $\frac{d(c_{\pi(i)},c_{\pi(i+1)})}{2} + 2K + \frac{d(c_{\pi(i)},c_{\pi(i+1)})}{2} \leq 3K$ . The mapping does achieve a period not greater than 3K, hence a solution to  $\mathcal{I}_2$ .

Suppose now that  $\mathcal{I}_2$  has a solution, i.e. a mapping of period not greater than 3K. We first observe that each processor is assigned at most one stage by the mapping, because executing two stages would require at least 2K + 2K units of time, which would be too large to match the period. This simple observation explains why the same reduction works for the three strategies, ONE-TO-ONE MAPPING, INTERVAL MAPPING and GENERAL MAPPING. Next, we observe that any slow link of bandwidth  $\frac{1}{5K}$  cannot be used in the solution: otherwise the period would exceed 5K.

Figure 5: The platform used in the reduction for Theorem 5.

The input processor  $P_{\text{in}}$  has a single fast link to  $P_1$ , so necessarily  $P_1$  is assigned stage  $S_1$  (i.e.  $\pi(1) = 1$ ). As observed above,  $P_1$  cannot execute any other stage. Because of fast links, stage  $S'_1$  must be assigned to some  $P_{1,j}$ ; we let  $j = \pi(2)$ . Again, because of fast links and of the one-to-one constraint, the only choice for stage  $S_2$  is  $P_{\pi(2)}$ . Necessarily  $j = \pi(2) \neq \pi(1) = 1$ , otherwise  $P_1$  would execute two stages.

We proceed similarly for stage  $S'_2$ , assigned to some  $P_{2k}$  (let  $k = \pi(3)$ ) and stage  $S_3$  assigned to  $P_{\pi(3)}$ . Owing to the one-to-one constraint,  $k \neq 1$  and  $k \neq j$ , i.e.  $\pi : [1..3] \to [1..m]$  is a one-to-one mapping. By induction, we build the full permutation  $\pi : [1..m] \to [1..m]$ . Because the output processor  $P_{\text{out}}$  has a single fast link to  $P_m$ , necessarily  $P_m$  is assigned stage  $S_m$ , hence  $\pi(m) = m$ .

We have built the desired permutation, there remains to show that  $d(c_{\pi(i)}, c_{\pi(i+1)}) \leq K$  for  $1 \leq i \leq m-1$ . The cycle time of processor  $P_{\pi(i)}$  is  $\frac{d(c_{\pi(i)}, c_{\pi(i+1)})}{2} + 2K + \frac{d(c_{\pi(i)}, c_{\pi(i+1)})}{2} \leq 3K$ , hence  $d(c_{\pi(i)}, c_{\pi(i+1)}) \leq K$ . Altogether, we have found a solution for  $\mathcal{I}_1$ , which concludes the proof.

### 4 Heuristics

In this section several heuristics for *Communication Homogeneous* platforms are presented. We restrict to such platforms because, as already pointed out in Section 1, clusters made of different-speed processors interconnected by either plain Ethernet or a high-speed switch constitute the typical experimental platforms in most academic or industry research departments.

Because of Theorem 4, we can restrict to interval-based mappings without any loss of generality. However, the complexity of determining the optimal interval-based mapping for Communication Homogeneous platforms is still open, this is why we propose several polynomial heuristics to tackle the problem. In the following, we denote by n the number of stages, and by p the number of processors.

#### 4.1 Greedy heuristics

The first heuristics are greedy, i.e. they assign a stage, or an interval of stages, to a given processor, and this choice is independent of further choices. In these heuristics, we systematically assign

$L = \lceil n/p \rceil$  consecutive stages per processor (except for the last processor if n is not divisible by p). In other words, the heuristics always assign the same set of intervals, the difference between them lies in the allocations that they enforce. In fact, there is a single exception to this rule: for one of the random heuristics, the size of the interval is randomly determined.

The number of processors which will be used in the final solution is thus  $\lceil n/L \rceil$ . Note that if  $n \leq p$ , then L = 1 and these heuristics perform a ONE-TO-ONE MAPPING algorithm.

- **H1a-GR:** random For each interval that needs to be assigned, we randomly choose a free processor which will handle it. As soon as a processor is handling an interval, it is not free any more and cannot be used to process another interval.

- **H1b-GRIL:** random interval length This variant of the greedy random **H1a-GR** is working similarly, but it further chooses the size of the interval to be assigned randomly. The distribution used is homogeneous, with an average length of L and a length between 1 and 2L-1. Notice that this heuristic is identical to H1a when L=1.

- **H2-GSW:** biggest  $\sum w$  In this heuristic, the choice is more meaningful since we select the interval with the most demanding computing requirement, and place it on the fastest processor. Intervals are sorted by decreasing values of  $\sum_{i \in Interval} w_i$ , processors are sorted by decreasing speed  $s_u$ , and the matching is achieved.

- **H3-GSD:** biggest  $\delta_{in} + \delta_{out}$  This heuristic is quite similar to **H2-GSW** except that the intervals are sorted according to their communication requirements,  $\delta_{in} + \delta_{out}$ , where in is the first stage of the interval, and out 1 the last one.

- **H4-GP: biggest period on fastest processor** This heuristic is balancing the computation and communication requirements of each interval: the processors are sorted by decreasing speed  $s_u$  and, for the current processor u, we choose the interval with the biggest period  $(\delta_{in} + \delta_{out})/b + \sum_{i \in Interval} w_i/s_u$ . Then we keep going with the remaining processors and intervals.

#### 4.2 Sophisticated heuristics

This second set of heuristics presents more elaborated heuristics, trying to make clever choices.

- **H5-BS121:** binary search for One-to-one Mapping This heuristic implements the optimal algorithm for the One-to-one Mapping case, described in Section 3.1. When p < n, we cut the application in intervals similarly as in the greedy heuristics. All these heuristics perform a One-to-one Mapping on this new application, so **H5-BS121** should always be better than all the greedy heuristics.

- **H6-SPL:** splitting intervals This heuristic sorts the processors by decreasing speed, and starts by assigning all the stages to the first processor in the list. This processor becomes used. Then, at each step, we select the used processor j with the largest period and we try to split its interval of stages, giving some stages to the next fastest processor j' in the list (not yet used). This can be done by splitting the interval at any place, and either placing the first part of the interval on j and the remainder on j', or the other way round. The solution which minimizes max(period(j), period(j')) is chosen if it is better than the original solution. Splitting is performed as long as we improve the period of the solution.

**H7a-BSL** and **H7b-BSC**: binary search (longest/closest) – The last two heuristics perform a binary search on the period of the solution. For a given period P, we study if there is a feasible solution, starting with the first stage (s = 1) and constructing intervals (s, s') to fit on processors. For each processor u, and each  $s' \geq s$  we compute the period (s, s', u) of stages s..s' running on processor u and check whether it is smaller than P (then it is a possible assignment). The first variant **H7a-BSL** choose the longest possible interval (maximizing s') fitting on a processor for a given period, and in case of equality, the interval and processor with the closest period to the solution period. The second variant **H7b-BSC** does not take into account the length of the interval, but only finds out the closest period.

The code for all these heuristics can be found on the Web at:

http://graal.ens-lyon.fr/~abenoit/code/skeleton-heuristics.c

# 5 Experiments

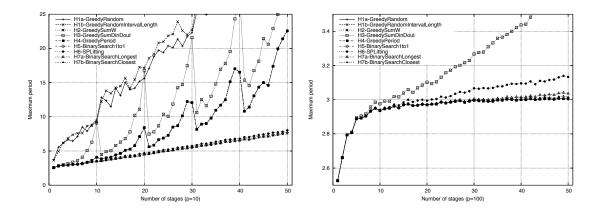

Several experiments have been conducted in order to assess the performance of the heuristics described in Section 4. We have generated a set of random applications with n=1 to 50 stages, and two sets of random platforms, one set with p=10 processors and the other with p=100 processors. The first case corresponds to a situation in which several stages are likely to be mapped on the same processor because there are much fewer processors than stages. However, in the second case, we expect the mapping to be a ONE-TO-ONE MAPPING, except when communications are really costly.

The heuristics have been designed for Communication Homogeneous platforms, so we restrict to such platforms in these experiments. In all the experiments, we fix b=10 for the link bandwidths. Moreover, the speed of each processor is randomly chosen as an integer between 1 and 20. We keep the latter range of variation throughout the experiments, while we vary the range of the application parameters from one set of experiments to the other. Indeed, although there are four categories of parameters to play with, i.e. the values of  $\delta$ , w, s and b, we can see from equation (2) that only the relative ratios  $\frac{\delta}{b}$  and  $\frac{w}{s}$  have an impact on the performance.

Each experimental value reported in the following has been calculated as an average over 100

Each experimental value reported in the following has been calculated as an average over 100 randomly chosen application/platforms pairs. For each of these pairs, we report the performance of the 9 heuristics described in Section 4.

We report four main sets of experiments. For each of them, we vary some key application/platform parameter to assess the impact of this parameter on the performance of the heuristics. The first two experiments deal with applications where communications and computations have the same order of magnitude, and we study the impact of the degree of heterogeneity of the communications, i.e. of the variation range of the  $\delta$  parameter: in the first experiment the communication are homogeneous, while in the second one  $\delta$  varies between 1 to 100. The last two experiments deal with imbalanced applications: the third experiment assumes large computations (large value of the w to  $\delta$  ratio), and the fourth one reports results for small computations (small value of the w to  $\delta$  ratio).

# 5.1 Experiment 1: balanced communication/computation, and homogeneous communications

In the first set of experiments, the application communications are homogeneous, we fix  $\delta_i = 10$  for i = 0..n. The computation time required by each stage is randomly chosen between 1 and 20. Thus, the communications and computations are balanced within the application.

Figure 6: Experiment 1: homogeneous communications.

We notice that the sophisticated heuristics perform much better than the greedy ones when p=10: they correspond to the lowest three curves. Heuristic H7b is the best for this configuration, before H7a and H6. H2 and H4 give the same result as H5 (binary search returning the optimal algorithm for a One-to-one Mapping), since the communications are homogeneous, and H3 is less good because it tries to make a choice among communications which are all identical. Finally, we see that all our heuristics are largely outperforming the random ones.

When p = 100, the optimal One-to-one Mapping algorithm returns the best solution (H5), obtained similarly by H2 and H4. The sophisticated heuristics are less accurate (but H7 gives a result very close to H5), and the random ones are not even represented on the plot: they always return a maximum period greater than 3.5, while we decided to zoom on the interesting part of the plots.

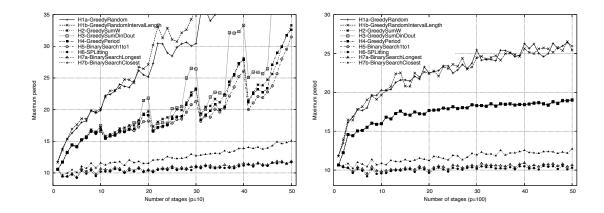

# 5.2 Experiment 2: balanced communication/computation, and heterogeneous communications

In this second set of experiments, the application communications are heterogeneous, chosen randomly between 1 and 100. Similarly to Experiment 1, the computation time required by each stage is randomly chosen between 1 and 20. Thus, the communications and computations are still relatively balanced within the application.

In the case with p=10, the sophisticated heuristics are the best ones, and H6 outperforms the binary search heuristics H7a and H7b. Also, the first binary search H7a is better than H7b, while it was the other way round with homogeneous computations. The splitting heuristic H6 is definitively better in this heterogeneous case. We also notice that H5 is better than all the greedy

Figure 7: Experiment 2: heterogeneous communications.

heuristics, which is due to the fact that it implements the optimal algorithm for a ONE-TO-ONE MAPPING (or fixed-length Interval Mapping).

For p=100, the sophisticated heuristics behave in the same way, but we notice that all the greedy heuristics find the optimal One-to-one Mapping solution, similarly to H5. In both cases, all our heuristics are much more efficient than the random ones.

# 5.3 Experiment 3: large computations

In this experiment, the applications are much more demanding on computations than on communications, making communications negligible compared to the computation requirements. We choose the communication time between 1 and 20, while the computation time of each application is chosen between 10 and 1000.

Figure 8: Experiment 3: large computations.

In this case, both plots are showing the same behavior as in Experiment 1. In fact, even though communications are not the same for each application, their relative importance is negligible in front of the computations, and thus the system behaves as if communications were homogeneous. Thus, the One-to-one Mapping heuristics are clearly the best with p=100, while H7b returns the smallest maximum period for p=10.

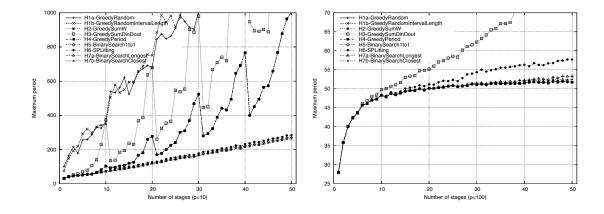

#### 5.4 Experiment 4: small computations

The last experiment is the opposite to Experiment 3 since the computations are now negligible compared to the communications. The communication time is still chosen between 1 and 20, but the computation time is now chosen between 0.01 and 10.

Figure 9: Experiment 4: small computations.

In this case, since communications are important, the sophisticated heuristics perform better. This is because these heuristics often choose different length intervals in order to reduce the communication cost, while all the greedy and random heuristics are always making the same choice of intervals

Similarly to the heterogeneous case (Experiment 2), H6 is the best heuristic, H7a and H7b are just a little bit ahead. Also, for ONE-TO-ONE MAPPING situations, the greedy heuristics returns the same result as H5.

However, in this situation, H3 is better than H2. This never happened before because computations were always the most relevant parameter to optimize. Also, we notice that the random heuristics are quite close to the greedy ones, because they choose the same intervals and so they pay the same communication cost. The clever choices performed by the greedy heuristics allow to save a little on the computation side.

#### 5.5 Summary

To summarize our experimental results, we first point out that our heuristics are always much more efficient than random mappings. Moreover, we identify three heuristics which may each turn out to be the most efficient, depending upon the application and platform characteristics.

When there are more processors than pipeline stages, we can expect that a ONE-TO-ONE MAP-PING might be a good choice. Actually, if the computations are the costly part of the application on a given platform, and communications are of lesser importance, then the greedy ONE-TO-ONE MAPPING heuristics return the best result, which we expect to be close to the optimal. This is also the case when communications are fully homogeneous between stages, because splitting between more stages does not add a large overhead. The optimal binary search H5 for ONE-TO-ONE MAPPING should be used in such cases.

The same balance between communications and computations leads to a different result when there are fewer processors, because it is then necessary to share the computation load between processors, and the decision where to split intervals can be really relevant. All the greedy heuristics are using intervals of fixed length and cannot make any clever choices. In such cases, H7b (Binary Search Closest) is the most efficient heuristic.

Moreover, as soon as communications are costly or with a high degree of heterogeneity, the greedy heuristics do not return satisfying results, because they may cut intervals on costly links between stages. Thus the more sophisticated INTERVAL MAPPING heuristics performs better. In such cases, the splitting heuristic H6 is the best choice.

# 6 Assessing the absolute performance of the heuristics

We introduce an integer linear program which allows to compute the optimal mapping for a given platform and application. We compare the results of the heuristics to the solution of this linear program, when available. The large number of integer variables in the linear program makes it impossible to solve large problem instances.

#### 6.1 Linear program formulation

We present here an integer linear program to compute the optimal interval-based mapping on Fully Heterogeneous platforms. We assume n stages and p processors, plus two fictitious extra stages  $S_0$  and  $S_{n+1}$  respectively assigned to  $P_{\text{in}}$  and  $P_{\text{out}}$ . First we need to define a few variables:

- For  $k \in [0..n+1]$  and  $u \in [1..p] \cup \{\text{in}, \text{out}\}$ ,  $x_{k,u}$  is a boolean variable equal to 1 if stage  $S_k$  is assigned to processor  $P_u$ ; we let  $x_{0,\text{in}} = x_{n+1,\text{out}} = 1$ , and  $x_{k,\text{in}} = x_{k,\text{out}} = 0$  for  $1 \le k \le n$ .

- For  $k \in [0..n]$ ,  $u, v \in [1..p] \cup \{\text{in,out}\}$  with  $u \neq v$ ,  $z_{k,u,v}$  is a boolean variable equal to 1 if stage  $S_k$  is assigned to  $P_u$  and stage  $S_{k+1}$  is assigned to  $P_v$ : hence  $\text{link}_{u,v}: P_u \to P_v$  is used for the communication between these two stages. If  $k \neq 0$  then  $z_{k,\text{in},v} = 0$  for all  $v \neq \text{in}$  and if  $k \neq n$  then  $z_{k,u,\text{out}} = 0$  for all  $u \neq \text{out}$ .

- For  $k \in [0..n]$  and  $u \in [1..p] \cup \{\text{in}, \text{out}\}$ ,  $y_{k,u}$  is a boolean variable equal to 1 if stages  $S_k$  and  $S_{k+1}$  are both assigned to  $P_u$ ; we let  $y_{k,\text{in}} = y_{k,\text{out}} = 0$  for all k, and  $y_{0,u} = y_{n,u} = 0$  for all u.

- For  $u \in [1..p]$ , first(u) is an integer variable which denotes the first stage assigned to  $P_u$ ; similarly,  $\mathsf{last}(u)$  denotes the last stage assigned to  $P_u$ . Thus  $P_u$  is assigned the interval  $[\mathsf{first}(u), \mathsf{last}(u)]$ . Of course  $1 \leq \mathsf{first}(u) \leq \mathsf{last}(u) \leq n$ .

- $T_{\text{period}}$  is the period of the pipeline.

We list below the constraints that need to be enforced. For simplicity, we write  $\sum_{u}$  instead of  $\sum_{u \in [1..p] \cup \{\text{in,out}\}}$  when summing over all processors. First there are constraints for processor and link usage:

- Every stage is assigned a processor:  $\forall k \in [0..n+1], \sum_{n} x_{k,n} = 1.$

- Every communication either is assigned a link or collapses because both stages are assigned to the same processor:

$$\forall k \in [0..n], \qquad \sum_{u \neq v} z_{k,u,v} + \sum_{u} y_{k,u} = 1$$

• If stage  $S_k$  is assigned to  $P_u$  and stage  $S_{k+1}$  to  $P_v$ , then  $link_{u,v}: P_u \to P_v$  is used for this communication:

$$\forall k \in [0..n], \forall u, v \in [1..p] \cup \{\text{in, out}\}, u \neq v, \qquad x_{k,u} + x_{k+1,v} \leq 1 + z_{k,u,v}$$

• If both stages  $S_k$  and  $S_{k+1}$  are assigned to  $P_u$ , then  $y_{k,u} = 1$ :

$$\forall k \in [0..n], \forall u \in [1..p] \cup \{\text{in,out}\}, \qquad x_{k,u} + x_{k+1,u} \le 1 + y_{k,u}$$

• If stage  $S_k$  is assigned to  $P_u$ , then necessarily first<sub>u</sub>  $\leq k \leq \mathsf{last}_u$ . We write this constraint as:

$$\forall k \in [1..n], \forall u \in [1..p], \qquad \text{first}_u \le k.x_{k,u} + n.(1 - x_{k,u})$$

$$\forall k \in [1..n], \forall u \in [1..p], \qquad \text{last}_u \ge k.x_{k,u}$$

• If stage  $S_k$  is assigned to  $P_u$  and stage  $S_{k+1}$  is assigned to  $P_v \neq P_u$  (i.e.  $z_{k,u,v} = 1$ ) then necessarily  $\mathsf{last}_u \leq k$  and  $\mathsf{first}_v \geq k+1$  since we consider intervals. We write this constraint as:

$$\begin{split} \forall k \in [1..n-1], \forall u,v \in [1..p], u \neq v, & \quad \mathsf{last}_u \leq k.z_{k,u,v} + n.(1-z_{k,u,v}) \\ \forall k \in [1..n-1], \forall u,v \in [1..p], u \neq v, & \quad \mathsf{first}_v \geq (k+1).z_{k,u,v} \end{split}$$

• There remains to express the period of each processor and to constrain it by  $T_{period}$ :

$$\forall u \in [1..p], \qquad \sum_{k=1}^n \left\{ \left( \sum_{t \neq u} \frac{\delta_{k-1}}{\mathsf{b}_{t,u}} z_{k-1,t,u} \right) + \frac{\mathsf{w}_k}{\mathsf{s}_u} x_{k,u} + \left( \sum_{v \neq u} \frac{\delta_k}{\mathsf{b}_{u,v}} z_{k,u,v} \right) \right\} \leq T_{\mathsf{period}}$$

Finally, the objective function is to minimize the period  $T_{\sf period}$ .

We have  $O(np^2)$  variables, and as many constraints. All variables are boolean or integer, except the period, which is rational. We present some experiments comparing the heuristics to the linear program solution, when the number of variables is small enough to allow for a resolution in reasonable time.

#### 6.2 LP Experiments

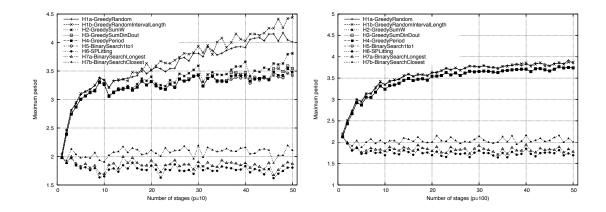

We compared the performance of the heuristics with the optimal solution returned by the linear program. Because of the large number of integer variables, experiments have been constrained to small platforms and applications. Also, in the following, we use only 10 instances of each application; we used 100 instances in the previous experiments but the LP programs can be quite long to solve. The results now represent an average over these 10 instances of the problem.

#### 6.2.1 LP limitation

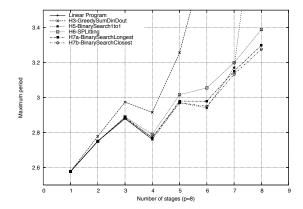

The largest experiment has been conducted with p=8 processors. We tried to solve the linear program with up to n=8 stages. The parameters are chosen randomly as in Experiment 1, with homogeneous communications and balanced communication/computation ratios (Section 5.1).

However, from n=4 stages, the LP program requires quite a long time to be solved: it took up to 14 hours of computation time to solve a single instance of the problem. Because it was already very long for n=4, we did not experiment with higher values of n. In practice, the use of the linear program in such cases is very limited because of the extremely long time required for the resolution.

We plotted (Figure 10) the result obtained with the LP program and some of the relevant heuristics. We see that the best heuristics, in this case the optimal ONE-TO-ONE MAPPING obtained with H5 and the binary search H7b, are very close to the result of the LP. The table displays the exact results, and we can see that there is only a tiny difference between the optimal result of the LP and the result returned by our heuristics. This can be explained by the precision of the binary search which was set to 0.0001. A more accurate result could have been obtained with the heuristics by increasing the precision.

| n | LP       | H5-BS121 | H7b-BSC  |

|---|----------|----------|----------|

| 1 | 2.576857 | 2.576882 | 2.576882 |

| 2 | 2.749913 | 2.749934 | 2.749934 |

| 3 | 2.879871 | 2.879900 | 2.883072 |

| 4 | 2.760960 | 2.760981 | 2.770690 |

Figure 10: LP limitation.

#### 6.2.2 LP on small platforms

Since we could not perform large experiments with the LP on platforms with many processors, we restricted ourselves to smaller platforms in order to study the absolute performance of the heuristics. The results seemed quite encouraging on the previous experiment with up to 4 stages and 8 processors, since we almost always found the optimal mapping.

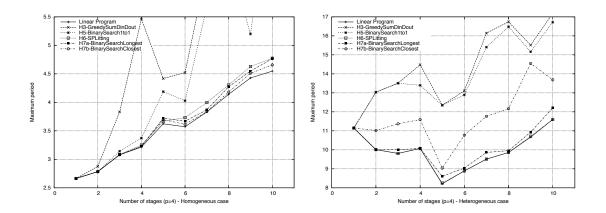

This experiment has been conducted on a platform with p=4 processors, and applications with up to n=10 stages. We plot the results for the homogeneous case (similar to Experiment 1, Section 5.1) and for the heterogeneous case (similar to Experiment 2, Section 5.2), which are the two most relevant cases. We restrict the plots (Figure 11) to some of the best heuristics identified in the previous experiments.

Figure 11: LP on small platforms.

In the homogeneous case, we point out that the best heuristic H7b is very close to the optimal result returned by the LP program. The maximum difference is for n = 10, with a difference of 0.11, which represents an error of less than 3%. This result is quite promising, even though we cannot conduct experiments for larger platforms because of the LP limitation.

The results are even better in the heterogeneous case, where the splitting heuristic H6 is almost always returning the optimal mapping, with a largest error less than 0.05%.

Altogether, despite its intrinsic limitation to small platforms, the LP formulation enables us to assess the absolute performance of our heuristics. The results are very satisfying since the heuristics are always very close to the optimal result. In addition, their execution time remains small for large application/platform pairs, while the LP is not usable for platforms with more than 8 processors, due to the large number of integer variables.

#### 7 Related work

As already mentioned, this work is an extension of the work of Subhlok and Vondran [32, 33] for homogeneous platforms. We have also discussed the relationship with the chains-to-chains problem [11, 20, 17, 21, 25, 26] in Section 3.2.2.

We classify several related papers along the following four main lines:

Scheduling task graphs on heterogeneous platforms— Several heuristics have been introduced to schedule (acyclic) task graphs on different-speed processors, see [24, 35] among others. Unfortunately, all these heuristics assume no restriction on the communication resources, which renders them somewhat unrealistic to model real-life applications. Recent papers [18, 19, 30] suggest to take communication contention into account. Among these extensions, scheduling heuristics under the one-port model [22, 23] are considered in [3]: just as in this paper, each processor can communicate with at most one other processor at a given time-step.

Mapping pipelined computations onto special-purpose architectures— There are two lines of work related to mapping pipeline computations onto special architectures: the first deal with special-purpose architectures and FPGA arrays. A representative example is the work by Fabiani and Lavenier [15]. They study the placement of linear computations onto reconfigurable arrays. The other line of work is related to the design of fault-tolerant or power-aware mappings for embedded systems. Representative examples are [36, 2].