# Using rewriting techniques to produce code-generators and proving them correct

A. Despland, M. Mazaud, Rivo Rakotozafy

#### ▶ To cite this version:

A. Despland, M. Mazaud, Rivo Rakotozafy. Using rewriting techniques to produce code-generators and proving them correct. RR-1046, INRIA. 1989. inria-00075513

## HAL Id: inria-00075513 https://inria.hal.science/inria-00075513

Submitted on 24 May 2006

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

UNITÉ DE RECHERCHE INRIA-ROCOUENCOURT

Institut National de Récherche en Informatique et en Automatique

Domaine de Voluceau Rocquencourt BP105 78153 Le Chesnay Cedex France Tel/(1) 39 63 5511

## Rapports de Recherche

N° 1046

Programme 1

## USING REWRITING TECHNIQUES TO PRODUCE CODE-GENERATORS AND PROVING THEM CORRECT

Annie DESPLAND

Monique MAZAUD

Raymond RAKOTOZAFY

Juin 1989

#### Programme 1

## Using rewriting techniques to produce code-generators and proving them correct

# Production et preuve de générateurs de code par techniques de réécriture

Annie Despland\* Monique Mazaud\*\* Raymond Rakotozafy\*

#### Abstract

A major problem in deriving a compiler from a formal definition is the production of correct and efficient object code. In this context, we propose a solution to the problem of code-generator generation.

Our approach is based on a target machine description where the basic concepts used (storage classes, access modes, access classes and instructions) are hierarchically described by tree-patterns. These tree-patterns are terms of an abstract data type. The program intermediate representation (input to the code-generator) is a term of the same abstract data type.

The code generation process is based on access modes and instructions template-driven rewritings. The result is that each program instruction is reduced to a sequence of elementary machine instructions, each of them representing an instance of an instruction template.

The axioms of the abstract data type are used to prove that the rewritings preserve the semantics of the intermediate representation.

#### Résumé

La production de code efficace et correct est un aspect crucial de la construction de compilateurs à partir de spécifications formelles. Nous proposons ici une solution au problème de la construction de générateurs de code.

Notre approche est fondée sur une description de la machine cible où les concepts de base (classes de ressources, modes d'accès, classes d'accès et instructions) sont décrits hiérarchiquement par des modèles d'arbres. Les modèles sont les termes d'un type abstrait. La représentation intermédiaire du programme source (donnée du générateur de code) est un terme de ce type abstrait.

Le processus de génération de code est un processus de réécriture d'arbre guidé par les modèles de modes d'accès et les modèles d'instructions. A la fin de ce processus, chaque instruction du programme source est transformée en une séquence d'instances de modèles d'instructions dont chaque élément correspond à une instruction machine.

Les axiomes du type abstrait sont utilisés pour démontrer que les réécritures préservent la sémantique de la représentation intermédiaire.

<sup>\*</sup> L.I.F.O. Université d'Orléans BP 6759, 45067 Orléans CEDEX2, France and I.N.R.I.A. \* \* I.N.R.I.A. Domaine de Voluceau, BP 105, 78153 Le Chesnay CEDEX, France.

## Using rewriting techniques to produce code-generators and proving them correct

Annie Despland\* Monique Mazaud\*\* Raymond Rakotozafy\*

- \* L.I.F.O. Université d'Orléans BP 6759, 45067 Orléans CEDEX2, France and I.N.R.I.A.

- \* \* I.N.R.I.A. Domaine de Voluceau, BP 105, 78153 Le Chesnay CEDEX, France.

#### Introduction

A compiler, in order to produce code, needs full knowledge of not only the syntax and the semantics of the source language but also of the structure of the target machine and the semantics of its instruction set. Therefore, each combination of source and target languages needs its own compiler. The profusion of new languages and computers leads to a constant demand for new compilers. Considerable research effort has been put into making the compiler construction as modular and automatic as possible. At present, automatic production of parsers from a BNF-like specification of grammars is widely known and used.

As the properties of the source and the target languages are quite different, it is necessary to introduce an intermediate representation (I.R).

Numerous works have developed techniques and tools for the implementation of retargetable code-generators. Such tools should combine portability features and ease of writing for the compiler writer. Moreover they must make it possible:

- to clearly separate the description of a general technique from its application to a particular machine.

- to describe and achieve various code generation subtasks without imposing any particular ordering on them.

- to accept as input a description easy to deduce from the handbook of the machine.

The use of formal description of a target machine within a compiler writing system has given rise to several techniques. Some use a table-driven description of the instruction set, others use templates for each I.R primitive for which code has to be produced.

In the past few years, the code selection problem has received a lot of attention and has been relatively successfully dealt with in works of Cattell [Cat 77], Graham-Glanvillle [GG 78][GH 84], Ganapathi-Fischer [GF 82], Ganzinger-Giegerich [Gan Gie 82].

In contrast, the storage allocation phase of code generation seems to have been neglected with the exception of the PQCC system [LCHNRSW 79] [Lew 81], which gives a partial solution to this problem.

In all these works, the I.R and the target machine specification are of a quite different nature.

- the Graham-Glanville approach is similar to the methods used for table-driven syntax analysis, and a target machine description is used to derive a parser. The overall structure of the code selection algorithm is similar to the one of an LR(1) parser, which works on the linearized string of an intermediate tree and produces a sequence of instructions. It is necessary to design an I.R for each combination of source and target languages.

- Cattell uses TCOL (a universal tree language) for the I.R. From a complete specification of the instruction set processor, tree templates are built which depict instructions. The code is emitted during a recursive top-down traversal of the I.R tree.

- Giegerich [Gie 85] describes the target machine as a signature of an algebraic abstract data type. The code generation is achieved by the production of a term of this abstract data type.

- Aho and Ganapathi [Aho Ga 85] propose to represent the target machine instructions as tree rewriting rules, each of them consisting in a replacement node, a tree template, a cost and an action. The code selection is done using a combination of efficient tree-pattern matching with dynamic programming. This can be done using the tree manipulation language called Twig, implemented by Tjiang [Tji 86]. Register allocation is done by user specified actions.

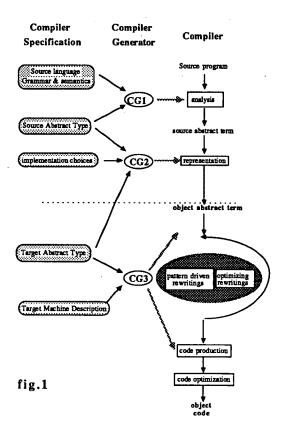

The main drawback of the systems above is that the input I.R can not be parameterized by the features of both the source language and the target machine. The solution proposed here overcomes this. It produces, as in the Perluette system [GDM 84] [Des 82], a compiler from a specification in three parts: a source language definition, a target language definition and the description of the implementation choices(see fig 1). The source and target language definitions are algebraic data types (ADT), the implementation choices define a mapping from the source ADT to the target ADT.

The target machine description is hierarchically structured in three levels [DMR 87]:

- storage description (sets of available locations i.e registers, memory locations, stacks..) as storage classes;

- addressing modes description (various ways to access locations) as access modes;

- instruction set description.

Generally speaking, the addressing mode semantics depends on the position (source or destination) of the corresponding operand. That is the reason why we have included the position in the definition of the concept of an access mode template. As an operand of an instruction may accept several access modes, the access modes are assembled in access classes. So the access classes are instruction parameters. The semantics of access modes and instructions is given as terms of the target data type. Once the correct I.R term is produced, the code generation will proceed in four steps (omitting optimization tasks):

- access modes templates and instructions templates pattern-matching. The bottom-up matching process of the I.R is carried out until the I.R is identified to instructions templates. In the context of an instruction template, operand subterms are matched with access mode templates. When it succeeds, the subterm is replaced by a representative tree of the access mode recognized. This representative is called in the sequel "canonical form". When it fails, an inner subterm, matching an access mode template, is replaced by a temporary resource. This requires the insertion of elementary universal store trees of temporary results in temporary storages.

The result is an I.R whose leaves are instantiated access modes in "canonical form". In order to recognize an instruction template instance, it is necessary to verify that the access modes of the I.R belong to the corresponding access classes of the instruction template. At this point of the rewriting process, the I.R is in its "canonical form".

We use universal store more efficiently than Cattell [Cat 77], because in our approach, temporaries are explicitly managed and have their own operators. This allows us to achieve the correct assignment of storage locations and an easy choice of the right mnemonic (for example the choice between MOVE.B, MOVE.W and MOVE.L on the MC68000 is thus possible).

- binding. Each temporary access mode is bound with the list of the allowed access modes.

- register assignment. According to the available storages, first we pick for each temporary the storage class related to the cheapest access mode of the preceding set. Second we choose the name of an available location of this storage class for the temporary.

- code production. Now, the I.R is a tree built up with instances of instruction templates rooted by the sequence operator. As each instruction template is decorated with the corresponding assembly instruction mnemonic, the code emission can be simply achieved by a top-down sequential tree traversal of these instances

All the above steps concern the I.R tree. In particular, the allocation of storage locations transforms the tree leaves but has no immediate effect on code production: unlike Cattell, the possibility of choosing the right mnemonic is postponed until the end. Moreover, in our system, and contrary to the PQCC, the temporaries generated by the algorithm are set clearly apart and have their own operators. This enables them to be explicitly

addressed. Optimizations specified by tree rewritings can take place at any time. Code production constitutes the ultimate phase of the global rewriting process of the I.R tree.

This solution allows a modular multi-pass code generation process with the different optimization tasks inserted as rewritings according to the compiler writer's wishes. Such an approach confers modularity and independence to our system as in the MUG2 system [GRW 77] [Gan Gie 82], while conserving the descriptive features of the Cattell and Graham-Glanville approaches.

Our solution to automatic production of code-generators is complete in the sense that it tackles correctly both the code selection and the storage allocation problems.

This paper is divided into three sections. The first one presents the two specifications required as input to the code-generator generator: a formal specification of the target machine and the I.R description.

The second one deals with the code-generator generator itself: first, definitions of tree templates associated with the target machine components are given, then the I.R rewriting algorithm (which precedes the code emission phase) is developed. Finally, the looping and blocking problems are discussed.

The third one deals with the correctness proof of the code-generator produced.

The basic concepts developed here are illustrated by MC68000 examples throughout the paper.

#### 1 Inputs to the code-generator generator

#### 1.1 Specification of the target machine

We provide a language to specify the instruction set processor of a target machine. The basic concepts used are described by specific constructs of the language: storage bases, storage classes, value classes, access modes, access classes and instructions.

Each construct is defined by properties such as the size of the associated addressable units or the semantics of the occurrence of the construct. This semantics is expressed using a term of the target abstract data type and takes into account this size.

As the occurrences of a construct are related to the size of the addressable units, their semantic descriptions are nearly identical [DMR 87]. A solution proposed to deal with large algebraic specifications [BGM 87] is the use of

parameterization and instantiation mechanisms. Such mechanisms fit very well to our machine specification language.

The compiler writer can factor some instances of a given construct in a generic pattern followed by the possible values of the generic parameters of the pattern. The system derives from this declaration as many occurrences of the construct as there are sizes of addressable units associated to it. The instantiation mechanism is bound to a name generation mechanism.

Throughout the paper the following notations will be used:

- . If n is a name and L is a variable, when L is instantiated by v, n! L builds the name n\_v.

- . <S V> means that V is a constant or a variable of sort S.

- . All keywords of the language are in bold letters in the following examples.

#### 1.1.1 Storage structuring

A component of the physical storage doesn't represent the same operand depending on the size associated to the operation applied to this operand. For instance, an access to a register may designate a byte operand, a word operand or a longword operand. So, we define two fundamental concepts: storage base and storage class. A storage base is defined as a set of smallest addressable units of physical storage. For a given storage base, the compiler writer must describe as many storage classes as there are ways to gather storage base elements to represent logical storage units.

A storage class occurrence is characterized by the following properties:

- its denotation

- its storage base viewed as an attribute (in the attributed grammars meaning) of a storage class

- the dereference operation that can be applied to this storage class i.e. the access operation to the contents of an element of this storage class.

In the machine description language, the storage class construct is described using a predefined keyword for each of these properties.

The MC68000 has two kinds of registers: the data registers dedicated to data values and address registers dedicated to addresses. Thus, the compiler writer must declare the two following storage bases:

```

Storage_base DREG -- Data registers

Set is { DREG [k] where k in 0 .. 31 }

End

Storage_base AREG -- Address registers

Set is { AREG [k] where k in 0 .. 13 }

End

```

Let us consider the storage classes related to the data register storage base. As an access to a data register may represent an access to a byte operand, a word operand or a long word operand, the compiler writer must declare three storage classes respectively: the "dregister\_B", the "dregister\_W" and "dregister\_L" storage classes.

```

Storage class

Storage class

Denotation < dregister_B D<sub>k</sub>>

Denotation <dregister_W D<sub>k</sub>>

Attributes

Attributes

Base = DREG

\$Base = DREG

Dereference operation

Dereference operation

cont_of_dreg_B (<dregister_B D<sub>k</sub>>)

cont_of_dreg_W (<dregister_W D<sub>k</sub>>)

Symbolic notation

Symbolic notation

D_k is DREG [4*k]

D_k is DREG [4*k..4*k+1]

where k in 0..7

where k in 0..7

End

End

```

The compiler writer must declare similarly the dregister\_L storage class.

Notice that these three declarations are quite similar. In this context, the use of the parameterization and instantiation mechanisms is specially useful. In order to avoid the repetition of similar declarations, the compiler writer can declare a generic pattern of a *data register* storage class using generic names. The instance part of the declaration includes the information needed by the name generation mechanism to build the effective names.

```

Storage_class

Denotation < dregister! size D<sub>k</sub>>

Attributes

$Base = DREG

Dereference operation

cont_of_dreg!size (<dregister!size Dk>)

Symbolic notation

D<sub>k</sub> is DREG [4*k..4*k+length-1]

where k in 0..7

Instances

size in {B, W, L}

case size is

B: length is 1

W: length is 2

L: length is 4

End case

End

```

From this pattern, the system deduces the three preceding descriptions of effective storage classes.

The specification of the address register class is similar to that of the data register class. The only difference is that the byte access to an address register is not available.

```

Storage class

Denotation <aregister!size A<sub>k</sub>>

Attributes

\$Base = AREG

Dereference operation

cont_of_areg!size (<aregister!size Ak>)

Symbolic notation

Ak is AREG [2*k..2*k+length-1]

where k in 0..7

Instances

size in {W, L}

case size is

W: length is 1

L: length is 2

End case

End

```

The system deduces the description of the "aregister\_W" and "aregister\_L" storage classes from this pattern.

#### 1.1.2 Value classes

On any machine, there are instructions whose operands are immediate constants. Their value is generally stored in the address space of the instruction. We define value classes corresponding to allowed ranges for the operands to get homogeneous description. We suppose that there exists a value base named INTEGER including all possible value classes. In the same way, we suppose that there exists a label value base named LABEL.

On the MC68000, an immediate value operand may be a signed integer represented by a byte, a word or a longword value.

```

Value_class

Denotation <value!size val>

Attributes

$Base = INTEGER

Symbolic_notation

val in -2**(length-1) ..2**(length-1) -1

Instances

size in {B, W, L}

case size is

B: length is 8

W: length is 16

L: length is 32

End case

End

```

#### 1.1.3 Access modes

Let us consider an assignment statement of A to B, we shall state in the sequel that A is the source operand and B the destination operand of the assignment. In an instruction context, an operand is designated by an addressing mode. Whereas an addressing mode in source position designates the contents of a storage, it designates the storage itself in destination position.

A particular machine has several addressing modes. For a given addressing mode of the machine, the compiler writer must define as many access modes as there are associated storage classes.

An access mode pattern is specified by:

- a canonical form, representative of the access mode, including its name and its parameters. These parameters are formal storage or value classes.

- its related attributes: length, format and costs.

- templates that describe the access path to the corresponding operand when it is respectively in destination position and in source position. They are introduced by the keywords dst and src and defined by a term of an abstract data type.

As for the storage class construct, the compiler writer can define a formal access mode.

Among the numerous addressing modes of the MC68000, let us consider the *data register* addressing mode. Its associated storage classes are byte data register, word data register, longword data register. Thus the compiler writer define a generic access mode pattern "dreg\_am!size" parameterized by the generic data register "dregister!size" defined in the §1.1.1. The instances define the effective *data register* access modes with their appropriate storage class.

```

Access mode

- - Data register access modes

Canonical form

dreg_am!size ( <dregister!size reg> )

Attributes

$length

- - length of the addressable unit

$fmt

~reg~

- - Assembly language format

Templates

dst

<dregister!size reg>

- - access path in destination position

src

cont_of_dreg!size (dst)

- - access path in source position

Instances

size in {B, W, L}

End

```

When an access mode template in source position is defined by the dereference operation (here "cont\_of\_dreg!size") applied to the term which defines the access mode template in destination position, the

compiler writer can use the abbreviation dst to denote the access mode template in destination position. For example, using the preceding definition, the system derives the definition of the "dreg\_am\_B" access mode.

```

Access mode

Canonical form

dreg_am_B (<dregister_B reg>)

Attributes

$length (dreg_am_B (<dregister_B reg> ))

$fmt (dreg_am_B(<dregister_B reg>))

= ~reg~

Templates

dst (dreg_am_B(<dregister_B reg> ))

= <dregister_B reg>

src (dreg_am_B(<dregister_B reg> ))

= cont_of_dreg_B (<dregister_B reg>)

End

The indirect with displacement access mode has instances which depend on the size of the location indirectly

accessed in source position.

Access mode

Canonical form

- - Indirect with displacement access modes

disp_am!size ( <aregister_L reg> , <value_W val>)

Attributes

$length

size

- - length of the addressable unit

~val(reg)~

$fmt

- - Assembly language format

Templates

dst

index!size

- - access path in destination position

(cont_of_areg_L(<aregister_L reg>)

,<value_W val>)

src

cont_of_laddress!size (dst)

- - access path in source position

Instances

size in {B, W, L}

End

```

#### 1.1.4 Access classes

The operands of an instruction are access classes which are defined as sets of access modes. An access class can be also specified by a generic pattern including the instantiation of its elements. There are as many instances of a generic access class as there are possible sizes of operands.

```

Access_class

<All_access!size AM>

= dreg_am!size (<dregister!size reg>)

= areg_am!size (<aregister!size reg>)

= ...

where size in {B, W, L }

where size in {W, L }

```

#### 1.1.5 Instructions

An instruction may be characterized by the following properties:

- the access classes defining the operands on which the instructions apply

- its related attributes: format, i.e the syntax in the assembly language, length ...

- the template describing what is performed by the instruction (it is a term of an abstract data type)

Nearly every instruction of the target machine may be applied to the different lengths of its operands. In order to avoid the repetition of such descriptions, the compiler writer specifies a pattern of an instruction and its instances.

Let us consider the *move* instruction which corresponds to an assignment operation. The size of the instruction may be specified to be a byte, a word or a longword. We get the following specification:

# Instruction move!size (<All\_access!size AM1>, <Altdata\_access!size AM2>) Attributes \$length = size \$fmt = ~MOVE.\$length \$fmt (<All\_access!size AM1>) , \$fmt (<Altdata\_access!size AM2>)~ Template assign!size (src (<All\_access!size AM1>) , dst (<Altdata\_access!size AM2>)) Instances size in {B, W, L}

#### End

The value of the attribute format (\$fmt) of an access class is synthetized from the value of the corresponding attribute of this access mode. The *add* instruction presented below adds an operand in a data register to an operand in memory location and puts the result in the data register.

```

Instruction

add!size ( <All_access!size AM1>, <Dregister_access!size AM2> )

Attributes

$length = size

$fmt = ~ADD.$length $fmt ( <All_access!size AM1> )

, $fmt ( <Dregister_access!size AM2> )~

Template

assign!size

(add!size (src ( <Dregister_access!size AM2>)

, src ( <All_access!size AM1> ))

, dst ( <Dregister_access!size AM2> )

Instances

size in {B, W, L}

End

```

#### 1.2 Intermediate representation

#### 1.2.1 Introduction

Let us summarize the specification process of the code-generator for a given target machine. The machine is specified by the description of available locations, access modes and instructions in the form presented above. As the locations are defined, names of sorts are associated to them. The access modes and instructions are specified by operators on locations. Thus, a set of operations with the corresponding domains and co-domains can be defined. Therefore the specification of the code-generator includes two parts:

- the target machine description

- the target abstract data type related to the target machine.

In the framework of a compiler writing system which works in three steps (see fig 1), the intermediate form input of the code-generator is a target abstract term. It is the representation of a source abstract term which is the semantic value associated to the source program. The source term corresponding to the semantic value of a statement is a term of type modification as defined in [GDM 84]. The representation of a modification of the source abstract data type is a modification of the target abstract data type.

The translation of the semantic value of the source program in terms of semantic value of the target program is specified and proved [GDM 84] to be the representation of one abstract data type into another. The translation of a source abstract term into a target abstract term is a rewriting corresponding to this representation. The basic I.R for the code generation process is the tree corresponding to the abstract target term. The code generation process can be considered as a rewriting process such that at the end of the rewritings, each son of the root is an instance of an instruction template.

#### 1.2.2 Abstract data type related to the target machine

In order to emit the code related to an instruction, it is necessary to recognize an instance of an instruction template. As in the syntactic analysis process, an automaton is derived automatically. It is used by a target machine independent kernel which consists of an analyser and modules of rewriting and tree construction. The target term, input to the code generation process belongs to the target abstract data type. The specification of the target abstract data type given by the compiler writer includes:

- a set of names of sorts

- a signature, i.e a set of names of operations with their corresponding domains and co-domains

- a set of axioms.

Sorts are defined from the machine description elements such as storage classes and value classes.

The description of the signature of the target machine ADT is factored in the same way that the description of the constructs in the machine specification language, using the name generation mechanism.

ADT target\_machine

#### Sort

```

laddress!size - Address

, aregister!size if size in {W, L} - address register

, dregister!size - data register

, value!size - Immediate Value Operand

, data_label!size - Data label

, code_label!size if size in {B, W} - Code label

```

Union of sorts represent basic concepts such as memory locations and operands.

```

cell!size = Union (aregister!size, dregister!size, laddress!size) - Memory Location

operand_src!size = Union (value!size, data_label!size, laddress!size) - contents of memory location

- or contents of register

operand_dst!size = Union (data_label!size, laddress!size, aregister!size, dregister!size, code_label!size)

operand_src = Union (operand_src_B, operand_src_W, operand_src_L)

operand_dst = Union (operand_dst_B, operand_dst_W, operand_dst_L)

```

#### **Operations**

The operations of the target abstract type include:

• the usual arithmetic and logical operations.

```

(value!size, value!size)-> value!size: add!size(value!size, value!size)-> value!size: sub!size

```

• the operations of sort modification that represents instructions.

```

(operand_src!size, cell!size)

-> modification

: assign!size

(modification, modification)

-> modification

: seq

```

- the operations describing access path to memory cells such as:

- the indexing operation which adds an offset to an address

- the access to the contents of an address (byte, word and long)

- the access to the contents of a data register or an address register

```

(laddress_L, value_W)

-> laddress!size

: index!size

(laddress!size)

-> operand_src!size

: cont_of_laddress!size

(aregister!size)

-> operand_src!size

: cont_of_areg!size

(dregister!size)

-> operand_src!size

: cont_of_dreg!size

```

```

Instances

```

--- size in {B, W, L}

End target\_machine

#### 2 The code-generator generator

#### 2.1 Introduction

The I.R. given as input to the code generation process is a sequence of modifications. Modifications  $M_i$  of the sequence are dealt with one after the other, trying to match each of them with an instruction template (because each instruction template corresponds exactly to one assembly instruction). Generally speaking, the modification  $M_i$  is not an instance of an instruction template. In that case, the code generation process transforms the tree  $M_i$  into a sequence of trees representing intermediate computations, followed by an instance of an instruction template.

Let us consider now the pattern matching process of a modification  $M_i$ , with an instruction template. It is necessary to recognize the sons  $S_{ij}$  of  $M_i$  as operands of an instruction template i.e. as elements of access classes. As an access class is a set of access modes, each son  $S_{ij}$  of  $M_i$  must be recognized first as an access mode.

When a subtree  $S_{ij}$  matches an access mode, it is replaced in  $M_i$  by a representative tree of the access mode which is the "canonical form" of the access mode. When the match fails, the largest subtree  $H_{ij}$  of  $S_{ij}$ , starting from the leaves that matches an access mode is considered. It computes an intermediate operand which is stored in a temporary resource. The subtree  $H_{ij}$  in  $S_{ij}$  is replaced by the reference to the temporary resource.

#### 2.2 Templates and canonical forms

#### 2.2.1 Access mode templates

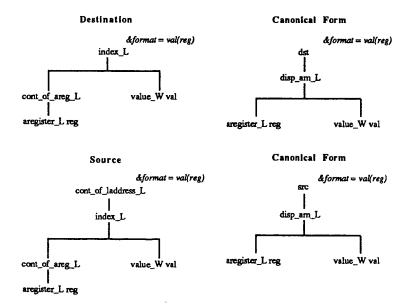

From the specification of access modes, the system deduces two families of trees: one for the access modes in source position, the other one for the access modes in destination position. In order to emit the corresponding code, it is necessary to store the format; this is done by means of the attribute & format. By convention, attribute names are preceded by "&".

For each tree template of these families, the system builds a tree corresponding to the related "canonical form".

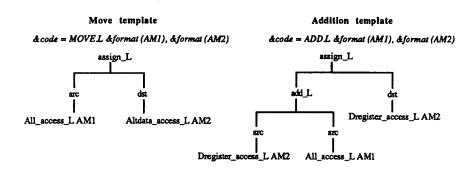

#### 2.2.2 Instruction templates

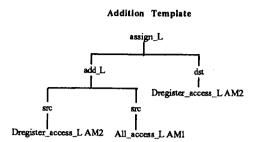

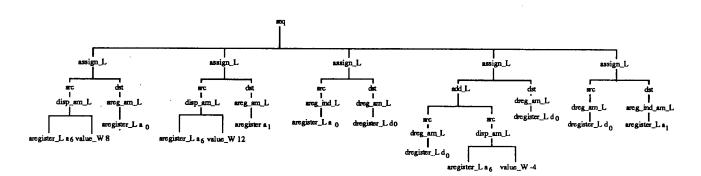

An instruction template is a tree (decorated with the code attribute), the parameters of which are either access modes in "canonical form" or access classes. The templates associated with a *move* instruction and with an *add* instruction are given below:

#### 2.3. Specification for intermediate representation rewritings

#### 2.3.1 Universal operations and temporaries

When the matching of a subtree of the I.R. with an access mode template fails, the computation of an intermediate operand must be designed. Such a computation is stored in a temporary location. In order to perform this, the following sort and the associated operation are provided by the system:

- the sort "temporary" with its related access mode: "temporary\_am" and its dereference operation "contents\_of"

- the universal store operation "Univ\_assign" which allows to store a source operand in a temporary location.

The store of an intermediate operand is represented by a tree, that must be rooted in sequence with the rewritten tree  $M_i$  (see § 2.1), in order to preserve the whole calculus. The "Univ\_seq" operator is provided by the system for that purpose.

In order to be able to produce code for trees involving universal operators, it is necessary to rewrite them into instances of instruction templates. That is the reason why, the compiler writer must specify equivalence declarations between the machine operators and the universal operators. This is declared by the compiler writer in an interface between the machine specification and the code-generator writing system. During the binding step the temporary access modes are bound to the access modes selected for the management of temporary locations.

The equivalence declarations for the MC68000 are specified below:

Univ\_seq : seq

Univ\_assign : assign!size where size in (B, W, L)

temporary\_am(<temporary temp>): areg\_am!size (<aregister!size temp>) where size in {W, L}

| dreg\_am!size (<dregister!size temp>) where size in {B, W, L}

| relative\_am!size (<data\_label!size temp>) where size in {B, W, L}

The universal sequence operator "Univ\_seq" is bound to the sequence operator "seq" of the target data type. The universal store operator "Univ\_assign" is bound to different assign operators of the target data type (assignment on byte, word and longword operands). The access mode on temporaries is bound to all access modes allowing direct access to an address register, to a data register or relative access to the memory. They are given in the preference order according to their cost; the binding step takes this order into account.

#### ADT universal use target\_machine

#### Sort

temporary

#### **Operations**

```

(temporary)-> operand_src: contents_of(operand_src, temporary)-> modification: Univ_assign(modification, modification)-> modification: Univ_seq

```

#### Axioms

```

Univ_seq(U<sub>1</sub>,...,U<sub>p</sub>,Univ_seq(V<sub>1</sub>,...,V<sub>n</sub>)) = Univ_seq(U<sub>1</sub>,...,U<sub>p</sub>,V<sub>1</sub>,...,V<sub>n</sub>)

where U<sub>1</sub>,...,U<sub>p</sub> and V<sub>1</sub>,...,V<sub>n</sub>: modification

```

#### End universal

The universal sequence operator has the associativity property. Axioms dealing with the canonical form of the temporary access modes are defined in the following section.

#### 2.3.2 Abstract data type of the canonical term

The axioms associated to the sort "operand" express the definition of the canonical form of the access modes. There is however a slight difficulty with the register access modes axioms. For such access modes, it is not possible to directly derive the axioms from the definition of the access paths in the two positions because the system would not be confluent. That is the reason why it is necessary to take into account the context of an instance of a register access mode. It is done using the context of the modification.

ADT canonical\_form use target\_machine, universal

```

Sort

```

```

operand!size = Union (operand_src!size, operand_dst!size)

operand = Union (operand_B, operand_W, operand_L)

```

#### **Operations**

```

(operand)

operand_src

src

(operand)

operand dst

dst

(aregister!size)

operand!size

areg_am!size

(aregister!size)

operand!size

areg_ind am!size

(register_L, value_W)

operand!size

disp_am!size

(temporary)

operand

temporary_am

```

#### Axioms

The new modifications appearing in the rewritten tree deal with the universal store operator and the sequence operator. As the "Univ\_assign" operator applies on an access mode in source position which is stored in a temporary in destination position, the axiom describing the semantics of "Univ\_assign" has a meaning only in that case. From now on, the target abstract data type will be the union of the abstract data type related to the target machine and of the universal operators and the abstract data type of the canonical form.

#### 2.4 Intermediate representation rewritings

#### 2.4.1 Introduction

The rewriting algorithm belongs to the target machine independent kernel of the code-generator. At present, this algorithm applies to an I.R corresponding to a sequence of modifications.

For each I.R term the rewriting algorithm needs to know the boundary where the access mode pattern matching can stop and where the instruction pattern matching can begin. For this purpose, we define a partition of instruction templates into instruction classes that have the same boundary.

The leaves of instruction templates are denotation of access classes (they can be considered as typed variables) or access modes. Two templates of an instruction class can only differ on the type of the variables. We are interested in the "canonical representative" of such a class, i.e., a tree in which all the sons of src and dst are replaced by variables where each variable has a single occurrence. If we consider all the addition instruction templates, the canonical representative of the instruction class is:

assign!size (add!size(src(X), src(Y)), dst(Z))

#### 2.4.2 The rewriting rules of a modification

Each term of the I.R. corresponding to a modification is rewritten until the pattern matching with an instruction template succeeds.

The strategy of application of the rewriting rules is strongly connected with the notion of canonical representative of an instruction class which defines the context of research of access modes.

The algorithm of §2.4.3 describes the strategy of applications of the rewriting rules.

#### 2.4.2.1 Introduction

The transformation rules of the I.R. are not rewriting rules in the common sense of term rewriting systems [HO 80].

Usually a rewriting rule is a formula of the form

$$\lambda \rightarrow 0$$

If t is a term filtered by  $\lambda$ , i.e. there exists a minimal substitution  $\sigma$  such that  $\sigma(\lambda) = t$ , then t is rewritten into t' such that  $t' = \sigma(\rho)$ .

There are major differences in the way our system applies rewriting rules.

The first one is that the filtering process by a pattern is replaced by the composition of filtering processes with patterns belonging to differents sets of patterns.

The second one is that the variables appearing in the pattern terms have restricted definition domains. In a certain extend, they are "sorted" variables. Thus when filtering, it is necessary to verify if a subterm related to a variable belongs to the definition domain of the variable. So, we get as in [Kap 87] a notion of positive/negative conditional rewritings.

Each transformation rule consists of:

- The description of the input pattern defined in an operational way by the composition of the filtering processes on the different sets of patterns.

- The conditions that must be verified by the variable instances during the filtering process.

- The pattern of the output tree.

The description of the first two points are interleaved.

#### 2.4.2.2 Different kinds of rewriting rules

#### **Notations**

Let AM<sub>source</sub> be the ordered set of access mode patterns in source position.

Let AM<sub>destination</sub> be the ordered set of access mode patterns in destination position.

Let I be the ordered set of instruction patterns.

Let IC be the ordered set of instruction class patterns.

Let us denote can(A) the canonical form of the access mode whose pattern is A.

Let TR be the set of access mode patterns (in canonical form) that are defined by the compiler writer as possible rewritings of the temporary access mode.

Let CA be the set of access classes. Any element of CA is defined as a set of access modes.

Let us denote INST(X) the set of instances of the patterns belonging to the set X.

Let us denote  $t / [t_i = a]$  the tree t' obtained by replacement of the subtree  $t_i$  in t by the tree a.

All the sets of patterns defined here are ordered.

In all the following rules, the search for a pattern of a set of patterns that matches a term is done by trying the patterns of the set one after the other, with respect to the set ordering.

#### **Definitions**

- 1. A substitution pair <x, e> consists of a variable x and of a term e; it is said to pertain to variable x.

- 2. A substitution  $\sigma = \{ \langle x_i, e_i \rangle | 1 \le i \le n \}$  is a finite set of substitution pairs pertaining to distinct variables. We ignore pairs such as  $\langle x, x \rangle$  in  $\sigma$ .

#### Rule R1

When matching a tree t with an instruction class pattern, the source and destination position contexts are set according to the position nodes in the instruction class pattern. If there is a subtree  $t_i$  of t which is an instance of an access mode pattern in the right position, then  $t_i$  is replaced in t by the instantiated canonical form of the access mode pattern. The instruction class and access mode patterns are matched with respect to the ordering of the two sets IC and AM.

Let t be the tree to transform,

suppose that there exist  $T \in IC$  and a substitution  $\sigma_{IC}$

such that  $\sigma_{IC} = \{ \langle \Delta_i, t_i \rangle | \Delta_i \in Var(T), 1 \leq i \leq n \}$  with  $\sigma_{IC}(T) = t$

then, if there exists a subtree  $t_i$  of t such that  $< \Delta_i, t_i > \in \sigma_{IC}$ , and the context of  $\Delta_i$  in T, is the position  $pos \in \{source, destination\}$

and if there exist  $A \in AM_{pos}$  and a substitution  $\sigma_{AM}$  such that  $\sigma_{AM}(A) = t_i$ , we define the rewriting of the tree t by:

$$t \rightarrow t / [t_i = \sigma_{AM}(can(A))]$$

#### Rule R2

When matching a tree t with an instruction class pattern, if we find a subtree  $t_i$  of t which is not an instance of an access mode pattern, then starting from the leaves of  $t_i$ , we look for the biggest subtree  $t_{ij}$  of  $t_i$  which is an instance of an access mode in source position. A universal assignment tree is built whose source operand is the instantiated canonical form of the access mode corresponding to  $t_{ij}$  and whose destination operand is the reference to a new temporary location. The subtree  $t_{ij}$  is replaced in  $t_i$  by the temporary access mode in source position applied to this new temporary location. The universal assignment tree and the rewritten tree are rooted by a universal sequence operator.

Let t be the tree to transform,

suppose there exist  $T \in IC$  and a substitution  $\sigma_{IC}$

such that  $\sigma_{IC} = \{ \langle \Delta_i, t_i \rangle | \Delta_i \in Var(T), 1 \le i \le n \}$  with  $\sigma_{IC}(T) = t$

and suppose there exists  $t_i$  such that  $\langle \Delta_i, t_i \rangle \in \sigma_{IC}$ , and if the context of  $\Delta_i$  in T is the position pos

and such that for all  $A \in AM_{pos}$  there exists no substitution  $\mu$  such that  $\mu(A) = t_i$ .

then if there exist:

a largest subtree tij starting from the leaves of ti,

and  $B \in AM_{source}$

and a substitution  $\gamma$  such that  $\gamma$  (B) =  $t_{ij}$ .

we define the rewriting of the tree t by:

$t \rightarrow Univ\_seq(Univ\_assign(\gamma(can(B)), \delta(dst(temporary\_am(< temporary \theta >))))$

,  $t / [t_{ij} = \delta(src(temporary_am(< temporary \theta >)))])$

where  $\delta$  is the substitution :  $\delta = \{ < \theta, \text{tmp}\alpha > \}$  where tmp $\alpha$  is a new temporary location.

#### Rule R3

When matching a tree t with an instruction class pattern, if there is a subtree  $t_i$  of t which is not an instance of any access mode pattern, then starting from the leaves of  $t_i$  we look for a subtree  $t_{ij}$  of  $t_i$  which is an instance of an access mode after replacement of a temporary access mode by one of the access modes defined in the rewriting rules declared in the interface and the replacement is done.

Let t be the tree to transform,

suppose there exist  $T \in IC$  and a substitution  $\sigma_{IC}$

such that

$$\sigma_{IC} = \{ < \Delta_i, t_i > | \Delta_i \in Var(T), 1 \le i \le n \}$$

with  $\sigma_{IC}(T) = t$

and suppose there exists  $t_i$  a subtree of t such that  $\langle \Delta_i, t_i \rangle \in \sigma_{IC}$ ,

and if the context of  $\Delta_i$  in T is the position pos

and for each  $A \in AM_{pos}$  there exists no substitution  $\mu$  such that  $\mu(A) = t_i$ .

then when the following conditions hold:

there exists a subtree  $t_{ik}$ , of  $t_i$ , and a substitution  $\tau$ , such that  $\tau(\operatorname{src}(\operatorname{temporary\_am}(\langle \operatorname{temporary} \theta \rangle))) = t_{ik}$  and there exists  $R \in TR$ , and  $M_R \in AM_{source}$  such that  $\operatorname{src}(R) = \operatorname{can}(M_R)$  and there exists a biggest subtree  $t_{ij}$ , starting from the leaves of  $t_i$ , strictly larger than  $t_{ik}$  such that:

- there exists  $M \in AM$  (  $AM = AM_{pos}$  when  $t_{ij} = t_i$  or  $AM = AM_{source}$  when  $t_{ij} < t_i$ )

- and a substitution  $\delta$  such that  $\delta(M) = t_{ij}/[t_{ik} = \tau(M_R)]$

we define the rewriting of the tree t by:

$$t \rightarrow t/[t_{ik} = \tau(M_R)]$$

#### Rule R4

The universal sequence operator has the associativity property:

$$Univ\_seq(U_1,...,U_p,Univ\_seq(V_1,...,V_n)) \rightarrow Univ\_seq(U_1,...,U_p,V_1,...,V_n)$$

#### Rule R5

If neither rule R1, nor rule R2, nor rule R3 can be applied and a subtree of t on the destination position context is not reduced to the canonical form of an access mode in the destination position, then the subtree is matched with access mode patterns in source position. If it succeeds a universal assignment tree is built whose source operand is the selected access mode in its canonical form. The subtree is replaced in t by the temporary access mode in source position applied to a new temporary location. The universal assignment tree and the rewritten tree are rooted by a universal sequence operator.

Let t be the tree to transform,

suppose that there exist  $T \in IC$  and a substitution  $\sigma_{IC}$

such that

$$\sigma_{IC} = \{ \langle \Delta_i, t_i \rangle | \Delta_i \in Var(T), 1 \le i \le n \}$$

with  $\sigma_{IC}(T) = t$

and neither rules R1, R2, R3 can be applied,

then there exists a subtree  $t_i$  of t such that  $<\Delta_i$ ,  $t_i>\in\sigma_{IC}$ , and if the context of  $\Delta$  in T is destination

and if there exist  $A \in AM_{source}$  and a substitution  $\sigma_{AM}$  such that  $\sigma_{AM}(A) = t_i$ ,

we define the rewriting of the tree t by:

$$t \rightarrow Univ\_seq(Univ\_assign(\sigma_{AM}(can(A)), \delta(dst(temporary\_am(< temporary \theta >))))$$

,

$$t/[t_i = \delta(src(temporary_am(< temporary \theta >)))])$$

#### Rule R6

If neither rule R1, nor rule R2, nor rule R3 can be applied and a subtree of  $t_i$  of t on the destination position context is not reduced to the canonical form of an access mode in the destination position, then the subtree  $t_i$  is matched with access mode patterns in source position. If it fails and if it exists an inner subtree which is a temporary access mode, such a tree is rewritten according to the rewriting rules of the interface in the source position context for the subtree  $t_i$ .

Let t be the tree to transform,

suppose that there exist  $T \in IC$  and a substitution  $\sigma_{IC}$

such that

$$\sigma_{IC} = \{ \langle \Delta_i, t_i \rangle | \Delta_i \in Var(T), 1 \le i \le n \}$$

with  $\sigma_{IC}(T) = t$

and neither rules R1, R2, R3 can be applied,

then there exists a subtree  $t_i$  of t such that  $<\Delta_i, t_i>$   $\in$   $\sigma_{IC}$ , and the context of  $\Delta_i$ , in T is destination

there exists a subtree  $t_{ik}$ , of  $t_i$ , and a substitution  $\tau$ , such that  $\tau(src(temporary_am(< temporary_\theta>))) = t_{ik}$

and there exists  $R \in TR$ , and  $M_R \in AM_{source}$  such that  $src(R) = can(M_R)$

and there exists  $M \in AM_{\text{source}}$  and a substitution  $\delta$  such that  $\delta(M) = t_i / [t_{ik} = \tau(M_R)]$

we define the rewriting of the tree t by:

$$t \rightarrow t/[t_{ik} = \tau(M_R)]$$

#### Rule R7

If a subtree  $t_i$  of t in the destination position is an instance of a temporary access mode in source position, and there exists an access mode A of the interface whose source template is the destination template of an access mode B, then  $t_i$  is replaced by the instantiated access mode B in destination position.

Let t be the tree to transform,

suppose that there exist  $T \in IC$  and a substitution  $\sigma_{IC}$

such that  $\sigma_{IC} = \{ \langle \Delta_i, t_i \rangle | \Delta_i \in Var(T), 1 \le i \le n \}$  with  $\sigma_{IC}(T) = t$

then there exists a subtree  $t_i$  of t such that  $<\Delta_i, t_i> \in \sigma_{IC}$ , and the context of  $\Delta_i$  in T, is destination

and a substitution  $\tau$ , such that  $\tau(\text{src}(\text{temporary}_{\text{am}}(<\text{temporary}_{\theta}))) = t$

and there exists  $R \in TR$ , and  $M_R \in AM_{source}$  such that  $R = can(M_R)$  and there exists  $B \in AM_{destination}$  and a substitution  $\delta$  such that  $\delta(B) = \tau(M_R)$

we define the rewriting of the tree t by:

$$\mathbf{t} \to \mathbf{t} / [t_i = \delta(B)]$$

#### Rule R8

If the matching of a tree t with an instruction pattern I fails because a subtree of t which corresponds to a source operand of I does not belong to the right access class and if there exists a rewriting of a temporary access mode which belongs to the right class, then a universal assignment tree is built and, in the tree t, the subtree corresponding to the source operand is replaced by the selected rewriting of the temporary access mode.

Let t be the tree to transform,

suppose there exist  $T \in IC$  and a substitution  $\sigma_{IC}$

such that

$$\sigma_{IC} = \{ < \Delta_i, t_i > | \Delta_i \in Var(T), \text{ and } t_i \in INST(AM), 1 \le i \le n \}$$

with  $\sigma_{IC}(T) = t$ , and  $AM = AM_{source} \cup AM_{destination}$

and I an instruction pattern of the instruction class T which is the closiest to t.

and  $\gamma$  the substitution such that  $\gamma(T) = I$

$\gamma = \{ \langle \Delta_i, a_i \rangle | \Delta_i \in Var(T), \text{ and } a_i \in CA \cup INST(AM) \}$

and there exists  $t_i$  in source position in T such that for all  $A \in a_i$ ,  $(< \Delta_i, a_i >)$  and  $a_i \in CA$ ,  $t_i$  has the following property:  $t_i \notin INST(A)$ . and there exists  $R \in TR$ , and  $R \in a_i$

then we define the rewriting of the tree  $\boldsymbol{t}$  by :

$$t \rightarrow Univ\_seq(Univ\_assign(t_i, dst(\delta(R))))$$

,

$$t/[t_i = src(\delta(R))]$$

where  $\delta$  is the substitution :  $\delta = \{ \langle \theta, \text{tmp}\alpha \rangle \}$  where tmp $\alpha$  is a new temporary location.

#### Rule R9

The goal is to match the tree t by an instruction pattern where a variable A occurs twice (once in source position, once in destination position). The matching of t fails because the subtrees of t corresponding to the two occurrences of A are not identical or they are identical but they do not belong to the right access class, a rewriting must be done. First the subtree of t corresponding to the source operand is saved in a temporary; second, an instance of the instruction pattern is generated using this temporary to instantiate the variable A, and third, a universal assignment tree is created whose destination is the subtree of t corresponding to the destination operand.

Let t be the tree to transform,

suppose there exist  $T \in IC$  and a substitution  $\sigma_{IC}$

such that

$$\sigma_{IC} = \{ \langle \Delta_i, t_i \rangle | \Delta_i \in Var(T), \text{ and } t_i \in INST(AM), 1 \le i \le n \}$$

with  $\sigma_{IC}(T) = t$

and let I be the instruction pattern of the instruction class T which is the closiest to t.

and let  $\gamma$  be the substitution such that  $\gamma(T) = I$

$$\gamma = \{ \langle \Delta_i, a_i \rangle \mid \Delta_i \in Var(T), \text{ and } a_i \in CA \cup INST(AM) \}$$

If there exist  $a_i$  and  $a_i \in CA$ ,  $< \Delta_i$ ,  $a_i > \in \gamma$  and  $< \Delta_j$ ,  $a_j > \in \gamma$ ,  $i \neq j$

such that  $Var(a_i) = Var(a_i)$  (by definition of an access class,  $Var(a_i)$  is reduced to a single variable)

and ( let  $\alpha_1$  and  $\alpha_2$  be the substitutions such that  $t_i = \alpha_1(\operatorname{src}(A))$  and  $t_j = \alpha_2(\operatorname{dst}(A))$ , and  $\alpha_1 = \{ < A, M > \}$ )

if  $\alpha_1 \neq \alpha_2$  or  $(\alpha_1 = \alpha_2 \text{ and for all } P \in a_i, M \notin INST(P))$

a; is a source operand and a; is a destination operand in I, then

we define the rewriting of the tree t by:

$$t \rightarrow Univ\_seq(Univ\_assign(t_i, \delta(dst(temporary\_am())))$$

,  $\delta_2 \circ \delta_1(I)$

,  $Univ\_assign(\delta(src(temporary\_am())), t_i))$

where  $\delta$  is the substitution :  $\delta$  = { < 0, tmp $\alpha$  > } where tmp $\alpha$  is a new temporary location.

and  $\delta_1$  is the substitution

$\delta_1 = \{ \langle Var(a_i), \delta(src(temporary\_am(\langle temporary \theta \rangle))) \rangle, \langle Var(a_j), \delta(dst(temporary\_am(\langle temporary \theta \rangle))) \rangle \}$ and  $\delta_2$  is the substitution

$$\delta_2 = \{ \langle \operatorname{Var}(a_k), t_k \rangle \mid 1 \le k \le n, k \ne j, k \ne i, \langle \Delta_k, t_k \rangle \in \sigma_{IC} \text{ and } a_k \in CA \}$$

#### Rule R10

If the matching of a tree t with an instruction pattern I fails, because a subtree of t which corresponds to a destination operand of I does not belong to the right access class. If there exists a rewriting of a temporary access mode which belongs to the right class, the subtree of t corresponding to the destination operand is replaced by the selected rewriting of the temporary access mode, and a universal assignment tree is built whose destination operand is the previous destination operand of t.

Let t be the tree to transform,

suppose there exist  $T \in IC$  and a substitution  $\sigma_{IC}$

such that

$$\sigma_{IC} = \{ < \Delta_i, t_i > | \Delta_i \in Var(T), \text{ and } t_i \in INST(AM), 1 \le i \le n \}$$

with  $\sigma_{IC}(T) = t$ , and  $AM = AM_{source} \cup AM_{destination}$

and I an instruction pattern of the instruction class T which is the closiest to t.

and  $\gamma$  the substitution such that  $\gamma(T) = I$

$$\gamma = \{ \langle \Delta_i, a_i \rangle | \Delta_i \in Var(T), \text{ and } a_i \in CA \cup INST(AM) \}$$

and there exists  $t_i$  in destination position in T such that for all  $A \in a_i$ ,  $(< \Delta_i, a_i >)$  and  $a_i \in CA$ ,  $t_i$  has the following property:  $t_i \notin INST(A)$ .

and there exists  $R \in TR$ , and  $R \in a_i$

then we define the rewriting of the tree t by:

$$\mathbf{t} \to \text{Univ\_seq}(\mathbf{t} / [\mathbf{t_i} = \text{dst}(\delta(R))]]$$

,  $\text{Univ\_assign}(\text{src}(\delta(R)), \mathbf{t_i}))$

where  $\delta$  is the substitution :  $\delta = \{ < \theta, \text{tmp}\alpha > \}$  where tmp $\alpha$  is a new temporary location.

#### 2.4.3 The code generation algorithm

#### 2.4.3.1 The instruction selection algorithm

Let t be the I.R tree of a modification:

- 1 Apply either rule R1 or rule R2 or rule R3 whenever possible.

- 2 Apply either rule R5 or rule R6 or rule R7 whenever possible.

- 3 Apply rule R9

- 4 Apply rule R8

- 5 Apply rule R10

- 6 Apply rule R4

Every application of a rewriting rule which search for an access mode must have as result the access mode corresponding to the largest subtree starting from the leaves (it leads to locally optimal code).

In practice, when a rewriting rule uses the rewriting rules of the interface, it is necessary to keep the result of all successfull applications of these rules.

#### 2.4.3.2 Binding and register assignment

Locally, for each tree of this sequence using a temporary, the instruction selection process builds a list of allowed access modes for this temporary access mode. For each temporary such information is processed over the whole tree, in order to get the list of the access modes available all over the sequence.

Then according to the available storages, the system first pick for each temporary the storage class related to the cheapest access mode of the preceding set. Second it chooses the name of an available location of this storage class for the temporary.

#### 2.4.4 Example

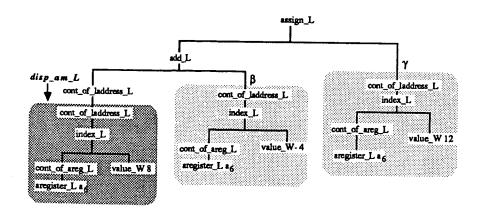

Let us consider in the C language, the I.R. subtree t corresponding to the assignment statement:

$$*J = cpt + *I$$

where I, J are formal parameters of a procedure, declared as pointers on integer; cpt is a local variable of type integer.

A tree which designates a variable in a call can be written by indexing the offset of the variable to the base content of the procedure to which this variable is local. We assume that:

- the address register a6 points to the beginning of the activation record of the current call

- 8 is the offset of I from the base of the procedure

- 12 is the offset of J from the base of the procedure

- - 4 is the offset of cpt from the base of the procedure

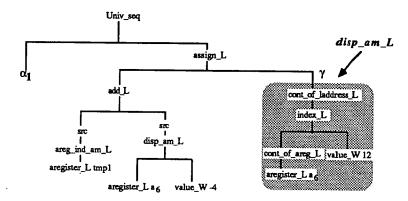

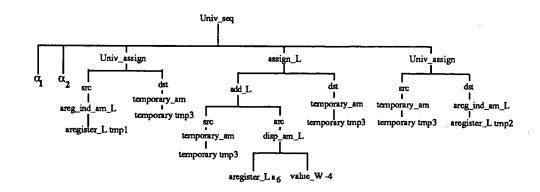

The following figures show successive rewritings. The access modes are designated by squares in dotted lines. The instruction pattern candidate to a matching of the modification of root assign\_L may be

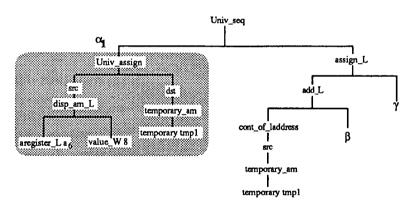

- Step a: The disp\_am access mode in source position is recognized. As its father is not a node of an instruction template, rule R2 is applied using the temporary tmp1 as temporary location. The system generates a universal store tree such that:

- its right child is an access mode temporary\_am in destination position

- its left child is the instantiated access mode disp\_am

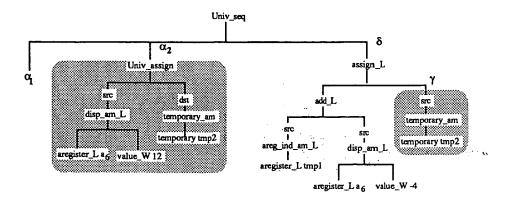

Step b: Using the equivalence declaration of the interface, rule R3 can be applied.

As areg\_am\_L (<aregister\_L tmp1>) is a rewriting of the temporary access mode and as src(areg\_am\_L (<aregister\_L tmp1>)) is the canonical form of cont\_of\_areg\_L(<aregister\_L tmp1>), src(temporary\_am (<temporary tmp1>)) is rewritten into cont\_of\_areg\_L (<aregister\_L tmp1>) in order to get an instance of the areg\_ind\_am\_L access mode.

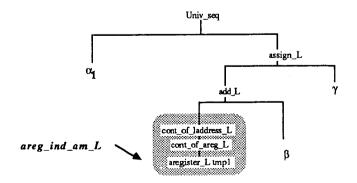

Step c: The rule R1 may be applied because an instance of the address register indirect access mode is recognized in source position. It is replaced by the instantiated canonical form of the access mode in the tree.

Step d: In the same way, the rule R1 may be applied because the tree  $\beta$  is recognized as an instance of the disp\_am access mode in source position.  $\beta$  is replaced by the instantiated canonical form of the disp\_am access mode.

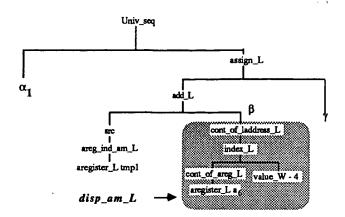

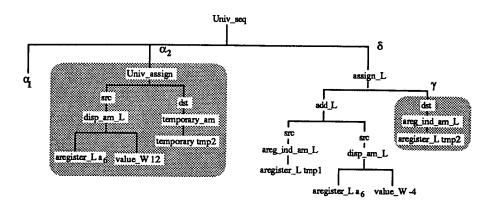

Step e: Now let us consider the  $\gamma$  tree, it is in destination position. But  $\gamma$  is not an instance of an access mode in destination position. Below the root of  $\gamma$ , there is no instance of access mode in source position that leads to a non-blocking situation. It is necessary to use a new strategy, as  $\gamma$  is an instance of the disp\_am access mode in source position, we apply the rule R5.

Step f: The tree γ has a root labelled by src in a destination position. It is an inconsistency that we need to delete. It is the purpose of the rule R7. As the temporary access mode is equivalent to the aregister access mode via the interface, let us replace the temporary access mode by the full template definition of the aregister access mode because it corresponds to the template of the areg\_ind\_am access mode in destination position. It comes.

Step g: As rules R1, R2, R3, R5, R6, R7 are no more applicable,  $\delta$  is compared with the instruction template where a variable occurs twice (once in source position, once in destination position). The matching of  $\delta$  fails because the subtrees V and  $\gamma$  are not identical. The rule R9 is applied.

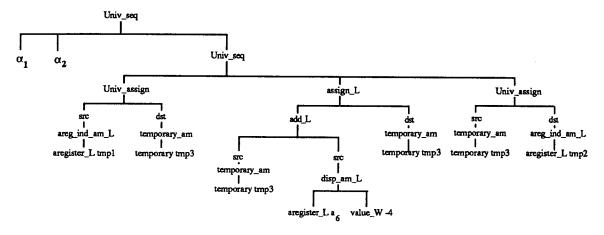

The rule R4 describing the associativity of the Univ\_seq operator can be applied twice. The sequence becomes:

Now, each subtree of the sequence is an instance of instructions templates.

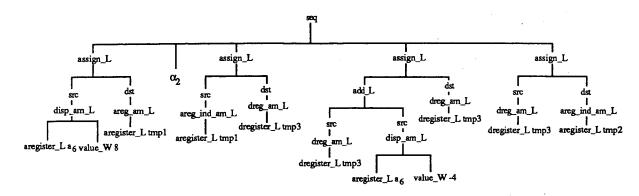

It is now necessary to bind each temporary with an actual resource. In the sequence got from the instruction selection step, all temporaries have been already bound to storage classes. That is the case of tmp<sub>1</sub> bound to an address register because step b used the equivalence rule between the temporary access mode and the address access mode. In the same way tmp<sub>2</sub> is bound to an address register (by step f). The data register access mode is the only allowed rewriting of the temporary access mode on tmp<sub>3</sub> according to the addition template. Thus tmp<sub>3</sub> is bound to a data register.

Finally the universal operators are rewritten in order to get instances of instructions templates. The result of the binding step is:

The register assignment step can now take place. Each temporary name  $tmp_i$  is replaced by a name of an actual resource (a<sub>0</sub>, is assigned to  $tmp_1$ , a<sub>1</sub> to  $tmp_2$ , d<sub>0</sub> to  $tmp_3$ ). The final sequence is:

As each instruction template corresponds exactly to an assembly instruction, the code emission can be performed by a simple left to right tree-traversal producing the following sequence of assembly code:

MOVE.L 8(a<sub>6</sub>), a<sub>0</sub>

MOVE.L 12(a<sub>6</sub>), a<sub>1</sub>

MOVE.L (a<sub>0</sub>), d<sub>0</sub>

ADD.L -4(a<sub>6</sub>), d<sub>0</sub>

MOVE.L d<sub>0</sub>, (a<sub>1</sub>)

### 3 Correctness of the code-generator produced

#### 3.1 Introduction.

We intend to prove that the rewriting of a term A into a term B preserves the semantics of the term A.

A term of the I.R is a modification corresponding to an instruction of the source program. Let us recall briefly from the theory developed by M.C Gaudel in her thesis that the semantics of a modification can be written by means of a primitive modification (substitution) applied to a state S. A state is a set of formulas t = t' (where t and t' are ground terms of the abstract data type).

Let m be a term. We note

$$S' = appl(m, S)$$

the resulting state when applying the modification denoted by m to the state S.

The action of a primitive modification subst  $(f(\lambda), \mu)$  on a state S is new state S' where the formulas of S corresponding to the old value of f at the point  $\lambda$  will be replaced by formulas taking into account the new value  $\mu$ . The new state S' is the smallest consistent state built from the formulas of S and the substitution.

Thus the definition of the assign operation is

assign

$$(v, i) = subst$$

(value\_of(v), i)

As the assignment instruction template which is dealt by the generator process is of the form assign (scr(can1), dst(can2)), the assign modification has the following definition:

appl (assign (scr(can1), dst(can2)), S) = appl (subst (contents (dst(can2), src(can1)), S)

or

```

assign (scr(can1), dst(can2)) = subst (contents (dst(can2)), src(can1))

```

A convenient abbreviation used in the sequel will be:

```

Sem [assign (scr(can1), dst(can2))] = { contents (dst(can2)) = src(can1)}

```

The compiler writer has to specify this semantic function in the axioms in a way like instruction\_context(assign (src(can1), dst(can2))) is true

```

\Rightarrow CONTENTS [ dst(can2)] = src(can1)

```

The compiler writer must define the axioms describing the semantics of the modification "modif\_name" appearing in the instruction. For that purpose, he uses a built-in function CONTENTS. When applied to a storage designated by dst(X), this function returns the term denoting the dereference operation applied to this storage.

For instance, for the temporary\_am access mode, we define:

```

CONTENTS [ dst(temporary_am(<temporary temp>))] = contents_of(<temporary temp>)

```

The axiomatic definition of the modification modif\_name must be written as follows:

instruction context(modif name (op (src(can1), src(can2), dst(can3))) is true

```

⇒ CONTENTS [dst(can3)] = SEM_VALUE [modif_name, op (src(can1), src(can2))] where SEM_VALUE is a user defined semantic function.

```

It is now necessary to enrich our definition for a sequence of modifications. The semantics of a sequence is defined as a composition of applications appl

$$appl (seq(m1, m2), S) == appl (m2, appl (m1, S))$$

We shall apply such a composition under a simplification hypothesis. As each rewriting generates always a new name for a temporary, the temporaries generated have a local scope. As a consequence, the states we are interested in are the initial and the final states. The intermediate states generated by the composition of "appl" inside a sequence cannot generate inconsistency with the initial state. We shall use the notation:

$$Sem [seq(m1, m2)] = Sem [m1] \oplus Sem [m2]$$

where  $\oplus$  is the adjonction of formulas: i.e the smallest consistent state built from the composition of the formulas of S, Sem (m1) and Sem (m2)

As the code-generator works by successive rewritings of a term into another term, the correctness of the codegenerator process can be achieved by proving each elementary rewriting.

#### 3.2 Correctness proof of the rewriting steps.

In order to prove the correctness of the rewriting step, it would be necessary to prove that each rewriting rule preserves the semantics. The full proof of all rewriting rules is not given here. Most of them are alike:

- the rule R1 replaces an instance of an access mode template by its instantiated canonical form. Such a

transformation is the straightforward application of the axiomatic definition of the canonical form of the

access mode.

- the rules R3, R6, R7 are compositions of the axiomatic definitions of the access modes and of the equivalence rules of the interface. Their correctness proof is also straightforward.

- the rule R2 consists in the store of an instance of an access mode in a temporary followed by the replacement of this instance in the input term by the access to a temporary.

The correctness proof of the rules R5 and R8 are quite alike.

- the rule **R9** deals with terms whose leaves are in the canonical form but do not satisfy the binding of the variables according to the instruction template.

We choose to present the scheme of the correctness proof for the rules R2 and R9.

#### 3.2.1 Correctness proof of the rule R2.

The I.R term I to which the rule R2 is applied is of the form:

which is matched by the instruction class:

$$modif_name(src(X), dst(Y)).$$

In the term I, let us consider an inner subterm of root h which is an instance of an access mode can1. It is convenient to denote it by src(can1) without loss of generality. In the same way, the subtree of root d will be denoted by dst(can2) in the sequel. Thus a convenient abbreviation of the term I could be:

The semantics related to I is described by the state:

$$SI = \{ Sem [ modif_name(f(g(src(can1))), dst(can2))] \}$$

The initial term I is rewritten into the term F:

which will be abbreviated into Univ\_seq (A1, A2). The semantics related to F is:

$$S_F = \{ Sem [ Univ\_seq (A_1, A_2)] \} = \{ Sem [A_1] \oplus Sem [A_2] \}$$

```

Sem[A_2] = Sem [modif_name(f(g(src(temporary_am(<temporary temp1>)))), dst(can2))]

According to the value of the predicate "instruction_context", the condition of the last axiom in §2.3.2 is true,

thus we get the following formula:

contents_of (<temporary temp1>) = src(can1)

and the state:

S_F = \{ contents\_of (< temporary temp1>) = src(can1) \}

⊕ Sem [A2] }

Sem[A_2] = Sem[modif_name(f(g(src(temporary_am(< temporary temp1>)))), dst(can2))]

As the predicate "source_operand_context" of the access mode temporary_am is true, we get:

src(temporary_am(temporary temp1>)) = contents_of (<temporary temp1>))

and Sem [A2] becomes:

Sem[A_2] = Sem [modif_name(f(g(contents_of(temporary temp1>)))), dst(can2))]

and the state:

S_F = \{ contents\_of (< temporary temp1>) = src(can1) \}

⊕ Sem [modif_name (f(g(contents_of (<temporary temp1>)))), dst(can2))] }

Taking into account the first formula of the state SF, the second formula becomes:

Sem [modif_name(f(g(src(can1)))), dst(can2))]

and the state

S_F = \{ contents\_of (< temporary temp1>) = src(can1) \}

⊕ Sem [modif_name(f(g(src(can1)))), dst(can2))] }

Let us compare the states S<sub>I</sub> and S<sub>F</sub>, we can notice that S<sub>F</sub> is an enrichment of the state S<sub>I</sub> by the formula:

contents_of (<temporary temp1>) = src(can 1)

The adjunction of the formula contents_of (<temporary temp1>) = src(can1)

cannot lead to remove an inconsistent formula from the state SI because we are sure that there is no formula

containing temp1 in S<sub>I</sub>. The reason is that we use a new name each time we need to store an intermediate result in

a temporary location.

3.2.2

Correctness proof of the rule R9.

The rule R9 is often applied on terms denoting arithmetic or logical operations. The instruction template to

be matched is of the following form:

modif_name (op (src(X), src(Y)), dst(X))

and the I.R term is of the form:

modif_name (op (src(can1), src(can2), dst(can3))

```

```

The semantics related to the I.R term is the following state

SI = { Sem [ modif_name(op( src(can1), src(can2)), dst(can3))] }

As the conditional part of the axiom above is true,

```

**SI** = { CONTENTS [ dst(can3)] = SEM\_VALUE [modif\_name, op (src(can1), src(can2)) ] }

```

The term I is rewritten into the term F:

Univ seq (Univ_assign ( src (can1), dst(temporary_am(<temporary temp1>))

, modif_name (op( src(temporary_am(<temporary temp1>)), src(can2))

, dst (temporary_am(<temporary temp1>)))

, Univ_assign ( src(temporary_am(<temporary temp1>))

, dst(can3)))}

which will be abbreviated into Univ_seq (A1, A2, A3). The semantics related to F is described by the state:

S_F = \{ Sem [Univ\_seq (A_1, A_2, A_3)] \} = \{ Sem [A_1] \oplus Sem [A_2] \oplus Sem [A_3] \}

Sem [A_1] = Sem [Univ\_assign (src(can1), dst(temporary\_am(<temporary temp1>))]

Let us apply the axiomatic definition of the universal operator "Univ_assign" to Sem [A1], we get the following

formula:

contents of (<temporary temp1>) = src(can1)

S_F = \{ contents_of (< temporary temp1>) = src(can1) \}

\oplus Sem [A<sub>2</sub>] \oplus Sem [A<sub>3</sub>] }

Sem [A_2] = Sem [modif_name (op(src(temporary_am(<temporary temp1>)), src(can2))

, dst (temporary_am(<temporary temp1>)))]

According to the canonical definition of temporary_am in source position, we get:

src(temporary_am (<temporary temp1>)) = contents_of (<temporary temp1>)

Thus

Sem [A_2] = Sem [modif_name (op(contents_of(<temporary temp1>), src(can2))]

, dst (temporary_am(<temporary temp1>)))]

Let us sum up:

S_F = \{ contents\_of (< temporary temp1>) = src(can1) \}

⊕ Sem [modif_name(op(contents_of (<temporary temp1>), src(can2))

, dst (temporary_am(<temporary temp1>)))]

⊕ Sem [A<sub>3</sub>] }

Taking into account the first formula of SF for the second formula, we get:

S_F = \{ contents\_of (< temporary temp1>) = src(can1) \}

⊕ Sem [modif_name (op(src(can1), src(can2))

, dst (temporary_am(<temporary temp1>)))]

⊕ Sem [A<sub>3</sub>]}

The second formula of the state SF computes the semantics of the modification modif_name. According to its

related axiom SF becomes:

S_F = \{ contents\_of (< temporary temp1>) = src(can1) \}

⊕ CONTENTS [dst (temporary_am(<temporary temp1>))] =

SEM_VALUE [modif_name, op (src(can1), src(can2)) ]

⊕ Sem [A<sub>3</sub>] }

```

using the definition of the function CONTENTS applied to dst (temporary\_am(<temporary temp1>)), we get:

```

S_F = \{ contents\_of (< temporary temp1>) = src(can1)

\oplus contents\_of (< temporary temp1>) = SEM_VALUE [modif_name, op (src(can1), src(can2))]

\oplus Sem [A_3] \}

```

The first formula becomes inconsistent since contents\_of (<temporary temp1>) is redefined. So the state Sp becomes:

```

S_F = \{ contents\_of (< temporary temp1>) = SEM_VALUE [modif\_name, op (src(can1), src(can2)) \}

\oplus Sem [A_3] \}

```

Sem [A<sub>3</sub>] = Sem [Univ\_assign( src(temporary\_am(<temporary temp1>)), dst(can3)))]

As the following axiom for Univ\_assign exists:

instruction\_context(Univ\_assign(src(temporary\_am <temporary temp>), dst(can))) is true

```

⇒ CONTENTS [ dst(can)] = src(temporary_am <temporary temp>)

Thus Sem [A<sub>3</sub>] = { CONTENTS [ dst(can3)] = src(temporary_am <temporary temp>) }

```

```

Let us apply the canonical definition of src(temporary_am ...)

```

```

Sem [A<sub>3</sub>] = { CONTENTS [ dst(can3)] = contents_of (<temporary temp>) }

```

Taking into account the first formula of SF for the second formula, we get:

We can notice that the state  $S_{\mathbf{I}}$  is an enrichment of the state  $S_{\mathbf{F}}$  by the formula :

```

contents_of (<temporary temp1>) = SEM_VALUE [modif_name, op (src(can1), src(can2))]

```

#### 3.2.3 Comments

Such correctness proof frameworks can be developed for each rewriting rule. They can be developed once and for all because they are independent of the target machine.

As the two first steps of the compiling process can be proved by techniques like [Mad 83], the correctness proof of the whole compiling process until the code selection process may be achieved.

#### Conclusion

We have provided ways to specify target machines in the framework of a compiler rewriting system using abstract data type specifications. The kernel of the code-generator is a set of rewriting rules that preserve the semantics of the I.R. Such as proof can be done by means of axioms on universal operators of the target abstract data type and thus it is machine independent. The termination of the code selection algoritm is straightforward because the replacement of a temporary access mode is only done when it allows to match an access mode that strictly contains the rewriting of the temporary access mode. Thus the depth of the I.R. term decreases until there is a blocking situation or until the level of the operand of the instruction is reached.

Generally speaking, the code selection algorithm is not confluent. The more global optimal code may be got by computing the cumulated costs for each solution.

Prolog has allowed us to develop quickly the experimental system PAGODE in order to achieve the production of code-generators from a target machine specification based on term templates. The code produced is locally optimal.

A work currently in progress aims at restricting the large number of temporaries before the binding step takes place. For that purpose, we use a concept of alive temporaries in the sequence. More generally, it is necessary now to integrate optimizing tasks in this framework.

#### **Bibliography**

- [AG 85] Aho A.V, Ganapathi M. "Efficient tree pattern matching: an aid to code generation" Conference Record of the Twelth Annual ACM Symposium on Principles of Programming Languages, pp 334-340, January 1985.

- [BGM 87] Bidoit M., Gaudel M.C., Mauboussin A. "How to make algebraic specifications more understandable? an experiment with the PLUSS specificaction language", Rapport LRI n° 343 Université d'Orsay, France 1987.

- [Cat 77] Cattell R. G. G. "A Survey and Critique of some Models of Code Generation" Carnegie-Mellon University, Computer Sciences Department, Technical Report no 78-115, 1977.