# BDl, A Language of Distributed Reactive Objects

Jean-Pierre Talpin, Albert Benveniste, Benoit Caillaud, Claude Jard, Zakaria Bouziane, Hubert Canon

#### ▶ To cite this version:

Jean-Pierre Talpin, Albert Benveniste, Benoit Caillaud, Claude Jard, Zakaria Bouziane, et al.. BDl, A Language of Distributed Reactive Objects. [Research Report] RR-3353, INRIA. 1998. inria-00073336

# HAL Id: inria-00073336 https://inria.hal.science/inria-00073336

Submitted on 24 May 2006

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

# BDL, a language of distributed reactive objects

Jean-Pierre Talpin, Albert Benveniste, Benoit Caillaud, Claude Jard, Zakaria Bouziane, Hubert Canon.

## N 3353

Janvier 1998

\_\_\_\_\_ THÈME 1 \_\_\_\_\_

BDL, a language of distributed reactive objects\*†

Jean-Pierre Talpin<sup>‡</sup>, Albert Benveniste<sup>‡</sup>, Benoit Caillaud<sup>‡</sup>, Claude Jard<sup>§</sup>, Zakaria Bouziane<sup>‡</sup>, Hubert Canon<sup>¶</sup>.

Thème 1 — Réseaux et systèmes Projets EPATR & PAMPA

Rapport de recherche  $\,$ n<br/>3353 — Janvier 1998 — 38 pages

Unité de recherche INRIA Rennes IRISA, Campus universitaire de Beaulieu, 35042 RENNES Cedex (France) Téléphone: 02 99 84 71 00 - International: +33 2 99 84 71 00 Télécopie: 02 99 84 71 71 - International: +33 2 99 84 71 71

Abstract: We introduce the definition of a language of distributed reactive objects, a Behaviour Description Language (BDL), as a unified medium for specifying, verifying, compiling and validating object-oriented, distributed reactive systems. One of the novelties in BDL is its seamless integration into the Unified Modeling Language approach (UML). BDL supports a description of objects interaction which respects both the functional architecture of system designs and the declarative style of diagram descriptions. This support is implemented by means of a partial-order theoretical framework. This framework allows to specify both the causality and the control models of object interactions independently of any hypothesis on the actual configuration of the system. Given the description of such a configuration, the use of BDL offers new perspectives for a flexible verification of systems by modeling them as an asynchronous network of synchronous components. It allows an optimized code generation by using compilation techniques developed for synchronous languages. It permits an accurate validation and test of applications by supporting the manipulation of both causal and control dependencies. BDL aims at maximizing the re-usability of high-level specifications while minimizing programming effort and test-case based validation of distributed systems.

$(R\acute{e}sum\acute{e}:tsvp)$

<sup>\*</sup> Funded by the French Ministry for Research, program Arctica.

<sup>&</sup>lt;sup>†</sup> Funded by Alcatel, project Reutel-2000.

<sup>&</sup>lt;sup>‡</sup> Institut National de Recherche en Informatique et Automatique (INRIA)

<sup>§</sup> Centre National pour la Recherche Scientifique (CNRS)

<sup>¶</sup> Délégation Générale pour l'Armement (DGA), FORMA project

# BDL, un langage à objets réactifs distribués

Nous proposons BDL (de l'anglais Behaviour Description Language) comme un moyen de spécifier, de vérifier, de compiler et de valider les applications distribuées temps-réel. L'un des traits les plus marquants de BDL est qu'il s'intègre facilement dans une approche de développement orientéobjet à la UML(Unified Modeling Language). Le langage BDL supporte tout à la fois une description de l'interaction entre objets qui respecte l'architecture fonctionnelle d'un système (telle qu'elle peut-être décrite en UML) et un style déclaratif proche de celui des diagrammes décrivant les scénarios d'utilisation et de collaboration à la UML. Ces traits sont mis en œuvre au moyen de la notion d'ordre partiel, qui permet de décrire les causalités et le contrôle sans qu'il soit nécéssaire de faire aucune hypothèse sur la configuration physique du système. Etant donnée une telle configuration, l'utilisation de BDL offre de nouvelles perspectives pour la vérification de systèmes (compris comme un ensemble asynchrone de sous-systèmes synchrones). BDL permet de générer des programmes qui mettent en œuvre de manière efficace le parallélisme d'une spécification (en faisant appel à des techniques de compilation utilisées par les langages de programmation synchrone). BDL permet une validation minutieuse des applications puisqu'il en décrit et les causalités et le contrôle. L'objectif de BDL est de maximiser la réutilisation de spécifications de hautniveau dans le développement d'applications distribuées et de minimiser les efforts de programmation et de validation nécéssaires à leur réalisation.

# Contents

| 1 | Introduction                                                                                                                 | 5              |  |  |

|---|------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|

| 2 | Presentation of BDL 2.1 Behavioural Layer                                                                                    | 8<br>10        |  |  |

| 3 | Semantics of BDL  3.1 Semantic Domains 3.2 Semantic Operators 3.3 Discussion 3.4 Endochrony and Isochrony 3.5 Meaning of BDL | 14<br>18<br>19 |  |  |

| 4 | Well-Typed Bdl expressions                                                                                                   |                |  |  |

| 5 | Using BdL                                                                                                                    |                |  |  |

| 6 | Contributions                                                                                                                |                |  |  |

| 7 | Perspectives                                                                                                                 | 29             |  |  |

| 8 | Conclusion                                                                                                                   | 31             |  |  |

# 1 Introduction

The development of distributed software systems is a highly complex process. In order to manage this complexity various software engineering methods have been developed, ranging from requirements and design specification techniques to verification, validation, testing and code generation tools. We focus on those methods which have a formal foundation. They are expected to be based on formally defined languages and to rely on well-defined transformations. At present, the emerging object-oriented distributed computing technology raises new questions about formal engineering development.

At the programming level, the first point to note is that there is a need to extend the interface description languages (like IDL for CORBA) with behavioural properties. Interface description languages describe the features of an object in the computational view without presenting too much of its interior. They should define all visible aspects, namely the applicable functions and the (abstract) behaviour that is connected to the functions. This latter aspect is not yet formally defined [15] (even in the TINA-ODL proposal where there is just a placeholder for the behaviour descriptions and no syntax).

In the present state of knowledge, this prevent most formal validation methods from being used. We thus argue for extending interfaces with formal specifications of behaviours: our Behavioural Description Language is called BDL. Although the behavioural aspects of interfaces are located to the architectural design phase of the development of object based distributed applications, this phase in the development process must be seen in the framework of a coherent methodology and life-cycle model [14].

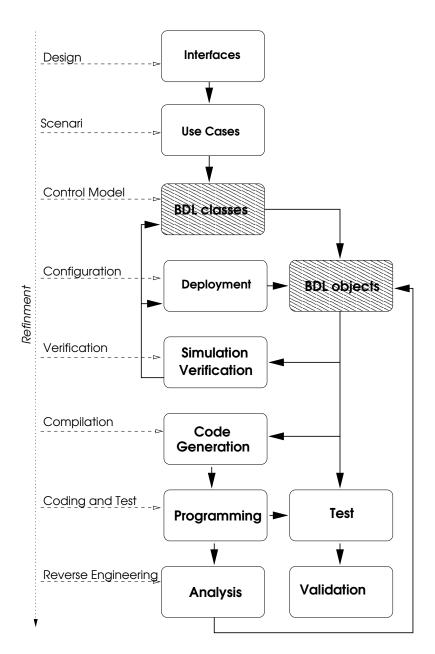

The emerging object-oriented methodologies are put into the Unified Modeling Language (UML), becoming a de facto standard [17]. This leads to our second point about the need to integrate BDL into UML to continuously accompany the development from specification phases to implementations (figure 1). Since we focus on dynamical aspects, we start from the idea that the most abstract level of behaviours can be described using scenari (like Message Sequence Charts). We will enrich these scenarios by a formal semantics and facilities to describe complex programming controls using variables and conditions.

Figure 1: BDL in its environment

Our paper introduces the definition of BDL as a unified medium for specifying, verifying, compiling and validating distributed, object-oriented, reactive systems. One of the novelties in BDL is its seamless integration into the UML approach. BDL supports a description of object components interaction which respects both the functional architecture of system designs and the declarative style of diagram descriptions. This support is implemented by means of a partial-order theoretical framework. Together with a logical notion of time and a notion of reaction, this framework allows to specify both the causality and the control models of object interactions independently of any hypothesis on the actual configuration of the system.

The focus of our approach is the partial orderings of method invocations in an application consisting of distributed reactive objects. In this article, we do not consider the dynamic creation of objects nor non-functional system requirements (such as *deadlines* or other temporal requirements). We focus instead on establishing a formal framework in which both verification and optimization of large-scaled, object-oriented, distributed applications are feasible by using existing tools.

## 2 Presentation of BDL

In order to fulfill the requirements of supporting both a description of the functional architecture of a system and a declarative specification of the interaction between its components, the definition of BDL shall integrate the features of an object-oriented language for structuring the specification of both the causality and the control models of object components. The syntax of BDL is composed of two layers. An object layer describes the structure of a system in a way akin to an UML design. An action layer describes the interaction of each object component with its environment. The definition of BDL classes, arrays and objects allows the reuse of action specifications from the design of the system functional architecture into that of its actual deployment (dimension and distribution) in order to match the configuration of a target system.

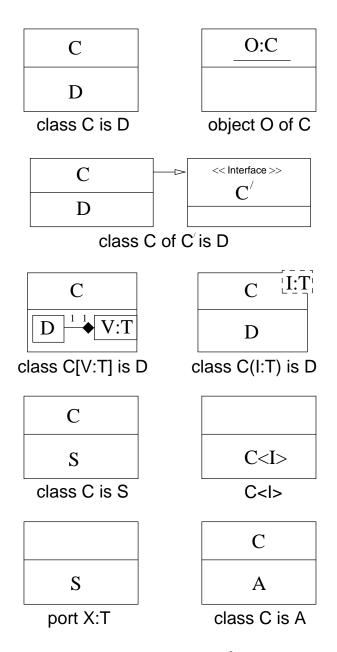

Figure 2: Formal syntax of BDL classes

As in UML, a set of identifiers I is assumed to name classes C, objects O, types T, ports X, symbolic constants V. Compound identifiers consisting of class names C, object names O, array references C[V], prepended to identifiers I are assumed as well. The architectural and declarative layers of the formal syntax of BDL is defined in the figure 2 together with its UML graphical representation, figure 3. The description of a system consists of structures S: classes and objects. A class C consists of a declaration D possibly restricted to an interface of type C', or parameterized by a template identifier I of type T or indexed by an identifier I of type T. An object O is an element of a class C. A declaration D is either the definition of a component S, a bound class  $C\langle I\rangle$  of a template class C with the parameter I, a port X receiving messages of type T or an action A. Both notions of attribute and method in UML correspond to the notion of port in BDL.

Figure 3: UML notation for BDL

### 2.1 Behavioural Layer

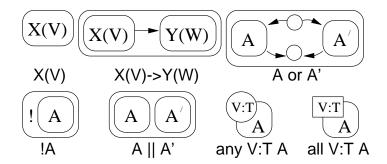

An action A is either a valuation X(V) (i.e.  $\ll$ value V is present at port  $X\gg$ ), the causality specification  $\ll X(V) \to Y(W)\gg$  (i.e.  $\ll X(V)$  is the cause of  $Y(W)\gg$ ) the disjunction  $\ll A$  or  $A'\gg$  of actions (non-deterministic choice), the activation  $\ll!A\gg$  of an action (i.e.  $\ll$ of course  $A\gg$ ), the synchronous composition  $\ll A \parallel A'\gg$  of actions. Enumerated composition and disjunction are written all V:T A and any V:T A.

$$\begin{array}{lll} A ::= & \text{action} \\ & \mid X(V) & \text{valuation} \\ & \mid X(V) \rightarrow Y(W) & \text{causality} \\ & \mid !A & \text{activation} \\ & \mid A \text{ or } A' & \text{disjunction} \\ & \mid A \mid A' & \text{composition} \\ & \mid \text{any } V \colon T \mid A & \text{disjunction} \\ & \mid \text{all } V \colon T \mid A & \text{composition} \end{array}$$

Figure 4: BDL actions A

Figure 5: Graphical syntax for BDL actions A

## 3 Semantics of BDL

The meaning of a BDL program is defined thanks to a true-concurrency semantics in which families of directed labeled graphs describe the causal dependencies (pre-order relations) between events for each possible behaviour of the program (section 3.1). There are three kinds of vertices: association of values to ports, activations/terminations and value passing through pins. Composition operators (section 3.2) on families of directed graphs are then introduced to reflect iteration and synchronous/asynchronous parallel composition of BDL terms: Graph concatenation (via pins) corresponds to repetitive activations of objects (iteration). If objects are interpreted as sets of constraints, the synchronous composition of two objects is the conjunction of the corresponding sets of constraints. Asynchronous composition is a weaker parallel composition in which it is not possible to test for the absence of port occurrence. It reflects asynchronous communication in a declarative setting. Finally, a discussion on endochrony (section 3.4) provides some intuitive insight on the design of BDL.

#### 3.1 Semantic Domains

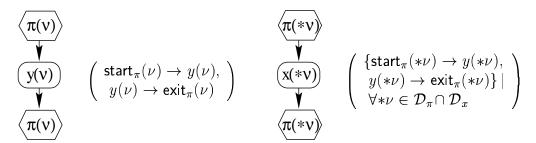

We are given a finite set of names x denoting ports as defined in the section 2. In addition, we consider a finite set of pins  $\pi$  with values in non-empty domains (written  $\mathcal{D}_{\pi}$ ). Pins  $\pi$  will be used to model «state-transitions» and carry values from a «reaction» to another. Pins are denoted by the graphical notations of the figure 6 (minimal and maximal pins  $\mathsf{start}_{\pi}$  and  $\mathsf{exit}_{\pi}$  holding given values v or arbitrary values, written v.

Figure 6: Pins

**Object** An object O is represented by a quadruple  $(\Sigma, \Pi, \Gamma, \gamma_0)$  where  $\Sigma$  denotes its ports x,  $\Pi$  its pins  $\pi$ ,  $\Gamma$  a family of well-formed labeled directed graphs  $\gamma$  and  $\gamma_0$  an initial graph which only contains pins of the form  $\mathsf{exit}_{\pi}(v)$  with  $\pi \in \Pi$  and  $v \in \mathcal{D}_{\pi}$ .

**Family of Graphs** A term  $\gamma \in \Gamma$  is a directed, possibly cyclic, graph, with vertices taken in some infinite ground set of events and labels of one of the forms: a pair x(v) of (port, value) such that  $x \in \Sigma$  and  $v \in \mathcal{D}_x$ , or a sorted pair  $\mathsf{start}_{\pi}(v)$  or  $\mathsf{exit}_{\pi}(v)$  of (sort, pin, value) where  $\pi \in \Pi$  is a pin and  $v \in \mathcal{D}_{\pi}$ .

**Extremal vertices** For each  $\gamma \in \Gamma$ , the set of pins occurring in  $\gamma$  is denoted  $\Pi_{\gamma} = \{\pi \mid \exists v \in \mathcal{D}_{\pi} \text{ s.t. start}_{\pi}(v) \in \gamma \text{ or exit}_{\pi}(v) \in \gamma \}$  By definition,  $\Pi_{\gamma} \subseteq \Pi$ . Vertices that are associated with pins are denoted by  $\mathsf{start}_{\Gamma} = \{\mathsf{start}_{\pi}(v) \mid \exists \gamma \in \Gamma \text{ s.t. } \pi \in \Pi_{\gamma} \}$  and  $\mathsf{exit}_{\Gamma} = \{\mathsf{exit}_{\pi}(v) \mid \exists \gamma \in \Gamma \text{ s.t. } \pi \in \Pi_{\gamma} \}$ .

Well-formed graphs A labeled directed graph is well-formed (e.g. figures 6 and 7) if and only if four conditions are satisfied:

- 1. For all  $x \in \Sigma$ ,  $\gamma$  contains at most one vertex of the form x(v) s.t.  $v \in \mathcal{D}_x$ .

- 2. For all  $\pi \in \Pi$ ,  $\gamma$  contains at most one  $\mathsf{start}_{\pi}(v)$  (resp.  $\mathsf{exit}_{\pi}(v)$ ) s.t.  $v \in \mathcal{D}_{\pi}$ .

- 3. Minimal elements of  $\gamma$  are of the form  $\mathsf{start}_{\pi}(v)$  s.t.  $\pi \in \Pi$  and  $v \in \mathcal{D}_{\pi}$ .

- 4. Maximal elements of  $\gamma$  are of the form  $\mathsf{exit}_{\pi}(v)$  s.t.  $\pi \in \Pi$  and  $v \in \mathcal{D}_{\pi}$ .

Silent and active graphs We assume that every family  $\Gamma$  contains a family of silent graphs  $\tau_{\Gamma} = \{ \vee_{v \in \mathcal{D}_{\pi}} \{ \text{start}_{\pi}(v) \to \text{exit}_{\pi}(v) \} \mid \pi \in \Pi \}$ . This models the fact that  $\Gamma$  may do nothing within a considered reaction. This guarantees a stuttering robustness property [13]. We write  $!\Gamma = \Gamma \setminus \tau_{\Gamma}$  for the family of active graphs of  $\Gamma$ .

**Graphical notations** An extension of the graphical syntax of figure 4 will be useful to support our discussion on the mathematical semantics of BDL. In the figure 7, the formula on the right defines the family obtained from the graph on the left. It is a set of well-formed graphs with universal quantification of variables \*v and \*w.

Figure 7: Graph with quantifications

### 3.2 Semantic Operators

**Concatenation** Consider two objects with identical  $\Sigma$  and  $\Pi$  and respective graph families  $\Gamma$  and  $\Gamma'$ . Pick  $\gamma \in \Gamma$  and  $\gamma' \in \Gamma'$ .

- Graphs  $\gamma$  and  $\gamma'$  are said to be *concatenables* (denoted  $\gamma \odot \gamma'$ ) if and only if the following condition is satisfied:  $(1) \forall \pi \in \Pi$ ,  $\mathsf{exit}_{\pi}(v) \in \max(\gamma) \land \mathsf{start}_{\pi}(v') \in \min(\gamma') \Rightarrow v = v'$ .

- If condition (1) is satisfied, then the concatenation  $\gamma_{\circ}\gamma'$  is obtained by

- 1. Identifying  $\operatorname{exit}_{\pi}(v) \in \max(\gamma)$  and  $\operatorname{start}_{\pi}(v) \in \min(\gamma')$

- 2. Taking the disjoint union of  $\gamma$  and  $\gamma'$

- 3. Retaining the pins  $exit_{\pi}(v)$  and  $start_{\pi}(v)$  which remain extremal after step 3, and discarding the other ones.

- 4. Whenever a pin is discarded, edges are inserted so that the transitive closure of the graph, restricted to pins that are not discarded is unchanged.

- The family  $\Gamma_{\circ}\Gamma'$  of graphs is composed of those  $\gamma_{\circ}\gamma'$  s.t.  $\gamma$  and  $\gamma'$  are concatenables:  $\Gamma_{\circ}\Gamma' = \{\gamma_{\circ}\gamma' \mid \gamma \in \Gamma, \gamma' \in \Gamma', \gamma \odot \gamma'\}$ .

In this way we define:  $\mathcal{G} = \gamma_{0} \circ (\Gamma)^{\omega}$ , where superscript (.) $^{\omega}$  denotes (infinite) countable concatenation, and this defines the semantics of an object. Note that the concatenation  $\Gamma \circ \Gamma'$  of families of graphs do not need a graphical notation, as the semantics of an object is given by  $\mathcal{G}$ .

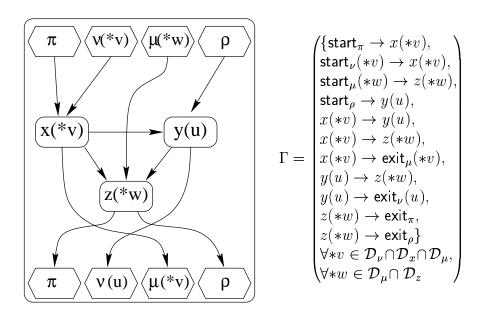

**Example** Figure 8 depicts the concatenation of a family of graphs  $\Gamma$  (that of figure 7) with itself. The diagram on the left in the figure 8 shows the maximal and minimal vertices of  $\Gamma$ . Their concatenation is shown on the diagram in the middle where shared pins  $\pi$ ,  $\rho$ ,  $\mu$  and  $\nu$  are superimposed in the grey box. In the diagram on the right, they are erased and transitive edges inserted.

Figure 8: Graph concatenation

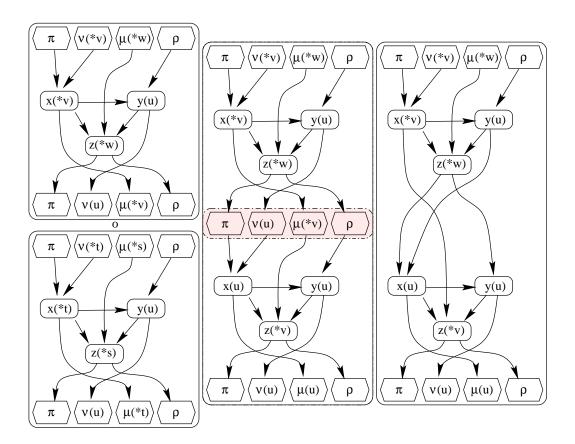

Synchronous composition Consider again two objects  $(\Sigma, \Pi, \Gamma, \gamma_0)$  and  $(\Sigma', \Pi', \Gamma', \gamma'_0)$ . Two graphs  $\gamma \in \Gamma$  and  $\gamma' \in \Gamma'$  are said synchronously composable (denoted  $\gamma \bowtie \gamma'$ ) if and only if any vertex x(v),  $\operatorname{start}_{\pi}(v)$  or  $\operatorname{exit}_{\pi}(v)$ , which satisfies  $(2): x \in \Sigma \cap \Sigma'$ , or  $\pi \in \Pi \cap \Pi'$  respectively, occurs in  $\gamma$  if and only if it occurs in  $\gamma'$ . If the condition (2) is satisfied, then the synchronous composition  $\gamma \parallel \gamma'$  is defined as the union of the graphs  $\gamma$  and  $\gamma'$  (where identical vertices are superimposed). The family  $\Gamma \parallel \Gamma'$  is composed of those graphs  $\gamma \parallel \gamma'$  such that  $\gamma \in \Gamma$  and  $\gamma' \in \Gamma'$  are composable:  $\Gamma \parallel \Gamma' = \{\gamma \parallel \gamma' \mid \gamma \in \Gamma, \gamma' \in \Gamma', \gamma \bowtie \gamma'\}$ . This defines the composition of objects as  $(\Sigma \cup \Sigma', \Pi \cup \Pi', \Gamma \parallel \Gamma', \gamma_0 \parallel \gamma'_0)$ , assuming that  $\gamma_0 \bowtie \gamma'_0$ . Hence, if objects are considered as sets of constraints, synchronous composition corresponds the conjunction of the corresponding constraints.

**Example** The left part of the figure 9 depicts  $\gamma || \gamma'$ , where  $\gamma$  and  $\gamma'$  are the two graphs inside the rectangles. Pin  $\pi$  and port y are shared: they are superimposed via composition, and the mechanism of port/pin unification results in fixing value v for ports x and y. The resulting graph is shown on the right hand side.

Figure 9: Graph composition

**Disjunction** The disjunction  $\Gamma \vee \Gamma'$  of two families  $\Gamma$  and  $\Gamma'$  is the set theoretic union of the families  $\Gamma$  and  $\Gamma'$ . The disjunction of two objects  $O = (\Sigma, \Pi, \Gamma, \gamma_0)$  and  $O' = (\Sigma', \Pi', \Gamma', \gamma'_0)$  with composable initial graphs  $(\gamma_0 \bowtie \gamma'_0)$  is defined as follows:  $O \vee O' = (\Sigma \cup \Sigma', \Pi \cup \Pi', \Gamma \cup \Gamma', \gamma_0 || \gamma'_0)$ .

Asynchronous composition Consider two objects such that every  $\gamma \in \Gamma$  and  $\gamma' \in \Gamma'$  are circuit-free. We will also need to consider their asynchronous composition, which, roughly speaking, consists of:

- 1. constructing  $\Gamma^{\omega}$  and  $(\Gamma')^{\omega 1}$ ,

- 2. taking the composition via intersection, exactly as before.

#### Formally speaking:

- 1. Let  $\gamma_{\omega} \in \Gamma^{\omega}$  be a possibly infinite labeled graph. Pick all vertices that are labeled with the same port name, say x: they are organized into a linear order, we call it a *flow*. Thus a flow has the form  $x(v_1) \to x(v_2) \to x(v_3) \to \ldots$  and carries a (finite or infinite) sequence  $v_1, v_2, v_3, \ldots$  of values.

- 2. Two graphs  $\gamma_{\omega} \in \Gamma^{\omega}$  and  $\gamma'_{\omega} \in (\Gamma')^{\omega}$  are said asynchronously composable if, for any shared port  $x \in \Sigma \cap \Sigma'$ , the sequences of values  $v_1, v_2, v_3, \ldots$  and  $v'_1, v'_2, v'_3, \ldots$  of the two flows are identical.

- 3. If the condition above is satisfied, then the asynchronous composition  $\gamma_{\omega}||_{a}\gamma'_{\omega}$  is defined as the union of the graphs  $\gamma$  and  $\gamma'$  (where identical vertices are superimposed).

- 4. The family  $\gamma_{0}\circ(\Gamma)^{\omega}\|_{a}\gamma'_{0}\circ(\Gamma')^{\omega}$  is composed of those graphs  $\gamma_{\omega}\|_{a}\gamma'_{\omega}$  such that  $\gamma_{\omega} \in \gamma_{0}\circ(\Gamma)^{\omega}$  and  $\gamma'_{\omega} \in \gamma'_{0}\circ(\Gamma')^{\omega}$  are composable: this defines  $\mathcal{G}\|_{a}\mathcal{G}'$ .

Note that this again corresponds to taking the conjunction of corresponding constraints, but without the possibility to test for the absence of ports in an activated object.

<sup>&</sup>lt;sup>1</sup>note that pins and memories are erased while building the  $\omega$ -concatenation

#### 3.3 Discussion

We see that we have defined two different notions of composition.

- 1. Synchronous composition is compliant with the synchronous model, in which programs progress according to a possibly infinite sequence of reactions «P ≡ R<sup>ω</sup>». This model of abstract machine allows us to decide upon presence/absence of a given port within a considered reaction, a significant advantage for BDL specification. In addition, synchronous composition is defined at the level of a single reaction, which makes it simple and easy to use for system specification. This model of abstract machine is perfectly suitable when the target architecture consists of a single processor, or any other architecture in which a global notion of program state is easily available. In turn, synchronous composition is not compliant with target architectures involving nondeterministic multithreading, and definitely not compliant with distributed architectures involving asynchronous communication media.

- 2. Asynchronous composition as we have defined it uses a minimally demanding model of communication: any communication medium which is compliant with that of a partial ordering would do. This amounts to requiring a send-receive type of communication in which messages are not lost and not shuffled, yet a significant requirement, but still much more realistic than asking for implementing perfect synchrony in distributed architectures. Practically, this means that our abstract machine model of asynchronous communication does not handle fault-tolerance by itself.

In turn, it is recognized that handling such type of module composition at specification stage makes it difficult for the designer to keep track of dead-lock freedom and correctness, unless she/he would stick on very strict and restrictive programming disciplines (such as client-server). This is why we have decided to base specification on a synchronous model of communication, and, to base actual distributed implementation on an asynchronous model of communication, and, finally, to thoroughly study how one can safely move from the former model to the latter one.

### 3.4 Endochrony and Isochrony

We seek for a class of BDL objects for which both synchronous and asynchronous types of composition are equivalent. Suppose we can exhibit such a class of so-called *endochronous* and *isochronous* objects in the sequel. Then we design systems according to the following methodology:

- 1. Design the system using the synchronous paradigm, by freely assembling objects and classes using synchronous composition.

- 2. Configurate the design, i.e., decide upon the actual architecture for execution. This results in distributing the system on a set of ≪processors≫ (they may just correspond to threads), having the form of BDL objects obtained by synchronous composition of finer grain modules from system specification design stage.

- 3. Check if the so obtained processors are endochronous and isochronous. If so, then we know that their communication can actually be interpreted as an asynchronous one, hence subsequent distribution would become much easier. If this property is not satisfied, then some additional protocols need to be included to the processors, but this topic is beyond the scope of this paper.

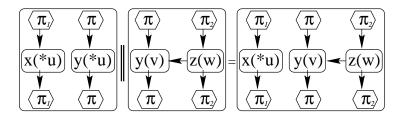

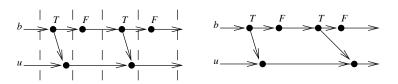

Thus these questions of endochrony and isochrony are central to our approach and make it attractive. How endochrony is feasible is intuitively illustrated in the figure 10, which shows the graph associated with the statement:  $\ll Guard\langle b, u \rangle \gg$ , defined in section 5.

Figure 10: Endochrony

The diagram on the left depicts the history or trace of this statement, showing the successive instants or reactions separated by thick dashed lines. Pins have been erased when performing concatenation. In the diagram on the right, an instant has been twisted and thick dashed lines have been removed, i.e., the notion of a reaction or instant has been lost. However, no information has been lost: we know that u should be got exactly when port b holds the value true, and thus it is only needed to wait for b in order to know whether u is to be waited for also. This suggest the way endochrony is formally defined. An object O considered with a given environment O' is isochronous if and only if object O has the same reactions (in terms of presence/absence of ports, disregarding values of ports) whether it is considered on its own or placed in the environment (O||O').

### 3.5 Meaning of BDL

Thanks to the mathematical framework introduced in sections 3.1 and 3.2, we can give a graphical denotation of the BDL actions A (figure 4) embedded in classes and objects. The mathematical denotation  $[\![A]\!]$  of an action A is defined in the figure 11 by induction on the structure of A. To any term A recursively corresponds a graph  $\Gamma$  whose ports  $\Sigma$  and pins  $\Pi$  are both  $\{x \mid x \text{ occurs in } A\}$ . The function  $[\![L]\!]$  considers actions A resulting of the expansion of well-typed BDL structures S (as defined in the figure 14). In the figure 11, we write  $[\![A]\!][*v/v]$  for the substitution of v by \*v in  $[\![A]\!]$  and  $[\![w/v]\!]$  for the composition of all  $[\![A]\!][w/v]$  s.t. w is of type T.

$$\begin{bmatrix} \mathbf{X}(\mathbf{V}) \\ \mathbf{X}(\mathbf{V}) \\ \mathbf{X}(\mathbf{V}) \\ \mathbf{X}(\mathbf{V}) \\ \mathbf{X}(\mathbf{V}) \\ \mathbf{Y} \\ \mathbf{Y}(\mathbf{W}) \end{bmatrix} = \begin{pmatrix} \operatorname{start}_x \to x(v) \to \operatorname{exit}_x \\ \downarrow \\ \operatorname{start}_y \to y(w) \to \operatorname{exit}_y \end{pmatrix} \begin{bmatrix} \mathbf{A} \\ \mathbf{A} \\ \mathbf{A} \end{bmatrix} = \begin{pmatrix} \|A\| \| \|A'\| \end{pmatrix} \begin{bmatrix} \mathbf{V} \cdot \mathbf{T} \\ \mathbf{A} \\ \mathbf{A} \end{bmatrix} = \begin{pmatrix} \|A\| \| \|A'\| \end{pmatrix} \begin{bmatrix} \mathbf{V} \cdot \mathbf{T} \\ \mathbf{A} \end{bmatrix} = \begin{pmatrix} \|A\| \| \|A'\| \end{pmatrix}$$

Figure 11: Denotation  $[\![A]\!]$  of an action A

# 4 Well-Typed BDL expressions

We formally define well-typed BDL phrases by the relation  $E \vdash S:t$  (figure 14) which associates a structure S to its type or signature t (figure 12) given an environment E. An environment E is a finite relation between identifiers I and types t (i.e.  $E \ni (I:t)$ ). A type is either a data-type d or an object type t. The relation  $E \vdash S:t$  is defined by induction on the syntax of BDL (figures 2 and 4). Each rule in the definition has the form  $\frac{P_{1..n}}{C}$  and defines the relation C as the conclusion of the conjunction of smaller premises  $P_1$  to  $P_n$ . Each rule is universally quantified over all its meta-names.

```

\begin{array}{l} d ::= \mathsf{bool} \mid \mathsf{int} \mid \mathsf{union} \ V_{1..n} \\ t ::= \mathsf{type} \ d \mid \mathsf{port} \ d \mid \mathsf{val} \ d \mid \mathsf{class} \ E \mid (I\!:\!t).t' \mid [V\!:\!d].t \end{array}

```

Figure 12: Data-types d and object-types t

The relation  $E \vdash S:t$  implements a contra-variant sub-typing relation  $t \leq t'$  between objects (figure 13). We identify the types (I:t).t' and (J:t).(t'[I/J]) for all J not occurring in t,t'.

$$\begin{array}{ll} \operatorname{port}\ d \leq \operatorname{port}\ d & \operatorname{val}\ d \leq \operatorname{val}\ d \\ \\ \underline{t \leq t'} \quad E \leq E' & \underline{E \leq E'} \\ \hline E, (I\!:\!t) \leq E', (I\!:\!t') & \operatorname{class}\ E \leq \operatorname{class}\ E' \\ \\ \underline{t' \leq t'''} \quad t'' \leq t & \underline{t \leq t'} \\ \hline (I\!:\!t).t' \leq (I\!:\!t'').t''' & \overline{[V\!:\!d].t \leq [V\!:\!d].t'} \\ \end{array}$$

Figure 13: Sub-typing relation  $t \leq t'$

The relation of well-typing  $E \vdash S : t$  is structurally decomposed into a relation  $E \vdash D : t$  on declarations D, a relation  $E \vdash I : t$  on identifiers and a relation  $E \vdash A$  on actions A. Notice that the type associated with a structure

S is exactly its  $\ll$ interface $\gg$ . Also notice that declaring this interface (i.e.  $\ll$ class C:C' is  $D\gg$ ) prevents other identifiers (i.e. in D but not in C') to be visible from the environment.

$$E \vdash D : t$$

$$E \vdash \mathsf{class}\ C \ \mathsf{is}\ D \colon \mathsf{class}\ (C \colon t)$$

$$E \vdash D \colon t \quad E \vdash C' \colon t' \quad t \le t'$$

$$E \vdash \mathsf{class}\ C \colon C' \ \mathsf{is}\ D \colon \mathsf{class}\ (C \colon t')$$

$$E \vdash T \colon \mathsf{type}\ d \quad E, (V \colon \mathsf{val}\ d) \vdash D \colon t$$

$$E \vdash \mathsf{class}\ C[V \colon T] \ \mathsf{is}\ D \colon \mathsf{class}\ (C \colon [V \colon d] \colon t)$$

$$E \vdash T \colon t \quad E, (I \colon t) \vdash D \colon t'$$

$$E \vdash \mathsf{class}\ C(I \colon T) \ \mathsf{is}\ D \colon \mathsf{class}\ (C \colon (I \colon t) \colon t')$$

$$E \vdash C \colon t$$

$$E \vdash \mathsf{object}\ O \ \mathsf{of}\ C \colon \mathsf{class}\ (O \colon t)$$

Figure 14: Relation  $E \vdash S:t$

Similarly, every declaration D introduces a binding between an identifier and a structure. Therefore, the relation  $E \vdash D:t$  also associates declarations D to object types.

$$\frac{E \vdash T : \mathsf{type} \ d}{E \vdash \mathsf{port} \ X : T : \mathsf{class} \ (X : \mathsf{port} \ d)}$$

$$\frac{E \vdash C : (J : t') . t \quad E \vdash I : t'' \quad t' \leq t''}{E \vdash C \langle I \rangle : t[J/I]}$$

Figure 15: Relation  $E \vdash D:t$

The type-checking of the selection of an element in a compound class or in an array class is implemented by the relation  $E \vdash I : t$  between compound identifiers I and types t as follows.

$$E, (I:t) \vdash I:t \qquad \frac{E \vdash C: (V:d).t \quad E \vdash W: \mathsf{val} \ d}{E \vdash C[W]: t[W/V]} \qquad \frac{E \vdash I: \mathsf{class} \ (E', (J:t))}{E \vdash I.J: t}$$

Figure 16: Relation  $E \vdash I:t$

Finally, the type-checking relation between environments E and actions A checks the conformance between data-types and object-types already declared and visible (in E) and the way they are used (in A).

$$\frac{E \vdash X \colon \mathsf{port} \ d \quad E \vdash V \colon \mathsf{val} \ d}{E \vdash X(V)} \qquad \frac{E \vdash X(V), Y(W)}{E \vdash X(V) \to Y(W)}$$

$$\frac{E \vdash A}{E \vdash !A} \qquad \frac{E \vdash A, A'}{E \vdash A \text{ or } A'} \qquad \frac{E \vdash A, A'}{E \vdash A \parallel A'}$$

$$\frac{E \vdash T \colon \mathsf{type} \ d \quad E, (V \colon \mathsf{val} \ d) \vdash A}{E \vdash \mathsf{all} \ V \colon T \ A}$$

$$\frac{E \vdash T \colon \mathsf{type} \ d \quad E, (V \colon \mathsf{val} \ d) \vdash A}{E \vdash \mathsf{any} \ V \colon T \ A}$$

Figure 17: Relation  $E \vdash A$

# 5 Using BDL

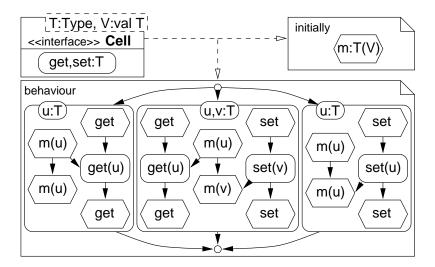

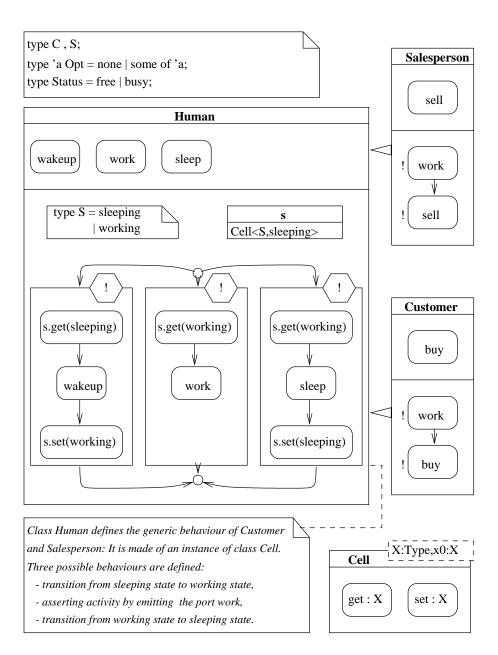

The complete definition of the BDL language consists of the core BDL syntax of section 2 enriched with a predefined class (Cell, figure 18) and a set of pervasive classes (such as Guard or Sync, figures 20 and 21) which can be defined in BDL with the only help of class Cell.

The pervasive class Cell The class Cell (defined figure 18) is a generic class of two parameters (the first one, T, is a data-type and the second one, V, is a value of that data-type). Class Cell acts like a memory in which values ranging over data-type T can be stored (using port set) and retrieved (using port get). Value are transported from a transition to another by resourcing to pins. Parameter V is the initial value of the memory m.

Figure 18: The pervasive class Cell

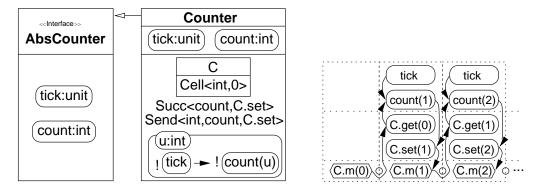

The class Counter A typical usage of class Cell is given in figure 19. The class Counter (on the left in the figure) emits on the port count the number of tick messages it receives. A trace of the counter, consisting of the concatenation  $\gamma_{0}$ , is depicted on the right in the figure.

Figure 19: Using Cell to define a Counter

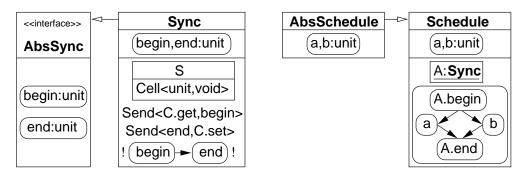

The class Sync Figure 20 gives the definition of class Sync, which can be used to enforce sequentiality between occurrences of groups of ports or objects. The use of the class Sync is examplified on the right in the figure 20. The synchronizer A defines a task, consisting of the events a and b, and enforces its completion within the bounds delimited by A.begin and A.end, and its sequentiality with any other task in causal relation with A.

Figure 20: Using Cell to define Sync

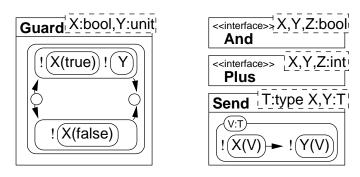

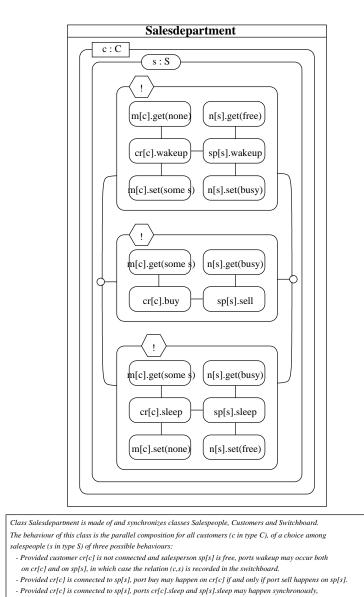

Other pervasive classes A few other pervasive, generic, classes are detailed in figure 21. The class Guard allows to condition the activation of a message Y by a boolean port X. The class Send models the synchronous transmission of a value V from a port X to a port Y. The interfaces And and Plus show that operations on booleans or integers ports X, Y, Z can be regarded as generic classes. A more significant example of BDL specification is detailed in figure 22 of the appendix. This example is self-contained and self-explanatory.

Figure 21: Other BDL pervasives

## 6 Contributions

The use of BDL integrates naturally in an UML object-oriented development process (figure 1). It allows to define a logical interaction model between the components described in the functional architecture of a system, with the help of a preliminary UML design and elementary scenari. BDL descriptions can be added to the preliminary UML design by means of stereotypes [2] in order to enrich the model with a behavioural view of the system.

At this stage of the development, object-oriented methodologies such as OMT or UML usually recommend the refinement of declarative diagram descriptions (architecture, scenari) using imperative automata specifications for describing the behavior of system components (e.g. using SDL [19], STATE-CHARTS [10] or [5]). All these approaches offer means of directly describing an «heterogeneous» architecture (i.e. an asynchronous network of synchronous, imperative, objects).

According to the above respects, our approach radically differs from previous works [19, 10, 5]. It is motivated by the fact that stepping from a declarative description of scenari to an imperative description of behaviours is difficult without making minimal hypothesis on the actual distribution of system components and on an interpretation of communications (in the scenari) and of concurrency (in the architecture). BDL solves this key issue by implementing a declarative description of objects interaction in terms of graph families without making any assumption about their distribution. This approach allows an homogeneous description of the functional architecture of distributed object-oriented applications. Mapping this architecture to a particular, heterogeneous, configuration is regarded as a separate issue of «deployment».

# 7 Perspectives

Given the configuration and dimensions of a target system (by means of an UML deployment of BDL diagrams), the functional architecture of the application can be instantiated to form an assembly which defines the behaviour of the target system in terms of a distribution of reactive objects. To each object corresponds a family of graphs which can be executed by iteratively choosing composable and concatenable graphs, as defined section 3. The causal relations between the components of the target system can be interpreted in several ways: synchronous communication (within a confined target object), asynchronous communication (between distributed target objects), data or control dependencies, real-time dependencies, etc.

The interpretation of distributed objects as communicating automata or symbolic transition systems allows to use efficient verification tools, such as CADP [8], in order to verify the global safety properties of the target systems (e.g., deadlock freedom, reachability of states). The interpretation of confined objects as synchronous programs allows to compile them separately in order to generate either simulation programs or intelligent program stubs implementing the scheduling of communications and concurrency of an object with its remote environment.

Just as IDL specifications describe what application components exchange with its environment, BDL specifications describe how these components interact with it. A BDL specification allows to compile its interaction pattern (i.e. communication and concurrency) as well as an IDL specification allows the automated generation of program stubs for an application component (i.e. code for marshaling and exchanging data with the environment and for plugging it with common ORB communication resources).

Thanks to its formulation using a partial-order theoretical framework, the BDL specification of a capsule (a set of application components, embedded according to a given configuration) allows an optimized compilation by resourcing to code generation techniques employed in synchronous programming languages, such as SIGNAL [6], for implementing embedded systems. More precisely, the graph family  $\Gamma$  of a BDL-capsule can be translated into a STS scheduling specification (Symbolic Transition Systems, [4, 16]) which describes both the control model (e.g. the valuations) and the causality model (e.g. the

arrows) of the service. By determining the tasks in this graph (i.e. the control configurations or states) and by hierarchizing them (i.e. determining the logical relations between them), the program implementing each capsule of a BDL specification can be automatically generated.

## 8 Conclusion

We have introduced the formal definition of a declarative specification language for describing distributed reactive objects, BDL, and demonstrated that BDL provides a unified medium for specifying, verifying and compiling distributed real-time applications. In contrast to the object-oriented extensions of conventional automata-based tools for specifying distributed systems [19, 10, 5], the BDL language implements a smoother phase transition between the specification of a system and its configuration. This allow to feature a better integration into UML.

BDL supports a description of object components interaction which respects both the functional architecture of UML system designs and the declarative style of UML diagram descriptions. BDL implements a both simple and expressive theoretical framework which allows to specify both the causality and the control models of object interactions independently of any hypothesis on the actual configuration of the system. The definition of BDL offers new perspectives for a flexible verification of systems, the generation of optimized code, an accurate validation of applications by supporting the manipulation of both causal and control dependencies. BDL aims at maximizing the re-usability of high-level specifications and at minimizing programming and validation efforts for the implementation of real-time, object-oriented, distributed systems.

## References

- [1] R. Alur, G.J. Holzmann and D. Peled. A analyzer for Message Sequence Charts. In *Tools and Algorithms for the Construction and Analysis of Sys*tems. Lecture Notes in Computer Science v. 1055., p. 35–48. Springer, 1996.

- [2] S.W. Ambler. The Unified modeling language and beyond: the techniques of object-oriented modeling, (http://www.ambysoft.com), August 1997.

- [3] C. André, F. Boulanger, M.-A. Péraldi, J.-P. Rigault, and G. Vidal-Naquet. Objects and synchronous programming. In *European Journal on Automated Systems*, v. 31(3), p. 417–432. Hermes, 1997.

- [4] A. Benveniste, P. Le Guernic and P. Aubry. Compositionality in dataflow synchronous languages: specification and code generation. In *Malente Workshop on Compositionality*. W.P. de Roever, A. Pnueli Eds, 1997.

- [5] F. Bertrand and M. Augeraud. BDL, a language to control the behavior of concurrent objects. In *Conference on Domain-Specific Languages*, p. 133-144. USENIX, 1997.

- [6] A. Benveniste, P. Le Guernic and C. Jacquemot. Synchronous programming with events and relations: the Signal language and its semantics. In *Science of Computer Programming*, v. 16, 1991.

- [7] R. Breu, U. Hinkel, C. Hofmann, C. Klein, B. Paech, B. Rumpe and V. Thurner. Towards a formalization of the unified modeling language. In *Proceedings of the 11th European Conference on Object-oriented programming*. Lecture Notes in Computer Science v. 1241. Springer, 1997.

- [8] J.-C. Fernandez, H. Garavel, A. Kerbrat, L. Mounier, R. Mateescu and M. Sighineanu. Computer Aided Verification. In *CADP: a protocol validation and verification toolbox*, 1996.

- [9] J. Grabowski, E. Rudolph and P. Graubman. Message Sequence Charts: composition techniques versus OO-techniques. In *Proceedings of the 7th.* SDL forum, 1995.

- [10] D. Harel and E. Gery. Executable Object Modeling with Statecharts. In Proceedings of the International Conference on Software Engineering, p. 246-257. IEEE, 1996.

- [11] I. Jacobson, M. Christerson, P. Jonsson and G. Overgaard. Object-Oriented Software Engineering A Use Case Driven Approach. ACM, 1992.

- [12] C. Jard, J.-M. Jézéquel and L. Nedelka. An Approach to Integrate Formal Validation in an OO Life-cycle of Protocols. In Proceedings of FMOODS'96. Chapman & Hall, March 1996.

- [13] L. Lamport. Specifying concurrent program modules. In *ACM Transactions on Programming Languages and Systems*, v. 5(2), p. 190-222. ACM, 1983.

- [14] S. Pickin, C. Sanchez, J.-C. Yelmo, J.-J. Gil and E. Rodriguez. Introducing formal notations in the development of object-based distributed applications. In *Proceedings of FMOODS'96*, p. 87–102. Chapman & Hall, March 1996.

- [15] A. Prinz. Including behaviour into interfaces. In *Proceedings of* FMOODS'96, p. 37–49. Chapman & Hall, March 1996.

- [16] A. Pnueli, et al. Symbolic Transition Systems. In *Malente Workshop on Compositionality*. W.P. de Roever, A. Pnueli Eds. September 1997.

- [17] J. Rumbaugh, I. Jacobson and G. Booch. *Unified Modeling Language Reference Manual*. ISBN n. 0-201-30998-X. Addison-Wesley, 1997.

- [18] B. Selic, G. Gullekson and P. T. Ward. Real-Time Object-Oriented Modeling. John Wiley & Sons, 1994.

- [19] Recommendation Z.100 CCITT specification and description language (SDL). International Telecommunication Union, March 1993.

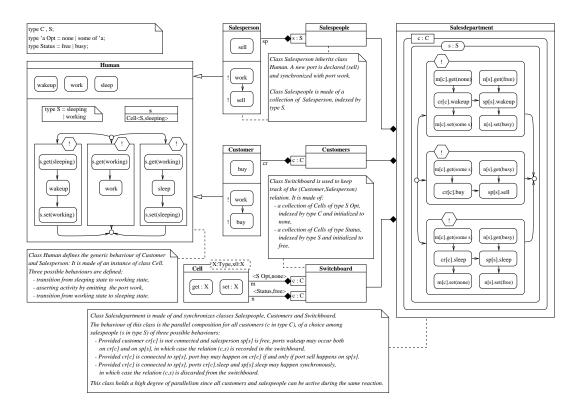

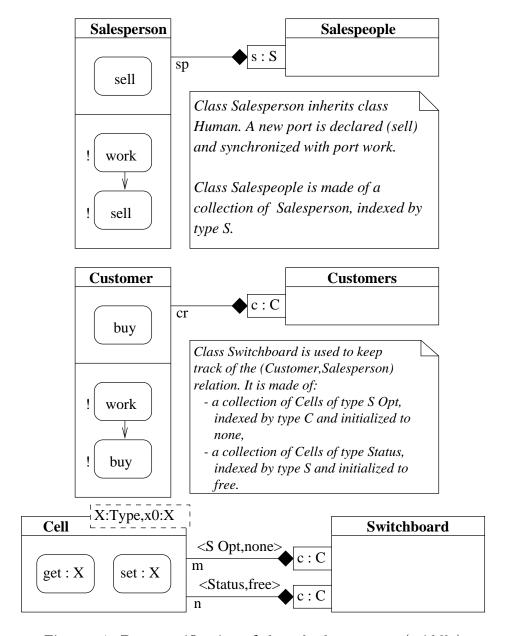

Figure 22: BDL specification of the salesdepartment

Figure 23: BDL specification of the salesdepartment (left)

Figure 24: BdL specification of the salesdepartment (middle)

Figure 25: BDL specification of the salesdepartment (right)

in which case the relation (c,s) is discarded from the switchboard.

All customers and salespeople can be active during the same reaction.

# List of Figures

| 1  | BDL in its environment                                  | 6  |

|----|---------------------------------------------------------|----|

| 2  | Formal syntax of BDL classes                            | 8  |

| 3  | UML notation for BDL                                    | 9  |

| 4  | BDL actions A                                           | 10 |

| 5  | Graphical syntax for BDL actions A                      | 10 |

| 6  | Pins                                                    | 11 |

| 7  | Graph with quantifications                              | 13 |

| 8  | Graph concatenation                                     | 15 |

| 9  | Graph composition                                       | 16 |

| 10 | Endochrony                                              | 19 |

| 11 | Denotation $[\![A]\!]$ of an action $A$                 | 21 |

| 12 | Data-types $d$ and object-types $t$                     | 22 |

| 13 | Sub-typing relation $t \leq t' \dots \dots \dots \dots$ | 22 |

| 14 | Relation $E \vdash S:t$                                 | 23 |

| 15 | Relation $E \vdash D:t$                                 | 23 |

| 16 | Relation $E \vdash I:t$                                 | 24 |

| 17 | Relation $E \vdash A$                                   | 24 |

| 18 | The pervasive class Cell                                | 25 |

| 19 | Using Cell to define a Counter                          | 26 |

| 20 | Using Cell to define Sync                               | 26 |

| 21 | Other BDL pervasives                                    | 27 |

| 22 | BDL specification of the salesdepartment                | 34 |

| 23 | BDL specification of the salesdepartment (left)         | 35 |

| 24 | BDL specification of the salesdepartment (middle)       | 36 |

| 25 | BDL specification of the salesdepartment (right)        | 37 |

Unit´e de recherche INRIA Lorraine, Technopôle de Nancy-Brabois, Campus scientifique,

615 rue du Jardin Botanique, BP 101, 54600 VILLERS LÈS NANCY

Unit´e de recherche INRIA Rennes, Irisa, Campus universitaire de Beaulieu, 35042 RENNES Cedex

Unit´e de recherche INRIA Rhône-Alpes, 655, avenue de l'Europe, 38330 MONTBONNOT ST MARTIN

Unit´e de recherche INRIA Rocquencourt, Domaine de Voluceau, Rocquencourt, BP 105, 78153 LE CHESNAY Cedex

Unit´e de recherche INRIA Sophia-Antipolis, 2004 route des Lucioles, BP 93, 06902 SOPHIA-ANTIPOLIS Cedex

Éditeur

INRIA, Domaine de Voluceau, Rocquencourt, BP 105, 78153 LE CHESNAY Cedex (France)

http://www.inria.fr

ISSN 0249-6399