# Optimal Register Saturation in Acyclic Superscalar and VLIW Codes

Sid Touati

#### ▶ To cite this version:

Sid Touati. Optimal Register Saturation in Acyclic Superscalar and VLIW Codes. RR-4263, INRIA. 2001. inria-00072324

## HAL Id: inria-00072324 https://inria.hal.science/inria-00072324

Submitted on 23 May 2006

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

# Optimal Register Saturation in Acyclic Superscalar and VLIW Codes

Sid-Ahmed-Ali TOUATI

N° 4263

September 14, 2001

\_THÈME 1 \_

apport de recherche

# Optimal Register Saturation in Acyclic Superscalar and VLIW Codes

Sid-Ahmed-Ali TOUATI

Thème 1 — Réseaux et systèmes Projet A3

Rapport de recherche n° 4263 — September 14, 2001 — 64 pages

Abstract: In previous work [TT00], we theoretically studied the register saturation notion in the acyclic data dependence graphs (DDG). It consists in computing the exact maximal number of registers needed to achieve the computation of DDGs independently from schedules. We proved that this problem is NP-complete and we proposed a greedy heuristic to solve it. In this work, we study how to compute the optimal solutions using the integer linear programming in the case of acyclic DDGs. Also, new theorems are given to formally prove some of our assertions written in the previous report. We prove also that the problem of reducing the register saturation by introducing new arcs is an NP-hard problem, and we give a method to compute an optimal solution for it using the integer linear programming.

**Key-words:** register constraints, register need, optimal register saturation, reducing register saturation

This work was partially supported by ESPRIT Project MHAOTEU

## Calcul Optimal de la Saturation en Registres dans les Codes Horizontaux et Verticaux

Résumé: Dans un travail précédent [TT00], nous avons étudié théoriquement la notion de saturation en registres dans les graphes de dépendance de données acycliques (GDD). Elle consiste à déterminer la borne maximale exacte du besoin en registres d'un GDD indépendemment des ordonnacements possibles. Nous avons prouvé que ce problème est NP-complet et avons proposé une heuristique gloutonne. Dans ce rapport, nous présentons comment calculer la solution optimale avec la programmation linéaire en nombres entiers dans le cas des GDD acycliques afin de prouver expérimentalement l'efficacité de notre heuristique. De nouveaux théorèmes sont formellement démontrés pour consolider nos affirmations dans le dernier rapport [TT00]. Nous prouvons également que le problème de la réduction de la saturation en registres en introduisant de nouveaux arcs est un problème NP-dur. Nous présentons une méthode basée sur la programmation linéaire en nombres entiers pour le calcul d'une solution optimale à ce problème.

Mots-clés : contraintes de registres, besoin en registres, saturation optimale en registres, réduction de la saturation en registres

# Contents

| 1 | Intr           | roduction                                        | 1        |

|---|----------------|--------------------------------------------------|----------|

| 2 | <b>Reg</b> 2.1 | gister Saturation DDG Model                      | <b>3</b> |

|   | 2.2            | Register Saturation                              | 4        |

|   |                | 2.2.1 Register Need of a Schedule                | 5        |

|   |                | 2.2.2 Register Allocation                        | 6        |

|   |                | 2.2.3 Register Saturation Problem                | 7        |

|   |                | 2.2.4 A Heuristic for Computing RS               | 14       |

|   | 2.3            | Optimal Register Saturation Computation          | 17       |

|   |                | 2.3.1 Integer Linear Programming                 | 18       |

|   |                | 2.3.2 Exact Register Saturation Problem Modeling | 18       |

| 3 | Opt            | timal Register Saturation Reducing               | 29       |

|   | 3.1            | NP-hardness of Reducing Register Saturation      | 29       |

|   | 3.2            | Heuristics for RS Reduction                      | 30       |

|   | 3.3            | Optimal Register Saturation Reducing Modeling    | 33       |

|   |                | 3.3.1 Exact Formulation                          | 34       |

|   |                | 3.3.2 Building Extended DDGs                     | 35       |

|   |                | 3.3.3 Problem of Negative or Null Cycles         | 36       |

| 4 | m Reg          | gister Saturation with Multiple Registers Types  | 37       |

|   | 4.1            | DDG Model                                        | 37       |

|   | 4.2            | Computing Register Saturation                    | 38       |

|   | 4.3            | Integer Programming Formulation                  | 39       |

|   |                | 4.3.1 Scheduling Variables                       | 39       |

|   |                | 4.3.2 Registers Constraints                      | 39       |

|   |                | 4.3.3 Objective Function                         | 41       |

|   | 4.4            | Reducing Register Saturation                     | 41       |

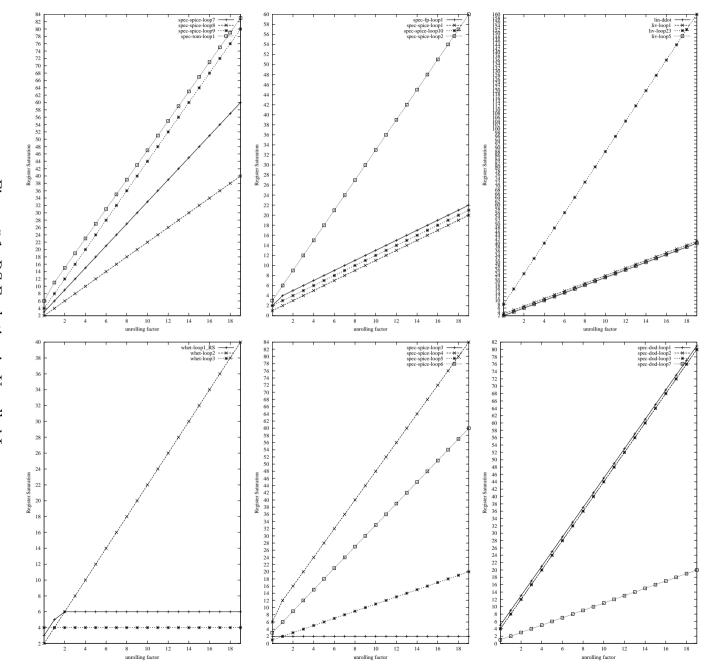

| 5 | Exp            | perimentation                                    | 43       |

|   | 5.1            | Optimal RS Computation                           | 43       |

|   | 5.2            | Optimal Reducing of Register Saturation          | 47       |

|   | 5.3            | RS Behavior in Unrolled Loops                    | 47       |

|   | 5.4            | ILP Loss in Unrolled Loops after RS Reduction    | 52       |

| 6 | Con            | nclusion                                         | 57       |

A Example of Optimal RS Computation

**59**

# List of Figures

| 2.1 | DAG Model                                                   | 5  |

|-----|-------------------------------------------------------------|----|

| 2.2 | Example of Register Allocation                              | 7  |

| 2.3 | Example for Theorem. 2.1 proof                              | 11 |

| 2.4 | Valid Killing Function                                      | 12 |

| 2.5 | Potential Killing DAG                                       | 14 |

| 2.6 | Bipartite Decomposition                                     | 15 |

| 2.7 | Example of Register Saturation Computing                    | 17 |

| 2.8 | Expressing an <i>n</i> -Disjunction with Linear Constraints | 20 |

| 2.9 | Expressing $max_n$ Operator with Linear Constraints         | 23 |

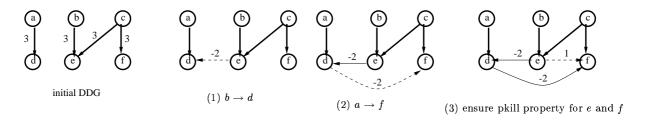

| 3.1 | Ensure $pkill$ operations property                          | 32 |

| 3.2 | Reducing register saturation                                |    |

| 3.3 | Optimal RS Reducing with Possibly Negative or Null Cycles   | 35 |

| 4.1 | DDG Model with Multiple Registers Types                     | 38 |

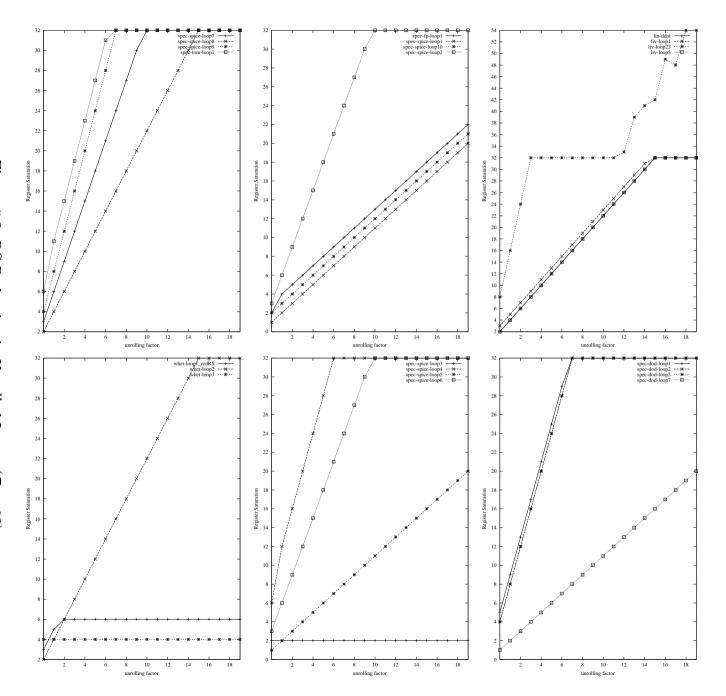

| 5.1 | RS Evolution in Unrolled Loops                              | 53 |

| 5.2 | RS Reduction in Unrolled Loops ( $\mathcal{R}=32$ )         |    |

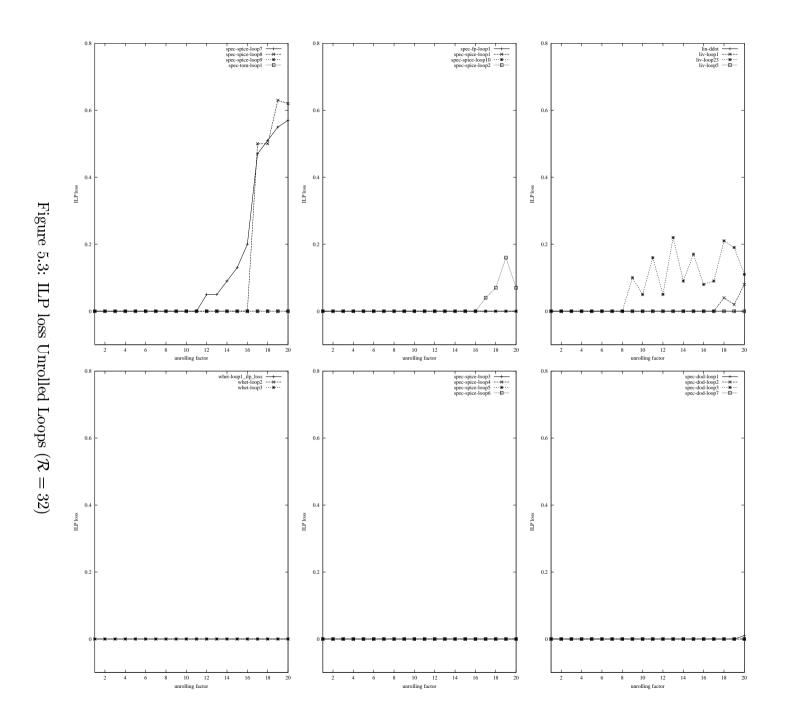

| 5.3 | ILP loss Unrolled Loops $(\mathcal{R} = 32)$                |    |

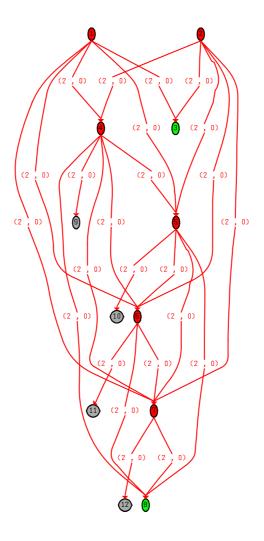

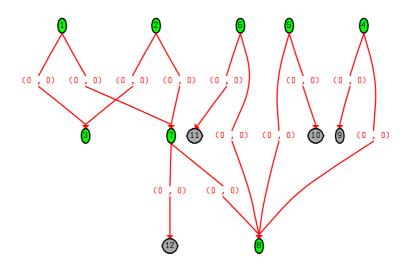

| A.1 | spec-spice : loop4 body                                     | 60 |

|     | spec-spice loop $4: PK(G)$                                  |    |

|     | spec-spice loop4 : $DV_{k^*}(G)$                            |    |

## Chapter 1

## Introduction

The peak performance of the processors is continuously increasing thanks to the architectural and technological advances. However, the memory bottleneck imposes the most crucial barrier to achieving best possible performance for real applications. To reduce processor idleness caused by long memory latencies, lots of ILP compilation techniques try to profit from memory hierarchy abilities as fast caches and multiple register files.

The rgisters are at the same time the fastest memory in processors and the most size-limited. This imposes lot of efforts to achieve their best exploitation. ILP compilers allocate data in registers to make them closer to processor core. Nevertheless, the number of registers is limited and a tradeoff must be done to decide which data must be kept in register and which must be spilled. In previous work [TT00], we studied the notion of register saturation (RS) in data dependence graphs (DDG). Register saturation is the maximum number of registers needed to achieve a computation independently of any schedule and functional units constraints. We proved that this problem is NP-complete and provided a heuristic to compute it. There are many purposes to study the register saturation. First, if the register saturation is lower than the number of available registers, we are sure than no spill is needed and all data can be kept in registers independently from any schedule. Second, it can be used to study worst possible register need in real applications, providing beneficial information to processor designers to decide about register file sizes. Third, we provide heuristics in order to reduce the register saturation in original DDGs by introducing new arcs. This enables us to keep the register need under the limit of available registers. Finally, a possible application is intended for real-time codes where timing constraints are critical. In such codes, the performance prediction is important to check if a given code can meet real-time constraints. With the RS analysis, we can check statically if no spill code is needed: this provides a beneficial help since register access delays are pratically null while memory access time latencies produced by spill code are time consuming and hard to predict in the presence of caches.

This work is an extension and continuation to [TT00]. We theoretically and experimentally study here the optimal register saturation and its reduction. The main aim is to prove empirically the efficiency of our heuristics. We also prove new theorems to validate some previous assertions. We invite the readers to first consult our previous work to have the basic mathematical results and achievements on the register saturation notion.

This report is organized as follows. Chapter 2 studies the computation of optimal register saturation using linear integer programming. We begin by defining DDG models and recalling some definitions and theorems. Then we write mathematical formulation of optimal RS computation. If the RS is greater than the number of available registers, we add serial arcs to reduce it. Computing an optimal RS reduction is studied in Chap. 3 where we prove that this problem is NP-hard. We extend the register saturation notion in order to take into account more than one register type in the same DDG in Chap. 4. We implemented some tools to make experimentations on various codes. Chapter. 5 gives experimental results on optimal vs. approximated solutions. We show that both heuristics of RS computation and reduction are nearly optimal: worst error in practice is always 1 register for RS computation, and 2 registers for RS reduction. We conclude by remarks and future work in Chap. 6.

## Notation and Definitions on DAGs

In this paper, we use the following notations for a given direct acyclic grapg DAG G = (V, E), where V is the set of nodes and E the set of arcs:

- $\Gamma_G^+(u) = \{v \in V/(u,v) \in E\}$  successors of u;

- $\Gamma_G^-(u) = \{v \in V/(v, u) \in E\}$  predecessors of u;

- $\forall e = (u, v) \in E \quad source(e) = u \land target(e) = v;$

- $\forall u, v \in V : u < v \iff \exists \text{ a path } (u, \dots, v) \text{ in } G$ ;

- $\forall u, v \in V : u \sim v \iff (u < v) \lor (v < u)$ . u and v are said **comparable**;

- $\forall u, v \in V : u || v \iff \neg(u \sim v)$ . u and v are said to be **parallel**;

- $\forall u \in V \uparrow u = \{v \in V / v = u \lor v < u\}$  u's ascendants including u;

- $\forall u \in V \downarrow u = \{v \in V / v = u \lor u < v\}$  u's descendants including u;

We give also the following definitions:

- two arcs e, e' are **adjacent** iff they share a node.

- $A \subseteq V$  is an antichain in  $G \iff \forall u, v \in A \quad u||v|$

- AM is a **maximal** antichain  $\iff AM$  is an antichain and  $\forall A$  antichain in  $G |A| \leq |AM|$ ;

- an **extended** DAG  $G \setminus^{E'}$  of G generated by the arcs set  $E' \subseteq V^2$  is the graph G after adding the arcs in E'. As consequence:  $G' = G \setminus^{E'} \Longrightarrow \Sigma(G') \subseteq \Sigma(G)$

- let  $I_1 = [a_1, b_1] \subset \mathbb{N}$  and  $I_2 = [a_2, b_2] \subset \mathbb{N}$  be two integer intervals. We say that  $I_1$  is before  $I_2$ , noted  $I_1 \prec I_2$ , iff  $b_1 < a_2$ .

## Chapter 2

## Register Saturation

In this chapter, we give formal definitions and results on RS computation. We recall our heuristics that compute it, and then we write linear integer programming models to compute the optimal solution. Let us begin by defining the direct acyclic DDG model which we use.

## 2.1 DDG Model

A DDG  $G = (V, E, \delta, \delta_w, \delta_r)$  in our study represents a direct acyclic graph (DAG) which defines data dependences between operations. Each operation u has a strictly positive latency lat(u). The DDG is then defined by:

- V is the set of operations;

- $E = \{(u, v) / u, v \in V\}$  are data dependence constraints;

- $\forall e = (u, v) \in E$ ,  $\delta(e) = lat(u)$  is the latency of the dependence in terms of processor clock cycles.

Since writing and reading into and from registers may be delayed from the beginning of the operation schedule time (VLIW case), we define the two delay functions  $\delta_r$  and  $\delta_w$ :

$$\delta_w: V \to \mathbb{N}$$

$$u \mapsto \delta_w(u)/0 \le \delta_w(u) < lat(u)$$

the write cycle of  $u$  is  $\sigma(u) + \delta_w(u)$

$$\delta_r: V \to \mathbb{N}$$

$$u \mapsto \delta_r(u)/0 \le \delta_r(u) \le \delta_w(u) < lat(u)$$

the read cycle of  $u$  is  $\sigma(u) + \delta_r(u)$

To simplify the writing of our formulas, we assume that the DDG has one source  $(\top)$  and one sink  $(\bot)$ . If not, we introduce two virtual nodes  $(\top,\bot)$  representing nops (that are evicted at the end of RS analysis).  $\top$  represents the only node without predecessor, and  $\bot$  the only node without successor. We add a virtual serial arc  $e_1 = (\top, s)$  to each source with  $\delta(e_1) = 0$ , and an arc  $e_2 = (t, \bot)$  from each sink with the latency of the sink operation  $\delta(e_2) = lat(t)$ . The null latency of an added arc  $e_1$  is not inconsistent with our assumption that latencies must be strictly positive because the added virtual serial arcs no longer represent data dependencies. Furthermore, we can avoid introducing these virtual nodes without any consequence on our theoretical study since their purpose is only to simplify some mathematical expressions. Our

hypothesis that latencies must be strictly positive is important since we use it to prove some crutial theorems devoted to give good heuristics.

Then, a valid schedule  $\sigma$  of G is a positive function that gives an integer execution (issue) time (clock cycle) for each operation:

$$\sigma: V \to \mathbb{N}$$

$$u \mapsto \sigma(u)$$

where

$$\sigma$$

is valid  $\iff \forall e = (u, v) \in E, \quad \sigma(v) - \sigma(u) \ge \delta(e)$

We note by  $\Sigma(G)$  the set of all valid schedules for G, and  $\overline{\sigma} = \sigma(\bot)$  the last execution step (total schedule time).

When studying register need in a DDG, we make a difference between nodes, depending on whether they define a value to be stored in a register or not, and also depending on which register type we are focusing on (int, float, etc.). We also make a difference between edges depending on whether they are flow dependencies through registers of the type considered type:

- $V_R \subseteq V$  is the subset of operations which define a value of the type under consideration (int, float, etc.), we simply call them **values**. We assume that at most one value of the type considered can be defined by an operation. Operations that define multiple values are taken into account if they define at most one value of the type considered. For instance, operations which write into one floating point register and set condition codes are acceptable in our model.

- $E_R \subseteq E$  is the subset of arcs representing true dependencies through a value of the considered type. We call them **flow** arcs. It is clear that  $e = (u, v) \in E_R \Longrightarrow u \in V_R$ , but this is not necessarily true for v; this is because some operations read values of a considered type and write a value of another type like test operations, loads, type conversion, etc.

- $E_S = E E_R$  are called **serial** arcs. Note that it is possible to have two value nodes that are data dependent but not through a value of the considered type. For instance, both operations u, v writes an integer and a float results. In the case where we focus on floating point values and operation v reads the integer value of u, then  $u, v \in V_R \land e = (u, v) \in E_S$ .

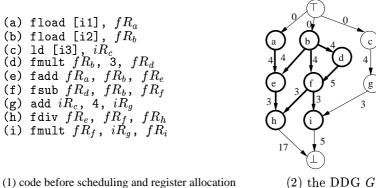

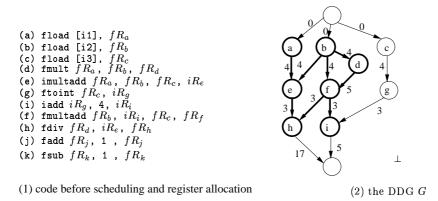

Figure 2.1 gives a DDG that we use in this paper. In this example, we focus on floating point registers: values and flow arcs are shown with bold lines. For simplicity, we assume that each read occurs exactly at the schedule time and each write at the final execution step:

$$\forall u \in V$$

$\delta_r(u) = 0 \land \delta_w(u) = lat(u) - 1$

## 2.2 Register Saturation

In this section, we make a study from a theoretical perspective of the register saturation notion. We first begin by recalling what the register need of a schedule is.

Figure 2.1: DAG Model

#### 2.2.1Register Need of a Schedule

Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$ , a value  $u \in V_R$  is alive at the first step after the writing of u until its last reading (consumption). The values that are not read in G are those that are still alive when exiting the computation and must be kept in registers. We handle these special values by considering that the bottom node  $\perp$  consumes them. We define the set of consumers for each value  $u \in V_R$  as

$$Cons(u) = \begin{cases} \{v \in \Gamma_G^+(u)/(u,v) \in E_R\} & \text{if } \exists (u,v) \in E_R \\ \bot & \text{otherwise} \end{cases}$$

Given a schedule  $\sigma \in \Sigma(G)$ , the last consumption of a value is called the killing date and noted;

$$\forall u \in V_R \quad kill_{\sigma}(u) = \max_{v \in Cons(u)} (\sigma(v) + \delta_r(v))$$

All consumers whose reading time is equal to u's killing date are called killers of u, and noted  $killers_{\sigma}(u)$ . We assume that a value written at clock cycle t in a register is available one step later. That is to say, if operation u reads from a register at clock cycle t while operation v is writing in it at the same clock cycle, u does not get v's result but gets the value previously stored in that register. Then, the **lifetime interval**  $L_u^{\sigma}$  of the value u according to  $\sigma$  is  $[\sigma(u) + \delta_w(u), kill_{\sigma}(u)].$

Having all value's lifetime intervals, the register need of  $\sigma$  is the maximum number of values simultaneously alive, which is the minimum number of registers needed to avoid spill code for that schedule.

**Definition 2.1 (Register Need)** Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$ , the register need  $RN_{\sigma}(G)$ of G for a schedule  $\sigma \in \Sigma(G)$  is defined by

$$RN_{\sigma}(G) = \max_{0 \le i \le \overline{\sigma}} |vsa_{\sigma}(i)|$$

where

$$vsa_{\sigma}(i) = \{u \in V_R/i \in L_u^{\sigma}\}$$

is the set of values alive at clock cycle  $i$

Values simultaneously alive that define the register need are called excessive values.

**Definition 2.2 (Excessive Values)** Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$  and a schedule  $\sigma \in \Sigma(G)$ , a set of excessive values noted  $EV_{\sigma}(G)$  is a set which contains a maximal number of values simultaneously alive

$$EV_{\sigma}(G) = vsa_{\sigma}(i) / RN_{\sigma}(G) = |vsa_{\sigma}(i)|$$

where i is a cycle where the maximum number of values simultaneously alive (register pressure) is achieved.

We call an **excessive clock cycle** a time when there is a maximum number of values simultaneously alive .

**Definition 2.3 (Excessive Clock Cycle)** Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$  and a schedule  $\sigma \in \Sigma(G)$ , an excessive clock cycle is an instant when there is a maximum number of values simultaneously alive:

t is an excessive clock cycle

$$\iff RN_{\sigma}(G) = |vsa_{\sigma}(t)|$$

As an example, a set of excessive values in the schedule described in Fig. 2.2.(1) of page 7 is  $\{a, b, d\}$  since they are the maximum number of values simultaneously alive . 9 is an excessive clock cycle since at this time there are 3 values simultaneously alive . Note that we can have more than one set of excessive values, since the register need can be defined with many sets of values simultaneously alive .

## 2.2.2 Register Allocation

A register allocation is a function that for a given schedule associates to each value a physical register to be stored in. Let R be the set of available registers.

**Definition 2.4 (Register Allocation)** Let  $G = (V, E, \delta, \delta_w, \delta_r)$  be a DDG and  $\sigma \in \Sigma(G)$  a schedule. A valid register allocation (noted alloc) is a function that associates to each value  $u \in V_R$  a physical register in alloc(u)  $\in R$  such that:

$$u \neq v, \ L_u^\sigma \cap L_v^\sigma \neq \phi \Longrightarrow alloc(u) \neq alloc(v)$$

We say that a register allocation *alloc* is **possible** according to  $\sigma$  if there are enough physical registers in R such that *alloc* is valid.

Given a schedule that needs no more than  $\mathcal{R}$  registers, its is easy to prove that a valid register allocation with  $\mathcal{R}$  available registers is possible. For this aim, we define the following DAG that models precedence relations between value's lifetimes intervals.

**Definition 2.5 (Value Lifetimes Precedence DAG)** Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$  and a schedule  $\sigma \in \Sigma(G)$ , a value's lifetime precedence DAG noted  $VLP_{\sigma}(G) = (V_R, E_{\prec})$  is defined by  $^1$ :

$$E_{\prec} = \{(u, v)/L_u^{\sigma} \prec L_v^{\sigma}\}$$

**Lemma 2.1** Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$  and a schedule  $\sigma \in \Sigma(G)$  with  $RN_{\sigma}(G) = \mathcal{R}$ , then there exists a possible register allocation according to  $\sigma$  with  $|R| = \mathcal{R}$  available registers.

$<sup>^{1}</sup>$ see  $\prec$  notation on page 2

Figure 2.2: Example of Register Allocation

#### Proof:

This lemma is trivial. To find a possible register allocation with  $\mathcal{R}$  available registers, we apply the following algorithm:

- 1. build  $VLP_{\sigma}(G)$  the value lifetime precedence DAG that reflects the precedence order between value's interval lifetimes;

- 2. find a minimal chain decomposition of  $VLP_{\sigma}(G)$  using Dilworth decomposition [CD73]: each chain is a list of successive and disjoint value's interval lifetimes. Since  $RN_{\sigma}(G) = \mathcal{R}$ , we are sure that there are exactly  $\mathcal{R}$  chains.

- 3. for each chain in the minimal decomposition, allocate a physical register from R to each value in this chain. In each chain, interval lifetimes do not interfere, thereby this allocation is valid. Also, we are sure that there are exactly  $\mathcal{R}$  chains, so we need exactly  $\mathcal{R}$  available registers.

\_

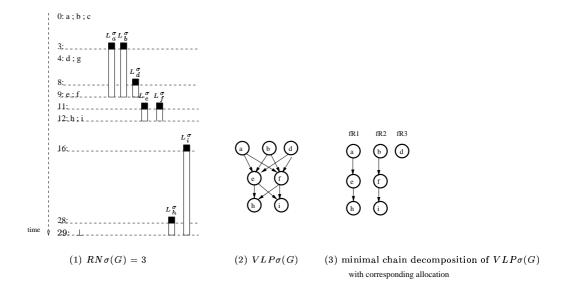

**Example 2.2.1** Part (1) of Fig. 2.2 shows a valid schedule of the DDG previously presented in Fig. 2.1 with a register need of 3 floating point registers. Part (2) is the value lifetimes precedence DAG after removing transitive arcs for clarity. A minimal chain decomposition and a possible register allocation with 3 floating point registers is given in Part (3).

## 2.2.3 Register Saturation Problem

The register saturation is the maximal register need for all valid schedules  $\sigma \in \Sigma(G)$ .

**Definition 2.6 (Register Saturation of a DDG)** Given  $DDGG = (V, E, \delta, \delta_w, \delta_r)$ , the register saturation RS(G) of G is defined as

$$RS(G) = \max_{\sigma \in \Sigma(G)} RN_{\sigma}(G)$$

We call  $\sigma$  a **saturating schedule** if  $RN_{\sigma}(G) = RS(G)$ , and we note  $\widehat{\Sigma}(G)$  the set of all saturating schedules. Also, a value is called **saturating** if it contributes to the register saturation, i.e. the clock cycle where the register need is saturated belongs to its lifetime interval:

$$\forall \sigma \in \widehat{\Sigma}(G)$$

u is a saturating value  $\iff \exists i \in L_u^{\sigma}, |vsa_{\sigma}(i)| = RS(G)$

In other words, a set of saturating values is only a set of excessive values in the case of a saturating schedule. Similarly, we call **saturated clock cycle** an excessive clock cycle in the case of saturating schedule.

In this section, we study how to compute RS(G). We will see that this problem comes down to answering the question "which operation must kill this value?" When looking for saturating schedules, we do not worry about the total schedule time. Our aim is only to prove that the register need can reach the register saturation but cannot exceed it. Minimizing the total schedule time is considered in Sect. 3 when we reduce the register saturation. Also for the purpose of building saturating schedules (to maximize the register need), looking for only one suitable killer of a value is sufficient rather than looking for a group of killers: for any schedule that assigns more than one killer for a value, we can build another schedule with at least the same register need such that this value is killed by only one consumer. We prove this assertion below. Let us begin by some definitions.

Since we do not assume any schedule for G, lifetime intervals are not defined so we cannot know at which date a value is killed. However, we can deduce which consumers in Cons(u) are impossible killers for the value u. If  $v_1, v_2 \in Cons(u)$  and  $\exists (v_1, v_2) \in E$ ,  $v_1$  is always scheduled before  $v_2$  with at least  $lat(v_1)$  processor cycles. Then  $v_1$  can never be the last read of u. For example, the consumer d in Fig. 2.1 can never kill the value b since it is always scheduled before f with at least 5 processor clock cycles. We consequently deduce which consumer can "potentially" kill a value (potential killers). We note  $pkill_G(u)$  the set of operations which can kill a value  $u \in V_R^2$ :

$$pkill_G(u) = \{v \in Cons(u)/ \downarrow v \cap Cons(u) = \{v\}\}$$

One can check that all operations in  $pkill_G(u)$  are parallel in G. We proved in [TT00] that any operation that does not belong to  $pkill_G(u)$  can never kill the value  $u^3$ .

**Theorem 2.1** Let  $G = (V, E, \delta, \delta_w, \delta_r)$  be a DDG and a schedule  $\sigma \in \Sigma(G)$ . If there is at least one excessive value that has more than one killer according to  $\sigma$ , then there exists another schedule  $\sigma' \in \Sigma(G)$  such that:

$$RN_{\sigma'}(G) \geq RN_{\sigma}(G)$$

and each excessive value is killed by a unique killer according to  $\sigma'$ .

<sup>&</sup>lt;sup>2</sup>see page 2 for definition of  $\downarrow$

<sup>&</sup>lt;sup>3</sup>in that proof, our assumption of strictly postive latencies is important

#### **Proof:**

We suppose that there exists a schedule  $\sigma \in \Sigma(G)$  with at least one excessive value that has more than one killer:

$$\exists \sigma \in \Sigma(G) \ \exists u \in EV_{\sigma}(G) \ |killers_{\sigma}(u)| > 1$$

We show in this proof how to build a new schedule  $\sigma' \in \Sigma(G)$  such that u is killed by a unique killer and  $\sigma'$  needs at least as many registers as  $\sigma$  does.

Suppose that u has j killers according to  $\sigma$ , and we note them:

$$killers_{\sigma}(u) = \{k_1, ..., k_j\}$$

with  $kill_{\sigma}(u) = \sigma(k_1) + \delta_r(k_1) = \cdots = \sigma(k_j) + \delta_r(k_j)$ . We choose one killer within this set to be the only one killer of u according to  $\sigma'$ , say  $k_1$ . We build  $\sigma'$  by "shifting" down  $k_1$  and all its descendants with a strictly positive factor, say 1:

$$\forall v \in V \quad \sigma'(v) = \begin{cases} \sigma(v) + 1 & \text{if } v \in \downarrow k_1 \\ \sigma(v) & \text{otherwise} \end{cases}$$

Now we prove that  $\sigma'$  is valid, needs at least as many registers as  $\sigma$  does, and  $k_1$  is the only killer of u according to  $\sigma'$ .

$\sigma'$  is valid: we can easily check that any dependence  $\forall e = (v_1, v_2) \in E$  is verified by  $\sigma'$ :

1. if both  $v_1, v_2 \not\in \downarrow k_1$ , then

$$\sigma'(v_2) - \sigma'(v_1) = \sigma(v_2) - \sigma(v_1) \ge \delta(e)$$

2. in the case when  $v_1 \notin \downarrow k_1 \land v_2 \in \downarrow k_1$

$$\sigma'(v_2) - \sigma'(v_1) = \sigma(v_2) + 1 - \sigma(v_1) > \delta(e)$$

- 3. the case of  $v_1 \in \downarrow k_1 \land v_2 \notin \downarrow k_1$  is impossible because the arc  $e = (v_1, v_2)$  exists;

- 4. in case when both  $v_1, v_2 \in \downarrow k_1$ , then

$$\sigma'(v_2) - \sigma'(v_1) = \sigma(v_2) + 1 - \sigma(v_1) - 1 \ge \delta(e)$$

$RN_{\sigma'} \geq RN_{\sigma}$ : let t be an excessive clock cycle according to  $\sigma$ , then all excessive values are simultaneously alive during t:

$$\forall v \in EV_{\sigma}(G) \qquad t \in L_{v}^{\sigma}$$

$$\Longrightarrow \forall v \in EV_{\sigma}(G) \qquad \sigma(v) + \delta_{w}(v) < t \leq kill_{\sigma}(v)$$

Here, we want to prove that these excessive values according to  $\sigma$  are still alive during t according to  $\sigma'$ . Any value  $v \in EV_{\sigma}(G)$  has the same definition date in  $\sigma'$  as in  $\sigma$ , this is because only  $\downarrow k_1$  nodes have been shifted down and:

$$\forall v \in EV_{\sigma}(G) - \{u\} \quad v \notin \downarrow k_1$$

otherwise  $L_u^{\sigma} \prec L_v^{\sigma}$  which is in contradiction with  $u, v \in EV_{\sigma}(G)$ . Then

$$\forall v \in EV_{\sigma}(G) \quad \sigma'(v) = \sigma(v)$$

However, the killing date of any excessive value  $v \in EV_{\sigma}(G)$  could be increased by the translation factor 1:

$$\forall v \in EV_{\sigma}(G) \quad kill_{\sigma}(v) \leq kill_{\sigma'}(v)$$

which gives

$$\forall v \in EV_{\sigma}(G) \quad \sigma'(v) < t \leq kill_{\sigma'}(v)$$

$$\Longrightarrow RN_{\sigma'} \ge |EV_{\sigma}(G)| = RN_{\sigma}(G)$$

$k_1$  is the only one killer of u: since  $k_1 \in pkill_G(u)$ , there is no other potential killer  $k \in pkill(u) \land k \neq k_1$  such that  $k \in \downarrow k_1$ . Otherwise,  $k_1$  cannot kill u (pkill operations property). In this case  $\sigma'(k) = \sigma(k)$  while  $\sigma'(k_1) = \sigma(k) + 1$ . We conclude

$$\forall k \in pkill_G(u) - \{k_1\} \quad \sigma'(k_1) + \delta_r(k_1) > \sigma'(k) + \delta_r(k) \Longrightarrow killers_{\sigma'}(u) = \{k_1\}$$

Finally, generalizing to arbitrary number of excessive values like u (those that have more than one killer and are simultaneously alive with u) is obviously done by iteratively building new  $\sigma'$  schedule for each of these values.

١

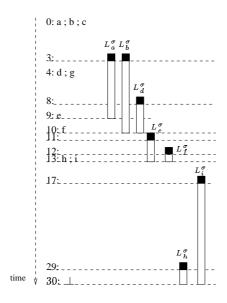

**Example 2.2.2** The excessive value b in the schedule presented in Fig. 2.2 in page 7 has two killers {e, f}. Let us choose f to be the only killer of b. A new schedule for this aim is presented in Fig. 2.3 where f and all its descendants are shifted down by one. The register need of this schedule is still equal to 3. One can remark that the definition date of each excessive value does not change, while the killing date of some excessive values (b and d) is shifted down by one. The new schedule ensures that each excessive values has a unique killer.

Corollary 2.1 Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$ , there is always a saturating schedule for G such that each saturating value has a unique killer.

Figure 2.3: Example for Theorem. 2.1 proof

### Proof:

It is a direct consequence of Theorem. 2.1. For any saturating schedule  $\sigma \in \widehat{\Sigma}(G)$  such that there exists some saturating values which have more than one killer, we can build a new schedule  $\sigma'$  where all saturating values are killed by a unique killer such that:

$$RS(G) \ge RN_{\sigma'}(G) \ge RN_{\sigma}(G) = RS(G) \Longrightarrow RN_{\sigma'}(G) = RS(G) \Longrightarrow \sigma' \in \widehat{\Sigma}(G)$$

\_

At this point, we have proven that to find a saturating schedule we can look for only one killer for each value. There may be more than one operation candidate for killing a value. Let us start by assuming a function that enforces an operation  $v \in pkill_G(u)$  to be the unique killer of  $u \in V_R$ .

**Definition 2.7 (Killing Function)** Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$ , a killing function k is defined by:

$$k: V_R \to pkill_G(u)$$

$$u \mapsto k(u)$$

If we assume that k(u) is the unique killer of  $u \in V_R$ , we must always verify the following assertion:

$\forall v \in pkill_G(u) - \{k(u)\}$

$$\sigma(v) + \delta_r(v) < \sigma(k(u)) + \delta_r(k(u))$$

(2.1)

There is a family of schedules that ensure this assertion. To define them, we extend G by new serial arcs that enforce all potential killing operations of each value u to be scheduled before k(u). This leads us to the following definition.

Figure 2.4: Valid Killing Function

**Definition 2.8 (DAG Associated to** k) Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$  and a killing function k, the extended DAG associated to k noted  $G_{\rightarrow k} = G \setminus^{E_k}$  is defined by:

$$E_{k} = \left\{ e = (v, k(u))/u \in V_{R} \quad v \in pkill_{G}(u) - \{k(u)\} \right\}$$

$$with \ \delta(e) = \delta_{r}(v) - \delta_{r}(k(u)) + 1$$

$$(2.2)$$

Then, any schedule  $\sigma \in \Sigma(G_{\to k})$  ensures that  $\forall u \in V_R$

$$\forall v \in pkill_G(u) - \{k(u)\} \quad \sigma(k(u)) + \delta_r(k(u)) > \sigma(v) + \delta_r(v)$$

The condition for the existence of such schedule gives the condition of a valid killing function:

k is a valid killing function  $\iff G_{\rightarrow k}$  is acyclic

Figure 2.4 gives an example of a valid killing function k. This function is shown by bold arcs in part (1), where each target kills its sources. Part (2) is the DAG associated to k.

Having a valid killing function k, we can deduce the values which can never be simultaneously alive for any  $\sigma \in \Sigma(G_{\to k})$ . Let  $\downarrow_R (u) = \downarrow u \cap V_R$  be the set of descendant values for  $u \in V$ , then any descendant value of k(u) can never be simultaneously alive with u, as stated in the following lemma.

**Lemma 2.2** Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$  and a valid killing function, then  $\forall u \in V_R$ :

1. the descendant values of k(u) cannot be simultaneously alive with u:

$$\forall \sigma \in \Sigma(G_{\to k}) \ \forall v \in \downarrow_R k(u) \quad L^u_\sigma \prec L^v_\sigma \tag{2.3}$$

2. other descendant values can be simultaneously alive with  $u, i.e. \exists \sigma \in \Sigma(G_{\rightarrow k})$ :

$$\forall v \in \left(\bigcup_{v' \in pkill_G(u)} \downarrow_R v'\right) - \downarrow_R k(u) \quad L^u_\sigma \cap L^v_\sigma \neq \phi \tag{2.4}$$

#### Proof:

Complete proof is given in [TT00], page 23.

\_

We define a DAG that models values which can never be simultaneously alive according to a killing function k.

**Definition 2.9 (Disjoint Value DAG)** Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$  and a valid killing function k, the disjoint value DAG of G associated to k, noted  $DV_k(G) = (V_R, E_{DV})$  is defined by:

$$E_{DV} = \{(u, v)/u, v \in V_R \land v \in \downarrow_R k(u)\}$$

Any arc (u, v) in  $DV_k(G)$  means that u's lifetime interval is always before v's lifetime interval according to any schedule of  $G_{\rightarrow k}$ , see part (3) of Fig. 2.4<sup>4</sup>. This definition permits us writing the following theorem.

**Theorem 2.2** Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$  and a valid killing function k then:

- $\forall \sigma \in \Sigma(G_{\to k}) : RN_{\sigma}(G) \leq |AM_k|$

- $\exists \sigma \in \Sigma(G_{\rightarrow k}) : RN_{\sigma}(G) = |AM_k|$

where  $AM_k$  is a maximal antichain in  $DV_k(G)$

#### Proof:

Complete proof is given in [TT00], page 18.

J

Theorem 2.2 allows us to rewrite the register saturation formula as

$$RS(G) = \max_{k \text{ a valid killing function}} |AM_k|$$

with  $AM_k$  a maximal antichain in  $DV_k(G)$ . We refer to the problem of finding such a killing function as the maximizing maximal antichain problem (MMA).

**Definition 2.10 (MMA Problem)** Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$ , find a valid killing function k such that:

$$\forall k' \ a \ valid \ killing \ function \ of \ G: |AM_k| > |AM_{k'}|$$

with  $AM_k$  and  $AM_{k'}$  two maximal antichains in  $DV_k(G)$  and  $DV_{k'}(G)$  respectively.

We call each solution for the MMA problem a **saturating killing function**, and  $AM_k$  are **saturating values**. Note that there may be more than one maximal antichain, and then we can have more than one set of saturating values. We search for only one such set, which is sufficient for our purpose. Unfortunately, finding a saturating killing function is NP-complete [TT00].

$<sup>^4\</sup>mathrm{We}$  can simplify this DAG by taking only its transitive reduction

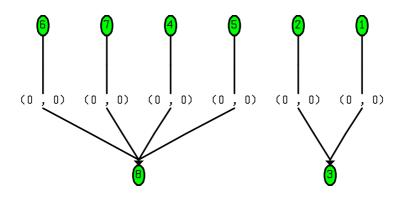

Figure 2.5: Potential Killing DAG

## 2.2.4 A Heuristic for Computing RS

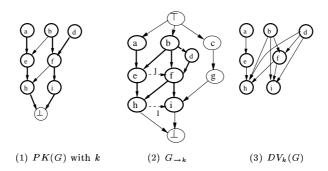

Since finding a saturating killing function is NP-complete, this section presents our heuristics to approximate an optimal k by another valid killing function  $k^*$ . We have to choose a killing operation for each value such that we maximize the parallel values in  $DV_k(G)$ . For this aim, we build a **potential killing DAG** of G, noted  $PK(G) = (V, E_{PK})$ , to model potential killing relations between operations, (see Fig. 2.5), where:

$$E_{PK} = \{(u, v) / u \in V_R \land v \in pkill_G(u)\}$$

We have to choose such a killing operation from the value's potential killing set since we have proven that only potential killers can kill that value  $^5$ . Our heuristics focus on the potential killing DAG PK(G), starting from source nodes to sinks. Our aim is to select a group of killing operations for a group of parents to keep as many descendant values alive as possible. The main steps of our heuristics are:

- 1. decompose the potential killing DAG PK(G) into connected bipartite components;

- 2. for each bipartite component, search for the best saturating killing set (defined below);

- 3. choose a killing operation within the saturating killing set (defined below).

We decompose the potential killing DAG into connected bipartite components (CBC) in order to choose a common saturating killing set for a group of parents. Our purpose is to have a maximum number of children and their descendants values simultaneously alive with their parents values.

**Definition 2.11 (Connected Bipartite Component)** Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$ , a connected bipartite component  $cb = (S_{cb}, T_{cb}, E_{cb})$  of its potential killing DAG  $PK(G) = (V, E_{PK})$  is defined by:

- $E_{cb} \subseteq E_{PK}$  arcs are potential killing relations;

- $cb = (S_{cb}, T_{cb}, E_{cb})$  is connected:  $\forall e_1, e_n \in E_{cb}$

$$\exists \ a \ list \ (e_1, \ldots, e_n) \quad e_i \ and \ e_{i+1} \ are \ adjacent$$

• any arc  $e \in E_{PK}$  adjacent to an arc  $e' \in E_{cb}$  also belongs to  $E_{cb}$ :

$$\forall e \in E_{PK} \ \exists e' \in E_{cb} / \ e, e' \ are \ adjacent \Longrightarrow e \in E_{cb}$$

<sup>&</sup>lt;sup>5</sup>here, our assumption that operation latencies must be strictly positive is important to prove this assertion

Figure 2.6: Bipartite Decomposition

- $S_{cb} = \{ s \in V_R / \exists e \in E_{cb} \land s = source(e) \}$  parent values;

- $T_{cb} = \{t \in V \mid \exists e \in E_{cb} \land s = target(e)\}\ children\ nodes\ (potential\ killing\ operations);$

- $cb = (S_{cb}, T_{cb}, E_{cb})$  is bipartite:

$$\nexists e, e' \in E_{cb} \quad target(e) = source(e')$$

A bipartite decomposition of the potential killing graph PK(G) is the set

$$\mathcal{B}(G) = \{cb = (S_{cb}, T_{cb}, E_{cb}) / \forall e \in E_{PK} \exists cb \in \mathcal{B}(G) : e \in E_{cb}\}$$

According to Def. 2.11, there exists only one bipartite decomposition<sup>6</sup>  $\mathcal{B}(G)$  for G (see Fig. 2.6) and

$$\forall cb \in \mathcal{B}(G) \ \forall s, s' \in S_{cb} \ \forall t, t' \in T_{cb} \ s||s' \wedge t||t' \ \text{in } PK(G)$$

A saturating killing set SKS(cb) of a bipartite component  $cb = (S_{cb}, T_{cb}, E_{cb})$  is a subset  $T'_{cb} \subseteq T_{cb}$  such that if we choose a killing operation from this subset, then we get a maximal number of descendant values of children in  $T_{cb}$  simultaneously alive with parent values in  $S_{cb}$ .

**Definition 2.12 (Saturating Killing Set)** Given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$ , a saturating killing set SKS(cb) of a connected bipartite component  $cb \in \mathcal{B}(G)$  is a subset  $T'_{cb} \subseteq T_{cb}$ , such that:

1. killing constraints: all parents in  $S_{cb}$  must be potentially killed by at least one child in  $T'_{cb}$

$$\bigcup_{t \in T'_{cb}} \Gamma^-_{cb}(t) = S_{cb}$$

2. minimizing the number of descendant values of  $T'_{cb}$

$$\min | \bigcup_{t \in T'_{cb}} \downarrow_R t |$$

However, given a DDG  $G = (V, E, \delta, \delta_w, \delta_r)$  and a connected bipartite component  $cb \in \mathcal{B}(G)$ , computing SKS(cb) is NP-complete [TT00].

<sup>&</sup>lt;sup>6</sup>A proof of this assertion is given in [TT00], page 29.

#### **Algorithm 1** Greedy-k: a Heuristic for MMA Problem

```

Require: a DDG G = (V, E, \delta, \delta_w, \delta_r)

for all values u \in V_R do

k^*(u) = \bot {all values are initially non killed}

end for

build \mathcal{B}(G) the bipartite decomposition of PK(G).

for all bipartite component cb = (S_{cb}, T_{cb}, E_{cb}) \in \mathcal{B}(G) do

X := S_{cb} {all parents are initially uncovered}

Y := \phi {initially, no cumulated descendant values}

SKS^*(cb) := \phi

while X \neq \phi do {build the SKS for cb}

select the child t \in T_{cb} with the maximal cost \rho_{X,Y}(t)

SKS^*(cb) := SKS^*(cb) \cup \{t\}

X := X - \Gamma_{cb}^{-}(t) {remove covered parents}

Y := Y \cup \downarrow_R t {update the cumulated descendent values}

end while

for all t \in SKS^*(cb) do {in decreasing cost order}

for all parent s \in \Gamma_{cb}^-(t) do

if k^*(s) = \bot then {kill non killed parents of t}

k^*(s) := t

end if

end for

end for

end for

```

A Heuristic for Finding a SKS Intuitively, we should choose a subset of children in bipartite component that would kill the greatest number of parents while minimizing the number of descendant values. For this aim, we define a cost function  $\rho$  that permits us to choose the best candidate child. Given a bipartite component  $cb = (S_{cb}, T_{cb}, E_{cb})$  and a set Y of (cumulated) descendant values and a set X of non (yet) killed parents, the cost of a child  $t \in T_{cb}$  is:

$$\rho_{X,Y}(t) = \begin{cases} \frac{|\Gamma_{cb}^-(t) \cap X|}{|\downarrow_R t \cup Y|} & \text{if } \downarrow_R t \cup Y \neq \phi \\ |\Gamma_{cb}^-(t) \cap X| & \text{otherwise} \end{cases}$$

The first case enables us to select the child that covers the most non killed parents with the minimum descendant values. If there is no descendant value, then we choose the child which covers the most non killed parents.

Algorithm 1 is a modified greedy heuristic that searches for an approximation  $SKS^*$  and computes a killing function  $k^*$  in polynomial complexity. Our heuristic has the following properties (proven in [TT00]):.

- 1. Greedy-k always produces a valid killing function  $k^*$ ;

- 2. PK(G) is an inverted tree  $\Longrightarrow$  Greedy-k gives an optimal solution for the MMA problem.

To summarize this section, here are our steps to compute the register saturation:

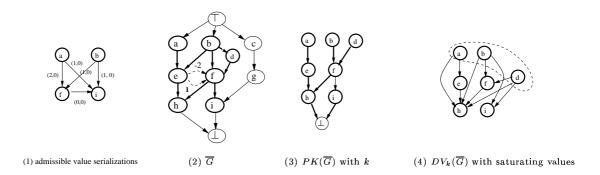

Figure 2.7: Example of Register Saturation Computing

- 1. apply Greedy-k on G. The result is a valid killing function  $k^*$ ;

- 2. construct the disjoint value DAG  $DV_{k^*}(G)$ ;

- 3. find a maximal antichain  $AM_{k^*}$  of  $DV_{k^*}(G)$  using Dilworth decomposition (minimal chain decomposition [CD73]); saturating values are then  $AM_{k^*}$  and  $RS^*(G) = |AM_{k^*}| \leq RS_k(G)^7$

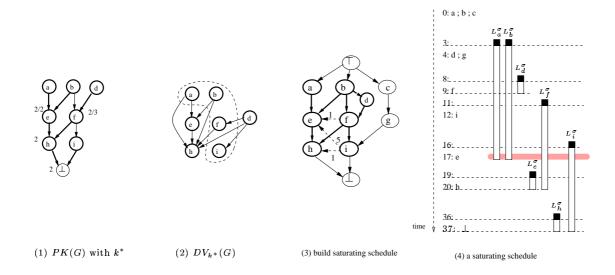

**Example 2.2.3** Figure 2.7 gives an example to summarize how we compute the register saturation. Part (1) gives a saturating killing function  $k^*$  computed by Greedy-k: bold arcs denotes that each target kills its sources. Each killer is labeled by its cost  $\rho$ . Part (2) gives the disjoint value DAG associated to  $k^*$ . Saturating values are  $\{a, b, f, i\}$ , so  $RS^*(G) = 4$  floating point registers. Part (3) shows an extended DAG of  $G_{\rightarrow k^*}$  to build saturating schedules: we must enforce saturating values to be simultaneously alive<sup>8</sup>. Any schedule of this DAG needs 4 registers: a saturating schedule is given in part (4).

## 2.3 Optimal Register Saturation Computation

In this section, we formalize the problem of computing the optimal register saturation using linear algebra. We build integer linear programming models to find saturating schedules  $\hat{\sigma} \in \hat{\Sigma}(G)$ , and then we deduce  $RS = RN_{\hat{\sigma}}(G)$ . Modeling scheduling problem using integer linear programming has been studied in [Saw97, GAG94, WKE95, Alt95, NG93]. We adapt their models to take into account register saturation and values simultaneously alive with delayed read/write from and into registers. We begin by recalling what is integer linear programming.

$<sup>^7\</sup>mathrm{emperical}$  introduced error by our heuristics is studied in Sect. 5

<sup>&</sup>lt;sup>8</sup>A proven correct algorithm is provided for this purpose in [TT00], page 20.

## 2.3.1 Integer Linear Programming

It is mainly used to formalize combinatory problems [Bea96, BT97, CCPS98]. An integer linear programming problem  $(P_{IL})$  consists in finding the maximum of a certain linear function under linear constraints. Formally, it is solving the following problem<sup>9</sup> (standard formulation):

$$(P_{IL}) \begin{cases} \text{Maximize (or Minimize)} z = c \cdot x & \text{objective function} \\ A \cdot x = b & \text{integer constraints} \\ x \in \mathbb{N}^n & \text{integer variables} \end{cases}$$

where A is an  $(m \times n)$  integer matrix, and b an m-vector. In general, finding an exact solution of IL problems is NP-complete [Bea96]. For resolution techniques, we invite readers to refer to [CCPS98].

## 2.3.2 Exact Register Saturation Problem Modeling

In this section, we consider a DAG  $G = (V, E, \delta, \delta_w, \delta_r)$  and write an integer linear programming model to compute the optimal RS. Operation latencies are integers<sup>10</sup>, and the arcs can be either flow dependencies or any other serial constraints<sup>11</sup>. We keep the notation of  $V_R$  and  $E_R$  which are the set of values and the set of flow arcs resp. Let us start by writing and defining some linear programming techniques.

#### Some Linear Programming Techniques

In this section, we define how to express some logical expression with linear programming techniques.

Expressing Boolean Operators with Linear Constraints Intrinsically, an integer LP problem defines the two boolean operators  $\wedge$  and  $\neg$ :

• having two constraints matrix A and A' with dimensions  $(m \times n)$  and  $(m' \times n)$ , saying that x must be a solution for both of them is modeled by defining an aggregated matrix  $\hat{A}$  of dimension  $(m + m') \times n$  where:

$$\hat{A} = \left(\begin{array}{c} A \\ A' \end{array}\right)$$

- having a linear constraint  $f(x) \ge b$ , saying that x must not verify the condition  $f(x) \ge b$  is modeled by setting f(x) < b.

- having a constraints matrix A with m lines (m linear constraints  $f_1, f_2, \dots, f_m$ ), saying that x must not verify  $Ax \geq b$  is modeled by:

$$f_1(x) < b_1 \lor f_2(x) < b_2 \lor \cdots \lor f_m(x) < b_m$$

In [GN72], the authors show how to model the disjunctive operator  $\vee$ . Consider the problem:

<sup>&</sup>lt;sup>9</sup>This formulation can be written using inequality constraints  $(\geq, \leq, >, <)$ .

<sup>&</sup>lt;sup>10</sup>we release the constraint that assume strictly positive latencies.

<sup>&</sup>lt;sup>11</sup>with possibly negative specified latencies.

- 1. maximize  $f(x), x \in \mathcal{D}$  ( $\mathcal{D}$  is the domain set of x)

- 2. subject to

$$\begin{pmatrix} g_1(x) \ge 0 \\ g_2(x) \ge 0 \\ \vdots \\ g_m(x) \ge 0 \end{pmatrix} \mathbf{or} \begin{pmatrix} h_1(x) \ge 0 \\ h_2(x) \ge 0 \\ \vdots \\ h_{m'}(x) \ge 0 \end{pmatrix}$$

By introducing a binary variable  $\alpha \in \{0, 1\}$ , this disjunction is equivalent to:

$$\begin{cases} g_1(x) \ge \alpha \underline{g_1} \\ g_2(x) \ge \alpha \underline{g_2} \\ \vdots \\ g_m(x) \ge \alpha \underline{g_m} \\ h_1(x) \ge (1 - \alpha) \underline{h_1} \\ h_2(x) \ge (1 - \alpha) \underline{h_2} \\ \vdots \\ h_{m'}(x) \ge (1 - \alpha) \underline{h_{m'}} \\ \alpha \in \{0, 1\} \end{cases}$$

where  $g_i \neq 0$  and  $\underline{h_i} \neq 0$  are two known non null finite lower bounds for  $g_i$  and  $h_i$  resp.

In our integer LP model, we will need to express the disjunctive formula with three linear constraints:

$$f_1(x) \ge 0 \ \lor \ f_2(x) \ge 0 \ \lor \ f_3(x) \ge 0 \ \sim \ (f_1(x) \ge 0 \ \lor \ f_2(x) \ge 0) \ \lor \ f_3(x) \ge 0$$

We introduce a boolean binary variable  $h \in \{0, 1\}$  to express the first dichotomy:

$$\left\{ \begin{array}{l} f_1(x) - h \underline{f_1} \ge 0 \\ f_2(x) - (1 - h) \underline{f_2} \ge 0 \\ h \in \{0, 1\} \end{array} \right\} \lor f_3(x) \ge 0$$

where  $\underline{f_1}$  and  $\underline{f_2}$  are two non null finite lower bounds of  $f_1$  and  $f_2$  resp. To express the last dichotomy, we introduce a second boolean binary variable  $h' \in \{0, 1\}$ :

$$\begin{cases} f_1(x) - h\underline{f_1} \ge h' \times \underline{f_1'} \\ f_2(x) - (1-h)\underline{f_2} \ge h' \times \underline{f_2'} \\ f_3(x) \ge (1-h')\underline{f_3} \\ h, h' \in \{0, 1\} \end{cases}$$

where  $(\underline{f_1'}, \underline{f_2'}, \underline{f_3})$  are finite non null lower bounds for  $(f_1 - h\underline{f_1}, f_2 - (1-h)\underline{f_2}, f_3)$  resp. We can chose  $(\underline{f_1'} = min(-1, \underline{f_1}))$  as a finite non null lower bound for  $f_1 - h\underline{f_1}$  because:

$$\left. \begin{array}{l} f_1(x) \geq \underline{f_1} \\ h \in \{0, 1\} \end{array} \right\} \Longrightarrow \left\{ \begin{array}{l} f_1(x) - h\underline{f_1} = f_1(x) \geq \underline{f_1} \text{ if } h = 0 \\ f_1(x) - h\overline{f_1} = f_1(x) - \overline{f_1} \geq 0 \text{ if } h = 1 \end{array} \right.$$

Figure 2.8: Expressing an n-Disjunction with Linear Constraints

Since  $(f_1' \neq 0)$ , this leads to:

$$f_1(x) - h\underline{f_1} \ge min(-1, \underline{f_1})$$

As the same manner, we set a lower bound  $(f_2' = min(-1, \underline{f_2}))$  for  $f_2 - h\underline{f_2}$ .

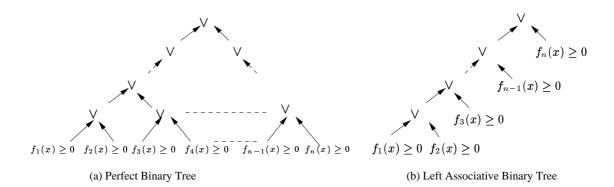

We can also generalize to arbitrary number of constraints in a disjunctive formula  $\vee_n$ :

$$\forall_n (f_1, \dots, f_n) = (f_1(x) \ge 0 \ \lor \ f_2(x) \ge 0 \lor \dots \lor \ f_n(x) \ge 0)$$

Since the dichotomy operator  $\vee$  is associative, we group the constraints two by two by using a binary tree. We can either express  $\vee_n$  by grouping the constraints using a perfect binary tree as shown in Fig. 2.8.(a), or using a left associative binary tree as shown in Fig. 2.8.(b). With both techniques, there is (n-1) internal  $\vee$  operators which need to define (n-1) boolean variables  $(h_1, \dots, h_{n-1})$ . The final constraints system to express  $\vee_n$  has  $\mathcal{O}(n)$  constraints  $(f_1, \dots, f_n)$  and  $\mathcal{O}(n-1)$  boolean binary variables  $(h_1, \dots, h_{n-1})$ . The non null lower bounds of the linear functions are always finite. They always can be computed statically and propagated up in the binary tree, as explained in the following example.

**Example 2.3.1** Let us express  $f_1(x) \ge 0 \lor f_2(x) \ge 0 \lor f_3(x) \ge 0 \lor f_4(x) \ge 0$ . This system is written by expressing the first two disjunctions (as explained above):

$$\left\{

\begin{array}{l}

f_1(x) - h_1 \underline{f_1} - h_2 \times min(-1, \underline{f_1}) \ge 0 \\

f_2(x) - (1 - h_1) \underline{f_2} - h_2 \times min(-1, \underline{f_2}) \ge 0 \\

f_3(x) - (1 - h_2) \underline{f_3} \ge 0 \\

h_1, h_2 \in \{0, 1\}

\end{array}

\right\} \mathbf{or} \ f_4(x) \ge 0$$

where  $\underline{f_1}, \underline{f_2}$  are two known non null finite lower bounds for  $f_1, f_2$  resp. We introduce a third binary variable  $h_3 \in \{0, 1\}$  to write the last disjunction in linear constraints:

$$\left\{ \begin{array}{l} \{0,1\} \ \ to \ \ write \ \ the \ \ last \ \ disjunction \ \ in \ \ linear \ \ constraints \\ \left\{ \begin{array}{l} f_1(x) - h_1\underline{f_1} - h_2 \times min(-1,\underline{f_1}) \geq h_3 \times \underline{f_1'} \\ f_2(x) - (1-h_1)\underline{f_2} - h_2 \times min(-1,\underline{f_2}) \geq h_3 \times \underline{f_2'} \\ f_3(x) - (1-h_2)\underline{f_3} \geq h_3 \times \underline{f_3'} \\ f_4(x) \geq (1-h_3) \times \underline{f_4} \\ h_1,h_2,h_3 \in \{0,1\} \end{array} \right.$$

where  $(\underline{f_1'},\underline{f_2'},\underline{f_3'},\underline{f_4})$  are the finite non null lower bounds for  $(f_1(x)-h_1\underline{f_1}-h_2\times min(-1,\underline{f_1}),\ f_2(x)-(1-h_1)\underline{f_2}-h_2\times min(-1,\underline{f_2}),\ f_3(x)-(1-h_2)\underline{f_3},\ f_4)$  resp.

We can chose  $(\underline{f'_1} = min(-1, \underline{f_1}))$  because:

$$f_1(x) - h_1 \underline{f_1} - h_2 \times min(-1, \underline{f_1}) = \begin{cases} f_1(x) - h_1 \underline{f_1} \ge min(-1, \underline{f_1}) & \text{if } h_2 = 0 \\ f_1(x) - h_1 \underline{f_1} - min(-1, \underline{f_1}) \ge 0 & \text{if } h_2 = 1 \end{cases}$$

Since  $min(-1, \underline{f_1})$  is negative, we set  $(\underline{f'_1} = min(-1, \underline{f_1}))$  as suitable lower bound. We chose the lower bounds for the other constraints as the same manner:

$$\frac{f_2'}{f_3'} = min(-1, \underline{f_2})$$

$$\underline{f_3'} = min(-1, \underline{f_3})$$

Since we know how to model  $(\neg, \land, \lor)$ , we can easily deduce the linear constraints of any other logical operator. Let  $g(x) \ge 0$  and  $h(x) \ge 0$  be two linear constraints on x:

- 1.  $g(x) \ge 0 \Longrightarrow h(x) \ge 0$  can be modeled by  $g(x) < 0 \lor h(x) \ge 0$

- 2.  $g(x) \ge 0 \iff h(x) \ge 0$  can be modeled by

$$(g(x) \ge 0 \land h(x) \ge 0) \lor (h(x) < 0 \land g(x) < 0)$$

The problem  $g(x) \ge 0 \Longrightarrow h(x) \ge 0$  becomes  $(-g(x) + 1 \ge 0 \lor h(x) \ge 0)$ . Thereby, it can be written using the dichotomy expression:

$$\begin{cases} -g(x) + 1 \ge \alpha \underline{g} \\ h(x) \ge (1 - \alpha)\underline{h} \\ \alpha \in \{0, 1\} \end{cases}$$

where  $\underline{g}$  and  $\underline{h}$  are two known non null finite lower bounds for (-g+1) and h respectively.

The problem  $g(x) \ge 0 \iff h(x) \ge 0$  becomes

$$\left(g(x) \geq 0 \land h(x) \geq 0\right) \lor \left(-g(x) + 1 \geq 0 \land -h(x) + 1 \geq 0\right)$$

and can be written using the dichotomy expression:

$$\begin{cases} g(x) \ge \alpha \underline{g} \\ h(x) \ge \alpha \underline{g} \\ -g(x) + 1 \ge (1 - \alpha) \underline{g'} \\ -h(x) + 1 \ge (1 - \alpha) \underline{h'} \\ \alpha \in \{0, 1\} \end{cases}$$

where  $\underline{g}$  and  $\underline{h}$  are two known non null finite lower bounds for g and h respectively, and  $\underline{g}'$  and  $\underline{h}'$  are two known non null finite lower bounds for (-g+1) and (-h+1) resp.

### Expressing the "maximum" with Linear Constraints

By using the linear constraints which describe the logical operators explained above, we can express some non linear functions with linear constraints. For instance, the function z = max(x, y) can be modeled by both the constraints:

$$\begin{cases} (x - y \ge 0) \Longrightarrow z = x \\ (y - x \ge 0) \Longrightarrow z = y \end{cases}$$

Note that z=x is equivalent to  $z-x\geq 0 \land x-z\geq 0$ , and thereby max can be written as the following problem using the dichotomy expression:

$$\left((x-y\geq 0)\Longrightarrow (z-x\geq 0 \land x-z\geq 0)\right) \text{ is written } \begin{cases} -x+y+1\geq \alpha_1\underline{g_1}\\ z-x\geq (1-\alpha_1)\underline{h_1}\\ x-z\geq (1-\alpha_1)\underline{h_2}\\ \alpha_1\in\{0,1\} \end{cases}$$

$$\left( (y-x \geq 0) \Longrightarrow (z-y \geq 0 \land y-z \geq 0) \right) \text{ is written } \begin{cases} -y+x+1 \geq \alpha_2 \underline{g_2} \\ z-y \geq (1-\alpha_2) \underline{h_3} \\ y-z \geq (1-\alpha_2) \underline{h_4} \\ \alpha_2 \in \{0,1\} \end{cases}$$

where  $(\underline{g_1}, \underline{h_1}, \underline{h_2}, \underline{g_2}, \underline{h_3}, \underline{h_4})$  are the finite non null lower bounds for (-x+y+1, z-x, x-z, -y+x+1, z-y, y-z) resp. So we need 6 linear inequalities and two boolean variables to express max(x, y).

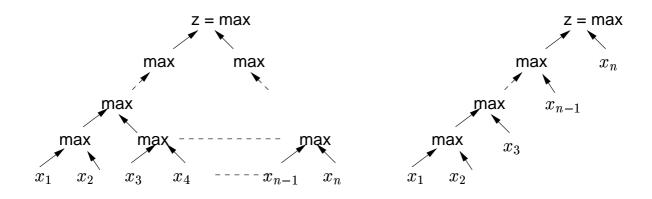

We can also express the  $max_n$  function with arbitrary number of parameters  $z = max_n(x_1, x_2, \cdots, x_n)$ . Since max is associative, we use a perfect binary tree (by grouping parameters from left to right) to compute the maximum of n variables in  $log_2(n)$  steps. The binary tree is shown in Fig. 2.9.(a): each parameter is a leaf and each couple (x, y) is connected by a max(x, y) node. We connect also each two internal nodes by a max operator as explained in the figure. We can also use a left associative binary tree as shown in Fig. 2.9.(b). With both techniques, the number of internal nodes including the root is equal to n-1, so we need to define n-2 intermediate variables (that hold intermediate maximums) and (n-1) systems to compute max operators. Which leads to a complexity of  $\mathcal{O}(n-2) = \mathcal{O}(n)$  intermediate variables and  $\mathcal{O}(6 \times (n-1)) = \mathcal{O}(n)$  linear constraints (each max operator needs 6 linear constraints to be defined) and  $\mathcal{O}(2n-2) = \mathcal{O}(n)$  booleans (each max operator needs 1 boolean). The total complexity of expressing  $max_n$  with linear constraints is  $\mathcal{O}(n)$  variables and  $\mathcal{O}(n)$  linear constraints. The general form of  $max_n$  operator using a left associative binary tree technique is:

$$\begin{cases} y_1 = max(x_1, x_2) \\ y_2 = max(y_1, x_3) \\ \vdots \\ y_{n-2} = max(y_{n-3}, x_{n-1}) \\ z = max(y_{n-2}, x_n) \end{cases}$$

where each max operator consists in 4 conjunctive linear constraints.

The non null lower bounds of the linear functions are always finite if the domain sets of the

(a) Perfect Binary Tree

(b) Left Associative Binary Tree

Figure 2.9: Expressing  $max_n$  Operator with Linear Constraints

variables  $x_i$  is bounded. They always can be computed statically and propagated up in the binary tree, as explained in the following example.

**Example 2.3.2** Let us write the following system  $(z = max(x_1, x_2, x_3))$  with linear constraints;

$$\begin{cases} y = max(x_1, x_2) \\ z = max(y, x_3) \end{cases}$$

By replacing the formulas of max operators and introducing 4 binary variables  $h_i \in \{0, 1\}$ , we get:

```

\begin{cases} -x_1 + x_2 + 1 \ge h_1 \underline{g_1} & \text{with } \underline{g_1} \text{ a lower bound for } -x_1 + x_2 + 1 \\ y - x_1 \ge (1 - h_1) \underline{g_2} & \text{with } \underline{g_2} \text{ a lower bound for } y - x_1 \\ x_1 - y \ge (1 - h_1) \underline{g_3} & \text{with } \underline{g_3} \text{ a lower bound for } x_1 - y \\ -x_2 + x_1 + 1 \ge h_2 \underline{g_4} & \text{with } \underline{g_4} \text{ a lower bound for } -x_2 + x_1 + 1 \\ y - x_2 \ge (1 - h_2) \underline{g_5} & \text{with } \underline{g_5} \text{ a lower bound for } y - x_2 \\ x_2 - y \ge (1 - h_2) \underline{g_6} & \text{with } \underline{g_6} \text{ a lower bound for } x_2 - y \\ h_1, h_2 \in \{0, 1\} \end{cases}

\begin{cases} -x_1 + x_2 + 1 \ge h_1 \underline{g_4} & \text{with } \underline{g_5} \text{ a lower bound for } -x_1 + x_2 + 1 \\ y - x_2 \ge (1 - h_2) \underline{g_5} & \text{with } \underline{g_5} \text{ a lower bound for } y - x_2 \\ x_2 - y \ge (1 - h_3) \underline{f_2} & \text{with } \underline{f_1} \text{ a lower bound for } -y + x_3 + 1 \\ z - y \ge (1 - h_3) \underline{f_2} & \text{with } \underline{f_2} \text{ a lower bound for } y - z \\ -x_3 + y + 1 \ge h_4 \underline{f_4} & \text{with } \underline{f_5} \text{ a lower bound for } -x_3 + y + 1 \\ z - x_3 \ge (1 - h_4) \underline{f_5} & \text{with } \underline{f_5} \text{ a lower bound for } x_3 - z \\ h_3, h_4 \in \{0, 1\} \end{cases}

```

Computing the finite non null lower bounds  $g_i$  and  $f_i$  is obvious if the domain sets of  $x_1, x_2, x_3$  is bounded. If  $(\underline{x_1}, \underline{x_2}, \underline{x_3})$  are the three lower bounds of  $(x_1, x_2, x_3)$ , then  $\underline{y} = min(\underline{x_1}, \underline{x_2})$  is a lower bound for  $\underline{y}$  and  $\underline{z} = min(x_1, x_2, x_3)$  is a lower bound for  $\underline{z}$ . Deducing the lower bounds  $g_i$

and  $f_i$  is statically done by taking into account both the finite lower bounds  $\underline{x_i}$  and upper bounds  $\bar{x_i}$ . For instance:

$$\frac{\underline{x}_1 \le x_1 \le \bar{x}_1}{\underline{x}_2 \le x_2 \le \bar{x}_2} \right\} \Longrightarrow -x_2 + x_1 + 1 \ge \underline{g_1} = \underline{x_1} - \bar{x}_2 + 1$$

A direct and better linear formulation of z = max(x, y) with only one binary variable  $\alpha$  and 4 linear constraints using upper bounds is:

$$\begin{cases} z \ge x \\ z \ge y \\ z \le (1 - \alpha)x + \alpha \bar{y} \\ z \le \alpha y + (1 - \alpha)\bar{x} \end{cases}$$

where  $(\bar{x}, \bar{y})$  are two finite non null upper bounds for x, y resp. We can use this formulation to express  $max_n$  with less constraints and boolean variables, but we need to define upper bounds rather than lower bounds. We can chose one of the two formulations of max depending if we are able to define statically lower or upper bounds of the variables.

All logical operators defined above will be used in our optimal RS formulation. For the aim of building this later, we will need further to express the problem consisting in finding the maximal independent set in an undirected graph as explained below.

### Maximal Independent Set

Given an undirected graph  $H = (\mathcal{N}, \mathcal{E})$  where  $\mathcal{N}$  is a set of nodes and  $\mathcal{E}$  is a set of undirected edges, an independent set is a subset of  $\mathcal{N}$  such that there is no two adjacent nodes. Finding a maximal independent set can be formulated by [BT97]:

- we define a binary variable  $x_i \in \{0,1\}$  for each node i.  $x_i = 1$  iff the node i belongs to the maximal independent set.

- the objective function is to maximize number of non adjacent nodes

Maximize

$$\sum_{i \in \mathcal{N}} x_i$$

• subject to:

$$\forall (i,j) \in \mathcal{E}$$

$x_i + x_j \le 1$

#### Optimal RS Integer LP Model

We recall that the purpose of our model is to find a valid schedule such that the register need is maximal. In this section, we show how to generate an integer LP model with  $\mathcal{O}(|V|^2)$  variables and  $\mathcal{O}(|E| + |V|^2)$  constraints to compute the optimal RS.

Schedule Variables and Constraints In our model, we define for each operation  $u \in V$  the integer schedule variable  $\sigma_u \in \mathbb{N}$ . The scheduling constraints are written:

$$\forall e = (u, v) \in E \qquad \sigma_v - \sigma_u \ge \delta(e)$$

There is  $\mathcal{O}(|V|)$  schedule variables and  $\mathcal{O}(|E|)$  scheduling constraints.

To make the domain of our scheduling variables bounded, we assume a worst total schedule time  $L_{max}$  taken sufficiently large, where for instance  $L_{max} = \sum_{u \in V} lat(u)$  is a suitable worst case total schedule time. And then, we write the constraint  $\sigma_{\perp} \leq L_{max}$ . This constraint imply necessarily that:

$$\forall u \in V \qquad \sigma_u \leq L_{max}$$

Values Simultaneously Alive The lifetime interval of a value u is

$$L_u^{\sigma} = ]\sigma_u + \delta_w(u), \max_{v \in Cons(u)} \sigma_v + \delta_r(v)]$$

We define for each value the variable that computes its killing date  $k_u = \max_{v \in Cons(u)} \sigma_v + \delta_r(v)$ . The number of such defined variables is  $\mathcal{O}(|V_R|)$ .

We use the  $max_n$  linear modeling to compute  $k_u$ : we need to define for each  $k_u \mathcal{O}(|Cons(u)|)$  intermediate variables and  $\mathcal{O}(|Cons(u)|)$  linear constraints to compute it (see  $max_n$  linear constraints). The total complexity to define all killing dates is bounded by  $\mathcal{O}(|V_R|^2)$  variables and  $\mathcal{O}(|V_R|^2)$  constraints.

Now, we define for each couple of values (u, v) with  $u \neq v$  a binary variable  $s_{u,v} \in \{0, 1\}$  such that  $s_{u,v} = 1$  iff u and v are simultaneously alive. The number of such variables is the number combinations of 2 values within  $|V_R|$ , i.e.  $(|V_R| \times (|V_R| - 1))/2$ .

To express to fact that  $s_{u,v} = 1$  iff u and v are simultaneously alive, we need to express the following constraints:

$$s_{u,v} = 1 \iff \neg (L_u^{\sigma} \prec L_v^{\sigma} \lor L_v^{\sigma} \prec L_u^{\sigma})$$

since  $s_{u,v} \in \{0,1\}$ , this constraint is equivalent to

$$s_{u,v} \geq 1 \Longleftrightarrow \neg (L_u^\sigma \prec L_v^\sigma) \ \land \ \neg (L_v^\sigma \prec L_u^\sigma)$$

We know that  $L_u^{\sigma} \prec L_v^{\sigma}$  iff  $k_u \leq \sigma_v + \delta_w(v)$ . Then, we have to write;

$$s_{u,v} \ge 1 \Longleftrightarrow \begin{cases} k_u > \sigma_v + \delta_w(v) \\ k_v > \sigma_u + \delta_w(u) \end{cases}$$

Which is equivalent to

$$s_{u,v} \ge 1 \Longleftrightarrow \begin{cases} k_u - \sigma_v - \delta_w(v) - 1 \ge 0 \\ k_v - \sigma_u - \delta_w(u) - 1 \ge 0 \end{cases}$$

We know that:

$$P \iff (Q \land T)$$

is equivalent to  $(P \land Q \land T) \lor (\neg P \land \neg Q) \lor (\neg P \land \neg T)$

where P, Q and T are logical expressions. Our equivalence constraints become

$$\left\{

\begin{array}{l}

s_{u,v} \ge 1 \\

k_u - \sigma_v - \delta_w(v) - 1 \ge 0 \\

k_v - \sigma_u - \delta_w(u) - 1 \ge 0

\end{array}

\right\} \lor \left\{

\begin{array}{l}

s_{u,v} < 1 \\

k_u - \sigma_v - \delta_w(v) - 1 < 0

\end{array}

\right\} \lor \left\{

\begin{array}{l}

s_{u,v} < 1 \\

k_v - \sigma_u - \delta_w(u) - 1 < 0

\end{array}

\right\}$$

We rewrite this system to exhibit the  $\geq$  relation:

$$\left\{ \begin{array}{l} s_{u,v} - 1 \geq 0 \\ k_u - \sigma_v - \delta_w(v) - 1 \geq 0 \\ k_v - \sigma_u - \delta_w(u) - 1 \geq 0 \end{array} \right\} \vee \left\{ \begin{array}{l} -s_{u,v} \geq 0 \\ -k_u + \sigma_v + \delta_w(v) \geq 0 \end{array} \right\} \vee \left\{ \begin{array}{l} -s_{u,v} \geq 0 \\ -k_v + \sigma_u + \delta_w(u) \geq 0 \end{array} \right\}$$

We previously defined how to write the linear constraints of the disjunction of three conjunctive constraints  $(P \vee Q \vee T)$ . We introduce the two boolean binary variables  $h, h' \in \{0, 1\}$ and we get:

$$\begin{cases} s_{u,v} - 1 - h \times (-1) \ge h' \times min(-1, -1) \\ k_u - \sigma_v - \delta_w(v) - 1 - h \times (-L_{max}) \ge h' \times min(-1, -L_{max}) \\ k_v - \sigma_u - \delta_w(u) - 1 - h \times (-L_{max}) \ge h' \times min(-1, -L_{max}) \end{cases}$$

$$\begin{cases} -s_{u,v} - (1 - h) \times (-1) \ge h' \times min(-1, -1) \\ -k_u + \sigma_v + \delta_w(v) - (1 - h) \times (-L_{max}) \ge h' \times min(-1, -L_{max}) \end{cases}$$

$$\begin{cases} -s_{u,v} \ge (1 - h') \times (-1) \\ -k_v + \sigma_u + \delta_w(u) \ge (1 - h') \times (-L_{max}) \end{cases}$$

$$h, h' \in \{0, 1\}$$

This system is simplified to (with  $L_{max} \geq 1$ ):

plified to (with

$$L_{max} \ge 1$$

):

$$\begin{cases}

s_{u,v} + h + h' - 1 \ge 0 \\

k_u - \sigma_v - \delta_w(v) + L_{max} h + L_{max} h' - 1 \ge 0 \\

k_v - \sigma_u - \delta_w(u) + L_{max} h + L_{max} h' - 1 \ge 0

\end{cases}$$

$$-s_{u,v} - h + h' + 1 \ge 0$$

$$-k_u + \sigma_v + \delta_w(v) - L_{max} h + L_{max} h' + L_{max} \ge 0$$

$$-s_{u,v} - h' + 1 \ge 0$$

$$-k_v + \sigma_u + \delta_w(u) - L_{max} h' + L_{max} \ge 0$$

$$h, h' \in \{0, 1\}$$

The complexity of computing all the  $s_{u,v}$  variables is  $\mathcal{O}(|V_R| \times (|V_R| - 1))$  booleans (two booleans for each couple of values (u, v) and  $\mathcal{O}(7/2 \times |V_R| \times (|V_R| - 1)|)$  linear constraints (7) linear constraints for each couple of values (u, v)). The total complexity is bounded by  $\mathcal{O}(|V_R|^2)$ variables and  $\mathcal{O}(|V_R|^2)$  constraints.

At this step, we can define the indirected interference graph  $H = (V_R, \mathcal{E})$ , such that  $(u,v) \in \mathcal{E}$  iff u and v interfere i.e.  $s_{u,v} = 1$ . The maximum number of values simultaneously alive is the cardinal of the maximal clique<sup>12</sup> in H. Rather than computing the maximal clique, we prefer to consider the indirected graph H' the complementary graph of  $H: H' = (V_R, \mathcal{E}')$ , such that  $(u, v) \in \mathcal{E}'$  iff u and v do not interfere i.e.  $s_{u,v} = 0$ . The maximal number of the values simultaneously alive is then the maximal independent set of H'. The independent sets are expressed by defining a binary variable  $x_u \in \{0, 1\}$  for each value  $u \in V_R$  such that  $x_u = 1$  iff u belongs to an independent set of the indirected graph H'. The number of  $x_u$  variables is  $\mathcal{O}(|V_R|)$ . The independent sets are expressed by:

$$x_u + x_v \le 1 \Longleftrightarrow s_{u,v} = 0$$

since  $s_{u,v} \in \{0,1\}$ , this is equivalent to

$$-x_u - x_v + 1 \ge 0 \Longleftrightarrow -s_{u,v} \ge 0$$

By using the linear expressions of the equivalence  $(\iff)$  and by introducing a boolean  $h \in \{0,1\}$ , we get:

$$\begin{cases}

-x_{u} - x_{v} + 1 \ge h \times (-1) \\

-s_{u,v} \ge h \times (-1)

\end{cases}$$

$$\begin{cases}

-x_{u} - x_{v} + h + 1 \ge 0 \\

-s_{u,v} + h \ge 0

\end{cases}$$

$$\begin{cases}

x_{u} + x_{v} - 2 \ge (1 - h) \times (-2) & \text{which is simplified to} \\

s_{u,v} - 1 \ge (1 - h) \times (-1)

\end{cases}$$

$$\begin{cases}

x_{u} + x_{v} - 2h \ge 0 \\

s_{u,v} - h \ge 0

\end{cases}$$

$$\begin{cases}

x_{u} + x_{v} - 2h \ge 0 \\

s_{u,v} - h \ge 0

\end{cases}$$

$$\begin{cases}

x_{u} + x_{v} - 2h \ge 0 \\

s_{u,v} - h \ge 0

\end{cases}$$

The complexity of expressing the independent sets (maximum number of values simultaneously alive) is  $\mathcal{O}(|V_R| + 1/2 \times |V_R| \times (|V_R| - 1))$  variables (one  $x_u$  for each value u, and one boolean h for each equivalence constraint). The total complexity of expressing the independent sets in H' is bounded by  $\mathcal{O}(|V|^2)$  variables and  $\mathcal{O}(|V|^2)$  constraints.

**Objective Function** In optimal RS computation, we need to maximize the maximum number of values simultaneously alive. This is done by maximizing the maximal independent set of H' (the complementary graph of the interference graph) by setting the following objective Function:

Maximize

$$\sum_{u \in V_R} x_u$$

**Summary** Our integer LP model has a total complexity bounded by  $\mathcal{O}(|V|^2)$  variables and  $\mathcal{O}(|E| + |V|^2)$  constraints:

- 1. the total number of integer variables is bounded by  $\mathcal{O}(|V|^2)$ :

- (a)  $\mathcal{O}(|V|)$  scheduling variables:  $\sigma_u$  for each node  $u \in V$ ;

<sup>&</sup>lt;sup>12</sup>a clique is a complete subgraph

- (b)  $\mathcal{O}((|V_R| \times (|V_R| 1))/2)$  interference binary variables:  $s_{u,v} \in \{0,1\}$  for all couple  $u, v \in V_R$ ;

- (c)  $\mathcal{O}(|V_R|)$  binary independent sets variables;  $x_u \in \{0,1\}$  for each value  $u \in V_R$ ;

- (d) the total number of intermediate variables for  $max_n$  functions is bounded by  $\mathcal{O}(|V|^2)$ ;

- (e) the total number of booleans defined to express  $max_n$ , the equivalence relations  $(\iff)$  and the disjunctive relations  $(\lor)$  is bounded by  $\mathcal{O}(|V|^2)$ ;

- 2. the total number of linear constraints is bounded by  $\mathcal{O}(|E| + |V|^2)$ :

- (a)  $\mathcal{O}(|E|)$  scheduling constraints;

- (b) the total number of interval lifetimes interference constraints (used to compute  $s_{u,v}$  variables) is bounded by  $\mathcal{O}(|V_R|^2)$ ;

- (c) the total number of independent sets constraints is bounded by  $\mathcal{O}(|V_R|^2)$ .

- 3. the objective function: maximize  $\sum_{u \in V_p} x_u$

#### Optimizing the Model

We can reduce the length of our model by considering;

- a precedence constraints e = (u, v) is redundant and can be evicted from the model iff  $lp(u, v) > \delta(e)$ ;

- two values  $(u, v) \in V_R$  can never be simultaneously alive iff for all schedules one value is always defined after the killing date of the other. Then, we do not need to define and compute  $s_{u,v}$  for the interference graph. The condition for that is:

$$\forall v' \in Cons(v) \ lp(v', u) \ge \delta_r(v') - \delta_w(u) \ \lor \ \forall u' \in Cons(u) \ lp(u', v) \ge \delta_r(u') - \delta_w(v)$$

## Chapter 3

## Optimal Register Saturation Reducing

We have shown in Sect.2.2.2 that if the register need of a schedule is less then or equal to the number of available registers, then a possible register allocation can be found in polynomial time. If not, spill code has to be introduced.

Reducing register saturation of a DDG G consists in adding extra serial arcs to build a new DDG  $\overline{G} = G \setminus^{\overline{E}}$  such that the register saturation is limited by a strictly positive integer (the number of available registers). Let  $\mathcal{R}$  be this limit. Then:

$$\forall \sigma \in \Sigma(\overline{G}) : RN_{\sigma}(\overline{G}) \leq RS(\overline{G}) \leq \mathcal{R}$$

We presented in [TT00] a heuristic that adds serial arcs to prevent some saturating values in  $AM_k$  from being simultaneously alive for any schedule  $\sigma \in \Sigma(\overline{G})$ , without increasing the critical path if possible. We prove in this section that finding such an extended DDG is NP-hard, and we give a method to build an optimal one. For the aim of the optimality, we release the definition of the extended DDG which states that it must be acyclic, i.e. we accept non acyclic extended DDGs that have negative or null cycles. In is easy to prove that valid acyclic schedules of DDGs with negative or null cycles exist.

### 3.1 NP-hardness of Reducing Register Saturation

**Definition 3.1 (ReduceRS problem)** Let be  $G = (V, E, \delta, \delta_w, \delta_r)$  a DDG and  $\mathcal{R}$  a strictly positive integer. Does there exist an extended DDG  $\overline{G} = G \setminus^{\overline{E}}$  of G such that:

$$RS(\overline{G}) \le \mathcal{R}$$

**Theorem 3.1** ReduceRS problem is NP-hard.

#### **Proof:**

First, ReduceRS does not belong to NP. Since computing register saturations is NP-complete, we cannot check in polynomial time if a given solution  $\overline{G}$  has  $RS(\overline{G}) \leq \mathcal{R}$ . Now, we prove that ReduceRS reduces to the problem of scheduling under registers constraints. Let us start by defining the latter problem.

**Definition 3.2 (SRC problem)** Let be  $G = (V, E, \delta, \delta_w, \delta_r)$  a DDG and  $\mathcal{R}$  a strictly positive integer. Does it exists a valid schedule  $\sigma \in \Sigma(G)$  such that:

$$RN_{\sigma}(G) \leq \mathcal{R}$$

SRC problem has been proven NP-complete in [Set75]. 1. **ReduceRS**  $\Longrightarrow$  **SRC** Let  $\overline{G}$  a solution for ReduceRS problem. Then, any valid schedule  $\sigma \in \Sigma(\overline{G})$  of  $\overline{G}$  is a solution for SRC.

#### 2. SRC $\Longrightarrow$ ReduceRS

Let  $\sigma$  be a solution for SRC, i.e.  $RN_{\sigma}(G) \leq \mathcal{R}$ . We build an extended DDG  $\overline{G}$  by serial arcs to impose value lifetimes of any schedule of  $\overline{G}$  to have same precedence relation as defined by  $\sigma$ .  $\forall u, v \in V_R/L_u^{\sigma} \prec L_v^{\sigma}$  then we add following arcs:

• if  $v \in pkill_G(u)$  then add the serial arcs  $\{e = (u', v)/v\}$

$$u' \in pkill_G(u) - \{v\} \text{ with } \delta(e) = \delta_r(u') - \delta_w(v)\}$$

• else add the serial arcs  $\{e = (u', v)/$

$$u' \in pkill_G(u)$$

with  $\delta(e) = \delta_r(u') - \delta_w(v)$