## PAGODE: a back-end generator for RISC machines

P. Canalda, Lucile Cognard, M. Mazaud, A. Despland

#### ▶ To cite this version:

P. Canalda, Lucile Cognard, M. Mazaud, A. Despland. PAGODE: a back-end generator for RISC machines. RT-0152, INRIA. 1993, pp.76. inria-00070016

## HAL Id: inria-00070016 https://inria.hal.science/inria-00070016

Submitted on 19 May 2006

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

# PAGODE: a back-end generator for RISC machines

Philippe CANALDA - Lucile COGNARD Monique MAZAUD - Annie DESPLAND

> N° 152 Mai 1993

PROGRAMME 2 \_\_\_\_\_

Calcul Symbolique, Programmation et Génie logiciel

PAGODE: a back-end generator for RISC machines <sup>1</sup>

PAGODE : un constructeur de générateurs de code pour machines RISC

Philippe CANALDA, Lucile COGNARD and Monique Mazaud <sup>2</sup>

INRIA Rocquencourt

Domaine de Voluceau, BP 105

78153 Le Chesnay Cedex

FRANCE

Annie Despland <sup>3</sup> LIFO Université d'Orléans BP 6759, 45067 Orleans CEDEX2 FRANCE

<sup>&</sup>lt;sup>1</sup>This work was partially supported by ESPRIT Project COMPARE

<sup>&</sup>lt;sup>2</sup>e-mail:Monique.Mazaud@inria.fr

<sup>&</sup>lt;sup>3</sup>e-mail:ade@chambord.univ-orleans.fr

#### Résumé

PAGODE est un constructeur de générateurs de code qui produit les différents moteurs (sélecteur d'instructions, module d'ordonnancement de code et allocateur de registres) d'un générateur de code de facon modulaire. Ce rapport technique présente la première version de ce système et constitue un manuel d'utilisation.

Mots-Clés: génération de code, sélection d'instructions, llocation de registres, ordonnancement de code

#### Abstract

PAGODE is a back-end generator that produces automatically the various engines of a code generator (instruction selector, scheduler and register allocator) from a target machine specification. This technical report presents the system in its first release and makes up a user's guide.

**Keywords:** code generation, instruction selection, register allocation, pipeline, code scheduling

## Contents

|   | 0.1  | Introduction                                        | 7  |  |  |  |  |  |  |  |  |  |  |  |

|---|------|-----------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|--|

| 1 | The  | SCALA language                                      | g  |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.1  | Introduction                                        | Ć  |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.2  | Storage bases                                       | 10 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.1 Error messages                                |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.3  | Storage classes                                     |    |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.3.1 Storage class declarations                    |    |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.3.2 Storage class referencing the memory          |    |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.3.3 Error messages                                |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.4  | Label classes                                       |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.5  | Value classes                                       |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.6  | Access modes                                        |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.0  | 1.6.1 Introduction                                  |    |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.6.2 Access mode declarations                      |    |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.6.3 Error messages                                |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.7  | Access classes                                      |    |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.7.1 Access class declarations                     |    |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.7.2 Error messages                                |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.8  | Instructions                                        |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.0  | 1.8.1 Instruction declarations                      |    |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.8.2 Convention                                    |    |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.8.3 Error messages                                |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.9  | Directives                                          |    |  |  |  |  |  |  |  |  |  |  |  |

|   |      | The interface specification                         |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.10 | The interface specification                         | 21 |  |  |  |  |  |  |  |  |  |  |  |

| 2 |      | struction selection 2                               |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.1  | Basic concepts                                      |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.2  | Input and output of the instruction selector engine | 24 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.1 Error messages                                | 25 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.2 MC68000 example                               | 2  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.3 SPARC example                                 | 26 |  |  |  |  |  |  |  |  |  |  |  |

| 3 | Bind | ding                                                | 29 |  |  |  |  |  |  |  |  |  |  |  |

| • | 3.1  | Basic concepts                                      |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.2  | Input and output of the binder engine               |    |  |  |  |  |  |  |  |  |  |  |  |

|   | -,-  | 3.2.1 Input term                                    |    |  |  |  |  |  |  |  |  |  |  |  |

|   |      |                                                     |    |  |  |  |  |  |  |  |  |  |  |  |

| A                                     | Der            | ivation          | chains             | for a SP.                   | ARC F     | MIR     |       |      |   |   |  |    |   |   |    |      |      |  | 62                |

|---------------------------------------|----------------|------------------|--------------------|-----------------------------|-----------|---------|-------|------|---|---|--|----|---|---|----|------|------|--|-------------------|

| Al                                    | NNE            | XES              |                    |                             |           |         |       |      |   |   |  |    |   |   |    |      |      |  | 61                |

| Bi                                    | bliog          | raphy            |                    |                             |           |         |       |      |   |   |  |    |   |   |    |      |      |  | 60                |

|                                       | 7.2<br>7.3     |                  |                    | e generato<br>n             |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       | 7.1            |                  |                    |                             | -         |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

| 7                                     | 0              |                  |                    |                             |           |         |       |      |   |   |  | 54 |   |   |    |      |      |  |                   |

|                                       |                | 6.3.2            | -                  | of the pre                  | _         |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       | 6.3            | Input 6.3.1      |                    | ut of the p<br>the prepa    |           | _       |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       |                | 6.2.3            | Error m            | essages .                   |           |         |       |      |   |   |  |    |   |   |    | <br> |      |  | . 52              |

|                                       |                | $6.2.1 \\ 6.2.2$ | _                  | ion of regi<br>ation for in |           |         |       |      |   | _ |  |    |   |   |    |      |      |  |                   |

|                                       | 6.2            |                  |                    | s for RISC                  |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

| 6.1 Code generators for CISC machines |                |                  |                    |                             |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

| 6                                     | <b>5</b> • • • |                  |                    |                             |           |         |       |      |   |   |  |    |   |   | 48 |      |      |  |                   |

|                                       | 5.3            | Input            | and outp           | ut of the s                 | schedule  | er engi | ne    |      |   |   |  |    |   |   |    |      |      |  | . 46              |

|                                       |                | 5.2.4            |                    | ations rela                 |           | -       |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       |                | $5.2.2 \\ 5.2.3$ |                    | ations rela<br>declaratio   |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       |                | 5.2.1            | _                  | ations rela                 |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       | 5.2            |                  | •                  | hine speci                  |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       |                | 5.1.2            |                    | verview of                  |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       | 0.1            | 5.1.1            | _                  | technique                   |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

| 5                                     | The 5.1        | sched<br>Basic   |                    |                             |           |         |       |      |   |   |  |    |   |   |    |      |      |  | <b>39</b><br>. 39 |

| _                                     | m'             |                  |                    |                             |           |         | -     |      | • | - |  | •  | • | • | -  | •    | -    |  |                   |

|                                       |                | 4.2.4            |                    | essages .                   |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       |                | $4.2.2 \\ 4.2.3$ | 0                  | nachine sp<br>vert const    |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       |                | 4.2.1            |                    | ncepts .                    |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       | 4.2            | Univer           | sal store          | rewriting                   |           |         |       |      |   |   |  |    |   |   |    |      |      |  | . 36              |

|                                       |                |                  | 4.1.2.3            | Spill in s                  |           | -       |       | -    |   |   |  |    |   |   |    |      |      |  |                   |

|                                       |                |                  | 4.1.2.1<br>4.1.2.2 | Register<br>Spill cod       |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       |                | 4.1.2            | •                  | get machir                  | -         |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       |                | 4.1.1            |                    | ncepts .                    |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

| •                                     | 4.1            | _                |                    | oring and s                 | spill cod | le proc | lucti | on . |   |   |  |    |   |   |    | <br> | <br> |  |                   |

| 4                                     | The            | regist           | er alloca          | ator                        |           |         |       |      |   |   |  |    |   |   |    |      |      |  | 32                |

|                                       |                |                  | 3.2.2.2            | Usedef ta                   | ables .   |         |       |      |   |   |  |    |   |   |    |      |      |  | . 31              |

|                                       |                |                  | 3.2.2.1            | Binding                     |           |         |       |      |   |   |  |    |   |   |    |      |      |  |                   |

|                                       |                | 3.2.2            | Output             | tables                      |           |         |       |      |   |   |  |    |   |   |    | <br> |      |  | . 30              |

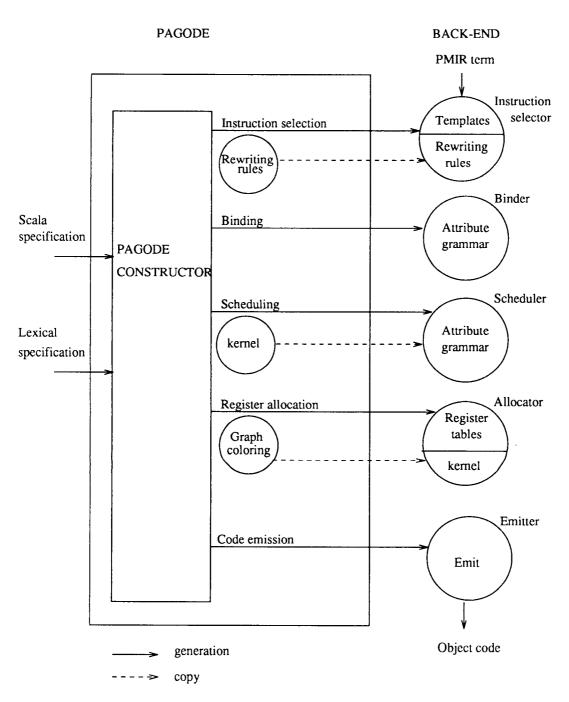

## List of Figures

| 0.1 | The Pagode System                        | 8  |

|-----|------------------------------------------|----|

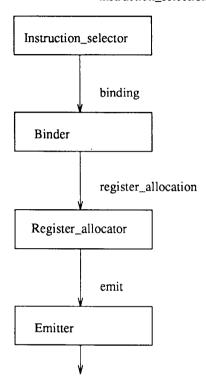

| 6.1 | The overall structure of a CISC back-end | 49 |

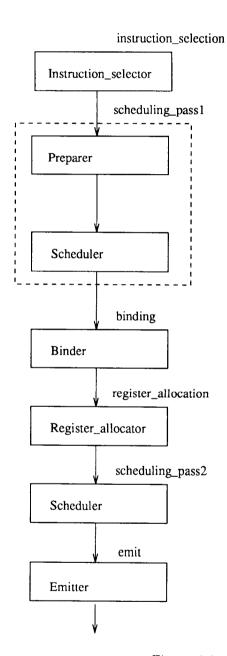

| 6.2 | The overall structure of a RISC back-end | 51 |

#### 0.1 Introduction

PAGODE is a back-end generator based on tree rewritings that takes as input a target machine description using a special purpose language called SCALA and produces a code generator that performs instruction selection, register allocation and scheduling and produces assembly code.

A target machine specification written in the SCALA language must be hierarchically organized into concepts corresponding to the main features of the instruction set processor: locations, addressing modes and instructions.

The semantics of each concept of the target machine specification is given by a template which is a term of an ADT (abstract data type). Such an ADT is specific to a given target machine and must be specified by the compiler writer while writing the SCALA specification. An abstract data type is a collection of sorts with their axioms. A sort is similar to a type with its operators. A term is an object of a given type built from these operators. The SCALA specification of a target machine requires only the syntactic part of the ADT. The axioms can be used by the compiler writer to specify some special cases (see section 1.6.2).

The terms built on this ADT are called PMIR (PAGODE medium intermediate representation), they are used as input to a back-end produced by the PAGODE system. In the PMIR input term to the back-end, instructions act on cells via operators denoting access paths to cells.

For CISC machines, the code generation process is divided into three steps: instruction selection, binding and register allocation. Additional steps of scheduling are provided for RISC machines. The engines that perform those steps are automatically produced by the PAGODE system.

The instruction selection process applies a set of rewriting rules driven by tree templates derived from the target machine specification to the PMIR term. Basically each instruction of the PMIR is matched with an instruction template. In the context of such a template, the operands are matched with addressing mode templates. If an operand does not match any addressing mode template and a subterm does, then the location depicted by the subterm is stored in a "temporary resource" using a universal store. The PMIR is rewritten using this temporary resource.

The output of the instruction selector belongs to the LIR (low level intermediate representation) of the target machine. It includes universal assignments, references to temporaries, addressing modes and instructions in their "canonical" representation.

The second code generation step, called binding, sets constraints on those temporaries according to the whole context and performs life-time analysis and packing on temporaries.

A LIR term can be either the input of the register allocator or the scheduler.

The register allocator needs knowledge of the actual resources of the target machine that have been declared in the target machine specification. If all registers have been assigned, it is necessary to spill some of them, thus a spill code strategy must be identified. That is the reason why a "spill code" construction has been added to the SCALA language, in fact it is a compiler strategy that uses both spill instructions and data storage directives.

The scheduler works on the LIR using data dependence analysis on the target machine resources and attributes on the use of functional units that have been added to the target machine specification.

Figure 0.1: The PAGODE System.

## Chapter 1

## The Scala language

#### 1.1 Introduction

The PAGODE system provides the special purpose language SCALA to specify the instruction set of a target machine. A SCALA specification is handled by the SYNTAX system which provides automatic construction of scanners and parsers for a given language. The definition of SCALA has been done using BNF rules and annotations aiming to give names to the abstract tree built during parsing. The code generator writer is guided during the development of a given target machine specification by the error messages of SYNTAX since this system implements in its parser and scanner a powerful error recovery mechanism [BJ 87].

A full syntactic definition of SCALA will be found in the next release of the reference manual. Currently, specifications given as examples of target machine and various sections described in this chapter can be considered as a sufficient introduction to the syntactic form of various sections of this language. In the sequel of this document, all keywords of SCALA are in bold letters.

A target machine description can be easily deduced from the handbook. The basic concepts of an assembly language are described by specific constructs of SCALA: storage bases, storage classes, label classes, value classes, access modes, access classes and instructions. A target machine description is hierarchically structured in seven levels:

- storage bases are used to declare storage descriptions (sets of available locations, i.e. registers, memory locations):

- storage classes are logical partition of storage bases: there must exist as many storage classes as there are ways to gather storage base elements:

- label classes are used to depict operands that are labels:

- value classes are used to depict operands that are immediate constants;

- access modes correspond to addressing modes description (various ways to access locations);

- access classes: since an operand of an instruction may accept several access modes, the access modes are assembled into access classes:

- instructions belong to the instruction set processor.

The semantics of each construct is expressed using a term of the target abstract data type (ADT) of the target machine and various attributes that describe the properties of the construct such as format, space cost, time cost, size ....

This chapter describes the various concepts used to depict a CISC machine, the features of the SCALA language related to the specific properties of a RISC machine are optional. They will be described entirely in the fifth chapter.

Since the occurrences of a construct for various sizes of the addressable units are often nearly identical, a solution proposed to deal with large algebraic specifications is the use of parameterization and instantiation mechanisms [DMR 90a]. Such mechanisms fit very well with our machine specification language. The compiler writer can factor out some instances of a given construct in a generic pattern followed by the possible values of the generic parameters of the pattern. The system derives from this declaration as many occurrences of the construct as there are sizes of addressable units associated with it. The instantiation mechanism is bound to a name generation mechanism. Throughout the paper the following notations will be used:

- If n is a name and L is a variable, when L is instantiated by v. n!L builds the name n\_v.

- $\langle S | V \rangle$  means that V is a variable or a constant of sort S.

A basic hypothesis of the PAGODE system is that the measure unit for the sizes is the byte.

#### 1.2 Storage bases

A storage base is defined as the set of the smallest addressable units of a physical storage.

For example the CYPRESS SPARC CY7C601/612 architecture has 136 32 bits-wide registers that are divided into a set of 128 window registers and a set of eight global registers. The 128 window registers are grouped into eight sets of 24 registers called windows that overlap on eight registers. At any given time, a program can address 32 active registers: 24 window registers and eight globals denoted by %gx. The window registers are divided into 8 input registers denoted by %ix, 8 local registers denoted by %lx and 8 ouput registers denoted by %ox, their names are listed in the Symbolic notation declaration. A list of register names is allowed as symbolic notation. Each item of the list can be depicted by a string followed by an integer interval. An item of this list may include the declaration of an alias for a register name, it is introduced by the keyword alias. Thus in the declaration below:

- %fp is an alias of %i6, among the input registers called %i1. %i2. %i3 ...

- %sp is an alias of %o6, among the output registers called %o1, %o2, %o3 ...

Thus, the compiler writer must declare the following storage base:

```

Storage_base GPR -- General purpose registers

Symbolic_notation

'REG' is %g (0..7)

.%i (0..7) with %fp alias %i6

.%o (0..7) with %sp alias %o6

.%(1(0..7)

$ base_units = 4

$ free = %(1(0..7)

End

```

The registers available for register allocation are specified into the **\$free** attribute, that is the case of the local registers only. For single precision, floating-point operands are placed in floating point registers. 32 floating-point registers are available, they are called %f1, %f2, %f3, %f4....

```

Storage_base FREG -- Floating point registers

Symbolic_notation

'FREG' is %f (0..31)

$ base_units = 4 ^

$ free = %f (0..31)

End

```

The PAGODE system assumes that there exists on every target machine an homogeneous and uniform storage base corresponding to the memory. By convention, this storage base is called MEM. It is not necessary to declare it in a SCALA specification.

#### 1.2.1 Error messages

The PAGODE constructor checks that the second element of an alias declaration belongs to the previous enumeration of resources. For instance, if the GPR storage base includes the following specification part

```

• Storage_base GPR -- General purpose registers

Symbolic_notation

'REG' is %g (0..7)

, %i (0..7) with %i6 alias %fp

...

End

```

then the PAGODE constructor would emit the following error message:

• Error: In the context of the storage base GPR, the alias name %fp must belong to the previous enumeration..

### 1.3 Storage classes

#### 1.3.1 Storage class declarations

For a given storage base, the compiler writer must describe as many storage classes as there are ways to gather storage base elements to represent logical storage units. Thus, we define a new concept: the storage class based on a storage base. For instance, an access to a register may designate a byte operand, a word operand or a longword operand.

A storage class occurrence is characterized by the following properties:

- its denotation introduced by the keyword **Denotation**.

- its storage base viewed as an attribute of a storage class is introduced by the keyword \$Base.

- basic operations introduced by the keyword Operations. The dereference operation, i.e. the access operation to the contents of an element of the storage class begins with the keywords dereference is. The cell constructor operation begins with the keyword cell\_constructor is.

When there exists an alternative on the sort of the contents of a storage class element, it is introduced by the keyword Union. In the following example, the contents of a general purpose register can be either an address or a 13 bit value, or a 22 bit value.

In the SCALA language, the storage class construct is described using a predefined keyword for each of these properties. Let us consider the storage classes related to the general purpose register storage base. As an access to a general register for the SPARC may represent an access to a word operand or a double word operand, the compiler writer must declare two storage classes respectively: the gpr\_W and gpr\_D storage classes. The compiler writer can declare a generic pattern of a general purpose register storage class using generic names. The Instances part of the declaration includes the information needed by the name generation mechanism to build the actual names.

```

Storage_class gpr

Denotation < gpr!size reg>

Attributes

\$Base = GPR

Operations

dereference is

cont_of_gpr!size

: gpr \(\to$ Union (address, value_13, value_22)

cell_constructor is

designates_gpr!size : gpr → gpr

Instances

size in { W, D}

case size is

W

: size = 4 base\_units

: size = 4 double base_units

D

End case

End

```

From this pattern, the system deduces the two descriptions of actual storage classes. The size of a given storage class is specified counting the base\_units occupied. The keyword double means that the PAGODE system will consider a pair of general purpose registers.

#### 1.3.2 Storage class referencing the memory

There must exists a storage class based on the MEM storage base. The information related to this storage class are used to generate the scheduler.

#### 1.3.3 Error messages

- Warning: Unknown storage base...in the declaration of the storage class....

- Error: Inconsistency between the number of instances and the number of case choices in the declaration of the storage class....

#### 1.4 Label classes

Some labels are used in addressing modes or in instructions, they must be specified, too. They are introduced by the keyword Label\_class. In the PAGODE system, the hypothesis that all labels belong to a set of labels called UNIV\_LABEL holds. UNIV\_LABEL is a keword of the PAGODE system.

```

Label_class data_label

Denotation < data_label lab>

Attributes

Base = UNIV_LABEL

Operations

const_dlabel: data_label — int_immediate_value

add_lab: address, int_immediate_value → address

Symbolic_notation

lab in DATA_LABEL

```

End

#### Value classes 1.5

The assembly language of the target machine uses immediate values as operands of instructions, as offsets or as displacements of addressing modes. According to the target machines these values take different sizes.

Thus on the SPARC architecture. 13-bit values are used to specify a frame pointer with displacement addressing mode. On the MC68000, the similar addressing mode takes a 16-bit value as

A similar comparison holds if one considers the relative offsets to the program counter for branches:

- 1. on a MIPS, branches have 16-bit offsets relative to the program counter.

- 2. on a SPARC, branches have 22-bit offsets relative to the program counter.

That is the reason why each different value size must be declared as a different sort with its operators, this concept is called a value class. A sort for an immediate value is introduced by the keyword Value\_class. The same hypothesis as for labels holds, i.e. there exists a general set of integers called UNIV\_INTEGER.

The specification of a 13-bit value for the SPARC is as follows:

```

Value_class value_13

Denotation < value_13 val>

Attributes

Base = UNIV_INTEGER

Operations

const_value_13: value_13 — value_13

add_13: value_13 . value_13 — value_13

sub_13: value_13. value_13 \rightarrow value_13

mul_13: value_13 . value_13 -- value_13

Symbolic_notation

val in INTEGER_13

End

```

#### 1.6 Access modes

#### 1.6.1 Introduction

Let us consider an assignment statement of A to B, we shall state in the sequel that A is the source operand(r-value) and B the destination operand (l-value) of the assignment. In an instruction,

an operand is an element of a set of access modes. Whereas an access mode in source position designates the contents of a location, it designates the location itself in destination position.

An access mode can be defined as an addressing mode of a virtual machine on which all standard addressing modes are available, i.e. direct addressing mode, indexed addressing mode, indirect addressing mode<sup>1</sup>.

#### 1.6.2 Access mode declarations

A particular machine has several addressing modes. For a given addressing mode of the machine, the compiler writer must define as many access modes as there are associated storage classes. An access mode is specified by:

- a canonical form representating the access mode, including its name and its parameters. These parameters are formal storage or value classes. It is introduced by the keyword Canonical form.

- its related attributes: length, format, space cost and time cost. They are respectively introduced by the keywords: \$length, \$fmt, \$space\_cost. \$time\_cost.

- a template that describes the access path to the corresponding operand: the operand in source (resp. destination) position is defined by the term obtained by applying the dereference (resp. the cell constructor) operation to this template. It is introduced by the keyword Template.

The canonical form of an access mode has parameters that characterize a given addressing mode. For instance, let us consider an indirect with displacement addressing mode on a SPARC, it takes as operands a general purpose register and a 13 bit offset. Now consider the similar addressing mode on a MC68000, it requires an address register and a 16 bit offset.

On the SPARC architecture, the related access mode when the size of the operand is half word can be specified as follows:

#### Access\_mode

```

Canonical_form -- Indirect with displacement access mode disp_am_H ( <gpr_W reg> . <value_13 val>)

Attributes

$length = H -- length of the addressable unit $fint = ~ reg + val ~ -- Assembly language format $space_cost = 0 $time_cost = 1

Template

index ( cont_of_gpr_W (<gpr reg>) . const_value_13 (<value_13 val>))

```

End

The template introduced by the keyword Template has no meaning in itself. The PAGODE constructor must handle that feature to build two templates from this definition: a template in r-value (i.e. in source position), a template in l-value (i.e. in destination position). For the previous disp\_am access mode definition, the PAGODE constructor works as follows. From the signature of the index

<sup>&</sup>lt;sup>1</sup>Notice that such an addressing mode does not always exist on a real target machine, that is the case of the SPARC for which there exists no indirect addressing mode. Since such a construct is necessary in the PMIR, we shall give a solution to deal with this issue in the sequel.

operator, the constructor returns an address whose dereference operator is "cont\_of\_address" and whose cell constructor is "designates\_address", the system derives the two following access modes, respectively in destination and source position:

```

designates_address_H (

index (cont_of_gpr_W (<gpr reg>), const_value_13 (<value_13 val>)))

cont_of_address_H (

index (cont_of_gpr_W (<gpr reg>), const_value_13 (<value_13 val>)))

```

In some cases, an access mode exists only in a given position, either source or destination position. The SCALA language provides two specific constructs to handle those cases. When the keyword Template is followed by the keyword Src, it means that the access mode exists only as an r-value. Thus an immediate value, on the MC68000, can be used only as an r-value, i.e. in source position.

```

Access_mode

Canonical_form

immediate_val_am!size (<immediate_value!size val>)

Attributes

$length

size

$fmt

~val~

$space_cost

1

=

$time_cost

case size is

B, W:4

L:8

End case

Template

Src

const_value_!size ( <immediate_value val>)

Instances size in {B, W, L}

End

```

When the keyword **Template** is followed by the keyword **Dst**, it means that the access mode exist only as a *l*-value. That is the case of the addressing modes used in branches. In the MC68000 specification, the specification of a destination of a branch can be specified by the following access mode:

```

Access_mode

Canonical_form

relative_clab_am (<code_label lab>)

Attributes

$length

L

$fint

~lab~

$space_cost

1

$time_cost

8

Template

Dst

const_clabel_W (<code_label lab>)

End

```

As for the storage class construct, the compiler writer can define a formal access mode. Among the numerous addressing modes of the MC68000, let us consider the indirect with displacement

addressing mode. This access mode has instances introduced by the keyword which depend on the size of the location indirectly accessed in source position. Thus the compiler writer defines a generic access mode pattern "disp\_am!size" parameterized by the size. This leads to three templates in source position (respectively in destination position) when the size is instantiated by {B, W, L}. The *indirect with index* access mode has instances which depend on the size of the location indirectly accessed in source position.

#### Access\_mode

```

- - Indirect with displacement access modes

Canonical_form

disp_am!size (<aregister_L reg> , <immediate_value_W val>)

when val = 0

disp_am!size (<aregister_L reg>, <immediate_value_W 0>)

Attributes

\theta = \theta

- - length of the addressable unit

size

$fmt

- - Assembly language format

\sim val (reg) \sim

when val = 0 \sim (reg) \sim

space\_cost = 1

time\_cost = case size is

B.W:8

L:12

End case

Template

index (cont_of_areg_L (<aregister reg>)

, const_value_W (<immediate_value val>))

when val = 0

cont_of_areg_L (<aregister reg>)

Instances

size in {B, W, L}

End

```

A special purpose construct called when has been introduced in SCALA to handle PMIR terms that cannot be recognized by any access mode template. Let us consider an indirect operation of the PMIR for a SPARC, it looks like the following:

```

cont_of_address (cont_of_areg_L (<aregister reg>)) in source position.

Similarly, an indirect operation in destination position corresponds to the template:

designates_address (cont_of_areg_L (<aregister reg>))

```

These PMIR terms can be recognized by the disp\_am access mode when val equals zero owing to the following axiom on the index operator:

```

index (address, value'0') = address

```

#### 1.6.3 Error messages

The PAGODE constructor checks whether a storage class occurring in an access mode declaration has been previously declared. When this condition does not hold the following error message is emitted:

• Error: Unknown storage class...in the declaration of the access mode....

#### 1.7 Access classes

#### 1.7.1 Access class declarations

The operands of an instruction are access classes which are defined as sets of access modes. An access class is introduced by the keword **Access\_class**. It can be also specified by a generic pattern including the instantiation of its elements, there are as many instances of a generic access class as there are possible sizes of operands.

#### Access\_class

The instances of a generic access class are also introduced by the keyword Instances.

#### Access\_class

#### 1.7.2 Error messages

The PAGODE constructor checks whether an access mode occurring in an access class declaration has been previously declared. When this condition does not hold the following error message is emitted:

• Error: Unknown access mode ...in the declaration of the access class ....

#### 1.8 Instructions

#### 1.8.1 Instruction declarations

An instruction may be characterized by the following properties:

- a canonical form representation of the instruction including the access classes to which the instructions apply. It is introduced by the keyword Canonical form.

- its related attributes: length, format, modification and time cost.

- the template describing what is performed by the instruction (it is a term of the abstract data type). It is introduced by the keyword Template.

The format attribute introduced by the keyword **\$format** corresponds to the syntax in the assembly language. The time cost is expressed into a number of clock cycles of the target machine, this specification begins with the keyword **\$time\_cost**. The space cost of an instruction is supposed to be one word. It is a hypothesis of the PAGODE system.

Let us consider the SPARC instruction "store" which stores the contents of a general purpose register in a memory location. We obtain the following specification:

#### Instruction

```

Canonical_form

st (<Gpr_access_W AM1>, <All_access_W AM2>)

Attributes

$length = W

$fmt = ~st $fmt(<Gpr_access_W AM1>)

, $fmt(<All_access_W AM2>) ~

$modification = store

$time_cost = 5

Template

assign_W (src (<Gpr_access_W AM1>), dst (<All_access_W AM2>))

End

```

The Attributes keyword introduces various properties of the instruction. The \$length attribute of an instruction must be the length of the operand in destination position. This length is generally the same that the size of its operands. Nevertheless there exists some cases in which the result has not the same size; that is the case of a multiply instruction on the MC68000 where the result is located on a double word:

#### Instruction

```

Canonical_form

muls (<Data_access_W AM1>, <Dregister_access_L AM2>)

Attributes

$length

L

$fint

~MULS $fmt(<Data_access_W AM1>)

, $fmt(<Dregister_access_W AM2>) ∼

$modification =

binary_arith

$time_cost

70

Template

assign_L (mul (

src (<Dregister_access_W AM1>)

, src (<Data_access_W AM1>))

, dst (<Dregister_access_L AM2>))

End

```

The **\$fmt** is a string included between  $\sim$  which uses the formats of the parameters of the instruction. It is used to emit the assembly code.

Instructions have been split into various families by means of the attribute **\$modification**. This allows one to build the control flow graph needed by the register allocator and the scheduler. The notion of family is not only related to the control flow graph, it is used by the instruction selector as well as by the register allocator and the scheduler to perform their specific jobs. Since the families of interest are not exactly the same for all of them, a rather fine grain of families has been defined.

• assignment families:

required by both instruction selector and scheduler.

- spill: a load or a store for CISC machines:

- load: assignment from memory to register must be specified for RISC machines;

- store: assignment from register to memory must be specified for RISC machines;<sup>2</sup>

- binary\_arith: assignment for arithmetic computations where general purpose resources are involved;

- unary\_arith: assignment for arithmetic computations where general purpose resources are involved;

- convert: for conversion operations;

- special\_arith: assignment for arithmetic computations where specific resources like SP or PC are involved;

#### • branch families:

to compute the control flow of the LIR output of the instruction selection, and of the LIR input of the scheduler;

```

- branch: for inconditional branches;

```

- cond\_branch: for conditional branches;

- proc\_call: for procedure calls;

- return\_proc: for return from procedure call;

#### • miscellaneous:

- test: for all kinds of comparisons

- putlabel: label setting is important to build the control flow graph;

- directive: for assembly directives;

- noop: for no-operation instructions.

The template expresses the semantics of this instruction: the source operand of the instruction (i.e the content of the general purpose register) is stored in the destination of the instruction (i.e a memory location designated by the access class All\_access\_W).

Nearly every instruction of the target machine may be applied to the different lengths of its operands. In order to avoid the repetition of such descriptions, the compiler writer specifies a pattern of an instruction and its instances. Let us consider the *addi* instruction on the MC68000 which corresponds to an immediate addition operation. The size of the instruction may be specified to be a byte, a word or a longword. The instances of a generic instruction are also introduced by the keyword **Instances**.

#### Instruction

```

Canonical_form

```

```

addi!size ( <Immediate_access!size AM1>, <Altdata_access!size AM2>)

Attributes

$length = size

$fint = ~ ADDI.$length $fint (<Immediate_access!size AM1>)

$fint (<Altdata_access!size AM2>) ~

$modification = binary_arith

$time_cost = case size is

B , W : 4

```

<sup>&</sup>lt;sup>2</sup>the load or store attribute is used by the scheduler for RISC machines.

## L:8 **End case**

#### Template

```

assign!size (

add!size (src ( <Altdata_access!size AM2>)

, src ( <Immediate_access!size AM1>))

, dst (<Altdata_access!size AM2>))

```

Instances size in {B, W, L} End

The time cost may depend on the size of the instruction, a case construct is available in the language for that purpose.

#### 1.8.2 Convention

- The source parameters of the canonical form of an instruction must always be declared before the destination parameter. This hypothesis is not used by the instruction selector but by the register allocator (see section 4.2.2) and the prepare engine (see section 6.1).

- Several instructions can have the same name. In that case, the PAGODE constructor renames these names from the second occurrence of an instruction. The second occurrence of a given name is renamed adding "1" to the initial name, the third occurrence is renamed adding "2"

This convention must be known by the compiler writer if the PMIR includes instructions in their canonical form.

#### 1.8.3 Error messages

The PAGODE constructor checks whether an access class occurring in an instruction declaration has been previously declared. When this condition does not hold the following error message is emitted:

Error: Unknown access class...in the declaration of the instruction....

• The PAGODE constructor checks whether a storage class occurring in an instruction declaration has been previously declared. When this condition does not hold the following error message is emitted:

Error: Unknown storage class...in the declaration of the instruction....

#### 1.9 Directives

Most assemblers provide "assembler directives" which are actually instructions for the assembler rather than the processor. Since they must be produced by the compiler too, the target machine specification must include a specification of such directives. Their syntactic form begins with the keyword **Directive** and includes only a **Canonical form**, a length and a format.

The EQU directive of the MC68000 is used to equate a number to a symbol. The following specification holds when this number is specified by an immediate value:

```

Directive

Canonical_form

equ ( immediate_dlab_am_W (<data_label_W lab>)

, immediate_val_am_W (<immediate_value_W val> ))

Attributes

$length = W

$fmt = ~ lab EQU val ~

End

```

The data storage directive "DS" of the MC68000 is used to reserve space in memory. Since the length specification determines whether bytes, words or longwords are reserved, this directive is specified as follows:

```

Directive

Canonical_form

data_storage!size ( immediate_val_am_W (<immediate_value_W val>))

Attributes

$length = size

$fmt = ~ DS.Slength ~

Instances

size in {B. W. L}

End

```

#### 1.10 The interface specification

Basically, the instruction selector matches each instruction of the PMIR with an instruction template. In the context of such a template, the operands are matched with addressing mode templates. If an operand does not match any addressing mode template and a subterm does, then the location depicted by the subterm is stored in a "universal resource" using a universal store instruction. The PMIR is rewritten using this universal resource [DMR 90a].

A universal resource stands for any actual resource of any sort associated to registers. The built-in sort temporary denotes the sort related to universal resources. A universal store stores the contents of a cell in a resource of sort temporary, this operator is denoted by Univ\_assign. The addressing mode for a temporary: temporary\_am is also provided by the PAGODE system.

A Univassign is a generic assignment operation. It means that the content of a location is stored in a universal temporary resource. One can say that it is a generic assignment in the sense that this operator can be overloaded by different operators of the PMIR.

The system needs to associate the internal names such as temporary\_am, Univ\_assign with the actual names of the machine specification that become possible synonyms during the 2rewriting process. For that purpose, the compiler writer uses an interface declaration construct introduced by the Interface declaration. For the MC68000 it follows:

```

Interface declaration

$Bind = {aregister, dregister}

Access_class

<Temporary_access AM>

= dreg_am!size (<dregister!size temp>)

= areg_am!size (<aregister!size temp>)

where size in {W, L}

```

```

Instances

```

size in {B, W, L}

End

Univ\_assign\_equivalence

Univ\_assign: assign!size where size in {B, W, L} \$space\_cost = 0, \$time\_cost = 4

End

The PAGODE system needs to know the proper storage synonyms of a temporary. This information can be deduced from the declaration of the **\$Bind** attribute.

PAGODE also needs to know the access modes that are correct aliases for the temporary access mode, these informations are deduced from the Access\_class construct in the interface specification part.

The Univ\_assign\_equivalence introduces an alias between the Univ\_assign operator and the assignment operator of the PMIR (with its right sizes). Costs must also be associated to this operator, this costs can be computed as the average of the costs of spill instructions.

## Chapter 2

## Instruction selection

In order to achieve the instruction selection task, the PAGODE constructor feeds the selector with several sets of templates that are automatically derived from the target machine specification. The instruction selector includes two parts: a bottom-up tree pattern matching [HO 82] and a reducer [RR 92]. These two engines come from the theory of rewriting terms with automata using bottom-up tree pattern matching.

#### 2.1 Basic concepts

The goal of the instruction selection step is to identify each modification of the PMIR with the canonical form of the instruction of the target machine. Such operation is also called "normalization problem" in the classical rewriting terms theory. It runs in two steps:

- the first one identifies a set of rewriting rules that can be applied to a PMIR modification. A composition of rewriting rules used to get such a PMIR modification will be called derivation chain in the sequel.

- the second one selects the cheapest derivation chain using the cost attributes in the target machine specification.

The bottom-up matching process of the PMIR is carried out until each instruction of the PMIR may be reduced into an instruction canonical form: we call LIR (low intermediate representation) the terms that are basically a sequence of instruction canonical forms.

For each instruction, in the context of an instruction template (respectively a canonical form of an instruction), operand subterms are matched with access mode templates (respectively with access mode canonical forms). If they are leaves of a canonical form of an instruction, they have to be in their canonical form and the reduction process is unnecessary. Otherwise, if the whole operand subterm matches an access mode template, the tree pattern matcher takes the tree where the operand is replaced by the canonical form of the access mode as a new goal. If it is only an inner subterm that matches an access mode template, the tree pattern matcher takes as a new goal the tree where the inner subterm is reduced to a temporary location.

The space cost of a derivation chain is computed adding the space cost of each instruction of the LIR, using the following definition for the space cost of an instruction of the LIR:

$space\_cost (instruction) = \sum \$space\_cost (access\_modes) + 1$

The time cost of a derivation chain is computed adding the time cost of each instruction of the LIR, using the following definition for the time cost of a LIR:

time\_cost (instruction) =  $\sum$ \$time\_cost (ins) + \$time\_cost (access\_modes)

The cost of the derivation chain may be increased by the cost of a universal store and the costs of its operands. The action associated to this reduction is the production of a universal store tree of the location designated by the recognized access mode into the temporary location.

The bottom-up matching process goes on in order to compute all the possible derivation chains that lead to an instruction in canonical form with their respective costs. The system selects the cheapest one. Once a derivation chain is selected, the reductions involved are effectively performed as well as the associated actions.

The modification tree is flattened into a sequence of universal store trees followed by an instance of the canonical form where the operands have been settled conforming to the instruction template that matches.

A universal store has the **Univ\_assign** operator as root. It stores the contents of a cell designated by an access mode in source position in a resource of sort **temporary**. A universal store is another kind of instruction of the LIR.

For each PMIR term, the rewriting algorithm needs to know the boundary where the access mode pattern matching must stop and where the instruction pattern matching must begin. On one hand, the rewriting system uses the set of instruction templates where each leaf refers to an access class, i.e a set of access modes to set the context. On the other hand, it uses the set of access mode templates for the reduction process and the set of arithmetic instructions.

A PMIR term representing an expression can contain embedded arithmetic and access path operators. It is not always possible to produce the related arithmetic instruction instead of the universal store assignment. For that purpose, the instruction selector needs to know for which instructions the **\$modification** attribute equals to binary\_arith, unary\_arith, special\_arith or to convert

The instruction selection algorithm applies the set of rules specified in [DMR 90b].

## 2.2 Input and output of the instruction selector engine

The input of the instruction selector is a PMIR term that may include actual registers, in that case the compiler must be aware that this register must not appear in the list of free registers of the related storage base.

Universal resources may also appear in the PMIR via the temporay\_am access mode. Such an occurrence may have been produced as output of an optimizing engine working on the PMIR. The output of the instruction selector is a LIR term, i.e a sequence of instructions in their canonical form where the access classes have been replaced by the right access mode or a temporay\_am access mode.

The instruction selector of PAGODE generates temporary resources which do not clash with the actual and temporary resources in the PMIR. The LIR includes different kinds of temporaries:

- those coming from the PMIR. Their life time may be greater than that of a basic block.

- those coming from the instruction selector. Their life time is local to a basic block. Their name begins by the string "&=&\_tmp" followed by a sequence of integers. To improve the legibility of this manual &=&\_tmp will be replaced by tmp in the sequel.

#### 2.2.1 Error messages

The PAGODE instruction selector checks whether a PMIR modification can be rewritten according to the templates derived from the target machine specification. When this condition does not hold one of the following error messages is emitted:

- Instruction selection failed. The system can not rewrite the PMIR tree of root ....

- Instruction selection failed. Rewriting interface fails because the system cannot find an access mode of root . . . .

- Instruction selection failed. The rewriting system is waiting for either an interface rule or another access class definition. The system can not rewrite the PMIR tree of root . . . .

#### 2.2.2 MC68000 example

Let us consider the MC68000 PMIR term that corresponds to the assignment X := X + T where X and T are local to a procedure. The offsets of X and T from the content of the frame pointer are respectively -4 and -8:

The bottom-up tree pattern matching system may generate several derivation chains. Among the solutions, two derivation chains derived from the previous PMIR term are shown below:

```

• seq ( Univ\_assign_{space\_cost=1}^{time\_cost=4} \ (Univ\_assign_{space\_cost=1}^{time\_cost=12} \ (alsp\_am\_L_{space\_cost=1}^{time\_cost=12} \ (alsp\_am\_L_{space\_cost=0}^{time\_cost=0} \ (add1\_L_{space\_cost=1}^{time\_cost=12} \ (add1\_L_{space\_cost=1}^{time\_cost=12} \ (alsp\_am\_L_{space\_cost=0}^{time\_cost=0} \ (alsp\_am\_L_{space\_cost=1}^{time\_cost=12} \ (alsp\_am\_L_{space\_cos

```

This example shows two derivation chains produced for the previous PMIR.

The first one is produced storing the left son of the PMIR term in the temporary tmp0. Then using the equivalence between the temporay am access mode and the dreg am access mode, the pattern matching of the modified PMIR term with the:

```

add_L (<Dregister_access_L AM1>,<Altmem_access_L AM2>)

```

succeeds since the disp\_am access mode belongs to the Altmem\_access\_L access class.

The second one is produced storing the left son of the PMIR in the temporary tmp0 first. Then using the equivalence between the temporay am access mode and the dreg am access mode, the root and the new left son of the modified PMIR is matched with the:

```

add_L (<All_access_L AM1>,<Dregister_access_L AM2>)

```

instruction. Finally, since the destination of the initial PMIR has not been matched a universal store is produced to store the destination of the add\_L instruction into the right destination.

Among these two derivation chains, the code selector selects the cheapest one, the cost of which is 44, whereas the second one has a global cost of 56.

#### 2.2.3 SPARC example

Let us consider for the SPARC, the PMIR term that corresponds to the assignment of L := 0. The offset of L from the content of the frame pointer is -4.

Three derivation chains are built from the previous SPARC PMIR:

```

• seq (

mov_{space\_cost=1}^{time\_cost=4} (

value\_13\_am\_L_{space\_cost=0}^{time\_cost=2} < value\_13 0 >

, temporary\_am_{space\_cost=0}^{time\_cost=1} < temporary tmp0> )

Univ\_assign_{space\_cost=1}^{time\_cost=5} (

temporary\_am_{space\_cost=0}^{time\_cost=1} <temporary tmp0>

global\_cost = 16^{time\_cost=14}_{space\_cost=2}

• seq (

Univ\_assign_{space\_cost=1}^{time\_cost=5} (

value\_13\_am\_L_{space\_cost=0}^{time\_cost=2} < \text{value\_}13 \text{ } 0 >

, temporary\_am_{space\_cost=0}^{time\_cost=1} < temporary tmp0>)

st_{space\_cost=1}^{time\_cost=6} (

temporary\_am_{space\_cost=0}^{time\_cost=1} < \text{temporary tmp0} >

, disp\_am_{space\_cost=0}^{time\_cost=1} < gpr\_W \%fp> < value\_13 -4> )

global\_cost = 18^{time\_cost=16}_{space\_cost=2}

• seq (

clr_{space\_cost=1}^{time\_cost=4} (

{\rm global\_cost} = 6^{time\_cost=5}_{space\_cost=1}

```

The respective meanings of these three derivation chains produced are respectively store, move and clear.

The first one is produced matching first the root and the left son of the PMIR with the: mov (<Reg\_or\_imm\_access AM1>, <Gpr\_access\_W AM2>)

instruction. Moreover, the destination of the initial PMIR hasn't been matched: the disp\_am access mode does not belong to the Gpr\_access\_W access class. So a universal store is produced to store the destination of the move instruction into the right destination. A full description of the pattern matching process can be found in Appendix A.

The second one is got storing the left operand of the PMIR in the temporary tmp0. Then using the access modes declared equivalent to the temporary\_am access mode in the interface, this temporary\_am access mode can be rewritten into either the gpr\_am or int\_freg\_am access modes. Then, it belongs to the Gpr\_access access class. The pattern matching with the:

```

st (<Gpr_access_W AM1>, <All_access_W AM2>)

```

instruction succeeds because the disp\_am access mode belongs to the All\_access\_W access class. Here, the temporary resource refers to two kind of registers which are respectively integer register and floating integer register. This last sort of register represents the floating point registers when used to store integers. This points out the use of the binding step after the instruction selection step.

The last one is only produced matching the root and the right son of the PMIR with the: clr (<All\_access\_W AM>)

instruction, where the displam access mode belongs to the All-access\_W access class.

Considering the costs associated with these derivation chains, the instruction selector chooses the cheapest one corresponding to the clear.

This example shows the multiple rewriting possibilities for a PMIR term in spite of its low complexity.

## Chapter 3

## **Binding**

#### 3.1 Basic concepts

At the end of the instruction selection step, each subtree of the sequence is a canonical instruction. The leaves of each instruction instance are either actual resources or temporary resources.

In order to prepare the job of the register allocator, it is necessary to bind each temporary access mode with a set of actual access modes. When a temporary is defined by a universal store tree, the related temporary am access mode is bound to the largest set of constraints deduced from the Access\_class construct of the interface. This set is restricted when the temporary is used within a following instruction.

Finally, the binder returns a set of available constraints for each temporary. Furthermore, the binder gathers use-def information that are used by the register allocator.

## 3.2 Input and output of the binder engine

#### 3.2.1 Input term

Let us consider the following result of the instruction selection process in which the LIR instruction appears with its number:

```

seq (

1

move_L (

immediate_val_am_L <immediate_value_L 1>

, disp_am_L <aregister_L a6> <immediate_value_W -4>)

2

move_L (

immediate_val_am_L <immediate_value_L 2>

, disp_am_L <aregister_L a6> <immediate_value_W -8>)

3

Univ_assign (

disp_am_B <aregister_L a6> <immediate_value_W -12>

, temporary_am <temporary tmp0>)

4

addi_W (

immediate_val_am_W <immediate_value_W 24>

, temporary_am <temporary tmp0>)

5

Univ_assign (

disp_am_L <aregister_L a6> <immediate_value_L 12>

, temporary_am <temporary tmp1>)

Univ_assign (

```

```

temporary_am <temporary tmp0>

, temporary_am <temporary tmp2>)

muls (

disp_am_W <aregister_L a6> <immediate_value_W -4>

, temporary_am <temporary tmp2> )

Univ_assign (

temporary_am <temporary tmp2>

, areg_ind_am_L <aregister_L tmp1> ))

```

#### 3.2.2 Output tables

#### 3.2.2.1 Binding constraints

This engine gathers the constraints on resources, i.e the the access modes that must be related to each of them. When a temporary tmpi is defined by a universal assignment of the form: Univ\_assign (..., temporary\_am (temporary tmpi)), it gets the maximal degree of freedom for binding, i.e it can be bound to all the access modes of the interface. This set is generally restricted when the temporary is used in a following instruction. Let us consider instruction number 4, it is a "addi\_W" instruction:

```

addi_W ( immediate_val_am_W <immediate_value_W 24> , temporary_am <temporary tmp0>)

```

It is an instance of the canonical form:

```

addi_W (<Immediate_access_W ...>). <Dregister_access_W ...>)

```

Thus temporary\_am access mode of instruction 4 must belong to the Dregister\_access\_W class, it means that the right access mode allowed for tmp0 is dreg\_am\_W.

tmp1 is bound to a aregister\_L because it appears in an areg\_ind\_am access mode in instruction 8.

tmp2 is bound to dreg\_am\_W before instruction 7 and to dreg\_am\_L in instruction 7 and after. This is set according to the template of muls that expresses that muls performs a multiplication on two word operands and puts the result as a long word in the second operand.

Finally the following constraints are built by the binder:

First a table that sets the list of resource sorts allowed for a temporary by means of its direct addressing mode.

```

\begin{array}{rcl} tmp0 & = & \{ \ dreg\_am\_W \ \}, \\ tmp1 & = & \{ \ areg\_am\_L \ \}, \\ tmp2 & = & \{ \ dreg\_am\_L \ \}. \end{array}

```

Second, a table that gives the size of a temporary in each instruction where it appears.

```

\begin{array}{rcl} tmp0 & = & [\ [3.W],[4.W],[6.W]], \\ tmp1 & = & [\ [5.L],[8.L]], \\ tmp2 & = & [\ [6.W],[7.L],[8.L]]. \end{array}

```

When tmp0 is defined in instruction 3, its size is undefined, but it takes the size "W" in instruction "addi". Similarly when tmp2 is defined in instruction 6, its size is undefined but it

takes the size "W" as an operand of the instruction muls (according to the specification of section 1.8.1); i.e before the execution of the "muls" instruction. Since the size of the destination operand of the muls instruction is "L", tmp2 takes this size from instruction 7. Finally the size of tmp1 is undefined from instruction 5, it will take the size "L" because it is bound to a aregister\_L storage class in instruction 8.

#### 3.2.2.2 Usedef tables

A use-def table has one entry per temporary. An entry for a temporary is a list of triples. A triple includes three items of information:

- the first one is the number of the instruction in which the temporary appears.

- the second one is 1 if the temporary is used in the instruction, 0 otherwise.

- the third one is 1 if the temporary is defined in the instruction, 0 otherwise.

```

\begin{array}{lll} tmp0 & = & [\ [3,0,1],[4,1,1],[6,1,0]]. \\ tmp1 & = & [\ [5,0,1],[8,1,0]]. \\ tmp2 & = & [\ [6,0,1],[7,1,1],[8,1,0]]. \end{array}

```

In the instruction number 3, tmp0 is defined since it is in destination position of a Univ\_assign. In the instruction number 4, tmp0 is used and defined in instruction 4 since it is the binary arithmetic instruction addi\_W.

## Chapter 4

## The register allocator

The input of the register allocator includes temporaries and universal store instructions. The register allocator works in two steps:

- 1. All the temporaries generated by the instruction selector or those which are already in the PMIR must be allocated, i.e the infinite set of temporaries must be restricted to the finite set of available registers of the target machine. When no more registers are available, the register allocator must choose a register and spill it in memory, that is commonly called spill code generation.

- 2. The universal store instructions must be rewritten into actual instructions of the LIR according to the colors assigned to the temporaries. In the sequel, we denote "univ\_assign\_rewriting" this step.

Finally, the output of the register allocator is a sequence of instructions in their canonical form for which assembly code can be emitted.

## 4.1 Temporary coloring and spill code production

#### 4.1.1 Basic concepts

A global register allocator achieves these goals. It is currently performed by an algorithm that is an adaptation of the Chow and Hennessy algorithm [CH 90]. A register allocator generated by Pagode uses a data-flow analysis of the LIR, the binding tables on temporaries, the description of the physical resources deduced from the target machine specification and an additional specification for the production of spill code. In this algorithm, the live range of a variable is defined as the set of basic blocks where this variable is live. A variable is colored to a single register inside a live range. During the register allocation, a live range can be split into two "sub" live ranges in order to decrease the number of coloring constraints on this live range. Therefore, a variable can be colored to different registers depending on the "sub" live ranges considered.

The concept of interfering live-ranges of variables of Chow and Hennessy has been extended to a more fine grain definition for temporaries that are alive in a single basic block.

Optimizations before code selection can introduce temporaries that are global to the whole program or local to a procedure. The instruction selector of PAGODE produces temporaries that are always local to a basic block. The register allocator is intra-procedural, it is able to handle

temporaries produced by the instruction selector as well as the temporaries that already exist in the PMIR.

Spill strategies currently available spill temporaries into a stack or into an area located in the load module at the end of the procedure. In the current state of implementation, no specific spill strategies depending on the temporary scope are available. The choice of a given strategy holds for all the temporaries. In the future, the PAGODE system will be able to apply a distinct strategy for each kind of temporaries when a symbol table for temporaries will be inherited from the front end.

Currently, the register allocator has to build the control flow graph and split the program into procedures. A procedure is supposed to have a single entry point and a single exit point.

The set of procedure names is built from the labels occurring in the instructions of the program whose **\$modification** value is "call\_proc".

The exit point of a procedure is the first instruction that has "return\_proc" as value of **\$modification**. All the following instructions that have "directive" as value of **\$modification** are expected to belong to the procedure. In particular, the register allocator is expected to find the directive giving the size of the stack among these instructions (when there is an instruction that sets the stack in the procedure).

#### 4.1.2 The target machine specification

#### 4.1.2.1 Register declarations

The description of the available registers is automatically deduced from the storage base specification in the target machine specification. More precisely, for each storage class related to registers, the following properties are given as input to the register allocator:

- the storage base,

- the access mode to access directly this storage class,

- the size in bytes (the size must be available in order to spill the right amount of bytes in the stack or in the area).

- single register or register pair.

- the actual names of the registers of this storage class.

```

size in {B, W, L}

case size is

B: size = 1 base_units

W: size = 4 base_units

L: size = 4 double base_units

End case

```

End

The input of the register allocator can be either the output of the binder engine for CISC machines or the output of the first pass of scheduling for RISC machines (see chapter 6). Register allocation on the previous example (see section 3.3) gives the following output:

```

seq (

1

immediate_val_am_L <immediate_value_L 1>

, disp_am_L <aregister_L a6> <immediate_value_W -4>)

move_L (

immediate_val_am_L <immediate_value_L 2>

, disp_am_L <aregister_L a6> <immediate_value_W -8>)

3

Univ_assign (

disp_am_B <aregister_L a6> <immediate_value_W -12>

, dreg_am_W <dregister_W d0>)

4

addi_W (

immediate_val_am_W <immediate_value_W 24>

, dreg_am_W < dregister_W d0>)

5

Univ_assign (

disp_am_L <aregister_L a6> <immediate_value_L 12>

, areg_am_L <aregister_L a0>)

6

muls (

disp_am_W <aregister_L a6> <immediate_value_W -4>

, dreg_am_L <dregister_L d0> )

Univ_assign (

, dreg_am_L <dregister_L d0> )

, areg_ind_am_L <aregister_L a0> ))

```

Instruction 6 does not exist any longer because it is a useless copy from d0 with size W to d0 with size W.

#### 4.1.2.2 Spill code strategies and target machine specification

In order to generate the appropriate spill code, the register allocator uses the spill code construct that depicts a particular computation needed by a given spill code strategy.

Two spill code strategies must be specified:

- the spill in stack strategy: the contents of a register is spilled on the stack, it is introduced by the keyword spill\_in\_stack:

- the spill in area strategy: the contents of a register is spilled into an area located in the load module at the end of the procedure, it is introduced by the keyword spill\_in\_area.

The spill code specification includes two sections, one for each of these strategies. These two sections begin with the definition of the variables of the specification denoting the values of interest.

#### 4.1.2.3 Spill in stack

The main hypotheses of this strategy are:

- There exists a fixed base and a variable offset that depends on each temporary to access a cell on the stack. A specific access mode is declared that performs this access.

- Specific load and store instructions depending on the storage class of the register are listed.

- At the end of each procedure, there is a directive that gives the equivalence between a label and the stack size.

- The stack is allocated at the beginning of the execution of the procedure using the label variable.

First of all, the compiler writer must declare the names of the variables denoting the offset, label, register and stack\_size values.

Then he must specify the access mode used to describe the access path to a cell of a stack using the offset variable is specified. For instance:

```

disp_am!size (<aregister_L a6>, <immediate_value_W X>)

```

The load keyword begins a construct where the instructions that can be used to load the contents of a cell of the stack in a given register are specified. There must be one load instruction specification per parameterized storage class of register.

Secondly, the **store** construct depicts the instructions that can be used to store the contents of a given register in a cell of the stack. The PAGODE constructor checks the consistency between the load and the store parts declarations.

The spill code generator works under the hypothesis that a spill instruction is always specified giving the parameters in the following order: first the source operands then the destination operand.

The stack\_link construct declares the instruction used to load the stack base.

The def\_stack\_size construct describes the directive that fixes the size of the stack for a procedure.

```

Spill code

case spill_in_stack:

\mathbf{offset}: X;

label: LAB;

register: REG;

stack_size : STACK_SIZE;

Reserved registers: < aregister a6>

Access_mode:

disp_am!size (<aregister_L a6>, <immediate_value_W X>)

load:

move!size (disp_am!size (<aregister_L a6>, <immediate_value_W X>)

, dreg_am!size (<dregister!size REG>))

where size in { B, W, L }

move!size (disp_am!size (<aregister_L a6>, <immediate_value_W X>)

, areg_am!size (<aregister!size REG>))

where size in { W, L }

store:

move!size (dreg_am!size (<dregister!size REG>))

, disp_am!size (<aregister_L a6>, <immediate_value_W X>)

```

```

where size in { B, W, L }

move!size (areg_am!size (<aregister!size REG>))

, disp_am!size (<aregister_L a6>, <immediate_value_W X>)

where size in { W, L }

stack_link:

link (areg_am_L (<aregister_L a6>)

, immediate_dlab_am_W (<data_label_W LAB>))

def_stack_size:

equ (immediate_dlab_am_W (<data_label_W LAB>)

, immediate_val_am (<immediate_value_W STACK_SIZE>))

Resource_length

case size is

B:1

W:4

L:8

End case

case spill_in_area:

{ . . .

```

An example that has been run with the two stategies one after the other can be found in appendix B. In order to demontrate the results of spill code generation, the number of available data registers has been reduced to d0 and d1.

#### 4.2 Universal store rewriting

#### 4.2.1 Basic concepts

At the end of the previous step, all instructions that are not universal stores match exactly the target machine specification. Owing to the previous step, the operands of the universal stores are actual access modes on actual resources.

The remaining task consists in finding an instruction of the spill or load or store families that matches the operands. If such an instruction exists, the universal store operator is rewritten according to this instruction. Otherwise, the PAGODE system assumes that there is a size misfit. In some cases, there exist assembly instructions that perform size conversions. This must be specified by the compiler writer in a special purpose construct called **Convert declaration**. If such a misfit can be solved by a conversion instruction, this instruction is inserted. By default, the PAGODE system assumes that the implicit conversion is performed by the assembler and the operand that will be converted is chosen: it is an operand that does not refer to the memory. The size of that operand is modified in order to match an instruction.

#### 4.2.2 Target machine specification

#### 4.2.3 The convert constructor

A convert declaration specifies a list of conversions. An item of this list associates a conversion between two access modes that only differ on their sizes and the instruction to generate when this conversion is applied.

Let us consider the conversion instructions on the MC68000:

#### Convert declaration

```

areg_am_W (<aregister_W X>) -> areg_am_L (<aregister_L X>)

: movea_W (areg_am_W(<aregister_W X>)

. areg_am_L (<aregister_L X>))

dreg_am_W (<dregister_W X>) -> dreg_am_L (<dregister_L X>)