# Accelerating Reinforcement Learning-Based CCSL Specification Synthesis Using Curiosity-Driven Exploration

Ming Hu, Min Zhang, Frédéric Mallet, Xin Fu, Mingsong Chen

#### ▶ To cite this version:

Ming Hu, Min Zhang, Frédéric Mallet, Xin Fu, Mingsong Chen. Accelerating Reinforcement Learning-Based CCSL Specification Synthesis Using Curiosity-Driven Exploration. IEEE Transactions on Computers, 2023, 72 (5), pp.1431-1446. 10.1109/TC.2022.3197956. hal-04178227

### HAL Id: hal-04178227 https://inria.hal.science/hal-04178227v1

Submitted on 23 Oct 2024

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Accelerating Reinforcement Learning-based CCSL Specification Synthesis Using Curiosity-Driven Exploration

Ming Hu, Student Member, IEEE, Min Zhang, Member, IEEE, Frédéric Mallet, Member, IEEE, Xin Fu, Senior Member, IEEE, and Mingsong Chen, Senior Member, IEEE

#### Abstract

The Clock Constraint Specification Language (CCSL) has been widely acknowledged as a promising system-level specification for the modeling and analysis of timing behaviors of real-time and embedded systems. However, along with the increasing complexity of modern systems coupled with strict time-to-market constraints, it becomes more and more difficult for requirement engineers to accurately figure out CCSL specifications from natural language-based requirement documents, since they lack both expertise in formal CCSL modeling and design automation tools to support quick and automatic generation of CCSL specifications. To solve the above problem, in this paper we introduce a novel and efficient Reinforcement Learning (RL)-based synthesis approach that can facilitate requirement engineers to quickly figure out their expected CCSL specifications. For a given incomplete CCSL specification, our approach adopts RL-based enumeration to explore all the feasible solutions to fill the holes within CCSL constraints, and leverages curiosity-driven exploration to accelerate the enumeration process. Based on the combination of our proposed curiosity-driven exploration heuristic and deductive reasoning techniques, our approach can not only prune unfruitful enumeration solutions effectively, but also optimize the enumeration process to search for the tightest solution quickly, thus the overall synthesis process can be accelerated dramatically. Comprehensive experimental results demonstrate that our approach significantly outperforms state-of-the-art methods in terms of both synthesis time and synthesis accuracy.

##

#### 1 Introduction

Model-driven design and implementation of real-time and embedded systems have become an effective means of developing trustworthy systems [1], [2]. Modeling languages play an essential role in model-driven approaches. They are expected to formally and rigorously describe requirements, constraints, properties, and designs of the systems to be developed and meanwhile to be expressive and natural to engineers. The *Clock Constraint Specification Language* (CCSL) is such an emerging modeling language, companioning a UML profile called *Modeling and Analysis of Real-Time and Embedded systems* (MARTE) [3], [4]. CCSL has attracted attention from both industrial and academic communities [5], [6], [7]. A main feature of CCSL is that it devises *logical clocks* to model the temporal dependencies and constraints on system events. This feature abstracts physical details of events and focuses on only logical aspects, making CCSL more amenable to compose and more efficient to verify than physical clock-based languages. For these merits, CCSL has become a promising formalism at the *Formal Specification Level* [8] to accurately model and analyze the causal and temporal timing behaviors of real-time and embedded systems [9], [10].

Similar to other modeling languages, CCSL faces the same challenge when used to model real-world systems, i.e., going from natural language to formal models is an inherently difficult process as it means removing potential ambiguities from the natural language description. Picking one semantic variation over another one may have many unforeseen effects on the global behavior. The challenge has become one of the major obstacles in applying formal languages like CCSL to model complex real-time and embedded systems. Worse still, due to the skyrocketing complexity of real-time and embedded systems, it is almost impossible for requirement engineers to enumerate all the possible timing behaviors (traces) of a system, particularly at the early design phase. Consequently, CCSL specifications have to be composed mainly based on very limited expectations on system timing behaviors, stipulating what should happen (as specifications do). It makes the CCSL specification generation process both time-consuming and error-prone, requiring a number of refinement steps before the specifications are used for verification and validation purposes [11], [12]. Existing validation-and verification-based methods [13], [14], [15] and tools [16] for CCSL are proposed under the assumption that the specifications are complete and ready for verification. Although such methods are effective in detecting the flaws of specifications or verifying certain properties of them, it is a dilemma that incomplete specifications that are not "ready-to-verify" cannot be verified by any tool, presumably.

Specification synthesis has been recognized as an effective approach to generating formal specifications [17], [18]. It leverages automatic reasoning techniques to learn potential candidate solutions to the missing parts in incomplete specifications based on the collected system information such as execution sequences, logs, and behaviors. In the context of CCSL specification synthesis, most

Ming Hu, Min Zhang and Mingsong Chen are with the Shanghai Key Lab of Trustworthy Computing at East China Normal University, Shanghai, 200062,

China (email: ecnu\_hm@163.com, {zhangmin, mschen}@sei.ecnu.edu.cn). Frédéric Mallet is with Université Cote d'Azur, CNRS, Inria, 13S, France (email: Frederic.Mallet@inria.fr). Xin Fu is with the ECE Department at University of Houston, Houston, TX 77204, United States (email: xfu8@central.uh.edu).

requirement engineers typically can figure out part of specifications based on their experience, leaving the unknown parts of causal and temporal constraints blank. As the first attempt to synthesize CCSL specifications, CCSLSketch [19], [20] enables the encoding of an incomplete CCSL specification together with its samples (i.e., expected timing traces) as a sketching problem, where the holes of incomplete CCSL constraints in the sketch can be filled automatically. However, since sketching is based on SAT solving, the scalability of CCSLSketch is strongly limited due to the state space explosion problem, especially for complex CCSL problems with a large number of correlated clocks and operators. Moreover, without considering the high-level syntax information of sketches, the underlying SAT solving of CCSLSketch may easily get stuck in local search, thus the synthesis time can be significantly prolonged. Therefore, for a given incomplete CCSL specification, it is desired to devise an effective approach to quickly figure out an optimal hole filling scheme among all the hole combinations satisfying the given timing traces.

Inspired by the curiosity mechanisms in [21], [22] and deduction work in [23], [24], this paper introduces a novel Reinforcement Learning (RL)-based CCSL specification synthesis method. To efficiently perform RL exploration, our approach tightly couples the merits of our proposed Curiosity-Driven Exploration (CDE) heuristic with deduction methods, thus accelerating the overall specification synthesis process. By formulating the syntax-guided CCSL specification synthesis based on hole enumerations as an RL problem, our approach formalizes a Markov Decision Process (MDP) for the RL training, where partial CCSL specifications are encoded as states and hole fillings are encoded as actions. Starting from an initial synthesis policy (i.e., a blank RL model) without any prior knowledge, our approach gradually improves the policy based on the MDP, which finally can be used to specify how to fill the holes of an incomplete CCSL specification to approximate its best-possible complete counterpart. To accelerate the convergence of policy generation, we resort to the help of our proposed CDE heuristic and deduction mechanisms as follows. Assume that *Spec* is an incomplete CCSL specification and *P* is the policy for *Spec*. By resorting to CDE, our approach can wisely fill one hole of *Spec* to get a more complete and suitable specification *Spec'*. Then, our approach uses the deductive reasoning methods to check whether *Spec'* is valid (i.e., *Spec'* admits the given traces) and update *P* accordingly based on our proposed reward mechanism. In this way, the deduction engine of our approach can refuse a filled CCSL specification at its earliest stage if it is invalid. The above RL training process repeats until *P* converges, which can finally be used to derive an optimal synthesis solution for the incomplete CCSL specification. Aiming at accelerating the above RL-based CCSL specification synthesis process, this paper makes the following **three major contributions**:

- 1) Based on our proposed state representation and reward design, we establish a novel RL-based synthesis framework, which involves various deduction reasoning mechanisms to enable efficient synthesis of CCSL specifications automatically.

- We develop a new CDE method based on two tables (i.e., greed table and curiosity table) to support the wise selection of benign hole-filler candidates during the RL-based synthesis process, which can dramatically accelerate the search for optimal solutions.

- 3) We conduct experiments on both well-known benchmarks and complex industrial examples to show the effectiveness of our approach. Especially, our proposed CDE heuristic not only can reduce synthesis time significantly, but also further enhance the synthesis accuracy.

The remainder of this paper proceeds as follows. Section 2 presents the related work of program synthesis and CCSL specification formalization. Section 3 introduces CCSL notations. Section 4 describes the implementation of our curiosity- and deduction-driven approach in detail. Section 5 presents the results of performance evaluation. Finally, Section 6 concludes the paper.

#### 2 RELATED WORK

Along with the increasing popularity of CCSL in timing behavior modeling of real-time and embedded systems [5], [6], [7], [25], [26], more and more verification methods based on CCSL specifications have been studied to check various desired timing properties of target systems. For example, schedulability is one of the critical properties that should be formally guaranteed. If a specification is not schedulable, it implies that there must be a deadlock where no event can be triggered. To address this issue, Yin *et al.* [29] and Zhang *et al.* [30], [31] developed various effective techniques to support the schedulability analysis of complex CCSL specifications. Besides, more complex temporal properties formalized in temporal logic such as Linear Temporal Logic (LTL) are also verifiable [15] in CCSL. Apart from static analysis, runtime verification is another powerful approach in which the correctness of system behaviors is verified based on CCSL specifications at run time [25]. Although the above methods are promising in verifying the desired properties of CCSL specification from different perspectives, most of them assume that the CCSL specifications to be checked are all complete, which is not always true in practice. To ease the formal modeling process of CCSL specifications, a variety of approaches have been investigated, such as providing user-friendly GUI for requirement modeling engineers [16], transforming from other existing models [27], and iterative verification and refinement [28]. However, most of them require both human efforts and expertise. In this paper, our RL-based approach tries to reduce human intervention and efforts as must as possible in the modeling process.

As for specification synthesis, its effectiveness has been acknowledged to support the automated generation of formal specifications from requirements, system execution logs, or other textual descriptions [17], [18]. To support automated generation of CCSL specifications from incomplete templates, Hu *et al.* [19] proposed a promising method named CCSLSketch, which encodes the synthesis of an incomplete CCSL specification against provided timing behaviors into a sketching problem. However, since sketching is implemented based on Satisfiability Modulo Theories (SMT) solving that is essentially a generalization of the SAT problem, the applicability of CCSLSketch is inevitably limited. Generally, when dealing with complex CCSL specifications with multiple holes, CCSLSketch requires significantly more time and resources to achieve synthesis results. To reduce the time overhead, more and more specification synthesis methods resorted to RL techniques and deduction operations to explore desired enumeration solutions, since they are good at pruning unfruitful enumeration spaces. For example,  $\lambda 2$  [32] and FlashMeta [33] adopted various effective methods, e.g., inverse

semantics and refutation, to decompose the synthesis task and guide the program search. By combining both deductive and statistical reasoning mechanisms, Chen *et al.* [23] introduced a domain-specific language synthesis algorithm, which uses RL to search for implementations under the guidance of an SMT-based deduction engine. In [24], Huang *et al.* proposed a cooperative synthesis framework called DryadSynth, which decomposes a synthesis problem into multiple subproblems and solves them individually based on both enumeration and deduction operations. Inspired by the above methods, to reduce the overall synthesis time, in this paper we propose a novel synthesis method for CCSL specifications based on RL-related techniques rather than using SAT- or SMT-based search.

As a promising heuristic to enable wise exploration on RL models, the curiosity mechanism has been widely investigated in RL to solve tasks with sparse rewards. Since curiosity-based methods enable more effective and sufficient search in RL, it has been used to potentially reduce the convergence time of RL training. For example, Pathak *et al.* [34] used the prediction error of forward dynamics models to some agent as an intrinsic reward to guide its exploration, where the extrinsic rewards to the agent are extremely sparse. In [21], Zheng *et al.* proposed an RL-based web testing framework that leverages a novel curiosity-driven reward function to efficiently explore diverse behaviors of web applications. In [22], Cao *et al.* introduced an effective human-machine interface software exploration framework named PathFinder, which uses a curiosity-based RL framework to choose actions that lead to the discovery of more unknown states. Although the above methods are promising in learning helpful knowledge for future scenarios, none of them can be directly applied on CCSL specification synthesis, since they are application-specific. To the best of our knowledge, our work is the first attempt that combines both deduction and CDE techniques to enable quick RL-based CCSL specification synthesis.

#### 3 PRELIMINARIES OF CCSL

Logical clocks represent repetitive system events without assuming any regular distance between two successive occurrences. The "real-time" is treated as a special cases where successive tags associated with each occurrence are evenly spread. In CCSL, the logical clocks [35] are inspired from Leslie Lamport's logical clocks and clocks of the synchronous languages. Logical clocks give a most welcome elasticity when building specifications as the time is spread as much as needed to insert details when needed.

**Definition 3.1 (Logical Clocks).** A logical clock c is a predicate over natural numbers. For any  $i \in \mathbb{N}^+$ , c(i) denotes that: i) if c is true at step i, c ticks at that step; or ii) if c is false, c is idle at step i.

According to their expressive power, logical clocks are classified into two categories, i.e., atomic clocks and expression clocks. An atomic clock is declared to represent a physical event in systems, while an expression clock is defined over existing clocks based on a certain relation. Such relations are defined by two types of operators, where relation operators (i.e.,  $O_b = \{=, <, \leq, =, \#, >, \geq, \geq\}$ ) are binary operators that define binary relations between clocks, and expression operators (i.e.,  $O_d = \{+, *, \land, \lor, \$, \propto\}$ ) are definitional operators that construct new clocks using other existing clocks.

TABLE 1 Syntax and Semantics of CCSL Operators

| Constraint   | Syntax                          | Semantics                                                                                                           |

|--------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Causality    | $c_1 \leq c_2$                  | $\chi_{\delta}(c_1, i) \ge \chi_{\delta}(c_2, i)$                                                                   |

| Coincidence  | $c_1 = c_2$                     | $\chi_{\delta}(c_1, i) = \chi_{\delta}(c_2, i)$                                                                     |

| Exclusion    | $c_1 \# c_2$                    | $c_1 \notin \delta(i) \lor c_2 \notin \delta(i)$                                                                    |

| Precedence   | $c_1 \prec c_2$                 | $(\chi_{\delta}(c_1, i) = \chi_{\delta}(c_2, i)) \implies c_2 \notin \delta(i)$                                     |

| Subclock     | $c_1 \subseteq c_2$             | $c_1 \in \delta(i) \implies c_2 \in \delta(i)$                                                                      |

| Delay        | $c_1 \triangleq c_2 \$ d$       | $\chi_{\delta}(c_1, i) = \max(\chi_{\delta}(c_2, i) - d, 0)$                                                        |

| Infimum      | $c_1 \triangleq c_2 \wedge c_3$ | $\chi_{\delta}(c_1, i) = \max(\chi_{\delta}(c_2, i), \chi_{\delta}(c_3, i))$                                        |

| Intersection | $c_1 \triangleq c_2 * c_3$      | $c_1 \in \delta(i) \iff c_2 \in \delta(i) \land c_3 \in \delta(i)$                                                  |

| Periodicity  | $c_1 \triangleq c_2 \propto p$  | $c_1 \in \delta(i) \iff c_2 \in \delta(i) \land \exists j \in \mathbb{N}^+, \chi_{\delta}(c_2, i) = j \times p - 1$ |

| Supremum     | $c_1 \triangleq c_2 \lor c_3$   | $\chi_{\delta}(c_1, i) = \min(\chi_{\delta}(c_2, i), \chi_{\delta}(c_3, i))$                                        |

| Union        | $c_1 \triangleq c_2 + c_3$      | $c_1 \in \delta(i) \iff c_2 \in \delta(i) \lor c_3 \in \delta(i)$                                                   |

Table 1 presents both the syntax and semantics of all the operators involved in CCSL constraints defined as follows. Due to space limitation, please refer to [7] for more explanations about the formal semantics of CCSL operators.

**Definition 3.2 (CCSL Constraints).** Let c,  $c_1$ ,  $c_2$  be logical clocks. A CCSL constraint is in one of the following four forms:

$$c_1 ? c_2$$

, where  $? \in O_b$  (1)

$$c_e \triangleq c_1 ? c_2$$

, where  $? \in O_d \setminus \{\$, \infty\}$  (2)

$$c_e \triangleq c \ \$ \ d$$

, where  $d \in \mathbb{N}^+$  (3)

$$c_e \triangleq c \propto p$$

, where  $p \in \mathbb{N}^+$  (4)

In Table 1, the semantics of CCSL operators is formalized based on the notations of *schedule* and *history*. According to Definition 3.3, we use a schedule  $\delta$  to describe a specific behavior of logical clocks. For a given time step i,  $\delta(i)$  represents the set of clocks that tick at step i, where  $\delta(i) \subseteq C$ . In CCSL, schedules are partially reflected by system traces, where a *trace* denotes a finite sequence of system events logged by their occurring time. Typically, a CCSL specification consists of a collection of constraints to which all the feasible schedules should conform. We say that a CCSL specification admits a system trace if the trace conforms to all the specification constraints.

**Definition 3.3 (Schedule).** Given a clock set C, a schedule is a total function  $\delta : \mathbb{N}^+ \to 2^C$  such that a clock  $c \in C$  ticks at step  $i \in \mathbb{N}^+$  if and only if  $c \in \delta(i)$  and  $\delta(i) \neq \emptyset$ .

In CCSL, logical clocks need to record how many ticks they have ticked in the past up to the current step. Let  $\chi_{\delta}$  be the *history* of  $\delta$ . For a given schedule  $\delta$  and a clock c, we use  $\chi_{\delta}(c,i)$  to denote the number of steps where c ticks before step i. In other words,  $\chi_{\delta}(c,i)$  represents the number of ticks of c up to step i-1.

**Definition 3.4 (History).** Let  $\delta$  be a schedule over clock set C. the history of  $\delta$  is a function in the form of  $\chi_{\delta}: C \times \mathbb{N}^+ \to \mathbb{N}$ , where

$$\chi_{\delta}(c,i) = \left\{ \begin{array}{ll} \chi_{\delta}(c,i-1) + 1 & \quad \text{if } c \in \delta(i-1), \\ \chi_{\delta}(c,i-1) & \quad \text{if } c \notin \delta(i-1), \\ 0 & \quad \text{if } i = 1. \end{array} \right.$$

We take the semantic definition of precedence as an example to explain how CCSL constraints are defined by the concepts of schedule and history. Given a schedule  $\delta$  and a constraint  $c_1 < c_2$ , we say that  $\delta$  satisfies  $c_1 < c_2$  (denoted by  $\delta \models c_1 < c_2$ ) if and only if the condition  $(\chi_{\delta}(c_1,i) = \chi_{\delta}(c_2,i)) \Longrightarrow c_2 \notin \delta(i)$  holds for all  $i \in \mathbb{N}^+$ . Here, if  $c_1$  and  $c_2$  have the same number of ticks before step n,  $c_2$  cannot occur at step n, i.e.,  $c_1$  always has more ticks than  $c_2$ . As a result, we can conclude that  $c_1$  precedes  $c_2$ . That is, the tick of  $c_2$  must be caused by a corresponding tick of  $c_1$ . Given a set of constraints, one fundamental issue known as *schedulability* [36] is to decide whether there exists a schedule satisfying all the constraints. If the set of constraints is not schedulable, there should be semantic conflicts among the constraints.

#### 4 Our RL-Based CCSL Specification Synthesis Method

This section introduces a novel approach that can naturally convert the synthesis process of an incomplete CCSL specification into an RL problem. Unlike traditional RL approaches, our method fully investigates the synergy between both CDE heuristic and deductive mechanisms to guide the whole RL learning process, where the CDE heuristic is used to enable effective action selection and the deduction mechanisms are used to prune logically invalid candidate solutions. Under the guidance of the combination of CDE heuristic and deductive techniques, our approach can quickly achieve an optimal solution with significantly less effort compared with state-of-the-art methods.

#### 4.1 Problem Formulation and Encoding

Due to the increasing complexity of real-time and embedded systems, it becomes more and more difficult to figure out complete CCSL specifications for timing behavior modeling at the beginning of requirement design. Typically, requirement engineers build CCSL specifications based on various kinds of modularized CCSL templates of system components in a bottom-up manner and leave various uncertainties as blanks (i.e., holes) during CCSL constraint design, resulting in incomplete specifications. An an example shown in [38], to model the timing behaviors of all the involved traffic lights of an intersection with a specific type (e.g., T-intersection, and cross intersection), requirement engineers can firstly construct an incomplete CCSL specification based on the CCSL template for a single traffic light, leaving the timing behaviors of traffic light interactions unspecified as holes. Based on the provided timing traces of expected traffic control scenarios, our approach can automatically and quickly figure out the CCSL specification for a specific-type interaction to enable accurate traffic control. In this subsection, we formalize the CCSL synthesis problem in terms of filling holes under the guidance of given system traces, and encode the CCSL synthesis as a classical RL problem based on a specific Markov decision process.

#### 4.1.1 CCSL Specification Synthesis

An incomplete CCSL specification may contain four kinds of holes, i.e.,  $\Box_o^b$ ,  $\Box_o^d$ ,  $\Box_c^d$ , and  $\Box_c^d$ , denoting holes for relation operators, expression operators, relation clocks, and expression clocks, respectively. Each hole indicates a placeholder for a specific clock or operator. For example, we use  $\Box_o^d$  and  $\Box_o^d$  to denote holes, whose candidate values come from  $O_b$  and  $O_d$ , respectively.

**Definition 4.1 (Incomplete CCSL Constraint).** An incomplete CCSL constraint is a constraint that contains one and only one hole h  $(h \in \{\Box_a^b, \Box_c^d, \Box_c^b, \Box_c^d, \Box_c^b, \Box_c^d\})$  for either a clock or an operator.

An incomplete CCSL specification is a set including both regular constraints and incomplete constraints. The synthesis of incomplete CCSL specifications tries to automatically generate full CCSL specifications with all the holes filled according to the given auxiliary information. In our approach, we synthesize CCSL specifications based on the execution timing traces of systems, where each execution timing trace is a sequence of ordered events that occur temporally. It is required that a synthesized full (complete) CCSL specification should admit all the provided execution timing traces.

**Definition 4.2 (CCSL Specification Synthesis Problem).** For a given incomplete CCSL specification  $\Phi$  and a set T of expected execution timing traces, the synthesis of  $\Phi$  using T is to fill all the holes in  $\Phi$  such that the completed specification can admit all the traces in T.

For a CCSL specification synthesis problem, based on a limited number of expected execution timing traces, there can be numerous solutions to filling holes. For two synthesized specifications s and s', we say that s is tighter than s' if s covers fewer traces that are not included in t than t. In this paper, our synthesis method focuses on searching for the tightest solutions (i.e., *golden references*) to incomplete CCSL specifications. It is important to note that, due to semantic conflicts among the constraints, there may exist no solutions for filling the holes. In other words, the synthesis will fail eventually.

**Definition 4.3 (Specification Tightness).** Assume that  $\Phi$  and  $\Phi'$  are two synthesized results of an incomplete CCSL specification  $\Phi_{\square}$ . We say that  $\Phi$  is tighter than  $\Phi'$  if and only if  $\delta \models \Phi$  implies  $\delta \models \Phi'$  for any schedule  $\delta$ . If there exist no completed specification that is tighter than  $\Phi$ , then  $\Phi$  is the tightest solution to  $\Phi_{\square}$ .

Since our approach is based on RL, the synthesis results may vary due to randomness. To enable fair comparison with state-of-the-art methods, we repeat the synthesis method for multiple times to achieve a set of synthesis results. We introduce the concept of *synthesis accuracy* as defined in Definition 4.4 to denote the ratio of the tightest solutions to all synthesis results in the set.

**Definition 4.4 (Synthesis Accuracy).** Let  $\Phi$  be an incomplete CCSL specification and T is a set of its expected execution timing traces. Assume that  $\Sigma = \{\sigma_1, \sigma_2, ..., \sigma_n\}$  is a finite set of synthesized solutions under  $\Phi$  and T, and  $\Sigma' = \{\sigma'_1, \sigma'_2, ..., \sigma'_m\}$  is a subset of  $\Sigma$  containing all and only the tightest solutions. The synthesis accuracy equals to  $\frac{m}{n}$ , indicating the ratio of the tightest solutions in  $\Sigma$ .

#### 4.1.2 MDP Encoding for CCSL Synthesis

Inspired by the success of RL in program synthesis [23], [37] and satisfiability problem solving [39], [40], the CCSL synthesis can be regarded as an RL process of filling candidate clocks or operators into the holes of incomplete constraints. This RL process can be modeled as an MDP [41], where agents get rewarded or punished based on their decisions on hole filling. In our approach, a state in the MDP is denoted by a list of holes, while an MDP transition indicates an action of filling one hole in the list. More precisely, the synthesis process of an incomplete CCSL specification can be formulated as an MDP in the form of a 4-tuple  $M = (S, \mathcal{A}, \mathcal{F}, \mathcal{R})$ , where:

- S is a set of states, where a state is a list whose elements are in the form of a 2-tuple  $\langle \Box^i, v \rangle$ , indicating whether an indexed hole  $\Box^i$  (i.e., a hole at index i) has been filled with some candidate value v. Here, we use the index i to specify the hole position in the list. If v equals null, it means that the hole  $\Box^i$  has not been filled yet. At the very beginning of RL, none of the holes for an incomplete specification is filled. Therefore, for the initial state, the value of each element in the list is null. On the contrary, a terminal state is represented by a list with all the element holes filled, indicating a possible solution for the synthesis. To prevent RL from repeated searches, our approach requires that holes to be filled in a specific order. For example, assume that  $\langle \Box^i, v_i \rangle$  and  $\langle \Box^j, v_j \rangle$  are two elements in the same list (state). If i < j,  $v_i = null$  implies  $v_j = null$ .

- $\mathcal{A}$  is a set of actions indicating filling holes with specific values. An element of  $\mathcal{A}$  is a hole-value mapping. in the form of  $(\Box^i, v)$ , denoting an action that fills an indexed hole  $\Box^i$  with some value v (i.e., a clock or an operator) depending on the hole type.

- $\mathcal{F}: \mathcal{S} \times \mathcal{A} \to \mathcal{S}$  is a transition function represented by a set of transitions, where each transition is in the form of  $\alpha \xrightarrow{(\square^i, v)} \alpha'$ . Here  $\alpha'$  is the successor state of  $\alpha$  by assigning  $\square^i$  with a value v.

- $\mathcal{R}: \mathcal{S} \to \mathbb{R}$  denotes a reward function. By using a predefined function  $\mathcal{R}(s) = RewardEvaluator(s)$ , our approach adopts an evaluator to conduct a reward or punishment when RL reaches a state s.

Taking the CCSL specification shown at the bottom left of Figure 1 as an example, the incomplete specification has six CCSL constraints, where four of them are incomplete. It has six clocks including four atomic clocks (i.e.,  $c_0$ ,  $c_1$ ,  $c_2$ , and  $c_3$ ) and two expression clocks (i.e.,  $e_0$  and  $e_1$ ). Based on the hole types, we can figure out the candidate values for each hole for the synthesis. For example,  $H_0$  is an expression clock hole, and  $H_2$  is a relation clock hole. Therefore, the values of  $H_0$  and  $H_2$  come from the clock set  $C = \{c_0, c_1, c_2, c_3, e_0, e_1\}$ . Since  $H_1$  is an expression operator hole, its candidate value will be selected from the set  $O_t = \{+, *, \land, \lor\} \subset O_d$ . As a relation operator hole, the candidate value of  $H_3$  belongs to the set  $O_b = \{=, <, \leq, \subseteq, \#, \gt, \geq, \supseteq\}$ . According to the definition, we construct one specific MDP  $M = (S, \mathcal{A}, \mathcal{F}, \mathcal{R})$  for the incomplete specification as follows.

- State set S. In this example, an MDP state is a list in the form of  $[\langle H_0, v_0 \rangle, \langle H_1, v_1 \rangle, \langle H_2, v_2 \rangle, \langle H_3, v_3 \rangle]$ , indicating the filling of four holes. Initially, the values of all the holes in the list equal to null, i.e.,  $[\langle H_0, null \rangle, \langle H_1, null \rangle, \langle H_2, null \rangle, \langle H_3, null \rangle]$ . After figuring out the hole types, we need to enumerate the holes one by one. The assignment of  $H_{i+1}$  is not allowed until  $H_i$  has been filled. We call a state a terminal state when all of its holes are filled, e.g.,  $[\langle H_0, c_0 \rangle, \langle H_1, * \rangle, \langle H_2, c_0 \rangle, \langle H_3, + \rangle]$ . In total, the MDP has  $|C| \times |C| \times |O_t| \times |O_b| = 1152$  possible terminal states.

- Action set  $\mathcal{A}$ . For a hole  $H_i$ , we use  $\mathcal{A}(H_i)$  to indicate a set of all possible actions that can be applied on  $H_i$ , where an element of  $\mathcal{A}(H_i)$  is a mapping in the form of  $(H_i, v_i)$ , indicating filling the hole  $H_i$  with a value  $v_i$ . Taking  $H_0$  as an example, the action set of  $H_0$  is  $\mathcal{A}(H_0) = \{(H_0, c_0), (H_0, c_1), (H_0, c_2), (H_0, c_3), (H_0, e_0), (H_0, e_1)\}$ . If no specific hole is specified,  $\mathcal{A}$  denotes the action set for all the holes, which equals to the union  $\mathcal{A}(H_0) \cup \mathcal{A}(H_1) \cup \mathcal{A}(H_2) \cup \mathcal{A}(H_3)$ .

- Transition set  $\mathcal{F}$ . A transition  $\alpha \stackrel{(H_i, v_i)}{\longrightarrow} \alpha'$  in  $\mathcal{F}$  indicates the effect of an action  $(H_i, v_i)$ , where  $\alpha$  and  $\alpha'$  are a non-terminal state and its successor state, respectively. The transition is enabled only when either i = 0 or  $v_i$  is *null* and  $v_{i-1}$  is not *null*. If the transition is triggered, the value of  $v_i$  in the current state  $\alpha$  will change from *null* to a candidate clock or operator.

- Reward function  $\mathcal{R}$ . Our reward function is the same as the one defined in [42], which can determine the quality (i.e., tightness) of specification synthesis results.

#### 4.2 Overview of Our Approach

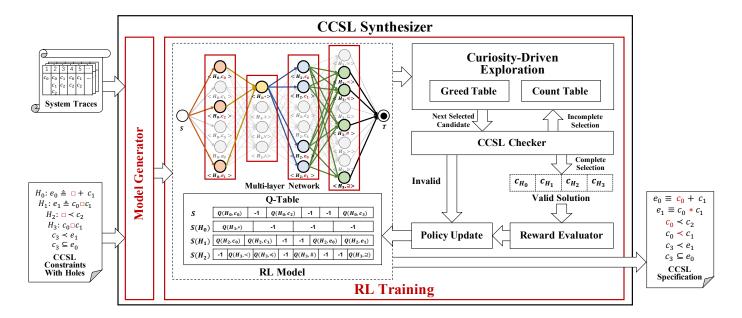

We adopt a classic RL algorithm, i.e., Q-learning [41], for CCSL specification synthesis. Figure 1 depicts an overview of our RL-based CCSL synthesis approach. The approach has two inputs, i.e., an incomplete CCSL specification (i.e., a set of incomplete CCSL constraints) and its corresponding system traces (i.e., execution timing traces). The output of our approach is a synthesized CCSL specification, which is complete and admits the given system traces. Our approach mainly consists of two steps, i.e., initial RL model generation by the model generator (see Section 4.1.2 for more details) and RL model training. At the beginning of specification

Fig. 1. Architecture and Workflow of our CCSL synthesizer accelerated by curiosity-driven exploration

synthesis, the model generator parses the two inputs and establishes a compact RL model including: i) a multi-layer network for MDP modeling and simulation, and ii) a Q-table for the training and generation of the best policy. As the key data structures of our approach, they are used in the RL training driven by our proposed CDE heuristic and deduction techniques. The RL training tries to explore the solution space of the given incomplete CCSL specification to quickly figure out an optimal solution. To make the exploration more efficient and sufficient, we use the CDE heuristic to guide the selection of candidate values. The deduction parts (i.e., CCSL checker and reward evaluator) have two main functions: i) checking whether an explored candidate solution admits the given system traces, and ii) performing reward evaluation for a candidate solution.

The workflow of our RL model training is as follows. After the establishment of an initial model based on input constraints and system traces, we use CDE to make the decisions of hole selection one by one until all the holes are filled. If one invalid hole filling is detected by the CCSL checker halfway, a penalty will be imposed on the Q-table. Otherwise, once all the holes are filled and the solution is valid, the reward evaluator will calculate the rewards for all the hole selection actions and update the Q-table accordingly. Note that, in our approach, one round of RL training involves only one update of the Q-table. In other words, any invalid hole selection made by the CCSL checker will lead to a new round of RL training (i.e., hole enumeration). Finally, the RL training terminates when either the training process converges or the specified number of training rounds ends. The following subsections present the key concepts and implementations of our approach in detail.

#### 4.3 Initial RL Model Construction

Based on the MDP definition presented in Section 4.1.2, the goal of our Q-learning-based specification synthesis approach is to derive a policy  $\pi$ , which can reach a terminal state and get a maximum reward. To enable Q-learning-based synthesis, our model generator can automatically construct an initial RL model (i.e., a multi-layer network coupled with its Q-table) from an incomplete CCSL specification, where the underlying MDP procedure is simulated on top of the multi-layer network, and the Q-table is used to record credits for hole filling actions during the decision-making processes.

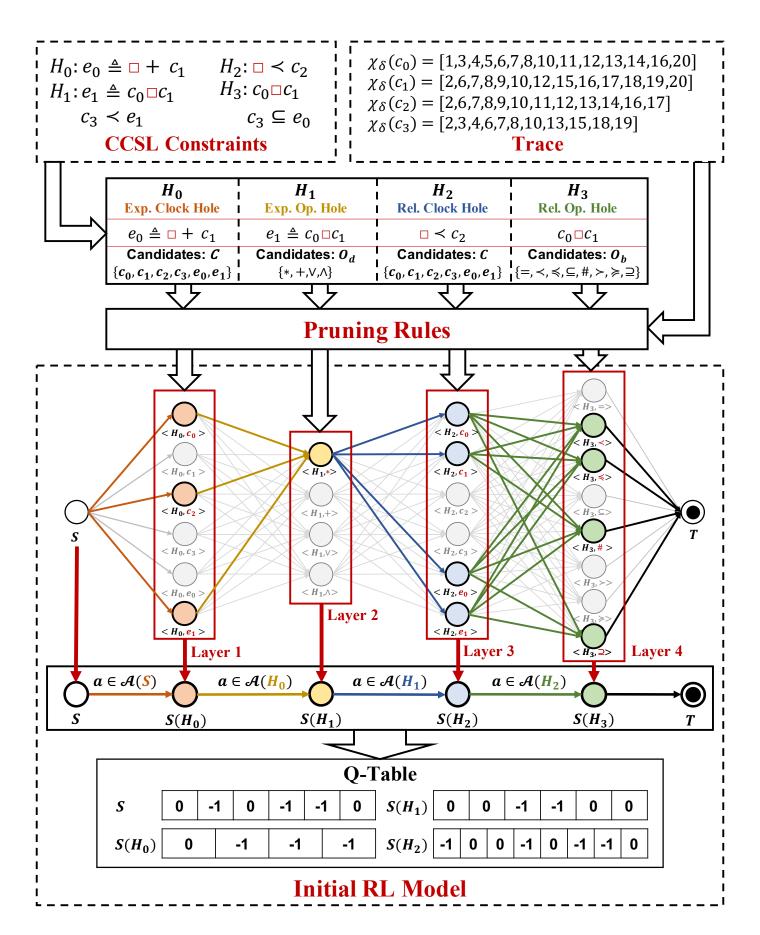

Based on the example presented in Figure 1, Figure 2 presents the major steps of initial RL model generation. Firstly, holes of the given incomplete specification are sorted and indexed according to their types, where each hole has multiple candidate values. Next, we construct a multi-layer network for MDP simulation, where each node in the network represents the result after filling some hole with a candidate value. A layer of the network indicates all the possible assignments of a specific hole. For instance, the hole  $H_0$  has six candidate clocks, which can be used to complete the constraint  $e_0 \triangleq \Box_c^d + c_1$ . As a result, the first network layer consists of six nodes. In the same way, the remaining layers contain four, six, and eight nodes, respectively. In the network, the layers are fully connected with each other, representing all possible solutions (i.e., hole enumerations) for the synthesis. To facilitate the modeling of solutions, we add two extra states, i.e., S and T, to represent the start and termination of one hole enumeration solution, respectively. A valid path from S to T indicates a feasible solution to filling all the specification holes.

In our RL-based approach, we use the reward mechanism to measure the quality of decision-making on hole filling, where the measuring results are reflected by a Q-table. The Q-table stores the expectation of the sum of rewards for each candidate, which can be used to guide the hole filling. Note that our approach does not adopt the traditional Q-table structure in Q-learning. This is because each row in a traditional Q-table indicates a state in the form of a list representing a path from S to a specific network node in the multi-layer network. Along with the increasing number of holes, the number of rows in the traditional Q-table will increases exponentially, which is not acceptable in practice due to extremely long RL-training time. Let us consider an example of the incomplete specification shown in Figure 2. If we use a traditional Q-table here, it requires  $2 + (6 + 6 \times 4 + 6 \times 4 \times 6 + 6 \times 4 \times 6 \times 8) = 1328$  rows, where "2" denotes

two states, i.e., S and T, and multiplication expressions in the parenthesis indicate the numbers of paths starting from S with different lengths (i.e., 1, 2, 3, and 4), respectively. As an alternative, in our approach all the nodes of a specific network layer share the same row within a Q-table, indicating the actions on a specific hole. For the example shown in Figure 2, our approach only needs four rows to construct a Q-table, thus the Q-table size can be dramatically reduced. Note that since different holes have different candidate values, the rows of our Q-tables may have different sizes. By default, all the Q-table cells are initialized to 0.

As shown in Figure 2, for the generated multi-layer network, each node (except S) of the multi-layer network connects to all the nodes of its predecessor layer. This is not necessary in practice, since there may exist semantic conflicts for some hole enumeration solutions. The full connections between network layers may easily result in unfruitful exploration in RL. For example, due to the conflict between the constraints  $e_0 \triangleq c_3 + c_1$  and  $c_3 \subseteq e_0$ , it is impossible to fill hole  $H_0$  with  $c_3$ . In other words, node  $\langle H_0, c_3 \rangle$  can be safely pruned to accelerate the RL training, while the synthesis results are not affected. In our approach, we resort to the static pruning method based on the *rules of the number of clock ticks* proposed in [42] to remove such network constructs, thus achieving a compact initial RL model. For an obtained fully-connected multi-layer network, the pruning method tries to delete its unfruitful nodes based on all the given traces. By setting some Q-table cell with -1, we can disable the corresponding node in the multi-layer network, indicating that the hole enumeration path via this node is forbidden. Based on one trace with a length of 20, Figure 2 shows an example of model pruning, where the deleted nodes are greyed. Please refer to [42] for more details about the pruning of initial RL models.

#### 4.4 RL Model Training

Algorithm 1 presents the implementation of our synthesis algorithm. Note that the input  $\pi_0$  (i.e., Q-table) is a pruned initial model, where each valid cell of the Q-table is initialized with 0. Unlike classic Q-learning methods, our approach adopts two new data structures (i.e., count table  $T_c$  that records action selection statistics for each hole during RL, and greed table  $T_g$  that records the maximum reward explored so far for corresponding holes and actions). Please refer to Section 4.5.1 for more details about  $T_c$  and  $T_g$ . In line 3, we initialize both  $T_c$  and  $T_g$  using the Q-table, which are designed to guide the candidate selection in our CDE heuristic. Note that we use " $\pi_0 + 1$ " to increase the values of all the valid Q-table cells by 1. The iteration at lines 5-21 details one RL round, which tries to select actions to fill all the holes of  $\Phi$ . Line 10 denotes the action selection step, which we explain next in Section 4.5. Line 11 appends the selection result to rList, which forms the current state in terms of hole filling status. Line 12 updates the specification S by filling S with the selected action S by filling S with the selection S by filling S with the selected action S by filling S with the selection S by filling S and S are recorded in S and S ar

#### Algorithm 1: Our CCSL Specification Synthesis Method

```

Input: i) \Phi, incomplete specification; ii) T, set of execution timing traces; iii) \pi_0, pruned initial policy; iv) rd, # of RL training rounds. Output: i) A synthesized specification for \Phi.

```

```

RLSyn DC(\Phi,T,\pi_0,rd) begin

\pi_{\theta} \leftarrow \pi_{0}, maxSumRw \leftarrow 0;

T_c \leftarrow \pi_0 + 1, T_g \leftarrow \pi_0;

3

for i \leftarrow 1 to rd do

4

S \leftarrow \Phi;

5

rList \leftarrow [];

6

unActList \leftarrow [];

7

8

for j \leftarrow 1 to S.holes.len() do

9

H \leftarrow S.holes[j];

a \leftarrow ActionChoose(\pi_{\theta}, H, T_c, T_g, i, rd);

10

rList.append((H,a));

11

12

S \leftarrow Fill(S,(H,a));

(r,\pi_{\theta},unActList,T_{c}) \leftarrow CCSLChecker(S,rList,\pi_{\theta},T,unActList,T_{c});

13

if r == -1 then

14

break;

15

end

16

17

end

if r == 1 \land unActList == [] then

18

(\pi_{\theta}, maxSumRw, T_c, T_g) \leftarrow PolicyUpdate(S, rList, \pi_{\theta}, maxSumRw, T_c, T_g, i, rd);

19

20

21

end

22

return ResultEvaluator(\Phi, \pi_{\theta});

23 end

```

#### 4.5 Curiosity-Driven Exploration

When dealing with a complex CCSL synthesis problem involving a large set of correlated holes (i.e., the holes that have dependencies on their fillings), existing RL methods may easily get stuck in the local enumerations, thus resulting in a long synthesis time. Moreover,

Fig. 2. An example of initial RL model generation with pruning

due to the inherent randomness of action selection, the insufficient search may strongly affect RL-based synthesis methods to quickly

converge to an optimal solution within limited rounds. For the example shown in Figure 2, assume that the RL only involves ten rounds in total for specification synthesis, where the first four rounds select hole candidates in a random manner and the last six rounds select hole candidates based on the Q-table with a probability 0.9 (i.e.,  $\epsilon = 0.1$ ). In this case, if a hole candidate is not touched in the first four rounds, its Q-value will be 0, where its chance to be selected in the last six rounds is very low, e.g., the probability of  $\langle H_0, c_0 \rangle$  in the last six rounds is  $(1 - [0.9 + (0.1 \times 2/3)]^6) = 14.1\%$ . Let " $c_0$ ", "\*", " $c_0$ ", and "<" be the optimal candidates for holes  $H_0 - H_4$ , respectively. The probability that  $\langle H_0, c_0 \rangle$  is not selected in all the ten rounds is  $((2/3)^4 \times [0.9 + (0.1 \times 2/3)]^6) = 16.12\%$ . Similarly, the probabilities that  $\langle H_2, c_0 \rangle$  and  $\langle H_3, \prec \rangle$  are not selected in the last six rounds are the same, i.e.,  $((3/4)^4 \times [0.9 + (0.1 \times 3/4)]^6) = 27.18\%$ . Therefore, the probability that the synthesizer cannot simultaneously cover all the four optimal candidates in all ten rounds is  $(1 - (1 - 16.12\%) \times 100\% \times (1 - 27.18\%) \times (1 - 27.18\%)) = 55.52\%$ . In other words, the synthesizer has a 55.52% probability of getting stuck at local enumeration. Inspired by the curiosity-based RL method used in software testing [21], this paper introduces a novel CDE approach, which investigates the synergy between curiosity and greed to further enhance the efficiency and effectiveness of our RL-based synthesis method for action selection.

#### 4.5.1 Design of Curiosity Mechanism

In our approach, we divide the whole RL training into two stages, i.e., *exploration-intensive stage* and *exploitation-intensive stage*. The exploration-intensive stage puts more focus on model exploration, where we use our proposed count table to ensure the quick coverage of all the model nodes. In other words, in this stage, we try to quickly establish a Q-table with acceptable performance. Based on the newly derived Q-table in the exploration-intensive stage and our proposed *greed table*, the exploitation-intensive stage focuses on wisely and efficiently searching for optimal solutions. Note that both the count table and the greed table have the same structure as the one of the Q-table.

In our approach, we maintain a count table (i.e.,  $T_c$ ) to record action selection statistics for each hole. For a hole H and an action a, we measure the curiosity by using Model-based Interval Estimation with Exploration Bonuses (MBIE-EB) [43]:

$$curiosity(H,a) = \frac{1}{\sqrt{T_c(H,a)}},$$

(5)

where  $T_c(H,a)$  denotes the corresponding count table cell value. Note that the value of  $T_c(H,a)$  is initialized to 1. During the exploration, once a candidate action (H,a) is selected to fill the hole H, we increase  $T_c(H,a)$  by 1. Equation (5) enables hole candidates that are selected with lower frequencies to have higher curiosity. During the exploration, the hole candidates with larger curiosity values will have higher chance to be selected firstly.

During the synthesis, some selected hole candidates may be independent of other holes. In this case, the hole candidates with the maximum rewards will be the ones in the final optimal solution. To facilitate the selection of such holes, we propose a greedy heuristic to assist the curiosity mechanism during the RL training. The heuristic uses a greed table (denoted by  $T_g(H,a)$ ) to record the maximum reward explored so far for corresponding H and a, and adopts a rank function defined as follows to guide the candidate selection:

$$rank(H,a) = \begin{cases} curiosity(H,a) + \delta(i) \times T_g(H,a) & p \in [0,\eta) \\ curiosity(H,a) + \delta(i) \times Q(H,a) & p \in [\eta,1] \end{cases}, \tag{6}$$

where p is a random real number variable whose value ranges between 0 and 1. Although there are two versions of rank calculation here, we can only choose one. In Equation (6), we use  $\eta$  to denote a specified probability. It means that the rank function has a probability  $\eta$  to use the first expression to calculate its value, and has a probability  $1-\eta$  to use the second expression to calculate its value. Note that in the exploration-intensive stage, we prefer a larger  $\eta$ , since it puts more weight for greed values. Alternatively, in the exploitation-intensive stage, we prefer a smaller  $\eta$ , since we need to mainly resort to the Q-table for selecting candidates. Let r be the given number of the overall training rounds. The notation  $\delta(i)$  indicating a coefficient at the  $i^{th}$  round is defined as  $\frac{i}{r-i+1}$ , whose value increases along with the increasing number of exploration rounds. Note that, at the beginning of the synthesis, both Q-table and greed table are not fully explored. In this case, we use  $\delta$  (with a small value) to limit the weights of the greed table and Q-table, where the count table dominates the exploration. However, along with the increasing value of  $\delta$ , the exploration becomes more inclined to select hole candidates using either greed table or Q-table rather than relying on the count table.

To wisely balance the effects of exploration and exploitation, our CDE heuristic uses the  $\epsilon$ -greedy method to decide whether to use the rank function for hole candidate selection. Our approach chooses the candidate with the highest rank value with a probability of  $\epsilon$ , and chooses the candidate based on the weight of each candidate with a probability of  $1 - \epsilon$ . We use the curiosity information to calculate the weight of each candidate that is defined as follows:

$$p(H,a) = \frac{curiosity(H,a)}{\sum_{a_i \in A(H)} curiosity(H,a_i)},$$

(7)

where A(H) is the candidate set of hole H. Generally, a candidate is more likely to be selected if it has a larger weight.

#### 4.5.2 Curiosity-Driven Candidate Selection

Algorithm 2 details the implementation of our curiosity-driven candidate selection, where the inputs  $T_c$  and  $T_g$  are the count table and greed table, respectively. Line 2 obtains all the valid candidates of the hole H. Line 4 assigns p with a random value that is uniformly distributed in the range of [0,1]. If  $p > \epsilon$ , lines 6-18 select a candidate with the maximum rank value. Lines 7-11 set the value of  $\eta$  to specify the stage of exploration, where  $i/round < \beta$  indicates the exploration-intensive stage and  $i/round \ge \beta$  denotes the exploitation-intensive stage. Line 13 calculates the rank value of the candidate, where the function RANK is defined based on Equation (6). If  $p \le \epsilon$ ,

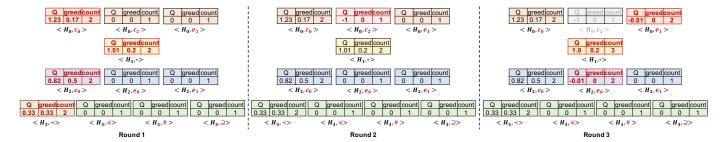

Fig. 3. An example of three consecutive rounds in our curiosity-driven exploration

#### **Algorithm 2:** Candidate Action Selection

```

Input: i) \pi_{\theta}, policy; ii) H, hole to be filled; iii) T_c, count table; iv) T_g, greed table; v) i, i^{th} round of training; vi) rd, # of training times

Output: i) candidate, a selected candidate.

ActionChoose(\pi_{\theta},H,T_c,T_g,i,rd) begin

candidateList \leftarrow \pi_{\theta}(H);

2

candidate \leftarrow candidateList[0];

3

p \leftarrow Random(0,1);

4

if p > \epsilon then

5

mRank \leftarrow 0;

6

if i/rd < \beta then

7

\eta \leftarrow \eta_1; // exploration-intensive stage

q

else

10

\eta_2; // exploitation-intensive stage

11

end

for each c in candidateList do

12

r = RANK(H, c, T_c, T_g, \eta);

13

if r > mRank then

14

mRank = r;

15

candidate = c;

16

17

end

18

end

19

else

choose candidate \in \mathcal{A}(H) using weight info.;

20

end

21

22

return candidate;

23 end

```

line 20 selects a candidate based on its weight information (see Equation (7)) following the uniform distribution. Note that when all the holes are filled, we need to update both the count table and greed table (see line 8 in Algorithm 3 and lines 8-9 in Algorithm 4). Finally, line 22 reports the selected action.

Figure 3 presents an example to illustrate the candidate selection process during the exploration-intensive stage based on the pruned initial model shown in Figure 2. Here, each round involves four levels, where each level corresponds to one layer of the pruned model in Figure 2. For each node, we present its three values of the Q-table, greed table, and count table, respectively. Note that the cells of the Q-table, greed table, and count table are initialized to 0, 0, and 1, respectively. In each round, we need to compute a solution that is capable of filling all the holes. In the first round, since all the nodes in the same layer have the same count value, greed value, and Q-value, the selection of nodes can only be random. Assume that the nodes in the red color are the ones selected in the first round. Based on this selection, we need to update all the three tables (Q table by line 14 of Algorithm 4, greed table by line 9 of Algorithm 4, count table by line 8 of Algorithm 4). For example, the count values of the selected nodes are increased by 1. In the second round, starting from layer 1, since the count value of the three candidates  $\langle H_0, c_0 \rangle$ ,  $\langle H_0, c_2 \rangle$ , and  $\langle H_0, e_1 \rangle$  are 2, 1 and 1, respectively, our approach tends to select  $\langle H_0, c_2 \rangle$  and  $\langle H_0, e_1 \rangle$  due to their smaller count values. We assume that  $\langle H_0, c_2 \rangle$  is selected here. Since  $\langle H_0, c_2 \rangle$  admits no given traces and this candidate is independent of other holes, we can prune this node from the model safely and terminate this round. Note that node  $\langle H_0, c_2 \rangle$  cannot be detected by the initial model pruning method proposed in [42]. In the third round, our approach selects  $\langle H_0, e_1 \rangle$ ,  $\langle H_1, * \rangle$  and  $\langle H_2, e_0 \rangle$  as the candidates for the first three holes. However, such selection fails to admit the given trace, and the selection of  $\langle H_2, e_0 \rangle$  depends on the selection  $H_1$ . Therefore, we terminate this round halfway through and update the Q table (by line 7 of Algorithm 3) and count table (by line 8 of Algor

#### 4.6 Deduction-Guided Checking and Reward Evaluation

To efficiently guide the hole filling and reward evaluation, we propose two deductive reasoning techniques: i) *deductive checking* that checks whether a filled constraint violates any provided traces; and ii) *deductive reward evaluation* that evaluates the reward of each hole filling action and updates the Q-Table correspondingly for a given complete specification.

#### **Algorithm 3:** Deduction-guided Checking

Input: i) S, an incomplete specification; ii) rList, a list of actions already applied on holes; iii) π<sub>θ</sub>, the policy; iv) T, a set of given execution timing traces; v) unActList, a list of uncertain actions; vi) T<sub>c</sub>, count table.

Output: i) r, deductive checking result; ii) π<sub>θ</sub>, an updated policy; iii) unActList, an updated list with unknown actions; iv) T<sub>c</sub>, an updated count table.

```

1 CCSLChecker(S,rList,\pi_{\theta},T,unActList,T_c) begin

(H,a) \leftarrow rList.getLast();

r \leftarrow Deduce((H,a),T);

3

if r == -1 then

4

if checkDep(S,(H,a)) then

5

for (H',a') \in rList do

6

7

\pi_{\theta}(H',a') \leftarrow \pi_{\theta}(H',a') - \Gamma;

8

T_c[\langle H', a' \rangle] = T_c[\langle H', a' \rangle] + 1;

end

9

10

\pi_{\theta}(H,a) \leftarrow -1;

11

12

else if r == 0 then

13

14

unActList.append(H,a);

15

16

(r,\pi_{\theta},unActList) \leftarrow UpdateUnAct(unActList,\pi_{\theta},S,T);

17

end

return (r,\pi_{\theta},unActList,T_c);

18

19

end

```

Algorithm 3 presents the implementation details of our deductive checking method. Line 2 computes the latest hole filling action. Line 3 deductively checks whether the action can admit all the given traces, where the return value of *Deduce* is saved in r. Here, r has three values (i.e., -1, 0, and 1) indicating that the action is invalid, unknown, and valid, respectively. If the action is invalid (i.e, r = -1), lines 5-12 will update the policy. In line 5, we use the function *checkDep* to check whether the action (H,a) depends on other holes. Here, the dependence means that changing the assignments of other holes will affect the semantics of the current filled constraint. For example, assume that  $e_0 \triangleq \Box_0 + c_0$  and  $e_0 \Box_1 c_2$  are two incomplete constraints of a specification. Since the filling of hole  $\square_0$  influences the behaviors of constraint  $e_0\square_1c_2$ , we say that  $\square_1$  depends on  $\square_0$ . If the dependence exists, line 7 will update the policy by applying a small penalty  $\Gamma$  on the Q-values related to the actions stored in *rList*, and line 8 will increase the values of corresponding count table items by 1. Otherwise, line 11 will set the Q-value of the latest action (i.e., (H,a)) to -1, denoting that the node < H,a>is removed from the multi-layer network. Note that, unlike the initial RL model pruning described in Section 4.3, line 11 denotes a new pruning technique based on the dependencies on hole assignments. Lines 13-14 indicate the case where the validity of the latest action is unknown. Taking the incomplete specification in Figure 2 as an example, assume that the latest action is filling  $H_0$  with  $e_1$ . At this moment, the content of  $H_1$  has not been determined yet, thus the timing behaviors of both  $e_0$  and  $e_1$  are uncertain. As a result, Deduce cannot determine the validity of action (H, a) at this stage. To record such uncertainties, line 14 appends the action to unActList. If the action is valid (i.e., r = 1), the function UnpdateUnAct in line 16 will check its impact on each unknown action in unActListand update unActList accordingly. If an unknown action in unActList becomes valid due to the latest action, it will be deleted from unActList. If an unknown action in unActList becomes invalid, UpdateUnAct will update both the policy and count table following the same way as shown in lines 5-12. Note that UpdateUnAct iterates until all the elements that can be inferred to be known in unActList are removed. Finally, line 18 reports the deductive checking results.

#### 4.6.2 Deductive Reward Evaluation for Updating Policy

The reward mechanism plays an important role in determining the quality (i.e., tightness) of specification synthesis results. Based on the analysis of logical connections between CCSL constraints, we introduce a novel deductive reward evaluation method for given enumerated hole solutions, which can guide the policy generation towards the tightest synthesis results.

Algorithm 4 details our reward evaluation and policy updating process. Note that the algorithm assumes that input S is a complete specification with all the hole filling information saved in rList. For each action of hole filling, lines 3-10 calculate its rewards and update the count table and greed table accordingly. In each iteration, line 5 uses the function rewardEvaluator to evaluate the reward for the selection, where the reward is defined within the range [0,1]. Note that we use different reward evaluation strategies for different hole types. Please refer to [42] for the detailed implementation of rewardEvaluator. Line 8 increases the corresponding items of count table  $T_c$  by 1. When the obtained reward is larger than the corresponding item in greed table  $T_g$ , line 9 needs to update the greed table. Lines 13-16 update the Q-table using the calculated rewards. To accelerate the convergence of Q-learning, the algorithm adopts the  $dynamic\ learning\ rate$  to enhance the reward and penalty effects. During RL, our approach is always inclined to learn from the search with the maximum sum of rewards. Meanwhile, our approach records the strategy with the highest reward sum explored so far. If the sum of rewards of a new search is greater than or equal to the record, we will increase the learning rate for the search. Otherwise, we will apply a lower learning rate on the search. Line 14 uses function  $\alpha(\delta,i,rd)$  to calculate the dynamic learning rate. Note that the

#### Algorithm 4: Deduction-guided Reward Evaluation

```

Input: i) S, a complete CCSL specification; ii) rList, a list of actions applied on holes; iii) \pi_{\theta}, the policy; iv) maxSumRw, maximum

sum of rewards; v) T_c, the count table; vi) T_g, the greed table; vii) i, the i<sup>th</sup> round of training; viii) rd, total number of training

Output: i) \pi_{\theta}, an updated policy; ii) maxSumRw, an updated maximum sum of rewards; iii) T_c, an updated count table; iv) T_{\theta}, an

updated greed table.

1 PolicyUpdate(S,rList,\pi_{\theta},maxSumRw,T_{c},T_{g},i,rd) begin

rewardList \leftarrow [], \ sumRw \leftarrow 0;

for j from rList.len() to 1 do

3

4

(H,a) \leftarrow rList[j];

reward \leftarrow rewardEvaluator((H,a),S);

5

rewardList.append(reward);

6

sumRw \leftarrow sumRw + reward;

7

T_c[\langle H, a \rangle] = T_c[\langle H, a \rangle] + 1;

8

T_{\varrho}[\langle H, a \rangle] = max(T_{\varrho}[\langle H, a \rangle], reward);

9

10

maxSumRw \leftarrow Max(maxSumRw, sumRw);

11

12

\delta \leftarrow maxSumRw - sumRw:

13

for j from 1 to rList.len() do

\pi_{\theta}(H,a) \leftarrow \pi_{\theta}(H,a) + (sumRw - \pi_{\theta}(H,a)) \times \alpha(\delta,i,rd);

14

sumRw \leftarrow sumRw - rewardList[j];

15

16

end

return (\pi_{\theta}, maxSumRw, T_c, T_g);

17

```

values of  $\alpha$  vary during the training. By default, if the reward sum obtained in the  $i^{th}$  round is the largest (indicated by  $\delta < 0$ ) so far, our approach will set  $\alpha$  to: i) 0.8 when i < rd/2; or ii) 0.98 when  $i \ge rd/2$ . Otherwise, the  $\alpha$  will be set to 0.1.

#### 5 Performance Evaluation

18 end

To evaluate the effectiveness of our RL-based CCSL synthesis approach, we implemented our CCSL synthesizer using Python (version 2.7) and conducted experiments on various synthetic and industrial CCSL specification benchmarks. We compared our approach with the state-of-the-art method *CCSLSketch* [19], whose underlying sketching engine is based on SMT solving. Our experiments try to answer the following three research questions.

- **RQ1** (Superiority): What is the performance of our approach compared with the state-of-the-art method?

- **RQ2** (Scalability): What are the impacts of different settings (e.g., the number of rounds, trace lengths, the number of traces) on scalability?

- RQ3 (Effects of CDE): Whether our proposed CDE heuristic can substantially improve synthesis time?

All the experimental results in this section were obtained from a laptop with 2.5GHz Intel i7 CPU and 16GB memory.

#### 5.1 Experimental Settings

#### 5.1.1 Benchmark Settings

We collected sixteen CCSL benchmarks (i.e., specifications) from four sources including: i) eleven benchmarks from the CCSL simulation tool *TimeSquare* [16] that investigates all the operators defined in Table 1; ii) three benchmarks (i.e., *Spec*<sub>1</sub>-*Spec*<sub>3</sub>) from *CCSLSketch* [19], [20], which is a state-of-the-art CCSL specification synthesis method based on sketching; iii) one complex synthetic benchmark (i.e., *Spec*<sub>4</sub>) generated by ourselves manually; and iv) one complex benchmark (i.e., *Spec*<sub>5</sub>) derived from an industrial land gear system [44] describing the timing behaviors of its aircraft undercarriage. To enable specification synthesis, firstly we used *TimeSquare* [16] to generate random timing traces with a specified length for each specification, which were used to guide the CCSL specification synthesis. Next, by randomly replacing clocks and operators from CCSL constraints with holes, we can form one incomplete version for each CCSL specification. According to Definition 4.1, each CCSL constraint within an incomplete specification has at most one hole for either a clock or an operator.

#### 5.1.2 Parameter Settings

In the experiments, we set  $\epsilon = 0.9$ , and set  $\beta = 30\%$  indicating that the exploration stage involves the first 30% RL rounds. We set  $\eta = 0.5$  for the exploration-intensive stage, and set  $\eta = 0.1$  for the exploitation-intensive stage. Since the given timing traces were derived from the collected CCSL specifications without holes, we treated them as the *golden reference specifications* for the synthesis. For a fair comparison, we applied our approach on each incomplete specification for 500 times. According to Definition 4.4, the synthesis accuracy in this case can be obtained with a precision of 0.2%. Note that requirement engineers can tune the number of repetitions to achieve their expected precision for the synthesis accuracy. Based on the obtained 500 synthesized specifications, we calculated the synthesis accuracy as the ratio of the synthesized specifications that have the same syntax as their golden reference specification. It is important to note that, for each incomplete CCSL specification, there may exist multiple synthesized specifications with different syntax formats satisfying the given timing traces. In this case, an accurately synthesized specification is the one that is as "tight" as its golden reference.

TABLE 2

Performance Comparison of Different CCSL Specification Synthesis Methods Using Collected Benchmarks

| Source             | Index             | CCSL Statistics |        |        | Hole Settings |            |            | CCSLSketch | # of   | RLSyn+D [42] |          | RLSyn+DC  |          |

|--------------------|-------------------|-----------------|--------|--------|---------------|------------|------------|------------|--------|--------------|----------|-----------|----------|

|                    |                   | Clk. #          | Exp. # | Rel. # | Clk. #        | Exp. Op. # | Rel. Op. # | Time (ms)  | Rounds | Time (ms)    | Acc. (%) | Time (ms) | Acc. (%) |

| TimeSquare [16]    | S =               | 2               | 0      | 1      | 0             | 0          | 1          | 867        | 10     | 4            | 50.8     | 4         | 100      |

|                    | S <               | 2               | 0      | 1      | 0             | 0          | 1          | 787        | 10     | 3            | 72.2     | 4         | 100      |

|                    | S <sub>≤</sub>    | 2               | 0      | 1      | 0             | 0          | 1          | 754        | 10     | 4            | 71.4     | 4         | 100      |

|                    | $S\subseteq$      | 2               | 0      | 1      | 0             | 0          | 1          | 791        | 10     | 3            | 100      | 4         | 100      |

|                    | S #               | 2               | 0      | 1      | 0             | 0          | 1          | 685        | 10     | 4            | 100      | 4         | 100      |

|                    | S *               | 3               | 1      | 1      | 0             | 1          | 0          | 6639       | 10     | 8            | 100      | 8         | 100      |

|                    | S +               | 3               | 1      | 1      | 0             | 1          | 0          | 6787       | 10     | 7            | 100      | 7         | 100      |

|                    | $S_{\vee}$        | 3               | 1      | 1      | 0             | 1          | 0          | 6922       | 10     | 7            | 100      | 7         | 100      |

|                    | $S_{\wedge}$      | 3               | 1      | 1      | 0             | 1          | 0          | 6880       | 10     | 8            | 100      | 7         | 100      |

|                    | $S_{\$}$          | 2               | 1      | 1      | 0             | 1          | 0          | 886        | 10     | 8            | 100      | 7         | 100      |

|                    | S <sub>∞</sub>    | 2               | 1      | 1      | 0             | 1          | 0          | 908        | 10     | 6            | 100      | 6         | 100      |

| CCSLSketch<br>[20] | Spec <sub>1</sub> | 4               | 1      | 3      | 0             | 0          | 3          | 13782      | 10     | 6            | 60.4     | 6         | 100      |

|                    |                   |                 |        |        |               |            |            |            | 20     | 12           | 92.8     | 12        | 100      |

|                    |                   |                 |        |        | 0             | 1          | 2          | 36716      | 20     | 11           | 91.2     | 12        | 100      |

|                    |                   |                 |        |        |               |            |            |            | 50     | 29           | 98.4     | 30        | 100      |

|                    | Spec <sub>2</sub> | 10              | 5      | 10     | 0             | 0          | 10         | 27689      | 50     | 69           | 81.8     | 70        | 98.6     |

|                    |                   |                 |        |        |               |            |            |            | 100    | 142          | 99.6     | 143       | 100      |

|                    |                   |                 |        |        | 4             | 2          | 4          | 40872      | 500    | 887          | 73.6     | 996       | 100      |

|                    |                   |                 |        |        |               |            |            |            | 1000   | 1807         | 96.8     | 1982      | 100      |

|                    | Spec <sub>3</sub> | 20              | 6      | 16     | 9             | 1          | 7          | 433523     | 500    | 1506         | 57.8     | 1415      | 81.8     |

|                    |                   |                 |        |        |               |            |            |            | 1000   | 2956         | 92.8     | 2888      | 99.4     |

|                    |                   |                 |        |        | 5             | 1          | 10         | 42166      | 500    | 1412         | 87       | 1553      | 100      |

|                    |                   |                 |        |        |               |            |            |            | 1000   | 2898         | 96       | 3030      | 100      |

| Synthetic          | Spec <sub>4</sub> | 9               | 4      | 5      | 0             | 4          | 0          | NA         | 50     | 101          | 61.2     | 105       | 94.6     |

|                    |                   |                 |        |        |               |            |            |            | 100    | 205          | 88.4     | 209       | 100      |

|                    |                   |                 |        |        | 5             | 1          | 1          | NA         | 2000   | 3116         | 83.4     | 3378      | 99.4     |

|                    |                   |                 |        |        |               |            |            |            | 3000   | 4548         | 97.4     | 4997      | 100      |

| LandGear<br>[44]   | Spec <sub>5</sub> | 25              | 74     | 54     | 1             | 1          | 5          | NA         | 500    | 5091         | 75.8     | 5349      | 100      |

|                    |                   |                 |        |        |               |            |            |            | 1000   | 10325        | 85.8     | 10407     | 100      |

|                    |                   |                 |        |        | 3             | 1          | 0          | NA         | 20     | 254          | 91.4     | 271       | 100      |

|                    |                   |                 |        |        |               |            |            |            | 50     | 805          | 99.8     | 706       | 100      |

#### 5.2 Performance Comparison (RQ1)

This subsection highlights the benefits of our approach. We conducted a comprehensive comparison with the state-of-the-art method *CCSLSketch* using the collected benchmarks. To enable synthesis, for each benchmark we used *TimeSquare* to generate five traces with a length of 50 each. Table 2 presents the performance comparison results. The first column shows the sources of the collected specifications, and the second column presents the indices of the CCSL specifications. The third column consists of three sub-columns denoting the statistics of CCSL specifications, which includes the number of clocks, expressions, and relations for the collected CCSL specifications, respectively. The fourth column also has three sub-columns, which present the numbers of clock holes, expression operator holes, and relation operator holes, respectively. Due to space limitation, for each specification of *Spec*<sub>1</sub>-*Spec*<sub>5</sub>, here we provided only two different sets of incomplete constraints. The fifth column gives the synthesis time using *CCSLSketch*, where "*NA*" indicates the cases that result in the crash of *CCSLSketch* due to the notorious *state explosion problem*. The sixth column shows the maximum number of rounds used by the RL-based synthesis methods, where the first 30% rounds are for the exploration-intensive stage and the remaining 70% rounds are for the exploitation-intensive stage. To evaluate the performance (e.g., convergence) of different synthesis methods, for specific sets of CCSL constraints, we checked multiple scenarios with different numbers of rounds. The seventh column contains two sub-columns, which present the average synthesis time and accuracy information for our method, respectively, without considering the CDE. Note that the approach *RLSyn+D* is the same as the method proposed in [42]. Similarly, the eighth column shows the average synthesis time and accuracy information by taking both our deduction methods and CDE heuristic into account.

From Table 2, we can observe that compared with CCSLSketch, our RL-based methods can significantly improve the synthesis time by up to three orders of magnitude. Especially, we can find that CCSLSketch failed to synthesize all the incomplete specifications for both  $Spec_4$  and  $Spec_5$ , while our RL-based approaches (i.e., RLSyn+D and RLSyn+DC) succeed in obtaining synthesis results. The reason why our approaches outperform CCSLSketch for  $Spec_4$  and  $Spec_5$  is mainly because our approaches are good at dealing with interrelated incomplete constraints, which cannot be efficiently handled by CCSLSketch. For example, "?  $< e_2$ ,  $e_2 = c_3 ? c_4$ " are two interrelated incomplete constraints in the second case of  $Spec_4$ . Since the second case of  $Spec_4$  has 5 clock holes, 1 expression operator hole and 1 relation operator hole, the size of its whole enumeration space is  $(9+4)^5 \times 4 \times 8 = 11,881,376$ . However, within 3000 rounds (enumerations), our RLSyn+DC method can achieve the tightest solution with an accuracy of 100%. It means that our method can achieve the same accuracy as CCSLSketch by exploring only 0.025% of its enumeration space, costing an average of 5 seconds for the CCSL specification synthesis. We can also observe that compared with RLSyn+D, although RLSyn+DC needs slightly higher time

overhead under the same restriction of the number of rounds, it can achieve much better accuracy results. As an example for the first case of  $Spec_3$ , when there are only 500 rounds allowed, RLSyn+D has an accuracy of 57.8%, while RLSyn+DC can achieve an accuracy of 81.8%. Interestingly, we can find that in this case RLSyn+DC requires 5.8% less synthesis time than RLSyn+D, since RLSyn+DC converges earlier than RLSyn+D. Based on the above facts, in practice, we recommend using RLSyn+DC for synthesizing complex CCSL specifications.

#### 5.3 Scalability Analysis (RQ2)

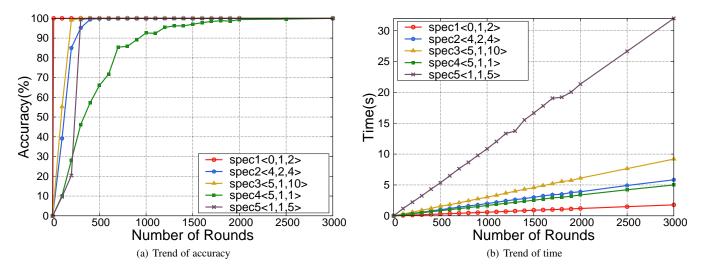

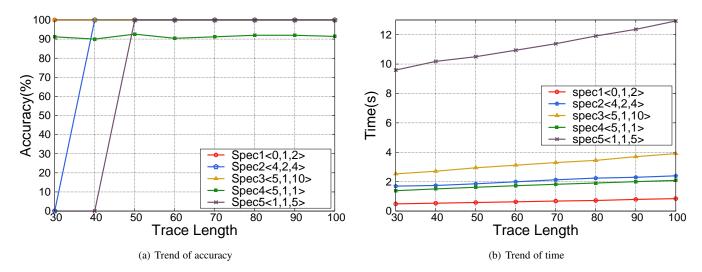

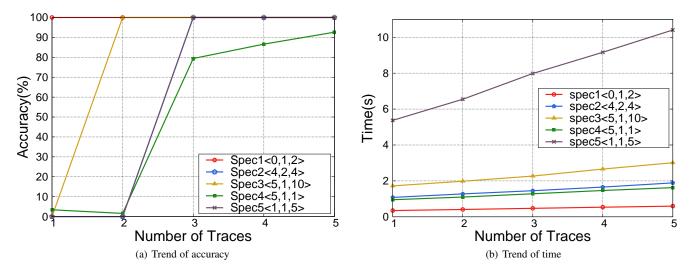

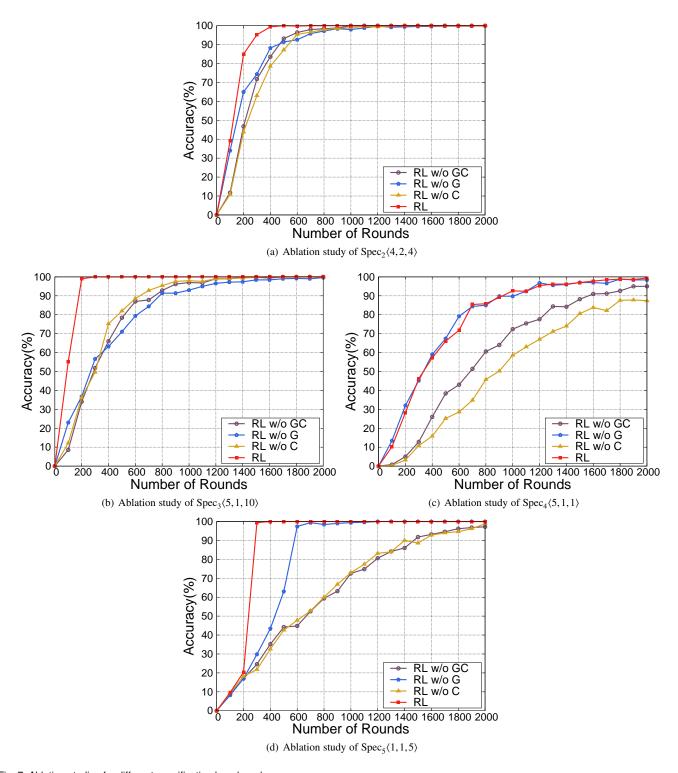

This subsection evaluates the impacts of three important factors (i.e., the number of RL rounds, trace lengths, the number of traces) on the scalability of our approach from the perspectives of synthesis time and accuracy. Note that all the synthesis results in this subsection were obtained by *RLSyn+DC*.

#### 5.3.1 Impact of the Number of RL Rounds