# Near-optimal Energy-Efficient Partial-Duplication Mapping of Real-Time Parallel Applications

Minyu Cui, Angeliki Kritikakou, Lei Mo, Emmanuel Casseau

## ▶ To cite this version:

Minyu Cui, Angeliki Kritikakou, Lei Mo, Emmanuel Casseau. Near-optimal Energy-Efficient Partial-Duplication Mapping of Real-Time Parallel Applications. AEiC 2022 - 26th Ada-Europe International Conference on Reliable Software Technologies, Jun 2022, Ghent, Belgium. pp.1-26. hal-03907727

# HAL Id: hal-03907727 https://inria.hal.science/hal-03907727

Submitted on 20 Dec 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Near-optimal Energy-Efficient Partial-Duplication Mapping of Real-Time Parallel Applications

Minyu Cui, Angeliki Kritikakou, Lei Mo, Emmanuel Casseau

Abstract Minimizing energy consumption, as well as meeting real-time and reliability constraints, are major goals during system deployment. When complex platforms, such as multicore architectures with DVFS, and parallel applications are considered, these goals are significantly impacted by task mapping. To minimize energy consumption, while meeting real-time and reliability constraints, this work proposes a task mapping approach to jointly solve the problem of task allocation, task scheduling, frequency assignment, and task duplication. A novel heuristic algorithm is proposed to cope with this NP-hard problem, consisting of a pruning phase, which maintains only the task configurations that satisfy reliability constraints, and a mapping phase, which minimizes total energy consumption under real-time and precedence constraints. The obtained results show that the proposed heuristic obtains near-optimal results, with low computation time, compared to optimal solvers, while it achieves better energy consumption and finds more solutions compared to other heuristic approaches.

**Keywords** Fault tolerant  $\cdot$  Task mapping  $\cdot$  DVFS  $\cdot$  Real-time execution  $\cdot$  Reliability  $\cdot$  Energy minimization

Acknowledgements This work is founded by China Scholarship Council (CSC).

Minyu Cui

Univ Rennes, INRIA, CNRS, IRISA, France, E-mail: minyu.cui@irisa.fr

Angeliki Kritikakou

Univ Rennes, INRIA, CNRS, IRISA, France, E-mail: angeliki.kritikakou@irisa.fr

Lei Mo

School of Automation, Southeast University, China, E-mail: lmo@seu.edu.cn

Emmanuel Casseau

$\label{lem:constraint} \mbox{Univ Rennes, INRIA, CNRS, IRISA, France, E-mail: emmanuel.casseau@irisa.fr}$

### 1 Introduction

#### 1.1 Context

The execution of embedded real-time parallel applications on multicore platforms require guarantees for real-time execution [1–3] and reliability [1,4]. Due to technology size reduction, multicore platforms are susceptible to transient faults [1]. Reliability is defined as the probability of executing a task without faults. Typical techniques to increase reliability are the execution of tasks with high frequency [5] and task replication [1,4]. However, both techniques can lead to large energy consumption. Dynamic Voltage and Frequency Scaling (DVFS) is a well-known energy management technique, which optimizes energy consumption by scaling down the processor supply voltage and frequency [1,4]. However, this has a negative impact on reliability, since more transient faults occur at a low voltage and frequency level [1,4]. Therefore, during the task mapping not only task allocation and scheduling, but also frequency assignment and task replication should be incorporated in the optimisation process to achieve energy efficiency, while meeting real-time and reliability constraints.

#### 1.2 Related work and motivation

Table 1 summarises representative State-of-the-Art (SoA) task mapping approaches that minimize energy consumption considering DVFS, under Real-Time (RT) and Reliability (R) constraints. The platform consists of Homogeneous (HO), Heterogeneous (HE) or Single (S) processor. The applied fault tolerance policy can be task Recovery (Rec.) or task Replication (Rep.). A task is executed successfully, if at least one replica is executed without faults [1]. Last, the proposed solving method can Optimal (O) or Heuristic (H).

Approaches exist without applying a fault tolerance policy, e.g., the task mapping problem is decomposed into a sub-problem that satisfies the reliability constraint and another that minimizes resources [5] and a whale optimization algorithm is proposed [6]. In [7], the scheduling algorithm for dependent multi-version tasks is studied based on Forward List Scheduling with the goal of minimise the total energy consumption under real-time constraint. Approaches execute a recovery task, e.g., individual [8] or shared [2, 9], or both [10], with maximum frequency, exploring available time slack to meet the reliability constraint. Last, approaches apply task replication. Some works decide the required number of replicas per task to always meet the reliability constraint, e.g., for independent tasks on homogeneous platform [1] and dependent tasks on heterogeneous platforms [4]. In [1], all replicas of a task are executed at same frequency, whereas in [4] no real-time constraints are taken into account. In [11] the number of replicas per task is given. In the first phase, half-plus-one copies per task are executed. If a fault occurs, the second phase is applied to execute the remaining number of copies. Other works decide among different reliability mechanisms for each task. In [12], a

Platform Task model Fault tol. Constraints Solution Ref. Rec. Rep. I. D. HO HE S RT $\overline{\mathbf{R}}$ O Η 5 [6] [7][2, 8, 10][3] 13 12[11 [14]Prop.

Table 1: Comparison with representative SoA approaches

heuristic explores among three reliability mechanisms in sequence to decide single task execution, task duplication and task triplication, without the requirements of always meeting the real-time and reliability constraints. In [3], a heuristic determines which tasks to be duplicated, removing the need of a recovery task for all tasks. An optimal approach decides which task to duplicate, taking into account reliability and real-time constraints for independent [13] and independent tasks [14].

Overall, optimal approaches are applicable only for small problem sizes and existing heuristics, either do not fully guarantee real-time or reliability constraints, or use a high number of replicas, leading to large energy consumption with a negative impact on execution time, and thus, potentially no feasible solution.

## 1.3 Contributions

This work addresses the task mapping problem of parallel applications on homogeneous multicore platforms with DVFS, with the goal of minimizing total energy consumption, under real-time and reliability constraints. An effective heuristic is proposed, considering multiple non-functional properties of execution time, energy and reliability, that combines task allocation, task scheduling, frequency assignment and selective task duplication. Unlike the majority of SoA techniques, original and duplicated tasks can have different operating frequencies, being more suitable for real-world systems [15]. A pruning phase maintains only the task configurations that satisfy reliability constraints. A mapping phase minimizes total energy consumption under real-time and precedence constraints. Last, but not least, the proposed method is evaluated both with task graphs from real applications and randomly generated graphs. The experiment results show that our approach provides near-optimal energy sav-

| Notations         | Definitions                                                     |

|-------------------|-----------------------------------------------------------------|

| $	au_i^o/	au_i^d$ | the original/duplicated copy of task $\tau_i$                   |

| $(v_l,f_l)$       | the $l^{th}$ voltage/frequency level                            |

| $W_i$             | WCEC of task $\tau_i$                                           |

| D                 | the global deadline                                             |

| $R_i^{th}$        | reliability threshold of task $\tau_i$                          |

| SL                | schedule length of DAG $G$                                      |

| $EST_i$           | earliest start time of task $\tau_i$                            |

| $LFT_i$           | latest finish time of task $\tau_i$                             |

| $st_i$            | actual start time of task $\tau_i$                              |

| $ft_i$            | actual finish time of task $\tau_i$                             |

| $et_i$            | execution time of task $\tau_i$                                 |

| $slack_i$         | time slack of task $\tau_i$                                     |

| $Pred\{\tau_i\}$  | all immediate predecessors of task $\tau_i$                     |

| $Succ\{\tau_i\}$  | all immediate successors of task $\tau_i$                       |

| $proc\{m\}$       | task set that are allocated on processor $\theta_m$             |

| $SC_i$            | Selected configuration of task $\tau_i$ in current task mapping |

| $NC_i$            | New checked configuration of task $\tau_i$                      |

Table 2: Main Notations and their definitions

ings, with low computation time compared to optimal solvers, while it has better energy consumption and feasibility compared to other heuristics.

The rest of the paper is organized as follows. Section 2 introduces the system model. Section 3 presents the formulation of the proposed approaches. Section 4 presents the evaluation results. Finally, Section 5 concludes this study.

## 2 System Model

Table 2 shows the main notations. For the sake of paper presentation, when original and duplicated tasks must be distinguished in mathematical formulations, the subscript  $k \in \{o, d\}$  indicates the original task (o) or the duplicated task (d). If no subscript exists, the mathematical formulation is valid for both.

## 2.1 Task Model

This work considers a real-time application modelled as a Directed Acyclic Graph (DAG)  $G(\mathbb{V}, \mathbb{E})$ , where  $\mathbb{V}$  denotes the set of N frame-based, non-preemptive, dependent tasks  $\{\tau_0^o, \ldots, \tau_{N-1}^o\}$ , while  $\mathbb{E}$  represents the edges, corresponding to the tasks' precedence constraints. Tasks are released at time 0 and have a global deadline D, given by the application frame. If a task has no predecessors (successors), it is an entry task  $\tau_{entry}$  (exit task  $\tau_{exit}$ ). A task is ready for execution when all its predecessors have been completed. Each task  $\tau_i$  is described by a tuple  $\{W_i, R_i^{th}\}$ , where  $W_i$  is the Worst Case Execution Cycles (WCEC) and  $R_i^{th}$  is its reliability threshold. Each task has

its own reliability constraint, since functions of an application exhibit distinct vulnerabilities, due to variations in the spatial and temporal vulnerabilities of different instructions [12].

## 2.1.1 Platform Model

The target platform has a shared-memory multicore architecture with M homogeneous processors  $M = \{\theta_0, \dots, \theta_{M-1}\}$ . Each processor supports DVFS and has L pairs of frequency/voltage level  $\{(f_0, v_0), \dots, (f_{L-1}, v_{L-1})\}$ . As the relationship of voltage and frequency is almost linear [4,9,11], we use the term frequency scaling to express the simultaneous change of voltage and frequency. We consider intra-task DVFS. When task  $\tau_i$  is executed with frequency  $f_l$ , its execution time is  $\frac{W_i}{f_l}$ . The power consumption is modeled as the sum of static power  $P_l^{sta}$  and dynamic power  $P_l^{dyn}$  considering a voltage/frequency level  $(v_l, f_l)$  [1, 4]. Specifically,

$$P_{l} = P_{l}^{sta} + P_{l}^{dyn} = P_{l}^{sta} + C_{eff}v_{l}^{2}f_{l}, \tag{1}$$

where  $C_{eff}$  is the effective switching capacitance.

## 2.1.2 Fault Model and Reliability

This work addresses transient faults, having a higher occurrence than permanent faults during the useful lifetime of the system [5]. During this period, the fault model, where the fault occurrence is given by a Poisson distribution with an average fault rate  $\lambda(f_l)$  at frequency  $f_l$ , is typically used [4,5,9,11]. The failure rate per time unit of a processor at frequency  $f_l$  is given by

$$\lambda(f_l) = \lambda_0 \times 10^{d_0 \frac{f_{\text{max}} - f_l}{f_{\text{max}} - f_{\text{min}}}},\tag{2}$$

where  $f_{\text{max}} = \max_{\forall l} \{f_l\}$ ,  $f_{\text{min}} = \min_{\forall l} \{f_l\}$ ,  $\lambda_0$  is the average failure rate of the processor corresponding to  $f_{\text{max}}$ , and  $d_0$  is a positive constant, indicating the sensitivity of failure rates to voltage scaling [4].

The reliability of task  $\tau_i$  is defined as the probability of executing  $\tau_i$  without any fault. Based on the exponential model in [1, 9], the reliability of a task executed at  $f_{\tau_i}$  is calculated as

$$R_i(f_l) = e^{-\varphi_i(f_l)},\tag{3}$$

where  $\varphi_i(f_l) = \lambda(f_{\tau_i}) \times et_{i,l}$ , and  $et_{i,l}$  is the execution time of task  $\tau_i$  at frequency  $f_l$ . If the reliability of original task  $\tau_i^o$  is larger than its reliability threshold  $R_i^{th}$ , the execution is considered as reliable [5] and the task reliability is given by  $R_i = R_i^o$ . Otherwise, the task  $\tau_i^o$  is duplicated and executed on a different processor, since it is unlikely that the execution of both original and duplicated tasks on different processors fail [1, 3, 4]. The duplicated task  $\tau_i^d$  has the same characteristics with the original task  $\tau_i^o$ . When the duplicated

task  $\tau_i^d$  is executed, its reliability is  $R_i^d$  and depends on the frequency it is executed. Then, the task reliability, after duplication, is

$$R_i = 1 - (1 - R_i^o)(1 - R_i^d). (4)$$

As our approach finds an offline optimal task mapping solution, with the goal of minimizing energy consumption, we consider only task duplication, i.e., a single replica per task, in order not to unnecessarily increase the number of replicas, in case no faults occur. An online mechanism can be applied to further improve the energy consumption of our solution (by not executing the duplicated task, when the first execution is correct), and to deal with the low probability cases, where both original and duplicated tasks are faulty. In this work, cores are assumed to operate below a temperature threshold, where temperature impact on reliability is low [16].

## 2.1.3 Problem under study

Given a DAG task graph G and M processors, the goal is to minimize the total energy consumption by deciding the: 1) task duplication, 2) assignment of frequencies to tasks, 3) allocation of tasks to processors, 4) start time of tasks, subject to reliability, real-time and task precedence constraints.

## 3 Proposed Approach

To solve the problem under study, we propose a *Heuristic for Reliability-aware Fault-tolerant Task Mapping (H\_RAFTM)*, described in Algorithm 1. The algorithm consists of two phases:

- 1. Phase A obtains, per task, the set of possible configurations that meet the reliability constraint, ordered in decreasing energy consumption.

- 2. Phase B obtains the application mapping, by allocating tasks to processors using the least total energy consumption, under task precedence and real-time constraints.

H\_RAFTM is based on the following definitions:

**Definition 1** (Configuration). A configuration j of a task  $\tau_i$  is denoted as  $C_i^j = \{f_i^o, f_i^d, et_i^o, et_i^d, E_i^o, E_i^d, R_i\}$ , where  $f_i^o$   $(f_i^d)$  is the assigned frequency,  $et_i^o$   $(et_i^d)$  is the required execution time,  $E_i^o$   $(E_i^d)$  is the energy consumption of the original (duplicated) task, and  $R_i$  is the reliability of the task (taking into account task duplication). If the task is not duplicated, we have  $f_i^d = et_i^d = E_i^d = 0$ .

**Definition 2** (Task Mapping). A mapping of a task  $\tau_i$ , under the task configuration  $C_i^j$ , is denoted as  $TM_i^{C_i^j} = \{\theta_i^o, \theta_i^d, st_i^o, st_i^d\}$ , where  $\theta_i^o$  ( $\theta_i^d$ ) is the allocated processor, and  $st_i^o$  ( $st_i^d$ ) is the start time of the original (duplicated) task. If a task is not duplicated, then  $f_i^d = 0$ , and the duplicated task takes no execution time, i.e., its start time is equal with its final time,  $st_i^d = ft_i^d$ .

**Definition 3** (Application Mapping). The mapping of the application (AM) is given by the set of mappings of N original tasks and  $S \subseteq N$  duplicated tasks. The mapping is valid if task precedence and real-time constraints are satisfied.

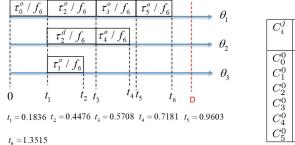

The next paragraphs describe in details the two phases of the proposed approach and illustrate them using the application DAG example of Fig. 1.

Part of  $RTE_5^*$  with  $W_5=1.4728\times 10^8$  and  $R_5^{th}=0.9994$  \*Processor model based on Table 3

|            | (GHz)  | (GHz) | (msec) | (msec) | (mJ)    | (mJ)    |           |

|------------|--------|-------|--------|--------|---------|---------|-----------|

| $C_5^0$    | 0.801  | -     | 18.387 | -      | 0.77944 | -       | 0.9908486 |

| $C_5^1$    | 0.8291 | -     | 17.764 | -      | 1.02746 | -       | 0.9966568 |

| $C_5^2$    | 0.8553 | -     | 17.220 | -      | 1.36084 | -       | 0.9986935 |

| $C_5^3$    | 0.8797 | -     | 16.742 | -      | 1.81375 | -       | 0.9994552 |

| $C_5^4$    | 0.9027 | -     | 16.315 | -      | 2.43532 | -       | 0.9997610 |

| $C_5^5$    | 1.0    | -     | 14.728 | -      | 3.29633 | -       | 0.9999926 |

| $C_5^6$    | 0.801  | 0.801 | 18.387 | 18.387 | 0.77944 | 0.77944 | 0.9999163 |

| :          |        | :     | :      | :      | :       | :       | :         |

| $C_5^{10}$ | 0.801  | 1.0   | 18.387 | 14.728 | 0.77944 | 3.29633 | $\sim 1$  |

| :          | :      | :     | :      | :      | :       | :       | :         |

| $C_5^{26}$ | 1.0    | 1.0   | 14.728 | 14.728 | 3.29633 | 3.29633 | $\sim 1$  |

Fig. 1: Illustration example: Application DAG (N=6) and part of  $RTE_5$ .

## 3.1 Phase A: Task configurations, under reliability constraint.

Phase A (Lines 1-9) is applied per task. For each task (Line 1), a Reliability, execution Time, Energy consumption (RTE) table is created based on all possible configurations (Line 2). For instance, part of the RTE of task  $\tau_5$  is depicted in Fig 1. A pruning step removes the task configurations that do not satisfy the reliability constraint (Line 3).

i) Reliability Constraint: A task must be executed meeting its reliability requirement, i.e.,  $R_i \geq R_i^{th}$ .

For instance, assuming that the reliability of  $\tau_5$  is  $R_5^{th} = 0.9994$ , the configurations  $C_5^0$ ,  $C_5^1$  and  $C_5^2$  are pruned in this step. The result is the Feasible Configurations (FC) of the task.  $FC_i$  considering only the original task  $\tau_i^o$  (when  $f_i^d = 0$  no duplicated task exists) serve as Baseline Configurations (BC) (Line 4). In our illustration example, the BC of  $\tau_5$  are  $C_5^3$ ,  $C_5^4$  and  $C_5^5$ . The next step prunes any feasible configuration with duplicated tasks, if both the energy consumption and the execution time are larger than any defined  $BC_i$  (Lines 5-7), e.g.,  $C_5^{10}$  and  $C_5^{26}$  in our illustration example of Fig 1. The result is the Possible Configurations (PC). The PC are ranked based on decreasing energy consumption  $(rPC_i)$  (Line 8).

## Algorithm 1: Proposed H\_RAFTM algorithm.

```

Require: Task graph (G) and set of processors (M).

Ensure: Application mapping (AM).

// Phase A

1: for each task \tau_i in N do

RTE_i = \{C_i^j : C_i^j \text{ is a configuration of } \tau_i\};

FC_i = RTE_i - \{C_i^j : R_i < R_i^{th}\};

BC_i = \{FC_i: f_i^{\grave{d}} = 0\};

4:

for each configuration bc in BC_i do

5:

PC_i = FC_i - \{FC_i: f_i^d \neq 0 \land \min\{et_i^o, et_i^d\} \ge et^{bc} \land

6:

\sum \{E_i^o, E_i^d\} > E^{bc}\};

end for

7:

rPC_i = \{PC_i: PC_i \text{ decreasing energy consumption}\};

8:

9: end for

// Phase B

10: for each task \tau_i in N do

Compute rank_i (Eq. 8);

13: PL = \{N: \text{ ordered in decreasing } rank_i\};

14: for each task \tau_i in PL do

SC_i = rPC_i[0];

Compute TM_i^{SC_i} (st_i = EST_i in Eq. 7);

15:

16:

17: end for

18: AM_0 = \{TM_i^{SC_i}\};

19: Compute SL_{AM_0} (Eq. 6);

20: if SL_{AM_0} > D then

Infeasible problem, algorithm stops.

22: else if SL_{AM_0} = D then

AM = AM_0, algorithm stops.

24: else if SL_{AM_0} < D then

AM relaxation (Algorithm 2);

26: end if

```

$3.2~\mathrm{Phase}$  B: Application mapping, under precedence and real-time constraints.

Phase B uses Phase A task configurations and performs the application mapping, subject to the following constraints:

ii) Precedence constraints: Based on the dependencies defined by the task graph, a task  $\tau_i$  can start execution only when all its predecessors are completed. Task predecessors include also the duplicated tasks, since our approach is applied offline, and thus, strict scheduling is considered where a task can be executed after all its predecessors are finished. Then, the Earliest Start Time

(EST) of  $\tau_i$  given by

$$EST_i = \begin{cases} 0, & if \ \tau_i = \tau_{entry} \\ \max_{\tau_i \in Pred\{\tau_i\}} \{EFT_j\}, \ else \end{cases}$$

(5)

where  $Pred\{\tau_i\}$  is the set of  $\tau_i$ 's predecessors, and  $EFT_j = EST_j + et_j$  is the Earliest Finish Time (EFT) of task  $\tau_j$ .

iii) Deadline constraint: The application must be finished before the deadline D. The Schedule Length, SL, of task graph G, under a given application mapping AM, is determined by the latest finish time of exit tasks:

$$SL_{AM} = \max\{ft_{\tau_{exit}}\} \le D. \tag{6}$$

Due to precedence constraints, the start time of a task is  $st_i \geq EST_i$ . Our goal is to exploit the available time slack to save energy, thus, we initially consider that tasks start execution as soon as possible, i.e.,  $st_i = EST_i, \forall \tau_i$ . iv) Non-overlapping constraint: Only a single task should be executed on a processor at a given time instance. Taking into account the earliest available time, avail[m], when processor  $\theta_m$  is ready for a task execution,  $EST_i$  is modified as

$$EST_{i} = \begin{cases} 0, if \ \tau_{i} = \tau_{entry} \\ \max \begin{cases} \max_{\tau_{j} \in Pred\{\tau_{i}\}} \{EFT_{j}\}, \\ avail[m], \end{cases}, else \end{cases}$$

(7)

The text paragraphs describe the three steps of Phase B (Lines 10-26):

Step 1 (Lines 10-13): Priorities are given to tasks for task allocation based on the upward rank value [4],  $rank_i$ , which is common for original and duplicated tasks (Lines 10-12):

$$rank_{i} = \begin{cases} \overline{et}_{i}, & if \ \tau_{i} = \tau_{exit} \\ \overline{et}_{i} + \max_{\tau_{j} \in Succ\{\tau_{i}\}} \{rank_{j}\}, else \end{cases}$$

(8)

where  $\overline{et}_i = (\sum_{l=1}^L W_i/f_l)/L$  is the average computation time of  $\tau_i$  and  $Succ\{\tau_i\}$  the immediate successors of  $\tau_i$ . Then, the Priority List (PL) is ordered in decreasing rank value (Line 13).

Step 2 (Lines 14-23): The initial application mapping  $AM_0$  is generated to check if the problem is feasible and whether time slack is available. For all task,  $AM_0$  uses the first configuration in  $rPC_i$  as the Selected Configuration  $SC_i$  (Line 15). Setting  $st_i = EST_i$  to Eq. 7, we obtain the task mapping  $(TM_i^{SC_i})$  per task (Line 16). The set of all task mappings provides the  $AM_0$  (Line 18). Then, its schedule length  $SL_{AM_0}$  is obtained (Line 19). If it is higher than the deadline, the problem is infeasible (Lines 20-21), and the algorithm stops. If it is equal to the deadline, the initial application mapping is the final mapping and the algorithm stops (Lines 22-23).

**Step 3:** (Lines 25-26) If the initial schedule length is less than the deadline (Line 24), time slack exists. Overall, different task configurations and different tasks that can be relaxed in order to obtain energy savings. Algorithm 2

## Algorithm 2: Mapping Relaxation Algorithm.

```

1: AM = AM_0, SL = SL_0;

2: while SL < D and rPC_i > 1(\forall \tau_i) do

for each task \tau_i in N do

NC_i^A = rPC_i[0];

4:

NC_i^B = rPC_i[j] with max \left\{ \sum_{k \in \{o,d\}} (ES_{\tau_i^k}^j / TI_{\tau_i^k}^j) \right\};

5:

NC_i = (E^{NC_i^A} \leq E^{NC_i^B}?NC_i^A:NC_i^B);

Compute TM_i^{NC_i}, i \in \mathbb{N} (st_i = EST_i in Eq. 7);

7:

AM_i = \{TM_i^{NC_i}\};

8:

Compute SL_{AM_i} (Eq. 6);

9:

\begin{split} SLI_{i} &= SL_{AM_{i}} - SL; \\ Gain_{i} &= \frac{\sum_{k \in \{o,d\}} (ES_{\tau_{k}^{NC_{i}}}^{NC_{i}} / TI_{\tau_{i}^{k}}^{NC_{i}}))}{SLI_{i}}; \end{split}

10:

11:

12:

for each task \tau_i in N do

13:

Compute slack_{AM_i} (Eqs. 7, 9, 10);

14:

15:

\tau_{rel} = \tau_i \text{ with } \arg\max_{i \in \mathcal{N}} (Gain_i) \wedge (TI_i^{NC_i} \leq slack_{AM_i});

16:

SC_{\tau_{rel}} = NC_{\tau_{rel}};

17:

AM = AM_{\tau_{rel}} and SL = SL_{AM_{\tau_{rel}}};

18:

for each configuration pc in rPC_{\tau_{rel}}^{'el} do

19:

rPC_{\tau_{rel}} = rPC_{\tau_{rel}} - \{rPC_{\tau_{rel}} : E^{pc} \ge E^{SC_{\tau_{rel}}}\};

20:

end for

21:

22: end while

```

decides the task to be relaxed and its configuration. Initially, the current mapping (schedule length) is initialised with the initial mapping (schedule length) (Line 1). The algorithm is applied iteratively, until the schedule length reaches the deadline or all tasks reach their configuration with the least energy consumption (Line 2). First, a local search decides a new configuration per task (Lines 3-12). We combine two criteria to select a potential New Configuration  $(NC_i)$  for a task.  $NC_i^A$  explores  $rPC_i$  sequentially, by selecting always the first configuration.  $NC_i^B$  selects the j configuration in  $rPC_i$  with the highest value  $(ES_{\tau_i^o}^j/TI_{\tau_i^o}^j) + (ES_{\tau_i^d}^j/TI_{\tau_i^d}^j)$ , where  $ES_{\tau_i^o}^j$   $(ES_{\tau_i^d}^j)$  is the energy savings and  $TI_{\tau^o}^j$   $(TI_{\tau^d}^j)$  is the time increase of task  $\tau_i$  in configuration j, compared to the current selected configuration  $SC_i$ . The final selected configuration  $NC_i$ is the one with the minimum energy consumption (Line 6). After selecting a new task configuration, all task mappings are updated accordingly (Line 7). The new application mapping  $AM_i$  (Line 8) and its schedule length  $SL_{AM_i}$ (Line 9) are obtained. The difference of  $SL_{AM_i}$  with the schedule length of the current mapping SL provides the Schedule Length Increase  $(SLI_i)$ , when task  $\tau_i$  changes its current configuration  $SC_i$  to  $NC_i$  (Line 10). With this information, the overall gain  $(Gain_i)$ , considering both energy and time, that this configuration modification will bring to the overall mapping, is computed (Line 11). After the local search finishes, the global decision takes place (Lines 13-22). The time slack of each task in the current mapping  $(slack_{AM_i})$  based on task mobility through Eqs. 7, 9, 10 (Lines 13-15):

$$slack_{AM_i} = LFT_i - EST_i - et_i. (9)$$

The Latest Finish Time (LFT) of  $\tau_i$  is:

$$LFT_{i} = \left\{ \begin{array}{l} D, if \ \tau_{i} = \tau_{exit} \\ \min \left\{ \begin{array}{l} \min \\ \tau_{p} \in Proc\{\tau_{i}\} \\ \min \\ \tau_{j} \in Succ\{\tau_{i}\} \end{array} \right\}, else \end{array} \right.$$

$$(10)$$

where  $LST_i = LFT_i - et_i$  is the Latest Start Time (LST) of task  $\tau_i$ .  $Proc\{\tau_i\}$  is the processor that the task is allocated, and  $\tau_p$  are the tasks, scheduled after task  $\tau_i$ , on the same processor. The task (and its corresponding configuration) to be relaxed  $(\tau_{rel})$  is the task with highest overall gain, whose time increase in this new configuration is not larger than its available slack in the current mapping (Line 16). Last, the selected configuration (SC) for the relaxed task, the application mapping and its schedule length are updated (Lines 17-18) and all configurations that have a higher energy consumption than the selected one are removed from  $rPC_{\tau_{rel}}$  (Lines 19-21).

Fig. 2, Fig. 3 and Fig. 4 illustrate the application mapping process for the DAG in Fig 1, when M=3 processors and D=1.4. Fig 2 shows on the left the initial application mapping  $AM_0$  (step 1 and step 2) and on the right the initial schedule configuration for each task. The total energy consumption of  $AM_0$  is  $E_{AM_0} = 48.12$  mJ and schedule length is  $SL_{AM_0} = 1.3515$  sec. Since the schedule length is lower than the deadline, there exists some time slack. During relaxation (step 3), the task  $\tau_1$  is selected, along with the configuration where both original and duplication copies are executed with frequency  $f_2$ , since this task and configuration provide the highest gain, since the energy consumption is reduced without increasing the schedule length (Inf means positive infinity in Fig. 3 and the one with most energy saving is selected if there are multiple Inf cases). The updated application mapping is depicted in Fig. 3. The algorithm continues to apply relaxation, as long as time slack is still available, by selecting the next task and configuration with the highest gain. The final application mapping is depicted in Fig 4, with an energy consumption equal to E = 41.67 mJ and a schedule length of SL = 1.3971 sec.

### 3.3 Time complexity

In the proposed heuristic approach, the maximum number of possible configurations for each task is  $L + \binom{2}{L}$  (denoted as K). Phase A takes O(NK) time to obtain the possible configuration space for all tasks. Phase B firstly

\*Scheduled configuration

| $C_i^j$         | $f_i^o$ | $f_i^d$ | $SLI_i$ | $Gain_i$ |

|-----------------|---------|---------|---------|----------|

|                 | (GHz)   | (GHz)   | (sec)   |          |

| $C_0^0$ $C_1^0$ | 1.0     | -       | -       | -        |

|                 | 1.0     | -       | -       | -        |

| $C_{2}^{0}$     | 1.0     | 1.0     | -       | -        |

| $C_2^0 \ C_3^0$ | 1.0     | -       | -       | -        |

| $C_4^0$         | 1.0     | -       | -       | -        |

| $C_{5}^{0}$     | 1.0     | -       | -       | -        |

Fig. 2: Illustration example (Fig. 1): Initial application mapping  $AM_0$ .

| $\tau_0^o / f$ | $\tau_6^o / f_6$ | $\tau_3^o / f_6$ | $\tau_5^o$ / | $f_6$   | $\rightarrow \theta_1$ |

|----------------|------------------|------------------|--------------|---------|------------------------|

|                | $\tau_2^d / f_6$ | $	au_1^d / f_2$  |              |         | $\rightarrow \theta$   |

|                | $\tau_1^o / f_2$ | $\tau_4^o / f_6$ |              |         | $\rightarrow \theta$   |

| 0              | t <sub>1</sub>   | $t_2 t_3$        | $t_{5}t_{6}$ | $t_7$ D |                        |

| $t_1 = 0.183$  | $t_2 = 0.50$     | $t_3 = 0.570$    | $t_4 = 0.7$  | 181     |                        |

| $t_5 = 0.90$   | 05 $t_6 = 0.96$  | $t_7 = 1.35$     | 515          |         |                        |

| *Scheduled configuration |         |         |         |          |  |  |  |  |  |

|--------------------------|---------|---------|---------|----------|--|--|--|--|--|

| $C_i^j$                  | $f_i^o$ | $f_i^d$ | $SLI_i$ | $Gain_i$ |  |  |  |  |  |

|                          | (GHz)   | (GHz)   | (sec)   |          |  |  |  |  |  |

| $C_0^0$                  | 1.0     | -       | 0.031   | 2,246.9  |  |  |  |  |  |

| $C_1^0$                  | 0.8291  | 0.8291  | 0       | Inf      |  |  |  |  |  |

| $C_2^0$                  | 1.0     | 1.0     | 0.066   | 2,309.2  |  |  |  |  |  |

| $C_{3}^{0}$              | 1.0     | -       | 0.08    | 858.9    |  |  |  |  |  |

| $C_4^0$                  | 1.0     | -       | 0       | Inf      |  |  |  |  |  |

| $C_5^0$                  | 1.0     | -       | 0.07    | 1,054.3  |  |  |  |  |  |

Fig. 3: Illustration example (Fig. 1):  $AM_1$  with task  $\tau_1$  relaxed.

| $	au_0^o / f_1$  | $\tau_2^o / f_6$     | $\tau_3^o / f_6$ | $\tau_5^o / f_6$ | $\theta_1$     |

|------------------|----------------------|------------------|------------------|----------------|

| $\tau_0^d / f_2$ | $\tau_2^d / f_6$     | $\tau_1^d / f_1$ |                  | $\theta_1$     |

|                  | $	au_1^o \ / \ f_1$  | $\tau_4^o / f_4$ |                  | $\theta$       |

| 0                | $t_1$ $t_2$          | $t_3$ $t_4$      | $t_6$ $t_6$      | 7 <sub>D</sub> |

| $t_1 = 0.2292$   | $t_2 = 0.5588 \ t_3$ | $= 0.6164  t_4$  | = 0.7838         | _              |

| $t_5 = 0.9461$   | $t_6 = 1.0059$       | $t_7 = 1.3971$   |                  |                |

|         | *Sched  | uled coi | nfigura | tion     |

|---------|---------|----------|---------|----------|

| $C_i^j$ | $f_i^o$ | $f_i^d$  | $SLI_i$ | $Gain_i$ |

|         | (GHz)   | (GHz)    | (sec)   |          |

| $C_0^0$ | 0.801   | 0.8291   | 0.008   | 13013.0  |

| $C_1^0$ | 0.801   | 0.801    | -       | -        |

| $C_2^0$ | 1.0     | 1.0      | 0.066   | 2309.2   |

| $C_3^0$ | 1.0     | -        | 0.41    | 168.2    |

| $C_4^0$ | 0.8797  | -        | 0.12    | 472.7    |

| $C_5^0$ | 1.0     | -        | 0.066   | 1054.3   |

Fig. 4: Illustration example (Fig. 1): Final application mapping.

requires O(NlogN) time to create the priority list (PL). When task mapping is computed based on Eq. 7, for each single task mapping, the complexity is O(2logN) considering the worst case that both original and duplication copies are executed. For each single application mapping, it traverses N tasks, so the time complexity is O(2NlogN). For each experiment, considering the worst case when deadline is very relaxed so that all configurations for all tasks have to be explored in the relaxation algorithm, the total complexity of the whole application mapping under this very relaxed deadline is  $O(2N^2KlogN)$ .

Table 3: Processor characteristics

| $v_l$ (V)   | 0.85   | 0.90   | 0.95   | 1.00   | 1.05   | 1.1    |

|-------------|--------|--------|--------|--------|--------|--------|

| $f_l$ (GHz) | 0.801  | 0.8291 | 0.8553 | 0.8797 | 0.9027 | 1.0    |

| $C_{eff}$   | 7.3249 | 8.6126 | 10.238 | 12.315 | 14.998 | 18.497 |

## 4 Experimental Results

This section evaluates the proposed heuristic (H\_RAFTM) with i) the optimal solver using Gurobi 9.0.2 (O\_RAFTM) as in [14], and ii) two SoA heuristics a) the Reliability-Aware Mapping (H\_RAM), that meets the reliability constraint without task duplication, similar to [5] and ESRG algorithm in [4], and b) the Task Duplication Mapping (H\_TDM), applying task duplication for all tasks, similar to [1,4], when the number of replicas is two, or to [17], with 100% task duplication. To evaluate the approaches, the following metrics are used:

- 1. Feasibility, i.e., the number of experiments where a solution is found out of the total number of experiments (NE).

- 2. Energy Consumption (EC) of proposed heuristic approach, compared to the energy consumption of the optimal approach O\_RAFTM and two SoA heuristic approaches H\_RAM and H\_TDM.

- 3. Reliability Improvement (RI)  $(RI = R_i R_i^{th})$ , i.e., the task reliability above the task reliability threshold.

- 4. Computation time (CT), i.e., the time required for each approach to find a solution.

Note that, an approach may fail to find a solution, especially in strict deadlines. In order to fairly compare the energy consumption, reliability improvement and the computation time, we present the average values of the experiments where both compared approaches (i.e., O\_RAFTM vs H\_RAFTM, H\_RAFTM vs H\_RAFTM vs H\_RAFTM vs H\_RAFTM vs H\_RAFTM) were able to find a solution.

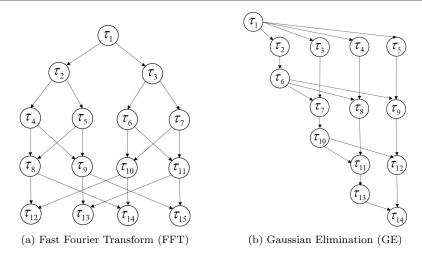

The model of the processor is based on a 32-bit RISC-V Instruction Set Architecture (ISA) with 5-stage pipeline [18]. Regarding DVFS, L=6 voltage/frequency levels are used [19] (Table 3), considering 64 nm technology. The number of processors in the experiments is M = 2, 4, 6. The task graphs are obtained both from real-world applications and randomly generated tasks. Regarding real-word applications, two commonly used parallel applications with different shapes of parallelism have been considered, i.e., Fast Fourier Transformation (FFT) (N = 15) and Gaussian Elimination (GE) (N = 14) [4,5]. Fig 5 depicts the shape of parallelism obtained by FFT and GE DAGs. Random generation is used for comparison with optimal approach (N=10) and for evaluation of the scalability of the heuristics (100). To obtain realistic values for the  $W_i$  of a task, common benchmarks from MiBench suite were executed on the processor. The execution cycles and memory accesses are counted and WCEC is computed, assuming that all cores may conflict during a memory access. The obtained range is  $[1 \times 10^8, 4 \times 10^8]$ , and it is used to randomly select the  $W_i$  of a task. The reliability threshold  $R_i^{th}$  of a task is selected within

Fig. 5: Real-world application DAG.

the range [0.9990, 0.9995], considering a typical magnitude  $10^{-3}$  for reliability target [1]. For each application task graph, a number of experiments (denoted as NE) is performed, each time with different task characteristics ( $W_i$  and  $R_i^{th}$ ). For each experiment, D is tuned from strict to relaxed deadlines, starting from  $SL_{AM_0}$  of the initial application mapping and increased with a step of 0.1 seconds for small randomly generated DAGs and real-world DAGs and 0.5 seconds for large randomly generated DAG.

## 4.1 Comparison with optimal approach

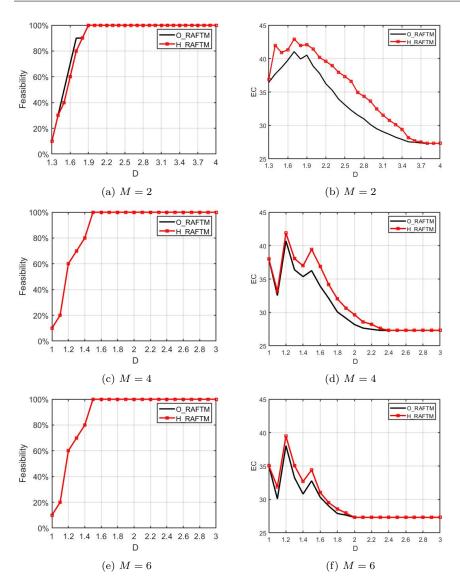

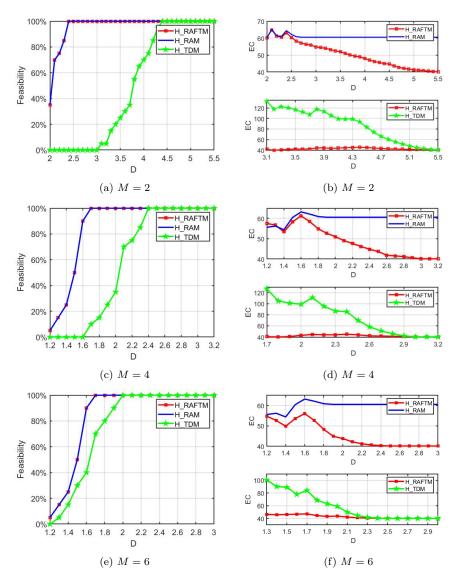

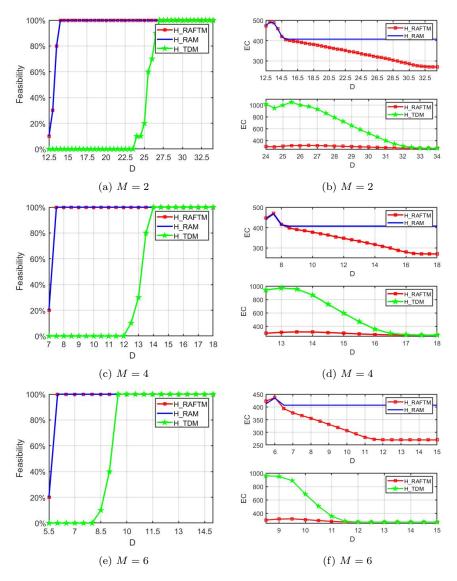

Fig. 6 and 7 compare the quality of solutions obtained by O\_RAFTM and H\_RAFTM approaches. We present the results of NE = 10 considering random graphs with N = 10 tasks, M = 2, M = 4 and M = 6 processors.

Regarding feasibility, when M=2, the H\_RAFTM feasibility is very close to the optimal feasibility, as shown in Fig. 6a, except for a few cases when the deadline is strict. The average difference before achieving 100% feasibility is 3.3%. With the number of processors increasing to M=4 (Fig. 6c) and M=6 (Fig. 6e), H\_RAFTM and O\_RAFTM achieve the same feasibility, since more resources are available to execute the original and potentially duplicated tasks.

Regarding energy consumption in Fig. 6b, Fig 6d, and Fig 6f, H\_RAFTM generally consumes slightly more energy than O\_RAFTM. When deadline is relaxed, H\_RAFTM and O\_RAFTM obtain solutions with the same energy consumption. H\_RAFTM consumes on average 7.3% (M=2), 4.4% (M=4) and 3.38% (M=6) more energy than the optimal solutions. With the processor number increasing, the energy consumption of both proposed heuristic and optimal solution flattens at earlier deadlines, since there are more processors

Fig. 6: Feasibility and Energy Consumption (EC in mJ) of optimal and heuristic approached for  $M=2,\ M=4$  and  $M=6\ (N=10)$

resource available to perform the task mapping, and thus, more options to start the tasks earlier.

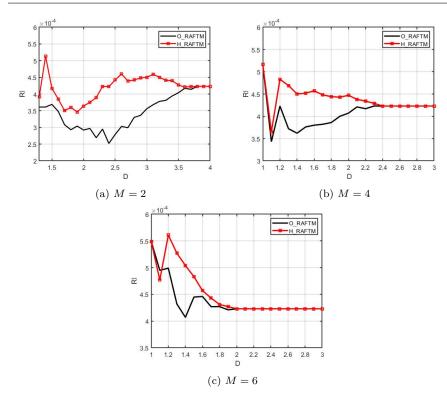

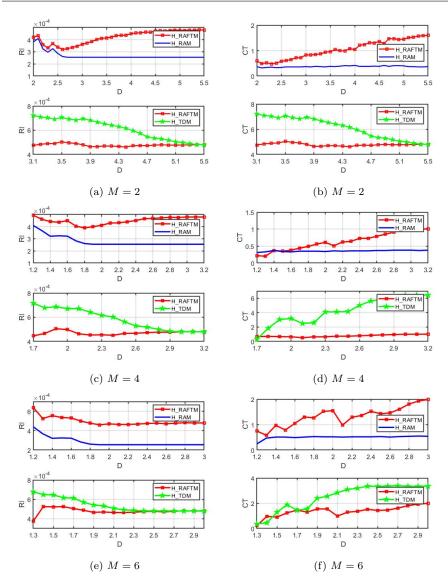

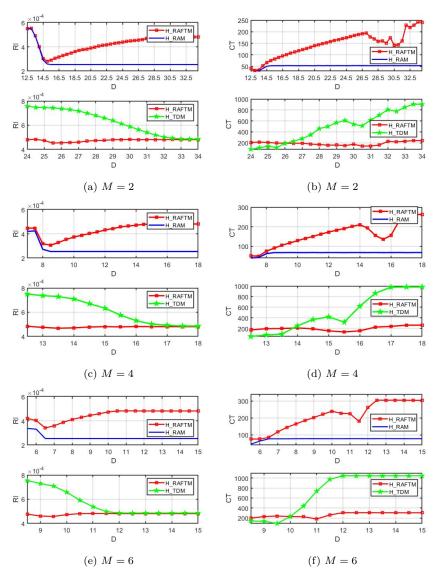

Regarding reliability improvement, H\_RAFTM provides more reliability improvement than optimal solutions at the price of consuming slightly more energy under the same deadlines, as depicted in Fig. 7a, Fig 7b, and Fig 7c.

Fig. 7: Reliability Improvement (RI) of optimal and heuristic approached for  $M=2,\,M=4$  and M=6 (N=10)

The average computation time of O\_RAFTM and H\_RAFTM is computed over the number of experiments than found a feasible solution. Table 4, Table 5 and Table 6 show the results in seconds per deadline D. It can be observed that although few tasks and processors are used, the time to obtain the optimal solution is very long, on average  $10^4$  more than the proposed H\_RAFTM.

Table 4: Computation time (seconds) for  $N=10,\,M=2$

| D       | 1.3      | 1.4      | 1.5      | 1.6      | 1.7      | 1.8      | 1.9      | 2.0      | 2.1      |

|---------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| O_RAFTM | 424.8    | 523.4    | 537.1    | 275.5    | 432.2    | 739.7    | 832.7    | 1,645.6  | 2,349.0  |

| H_RAFTM | 0.15     | 0.13     | 0.14     | 0.17     | 0.17     | 0.20     | 0.22     | 0.23     | 0.29     |

| D       | 2.2      | 2.3      | 2.4      | 2.5      | 2.6      | 2.7      | 2.8      | 2.9      | 3.0      |

| O_RAFTM | 3,358.1  | 5,368.3  | 4,543.9  | 9,335.6  | 11,974.2 | 13,038.4 | 19,364.5 | 27,312.9 | 19,378.6 |

| H_RAFTM | 0.32     | 0.31     | 0.36     | 0.33     | 0.36     | 0.35     | 0.41     | 0.42     | 0.42     |

| D       | 3.1      | 3.2      | 3.3      | 3.4      | 3.5      | 3.6      | 3.7      | 3.8      | 3-4      |

| O_RAFTM | 13,155.9 | 21,493.1 | 24,228.4 | 77,477.5 | 5,472.0  | 4,868.6  | 4,096.3  | 2        | .5       |

| H_RAFTM | 0.49     | 0.52     | 0.47     | 0.52     | 0.56     | 0.58     | 0.59     | 0.       | 63       |

Table 5: Computation time (seconds) for N = 10, M = 4

| D            | 1.0  | 1.1  | 1.2            | 1.3            | 1.4            | 1.5            | 1.6            | 1.7        | 1.8            | 1.9        | 2.0   |

|--------------|------|------|----------------|----------------|----------------|----------------|----------------|------------|----------------|------------|-------|

| O_RAFTM      | 14.9 | 61.0 | 74.9           | 138.2          | 202.1          | 256.9          | 327.3          | 219.0      | 1039.3         | 1054.7     | 126.8 |

| H_RAFTM      | 0.19 | 0.26 | 0.27           | 0.30           | 0.35           | 0.27           | 0.33           | 0.43       | 0.47           | 0.50       | 0.57  |

|              |      |      |                |                |                |                |                |            |                |            |       |

| D            | 2.1  | 2.2  | 2.3            | 2.4            | 2.5            | 2.6            | 2.7            | 2.8        | 2.9            | 3.0        | -     |

| D<br>O_RAFTM |      |      | <b>2.3</b> 4.9 | <b>2.4</b> 1.9 | <b>2.5</b> 1.4 | <b>2.6</b> 0.6 | <b>2.7</b> 1.8 | 2.8<br>1.0 | <b>2.9</b> 1.8 | 3.0<br>2.3 | -     |

Table 6: Computation time (seconds) for N = 10, M = 6

| D       | 1.0  | 1.1   | 1.2   | 1.3   | 1.4   | 1.5    | 1.6   | 1.7   | 1.8   | 1.9   | 2.0  |

|---------|------|-------|-------|-------|-------|--------|-------|-------|-------|-------|------|

| O_RAFTM | 0.83 | 58.10 | 26.95 | 89.89 | 81.87 | 109.82 | 58.60 | 62.77 | 59.77 | 14.69 | 2.49 |

| H_RAFTM | 0.32 | 0.27  | 0.33  | 0.48  | 0.54  | 0.50   | 0.58  | 0.68  | 0.69  | 0.70  | 0.67 |

| D       | 0.1  | 0.0   | 0.0   | 2.4   | 2 5   | 2.6    | 2.7   | 0.0   | 2.0   | 2.0   |      |

| ע       | 2.1  | 2.2   | 2.3   | 2.4   | 2.5   | 2.6    | 2.1   | 2.8   | 2.9   | 3.0   | -    |

| O_RAFTM | 0.74 | 0.65  | 0.63  | 0.66  | 0.66  | 0.64   | 0.64  | 0.63  | 0.60  | 0.60  | -    |

Overall, the obtained results show that i) H\_RAFTM provides near-optimal solutions, and the solutions tend to converge to the optimal ones with the number of processors increasing, ii) as expected, H\_RAFTM takes significantly less time to obtain the results compared to the optimal approaches.

## 4.2 Comparison with other heuristics

This section evaluates the behavior of the proposed H\_RAFTM heuristic to H\_RAM and H\_TDM heuristics, considering real-world application DAGs and large random generated DAGs.

## 4.2.1 Real-word DAG

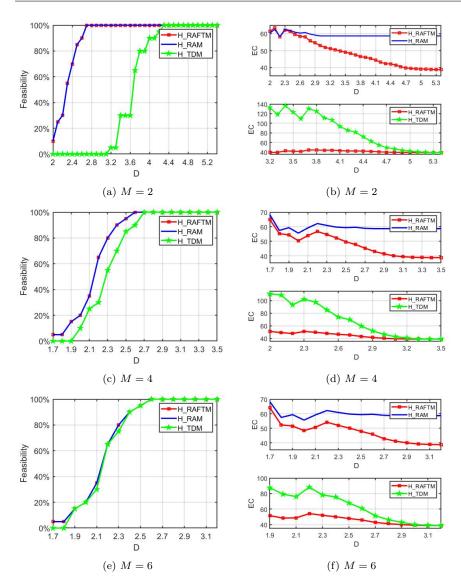

The quality of solutions obtained by H.RAFTM, H.RAM and H.TDM heuristics for the FFT (N=15) are compared in Fig. 8 and Fig. 10, and for the GE (N=14) in Fig. 9 and Fig. 11, considering M=2, M=4 and M=6 processors, and NE=20 experiments.

The feasibility of the three heuristics for FFT and GE benchmarks is depicted in the left column of Fig. 8 and Fig. 9. Comparing to H\_TDM, the proposed H\_RAFTM can find solutions in significantly more experiments than H\_TDM, especially when the deadline is not fully relaxed or number of cores is reduced. When tasks meet their reliability constraint, H\_RAFTM does not need to duplicate these tasks. However, H\_TDM duplicates all tasks, and thus, it is able to find solutions only when the deadline is relatively relaxed or several processors exist to run the tasks in parallel. Before obtaining 100% feasibility for both approaches, on average, H\_RAFTM finds a solution in more experiments than H\_TDM, i.e., 70.2% for FFT and 59.4% for GE (M=2), 47.5%

Fig. 8: Feasibility and energy consumption (EC in mJ) of FFT (N=15) for  $M=2,\,M=4$  and M=6.

for FFT and 14.5% for GE (M=4) and 47.5% for FFT and 2.2% for GE (M=6). Note that, H\_RAFTM and H\_RAM have the same feasibility. This behavior is explained as follows: when H\_RAM finds a solution, it means the reliability constraint of all tasks can be met by executing only the original task with a high frequency. In this case, H\_RAFTM is also able to find this solution.

Fig. 9: Feasibility and Energy Consumption (EC in mJ) of GE (N=14) for  $M=2,\ M=4$  and M=6.

The energy consumption obtained by the solutions of the three heuristics for FFT and GE is depicted in the right column of Fig. 8 and Fig. 9. Comparing H\_RAFTM and H\_RAM, we observe that they consume similar energy at very strict deadlines, when the number of processors is small. In this case, H\_RAFTM behaves similarly to H\_RAM, i.e., mainly executing the original tasks with the frequency required to achieve the reliability constraint. With

deadline relaxing, H\_RAFTM starts to consume less energy than H\_RAM. H\_RAFTM achieves this gain by exploring the available time slack to duplicate tasks in order to save energy, e.g., up to ~50.9% for FFT at relaxed deadlines. Similarly, when more processors are available, H\_RAFTM can take advantage of these resources and execute duplicated task in parallel. Comparing H\_RAFTM and H\_TDM, as H\_TDM applies task duplication for every task, it cannot find solutions in very strict deadlines. H\_RAFTM consumes significantly less energy than H\_TDM. H\_RAFTM selects the task configuration, if exists, with only the original task, meeting the reliability constraint and consuming less energy than configurations with duplicated tasks. Since H\_TDM duplicates all tasks, its energy consumption can be significant, when it finds a solution. In relaxed deadlines, H\_RAFTM behaves similar to H\_TDM, i.e. duplicates the tasks when less energy is consumed.

The average reliability improvement obtained by the solutions of the three heuristics is depicted in the left column of Fig. 10 and Fig. 11. H\_RAFTM achieves higher reliability than RAM, except in very strict deadlines. As explained above, when there is not available time slack to perform duplication, H\_RAFTM behaves similarly to H\_RAM as most of the tasks are executed with only their original copy. Compared to H\_TDM, H\_RAFTM provides lower reliability for tight deadlines, as it duplicates only a part of the task-set. The same reliability improvement can be achieved in relaxed deadlines, since both H\_RAFTM and H\_TDM duplicate tasks similarly.

The computation time of H\_RAFTM, H\_RAM and H\_TDM heuristics is depicted in the right column of Fig. 10 and Fig. 11. Overall, when the deadline increases, the trend of computation time for H\_RAM is to remain stable, for H\_RAFTM to slightly increase and for H\_TDM to increase with a higher factor. The computation time to obtain a feasible solution increases with deadline relaxing, due to the fact that the proposed heuristic explores the PC space for each task, based on the deadline constraints. Therefore, the more relaxed the deadline is, the larger is the PC space to be explored per task, and thus, more time is needed. Note that, H\_TDM is the most expensive approach in terms of computation time. This behavior is due to the fact that all tasks are duplicated, which increases the total number of tasks to be scheduled and the number of PCs in each task PC space, and thus, the time to find a solution. For H\_RAM, it only executes original tasks, thus it has a reduced number of PCs in the PC space, taking the least time to obtain a solution. However, it provides less energy savings as explained above, especially at relaxed deadlines.

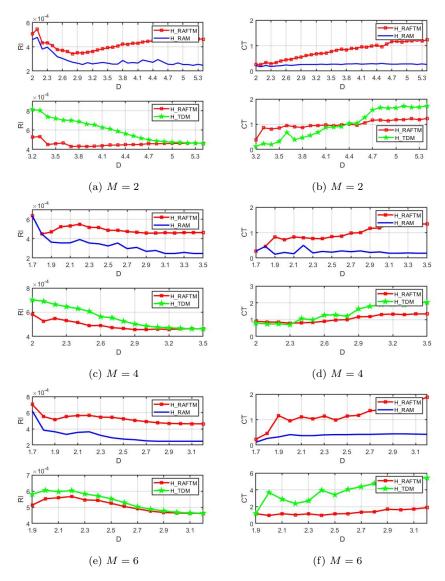

#### 4.2.2 Large random generated DAGs

Fig. 12 and Fig. 13 compare the quality of solutions obtained by H\_RAFTM, H\_RAM and H\_TDM heuristics for a large randomly generated task graph with  $N=100,\,M=2,\,M=4$  and M=6 processors, and NE=10 experiments. Previous observations regarding feasibility, energy consumption, reliability improvement and computation time for the three heuristics are also verified by the experiments with the large randomly generated DAG. For instance, as

Fig. 10: Reliability improvement (RI) and Computation Time (CT in seconds) of FFT (N=15) for  $M=2,\ M=4$  and M=6.

the deadline is not fully relaxed or number of cores is reduced H\_RAFTM has increased feasibility compared to H\_TDM, i.e., 84.8% for M=2, 85.7% for M=4 and 83.8% for M=6. Moreover, as the number of processors is increased the energy consumption is reduced as lower frequencies can be selected and partial task duplication can be applied by H\_RAFTM, as long as the reliability constraint is met.

Fig. 11: Reliability improvement (RI) and Computation Time (CT in seconds) of GE (N=14) for  $M=2,\ M=4$  and M=6.

Regarding computation time, it is increased when the number of tasks increases as expected, but still remains low compared to the prohibited computation time required for the optimal approach. For a small randomly generated task with N=10 (Table 5 when M=4 and Table 6 when M=6), the proposed heuristic takes less than 1 sec to find a solution for all experiments whereas for a large randomly generated task with N=100, the average com-

putation time (considering all experiments and deadlines) is 144 sec (M=2), 159 sec (M=4) and 212 sec (M=6). Comparing the computation time of the three heuristics for large DAGs N=100, the average computation time for H\_RAM is 52 sec (M=2), 66 sec (M=4) and 75 sec (M=6). For H\_TDM, the average computation time is 488 (M=2), 501 sec (M=4) and 718 sec (M=6). Overall, we observe that the H\_TDM is the more time consuming approach, and H\_RAM the least time consuming approach. However, H\_TDM is not able to always find solutions, whereas H\_RAFTM finds solutions with always same or less energy consumption compared to H\_RAM and H\_TDM.

#### 5 Conclusion

A heuristic algorithm is proposed to obtain the task mapping of parallel applications, under real-time, reliability and task dependency constraints. The goal is to minimize total energy consumption by deciding frequency assignment, task allocation, task scheduling and task duplication. Based on the experimental results from real-world applications and randomly generated task graphs, the proposed heuristic achieves near-optimal results, with low computation time. Compared to similar heuristics, it achieves better energy consumption and is able to find solutions even when the other approaches fail. As future work, we will propose similar heuristics for other DVFS schemes provided by platforms, such as assigning a common frequency at cluster, processor and platform level.

## References

- M. A. Haque, H. Aydin, and D. Zhu, "On reliability management of energy-aware realtime systems through task replication," *IEEE Trans. Parallel and Distributed Systems*, vol. 28, no. 3, pp. 813–825, 2017.

- 2. K. Huang, X. Jiang, X. Zhang et al., "Energy-efficient fault-tolerant mapping and scheduling on heterogeneous multiprocessor real-time systems," *IEEE Access*, vol. 6, pp. 57614–57630, 2018.

- 3. C. Gou, A. Benoit, M. Chen et al., "Reliability-aware energy optimization for throughput-constrained applications on MPSoC," in *IEEE International Conference on Parallel and Distributed Systems*, 2018, pp. 1–10.

- 4. G. Xie, Y. Chen, X. Xiao et al., "Energy-efficient fault-tolerant scheduling of reliable parallel applications on heterogeneous distributed embedded systems," *IEEE Trans. Sustainable Computing*, vol. 3, no. 3, pp. 167–181, 2018.

- G. Xie, Y. Chen, Y. Liu et al., "Resource consumption cost minimization of reliable parallel applications on heterogeneous embedded systems," *IEEE Trans. Industrial In*formatics, vol. 13, no. 4, pp. 1629–1640, 2017.

- Z. Deng, D. Cao, H. Shen et al., "Reliability-aware task scheduling for energy efciency on heterogeneous multiprocessor systems," The Journal of Super computing, 2021.

- J.Roeder, B. Rouxel, S. Altmeyer et al., "Energy-aware scheduling of multi-version tasks on heterogeneous real-time systems," in Proceeding of the 35th Annual ACM Symposium on Applied Computing, 2020, pp. 501–510.

- L. Zhang, K. Li, K. Li et al., "Joint optimization of energy efficiency and system reliability for precedence constrained tasks in heterogeneous systems," Int. Journal of Electrical Power Energy Systems, vol. 78, pp. 499–512, 2016.

Fig. 12: Feasibility and Energy Consumption (EC in mJ) of large randomly generated DAG (N=100) for  $M=2,\ M=4$  and M=6.

- B. Zhao, H. Aydin, and D. Zhu, "Shared recovery for energy efficiency and reliability enhancements in real-time applications with precedence constraints," ACM Trans. Design Automation of Electronic Systems, vol. 18, no. 2, pp. 1–21, 2013.

- Y. Guo, D. Zhu, and H. Aydin, "Reliability-aware power management for parallel realtime applications with precedence constraints," in *IEEE Int. Green Computing Conf.*, 2011, pp. 1–8.

- 11. M. Salehi, A. Ejlali, and B. M. Al-Hashimi, "Two-phase low-energy n-modular redundancy for hard real-time multi-core systems," *IEEE Trans. Distributed Systems*, vol. 27,

Fig. 13: Reliability Improvement (RI) and Computation Time (CT in seconds) of large randomly generated DAG (N=100) for  $M=2,\ M=4$  and M=6.

- no. 5, pp. 1497–1510, 2016.

- 12. M. Salehi, M. K. Tavana, S. Rehman *et al.*, "DRVS: Power-efficient reliability management through dynamic redundancy and voltage scaling under variations," in *IEEE/ACM Int. Symp. Low Power Electronics and Design*, 2015, pp. 225–230.

- 13. M. Cui, L. Mo, A. Kritikakou, and E. Casseau, "Energy-aware partial-duplication task mapping under real-time and reliability constraints," in *International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation*, ser. Lecture Notes in Computer Science, A. Orailoglu, M. Jung, and M. Reichenbach, Eds., vol.

- $12471. \quad {\rm Springer}, \ 2020, \ {\rm pp.} \ \ 213-227.$

- M. Cui, A. Kritikakou, L. Mo, and E. Casseau, "Fault-tolerant mapping of real-time parallel applications under multiple DVFS schemes," in *IEEE Real-Time and Embedded Technology and Applications Symposium*. IEEE, 2021, pp. 387–399.

- 15. J. Zhou, J. Sun, X. Zhou et al., "Resource management for improving soft-error and lifetime reliability of real-time MPSoCs," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 38, no. 12, pp. 2215–2228, 2019.

- K. Skadron, M. R. Stan, K. Sankaranarayanan, W. Huang, S. Velusamy, and D. Tarjan, "Temperature-aware microarchitecture: Modeling and implementation," ACM Transactions on Architecture and Code Optimization, vol. 1, no. 1, p. 94–125, Mar. 2004.

- 17. S. Tosun, "Energy- and reliability-aware task scheduling onto heterogeneous MPSoC architectures," *The Journal of Supercomputing*, vol. 62, 2012.

- 18. S. Rokicki, D. Pala, J. Paturel *et al.*, "What you simulate is what you synthesize: Designing a processor core from c++ specifications," in *IEEE/ACM Int. Conf. Computer-Aided Design*, 2019.

- G. Quan and V. Chaturvedi, "Feasibility analysis for temperature-constraint hard realtime periodic tasks," *IEEE Trans. on Industrial Informatics*, vol. 6, no. 3, pp. 329–339, 2010