## Exploring the collaboration between FEniCSx and StarPU

Thomas Morin

### ▶ To cite this version:

Thomas Morin. Exploring the collaboration between FEniCSx and StarPU. Distributed, Parallel, and Cluster Computing [cs.DC]. 2022. hal-03897912

### HAL Id: hal-03897912 https://inria.hal.science/hal-03897912

Submitted on 14 Dec 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Exploring the collaboration between FEniCSx and StarPU

Thomas Morin

14th December 2022 Version: First Draft

## Exploring the collaboration between FEniCSx and StarPU

BY Maelstrom team

Investigate cooperation between FEniCSx' DOLFINx computational back-end for the Finite Element Method and the StarPU task-based runtime system developed by STORM

14th December 2022

#### Thomas Morin

Exploring the collaboration between FEniCSx and StarPU Internship report, 14th December 2022 Supervisors: Olivier Aumage James D. Trotter

### Maelstrom team

Bordeaux, Oslo

Thanks

## Abstract

Motivated by the idea of having all the work chain parallelized for the Finite Element Method; we looked at the parallelization of the assembling phase on the FEM.

We have used the FEniCSx collection of tools for solving Partial Differential Equations; used by the Simula laboratory for the FEM part, and we try to use the StarPU runtime for parallelizing manycore architectures developed by the STORM team at INRIA Bordeaux

In this document, we explore different strategies for combining these tools.

## Contents

| 1 | Intro                                                                                        | oduction                                                                                                                                                                                                                                                                                                                                                                   | 1                                 |

|---|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|   | 1.1                                                                                          | The Finite Element Method                                                                                                                                                                                                                                                                                                                                                  | 5                                 |

|   | 1.2                                                                                          | The FEniCSx tools for the Finite Element Method                                                                                                                                                                                                                                                                                                                            | 6                                 |

|   |                                                                                              | 1.2.1 A benchmark code for having a concise code                                                                                                                                                                                                                                                                                                                           | 7                                 |

|   | 1.3                                                                                          | A parallel programming model: the task programming model and                                                                                                                                                                                                                                                                                                               |                                   |

|   |                                                                                              | the Sequential Task Flow (STF)                                                                                                                                                                                                                                                                                                                                             | 7                                 |

|   | 1.4                                                                                          | StarPU, a runtime system based on the STF                                                                                                                                                                                                                                                                                                                                  | 9                                 |

|   | 1.5                                                                                          | Research Aim                                                                                                                                                                                                                                                                                                                                                               | 11                                |

|   | 1.6                                                                                          | Difficulties and race conditions on the assembly part                                                                                                                                                                                                                                                                                                                      | 12                                |

|   | 1.7                                                                                          | Research Guidelines                                                                                                                                                                                                                                                                                                                                                        | 12                                |

|   | 1.8                                                                                          | Dissertation Outline                                                                                                                                                                                                                                                                                                                                                       | 13                                |

|   | 1.9                                                                                          | Experimental environment                                                                                                                                                                                                                                                                                                                                                   | 13                                |

|   |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                            |                                   |

| 2 | Parc                                                                                         | allelize the assembly part of the FEM by using the atomic solution                                                                                                                                                                                                                                                                                                         | 17                                |

| 2 | <b>Para</b><br>2.1                                                                           | allelize the assembly part of the FEM by using the atomic solution<br>Explanation of the atomic solution                                                                                                                                                                                                                                                                   | <b>17</b><br>18                   |

| 2 |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                            |                                   |

| 2 | 2.1                                                                                          | Explanation of the atomic solution                                                                                                                                                                                                                                                                                                                                         | 18                                |

| 2 | 2.1<br>2.2                                                                                   | Explanation of the atomic solution                                                                                                                                                                                                                                                                                                                                         | 18<br>19                          |

| 2 | 2.1<br>2.2<br>2.3                                                                            | Explanation of the atomic solution                                                                                                                                                                                                                                                                                                                                         | 18<br>19<br>19                    |

| 2 | <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ol>                  | Explanation of the atomic solution                                                                                                                                                                                                                                                                                                                                         | 18<br>19<br>19<br>20              |

|   | <ul> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>Why</li> </ul>     | Explanation of the atomic solution                                                                                                                                                                                                                                                                                                                                         | 18<br>19<br>19<br>20              |

|   | <ul> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>Why</li> </ul>     | Explanation of the atomic solution       Implementation of the atomic solution         Implementation of the atomic solution       Implementation         Prior remarks       Implementation         Testing the solution       Implementation         Chapter Summary       Implementation         Y the buffer solution is not a good solution for parallelizing the as- | 18<br>19<br>19<br>20<br>23        |

|   | <ul> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>Why sem</li> </ul> | Explanation of the atomic solution                                                                                                                                                                                                                                                                                                                                         | 18<br>19<br>20<br>23<br><b>25</b> |

|    | 3.4        | Chapter Summary                                                            | 29       |

|----|------------|----------------------------------------------------------------------------|----------|

| 4  |            | g a different algorithm, designed for massive parallelism                  | 31       |

|    | 4.1        | Using a different algorithm: the rowwise algorithm                         | 33<br>34 |

|    | 4.2<br>4.3 | Implementation of the algorithm         Testing and evaluate the algorithm | 34<br>35 |

|    | 4.0        | 4.3.1 The rowwise algorithm on CPUs                                        | 35       |

|    |            | 4.3.2 The rowwise algorithm on GPUs                                        | 38       |

|    |            | 4.3.3 The rowwise algorithm on heterogeneous nodes                         | 39       |

|    | 4.4        | What about managing computing resources in a clustered man-                |          |

|    |            | ner?                                                                       | 41       |

|    | 4.5        | Chapter Summary                                                            | 42       |

| 5  | Col        | oring the mesh to avoid race conditions                                    | 43       |

|    | 5.1        | Trying to color the mesh to avoid the race conditions on the cell-         |          |

|    |            | wise algorithm                                                             | 45       |

|    |            | 5.1.1 Experiments                                                          | 46       |

|    | 5.2        | First version of the solution: one color by task                           | 46       |

|    | 5.3        | Second version of the coloration: enabling several slices on the           |          |

|    |            | same color, use of barrier                                                 | 49       |

|    |            | 5.3.1 Coloration of the mesh and needed dependencies.                      | 49       |

|    |            | 5.3.2 A preliminary solution: express dependency by a barrier              | 50       |

|    |            | 5.3.3 Evaluation of the solution                                           | 51       |

|    | 5.4        | Third version of the coloration: enabling an unordered execution,          | 52       |

|    |            | simplification of the problem                                              | 52       |

|    |            | 5.4.2 Go out of the FEM to simplify the problem                            | 54       |

|    |            | 5.4.3 Description of the used algorithm                                    | 56       |

|    |            | 5.4.4 Evaluation of the idea                                               | 57       |

|    |            | 5.4.5 Go back to the FEM                                                   | 59       |

|    | 5.5        | Chapter Summary                                                            | 61       |

| 6  | Cor        | nclusion                                                                   | 63       |

|    | 6.1        | Different techniques to assemble matrices                                  | 64       |

|    | 6.2        | Evaluation of the different strategies                                     | 64       |

|    | 6.3        | Future work to improve these strategies                                    | 65       |

| Re | eferer     | nces                                                                       | 67       |

### References

## List of Figures

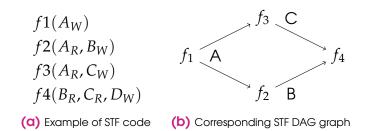

| 1.1 | Example of task graph generated from sequential source code           | 9  |

|-----|-----------------------------------------------------------------------|----|

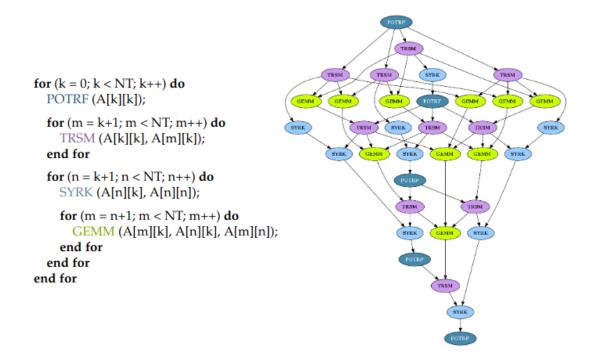

| 1.2 | Tiled Cholesky factorization and the resulting task graph [8]         | 10 |

| 1.3 | Topology of the machines sirocco23 and sirocco24.                     | 14 |

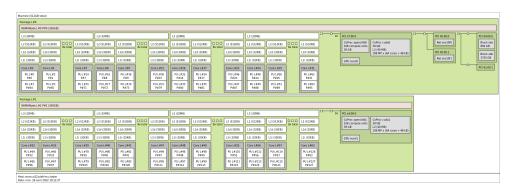

| 1.4 | Topology of the machines of partition bora                            | 15 |

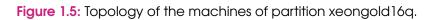

| 1.5 | Topology of the machines of partition xeongold16q.                    | 16 |

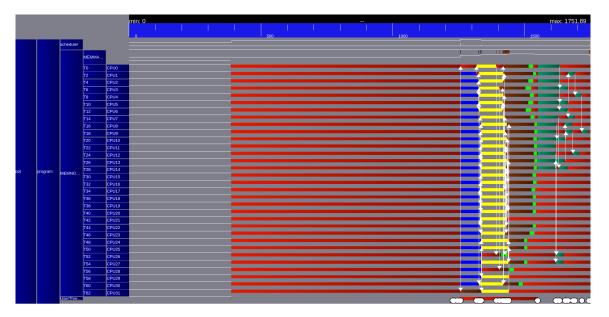

| 3.1 | Trace of problematic buffered operations on the assembly bench-       |    |

|     | mark code.                                                            | 27 |

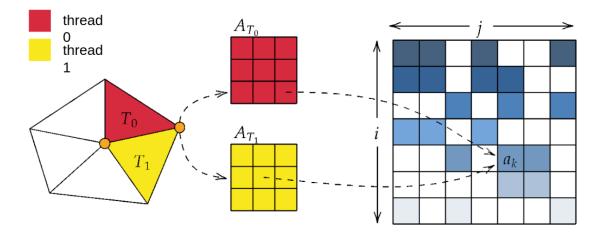

| 4.1 | Illustration of the cellwise algorithm                                | 33 |

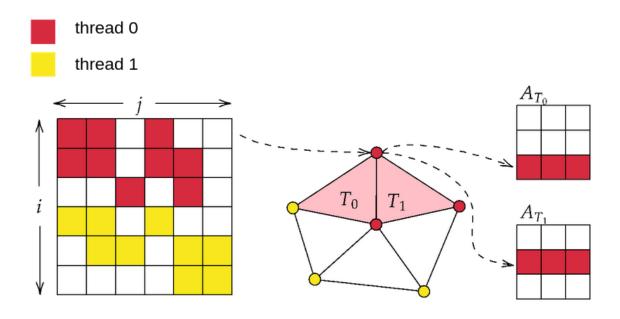

| 4.2 | Illustration of the rowwise algorithm                                 | 34 |

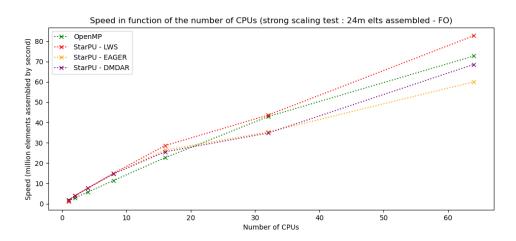

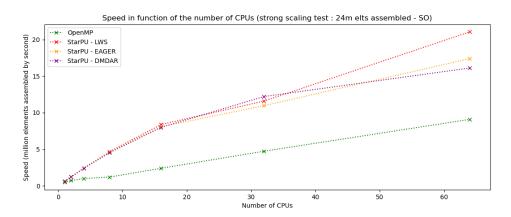

| 4.3 | Speed of assembling the first order Laplacian operator according      |    |

|     | to the number of cores.                                               | 36 |

| 4.4 | Speed of assembling the second order Laplacian operator ac-           |    |

|     | cording to the number of cores.                                       | 36 |

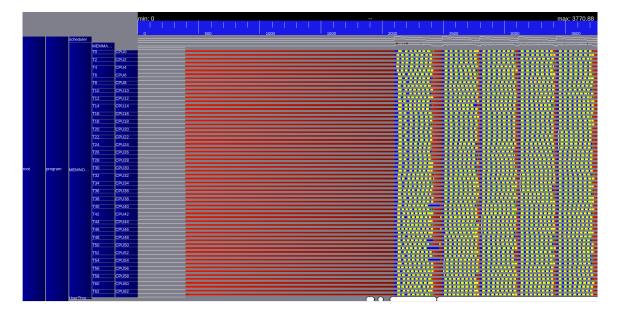

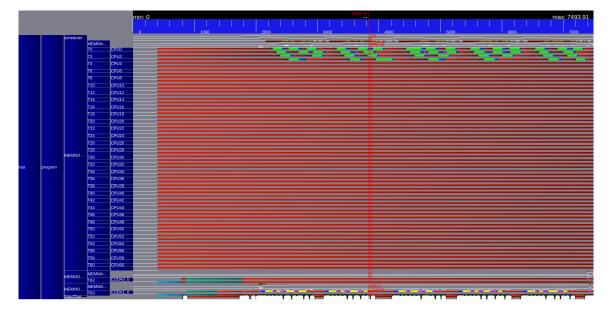

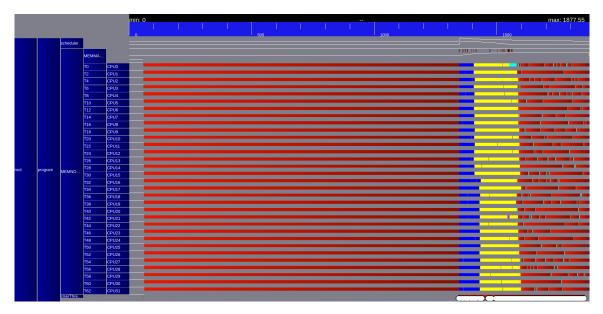

| 4.5 | Trace of execution of the assembly with 64 CPUs and the LWS sched-    |    |

|     | uler on the assembly benchmark code.                                  | 37 |

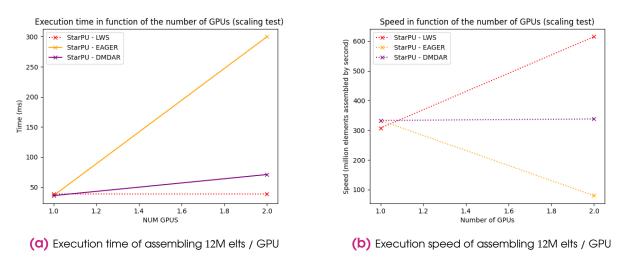

| 4.6 | Execution time and speed of assembling 12M elts / GPU on A100s        | •  |

| no  | GPUs.                                                                 | 38 |

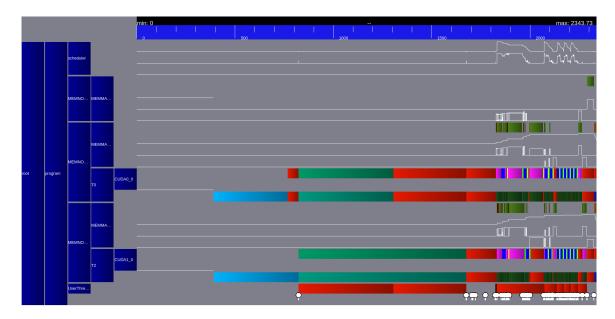

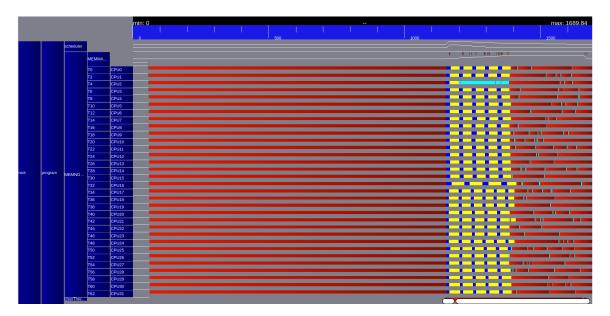

| 4.7 | Trace of execution of the assembly with 2 GPUs and the LWS sched-     | 00 |

| ,   | uler on the assembly benchmark code.                                  | 39 |

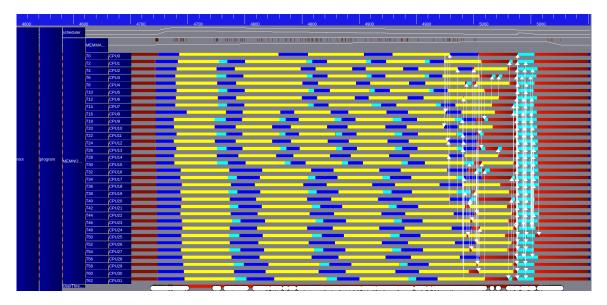

| 4.8 | Trace of execution of the assembly with 64 CPUs; 2 GPUs with the      | 07 |

| 4.0 | DMDAR scheduler on the assembly benchmark code.                       | 40 |

|     | Divid/ it scheduler of the assembly benchmark code.                   | 40 |

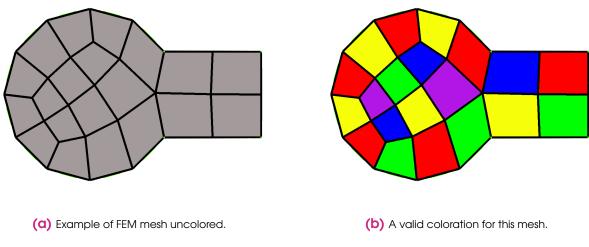

| 5.1 | A mesh and a possible correct coloration                              | 45 |

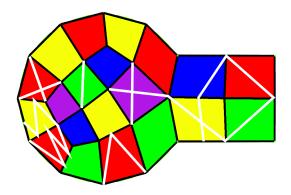

| 5.2 | A slice coloration of the mesh of Figure 5.1a but with smaller cells. | 46 |

| 5.3  | Trace of execution of the assembly with 32 CPUs with the LWS sched-  |    |

|------|----------------------------------------------------------------------|----|

|      | uler on DOLFINx; write accesses for scatter (scatter tasks are se-   |    |

|      | quential)                                                            | 47 |

| 5.4  | Trace of execution of the assembly with 32 CPUs with the LWS sched-  |    |

|      | uler on DOLFINx; write accesses for scatter and priorities (scatter  |    |

|      | tasks are sequential)                                                | 48 |

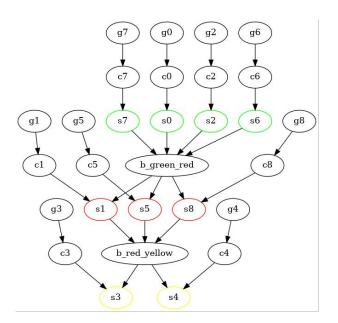

| 5.5  | Example of DAG with coloration for NTASKS = 9; NCOLS = $3 \dots$     | 51 |

| 5.6  | Trace of execution of the assembly with 32 CPUs with the LWS sched-  |    |

|      | uler on DOLFINx ; coloration of scatter tasks with barrier           | 52 |

| 5.7  | Time in seconds of coloration problem for different strategies, dif- |    |

|      | ferent configurations, and different numbers of CPUs                 | 58 |

| 5.8  | Appendix of Figure 5.7 ; mix of $3^{rd}$ and $5^{th}$ strategies     | 58 |

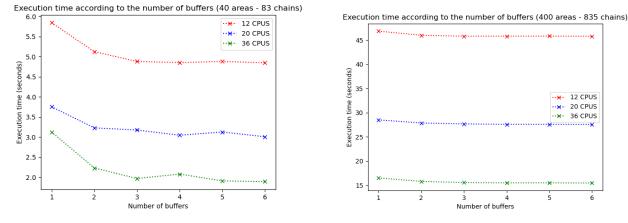

| 5.9  | Evolution of the execution time according to the number of buffers   |    |

|      | with different configurations.                                       | 59 |

| 5.10 | Trace of execution of assembly with 32 CPUs, Poisson case (4096 x    |    |

|      | 2048), xeongold16q partition                                         | 60 |

|      |                                                                      |    |

### Introduction

**77** There is no wealth but life. Life, including all its powers of love, of joy, and of admiration.

– John Ruskin –

| 1.1 | The Finite Element Method                                      | 5  |

|-----|----------------------------------------------------------------|----|

| 1.2 | The FEniCSx tools for the Finite Element Method                | 6  |

|     | 1.2.1 A benchmark code for having a concise code               | 7  |

| 1.3 | A parallel programming model: the task programming             |    |

|     | model and the Sequential Task Flow (STF)                       | 7  |

| 1.4 | StarPU, a runtime system based on the STF                      | 9  |

| 1.5 | Research Aim                                                   | 11 |

| 1.6 | Difficulties and race conditions on the assembly part $\ldots$ | 12 |

| 1.7 | Research Guidelines                                            | 12 |

| 1.8 | Dissertation Outline                                           | 13 |

| 1.9 | Experimental environment                                       | 13 |

|     |                                                                |    |

Today, modeling the world is based on Partial Differential Equations (PDEs). PDEs show us how a parameter influences a phenomenon. We find a lot of PDEs in many fields. Their goal is to model different aspects of the world. In particular, they focus on fields for modeling properties such as Physics, Financial sciences, Fluid mechanics, and Quantum mechanics.

A PDE is an equation for which the unknowns are multi-variable functions, and the relations on the equation are on the partial derivatives of the functions. They are expressed in a domain, called solving space. The PDEs are a generalization of the Ordinary Differential Equations (ODE). Often, they may have several solutions because, in contrast to ODEs, they have less restrictive boundary conditions. They are everywhere because they allow us to understand how different parameters evolve together like in complex systems. We can for example talk about the Heat Equation, which explains how heat is diffused in a system, or the Burger Equation, which is used for illustrating Adaptive Mesh Refinement codes. Another really important set of PDEs is Maxwell's equations, which is the foundation of classical electromagnetism. Among the most important questions concerning PDEs, we can talk about the existence and smoothness of solutions for the Navier-Stokes equations, which describe the motion of viscous fluid substances, and which is one of the Millennium Prize Problems defined in 2000.

Generally, it is admitted that there is no general fashion for solving PDEs. In fact, PDEs are divided into different types, each with its own particular solving methods.

Numerical methods are important tools for solving PDE. They include the Finite Element Method, the Finite Difference Method, and the Finite Volume Method. These methods use the same scheme of solving to approximate the solution. These methods approximate the solution by dividing the solving space into smaller pieces. Then, for each piece, the idea is to express the problem with fewer constraints which enables us to easily solve it. Finally, unifying all the smaller solutions gives an approximation of the solution on the global mesh. Unfortunately, these methods are resource-greedy.

However, for some years, we have seen supercomputers and manycores architectures appearing. With this type of machine, all these methods become more tractable and much more accurate. Thus, it allows us to use them and give us good approximations. The problem is that computers become more and more complex and more and more difficult to program. To give an example, in June 2012, the first system in TOP500 was Sequoia - BlueGene/Q, with 17 petaflop/s with 1,572,864 cores. In June 2022, the first system in TOP500 is Frontier, with 8,730,112 cores and computing power of 1102 petaflop/s. Thus, in 10 years, the best computers are 65 times more powerful, with 5 times more cores and over 400 times more RAM (700 PB versus 1.6 PB). Similarly, Frontier has CPUs and GPUs, while Sequoia has only CPUs. It means that this new computer is heterogeneous, so balancing work is really difficult.

There are several methods to deal with this problem but a common one is the task programming and the Sequential Task Flow (STF) programming model. The idea of this method is to divide the work into small pieces, the tasks, and are executed by different process units. The idea of STF is that in addition to the work, pieces of data and access modes are also given to the tasks; and then the model ensures the coherency of data. An access mode associated with a piece of data is the way the piece of data is accessed. It specifies that a piece of data will be either read, written, or both read and written by a given task. There are also additional access modes, such as the commute one, but the most important are the three described before. For example, a task  $T_1$  which is going to make a write access on a piece of data A has to be executed before any task submitted subsequently, which also makes access on A.

Finally, before giving our goal on this project, we are going to quickly present two different tools. The first is FeniCSx; a PDE solver which uses the Finite Element Method. The goal of FeniCSx is to describe our PDEs' problems in a high-level fashion (in Python or C++) and then all the resolution is made in the back-end with auto-generated code. The laboratory Simula of Oslo is one of the institutions involved in the FeniCS project. The second tool is StarPU; a runtime system that implements the STF model. This tool allows us to execute tasks in different types of process units only by using one of the predefined scheduling policies. It is developed at Inria & Inria centre at the University of Bordeaux, in the STORM team.

Finally, the main aim of this report is to present how it is possible to parallelize the assembly part of the Finite Element Method (FEM). For this, we would like to evaluate different strategies of parallelization. The aim is not to create a PDE solver and a runtime system, so we will use on one hand FeniCSx as a PDE solver, and on the other hand StarPU as a runtime system. The challenge is to succeed to associate these two tools.

This project has been realized during an internship, with the tutorship of Olivier Aumage (INRIA, Bordeaux) and James D. Trotter (Simula, Oslo) in the context of the associated Team Maelstrom.

### 1.1 The Finite Element Method

In this section, we will present an overview of the Finite Element Method (FEM). This is only a summary, the reader interested in more detail is encouraged to read a numerical analysis lecture, like the one by Reddy [1], which is a good introduction to the FEM.

The FEM is a numerical analysis tool used to approximate in a given domain the solution of a partial differential equation. The idea of the FEM is to divide the domain into a collection of subdomains. For each subdomain, there is a set of equations that represents the contribution of the subdomain to the global domain. The idea is that if we solve all the equations, we will solve the initial problem. Moreover, each sub-equation is chosen to be simpler to solve (using linear systems) than the initial problem.

There are different phases for the FEM:

- 1. The first step is to make the domain discrete. This is the step described above.

- 2. Then, when there is a collection of subdomains, the goal is to create for each subdomain a linear system of equations, and so a sub-matrix per domain.

- 3. After, there is the assembly part. The aim is to create a global matrix from all the small local matrices corresponding to each subdomain problem. This matrix is sparse, which limits the amount of memory used; but it increases also the cost of potential load imbalance.

- 4. Finally, the last step is to solve this global matrix, thus resolving the initial problem.

### 1.2 The FEniCSx tools for the Finite Element Method

The FeniCSx tools are a collection of different tools for solving Partial Differential Equations. This is an open source computing platform. FEniCSx enables users to describe problems with high-level languages, like Python, and to solve them with efficient code. Also, this is an easy-to-use tool; but it allows powerful capacities for experienced and motivated programmers. FeniCSx is a new version of the FEniCS library [2], and the considered version of FEniCSx is the 0.5 version (August 2022).

To solve a problem with FEniCSx, there are several steps :

- Describe the problem with a high-level interface (in Python or C++). This is a mathematical step, with no need for a programming background; only a comprehension of the FEM.

- Compiling the described problem into low-level code. This step is managed entirely by FEniCSx. Otherwise, this is the most important part of FEniCSx: without it, it will be a classical solver.

- When the problem is compiled, you can now start to solve the problem. The first step is to assemble the matrix, to obtain the problem described in a numerical way.

- Finally, you can solve the problem by solving the assembled matrix.

- It is also possible to improve the code generated by FEniCSx, with a little programming background.

FEniCSx is not a unique tool, but it is composed of several tools :

- UFL for Unified Form Language [3]. This is a language defined for FEniCSx for the declaration of finite elements or variational forms.

- FFCx for FEniCS Form Compiler [4] is a compiler that takes UFL code and generates UFC output, a c++ interface of low-level functions. FFCx is defined for Python and C++.

- BASIX [5], which is a library with definitions for all Finite Elements. It is a domain-specific library, for evaluating functions, and having information on the topology of a mesh.

• DOLFINx, the C++ back-end which assembles the matrices and generates data for solving; and also for binding all the different parts of FEniCSx.

The solving part of the matrix generated by DOLFINx is managed by other libraries, like PETSc for example.

### 1.2.1 A benchmark code for having a concise code.

During this report, we may occasionally use a benchmark code instead of the real code of FENICSx. This is because FENICSx is a quite complex collection of tools, and so interactions between the different software and the different hard-ware could be tedious in a first approach.

To counter this, James D. Trotter has made a more concise code to isolate the assembly of the FEM; and we will use it sometimes. All the code has been tested, and the correctness of the results has been verified by hand in comparison to the results given by FENICSx.

Most of the time we have made, before making an implementation on FEN-ICSx, a previous implementation on this benchmark code. If it looks promising, then it is included on FENICSx to have a real point of view.

# 1.3 A parallel programming model: the task programming model and the Sequential Task Flow (STF)

For using all the processing units of a computer, and for having parallelism, there are several ways.

The first one is to make several processes, and each process makes a section of the work. This fashion is not hard to do but could be really hard to optimize and make efficient because interactions between processes could be tedious.

Another way is to use loop parallelism. The idea is that most of the time, the iterations of a loop are independent; or with a bit of work, this is possible to make them independent. With this idea, the goal is to make blocks of iterations and

execute each block on a different processing unit. This could be easily used for parallelizing on GPUs but it could be tedious to use it when using several types of process units together, like CPUs and GPUs.

For this, we can use the task programming model. The idea is to divide computation into small pieces of work, called tasks. The notion of task is quite close to functions: the main difference is that when you submit a task, it will be executed later, but you do not know when. For example, the cilk programming language ([6]) is an efficient language to express some variants of the task programming model.

With the task programming model, your whole application will be defined by all the tasks and the interactions between them.

There are several types of interactions between tasks but we will restrict ourselves to talking about interactions with pieces of data. Thus, it is natural to talk about the Sequential Task Flow (STF) programming model, which is a way of using tasks. The idea of the STF is to define a task as a portion of code and also pieces of data. For each piece of data, you give memory access (ie if a piece of data will be accessed in a read mode, write mode, or read-write mode); and then dependencies between tasks will be computed according to the sequential flow of task submissions [7]:

- A task *T* which makes Read access on a piece of data *D* will be executed after all the tasks which make a Write Access on *D*, which have been submitted before *T*.

- A task *T* which makes Write access on a piece of data *D* will be executed after all the tasks which make a Write or a Read Access on *D*, which have been submitted before *T*.

- Consequently, submitting a set of tasks T<sub>1</sub>; ...; Tn which makes read access on a piece of data A; between two tasks in write mode on A; allows the tasks T<sub>1</sub>, ...T<sub>n</sub> to be executed at the same moment, which generates parallelism.

There are other task models, more permissive, but the counterpart is the STF constraints allow the runtime to have more optimizations.

We can see on Figure 1.1a an example of code with the STF ; and in Figure

Figure 1.1: Example of task graph generated from sequential source code.

1.1b the corresponding dependencies represented as a graph.

The name Sequential comes from the data dependencies: there is a guarantee of semantic equivalence of a compliant parallel STF execution with respect to the sequential execution of the tasks. The equivalence is only on the declared data dependencies. Also, the sequential order is determined by the order of the sequential submission of the tasks. It means that generally, you cannot have more than one processing unit which submits tasks; or you don't have any data dependency between the tasks submitted by different PUs.

The STF is a really powerful way to express parallelism because this is a contract with a runtime system (submit-and-forget parallelism). You do not have to manage by hand all the coherency of data if the dependencies are correctly expressed. Also, another advantage is, generally, the algorithms of the sequential application and the STF application are identical, or really similar.

Finally, to represent an application with STF, it is common to use Directed Acyclic Graph. On this type of graph, a node is a task, and an edge from a task *A* to a task *B* expresses that the task *B* depends on *A*. We can see in Figure 1.2 an example of a Cholesky factorization expressed in an STF way; and the corresponding DAG.

### 1.4 StarPU, a runtime system based on the STF

We have seen that a good way of making an application parallel is using the STF. Moreover, we have also seen that computers become more and more parallel. Nowadays, most computers have one or more accelerators, like GPUs or FPGAs; and commonly, they are divided into several memory spaces (NUMA nodes). All those elements mean that it is really complicated to program computers. For example, it could be tedious, if you have several different STF tasks,

9

Figure 1.2: Tiled Cholesky factorization and the resulting task graph [8].

to know which processing unit should execute which task to optimize either the execution time or the energy consumption. To deal with this type of problem, we can talk about runtime systems, like StarPU. StarPU ([9]) is an implementation of the STF for heterogeneous multicore architectures. It means that it can efficiently use CPUs, GPUs, and also FPGAs. We call each process unit, without distinction, a worker.

Moreover, StarPU is an efficient runtime system. It means that more than giving a unified view of a heterogeneous system, it offers different schedulers for mapping and executing tasks onto a heterogeneous machine. Finally, with StarPU, the programmer does not have to deal with low-level problems, such as memory transfers, which are included on StarPU; or the architecture of the machine. For the case of changing the configuration of the machine, for example by only considering a part of the CPUs, StarPU will take it into account and try to execute the program in the most efficient way, without changing any line of code.

Also, using a new GPU or FPGA is really easy: the only requirement is to write the new version of the functions for the new units; without managing the data transfers, initialization, or other low-level details.

Finally, an important thing about StarPU is the scheduling engine. This is im-

portant because the goal of StarPU is to "Make hardware-dependent decisions on behalf of the programmer". For this, there are different policies already programmed; and it is easy to create another policy. These policies came from a theoretical algorithmic corpus.

The first type of policy is the reactive one. The idea is to make work stealing, so attribute to each worker a queue of tasks; and when a worker has ended its queue, it will steal a task from another worker. There are two main policies, the first is **WS** (Work-Stealing), described as above; and the second is **LWS** (Locality Work-Stealing), which is a variant of WS, and the idea is a worker is going to steal tasks from neighbor workers.

The second type of policy is the anticipative one. The idea is to plan where this is the best choice to put a task. To do this, StarPU has performance models. This is a registration of the execution of the task according to the parameters, which is possible because a task in StarPU is not preemptible. Then, when submitting a task, StarPU will predict where the execution will be the best to minimize the execution time. There are several policies of this type. The most common is **DM**. It schedules tasks where their termination time will be minimal. A variant is **DMDA**, which takes also into account the data transfer times; and **DMDAR**; which takes into account the disponibility of buffers on the target worker.

### 1.5 Research Aim

We have seen that there are tools for approximate solutions of PDEs by the Finite Element Method, like FEniCSx. We have also seen that the FEM is divided into two major computation phases, the assembling phase, and the solving phase. The solving phase has been already studied; and there are some answers for parallelizing this phase. For FEniCSx we use the toolbox PETSC; which is already parallel. However, parallelization strategies for the assembling phase have not been studied a lot despite it could be really costly in computational time. The aim of this report is to explore different strategies for parallelizing this phase with the help of the runtime StarPU.

### 1.6 Difficulties and race conditions on the assembly part

Basically, the assembly part is a loop on all the entities of the mesh; and for each entity of the mesh, we have a global matrix in which we "put" the local contribution.

In the original algorithm, called cellwise, the idea is to make a loop on all the cells of the mesh, and then, for each cell, make a loop on all the vertices of the cell (called degrees of freedom).

Then for each degree of freedom, the idea is to do three different phases :

- 1. First, we have to recover the geometry of the cells, to know how and where the degree is going to contribute. We call this phase gather.

- 2. Second, we have to compute the contribution of the degree of freedom. We call this phase compute.

- 3. Finally, we need to add the local contribution to the global matrix. We call this phase scatter.

There are some important points to emphasize. The first point is that the first and the second phases induct no race conditions. It means that they can be performed in parallel without any problem: they only make read accesses on global memory and write only to local memory. The other important thing is each degree of freedom is going to write on a different (unpredictable in the general case) place on the matrix during the scatter phase. Moreover, it is possible for two different degrees of freedom to write at the same place during this phase. It means that there is a race condition in the scatter phase. So, we need to find solutions to make the assembly correct, and this is the most important part of this work. The difficulty is to make the scatter correctly because the other phases are not problematic in comparison.

### 1.7 Research Guidelines

Some ideas have been suggested for leading the project:

1. The atomic solution. The idea is basically to make the addition of the local contribution on the global matrix atomically, and so even if the addition is

more expensive, the operations ensure that they will be correct.

- 2. The buffer solution or "trade memory space for more parallelism". This is another way of working which could be interesting. The idea is to make additions using different matrices and after the end, make the addition of the buffers.

- 3. Using a different algorithm, the rowwise algorithm. Instead of iterating on all the cells and computing the degrees of freedom; the idea is to iterate on all the degrees of freedom, and for each one computing the cells and making the addition only for the part of the cell which has an influence on the degree of freedom. With this, you avoid the race condition because you consider sequentially all the modifiers of each degree of freedom.

- 4. The coloring solution. The idea is to divide the mesh into blocks and color the blocks. It means that two blocks have the same color if they don't have any common degree of freedom, and so they could be performed in parallel.

### 1.8 Dissertation Outline

This dissertation is presented as...

- Chapter 1: short brief of the subject; presentation of the different things to know, of the problem and introduction to the different solutions

- Chapter 2: explanation of the atomic solution, evaluation.

- Chapter 3: explanation of the buffer solution, why this is not a good solution.

- Chapter 4: explanation of the rowwise algorithm, a surprising problem.

- Chapter 5: explanation of the coloring solution.

### 1.9 Experimental environment

In this section, we will describe the environment used for our experiments.

For making experiments, we used two different platforms.

Figure 1.3: Topology of the machines sirocco23 and sirocco24.

The first is PlaFRIM. This is a computing platform used for experiments in Bordeaux. It is composed of several partitions. Each partition has its particularities, in terms of architecture. We have used the sirocco partition; which is composed of accelerated nodes; and the bora partition; which is composed of standard nodes.

On the sirocco partition, we have used the machine sirocco23 and sirocco24; with the same configuration :

- For the CPUs : 2x 32-core AMD Zen3 EPYC 7513 @ 2.60 GHz.

- For the GPUs : 2 NVIDIA A100 (40GB).

- For the memory : 512GB (10.6GB/core) @ 3200 MT/s.

We can see in Figure 1.3 the topology of this corresponding machine.

On the bora partition, we have used different machines; all of them have the same configuration :

- For the CPUs: 2x 18-core Cascade Lake Intel Xeon Skylake Gold 6240 @ 2.6 GHz.

- No GPUs.

- For the memory : 192 GB (5.3 GB/core) @ 2933 MT/s.

We can see in Figure 1.4 the topology of this corresponding machine.

The second platform we used is the Ex3 platform; a computing platform used at Simula (Oslo). There are also several partitions in this platform. The one we

| Machine (191GB total)                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package L#0                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NUMANode L#0 P#0 (95GB)                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| L3 (25MB)<br>L2 (1024KB) L2 (1024KB)<br>L3 (25KB) L1d (32KB)<br>L1d (32KB) L1d (32KB)<br>L1 (32KB) L1 (32KB)<br>L1 (32KB)       | PCI 00:11.5<br>PCI 00:17.0<br>1.0<br>1.0<br>Net em3<br>PCI 10:00.0<br>1.0<br>PCI 01:00.0<br>Net em1<br>PCI 01:00.0<br>PCI 01:00.0 |

| Core L#0         Core L#1         Core L#17           PUL#0         PUL#1         PUL#17           P#2         P#2         P#34 | 1.0         PCI 01:00.1           Net em4         4.0           0.5         0.5           PCI 03:00.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Package L#1                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NUMANode L#1 P#1 (96GB)                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| L3 (25MB)                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| L2 (1024KB) L2 (1024KB)<br>18x total L2 (1024KB)                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| L1d (32KB) L1d (32KB) L1d (32KB)                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| L1i (32KB) L1i (32KB) L1i (32KB)                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Core L#18         Core L#19         Core L#35           PU L#18         P#3         PU L#35         P#35                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |