# A denotational semantics of Simulink with higher-order UTP

Xiong Xu, Bohua Zhan, Shuling Wang, Jean-Pierre Talpin, Naijun Zhan

# ▶ To cite this version:

Xiong Xu, Bohua Zhan, Shuling Wang, Jean-Pierre Talpin, Naijun Zhan. A denotational semantics of Simulink with higher-order UTP. Journal of Logical and Algebraic Methods in Programming, 2023, 130, pp.100809. 10.1016/j.jlamp.2022.100809. hal-03888092

# HAL Id: hal-03888092 https://inria.hal.science/hal-03888092v1

Submitted on 7 Dec 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A denotational semantics of Simulink with higher-order UTP

Xiong Xu<sup>a,c</sup>, Bohua Zhan<sup>a,b</sup>, Shuling Wang<sup>a</sup>, Jean-Pierre Talpin<sup>c</sup>, Naijun Zhan<sup>a,b,\*</sup>

<sup>a</sup>Institute of Software, Chinese Academy of Sciences, Beijing, China <sup>b</sup>University of Chinese Academy of Sciences, Beijing, China <sup>c</sup>Inria, Rennes, France

## Abstract

Matlab/Simulink is a de-facto industrial standard for modelling embedded systems. Reflecting the complexity of cyber-physical system (CPS) design, the semantics of Simulink is complex, mixing discrete and continuous time and events. In this paper, we define a compositional semantics of hierarchical Simulink diagrams using Higher-order Unifying Theories of Programming (HUTP) for CPS design. The HUTP theory satisfies the suitable algebraic properties to serve as a mathematical foundation for expressing the semantics of CPSs, in particular Simulink diagrams. We characterise a class of well-formed Simulink diagrams and prove the determinacy of their HUTP semantics. Moreover, we construct a framework for proving the consistency between Simulink diagrams and their translation to HCSP (Hybrid Communicating Sequential Processes). Finally, we provide a case study to illustrate and justify this translation.

*Keywords:* model-based design, cyber-physical systems, unifying theory of programming, denotational semantics, Mathworks Simulink

# 1. Introduction

Cyber-Physical Systems (CPSs) are networked computing units controlling physical plants as diverse as grids, factories, supply chains, ground, sea, air and space transportation systems. CPSs are complex to design, verify and maintain, while often entrusted safety-critical roles. The efficient and verified development of safe and reliable CPSs is hence a priority mandated by many

<sup>\*</sup>Corresponding author

Email address: znj@ios.ac.cn (Naijun Zhan)

standards, yet a notoriously difficult and challenging field of engineering and research. Matlab/Simulink is a de-facto industrial standard for modelling cyber-physical systems. Reflecting the complexity of CPS design, Simulink is known to have a complex semantics, which need to describe interactions between discrete and continuous time behaviors, trigger events, hierarchical structure, and so on.

Model-based design (MBD) (Gajski et al., 2009) has long become a predominant approach to break down the difficulties and challenges in CPS design into abstracted and comprehensible elements. Hoare and He's Unifying Theories of Programming (UTP) (Hoare and He, 1998) is built upon the mathematical foundations of theorem proving and has both the core simplicity and the necessary extensibility to capture models of imperative and concurrent software, hardware, and physics found in CPS design under a common relational calculus suitable for design and verification.

Hybrid systems, which could be subsumed in the domain of CPSs, seamlessly integrate discrete behavior with continuous dynamical systems, and have been extended to capture probabilistic, stochastic, time-delayed behaviours and even more complex features. In previous works (Xu et al., 2022a), we defined one such conservative extension to Hoare and He's UTP theory with higher-order quantification, i.e., the Higher-order UTP (HUTP), to provide a formal semantics for modelling and verifying hybrid systems, mixing discrete real-time processes and continuous dynamics. Within HUTP, we defined a calculus of *normal hybrid designs* to model and analyse hybrid systems. A normal hybrid design describes a contract between the component and its environment, and therefore supports the decomposition of engineering tasks to resolve system design complexity. Normal hybrid designs as a firstclass notion in the HUTP theory enjoys some desired algebraic properties, and therefore can serve as a semantic foundation for CPS design.

In (Zou et al., 2013b, 2015), we introduced methods for translation of Simulink and Stateflow diagrams to Hybrid Communicating Sequential Processes (HCSP), in order to verify them using the Hybrid Hoare Logic prover implemented in Isabelle/HOL (Zou et al., 2013a; Wang et al., 2015). The correctness of the translation can be proved using HUTP. Concretely, we define the respective HUTP semantics for Simulink and HCSP, and then compare the HUTP representations of Simulink diagrams and their HCSP models to check the semantic consistency. In (Xu et al., 2022a), we defined a formal semantics for Simulink based on normal hybrid designs. However, the normal-hybrid-design semantics is complex, which pose difficulties for ensuing analysis and verification. The complexity comes from (1) involvement of a large number of communications (including the communications between atomic discrete blocks), and (2) the use of normal hybrid design, although intuitive for system design, makes the definitions long and cumbersome. Moreover, compositional semantics for hierarchical Simulink subsystems is not considered.

Therefore, we introduce in this paper a new compositional formalisation of denotational semantics for hierarchical Simulink diagrams based on HUTP, featuring both discrete and continuous behaviours, as well as composition using normal, enabled and triggered subsystems. The expressivity of the present denotational semantics is well-suited for verifying correctness of translation from Simulink to other formalisms, such as HCSP (Zou et al., 2013b), differential dynamic logic (Liebrenz et al., 2018) and hybrid automata (Agrawal et al., 2004). We exercise this capability by constructing a framework for proving the semantic consistency between Simulink diagrams and their corresponding HCSP models, and provide a case study to demonstrate and justify our translation of Simulink into HCSP.

In summary, the main contributions of this paper comprise:

- A notion of Simulink processes and their parallel composition based on conjunction of relations, which simplifies the HUTP theory for Simulink;

- A denotational semantics for hierarchical Simulink diagrams based on Simulink processes, reflecting the composability of subsystems and therefore following the principle of modular design;

- Notions of well-formedness of Simulink diagrams, and proof of semantic determinacy for these diagrams;

- A framework for proving correctness of translation from Simulink to HCSP, which is illustrated with a simple case study.

Paper Organisation. The rest of the paper is organised as follows. Section 2 retrospects some preliminary concepts of Simulink, UTP and Higher-order UTP. Section 3 defines the notion of Simulink processes which serve as the semantic foundation for Simulink. Starting from Simulink blocks, Section 4 defines the HUTP semantics for Simulink diagrams by Simulink processes, and proves determinacy of the semantics for well-formed diagrams. Section 5 defines the compositional HUTP semantics for hierarchical Simulink diagrams containing normal, triggered and enabled subsystems. In Section 6, we illustrate by a case study how to prove the semantic consistency between Simulink diagrams and the corresponding HCSP models. Section 7 addresses the related work and Section 8 concludes this paper and discusses future work.

# 2. Preliminaries

In this section, we will present the preliminaries on Simulink, classical UTP, and our previous work on the higher-order UTP for hybrid systems.

#### 2.1. Simulink

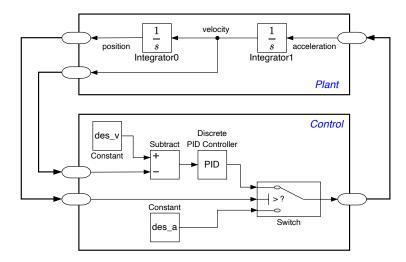

Simulink (MathWorks, 2013) is a widely-used design environment for building embedded control systems, with support for graphical modelling and efficient numerical simulation. Dynamic systems, possibly combining continuous and discrete behaviors, can be modelled by Simulink block diagrams. A rich set of fixed-step and variable-step solvers is provided for simulating dynamic systems. Fig. 1 shows how a simple plant-control system can be modelled in Simulink.

Fig. 1: A Simulink diagram of a plant-control model

Blocks are the basic units for building Simulink models. Each block is defined with input and output ports, an output method that defines how the output values are calculated, optional internal states and corresponding update methods that define how the states are changed. It may also contain user-defined parameters that alter the functionality, such as the symbol parameter "+-" for Add block, resulting in Subtract; the parameter of threshold for Switch block, and so on. Sample time is one of the most important parameters of a block and specifies the rate of execution when the block executes the output method and the update method (if it exists). Among the different types of sample time, three basic ones are frequently used: discrete with sample time st for some st > 0, continuous with sample time 0, and inherited. For the inherited case, the sample time is not defined explicitly,

but instead determined from the context of the corresponding block through a process called sample time propagation. For instance, if the sample times of all the input signals of an inherited block are known, then sample time of the block is computed as the greatest common divisor of the sample times of these input signals. According to sample time, blocks can be categorised into two kinds: discrete and continuous blocks. Simulink provides discrete and continuous solvers to compute the states of blocks at each time step respectively.

Blocks are connected using lines to transfer signals from one block to another. The signals are time-varying and can be considered as functions mapping from real time to values. For discrete blocks the functions are piecewise constant. Blocks in a diagram may have different sample times, e.g. a multi-rate discrete system with discrete blocks that sample at different rates, or a hybrid continuous and discrete system. For such diagrams, the simulator must meet the precision specified on the continuous states, and hit all the sample times for the discrete states. The simulator needs to sort (or schedule) the blocks to be executed in a certain order. This may not be possible if there are *algebraic loops* in the diagram, in which case the diagram may be considered to be invalid. The blocks which maintain state variables such as the **Integrator** or **Unit Delay** blocks can break the loop.

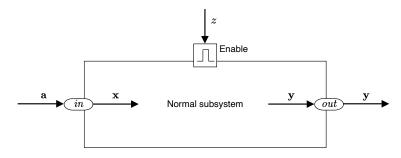

Blocks can be grouped into subsystems to establish a hierarchical structure on Simulink diagrams. We consider three types of subsystems: normal subsystems, triggered subsystems and enabled subsystems. A normal subsystem executes as a single unit within the model. It can specify its system sample time and its execution is equivalent to executing the blocks inside the subsystem. Both triggered and enabled subsystems are conditionally executed subsystems. A triggered subsystem is defined with inherited sample time, that runs when the trigger signal is rising, falling, or either (rising or falling) through a zero value. An enabled subsystem runs when its control signal is positive.

A hierarchical Simulink model is thus composed of blocks, subsystems, and lines between them. After a Simulink model is built, it is ready for simulation. Each step of simulation corresponds to one sample time of the overall diagram. At each step, first compute the internal state and output of each block by invoking the corresponding output and update methods in the correct order; second, choose appropriate ODE solvers to compute evolution of continuous blocks through time. If there are triggered subsystems or integrator blocks with resets, zero crossings may need to be computed. The process ends when the given simulation time is reached.

#### 2.2. Unifying Theories of Programming

Hoare and He's Unifying Theories of Programming (UTP) (Hoare and He, 1998) is an alphabetised refinement calculus unifying heterogeneous programming paradigms. An alphabetised relation consists of an alphabet  $\alpha(P)$ , containing its variables x and primes x', and a relational predicate P referring to this vocabulary. The terms x and x' are called observable variables: x is observable at the start of execution and x' is observable at the end of execution. The behaviour of a program is encoded as a relation between the observable variables x and x'. In particular, assignment, sequential composition, conditional statement, non-deterministic choice, and recursion of imperative programs can be specified as alphabetised relations below, where x and x' are sequences or vectors of variables,  $x \setminus \{x\}$  ( $x' \setminus \{x'\}$ ) denotes excluding x (x') from x (x'). To start with, the relational calculus comprises all operators of first-order logic.

$$\begin{aligned} x &:= e \quad \widehat{=} \quad x' = e \land \mathbf{x}' \backslash \{x'\} = \mathbf{x} \backslash \{x\} \\ P \stackrel{\circ}{\circ} Q \quad \widehat{=} \quad \exists \mathbf{x}_* \cdot P[\mathbf{x}_*/\mathbf{x}'] \land Q[\mathbf{x}_*/\mathbf{x}] \\ P \lhd b \rhd Q \quad \widehat{=} \quad (b \land P) \lor (\neg b \land Q) \\ P \sqcap Q \quad \widehat{=} \quad P \lor Q \\ P \sqcup Q \quad \widehat{=} \quad P \land Q \end{aligned}$$

Conventionally,  $\sqcap$  is an algebraic sibling for  $\land$  and  $\sqcup$  for  $\lor$ . In the equal tradition of UTP (Hoare and He, 1998; Xu et al., 2022a), however, they denote  $\lor$  and  $\land$ , respectively. We will follow UTP's convention in this paper.

Assignment x := e is defined by observing the update x' of variable x once its value e is evaluated, leaving other variables in the alphabet x unchanged. Sequence  $P \$  Q is modelled by locally binding, through  $x_*$ , the final state x' of P and the initial state x of Q, both of which are instantiated to  $x_*$ . Note that  $\$ requires  $\alpha_{out}(P) = \alpha'_{in}(Q)$ , where  $\alpha_{out}(P)$  and  $\alpha_{in}(Q)$  denote the sets of output and input variables in  $\alpha(P)$  and  $\alpha(Q)$ , respectively, and  $\alpha'_{in}(Q)$  is the primed version by priming all the variables in  $\alpha_{in}(Q)$ . The conditional  $P \lhd b \triangleright Q$  evaluates as P if b is true and as Q otherwise.  $P \sqcap Q$ non-deterministically chooses P or Q, and  $P \sqcup Q$  is a conjunction of P and Q.

Let P and Q be two predicates with the same alphabet, say  $\{x, x'\}$ . Then, Q is a *refinement* of P, denoted  $P \sqsubseteq Q$ , if  $\forall x, x' \cdot Q \Rightarrow P$ . In addition,  $P \sqsubseteq Q$  iff  $P \sqcap Q = P$  iff  $P \sqcup Q = Q$ . With respect to the refinement order  $\sqsubseteq$ , the least  $(\mu)$  and greatest  $(\nu)$  fixed points of a function F between programs can be defined as follows:

$$\mu F \stackrel{\cong}{=} \prod \{ X \mid F(X) \sqsubseteq X \}$$

$$\nu F \stackrel{\cong}{=} \bigsqcup \{ X \mid X \sqsubseteq F(X) \}$$

The notion of healthings conditions plays an important role in the UTP theory. If a predicate satisfies  $P = \mathcal{H}(P)$ , then it is said to be  $\mathcal{H}$ -healthy. In other words, a healthiness condition  $\mathcal{H}$  defines an invariant predicate set  $\{X \mid \mathcal{H}(X) = X\}$ , and is required to be idempotent  $(\mathcal{H} \circ \mathcal{H} = \mathcal{H})$ , which means that taking the medicine twice leaves you as healthy as taking it once (no overdoses). So, in UTP, the healthy predicates of a theory are the fixed points of idempotent functions. When  $\mathcal{H}$  is monotonic on a complete lattice  $(\mathbb{C}, \sqsubseteq)$ , then according to the Knaster-Tarski theorem (Tarski, 1955), the UTP theory satisfying  $\mathcal{H}$  forms a complete lattice  $\{X \in \mathbb{C} \mid \mathcal{H}(X) = X\}$ . Additionally, recursion can be well defined. Distinct healthiness conditions can be composed to capture the characteristics of different programming paradigms. Concretely, a programming paradigm can be defined by a collection of healthiness conditions  $\mathcal{H}_1, \mathcal{H}_2, \dots, \mathcal{H}_n$ . Their composition  $\mathcal{H}_1 \circ \mathcal{H}_2 \circ \cdots \circ \mathcal{H}_n$  forms the semantic model of the domain-specific paradigm under consideration. For example, in Section 3.1, we introduce healthiness conditions characterising Simulink processes.

## 2.3. The higher-order UTP for hybrid systems

Higher-order UTP (HUTP) (Xu et al., 2022a) is a conservative extension to Hoare and He's UTP theory which supports the specification of discrete, real-time and continuous dynamics, concurrency and communication, and higher-order quantification. In (Xu et al., 2022a), we defined a formal semantics for Simulink based on a notion of normal hybrid designs. However, this semantics is complex and difficult to analyse for reasons given in Section 1. In this paper, we instead consider an abstracted HUTP semantics for Simulink, based on the notion of *abstract hybrid processes* proposed in (Xu et al., 2022a) as future work. While having weaker algebraic structure than normal hybrid designs (e.g., chaos is not a left zero of sequential composition), abstract hybrid processes are simpler, of sufficient expressivity to define a semantics of Simulink, and are more comfortable for verification.

#### 2.3.1. Abstract hybrid processes

As mentioned in (Xu et al., 2022a), HUTP separates the concerns in hybrid system design into time, state and trace. We introduce the notion of time by two observational variables  $ti, ti' : \mathbb{R}_{\geq 0} \cup \{+\infty\}$  to specify the startand end-time of the observed behaviour. The notion of state is represented by real-time variables and their derivatives, which are functions over time, and differential relations over them that are very powerful to express all kinds of continuous dynamics. Therefore, there are three versions for each state variable v:

- $v \in \mathbb{D}$  stands for its initial value in the domain  $\mathbb{D}$ , where  $\mathbb{D}$  could be a Banach space;

- the primed version  $v' \in \mathbb{D}$  stands for the final value, i.e., the output state variable; and

- the real time version  $\underline{v} : [ti, ti') \to \mathbb{D}$  stands for its dynamic trajectory from the start time ti to the end time ti', and  $\underline{v} : (ti, ti') \to \mathbb{D}$  is a partial function denoting the derivative of  $\underline{v}$ .

Timed traces tr and tr' record the execution history and capture communication behaviours, where tr represents the timed trace before the process is started and tr' stands for timed trace up to the moment of observation. However, in this paper, no communication is involved and the parallel composition is based on shared variables, so timed traces are abstracted away, which is the main feature of abstract hybrid processes.

We use the boldface symbols  $\boldsymbol{v}, \boldsymbol{v}', \boldsymbol{v}$  and  $\boldsymbol{\dot{v}}$  to denote respective vectors of input, output, real-time state variables and their derivatives. The alphabet our theory depends on is  $\{ti, ti', \boldsymbol{v}, \boldsymbol{v}, \boldsymbol{\dot{v}}, \boldsymbol{v}'\}$  by default. Therefore, first-order predicate  $P(\boldsymbol{x}, \boldsymbol{x}')$  used in classical UTP (Hoare and He, 1998) can be extended to higher-order differential relation  $\mathcal{P}(ti, ti', \boldsymbol{v}, \boldsymbol{v}, \boldsymbol{\dot{v}}, \boldsymbol{v}')$ . However, not all higher-order differential relations are expected, such as ti > ti' indicating time going backwards. Thus, we use *healthiness conditions* to exclude the ill behaviours. As introduced in (Xu et al., 2022a), the features of abstract hybrid processes can be captured by the following four healthiness conditions  $(\mathcal{H}_1$  is defined for traces, hence not applicable for abstract hybrid processes):

• Time must be irreversible:

$$\mathcal{H}_{0}^{\mathrm{A}}(X) = X \wedge ti \leq ti'$$

• If the preceding process does not terminate, i.e.,  $ti = +\infty$ , the current process should do nothing but keep the time observation unchanged, i.e.,

$$\mathcal{H}_{2}^{A}(X) = (ti = ti') \triangleleft ti = +\infty \triangleright X$$

where  $P \lhd b \rhd Q \cong (b \land P) \lor (\neg b \land Q)$ .

If the current process does not terminate, i.e., ti' = +∞, the values of the output state variables are unobservable, i.e.,

$$\mathcal{H}_{3}^{\mathrm{A}}(X) = (\exists \boldsymbol{v}' \cdot X) \triangleleft ti' = +\infty \triangleright X$$

• If the process evolves for a period of time, i.e., ti < ti', the real-time value  $\boldsymbol{v}$  should stay right-continuous (RC) and semi-differentiable (SD). Let  $\boldsymbol{v}_k, \boldsymbol{v}_k$ , and  $\boldsymbol{v}'_k$  denote the k-th variable in  $\boldsymbol{v}, \boldsymbol{v}_k$ , and  $\boldsymbol{v}'_k$ , respectively. Then, we define

$$\begin{aligned} RC & \stackrel{\widehat{=}}{=} \quad \forall k \cdot \forall t \in [ti, ti') \cdot \exists d \cdot \boldsymbol{v}_k(t) = \lim_{\delta \to 0^+} \boldsymbol{v}_k(t+\delta) = d \\ SD & \stackrel{\widehat{=}}{=} \quad \forall k \cdot \forall t \in (ti, ti') \cdot \exists d_0 \cdot \lim_{\delta \to 0^+} (\boldsymbol{v}_k(t+\delta) - \boldsymbol{v}_k(t)) \, / \delta = d_0 \\ & \wedge \exists d_1 \cdot \lim_{\delta \to 0^-} (\boldsymbol{v}_k(t+\delta) - \boldsymbol{v}_k(t)) \, / \delta = d_1 \end{aligned}$$

The healthiness condition

$$\mathcal{H}_4(X) = X \wedge RC \wedge SD$$

rules out some ill behaviours, such as the Dirichlet function (returning 1 if t is a rational number and 0 otherwise) and the Weierstrass function (continuous everywhere but differentiable nowhere).

**Remark 1.** Note that  $\mathcal{H}_3^A$  does not mean that the values of  $\boldsymbol{v}$  exist at infinity. The existential quantifier just indicates that the output  $\boldsymbol{v}'$  can take arbitrary values, i.e., chaos. In addition, the output of a process exhibiting Zenobehaviour should also be unobservable (chaos). However, it cannot be captured by abstract hybrid processes as the trace information is abstracted away.

An abstract hybrid process is a fixed point of  $X = \mathcal{H}_{HP}^{A}(X)$ , where

$$\mathcal{H}^{\mathrm{A}}_{\mathrm{HP}} \;\; \widehat{=} \;\; \mathcal{H}^{\mathrm{A}}_{0} \circ \mathcal{H}^{\mathrm{A}}_{2} \circ \mathcal{H}^{\mathrm{A}}_{3} \circ \mathcal{H}_{4}$$

It is proved in (Xu et al., 2022a) that  $\mathcal{H}^{A}_{HP}$  is idempotent and monotonic, which indicates that abstract hybrid processes form a complete lattice under the refinement order  $\sqsubseteq$ .

#### 3. Simulink processes in HUTP

Based on abstract hybrid processes, we propose a new notion of Simulink processes which can serve as the semantic foundation for Simulink. We further define parallel composition of Simulink processes as conjunction of relations. Finally, we define some syntactic sugar to simplify the ensuing presentations.

#### 3.1. Simulink processes

The semantics of Simulink can be represented by a subset of abstract hybrid processes subject to additional healthiness conditions. First, we assume that the execution of Simulink diagrams will consume time (ti < ti').

This corresponds to the requirement that simulation will last for non-zero amount of time. Moreover, we require that simulations will always terminate  $(ti' < +\infty)$ . These two properties can be captured by the following healthiness condition:

$$\mathcal{H}_{\text{SIM}}(X) = X \wedge ti < ti' < +\infty$$

It can be proved that  $\mathcal{H}_{\text{SIM}}$  is idempotent and monotonic, which indicates that

$$\mathcal{H}^{\mathrm{A}}_{\mathrm{\scriptscriptstyle SIM}} \;\; \widehat{=} \;\; \mathcal{H}_{\mathrm{\scriptscriptstyle SIM}} \circ \mathcal{H}^{\mathrm{A}}_{\mathrm{\scriptscriptstyle HP}}$$

also forms a complete lattice under the refinement order. We call the  $\mathcal{H}_{\text{SIM}}^{\text{A}}$  healthy relations *Simulink processes*, and we prove the following property, which reveals that  $\mathcal{H}_{0}^{\text{A}}$ ,  $\mathcal{H}_{2}^{\text{A}}$  and  $\mathcal{H}_{3}^{\text{A}}$  are redundant and therefore simplifies the representation of Simulink processes.

# Property 2. $\mathcal{H}_{\text{SIM}}^{\text{A}} \equiv \mathcal{H}_{\text{SIM}} \circ \mathcal{H}_{4}$

*Proof.* It can be checked that  $\mathcal{H}_{\text{SIM}} \circ \mathcal{H}_0^{\text{A}}(X) = \mathcal{H}_{\text{SIM}} \circ \mathcal{H}_2^{\text{A}}(X) = \mathcal{H}_{\text{SIM}} \circ \mathcal{H}_3^{\text{A}}(X) = \mathcal{H}_{\text{SIM}}(X).$

We next describe the meet  $(\Box, \lor)$ , join  $(\sqcup, \land)$  and sequential composition ( $\mathfrak{s}$ ) operations on Simulink processes. They are specializations of corresponding operations for general hybrid processes defined in (Xu et al., 2022a). The sequential composition of two Simulink processes P and Q is defined as follows:

$$\mathsf{P} \, \mathring{} \, \mathsf{Q} \ \widehat{=} \ \exists ti_0, \boldsymbol{v}_0 \cdot \mathsf{P}[ti_0, \boldsymbol{v}_0/ti', \boldsymbol{v}'] \land \mathsf{Q}[ti_0, \boldsymbol{v}_0/ti, \boldsymbol{v}]$$

provided that  $\alpha_{out}(\mathsf{P}) = \alpha'_{in}(\mathsf{Q})$ , where  $\alpha_{out}(\mathsf{P})$  and  $\alpha_{in}(\mathsf{Q})$  denote the sets of output and input variables in the respective alphabets of  $\mathsf{P}$  and  $\mathsf{Q}$ , and  $\alpha'_{in}(\mathsf{Q})$  is the primed version by priming all the variables in  $\alpha_{in}(\mathsf{Q})$ . If  $\alpha_{out}(\mathsf{P}) \neq \alpha'_{in}(\mathsf{Q})$ , then we can extend the alphabets by

$$\alpha_{out}^{+}(\mathsf{P}) = \alpha_{in}^{+\prime}(\mathsf{Q}) \cong \alpha_{out}(\mathsf{P}) \cup \alpha_{in}^{\prime}(\mathsf{Q})$$

to ensure the well-definedness of  $\$ . The meet and join operations simply correspond to union and intersection of relations. We then prove  $\$ ,  $\lor$  and  $\land$  are  $\mathcal{H}^{A}_{SIM}$ -preserving, and the proofs for other operations on Simulink processes are similar.

**Property 3.** If  $\mathsf{P}$  and  $\mathsf{Q}$  are  $\mathcal{H}^{\mathsf{A}}_{\mathsf{SIM}}$ -healthy, so are  $\mathsf{P} \, \operatorname{\stackrel{\circ}{\scriptscriptstyle S}} \mathsf{Q}$ ,  $\mathsf{P} \lor \mathsf{Q}$ , and  $\mathsf{P} \land \mathsf{Q}$ .

*Proof.* By the definition of  $\mathcal{H}_{\text{SIM}}^{\text{A}}$ ,

$$\begin{split} \mathsf{P} \, \mathring{}_{9} \, \mathsf{Q} &= 0 < ti < ti' < +\infty \land \mathsf{P} \land RC(\underline{v}, ti, ti') \land SD(\underline{v}, ti, ti') \, \mathring{}_{9} \\ &\quad 0 < ti < ti' < +\infty \land \mathsf{Q} \land RC(\underline{v}, ti, ti') \land SD(\underline{v}, ti, ti') \, \mathring{}_{9} \\ &= \exists ti_{0}, \boldsymbol{v}_{0} \cdot 0 < ti < ti_{0} < +\infty \land 0 < ti_{0} < ti' < +\infty \\ &\quad \land \mathsf{P}[ti_{0}, \boldsymbol{v}_{0}/ti', \boldsymbol{v}'] \land \mathsf{Q}[ti_{0}, \boldsymbol{v}_{0}/ti, \boldsymbol{v}] \\ &\quad \land RC(\underline{v}, ti, ti_{0}) \land RC(\underline{v}, ti_{0}, ti') \land SD(\underline{v}, ti, ti_{0}) \land SD(\underline{v}, ti_{0}, ti') \\ &= \exists ti_{0}, \boldsymbol{v}_{0} \cdot 0 < ti < ti_{0} < ti' < +\infty \\ &\quad \land \mathsf{P}[ti_{0}, \boldsymbol{v}_{0}/ti', \boldsymbol{v}'] \land \mathsf{Q}[ti_{0}, \boldsymbol{v}_{0}/ti, \boldsymbol{v}] \\ &\quad \land \mathsf{RC}(\boldsymbol{v}, ti, ti') \land SD(\boldsymbol{v}, ti, ti') \end{split}$$

where RC and SD denote  $\underline{v}$  is right continuous and semi-differentiable as specified in healthiness condition  $\mathcal{H}_4$ . We can also prove

$$\begin{array}{lll} \mathsf{P} \lor \mathsf{Q} &=& 0 < ti < ti' < +\infty \land \mathsf{P} \land RC(\underline{v}, ti, ti') \land SD(\underline{v}, ti, ti') \lor \\ & 0 < ti < ti' < +\infty \land \mathsf{Q} \land RC(\underline{v}, ti, ti') \land SD(\underline{v}, ti, ti') \\ &=& 0 < ti < ti' < +\infty \land (\mathsf{P} \lor \mathsf{Q}) \land RC(\underline{v}, ti, ti') \land SD(\underline{v}, ti, ti') \\ \mathsf{P} \land \mathsf{Q} &=& 0 < ti < ti' < +\infty \land \mathsf{P} \land RC(\underline{v}, ti, ti') \land SD(\underline{v}, ti, ti') \land \\ & 0 < ti < ti' < +\infty \land \mathsf{Q} \land RC(\underline{v}, ti, ti') \land SD(\underline{v}, ti, ti') \land \\ & 0 < ti < ti' < +\infty \land \mathsf{Q} \land RC(\underline{v}, ti, ti') \land SD(\underline{v}, ti, ti') \\ &=& 0 < ti < ti' < +\infty \land (\mathsf{P} \land \mathsf{Q}) \land RC(\underline{v}, ti, ti') \land SD(\underline{v}, ti, ti') \end{array}$$

According to the above results, we can prove that P; Q,  $P \lor Q$  and  $P \land Q$  are  $\mathcal{H}^A_{SIM}$ -healthy.

# 3.2. Parallel composition

Of all the operations, parallel composition is the most important. In (Xu et al., 2022a), we assume that the state variables of different processes are disjoint. Based on this assumption, a parallel-by-merge scheme is given. In this paper, we relax this assumption: state variables can be shared among processes. Intuitively, the combination is well-behaved because although variables are shared, the value of each variable is controlled by at most one process and only read by others. Hence, under some additional assumptions, we can prove that there exists unique assignment to all variables given the values of input variables to the overall process.

Therefore, the parallel-by-merge scheme (Fig. 1 of (Xu et al., 2022a)) can be revisited to represent the parallel composition by shared state variables in this paper. The parallel-by-merge, originated from (Hoare and He, 1998), is a typical scheme to define parallel composition in UTP (Xu et al., 2022a; Foster et al., 2020). Intuitively, parallel processes first execute independently and their respective outputs are fed into the merge predicate M. Then, Mproduces the merged result as the output of the parallel composition. Each merge predicate reflects a parallel scheme, therefore the parallel composition is parametric over M, which is indicated by the notation  $\|_M$ . Concretely, let  $\mathsf{P}$  and  $\mathsf{Q}$  be the parallel processes with respective state variables  $v_0$  and  $v_1$  (which are not necessarily disjoint), then

$$\mathsf{P}\|_{M}\mathsf{Q} \quad \widehat{=} \quad \mathcal{H}^{\mathsf{A}}_{\mathrm{SIM}}\left(\left(\mathsf{P}_{X} \land \mathsf{Q}_{Y}\right) \overset{\circ}{,} M\right)$$

where  $\mathsf{P}_X(\mathsf{Q}_Y)$  makes an X(Y)-version of  $\mathsf{P}(\mathsf{Q})$  by adding the time variable ti' in  $\mathsf{P}(\mathsf{Q})$  with the X(Y)-subscript, i.e.,

$$\begin{array}{rcl} \mathsf{P}_X & \widehat{=} & \mathsf{P} \, \widehat{\scriptscriptstyle 9} \, (ti = ti'_X \wedge \boldsymbol{v}_0 = \boldsymbol{v}'_0) & = & \mathsf{P}[ti'_X/ti'] \\ \mathsf{Q}_Y & \widehat{=} & \mathsf{Q} \, \widehat{\scriptscriptstyle 9} \, (ti = ti'_Y \wedge \boldsymbol{v}_1 = \boldsymbol{v}'_1) & = & \mathsf{Q}[ti'_Y/ti'] \end{array}$$

**Remark 4.** Note that the  $\mathcal{H}_{SIM}^A$ -healthiness of parallel composition  $\mathsf{P}||_M \mathsf{Q}$  is enforced. Otherwise,  $\mathcal{H}_{SIM}^A$ -healthiness could be violated, because the merge predicate M can be arbitrary. We could investigate well-defined merge predicates that guarantee  $\mathcal{H}_{SIM}^A$ -healthiness by definition (just as the merge predicate SIM, which does), but it is not the concern in this paper.

For Simulink, we define a new merge predicate:

$$\mathsf{SIM} \quad \widehat{=} \quad ti_X = ti_Y = ti' \land \boldsymbol{v}_0' = \boldsymbol{v}_0 \land \boldsymbol{v}_1' = \boldsymbol{v}_1$$

It states that the parallel processes are synchronous on time  $(ti_X = ti_Y)$ , i.e., their termination time should be identical  $(+\infty \text{ for non-termination})$ ; and the output values of the shared state variables  $v_0 \cap v_1$  should keep consistent. We denote the parallel operator defined by SIM as  $\|_{\text{SIM}}$ . For brevity, in the remainder, we write  $\|$  for  $\|_{\text{SIM}}$  unless otherwise stated. The following property states that  $\|$  is equivalent to conjunction.

**Property 5.**  $P \parallel Q \equiv P \land Q$  if P and Q are Simulink processes.

*Proof.* According to the definition,  $\mathsf{P} \| \mathsf{Q} = \mathcal{H}^{\mathsf{A}}_{\mathsf{SIM}}((\mathsf{P}_X \wedge \mathsf{Q}_Y) \, \operatorname{\mathsf{s}SIM})$ , where

$$(\mathsf{P}_X \land \mathsf{Q}_Y) \, \mathring{\mathsf{S}} \, \mathsf{SIM} = (\mathsf{P}[ti'_X/ti'] \land \mathsf{Q}[ti'_Y/ti']) \mathring{\mathsf{s}} \\ (ti_X = ti_Y = ti' \land \mathbf{v}_0' = \mathbf{v}_0 \land \mathbf{v}_1' = \mathbf{v}_1) \\ = \exists ti^*_X, ti^*_Y, \mathbf{v}_0^*, \mathbf{v}_1^* \cdot \mathsf{P}[ti^*_X, \mathbf{v}_0^*/ti', \mathbf{v}_0'] \land \mathsf{Q}[ti^*_Y, \mathbf{v}_1^*/ti', \mathbf{v}_1'] \\ \land (ti^*_X = ti^*_Y = ti' \land \mathbf{v}_0' = \mathbf{v}_0^* \land \mathbf{v}_1' = \mathbf{v}_1^*) \\ = \mathsf{P} \land \mathsf{Q}$$

Since P and Q are  $\mathcal{H}_{SIM}^{A}$ -healthy,  $P \wedge Q$  is also  $\mathcal{H}_{SIM}^{A}$ -healthy (Property 3). Then, we can get

$$\mathsf{P} \| \mathsf{Q} = \mathcal{H}^{\mathsf{A}}_{\mathrm{SIM}} \left( (\mathsf{P}_X \land \mathsf{Q}_Y) \, \mathring{,} \, \mathsf{SIM} \right) = \mathcal{H}^{\mathsf{A}}_{\mathrm{SIM}} (\mathsf{P} \land \mathsf{Q}) = \mathsf{P} \land \mathsf{Q}$$

The property is proved.

Although parallel composition is equivalent to conjunction in essence, we distinguish the two concepts in this paper. Concretely, parallel composition between blocks in a Simulink diagram or within a subsystem is called *conjunction*; while parallel composition between subsystems is called *parallel composition*. Consider the Simulink diagram in Fig. 1, where each block can be translated to a Simulink process. The semantics of subsystem Plant can be defined by the conjunction Integrator $0 \wedge$ Integrator1, while the semantics of the whole diagram can be defined by the parallel composition Plant ||Control, which is logically equivalent to Plant  $\wedge$  Control.

## 3.3. Syntactic sugar

For brevity in the ensuing presentation, we introduce some syntactic sugar for the HUTP representation of Simulink semantics. Notice that the following notations are different from the definitions in (Xu et al., 2022a). Let  $\underline{P}$  denote a predicate relating  $\underline{v}$  and  $\underline{\dot{v}}$ , then

$$\begin{bmatrix} \underline{P} \end{bmatrix} \widehat{=} \mathcal{H}_{\text{SIM}}^{\text{A}} \left( \forall t \in (ti, ti') \cdot \underline{P}(\underline{v}(t), \underline{\dot{v}}(t)) \right)$$

is a continuous process reflecting the flow of  $\underline{v}$  over the time interval (ti, ti') for ti < ti', and it states that  $\underline{P}$  holds at every instant t from ti to ti'. Note that although the input and output state variables v and v' do not appear in  $\lceil \underline{P} \rceil$ , they are in the alphabet of  $\lceil \underline{P} \rceil$ , or in other words, v and v' can take arbitrary values. We can also bind v and v' to the initial and final values of  $\underline{v}$ , respectively, resulting in the following definitions:

$$\begin{array}{lll} \begin{bmatrix} P \\ P \end{bmatrix} & \widehat{=} & \boldsymbol{v} = \boldsymbol{v}(ti) \land \begin{bmatrix} P \\ P \end{bmatrix} \\ \begin{bmatrix} P \\ P \end{bmatrix} & \widehat{=} & \begin{bmatrix} P \\ P \end{bmatrix} \land \boldsymbol{v}' = \boldsymbol{v}(ti'^{-}) \\ \begin{bmatrix} P \\ P \end{bmatrix} & \widehat{=} & \boldsymbol{v} = \boldsymbol{v}(ti) \land \begin{bmatrix} P \\ P \end{bmatrix} \land \boldsymbol{v}' = \boldsymbol{v}(ti'^{-}) \end{array}$$

Especially, we define

Idle

$$\widehat{=}$$

$[\![ec{v}=0]\!]$

Besides, we add subscripts to the above definitions to constrain the duration. For example,

$$\begin{split} \| \tilde{P} \|_d & \stackrel{\cong}{=} & \| \tilde{P} \| \wedge ti' - ti = d \\ \| \tilde{P} \|_{\leq d} & \stackrel{\cong}{=} & \| \tilde{P} \| \wedge ti' - ti \leq d \\ \end{split}$$

Note that the above continuous processes are all Simulink processes as they are  $\mathcal{H}^{A}_{SIM}$ -healthy.

A causal sequence of operations or events which is assumed to take no time is called super-dense computation (Manna and Pnueli, 1993). Under superdense computation, rendering the time to compute the discrete operations is negligible. However, the causal order of computations is still significant. Under the assumption of super-dense computation, a discrete process is defined by

$$[P] \quad \widehat{=} \quad ti = ti' < +\infty \land P$$

where P denotes a predicate relating  $\boldsymbol{v}$  and  $\boldsymbol{v}'$ . It executes instantly at time ti = ti', rather than continuously over a time interval. Note that [P] is not a Simulink process as its duration is 0. This would violate the healthiness condition  $\mathcal{H}_{\text{SIM}}$ . However, the sequential composition of [P] and a Simulink process is usually  $\mathcal{H}^{\text{A}}_{\text{SIM}}$ -healthy, as demonstrated in the later content. We define

Skip

$$\hat{=}$$

$ti = ti' < +\infty \land v = v'$

Similar to Property 16 in (Xu et al., 2022a), it can be proved that (Skip;P) = (P;Skip) = P for any Simulink process P.

Since Simulink processes form a complete lattice according to the discussion at the end of Section 2.3.1, recursion can be defined. Theoretically, recursion is denoted by the fixed points of the equation X = F(X), where Fconstructs the body of the recursion. If F is monotonic, the fixed points of X = F(X) also form a complete lattice by the Knaster-Tarski theorem (Tarski, 1955). The least fixed point is denoted by  $\mu X.F(X)$ , based on which we can define

$$\mathsf{P}^* \cong \mu X.(\mathsf{Skip} \lor \mathsf{P} \, ; X)$$

where P is a Simulink process.

#### 4. Semantics for Simulink blocks

In this section, we give the HUTP semantics of Simulink blocks in terms of Simulink processes. A (non-hierarchical) Simulink diagram consists of blocks graphically connected by directed lines. Each such connection is the output signal of a unique block. We represent a signal by a variable x defined as a real-valued function of time  $x \in F \cong \mathbb{R}_{\geq 0} \to \mathbb{R}$ . A Simulink block can be represented by the tuple  $(\mathcal{I}, \mathcal{O}, \mathcal{S}, \mathcal{R})$ , where  $\mathcal{I}$  is the set of input variables,  $\mathcal{O}$  is the set of output variables,  $\mathcal{S}$  is the set of internal state variables, and  $\mathcal{R}$  is a relation between the signals  $F^{\mathcal{I}}$ ,  $F^{\mathcal{S}}$  and  $F^{\mathcal{O}}$ . In the following, we use  $\boldsymbol{x}(t)$  for the vector of input variables as a function of time,  $\boldsymbol{y}(t)$  for the vector of output variables, and  $\boldsymbol{s}(t)$  for the vector of state variables. Note that  $\boldsymbol{s}$  is different from the state variables  $\boldsymbol{v}$  in HUTP (Section 2.3), and the latter is actually the group of  $\boldsymbol{x}, \boldsymbol{s}$  and  $\boldsymbol{y}$ . **Example 6.** A continuous Add block specifies that the output signal y is the sum of the two input signals  $x_0$  and  $x_1$ . Here  $\mathcal{I} = \{x_1, x_2\}, \mathcal{O} = \{y\}, \mathcal{S} = \emptyset$ , and the relation for  $\mathcal{R}$  is given by

$$\forall t \ge 0 \cdot y(t) = x_1(t) + x_2(t).$$

**Example 7.** A discrete Add block with sample time st > 0 specifies that the output is updated to the sum of inputs whenever the time is a multiple of st, and keeps constant otherwise. Here,  $\mathcal{I}$ ,  $\mathcal{O}$  and  $\mathcal{S}$  are the same as before. The relation for  $\mathcal{R}$  is given by

$$\forall k \in \mathbb{N} \cdot \forall t \in [k \cdot st, (k+1)st) \cdot y(t) = x_1(k \cdot st) + x_2(k \cdot st).$$

**Example 8.** A continuous Switch block with condition ">0" specifies that the output y is equal to the top input  $x_1$  if the middle input  $x_2$  satisfies the condition; and the bottom input  $x_3$  otherwise ( $x_2 \leq 0$ ). Here  $\mathcal{I} = \{x_1, x_2, x_3\}$ ,  $\mathcal{O} = \{y\}$  and  $\mathcal{S} = \emptyset$ . The relation for  $\mathcal{R}$  is given by

$$\forall t \ge 0 \cdot y(t) = x_1(t) \triangleleft x_2(t) > 0 \triangleright y(t) = x_3(t).$$

**Example 9.** A Unit Delay block with sample time st > 0 and initial value  $v_0$  updates its state whenever the time is a multiple of st, and outputs the previous value of state. Here  $\mathcal{I} = \{x\}$ ,  $\mathcal{O} = \{y\}$  and  $\mathcal{S} = \{s\}$ . The relation for  $\mathcal{R}$  is given by

$$\begin{aligned} \forall k \in \mathbb{N} \cdot \forall t \in [k \cdot \mathbf{st}, (k+1)\mathbf{st}) \cdot s(t) &= x(k \cdot \mathbf{st}) \\ \wedge \quad \forall t \in [0, \mathbf{st}) \cdot y(t) &= v_0 \quad \wedge \\ \forall k \in \mathbb{N} \cdot \forall t \in [(k+1)\mathbf{st}, (k+2)\mathbf{st}) \cdot y(t) &= s(k \cdot \mathbf{st}). \end{aligned}$$

**Example 10.** An Integrator block with initial state  $s_0$  specifies that its state is the integral of the input signal and the output signal is consistent with the state. Here  $\mathcal{I} = \{x\}$ ,  $\mathcal{O} = \{y\}$  and  $\mathcal{S} = \{s\}$ . The relation for  $\mathcal{R}$  is given by

$$y(0) = s(0) = s_0 \land \forall t > 0 \cdot \dot{s}(t^+) = x(t) \land s(t^-) = s(t) = y(t).$$

Given a Simulink diagram consisting of blocks  $\{\mathbf{b}_i\}_{1 \leq i \leq m}$ . Let  $\mathcal{I}(\mathbf{b}_i)$ ,  $\mathcal{O}(\mathbf{b}_i)$ ,  $\mathcal{S}(\mathbf{b}_i)$  and  $\mathcal{R}(\mathbf{b}_i)$  be the sets of input variables, output variables, state variables, and relation for block  $\mathbf{b}_i$ , respectively. We require the state variables  $\mathcal{S}(\mathbf{b}_i)$  are disjoint from each other and from the input/output variables. Let  $\{v_j\}_{1 \leq j \leq \ell}$  be the set of variables denoting the lines (signals) connecting blocks of the Simulink diagram. Each  $v_j$  is in at most one  $\mathcal{O}(\mathbf{b}_i)$ . The semantics of the Simulink diagram is a relation on  $v_i(t)$ , defined to be the conjunction of the relation for each block:

$$\mathcal{R} = \bigwedge_{1 \le i \le m} \mathcal{R}(\mathsf{b}_i)$$

Following the above analysis, we can define the HUTP semantics for (nonhierarchical) Simulink diagrams. The definition is bottom-up as we start from the individual blocks, then combine them to form the semantics of the entire diagram.

### 4.1. Discrete blocks

A discrete block is specified by a sample time  $\mathbf{st} > 0$ , initial state  $\mathbf{s}_0$ , and two functions f and g for updating the state and computing the output, respectively. The values of state and output variables of a discrete block are constant on each time interval  $[k \cdot \mathbf{st}, (k+1)\mathbf{st})$  for  $k \in \mathbb{N}$ . Hence, we only need to specify their values at times  $k \cdot \mathbf{st}$ . They satisfy the following equations:

$$\begin{array}{lll} \boldsymbol{s}(k\cdot\mathsf{st}) &=& f(\boldsymbol{x}(k\cdot\mathsf{st}), \boldsymbol{s}((k-1)\cdot\mathsf{st})) \\ \boldsymbol{y}(k\cdot\mathsf{st}) &=& g(\boldsymbol{x}(k\cdot\mathsf{st}), \boldsymbol{s}((k-1)\cdot\mathsf{st})) \end{array}$$

where we take  $\mathbf{s}((k-1)\mathbf{st})$  to be  $\mathbf{s}_0$  for k = 0. The main idea here is that the output and state at the current round is computed from the input at *current* round and state at *previous* round.

For example, the discrete Add block in Example 7 is given by

$$y(k \cdot \mathsf{st}) = g(x_1(k \cdot \mathsf{st}), x_2(k \cdot \mathsf{st})) = x_1(k \cdot \mathsf{st}) + x_2(k \cdot \mathsf{st}).$$

There is no need for f as there are no state variables. The discrete Unit Delay block in Example 9 is given by

$$\begin{aligned} s(k \cdot \mathsf{st}) &= f(x(k \cdot \mathsf{st}), s((k-1) \cdot \mathsf{st})) &= x(k \cdot \mathsf{st}) \\ y(k \cdot \mathsf{st}) &= g(x(k \cdot \mathsf{st}), s((k-1) \cdot \mathsf{st})) &= s((k-1) \cdot \mathsf{st}). \end{aligned}$$

Now we describe how to encode the above formulas using the HUTP language. A discrete block can either be *stateful* or *stateless*. For a stateless discrete block, there is no need for the function f. The computation of g is instant and can be expressed by the following discrete process:

$$\mathsf{Comp} \ \widehat{=} \ [\boldsymbol{y}' = g(\boldsymbol{x}')].$$

Intuitively, this means that the output y' is computed from the input values only after they are computed by other processes at the same round, that is after the values of x' are all available. This will enforce the ordering between computation of different blocks, as we will demonstrate afterwards.

After the computation, the block will keep quiescent for the period of st (sample time), i.e., the output y remains unchanged, specified by the following continuous process:

Period

$$\widehat{=}$$

$\llbracket \dot{oldsymbol{y}} = 0

floor_{\mathsf{st}}$

Thus, the hybrid process of the stateless discrete block is defined by

DisBlock

$$\widehat{=}$$

(Comp  $\operatorname{Period})^* \operatorname{Period}$ ) Tail

where

Tail

$$\ \widehat{=} \ \ [\![ \dot{m{y}} = 0 ]_{<\mathsf{st}}$$

means that the block can terminate at the times  $k \cdot \mathsf{st}$  or within the time intervals  $(k \cdot \mathsf{st}, (k+1)\mathsf{st})$ .

For a stateful discrete block, its state variables s should be initialised, given by

Init

$$\widehat{=}$$

$[m{s}'=m{s}_0]$

The state variables s and output variables y are updated periodically according to functions f and g, respectively. The update is instant and can be described by the following discrete process:

$$\mathsf{Comp}' \ \widehat{=} \ [\boldsymbol{s}' = f(\boldsymbol{x}', \boldsymbol{s}) \land \boldsymbol{y}' = g(\boldsymbol{x}', \boldsymbol{s})]$$

The waiting period of the stateful discrete block is represented by the following continuous process:

Period'

$$\hat{=}$$

$[\dot{s} = \dot{y} = 0]_{st}$

During the period, state variables s and output variables y keep unchanged. Thus, similar to DisBlock, the hybrid process of the stateful discrete block is given by

DisBlockSt

$$\hat{=}$$

Init  $\hat{}$  (Comp'  $\hat{}$  Period')\*  $\hat{}$  Comp'  $\hat{}$  Tail'

where

Tail'

$$\hat{=}$$

$[\![\dot{s} = \dot{y} = 0]_{\leq \mathsf{st}}]$

Theorem 11. DisBlock and DisBlockSt are Simulink processes.

*Proof.* The sequential composition Comp<sup>§</sup> Period can be expanded to

$$[\boldsymbol{y}' = g(\boldsymbol{x}')] \, \boldsymbol{\hat{\varsigma}} \, [\![ \boldsymbol{\dot{y}} = \boldsymbol{0} \!]_{\mathsf{St}} = \boldsymbol{y}(ti) = g(\boldsymbol{\dot{x}}(ti)) \land [\boldsymbol{\dot{y}} = \boldsymbol{0} \!]_{\mathsf{St}}$$

which is  $\mathcal{H}_{\text{SIM}}^{\text{A}}$ -healthy according to the definition in Section 3.3. Similarly, we can prove Comp ; Tail is also  $\mathcal{H}_{\text{SIM}}^{\text{A}}$ -healthy. According to Property 3 and by induction on the number of iterations of \*, DisBlock is  $\mathcal{H}_{\text{SIM}}^{\text{A}}$ -healthy. Similarly, we can also prove DisBlockSt is  $\mathcal{H}_{\text{SIM}}^{\text{A}}$ -healthy.

**Example 12.** Consider two discrete blocks in sequence. One block  $B_1$  has input line x and output line y, and set y := x + 1 every sample time 1; the other block  $B_2$  has input line y and output line z, and set  $z := 2 \cdot y$  every sample time 1. The Simulink processes for  $B_1$  and  $B_2$  are given by:

$$\begin{split} & [\![\mathsf{B}_1]\!]_{\mathsf{HUTP}} \quad \widehat{=} \quad ([y' = x' + 1] \, \mathring{\mathsf{s}} \, [\![\dot{y} = 0]_1)^* \, \mathring{\mathsf{s}} \, [y' = x' + 1] \, \mathring{\mathsf{s}} \, [\![\dot{y} = 0]_{\leq 1} \\ & [\![\mathsf{B}_2]\!]_{\mathsf{HUTP}} \quad \widehat{=} \quad ([z' = 2 \cdot y'] \, \mathring{\mathsf{s}} \, [\![\dot{z} = 0]_1)^* \, \mathring{\mathsf{s}} \, [z' = 2 \cdot y'] \, \mathring{\mathsf{s}} \, [\![\dot{z} = 0]_{\leq 1} \end{split}$$

We first rewrite the above two definitions to corresponding logical equations. By the definition of sequential composition , the definition for [y' = x' + 1];  $[[\dot{y} = 0]_1$  in  $[[B_1]]_{HUTP}$  expands to

$$[y' = x' + 1] \, \mathbf{\hat{s}} \, [\![\dot{y} = 0]\!]_1 \tag{1}$$

$$= (ti = ti' < +\infty \land y' = x' + 1) ;$$

(2)

$$\begin{pmatrix} ti < ti' < +\infty \land x = \underline{x}(ti) \land y = \underline{y}(ti) \\ \land \forall t \in (ti, ti') \cdot \underline{y}(t) = 0 \land ti' - ti = 1 \\ \land RC(\underline{x}, \underline{y}, ti, ti') \land SD(\underline{x}, \underline{y}, ti, ti') \end{pmatrix}$$

(3)

$$= \exists t_0, x_0, y_0 \cdot ti = ti_0 < +\infty \land y_0 = x_0 + 1 \land ti_0 < ti' < +\infty \land x_0 = x(ti_0) \land y_0 = y(ti_0) \land \forall t \in (ti_0, ti') \cdot \dot{y}(t) = 0 \land ti' - ti_0 = 1 \land RC(x, y, ti_0, ti') \land SD(x, y, ti_0, ti') = ti' - ti = 1 \land y(ti) = x(ti) + 1 \land \forall t \in (ti, ti + 1) \cdot \dot{y}(t) = 0 \land RC(x, y, ti, ti + 1) \land SD(x, y, ti, ti + 1)$$

Note that although  $\underline{x}$  does not appear in  $[\![ \underline{\dot{y}} = 0 ]\!]_1$ , it is in the alphabet of  $[\![ B_1 ]\!]_{HUTP}$ . Therefore, we cannot remove  $x = \underline{x}(ti)$  from  $[\![ \underline{\dot{y}} = 0 ]\!]_1$  (see (3)). Besides, by  $\mathcal{H}_4^A$ , the continuous state variables in  $[\![ \underline{\dot{y}} = 0 ]\!]_1$  are right continuous and semi-differentiable during the period, specified by RC and SD. Then, by induction, we can get

$$([y' = x' + 1] ; [[\dot{y} = 0]_1)^*$$

$$= \operatorname{Skip} \lor \begin{pmatrix} \exists n \in \mathbb{N}^+ \cdot ti' - ti = n \\ \land \forall k \in \mathbb{N}_{< n} \cdot \underline{y}(ti + k) = \underline{x}(ti + k) + 1 \\ \land \forall t \in (ti + k, ti + k + 1) \cdot \underline{y}(t) = 0 \\ \land RC(\underline{x}, \underline{y}, ti, ti + n) \land SD(\underline{x}, \underline{y}, ti, ti + n) \end{pmatrix}$$

$$(4)$$

where  $\mathbb{N}^+ \cong \mathbb{N} \setminus \{0\}$  and  $\mathbb{N}_{< n} \cong \{k \in \mathbb{N} \mid k < n\}$ . Similar to (1),

$$[y' = x' + 1] \, \mathrm{\widehat{s}} \, [\![ \dot{\underline{y}} = 0 \!]_{\leq 1} \ = \ 0 < ti' - ti \leq 1 \wedge \underbrace{y}(ti) = \underbrace{x}(ti) + 1 \, \mathrm{\widehat{y}}(ti) = \underbrace{x}(ti) + 1 \,$$

$$\wedge \forall t \in (ti, ti') \cdot \underline{\dot{y}}(t) = 0 \wedge RC(\underline{x}, y, ti, ti') \wedge SD(\underline{x}, y, ti, ti')$$

Based on the above results,  $[B_1]_{HUTP}$  expands to

$\exists n \in \mathbb{N} \cdot n < ti' - ti \leq n + 1 \land$  $\forall k \in \mathbb{N}_{< n} \cdot \underbrace{y(ti+k)}_{\leq n} = \underbrace{x(ti+k)}_{\leq (ti+k)} + 1 \land \underbrace{y(ti+n)}_{\leq (ti+n)} = \underbrace{x(ti+n)}_{\leq (ti+n)} + 1 \land \forall t \in (ti+k, ti+k+1) \cdot \underbrace{\dot{y}(t)}_{\leq (ti+n)} = 0 \land \forall t \in (ti+n, ti') \cdot \underbrace{\dot{y}(t)}_{\leq (ti+n)} = 0 \land RC(\underbrace{x, y, ti, ti'}_{\leq (ti+n)}) \land SD(\underbrace{x, y, ti, ti'}_{\leq (ti+n)})$

Similarly,  $[B_2]_{HUTP}$  expands to

$\begin{aligned} \exists n \in \mathbb{N} \cdot n < ti' - ti &\leq n + 1 \land \\ \forall k \in \mathbb{N}_{< n} \cdot \underline{z}(ti+k) = 2 \cdot \underline{y}(ti+k) \land \underline{z}(ti+n) = 2 \cdot \underline{y}(ti+n) \\ \land \forall t \in (ti+k, ti+k+1) \cdot \underline{\dot{z}}(t) = 0 \land \forall t \in (ti+n, ti') \cdot \underline{\dot{z}}(t) = 0 \\ \land RC(y, \underline{z}, ti, ti') \land SD(y, \underline{z}, ti, ti') \end{aligned}$

The connection of  $B_1$  and  $B_2$  can be defined by  $[\![B_1]\!]_{HUTP} \wedge [\![B_2]\!]_{HUTP}$ , i.e.,

$\begin{aligned} \exists n \in \mathbb{N} \cdot n < ti' - ti \leq n + 1 \wedge \\ \forall k \in \mathbb{N}_{<n} \cdot \underbrace{y}(ti+k) = \underbrace{x}(ti+k) + 1 \wedge \underbrace{z}(ti+k) = 2 \cdot \underbrace{y}(ti+k) \\ \wedge \underbrace{y}(ti+n) = \underbrace{x}(ti+n) + 1 \wedge \underbrace{z}(ti+n) = 2 \cdot \underbrace{y}(ti+n) \\ \wedge \overleftarrow{\forall}t \in (ti+k, ti+k+1) \cdot \underbrace{\dot{y}}(t) = \underbrace{\dot{z}}(t) = 0 \\ \wedge \forall t \in (ti+n, ti') \cdot \underbrace{\dot{y}}(t) = \underbrace{\ddot{z}}(t) = 0 \\ \wedge RC(\underbrace{x}, y, \underbrace{z}, ti, ti') \wedge SD(\underbrace{x}, y, \underbrace{z}, ti, ti') \end{aligned}$

This example demonstrates that the parallel composition of the HUTP semantics for  $B_1$  and  $B_2$  simplifies to the desired form, enforcing that the computation in  $B_1$  is performed before that of  $B_2$  at every sample time. We further note that the values of  $\underline{y}$  and  $\underline{z}$  are determined given values of input signal  $\underline{x}$ .

#### 4.2. Continuous blocks

We consider two kinds of continuous blocks: *computation* blocks and **Integrator** blocks. A computation block is a stateless block with sample time 0 (see Examples 6 and 8). When building Simulink diagrams, the sample time of computation blocks are usually inherited from integrator blocks by sample time propagation. It is specified by a function g from its input  $\boldsymbol{x}$  to its output  $\boldsymbol{y}$ , so its relation is specified by  $\forall t \geq 0 \cdot \boldsymbol{y}(t) = g(\boldsymbol{x}(t))$ . Hence, its HUTP representation is

ConBlock

$$\widehat{=}$$

$ig[oldsymbol{y}=g(oldsymbol{x})ig]$

**Remark 13.** For a continuous block, our concern is the evolution of its output signals  $(\underline{y})$  according to its input signals  $(\underline{x})$  rather than its initial and/or final observations (x, y, x', and y'). Thus, we use  $\lceil \cdot \rceil$  rather than  $\lceil \cdot \rceil$  in ConBlock.

The **Integrator** block is already given in Example 10, and its HUTP representation is given by

IntBlock

$$\widehat{=} y(ti) = \underline{s}(ti) = s_0 \land [\underline{\dot{s}}^+ = \underline{x} \land \underline{s}^- = \underline{s} = \underline{y}]$$

where  $s_0$  is the initial state of s, and  $\dot{s}^+$  and  $\underline{s}^-$  denote the right-hand derivative and the left limit of  $\underline{s}$ , respectively. Since  $\underline{x}$  could be discontinuous but at least right continuous as stated by  $\mathcal{H}_4$ , we use  $\dot{\underline{s}}^+$  rather than  $\dot{\underline{s}}$  in the representation. Besides,  $\underline{s}$  should be continuous and the output signal should keep consistent with the state, so we need the condition  $\underline{s}^- = \underline{s} = \underline{y}$ .

Theorem 14. ConBlock and IntBlock are Simulink processes.

*Proof.* ConBlock and IntBlock are  $\mathcal{H}^{A}_{SIM}$ -healthy by the definition of  $\lceil \cdot \rfloor$  specified in Section 3.3.

**Property 15.**  $\left\lceil \underline{P} \right\rfloor \wedge \left\lceil \underline{Q} \right\rfloor = \left\lceil \underline{P} \wedge \underline{Q} \right\rfloor$

*Proof.* According to the definition of  $\lceil \cdot \rfloor$ ,

$$\begin{split} \left\lceil \underline{\mathcal{P}} \right\rfloor \wedge \left\lceil \underline{\mathcal{Q}} \right\rfloor &= 0 < ti < ti' < +\infty \land \forall t \in (ti, ti') \cdot \underline{\mathcal{P}}(\underline{\boldsymbol{v}}(t), \underline{\dot{\boldsymbol{v}}}(t)) \\ & \wedge RC(\underline{\boldsymbol{v}}, ti, ti') \land SD(\underline{\boldsymbol{v}}, ti, ti') \land \\ & 0 < ti < ti' < +\infty \land \forall t \in (ti, ti') \cdot \underline{\mathcal{Q}}(\underline{\boldsymbol{v}}(t), \underline{\dot{\boldsymbol{v}}}(t)) \\ & \wedge RC(\underline{\boldsymbol{v}}, ti, ti') \land SD(\underline{\boldsymbol{v}}, ti, ti') \\ &= \left\lceil \underline{\mathcal{P}} \land \underline{\mathcal{Q}} \right\rfloor \end{split}$$

The property is proved.

**Example 16.** Consider an Integrator block  $B_3$  with state s, input line z and output line x, and s is set to 0 initially. The Simulink process for  $B_3$  is given by:

$$\begin{split} \llbracket \mathsf{B}_3 \rrbracket_{\mathsf{HUTP}} &= \begin{split} \mathfrak{x}(ti) &= \mathfrak{s}(ti) = 0 \land [\dot{\mathfrak{s}}^+ = \mathfrak{z} \land \mathfrak{s}^- = \mathfrak{s} = \mathfrak{x}] \\ &= \begin{pmatrix} ti < ti' < +\infty \land \mathfrak{x}(ti) = \mathfrak{s}(ti) = 0 \\ \land \forall t \in (ti, ti') \cdot \dot{\mathfrak{s}}(t^+) = \mathfrak{z}(t) \land \mathfrak{s}(t^-) = \mathfrak{s}(t) = \mathfrak{x}(t) \\ \land RC(\mathfrak{x}, \mathfrak{s}, \mathfrak{z}, ti, ti') \land SD(\mathfrak{x}, \mathfrak{s}, \mathfrak{z}, ti, ti') \end{pmatrix} \end{split}$$

#### 4.3. Composition

A (non-hierarchical) Simulink diagram is composed of discrete and continuous blocks connected by lines. Given such a diagram, we can construct a directed graph  $\mathcal{G}$ , called its *causality graph*, as follows. The vertices of  $\mathcal{G}$ are the input/output variables, and there is an edge from  $v_i$  to  $v_j$  if  $v_i$  is the input and  $v_j$  is the output of some non-delay discrete or computation block  $B_k$ . Note that the discrete delay block and the integrator block are excluded. If  $\mathcal{G}$  is acyclic, then the diagram is said to be well-formed. Otherwise, there exist some loops among discrete and/or computation blocks called *algebraic loops* (also called logical loops in (Zou et al., 2013b)), which may not always admit a solution. Actually, the cycle-freedom of causality graphs is a necessary condition for Simulink diagrams to behave well. In particular, it allows to avoid straightforward deadlocks. To our knowledge, should the causality graph of a diagram contain a cycle, the tool Matlab/Simulink would reject it, returning an error or a warning. Accordingly, we only consider Simulink diagrams with acyclic causality graphs in this paper.

If the diagram is well-formed, its HUTP semantics can be described by the parallel composition of the atomic blocks it contains. Specifically, given a well-formed diagram consisting of n blocks whose semantics are represented by  $\mathsf{P}_i$   $(1 \le i \le n)$ , the semantics of the diagram is denoted by the following parallel composition, which is equivalent to the conjunction by Property 5:

$$\mathsf{P}_1 \| \cdots \| \mathsf{P}_n \equiv \bigwedge_{i=1}^n \mathsf{P}_i$$

We say the semantics of a diagram is *determined* if, given any choice of input signals to the overall diagram, there are unique functions for all output and state variables that satisfies  $\bigwedge_{i=1}^{n} \mathsf{P}_{i}$ . We wish to prove that under additional conditions related to the unique solvability of ODEs, the HUTP semantics of a well-formed diagram is determined. Before proving this result, we prove the following lemmas.

**Lemma 17.** Consider a well-formed Simulink diagram consisting of n discrete blocks whose semantics are represented respectively by  $P_i$ . Given any choice of input signals to the overall diagram, there are unique functions for all input, output, and state variables that satisfy  $\bigwedge_{i=1}^{n} P_i$ . Moreover, let st be the sample time of the diagram (greatest common divisor of the sample times of the blocks), then the values of output and state variables depend only on the values of input variables at multiples of st, and they are constant over each time interval  $[k \cdot st, (k+1) \cdot st)$ .

*Proof.* Since the causality graph  $\mathcal{G}$  of the Simulink diagram is acyclic, we can choose a topological ordering  $\underline{v}_1, \dots, \underline{v}_m$  for the input and output variables

of the blocks in the diagram. For brevity, we assume that the sample time of the diagram is 1. We prove by induction on k that there exist unique values for input, output and state variables on each time interval [k, k + 1). First, consider the base case k = 0, we perform a second induction on the index i in the ordering  $y_i$ . For the variable  $y_i$ , by the induction hypothesis, we can assume  $y_j(0)$  is uniquely determined for each j < i.  $y_i$  is either an input to the overall diagram, or the output of some block  $B_j$ . If  $B_j$  is a delay block, then  $y_i(0)$  is given by the initial value of the state. Otherwise, according to the definition of  $\mathcal{G}$ , all input variables of the block occur earlier in the topological order, whose values at 0 are uniquely determined by induction, so again  $y_i(0)$  is uniquely determined. Since the values of state variables at time 0 is a function of input variables at time 0 and the initial state, they are also determined.

Now consider the inductive case k + 1. Again, we induct on the index iin the ordering  $y_i$ . If  $y_i$  is an input to the overall diagram, then it is already determined. So suppose  $y_i$  is the output of some block  $B_j$ . If the sample time of block  $B_j$  is a multiple of k + 1, again we divide into cases for delay block and non-delay block. For the delay block, the value of  $y_i(k+1)$  is given by the value of state at a previous time. For non-delay blocks, the value of  $y_i(k+1)$  is a function of  $y_j(k+1)$  for j < i and state variables at time k. In both cases the value is determined. Finally, if the sample time of  $B_j$  is not a multiple of k + 1, we have  $y_i(k+1) = y_i(k)$ . This shows  $y_i(k+1)$  is determined for all  $1 \le i \le m$ . Then, since the state variables at time k + 1is a function of variables  $y_i(k+1)$  and state variables at time k, they are determined as well.

In this way, we construct the values of all  $y_i$ , as well as that of the state variables, at the integer time points. In the process, we have considered relations for all blocks. Hence, the solution we obtained satisfies the relation  $\bigwedge_{i=1}^{n} \mathsf{P}_i$ . Finally, by the construction in this proof, it is clear that the output and state variables depend only on the values of input variables at each integer k, and are constant over each time interval [k, k+1).

**Lemma 18.** For a well-formed Simulink diagram consisting of continuous blocks, let v be the line variables of the diagram, where x denote the input variables to the diagram and s and y represent the state and output variables of the Integrator blocks in the diagram. Then,

(1) its semantics can be expressed in the form of

$$\boldsymbol{y}(ti) = \boldsymbol{s}(ti) = \boldsymbol{s}_0 \land \left[ \overset{\circ}{P}(\boldsymbol{x}) \land \overset{\circ}{\boldsymbol{s}}^+ = E(\boldsymbol{x} \uplus \boldsymbol{s}) \land \boldsymbol{s}^- = \boldsymbol{s} = \boldsymbol{y} \right]$$

(5)

where  $\mathbf{s}_0$  are the initial states of  $\mathbf{s}$ ,  $\underline{P}$  is a relation only relating  $\underline{v}$ , and E is a (vector) function in terms of variables in  $\underline{x} \uplus \underline{s}$ ;

- (2) if the function E satisfies the global Lipschitz condition, given any choice of input signals to the overall diagram, there are unique functions for all input, output, and state variables that satisfy the semantics.

- *Proof.* (1) Assume the diagram consists of m Integrator blocks and n computation blocks. Label the Integrator blocks by  $B_i$  for  $1 \le i \le m$ , and the computation blocks by  $B_j$  for  $m + 1 \le j \le m + n$ . Let  $a_i$ ,  $s_i$  and  $y_i$  be the input, state and output variables of an Integrator block  $B_i$ , respectively, and  $b_j$  and  $c_j$  be the input and output variables of a computation block  $B_j$ , respectively. According to the semantics of these continuous blocks (see Section 4.2) and Property 15, the semantics of the diagram can be defined by

Init

$$\wedge$$

Evolve (6)

where

Init

$$\widehat{=} \bigwedge_{i=1}^{m} \underbrace{y_i(ti)}_{i=1} = \underbrace{s_i(ti)}_{i=i} = s_{i,0}$$

Evolve  $\widehat{=} \left[ \bigwedge_{i=1}^{m} \underbrace{\dot{s}_i^+}_{i} = \underbrace{g_i \land \underline{s}_i^-}_{i} = \underbrace{g_i}_{i} = \underbrace{y_i \land \bigwedge_{j=m+1}^{m+n} \underline{c}_j}_{j=m+1} = g_j(\underline{b}_j) \right]$

where  $s_{i,0}$  is the initial value of  $s_i$ . For each computation block  $\mathsf{B}_j$ , it defines a variable substitution mapping  $\Gamma_{jk}$ . Concretely, it maps each output variable  $c_{jk} \in \mathbf{c}_j$  of the block to an expression  $g_{jk}$  on the input variables  $\mathbf{b}_j$ , i.e.,  $\Gamma_{jk}(c_{jk}) = g_{jk}(\mathbf{b}_j)$ , where all the  $g_{jk}$  form the function  $g_j$ . Since the diagram is well-formed, the input and output variables of all computation blocks in the diagram form a directed acyclic graph. Therefore, all the mapping functions  $\Gamma_{jk}$  can be composed to form a function  $\Gamma$  that maps the input variable  $a_i$  (which could be some  $c_{j,k}$ ) of each Integrator block  $\mathsf{B}_i$  to  $\Gamma(a_i)$  which is an expression on  $\mathbf{x} \uplus \mathbf{s}$ , denoted  $e_i(\mathbf{x} \uplus \mathbf{s})$ . Note that for  $a_i \notin \operatorname{dom}(\Gamma)$ , we let  $\Gamma(a_i) = a_i$ . All the expressions  $e_i(\mathbf{x} \uplus \mathbf{s})$  form the expression function E. Besides,  $\bigwedge_{j=m+1}^{m+n} \mathbf{c}_j = g_j(\mathbf{b}_j)$  denotes the relation  $\mathcal{P}$  in the representation. In summary, the formula of (6) can be expresses in the form of (5).

(2) According to Equation (5), the right-hand derivative of  $\underline{s}$  always exists, which means  $\underline{s}$  is piecewise differentiable. By induction on the time intervals where  $\underline{s}$  is differentiable, and using the fact that E satisfies the global Lipschitz condition, we obtain the existence and uniqueness of the solution.

The lemma is proved.

**Theorem 19.** For a well-formed diagram consisting of discrete and continuous blocks, if the expression function E of the continuous sub-diagram (consisting of the continuous blocks) satisfies the global Lipschitz condition, then the HUTP semantics of the entire diagram is determined and can be represented by a Simulink process.

*Proof.* By Property 3 and Theorems 11 and 14, the HUTP semantics is a Simulink process. To show that the HUTP semantics of the combination of discrete and continuous sub-diagrams is determined, we perform an induction on multiples of the sample time st of the discrete sub-diagram (as defined in Lemma 17). At each step k, the computation of the discrete diagram provides the initial conditions at time  $k \cdot st$  for evolution of the continuous diagram, and the continuous evolution provides the initial value for the discrete diagram at time  $(k + 1) \cdot st$ . Hence determinacy follows from Lemma 17 and Lemma 18.

**Example 20.** The connection of  $B_1$ ,  $B_2$  (Example 12) and  $B_3$  (Example 16) forms a closed Simulink diagram with the causality graph  $\mathcal{G} = \{(x, y), (y, z)\}$  acyclic, hence the diagram is well-formed. Then, the HUTP semantics of this diagram is  $[B_1]_{HUTP} \land [B_2]_{HUTP} \land [B_3]_{HUTP}$ , expanding as follows:

$$\begin{cases} x(ti) = \underline{s}(ti) = 0 \land \\ \exists n \in \mathbb{N} \cdot n < ti' - ti \leq n + 1 \land \forall k \in \mathbb{N}_{< n} \land \\ y(ti+k) = \underline{x}(ti+k) + 1 \land \underline{z}(ti+k) = 2 \cdot \underline{y}(ti+k) \land \\ y(ti+n) = \underline{x}(ti+n) + 1 \land \underline{z}(ti+n) = 2 \cdot \underline{y}(ti+n) \land \\ \forall t \in (ti+k, ti+k+1) \cdot \underline{y}(t) = \underline{z}(t) = 0 \land \underline{s}(t) = \underline{z}(t) \land \\ \forall t \in (ti+n, ti') \cdot \underline{y}(t) = \underline{z}(t) = 0 \land \underline{s}(t) = \underline{z}(t) \land \\ \forall t \in (ti, ti') \cdot \underline{s}(t^{-}) = \underline{s}(t) = \underline{x}(t) \land \\ RC(\underline{x}, y, \underline{z}, \underline{s}, ti, ti') \land SD(\underline{x}, y, \underline{z}, \underline{s}, ti, ti') \end{cases}$$

Since  $\underline{z}$  is differentiable within the intervals (ti+k, ti+k+1) and (ti+n, ti'),  $\underline{\dot{s}}(t^+)$  is replaced with  $\underline{\dot{s}}(t)$  in the above formula. For ensuring the continuity of  $\underline{s}$ , there should be  $\underline{s}^- = \underline{s}$  during the period. For the above formula, we get the following unique solution:

$$\forall t \in [ti, ti') \cdot \exists d \in \mathbb{R} \cdot d = t - ti \land \begin{pmatrix} \underline{s}(t) &= 2 \cdot 3^{\lfloor d \rfloor}(d - \lfloor d \rfloor) + 3^{\lfloor d \rfloor} - 1\\ \underline{x}(t) &= 2 \cdot 3^{\lfloor d \rfloor}(d - \lfloor d \rfloor) + 3^{\lfloor d \rfloor} - 1\\ \underline{y}(t) &= 3^{\lfloor d \rfloor}\\ \underline{z}(t) &= 2 \cdot 3^{\lfloor d \rfloor} \end{pmatrix}$$

which is exactly the semantics of the Simulink diagram (here  $\lfloor \cdot \rfloor : \mathbb{R} \to \mathbb{Z}$  is the floor function).

## 5. Hierarchical Simulink diagrams

Modular design is a design principle that subdivides a system into smaller parts called modules (or subsystems), which can be independently created, modified, replaced, or exchanged with other modules or between different systems. The modelling of hierarchical Simulink diagrams reflects the principle of modular design: a Simulink diagram is composed of hierarchical subsystems, which may include enabled or triggered behaviours. In this section, we establish the HUTP semantics for *normal*, *triggered* and *enabled* subsystems, which forms hierarchical Simulink diagrams.

#### 5.1. Normal subsystems

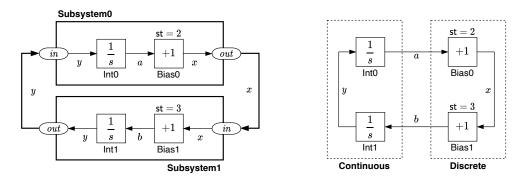

A normal subsystem groups a set of atomic Simulink blocks together, and will execute them as a single unit. Simulink distinguishes the input (output) variables i (o) as seen from within the subsystem and the input (output) variables  $\overline{i}$  ( $\overline{o}$ ) as seen from outside (as lines in the overall diagram). For normal subsystems, we will identify the variables i with  $\overline{i}$ , and variables owith  $\overline{o}$  (see x and y in Fig. 2). Later on, we may not identify i with  $\overline{i}$  for triggered and enabled subsystems.

A normal subsystem is *well-formed* if its causality graph is acyclic. The effect of executing a well-formed normal subsystem is equivalent to executing the corresponding Simulink diagram consisting of the same set of blocks. Therefore, the semantics of a normal subsystem can be defined by the conjunction of the semantics of all the blocks it contains, as specified in Section 4.3.

Fig. 2: A well-formed Simulink diagram composed of two subsystems. The left is the original hierarchical diagram and the right is the flattened form.

In the translation algorithm from Simulink to HCSP presented in (Zou et al., 2013b), the subsystem is flattened by connecting the in-ports and outports as seen from inside with the corresponding in-ports and out-ports on the

outside. The result of this process is shown on the right side of Fig. 2. This flattening makes the translation process easier to implement, and is necessary for collecting together all continuous blocks in the diagram for translation to a single ODE. However, it violates to some extent the principle of modular design, i.e., the hierarchical structure of the Simulink diagram is not reflected in the translated HCSP process. In this paper, subsystems are not flattened and therefore the structure of Simulink diagrams can be reflected in their HUTP semantics. For example, the Simulink diagram on the left of Fig. 2 is composed of two well-formed subsystems Subsystem0 and Subsystem1 whose semantics are given by

$$[Subsystem0]_{HUTP} \stackrel{\frown}{=} [Int0]_{HUTP} \land [Bias0]_{HUTP} \\ [Subsystem1]_{HUTP} \stackrel{\frown}{=} [Int1]_{HUTP} \land [Bias1]_{HUTP}$$

where  $[Bias0]_{HUTP}$  and  $[Bias1]_{HUTP}$  are discrete processes (Section 4.1), and  $[Int0]_{HUTP}$  and  $[Int1]_{HUTP}$  are continuous processes (Section 4.2).

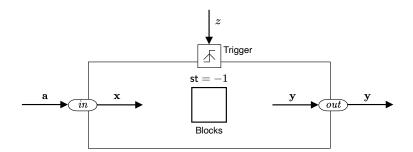

#### 5.2. Triggered subsystems

A triggered subsystem only contains blocks with inherited sample time (-1). Such a block has no specified sample time, whose execution depends solely on the triggering signal. Concretely, the blocks execute at the instant when the trigger condition on the trigger line holds. A sketch of a triggered subsystem with rising edge trigger is shown in Fig. 3. Similar to well-formed normal subsystems, a triggered subsystem is well-formed if its causality graph is acyclic. The trigger port senses the input signal z in real time. In this paper, we assume that each triggered subsystem has only one trigger line. There are three basic trigger types: rising, falling and either. For the rising edge trigger, the subsystem is triggered at time t whenever (1) z rises from negative to non-negative at t or (2) z rises from non-positive to positive at t. Formally,

$$z(t^-) < 0 \land z(t) \ge 0 \quad \lor \quad z(t^-) \le 0 \land z(t) > 0$$

The triggering conditions for the other two trigger types can be defined similarly. Therefore, in this section, we only define the HUTP semantics for triggered subsystems with rising edge trigger. In this paper, we assume that the trigger line of each triggered subsystem is the output of a discrete block, hence piecewise constant with some sample time st. Treatment of continuous triggering will be more complicated, involving analysis of zero-crossing detection and potential cascade of zero-crossings (Benveniste et al., 2012).

Fig. 3: A sketch of a triggered subsystem with rising edge trigger

Now we consider the HUTP semantics of well-formed triggered subsystems. The subsystem is triggered at current time iff (1) the previous value of the signal z is less than 0 and the current value of z reaches or crosses 0; or (2) the previous value of z is not greater than 0 and the current value of z crosses 0. After that, the signal z will keep "not triggering" for some period until it satisfies the trigger condition again. Therefore, the behaviour of z between two adjacent triggering time instants can be defined by

Trigger

$$\hat{=} [z < 0 \land z' \ge 0 \lor z \le 0 \land z' > 0]$$

$[\neg$ trigger

where

trigger

$$\hat{=} z^- < 0 \land z \ge 0 \lor z^- \le 0 \land z > 0$$

When triggered, the subsystem gets the latest values from the input ports, given by the relation  $\mathbf{x}(ti) = \mathbf{a}(ti)$ , where ti is the current triggering time,  $\mathbf{x}$  denote the input variables from within the subsystem while  $\mathbf{a}$  denote the input variables to the overall subsystem (see Fig. 3). The reason we distinguish  $\mathbf{x}$  and  $\mathbf{a}$  is that their values are not the same at all times: during the idle period of the subsystem,  $\mathbf{x}$  will keep unchanged while  $\mathbf{a}$  can change dynamically according to the behaviour of its source subsystem. The input variables  $\mathbf{x}$  synchronise with the input variables  $\mathbf{a}$  from the outside only when the triggering signal arrives. However, for output variables, it is not necessary to distinguish the output variables to within the subsystem and the output variables from the overall subsystem, because the output variables are controlled by the subsystem solely and they will not be modified by other subsystems, i.e., they always keep consistent.

After the input synchronisation ( $\boldsymbol{x}$  obtain the values of  $\boldsymbol{a}$ ), the subsystem will perform the computation and then keep idle for some period, which can be represented by the conjunction of the idle process  $\lceil \boldsymbol{v} = \boldsymbol{0} \rfloor$ , where  $\boldsymbol{v}$  are the variables inner the subsystem, and the continuous processes  $\lceil \boldsymbol{\mathcal{P}}_i \rfloor$  ( $1 \leq i \leq n$ ) of all blocks in the subsystem. Therefore, according to Property 15, which indicates

$$ig[ \dot{oldsymbol{v}} = oldsymbol{0} ig] \wedge ig \wedge igc[ \sum_{i=1}^n ig[ \sum_{i} ig] = igc[ igc] \wedge igc] igc[ \sum_{i=1}^n igc] igc]$$

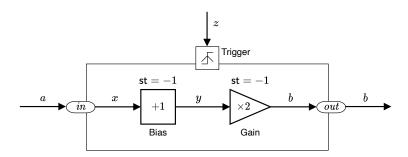

Fig. 4: An example of a triggered subsystem with rising edge trigger

the behaviour of the subsystem can be captured by

SubSys

$$\widehat{=} \ \underline{x}(ti) = \underline{a}(ti) \land [\underline{\dot{v}} = \mathbf{0} \land \bigwedge_{i=1}^{n} \underline{\gamma}_{i}]$$

Before triggering, the variables v of the lines in the subsystem should be initialised, because if the subsystem is not triggered at the beginning, it should be guaranteed that the values of v are valid. By default, v are initialised to **0** in Simulink. If the subsystem is not triggered initially, the values of vwill keep constant. Besides, the trigger line z should also be initialised, because at the beginning, it will compare the initial value of z with the current value of z to determine if the subsystem should be triggered at the time. By default, we also set z to 0 initially. Then, the initialisation is specified by

InitTrig

$$\hat{=}$$

$[v' = 0 \land z' = 0]$  ; (Trigger  $\land$  SubSys  $\lor$  Idle)

In summary, the semantics of triggered subsystem can be defined by

TrigSubSys  $\hat{=}$  InitTrig  $\hat{g}$  (Trigger  $\wedge$  SubSys)\*

When creating the causality graph of a triggered subsystem, we add edges from the trigger line to each input line inside the subsystem, since whether the input lines receive values from the outside is determined by the trigger line. For the example in Fig. 4, the causality graph  $\mathcal{G}$  is given by  $\{(z, x), (a, x), (x, y), (y, b)\}.$

**Example 21.** Consider the triggered subsystem in Fig. 4, we only analyse SubSys. Concretely, SubSys is equivalent to

$$\underline{x}(ti) = \underline{a}(ti) \land \lceil \underline{\dot{x}} = \underline{\dot{y}} = \underline{\dot{b}} = 0 \land \underline{b} = 2 \cdot \underline{y} \land \underline{y} = \underline{x} + 1 \rfloor$$

which can expand as follows:

$$\underline{x}(ti^+) = \underline{x}(ti) = \underline{a}(ti) = \underline{a}(ti^+) \land \underline{y}(ti) = \underline{y}(ti^+) \land \underline{b}(ti) = \underline{b}(ti^+) \land$$

(7)

$$\forall t \in (ti, ti') \cdot \dot{x}(t) = \dot{y}(t) = \dot{y}(t) = 0 \land \dot{y}(t) = 2 \cdot \dot{y}(t) \land \dot{y}(t) = \dot{x}(t) + 1 \quad (8)$$

$$\land RC(a, ti, ti') \land SD(a, ti, ti')$$