# A Simple Analysis to Determine the Limits of a CMOS Technology to Implement SC DC-DC Converters

Ricardo Madeira, Nuno Paulino

# ▶ To cite this version:

Ricardo Madeira, Nuno Paulino. A Simple Analysis to Determine the Limits of a CMOS Technology to Implement SC DC-DC Converters. 11th Doctoral Conference on Computing, Electrical and Industrial Systems (DoCEIS), Jul 2020, Costa de Caparica, Portugal. pp.265-273, 10.1007/978-3-030-45124-0\_25. hal-03741562

# HAL Id: hal-03741562 https://inria.hal.science/hal-03741562

Submitted on 1 Aug 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

This document is the original author manuscript of a paper submitted to an IFIP conference proceedings or other IFIP publication by Springer Nature. As such, there may be some differences in the official published version of the paper. Such differences, if any, are usually due to reformatting during preparation for publication or minor corrections made by the author(s) during final proofreading of the publication manuscript.

## A Simple Analysis to Determine the Limits of a CMOS Technology to Implement SC DC-DC Converters

Ricardo Madeira and Nuno Paulino

Dept. of Electrical Engineering (DEE), Faculty of Sciences and Technology (FCT NOVA), Caparica, Portugal Centre for Technologies and Systems (CTS) – UNINOVA, Caparica, Portugal <u>r.madeira@campus.fct.unl.pt</u>, <u>nunop@uninova.pt</u>

**Abstract.** This paper presents a simple analysis that allows to determine the maximum power density and efficiency of a SC DC-DC converter for a given CMOS technology. By determining the values of the ratio between the switches' gate capacitance and channel width, and between the ON resistance and the channel width, together with the parasitic capacitances from the flying capacitor, it is possible to plot the efficiency as a function of the power density for a given input voltage and output voltage of the converter, allowing to quickly determine both the expected efficiency of the converter and clock frequency ranges, for a given CMOS technology.

Keywords: power management unit, switched-capacitor (SC) converter, design techniques

### 1 Introduction

Nowadays, with the growing number of Internet-of-things (IoT) devices, the collection of real live raw data from innumerous processes has greatly increased, e.g., in industrial, health, transportation, communications processes and others [1]. This raw data can be analyzed inside of the IoT device thus distributing the data processing capabilities and decreasing the reaction time. This sensing and processing of information costs energy. Hence, it is extremely important to have efficient systems, in a macro scale it contributes for reducing the carbon footprint, and at a small scale, it allows improving the battery life of devices thus reducing maintenance costs.

There are several energy sources, like solar, piezoelectrical, thermal, and others [2]. This energy can be fed directly to the system, and/or be stored in an energy storing device, like a battery or supercapacitor. These energy sources produce a variable voltage, which requires the use of a Power Management Unit (PMU) to obtain a constant output voltage. The PMU provides a bridge between the energy sources and the system using, for example, DC-DC converters. These can be inductive or capacitive, where the latter has receiving a lot of attention in recent years since they are composed by switches and capacitors that are native in CMOS technology and thus, they can be easily integrated, resulting in a smaller footprint and cost, and still achieve high performance values [2]–[6].

#### 262 R. Madeira and N. Paulino

The Switched-Capacitor (SC) DC-DC converters transfer charge from the input to the output through a capacitor, where the frequency at which the charge is transferred will determine the output voltage value of the converter. This charge transferring is controlled by a clock signal, allowing for different circuit configurations on each clock phase. The quality of both the capacitors and switches will affect the converter's energy efficiency and power per area value [6]-[8]. The characteristics of the passive devices depend on the CMOS technology node for the system implementation, for example, the lower the CMOS node, the higher the capacitance per area of the capacitors. This is because smaller oxide thickness means higher capacitance values. However, small oxide thickness also means lower breakdown voltage values and larger current leakage. The same goes for switches, the lower the node, the higher switching frequency can be. This raises the question, what is the expected performance for each technological node? To answer this, this work shows an analysis that characterizes both the capacitors and switches of the 130 nm bulk CMOS technology into a set of coefficients that are used to determine the converter efficiency and power per area. This can be applied to any technology node.

#### 2 Relationship to Technological Innovation for Life Improvement

The IoT devices can enhance our life quality in many ways, e.g., increasing the surgery span of patient with medical embedded devices, like pacemakers, by increase the battery life of the devices. Such devices can also be used to monitoring our health, which can give us a better control of our daily life needs. There are several number of other examples in different areas, where all these devices, which need energy to operate, will benefit from energy efficient PMUs. The energy improvement of such devices will consequently have a direct impact on the human's life quality.

## **3** SC DC-DC Converter Theoretical Analysis

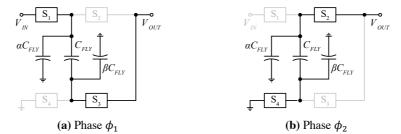

Fig. 1 shows the schematic of a Step-down Series-Parallel (SP) SC DC-DC converter with a Conversion Ratio (CR) of 1/2. It is composed by 1 flying capacitor  $C_{FLY}$  and 4 switches, where  $S_{1,3}$  are ON in the phase  $\phi_1$  and  $S_{2,4}$  are ON in phase  $\phi_2$ , where  $\phi_{1,2}$ are two clock signals complementary to each other. Hence, on  $\phi_1$ ,  $C_{FLY}$  connects between the input voltage  $V_{IN}$  and the output voltage  $V_{OUT}$ , and on  $\phi_2$ ,  $C_{FLY}$  connects between  $V_{OUT}$  and ground. In the schematic it is also represented the  $C_{FLY}$  parasitic capacitances by  $\alpha$  and  $\beta$ , these refer to the top and bottom parasitic capacitance, respectively, as percentage of  $C_{FLY}$ . Assuming that  $V_{OUT}$  is kept at a constant voltage, the charge equations can be drawn:

$$(V_{IN} - V_{OUT}) C_{FLY} + V_{IN} (\alpha C_{FLY}) = V_{OUT} (C_{FLY} + \alpha C_{FLY}) + \Delta q_o^{\phi_2} , \qquad (1)$$

$$-V_{OUT} C_{FLY} = (V_{OUT} - V_{IN}) C_{FLY} + V_{OUT} (\beta C_{FLY}) + \Delta q_0^{\phi_1}, \qquad (2)$$

A Simple Analysis to Determine the Limits of a CMOS Technology 263

$$V_{OUT} (C_{FLY} + \alpha C_{FLY}) = (V_{IN} - V_{OUT}) C_{FLY} + V_{IN} (\alpha C_{FLY}) - \Delta q_i^{\phi_1} .$$

(3)

where  $\Delta q_o^{\phi_{1,2}}$  are the amount of charge absorbed by  $V_{OUT}$ , in the respective phase, and  $\Delta q_i^{\phi_1}$  the amount of charge drawn by the circuit from  $V_{IN}$ , in this case only during  $\phi_1$ .

Fig. 1 Simplified schematic of the SP 1/2 SC DC-DC converter in each clock phase [3],[4].

These equations can be solved in respect to  $\Delta q_i^{\phi_1}$ ,  $\Delta q_o^{\phi_1}$ , and  $\Delta q_o^{\phi_2}$ , and used to determine the input and output current and power:

$$I_{IN} = \Delta q_i^{\phi_1} F_{CLK} = C_{FLY} \left( V_{IN} \left( 1 + \alpha \right) - V_{OUT} \left( 2 + \alpha \right) \right),$$

(4)

$$I_{OUT} = \left(\Delta q_o^{\phi_1} + \Delta q_o^{\phi_2}\right) F_{CLK} = C_{FLY} F_{CLK} \left(V_{IN} \left(2 + \alpha\right) - V_{OUT} \left(4 + \alpha + \beta\right)\right),$$

(5)

$$P_{IN} = V_{IN} I_{IN} = C_{FLY} F_{CLK} V_{IN} \left( V_{IN} \left( 1 + \alpha \right) - V_{OUT} \left( 2 + \alpha \right) \right),$$

(6)

$$P_{OUT} = V_{OUT} I_{OUT} = C_{FLY} F_{CLK} V_{OUT} \left( V_{IN} \left( 2 + \alpha \right) - V_{OUT} \left( 4 + \alpha + \beta \right) \right).$$

(7)

The converter efficiency  $\eta$  can be obtained by (8) and its output impedance  $R_{OUT}$  by (9). Both  $V_{OUT}$  and  $F_{CLK}$  can be determined by (10) and (11), where  $R_L$  is the load resistor and  $P_{OUT} = V_{OUT}^2/R_L$ .

$$\eta = \frac{P_{OUT}}{P_{IN}} = \frac{V_{OUT} \left( V_{IN} \left( 2 + \alpha \right) - V_{OUT} \left( 4 + \alpha + \beta \right) \right)}{V_{IN} \left( V_{IN} \left( 1 + \alpha \right) - V_{OUT} \left( 2 + \alpha \right) \right)} , \tag{8}$$

$$R_{OUT} = \frac{CRV_{IN} - V_{OUT}}{I_{OUT}} = \frac{V_{IN} - 2V_{OUT}}{2C_{FLY}F_{CLK}(V_{in}(2+\alpha) - V_{OUT}(4+\alpha+\beta))} = |_{\alpha,\beta=0} \frac{1}{4C_{FLY}F_{CLK}}, \quad (9)$$

$$V_{OUT} = I_{OUT} R_L \Rightarrow V_{OUT} = \frac{C_{FLY} F_{CLK} R_L V_{IN} (2+\alpha)}{1 + C_{FLY} F_{CLK} R_L (4+\alpha+\beta)},$$

(10)

$$F_{CLK} = \frac{V_{OUT}}{C_{FLY}R_L(V_{IN}(2+\alpha) - V_{OUT}(4+\alpha+\beta))} = \frac{P_{OUT}}{C_{FLY}V_{OUT}(V_{IN}(2+\alpha) - V_{OUT}(4+\alpha+\beta))}.$$

(11)

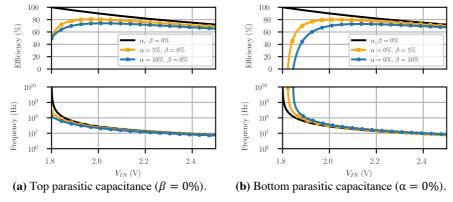

Fig. 2 shows the converter's  $\eta$  and  $F_{CLK}$  as a function of  $V_{IN}$  for different values of  $\alpha$  and  $\beta$ , with  $C_{FLY} = 100$  pF, and  $P_{out} = 1$  mW. The graphs show that while both parasitic capacitances have a negative impact on both  $\eta$  and  $F_{CLK}$ , the top parasitic capacitance has a smaller impact when compared to the bottom parasitic capacitance. Moreover, it pushes the peak efficiency for lower  $V_{IN}$  values while decreasing  $F_{CLK}$  for the same input/output ratio. This is because the charge absorbed on  $\phi_1$  is supplied to  $V_{OUT}$  on  $\phi_2$ . This acts like a parallel 1/1 converter and thus allowing the converter to work at a lower  $F_{CLK}$  value for the same input/output voltage ratio. Hence, in this

#### 264 R. Madeira and N. Paulino

topology, when implementing the  $C_{FLY}$  the highest parasitic plate should be connected as the top parasitic capacitance [9]. These equations were validated through electrical simulations in [10], [11].

Fig. 2 Efficiency as a function of  $V_{IN}$ , for  $V_{OUT} = 0.9$  V,  $C_{FLY} = 100$  pF, and  $P_{out} = 1$  mW.

Expression (8) assumes that the clock phases are long enough to allow  $C_{FLY}$  to completely charge (or discharge), however, the finite  $R_{ON}$  value of the switches cause partial charging depending on  $F_{CLK}$ , hence it will have an impact on the converter efficiency [5]. According to [5],  $R_{OUT}$  can be re-written to take in the effect of partial charging:

$$R_{OUT} = \frac{1}{\gamma} \frac{1}{4 C_{FLY} F_{CLK}}, \qquad (12)$$

this equation is identical to (9) except for a scaling factor,  $\gamma$ , which accounts for incomplete charging [5]. Let  $\tau'$  be everything else that is in the exponential before  $F_{CLK}$ ( $\tau' = 2 R_{ONtot} C_{FLY}$ ), then the number of time constant in a period sets the value of  $\gamma$ . For  $3\tau'$ , the  $\gamma$  value is 90.05%, for  $4\tau'$ , it is 96.40%, and for  $5\tau'$  it is 98.66%. Thus, for values lower than  $4\tau'$ , the value of  $\gamma$  drops significantly. Hence,  $4\tau'$  offers a good compromise point for sizing the converter switches without having a significant impact on the converter's efficiency. The  $4\tau'$  allows to size the switches  $R_{ON}$  and thus determining the transistor's W. This allows to determine the power required to charge the gate switches' parasitic capacitance ( $C_{GG}$ ), which will also impact the converter's efficiency.

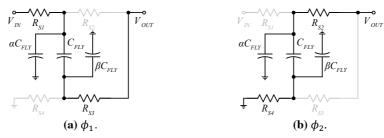

Fig. 3 Simplified schematic of the converter with the switches replaced by  $R_{ON}$ .

Fig. 3 shows the converter's schematic with its ON switches replaced by the respective  $R_{ON}$ . Both  $\phi_1$  and  $\phi_2$  have the same time constant given by:

$$\tau = R_{ONtot} C_{FLY} = \frac{1}{2F_{CLK}}, \qquad (13)$$

where  $R_{ON_{tot}} = R_{ON_{S1}} + R_{ON_{S2}}$  is the total resistance value of switches in series per phase. Assuming that  $R_{ON_{S1}} = R_{ON_{S2}} = R_{ON}$  which means that  $R_{ON} = R_{ON_{tot}}/2$ , then, the  $R_{ON}$  value for the  $4\tau'$  operation point is given by

$$R_{ON_{total}} = \frac{1}{4\tau'} = \frac{1}{8 C_{FLY} F_{CLK}} \Rightarrow R_{ON} = \frac{1}{16 C_{FLY} F_{CLK}}.$$

(14)

For small drain-to-source voltages ( $V_{DS} \ll V_{GS} - V_{TH}$ ), the switch  $R_{ON}$  and  $C_{GG}$  are given by:

$$R_{ON} \cong \frac{L}{C_{ox}\mu_n W(V_{GS} - V_{TH})} \approx \frac{k_R}{W} , \qquad (15)$$

$$C_{GG} = C_{GD} + C_{GS} \cong WLC_{ox} + WC_{ov} \approx k_C W .$$

<sup>(16)</sup>

These equations show that  $R_{ON}$  is inversely proportional to the transistor's width (W), and that  $C_{GG}$  is directly proportional to W. Furthermore, if  $V_{GS}$ , L,  $C_{ox}$  and  $\mu_n$  are kept constant, and  $V_{DS} \ll V_{GS} - V_{TH}$ , then the previous equations can be approximated by a constant coefficient,  $k_R$  and  $k_C$ , that relates both  $R_{ON}$  and  $C_{GG}$  with W [10], [12]. Hence,  $C_{GG}$  can be given by (17). The switches' power dissipation can be determined by summing all the switches'  $C_{GG}$  and multiplying it by  $F_{CLK}$  and the switches drive voltage  $V_{SW}$  squared, as shown in equation (19). Notice that  $P_{SW}$  is given by the sum of the  $k_R$  and  $k_C$  coefficients of each switch, where N is the total number of switches, where  $K_{SW} = k_{C_1} k_{R_1} + k_{C_2} k_{R_2} + \cdots + k_{C_N} k_{R_N}$ .

$$C_{GG} = \frac{K_R K_C}{R_{ON}} = 16 \, k_C \, k_R \, C_{FLY} \, F_{CLK} \, , \tag{17}$$

$$P_{SW} = \left(C_{GG_{S1}} + C_{GG_{S2}} + C_{GG_{S3}} + C_{GG_{S4}}\right) F_{CLK} V_{SW}^2 =$$

(18)

$$= 16 \left( k_{C_1} k_{R_1} + \dots + k_{C_N} k_{R_N} \right) C_{FLY} F_{CLK}^2 V_{SW}^2 = 16 K_{SW} C_{FLY} F_{CLK}^2 V_{SW}^2 .$$

(19)

The effect of  $P_{SW}$  can now be added to the converter's efficiency, resulting in

$$\eta = \frac{P_{OUT}}{P_{IN} + P_{SW}} = \frac{V_{OUT} (V_{IN} (\alpha + 2) - V_{OUT} (\alpha + \beta + 4))}{16 F_{CLK} V_{OUT}^2 K_{SW} + V_{IN}^2 (\alpha + 1) - V_{IN} V_{OUT} (\alpha + 2)}.$$

(20)

Due to the  $F_{CLK}^2$  in (19),  $F_{CLK}$  does not cancel out in (20). Thus, replacing  $F_{CLK}$  by (11) and considering that  $C_{FLY}$  can be given by the the capacitance area  $A_c$  times  $C_{den}$  of the device chosen to implement it, e.g. 10 fF/µm<sup>2</sup> in the MOS capacitor. Then,  $C_{FLY}$  can be re-written by  $C_{FLY} = A_c \times C_{den}$ . This gives  $\eta$  as a function of  $P_{OUT}$  per capacitance area, i.e. power density, as shown below.

#### 266 R. Madeira and N. Paulino

$$\eta = \frac{V_{OUT} \left( V_{IN} \left( \alpha + 2 \right) - V_{OUT} \left( \alpha + \beta + 4 \right) \right)}{V_{IN}^2 \left( \alpha + 1 \right) - V_{IN} V_{OUT} \left( \alpha + 2 \right) + \frac{16 K_{SW} P_{OUT} V_{OUT}}{A_C C_{den} \left( V_{IN} \left( 2 + \alpha \right) - V_{OUT} \left( 4 + \alpha + \beta \right) \right)}}.$$

(21)

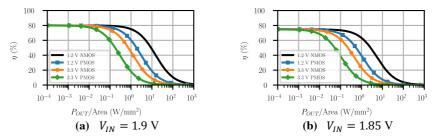

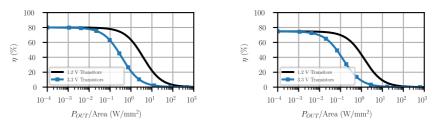

The equation above allows to determine the converter's efficiency as a function of the power density for a given  $V_{IN}$  and  $V_{OUT}$ , and for a given  $K_{SW}$ , which depends on the type of transistors chosen to implement the switches. Considering four different cases, where the transistors are all implemented by 1.2 V ( $k_R = 577.40 \ \Omega \cdot \mu m^2$  and  $k_C =$ 1.34 fF/ $\mu$ m<sup>2</sup>) and 3.3 V ( $k_R = 5337.56 \,\Omega \cdot \mu$ m<sup>2</sup> and  $k_C = 1.77 \,\text{fF}/\mu$ m<sup>2</sup>) NMOS transistors, 1.2 V ( $k_R = 2709.51 \,\Omega \cdot \mu m^2$  and  $k_C = 1.41 \,\text{fF}/\mu m^2$ ) and 3.3 V ( $k_R =$ 20570.40  $\Omega \cdot \mu m^2$  and  $k_c = 1.95 \text{ fF}/\mu m^2$ ) PMOS transistors, the  $k_R$  and  $k_c$  were taken for a  $V_{GS} = 0.9$  V through electrical simulations. Fig. 4 (a) and (b) show the efficiency (21) as a function of the power density for  $V_{SW} = V_{OUT} = 0.9$  V and for  $C_{FLY}$ implemented by a PMOS transistor ( $C_{den} = 10 \text{ fF}/\mu m^2$ ,  $\alpha = 4.5 \%$ , and  $\beta \approx 0 \%$ ). As expected, the graph clearly show that 1.2 V transistors are preferable in comparison with 3.3 V transistors. Furthermore, 1.2 V NMOS transistors allow maximizing the efficiency and power density. However, 1.2 V transistors may not be an option if their voltages exceed the transistor's breakdown voltage. Moreover, 1.2 V NMOS requires  $V_{GS} > V_{th}$ , which in the case switch  $S_1$  it would require a gate voltage higher than  $V_{IN}$ . Hence, choosing to implement  $S_1$  with a 1.2 V PMOS transistor can be a good compromise given the complexity of the NMOS driver would require.

Fig. 4 Converter's  $\eta$  as a function of  $P_{OUT}/A_c$  for different switches' implementation with  $V_{OUT} = 0.9$  V.

Fig. 5 (a) and (b) show the efficiency (21) as a function of the power density with  $S_{1,2,3}$  implemented with PMOS transistors and  $S_4$  with an NMOS transistor,  $C_{FLY}$  implemented with a PMOS transistor, and for  $V_{OUT} = 0.9$  V. The graphs show that depending on the input voltage limit, the maximum power density, whilst keeping efficiency constant, is within the 10 to 100 mW/mm<sup>2</sup>, depending if either 1.2 V or 3.3 V transistors are used.

A Simple Analysis to Determine the Limits of a CMOS Technology 267

(a)

$$V_{IN} = 1.9 \text{ V}$$

(b)  $V_{IN} = 1.85 \text{ V}$

Fig. 5 Converter's  $\eta$  as a function of  $P_{OUT}/A_c$  with  $S_{1,2,4}$  implemented with PMOS transistor and  $S_3$  with NMOS transistor, for  $V_{OUT} = 0.9$  V.

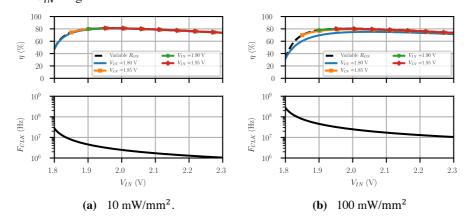

It is important to notice that once the switch is sized, the switches'  $R_{ON}$  is fixed throughout the whole  $V_{IN}$  range. In the previous graphs, the switch's  $R_{ON}$  was modified according to the  $V_{IN}$  value. In a real scenario, the converter's minimum  $V_{IN}$  value must be fixed, which sets the minimum  $R_{ON}$  value. Hence, the previous analysis is used to set  $R_{ON_{Min}}$  and then  $\eta$  is recalculated using the constant  $R_{ON_{Min}}$  value throughout the whole  $V_{IN}$  range.

Fig. 6 Converter's  $\eta$  with both the  $C_{FLY}$  and the switches' parasitic capacitances for a fixed  $R_{ON}$  value determined by the minimum  $V_{IN}$  value of the converter, for  $V_{OUT} = 0.9$  V.

Fig. 6 (a) and (b) show  $\eta$  recalculated using the  $R_{ON}$  calculated for different  $V_{IN}$ , for 10 mW/mm<sup>2</sup> and 100 mW/mm<sup>2</sup>. The efficiency values after  $V_{IN_{limit}}$  are not drawn because  $F_{CLK}$  increases beyond the  $4\tau'$  limit resulting in incomplete settling, making the equation no longer valid. These graphs show that as  $V_{IN_{limit}}$  gets closer to the voltage CR there is a significantly impact on  $\eta$ , especially at high power density values, such as 100 mW/mm<sup>2</sup>. Hence, avoiding working close to the CR voltage value (1.8) is recommend because the value of  $R_{ON}$  is extremely low. Furthermore, the frequency increases rapidly close to the CR voltage value, hence any deviation from that point would cause  $V_{OUT}$  to rapidly deviate from the 0.9 V target. Nonetheless, the previous analysis with the variable  $R_{ON}$  and with fixed  $R_{ON}$  are quite similar when working under the maximum power density (<100 mW/mm<sup>2</sup>) and far enough from the CR voltage value ( $V_{IN} > 1.85$ ). The efficiency plot should be analyzed together with  $F_{CLK}$  because, as Fig. 6 (b) shows, to achieve a power density of 100 mW/mm<sup>2</sup> the converter must work at frequencies of 10 to 100 MHz, which adds complexity to the system design, mainly the clock generator and the switch drivers. Hence lower power densities, such has the ones in Fig. 6 (a) may be preferable, due to the lower  $F_{CLK}$  value.

### 4 Conclusions

This paper describes a theorical analysis that allows characterizing the performance of an SC DC-DC converter for a given technological node. In this case, the 130 nm CMOS technology was chosen to implement a 1/2 SP SC DC-DC converter for converting an input voltage range of 2.3 to 1.8 V to an output voltage of 0.9 V. The results show that with this topology and technology the maximum efficiency would be around 80% and the power density per area in the range of 10 to 100 mW/mm<sup>2</sup>, depending on the transistors chosen to implement the passive devices.

Acknowledgments. This work was supported by the Portuguese Foundation for Science and Technology under a Ph.D. Grant (SFRH/BD/115543/2016), and UIDB/00066/2020 (CTS – Center of Technology and Systems).

### References

- S. Abdelwahab, B. Hamdaoui, M. Guizani, and A. Rayes, "Enabling Smart Cloud Services Through Remote Sensing: An Internet of Everything Enabler," *IEEE Internet Things J.*, vol. 1, no. 3, pp. 276–288, Jun. 2014.

- X. Liu, K. Ravichandran, and E. Sanchez-Sinencio, "A Switched Capacitor Energy Harvester Based on a Single-Cycle Criterion for MPPT to Eliminate Storage Capacitor," *IEEE Trans. Circuits Syst. I Regul. Pap.*, vol. 65, no. 2, pp. 1–11, Feb. 2017.

- S. Bang, A. Wang, B. Giridhar, D. Blaauw, and D. Sylvester, "A fully integrated successive-approximation switched-capacitor DC-DC converter with 31mV output voltage resolution," in *Digest of Technical Papers - IEEE International Solid-State Circuits Conference*, 2013, vol. 56, no. June 2009, pp. 370–371.

- S. Bang *et al.*, "A Successive-Approximation Switched-Capacitor DC–DC Converter With Resolution of for a Wide Range of Input and Output Voltages," *IEEE J. Solid-State Circuits*, vol. 51, no. 2, pp. 543–556, Feb. 2016.

- R. Harjani and S. Chaubey, "A unified framework for capacitive series-parallel DC-DC converter design," in *Proceedings of the IEEE 2014 Custom Integrated Circuits Conference*, 2014, pp. 1–8.

- H. P. Le, S. R. Sanders, and E. Alon, "Design Techniques for Fully Integrated Switched-Capacitor DC-DC Converters," *IEEE J. Solid-State Circuits*, vol. 46, no. 9, pp. 2120– 2131, Sep. 2011.

- A. Sarafianos and M. Steyaert, "Fully Integrated Wide Input Voltage Range Capacitive DC-DC Converters: The Folding Dickson Converter," *IEEE J. Solid-State Circuits*, vol. 50, no. 7, pp. 1560–1570, Jul. 2015.

- S. S. Kudva and R. Harjani, "Fully Integrated Capacitive DC–DC Converter With All-Digital Ripple Mitigation Technique," *IEEE J. Solid-State Circuits*, vol. 48, no. 8, pp. 1910–1920, Aug. 2013.

- R. Madeira and N. Paulino, "Improving the efficiency of a 2:1 SC DC-DC converter using the parasitic capacitances," in 2015 Conference on Design of Circuits and Integrated Systems (DCIS), 2015, pp. 1–5.

- H. Serra, R. Madeira, and N. Paulino, "Analysis of a Multi-Ratio Switched Capacitor DC-DC Converter for a Supercapacitor Power Supply," in *Technological Innovation for Cloud-Based Engineering Systems*, 2015, pp. 477–485.

- 11. R. Madeira and N. Paulino, "Analysis and implementation of a power management unit with a multiratio switched capacitor DC-DC converter for a supercapacitor power

A Simple Analysis to Determine the Limits of a CMOS Technology 269

supply," *Int. J. Circuit Theory Appl.*, vol. 44, no. 11, pp. 2018–2034, Nov. 2016. C. Carvalho, "CMOS Indoor Light Energy Harvesting System for Wireless Sensing," Faculdade de Ciências e Tecnologia, 2014. 12.