# Robust FinFET Schmitt Trigger Designs for Low Power Applications

Leonardo B. Moraes, Alexandra Lackmann Zimpeck, Cristina Meinhardt,

Ricardo Reis

## ▶ To cite this version:

Leonardo B. Moraes, Alexandra Lackmann Zimpeck, Cristina Meinhardt, Ricardo Reis. Robust Fin-FET Schmitt Trigger Designs for Low Power Applications. 27th IFIP/IEEE International Conference on Very Large Scale Integration - System on a Chip (VLSI-SoC), Oct 2019, Cusco, Peru. pp.45-68, 10.1007/978-3-030-53273-4\_3. hal-03476603

# HAL Id: hal-03476603 https://inria.hal.science/hal-03476603

Submitted on 13 Dec 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

## Robust FinFET Schmitt Trigger Designs for Low Power Applications

Leonardo B. Moraes<sup>1</sup>, Alexandra L. Zimpeck<sup>2</sup>, Cristina Meinhardt<sup>3</sup>, and Ricardo Reis<sup>1</sup>

<sup>1</sup> Instituto de Informática - PGMicro Universidade Federal do Rio Grande do Sul - UFRGS, Brazil

<sup>2</sup> Programa de Pós-Graduação em Engenharia Eletrônica e Computação <sup>3</sup> Universidade Católica de Pelotas - UCPEL, Brazil

<sup>4</sup> Departamento de Informática Aplicada e Estatística Universidade Federal de Santa Catarina - UFSC, Brazil {lbmoraes,cmeinhardt,reis}@inf.ufrgs.br alexandra.zimpeck@ucpel.edu.br

Abstract. The IoT development alongside with the more pronounced impact of process variability in modern technology nodes, is the central reason to control variability impact. Given the broad set of IoT devices running on battery-oriented environments, energy consumption should be minimal and the operation reliable. Schmitt Trigger inverters are frequently used for noise immunity enhancement, and have been recently applied to mitigate radiation effects and variability impact. Yet, Schmitt Trigger operation at nominal voltage still introduces high deviation on power consumption. Thus, the main contribution of this work is to identify the relationship between transistor sizing, supply voltage, energy, and process variability robustness to achieve a minimal energy consumption circuit while keeping robustness. On average, scenarios with a lower supply voltage applied on layouts with a smaller number of fins, presented adequate robustness in high variability scenarios. Exploring voltage and transistor sizing made possible a reduction of about 24.84% on power consumption.

**Keywords:** Process Variability Mitigation  $\cdot$  Schmitt Trigger  $\cdot$  Low Power  $\cdot$  FinFET technology

#### 1 Introduction

Ultra-low Power (ULP) circuits are widely applied in various portable electronics applications such as cellular phones, bio-medical assistance devices and sensing networks. The ULP designs rise, alongside battery technology improvements, have provided us with portable, powerful and useful equipment for our daily routine, with wireless communication making information available anytime and anywhere [1][2]. One of the most proeminent ULP applicants is the Internet of Things (IoT) industry, determining technology development and industry tendencies.  $\mathbf{2}$

As IoT devices emerged new kinds of applications have surfaced as well. From improving maintenance for all sorts of facilities, to sensor in remote areas and even automobile applications. However IoT applications still depend on an energy source, with battery-oriented applications being the most prominent. Given the limited life cycle of batteries, self-sufficient systems have appeared in order to alleviate the power consumption dilemma [2]. Given so, an IoT application will always be restricted by its power budget, with devices that can perform their functionality under heavy power constraints being essential [3]. The ideal circuit for ULP applications is the one that can perform a given task while consuming the least amount of energy. Such circuits might be achieved under transistor sizing and supply voltage tuning, being technology and application-dependent [2].

Nevertheless, the technology advance over transistor sizing has increased the density of chips and the challenges related to the manufacturing process, for example, the process variability and aging effects, the higher power consumption due to larger leakage currents, and the increase in the radiation-induced soft errors [4]. Multigate devices, as the Fin Field Effect Transistor (FinFET), have been proposed to help overcome some of those issues. The structure of FinFETs shows superior channel control due to the reduced short-channel effects (SCE) and diminished Random Dopant Fluctuation (RDF) effect due to the fully depleted channel [5]. However, process variability is one of the major challenges in nanometer technology, even on FinFET designs [6]. At deep nanotechnology nodes, each chip may show a distinct behavior due to process variations during the lithography steps in the manufacturing process. These variations exert influence over the metrics of the circuit such as performance and power consumption, which can bring unpredictable circuit degradation, making them unsuitable from its expected operation regime [4][7].

This work aims to explore a low power solution considering the effects of process variability in the Schmitt Trigger (ST) designs. ST circuits are widely applied on low power applications due to its noise immunity, and, recently have been considered for process variability mitigation on nanometer technologies. This set of data can provide relevant information for ULP designers, and also for other low power applications that need to manage process variability impact. Thus, the main contribution of this work is an in-depth evaluation of the influence of different factors on the ST design, considering: 1) multiple combinations of supply voltages; 2) different levels of process variability; and 3) the variable transistor sizing relation (number of fins). The experiments analysis the impact of these factors on the maximum achievable frequency within a failure threshold, the trade-off among these parameters and power consumption.

Next section aims to give more context to this work, commenting on related works and the main differences and contributions of this work in comparison. Section III gives a more in-depth explanation about variability and its several factors and phenomena. Section IV introduces the FinFET technology and the variability influence over it. Section V the main aspects of ST are shown as well its robustness enhancing capabilities. The methodology adopted to allow all the evaluations is explained in Section VI. The results are discussed in Section VII and finally, Section VIII presents the main conclusions.

### 2 Related Work

Many works evaluate the effects of Process, Voltage and Temperature (PVT) variability on circuits and devices, but few works consider the effects for ULP designs.

Some works address theses issues focusing on the yield improvement. In [4] is developed a mathematical methodology for increase the yield considering aging, and PVT variability. With such method, the circuit sizing was optimized and, obeying some performance and power constraints, it was possible to achieve an increase from about 40% to 99% yield. [8] provides a characterization of the effects of open defects on nanoscale CMOS gates and circuits. It shows the difference on output value for several circuits, technology nodes and most important under the influence of PVT variability. In [9] is shown the implication of PVT variations on subthreshold device and circuit performance metrics. It was found that a  $\pm 10\%$  on several transistor parameters could introduce up to a 77% variation in Energy, or Power-Delay Product (PDP). In this context, the use of STs is being investigated as an effective method for increasing the on-tooff current ratio, and consequently, for mitigating the process variation effects [3] on subthreshold operating systems.

Other works have evaluating the impact on arithmetic circuits, mainly on Full-Adders (FA). In [10] the effects of PVT variability in different Full Adder (FA) designs are investigated. Both Transmission Gate Adder (TGA) and Transmission Function Adder (TFA) architectures showed acceptable behavior under PVT variability with the lowest power consumption sensibility amongst the tested FAs, reaching about 11x smaller in comparison with Complementary Pass Transistor Logic (CPL) FA. In [11] simulations were performed on several FA circuits considering Carbon Nanotube Field Effect Transistor (CNFET) and bulk Complementary Metal-Oxide-Semiconductor (CMOS) technology. Results show that the TGA is the most robust circuit with its CNFET version providing up to 3x less variations. [12] presents a study about the delay variability caused by supply variations in the TGA. The experiments were performed at layout level. It showed that lower supply voltages bring more delay variability to the circuit with the TGA presenting worse results in comparison to static logic.

Given the energy constraints of ULP applications and the variability impact on recent nodes, the ST circuit has been pointed as an circuit-level alternative. The classical ST has been employed as a key element for several ULP circuits [13–16] and for variability mitigation, mainly attenuating the deviation on the power consumption. Schmitt Trigger was applied replacing internal inverters of full adders in [17], where spreads in major metrics were successfully limited. Also, the same experiment was executed at electrical and layout levels considering FinFET technology, and showed a considerable decrease in overall variability 4 L. B. Moraes, A. L. Zimpeck, C. Meinhardt and R. Reis

impact on metrics [18][19]. However, with a considerable increase in delay and power consumption.

It is important to highlight that the mentioned works do not consider analysis at the layout-level in modern technology nodes. Additionally, most works do not consider such a combination of variables and even if they do, the analysis is often performed considering the circuit under the influence of only one of the variables at a time. This work presents a layout-level analysis, considering all parasitics and electrical behavior related to transistor placement and routing, as well as all considered variables exerting their influence at the same time, as would occur on a real scenario.

#### 3 On Variability

As technology scaling advanced, decreasing the transistor dimensions, the ratio between device geometrical parameters and the atom-size itself have been shrinking. Multiple techniques have been developed to reduce the loss of precision due to the manufacturing process at different end-of-lines. However, as the quantum-mechanical limit approaches, manufacturing-induced imprecision impact rises [20].

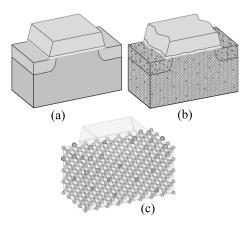

Variability consists of characteristic deviations, internal or external to the circuit, which can determine its operational features and can be divided by three types concerning its sources: Environmental Factors - External factors to the circuits e.g. temperature and supply voltage variations [7,21], Reliability Factors - related to the aging process e.g. Negative Bias Temperature Instability (NBTI), electromigration, dielectric breakdown and Hot Carrier Injection (HCI) [22–25, 7, 21] and Physical Factors - caused by the manufacturing process, consequence of imprecision in the manufacturing process which can be systematic, design dependent or random [21, 26–32]. Fig. 1, depicts the transistor intrinsic variability.

Despite the multiple advantages of new technologies, the atom scale makes process variability one of the most relevant challenge. FinFET devices have been investigated about the variability impact and the next subsection introduces the main concepts about FinFET technology to understand the variability impact on this device.

#### 3.1 FinFET Technology and Variability Impact

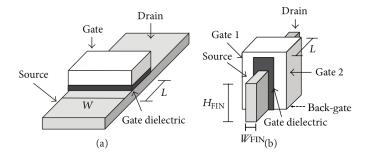

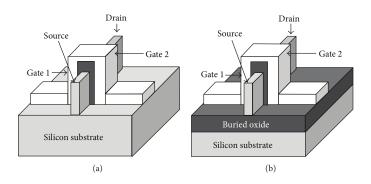

The FinFET main geometric parameters are the gate length  $(L \text{ or } L_G)$ , fin width  $(W_{FIN}, T_{FIN} \text{ or } T_{SI})$ , fin height  $(H_{FIN})$  and Oxide Thickness  $(T_{OX})$ . FinFET transistors can be built on a traditional bulk or on a Silicon on Insulator (SOI) substrate with a conducting channel that rises above the level of the insulator, creating a thin silicon structure, the gate, as shown in Fig. 2 and Fig. 3.

The channel being surrounded from three dimensions by the gate results in a superior control, reduced SCE and RDF effect due to the fully depleted channel that causes less sensitivity to process variations [34]. FinFETs also present

Fig. 1. Levels of abstraction from a ideal transistor towards a realistic concept. (a) Depicts a the current approach of semiconductor device simulation. (b) Depicts a 20-nm Metal-Oxide-Semiconductor FET (MOSFET). (c) Depicts a 4-nm MOSFET. [28].

Fig. 2. Structural comparison between (a) planar MOSFET and (b) FinFET transistors. Modified from [33].

Fig. 3. Structural comparison between (a) bulk and (b) SOI FinFETs [33].

5

$\mathbf{6}$

relative immunity to gate Line Edge Roughness (LER), a major source of variability in planar nanoscale FETs [35]. Overall, the major sources of variability expected for FinFETs are the  $L_G$ ,  $W_{FIN}$ ,  $H_{FIN}$  and gate WF [36]. Amongst all variability sources, it is shown that the  $V_t$  is mainly set by the gate WF, with fluctuations having a direct impact on its limits [37–40].

Given the challenges intrinsic to the adoption of high-k dielectrics in order tackle the increasing gate leakage due to the scaling down of gate oxide, a metal gate was adopted on FinFET devices [41–44]. Metals exist *in natura* in the form of crystals where each atom has several bonds with adjacent atoms. Although, due to defects and disorientation, several crystals are formed, with "grain boundaries" between regions of regularity (crystal grains) in the metal [45].

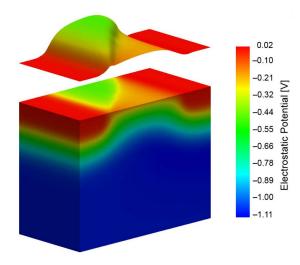

The electrostatic potential (e.g.  $V_t$ ) varies depending on each grain boundary, as shown in Fig. 4. At Table 1 a example of possible orientation, probability and WF is given. Between several technology nodes - FD-SOI, Bulk and FinFET the latter showed the lowest  $V_t$  variation due to the much larger gate area [45].

Fig. 4. Electrostatic potential in a generic 30-nm MOSFET with the surface potential shown below. The metal gate has two grains with the grain boundary diagonally across the channel [46].

Table 1. Metal orientation, probability and related work function [46].

| <b>Orientation Probability Work Function</b> |     |         |  |  |  |  |  |  |

|----------------------------------------------|-----|---------|--|--|--|--|--|--|

| <200>                                        | 60% | 4.6  eV |  |  |  |  |  |  |

| <111>                                        | 40% | 4.4 eV  |  |  |  |  |  |  |

#### 4 Schmitt Trigger for Process Variability Mitigation

Schmitt Trigger circuits present a hysteresis characteristic. Hysteresis exists in the presence of two switching threshold voltages  $(V_t)$ . If the input level is inside the hysteresis interval, the ST will not switch. Such characteristic provides a higher static noise margin (SNM) in comparison to traditional inverters, ensuring a high noise immunity. Deviations in physical parameters became alarming at ultra-deep sub-micron (UDSM) nodes due to the following supply voltage scaling, making the circuits more susceptible to noise and electromagnetic interference due to the deterioration in SNM [48].

There are several ST topologies proposed in the literature. In [49], three threshold adjustable ST circuits are presented, wher two are semi-adjustable (only one threshold level can be adjusted) and one are a fully adjustable (both threshold levels can be adjusted) topology. All circuits presents small chip area, and very low static power consumption. A higher performance ST is proposed in [50] where, by a different design, a smaller load capacitor value is achieved, decreasing the slew rate of the ST internal node.

In [51] a low-power ST is proposed as well by forward body biasing, decreasing the  $V_t$ , improving performance and decreasing the short circuit current. [52] proposes a 10T ST which its hysteresis interval does not depend on transistors width/length ratios being, consequently, more robust to process variations.

In [53] a ST with a programmable hysteresis is proposed. The programmable hysteresis is achieved by adding a P and N transistors in series with the 6T ST  $P_F$  and  $N_F$  transistors, respectively, both receiving the same gate signal. A low-power ST is proposed at [54] with low short circuit current achieved by the presence of only one path to each power rail, being recommended for low power, very low frequency applications. Additionally, [55] proposes a low-power ST by having only one transistor transmitting (at stable output values), considerably reducing power consumption.

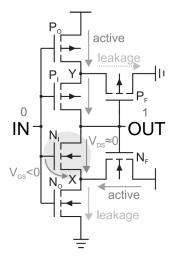

As show in Fig. 5, this work explores a traditional ST topology, where the major difference from the most popular versions is the presence of  $P_F$  and  $N_F$  transistors [56]. These transistors are responsible for a feedback system. For example, if the output is at a high level, the  $N_F$  is closed, pulling the node X to a high potential, and forcing the drain-source voltage of transistor  $N_I$  almost zero and its gate-source voltage into the negative region. This kind of arrangement reduces the leakage current  $N_I$  exponentially, increasing the  $I_{on}/I_{off}$  current ratio, minimizing the output degradation [16].

The main effect of process variability on ST circuits is a shift in the Voltage Transfer Curve (VTC) due to the threshold voltage variation. Mostly, the input voltage, where a device starts transmitting current, is directly dependent on the  $V_t$ . Given so, the variability impact onto the VTC is reduced as a result of the

Fig. 5. ST inverter leakage suppression [16].

high influence of the gate-source voltage of the ST inner transistors  $(N_I \text{ and } P_I)$  over its switching point [16].

#### 5 Methodology

8

To present an broad exploration of power consumption and the process variability effects on the ST characteristics, this work evaluates: 1) ST circuit operating at multiple combinations of supply voltages; 2) the impact of different levels of process variability; 3) the influence of the transistor sizing exploring devices with different number of fins, all at the same time composing over 175 possible scenarios. The impact of these parameters on the maximum achievable frequency within a failure threshold will be analysed.

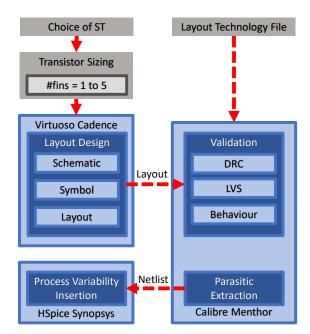

The design flow is shown at Figure 6. The project was divided into two main steps: the layouts designing and electrical simulations. After finishing the layout design process, each layout passed through validation which consisted of a Design Rule Checking (DRC) to detect if the layout obeys the technology geometry restrictions and layer rules, Layout Versus Schematic (LVS) where layout and schematic are compared to detect their equivalence (same nodes and nets) and a Behavioral test, in order to observe if the circuit works as expected at nominal operation.

#### 5.1 Layout Design

All ST layouts were designed on the Virtuoso tool from Cadence® with the process design kit (PDK) of 7-nm FinFET (ASAP7) from the Arizona State University in partnership with ARM [57]. This PDK was chosen due to a realistic design conjecture regarding the current design competencies and for being

9

Fig. 6. Design flow of the experiments.

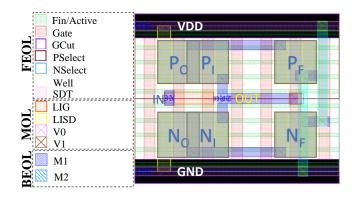

available for academic use. FinFET technologies present the width quantization aspect [58]. With a 27nm fin pitch, a high-density layout is achieved with 3-fins transistors. Otherwise, for a higher fin count, there is a lower density and routing complexity [59]. The main PDK rules and lithography assumptions considered in this work are shown in Table 2. The main layers and the 3-fin ST are shown in Fig. 7.

Table 2. Key layer lithography assumptions, widths and pitches [57].

| Layer               | Lithography | Width/drawn (1 | nm) Pitch (nm) |

|---------------------|-------------|----------------|----------------|

| Fin                 | SAQP        | 6.5/7          | 27             |

| Active (horizontal) | EUV         | 54/16          | 108            |

| Gate                | SADP        | 21/20          | 54             |

| SDT/LISD            | EUV         | 25/24          | 54             |

| LIG                 | EUV         | 16/16          | 54             |

| VIA0-VIA3           | EUV         | 18/18          | 25             |

| M1-M3               | EUV         | 18/18          | 36             |

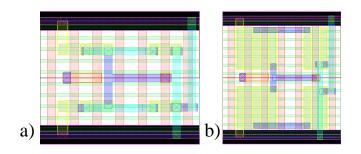

This work evaluates the ST with 1 to 5 fins. For comparison, the 1 and 5-fins layouts are shown in Fig. 8. For the layouts with 1 and 2 fins, due to the minimum active area technology restriction, it was not possible to lower the cell area in comparison to the 3-fins layout. Although considering a possible scenario, the

Fig. 7. 3-fins variant ST layout in 7nm FinFET Technology (ASAP7) [60]

Fig. 8. a) 1 and (b) 5-fins ST layouts

2 and 1-fin layouts would present a 20% and 40% reduction in area, compared to the 3-fins variant, respectively. The 3, 4 and 5-fins ST area, height and area increase are shown at Table 3.

It is important to clarify that a lower fin count does not necessarily mean an area reduction. The routability could turn into a challenge and a width of height increase would be necessary.

The ASAP7 PDK contains the manufacturing process composed by front end of line (FEOL), middle of line (MOL) and back end of line (BEOL). The layouts were developed in a continuous diffusion layer with every gate surrounding another gate in the horizontal axis. The Source-Drain Trench (SDT) connects the active area to the LISD layer. The Local-Interconnect Gate (LIG) is applied to connect the gate terminal, and Local-Interconnect Source-Drain (LISD) is used to connect the source and drain of the transistors. The function of V0 is to join the LIG and LISD to the BEOL layers. The Metal 1 (M1) is used for intra-cell routing and short connections. The Metal 2 (M2) was applied to connect the  $P_F$  and  $N_F$  drains to ground and source, respectively. For the layouts with a fin count below 3, M2 was applied to connect the source/drain of the  $P_F$  and

11

Table 3. 3, 4 and 5-fins STs area, height (in tracks of Metal 2), and the area increase corresponding to each extra fin.

| #Fins | Area $(nm^2)$ | Height (M2 Tracks) | Area increase |

|-------|---------------|--------------------|---------------|

| 3     | 131220        | 7.5                | -             |

| 4     | 157464        | 9                  | 20%           |

| 5     | 183708        | 10.5               | 40%           |

$N_F$  transistors to the X and Y layout nodes. Given the smaller area to work with, it was necessary to apply M2 in order to respect the M1 spacing rules, bringing to light one of the challenges related to a smaller layout. The M2 usage in those cases will increase the design parasitics from the neccessary extra vias connecting M1 and M2. To successfully pass the LVS step, it was necessary the addition of a TAP-cell to connect the transistors back-gates.

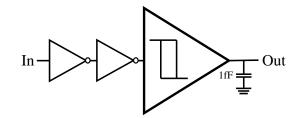

#### 5.2 Electrical Simulation

The simulations were carried out in HSPICE [61] using the netlist obtained after the physical verification flow and the parasitic extraction. The reference values from ASAP7 technology for electrical simulations are shown in Table 4. For a more realistic test-bench, it was considered a scenario where the ST receives the signal from two inverters and drives a 1fF output capacitance, as shown in Fig. 9. The same supply voltage is applied in the entire testbench. Only the ST suffers from variability, and the inverters are the same (3-fins transistors) for all experiments. All designs present in the test-bench, inverters and ST, are simulated from the extracted layouts.

| Parameter              | 7nm               |  |  |  |  |

|------------------------|-------------------|--|--|--|--|

| Nominal Supply Voltage | 0.7 V             |  |  |  |  |

| Gate Length (Lg)       | 21nm              |  |  |  |  |

| Fin Width (Wfin)       | $6.5 \mathrm{nm}$ |  |  |  |  |

| Fin Height (Hfin)      | 32nm              |  |  |  |  |

| Oxide Thickness (Tox)  | 2.1nm             |  |  |  |  |

| Channel Doping         | $1x10^{22}m^{-3}$ |  |  |  |  |

| Source/Drain Doping    | $2x10^{22}m^{-3}$ |  |  |  |  |

| Work Function          | NFET 4.372 eV     |  |  |  |  |

| WORK FUNCTION          | PFET 4.8108 eV    |  |  |  |  |

Table 4. Parameters applied in the electrical simulations [57].

The process variability evaluation was taken through 2000 Monte Carlo (MC) simulations [58] varying the WF of devices according to a Gaussian distribution considering a  $3\sigma$  deviation. This work explores the behavior of ST with variations from 1% up to 5%. For each step on WF variation, all simulations were carried

Fig. 9. Test-bench applied in all simulations [60].

from 0.1V to 0.7V supply voltage, with steps of 0.1V at a nominal temperature of 27°C. The voltage of 0.1V shows to be the technological limit to work without the loss of the hysteresis characteristic. For all experiments, it was observed maximum values, mean ( $\mu$ ), standard deviation ( $\sigma$ ) and normalized standard deviation ( $\sigma/\mu$ ) for each metric: hysteresis interval, delay, and energy, where  $\sigma/\mu$  represents the sensibility of the cell to process variability.

Due to the variability impact a circuit may present performance degradation, given that, in order to determine the maximum frequencies for the layouts evaluated, this work considers a 10% maximum failure threshold in the Monte Carlo simulations. Failures are defined as cases where a pair of operations (high-to-low and low-to-high) propagation times do not fit into the determined frequency. In the case of a number of failures above 10%, the frequency is decreased.

#### 6 Results and Discussion

This section is divided into three parts. First, a discussion concerning energy consumption where a scenario-specific analysis is performed, and different sets of fin count and supply voltage are recommended. A performance analysis (delays and maximum frequencies) will follow, presenting an analysis of the fin count and supply voltage over absolute and deviation values. And finally, the ST hysteresis interval values are presented in relation to the variability level and number of fins.

#### 6.1 Energy Consumption

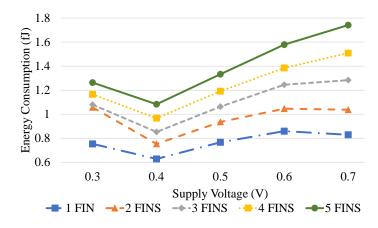

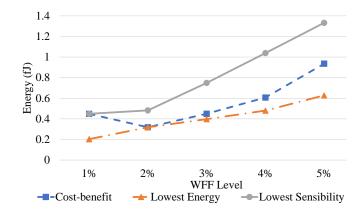

For each level of WFF explored in this work, there is a distinct ideal scenario for each kind of application. As shown in Table 5, considering the absolute energy consumption observed, the 1-fin layout showed, in all cases, the lowest. It is due to its smaller driving capability, resulting in smaller currents.

The supply voltage recommended for each scenario increases almost linearly in relation to the level of WFF variability. The 0.1V regime did not prevail as the best option across all scenarios, shows the dependency of energy consumption with propagation times. Fig. 10 shows an average between the each particular variability scenario related to the number of fins. It can be observed a difference

| WFF | Lowe   | st Energy  | Mos    | t Robust   | Cost-Benefit |            |  |

|-----|--------|------------|--------|------------|--------------|------------|--|

|     | # Fins | Supply (V) | # Fins | Supply (V) | # Fins       | Supply (V) |  |

| 1%  | 1      | 0.1        | 1      | 0.7        | 1            | 0.7        |  |

| 2%  | 1      | 0.2        | 1      | 0.7        | 1            | 0.7-0.2    |  |

| 3%  | 1      | 0.2        | 5      | 0.3        | 1            | 0.3        |  |

| 4%  | 1      | 0.3        | 5      | 0.4        | 1            | 0.4        |  |

| 5%  | 1      | 0.4        | 5      | 0.5        | 1            | 0.5        |  |

Table 5. Recommended setup by each specific scenario [60].

above 100%, between maximum and minimum, showing a higher dependence of the number of fins in determining the circuits energy consumption. Results below 0.3V did not feature the chart in order to preserve its scale, since for 0.2V and 0.1V there are a 1 and 2 orders of magnitude increase on energy consumption, respectively.

Fig. 10. Average energy consumption over supply voltage scaling [60].

Into the robustness analysis, a shift can be observed. For lower variability scenarios the setup recommended is at 1 fin layout and 0.7V for 1% and 2% WFF. From moderate to high variability (3% to 5%), the 5 fins layout gains advantage with the supply voltage scaling linearly.

The energy robustness is mainly determined by variations in the  $I_{on}$  and, consequently, the time necessary for the circuit charging/discharging. At nominal supply voltages, the  $I_{on}$  falls into the saturation region with an exponential dependence over the  $V_t$ . Given that, variations on the  $V_t$  will result in exponential variations. With the supply voltage decrease, the  $I_{on}$  falls into the linear region, diminishing the impact of  $V_t$  variations on the  $I_{on}$ .

Thus, at low variability scenarios, close-to-nominal supply voltages will not suffer from the exponential  $V_t$  dependence, weakening its effect with high current

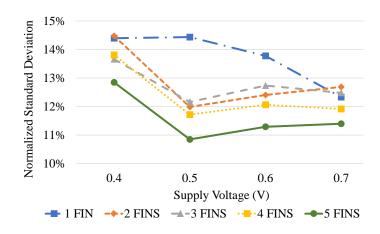

Fig. 11. Average energy consumption sensibility scaling over supply voltage [60].

peaks, small signal slopes overcharging and discharging and higher noise immunity. As variability rises, the linearity from the  $V_t$  will present an advantage, favoring smaller supply voltages. However, as variability rises again, the rise and variation in propagation times will start to determine the adequate supply voltage. Fig. 11, shows the average scaling on the impact of process variability on energy consumption. It can be seen a lower than 5% discrepancy between best and worst cases, showing the minor dependence of the number of fins in determining the circuits robustness. Results below 0.4V did not appear on the chart in order to preserve its scale. For 0.3V, 0.2V and 0.1V, maximum normalized standard deviations are 108.64%, 266.82% and 358%, respectively.

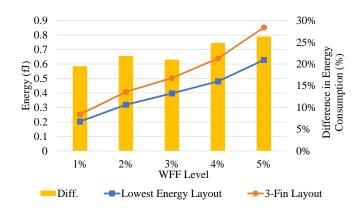

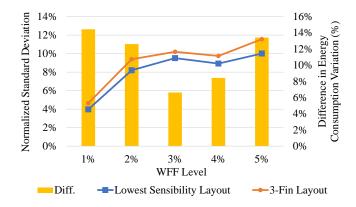

For the sake of comparison, Fig. 12 and Fig. 13 present the difference between the respective layouts with the lowest energy consumption and energy consumption variation and the traditional 3-fins layout. The highest difference was 27.85% and 14.44% for energy consumption and variability, respectively.

Considering a cost-benefit scenario, the best choice was defined by the lowest value given by the product of the energy consumption and the normalized deviation product (Energy-Deviation Product - EDP). It can be noticed a shift from a more robust layout (at 1% and 2% WFF) to a low energy layout at higher WFFs (3% to 5%). At 2% there are two supply voltages recommended since the EDP values similar. At this variability point the layout at 0.7V presents the highest robustness and acceptable energy consumption, due to the lower propagation times, while the layout operating at 0.2V presents the lowest energy consumption and acceptable energy deviation.

A comparison between the layouts with the lowest energy consumption, energy variability, and the best cost-benefit are shown in Figs. 14 and 15 in relation to energy consumption and energy variability, respectively. The energy variability of the lowest energy layout at 3% WFF is one example of why a cost-benefit analysis should be made since it shows an 11.5% lower energy consumption with a 582.47% higher sensibility.

Fig. 12. Energy consumption comparison between the layout with the lowest energy consumption and the traditional 3-fins layout at the same supply voltage [60].

Fig. 13. Energy variability comparison between the layout with the lowest sensibility and the traditional 3-fins layout at the same supply voltage [60].

#### 6.2 Propagation Delays and Maximum Frequencies

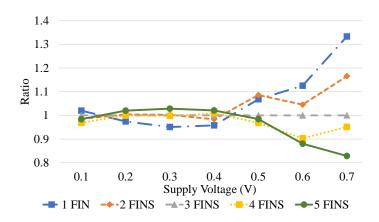

At performance scaling it can be observed a worsening on propagation times over the lowering of the supply voltage and fin count. The transistor driving capability is proportional to the fin count, given that with more fins there is a larger active area passing current, fastening the charging/discharging process. Given the area penalty, which will be discussed, the 4-fins layout only gives a 10% penalty on propagation times, being a good choice over area constraints in comparison to the 5-fins layout. The 3, 2 and 1 fins layouts bring a 42%, 92% and 268% delay increase on average, respectively.

In comparison to the traditional 3-fins layout, the 5 and 4-fins variants bring 20% and 13.612% decrease on propagation times while the 2-fins and 1-fin variants bring 27.24% and 107% delay increase, respectively.

16 L. B. Moraes, A. L. Zimpeck, C. Meinhardt and R. Reis

Fig. 14. Energy consumption comparison among the layouts with the best cost-benefit, lowest energy consumption and lowest variability sensibility [60].

Fig. 15. Energy variability comparison among the layouts with the best cost-benefit, lowest energy consumption and lowest variability sensibility [60].

For variability impact, it can be observed a tendency of lower sensibility over higher fin count at higher supply voltages. As supply voltage scales down, a lower number of fins starts to keep up with the variability robustness, as shown in Fig. 16. It can be concluded that due to the exponential relation of drain current with gate-to-source voltage, the higher fin count is capable of providing the necessary current drive at higher supply voltages. At lower supply voltages, with the drain current decreasing exponentially, the fin count impact on variability robustness is diminished.

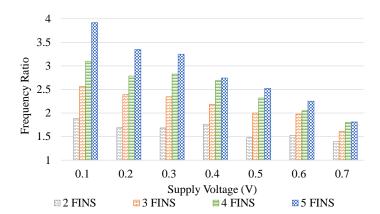

Maximum frequencies are shown at Table 6. The maximum frequencies are proportional to the supply voltage and fin count. The higher fin count allows faster charging and discharging due to a bigger active area driving current. On average, the 5 and 4-fins layouts were able to present 16% and 10.34% higher

Fig. 16. Delay sensibility ratio between layouts [60].

frequencies while the 2 and 1-fin variants showed 19.18% and 44.65% lower frequencies, in comparison to the 3-fins variant.

Fig. 17 and Fig. 18 show the average ratio between the different variability and circuits scenarios normalized in relation to the 1 Fin layout and 5% WFF scenario, respectively. It can be noticed a considerable 52.597 times ratio between low and high variability scenarios, being the main variable determining the circuit frequency. In comparison, the number of fins brings a maximum 3.917 times ratio between 5 and 1 fins layouts, exposing the advantage of a higher number of fins on low supply voltages.

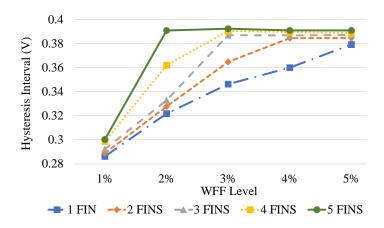

#### 6.3 Hysteresis Interval

Hysteresis is one of the major characteristics related to the circuit ability to filter noise. A higher hysteresis interval brings more robustness to the circuit. As a priority, the ratio between its value and the supply voltage should be as high as possible. The ST, at nominal operation (nominal supply voltage and no process variability), presented a maximum hysteresis interval of approximately 0.45V. Given that, considering the average absolute values of the hysteresis interval, it can be observed a difference below than 5% between the best and worst cases, considering different fin counts.

At higher supply voltages of 0.6V and 0.7V, the difference widens up reaching up to 10.76% and 25.26% between the 5-fins and 1-fin layout, respectively. Such results come from the faster charging/discharging, which decreases the signal slopes widening the circuit hysteresis interval. At lower supply voltages, a decreased number of fins is sufficient to keep the slopes low enough, presenting high hysteresis to supply voltage ratios while at higher supply voltages a lower number of fins will increase the signal slopes.

Although, there is a hysteresis interval improvement, as shown in Fig. 19, over the WFF increase as well. Such behavior happens due to the hysteresis

#### 18 L. B. Moraes, A. L. Zimpeck, C. Meinhardt and R. Reis

| WFF                      | # Fins   | Supply Voltage (V)  |                     |                    |                    |                    |                     |                   |  |  |

|--------------------------|----------|---------------------|---------------------|--------------------|--------------------|--------------------|---------------------|-------------------|--|--|

| <b>VV 1</b> , <b>1</b> , | # 1 1115 | 0.1                 | 0.2                 | 0.3                | 0.4                | 0.5                | 0.6                 | 0.7               |  |  |

|                          | 1        | 600KHz              | $15 \mathrm{MHz}$   | $350 \mathrm{MHz}$ | 2 GHz              | 8 GHz              | 12GHz               | 16GHz             |  |  |

| 1%                       | 2        | 1.1MHz              | $25 \mathrm{MHz}$   | $600 \mathrm{MHz}$ | 4 GHz              | 13 GHz             | 19GHz               | $24 \mathrm{GHz}$ |  |  |

|                          | 3        | $1.5 \mathrm{MHz}$  | $35 \mathrm{MHz}$   | $900 \mathrm{MHz}$ | $5 \mathrm{GHz}$   | $17 \mathrm{GHz}$  | 24GHz               | 29GHz             |  |  |

|                          | 4        | $1.75 \mathrm{MHz}$ | 40MHz               | 1GHz               | 6 GHz              | $19 \mathrm{GHz}$  | $27 \mathrm{GHz}$   | 33GHz             |  |  |

|                          | 5        | $2.25 \mathrm{MHz}$ | $50 \mathrm{MHz}$   | $1.2 \mathrm{GHz}$ | 6 GHz              | $21 \mathrm{GHz}$  | $30 \mathrm{GHz}$   | $35 \mathrm{GHz}$ |  |  |

|                          | 1        | 200KHz              | $5 \mathrm{MHz}$    | $150 \mathrm{MHz}$ | $1.5 \mathrm{GHz}$ | $5 \mathrm{GHz}$   | 11GHz               | $15 \mathrm{GHz}$ |  |  |

|                          | 2        | 400KHz              | 9MHz                | $250 \mathrm{MHz}$ | $2.5 \mathrm{GHz}$ | $7 \mathrm{GHz}$   | 18GHz               | 23GHz             |  |  |

| 2%                       | 3        | 600KHz              | $12.5 \mathrm{MHz}$ | $300 \mathrm{MHz}$ | $3 \mathrm{GHz}$   | $9 \mathrm{GHz}$   | $22.5 \mathrm{GHz}$ | 28GHz             |  |  |

|                          | 4        | $700 \mathrm{KHz}$  | $15 \mathrm{MHz}$   | $450 \mathrm{MHz}$ | 4 GHz              | 11GHz              | $17 \mathrm{GHz}$   | 31GHz             |  |  |

|                          | 5        | 900KHz              | 18MHz               | $500 \mathrm{MHz}$ | 4 GHz              | 12GHz              | 20GHz               | $25 \mathrm{GHz}$ |  |  |

|                          | 1        | $100 \mathrm{KHz}$  | 2 MHz               | $60 \mathrm{MHz}$  | $1 \mathrm{GHz}$   | 4 GHz              | 8 GHz               | 14GHz             |  |  |

|                          | 2        | $200 \mathrm{KHz}$  | 3MHz                | $100 \mathrm{MHz}$ | $1.5 \mathrm{GHz}$ | 6 GHz              | 11GHz               | 20GHz             |  |  |

| 3%                       | 3        | $200 \mathrm{KHz}$  | $5 \mathrm{MHz}$    | $125 \mathrm{MHz}$ | 2 GHz              | 8 GHz              | 14GHz               | 19GHz             |  |  |

|                          | 4        | $300 \mathrm{KHz}$  | 6 MHz               | $150 \mathrm{MHz}$ | $2.5 \mathrm{GHz}$ | 9 GHz              | 16 GHz              | $21 \mathrm{GHz}$ |  |  |

|                          | 5        | $400 \mathrm{KHz}$  | $6 \mathrm{MHz}$    | $150 \mathrm{MHz}$ | $2.5 \mathrm{GHz}$ | $10 \mathrm{GHz}$  | $17 \mathrm{GHz}$   | $23 \mathrm{GHz}$ |  |  |

|                          | 1        | $50 \mathrm{KHz}$   | 800KHz              | $25 \mathrm{MHz}$  | $500 \mathrm{MHz}$ | $3 \mathrm{GHz}$   | 6 GHz               | 13GHz             |  |  |

|                          | 2        | $75 \mathrm{KHz}$   | $1.5 \mathrm{MHz}$  | 40MHz              | 900MHz             | 4 GHz              | 8GHz                | $15 \mathrm{GHz}$ |  |  |

| 4%                       | 3        | $125 \mathrm{KHz}$  | 2 MHz               | $50 \mathrm{MHz}$  | 1GHz               | 6 GHz              | $12.5 \mathrm{GHz}$ | $18 \mathrm{GHz}$ |  |  |

|                          | 4        | $150 \mathrm{KHz}$  | $2.5 \mathrm{MHz}$  | $60 \mathrm{MHz}$  | $1.1 \mathrm{GHz}$ | $7 \mathrm{GHz}$   | $14 \mathrm{GHz}$   | $20 \mathrm{GHz}$ |  |  |

|                          | 5        | $150 \mathrm{KHz}$  | $2.5 \mathrm{MHz}$  | $60 \mathrm{MHz}$  | $1.4 \mathrm{GHz}$ | $7.5 \mathrm{GHz}$ | $15 \mathrm{GHz}$   | $22 \mathrm{GHz}$ |  |  |

|                          | 1        | $15 \mathrm{KHz}$   | $350 \mathrm{KHz}$  | 9MHz               | $250 \mathrm{MHz}$ | $2 \mathrm{GHz}$   | $5 \mathrm{GHz}$    | 11GHz             |  |  |

|                          | 2        | 40KHz               | $600 \mathrm{KHz}$  | $10 \mathrm{MHz}$  | $350 \mathrm{MHz}$ | $2.5 \mathrm{GHz}$ | 8 GHz               | $14 \mathrm{GHz}$ |  |  |

| 5%                       | 3        | $50 \mathrm{KHz}$   | 800KHz              | $18 \mathrm{MHz}$  | $450 \mathrm{MHz}$ | 4 GHz              | $10 \mathrm{GHz}$   | $17 \mathrm{GHz}$ |  |  |

|                          | 4        | 90KHz               | 1MHz                | $20 \mathrm{MHz}$  | $500 \mathrm{MHz}$ | $5 \mathrm{GHz}$   | $12 \mathrm{GHz}$   | $19 \mathrm{GHz}$ |  |  |

|                          | 5        | 80KHz               | 1MHz                | $20 \mathrm{MHz}$  | $500 \mathrm{MHz}$ | $5 \mathrm{GHz}$   | $12.5 \mathrm{GHz}$ | $20 \mathrm{GHz}$ |  |  |

Table 6. Each scenario respective maximum frequency.

interval dependency over the PFET and NFET threshold voltages [56]. This means that lower WF decreases the NFET threshold, while higher WF will increase the NFET threshold, and vice-versa for PFET devices. Therefore, the ideal scenario would be with negative WFF for the PFET devices and positive WFF for the NFET devices. Though, the NFET term also depends on the  $\beta$ -ratio (ratio between the transistor emitter and base current) of the PFET and NFET transistors. Giving an estimate based on saturation and off-currents from [57], the NFET threshold voltage influence on the final hysteresis interval is almost 40% higher, in comparison to its counterpart.

As shown in Table 7, the only cases with considerable hysteresis worsening happens when the NFET WF is above 2%, while the subset showing improvements includes most of the possible scenarios. And since the hysteresis voltage will never be higher than the supply voltage, the average tends to the supply voltage value.

60 50 Frequency Ratio 40 30 20

0.3

**→-**2% WFF

Fig. 17. Average frequency ratios between different layouts.

Fig. 18. Average frequency ratios between different WFF scenarios.

0.4 Supply Voltage (V)

0.5

📥 3% WFF

0.6

-∎-4% WFF

0.7

#### 7 Conclusions

10 0

0.1

0.2

An analysis over multiple scenarios considering several levels of process variability, supply voltages, and transistor sizing was performed in order to identify the adequate number of fins and supply voltage for various kinds of applications prioritizing energy consumption and the minimization of deviations.

ST is a promising circuit for variability effects mitigation and enhancement of noise immunity being fairly applied on critical applications with tight reliability constraints. The results show that fewer fins can enable considerable energy reduction. On the contrary, for the ST robustness, a higher fin count will bring an increase in the on-current, bringing noise immunity improvements.

In performance results, it could be observed up to 16% and 44.65% maximum average increase and decrease in frequency, respectively, with differences between variability impact in the layouts rising alongside the supply voltage

20 L. B. Moraes, A. L. Zimpeck, C. Meinhardt and R. Reis

Fig. 19. Average of hysteresis interval increase over WFF scaling [60].

**Table 7.** Hysteresis interval ratio dependency over NFET and PFET workfunction[60].

| PFET<br>NFET | 5%   | 4%   | 3%   | 2%   | 1%   | 0%   | -1%  | -2%  | -3%  | -4%  | -5%  |

|--------------|------|------|------|------|------|------|------|------|------|------|------|

| 5%           | 0.30 | 0.28 | 0.28 | 0.27 | 0.26 | 0.25 | 0.26 | 0.27 | 0.28 | 0.30 | 0.32 |

| 4%           | 0.46 | 0.46 | 0.55 | 0.54 | 0.54 | 0.54 | 0.55 | 0.56 | 0.57 | 0.59 | 0.61 |

| 3%           | 0.76 | 0.76 | 0.76 | 0.78 | 0.80 | 0.81 | 0.83 | 0.84 | 0.86 | 0.87 | 0.89 |

| 2%           | 0.88 | 0.90 | 0.92 | 0.92 | 0.95 | 0.97 | 0.99 | 1.00 | 1.00 | 1.00 | 1.00 |

| 1%           | 0.93 | 0.94 | 0.97 | 0.99 | 1.00 | 1.00 | 1.00 | 1.00 | 1.00 | 1.00 | 1.00 |

| 0%           | 0.95 | 0.96 | 0.97 | 1.00 | 1.00 | 1.00 | 1.00 | 1.00 | 1.00 | 1.00 | 1.00 |

| -1%          | 0.95 | 0.96 | 0.99 | 0.99 | 1.00 | 1.00 | 1.00 | 1.00 | 1.00 | 1.00 | 1.00 |

| -2%          | 0.96 | 0.97 | 0.99 | 1.00 | 1.00 | 0.99 | 0.99 | 0.99 | 0.99 | 0.98 | 0.98 |

| -3%          | 0.95 | 0.97 | 0.99 | 0.99 | 0.99 | 0.99 | 0.98 | 0.98 | 0.98 | 0.97 | 0.97 |

| -4%          | 0.93 | 0.94 | 0.97 | 0.97 | 0.96 | 0.96 | 0.96 | 0.95 | 0.95 | 0.95 | 0.94 |

| -5%          | 0.93 | 0.94 | 0.96 | 0.96 | 0.96 | 0.95 | 0.95 | 0.94 | 0.94 | 0.94 | 0.93 |

value. The hysteresis intervals showed clear advantages over higher fin count and supply voltages with 10.76% and 25.26% better hysteresis. Considering energy consumption and variability, it was possible to achieve 24.84% and 14.44% decreases, respectively, with robust layouts taking advantage of a higher number of fins and a small decrease on the supply voltage while still maintaining very high frequencies of about 5GHz. A cost-benefit analysis was made as well, giving an additional option in order to achieve acceptable energy consumption and variability robustness.

For future works, we expect to investigate the effects of sizing on each feedback transistor on the ST circuit independently, introduce new designs and technology nodes into the analysis, take radiation effects, on top of the variability, into account and apply such circuits into more complex projects.

#### Acknowledgements

This study was financed in part by the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - Brasil (CAPES) - Finance Code 001, by the Brazilian National Council for Scientific and Technology Development (CNPq), and by the Research Support Foundation of the State of Rio Grande do Sul (FAPERGS).

#### References

- 1. Miorandi, D., Sicari, S., De Pellegrini, F., Chlamtac, I.: Internet of things: Vision, applications and research challenges. Ad hoc networks **10**(7) (2012) 1497–1516

- Manoli, Y.: Energy harvesting—from devices to systems. In: 2010 Proceedings of ESSCIRC, IEEE (2010) 27–36

- Bleitner, A., Goeppert, J., Lotze, N., Keller, M., Manoli, Y.: Comparison and optimization of the minimum supply voltage of schmitt trigger gates versus cmos gates under process variations. In: ANALOG 2018; 16th GMM/ITG-Symposium, VDE (2018) 1–6

- Abbas, Z., Olivieri, M., Khalid, U., Ripp, A., Pronath, M.: Optimal nbti degradation and pvt variation resistant device sizing in a full adder cell. In: Reliability, Infocom Technologies and Optimization (ICRITO)(Trends and Future Directions), 2015 4th International Conference on. (2015) 1–6

- Farkhani, H., Peiravi, A., Kargaard, J.M., Moradi, F.: Comparative study of finfets versus 22nm bulk cmos technologies: Sram design perspective. In: 2014 27th IEEE International System-on-Chip Conference (SOCC), IEEE (2014) 449–454

- Zimpeck, A.L., Meinhardt, C., Posser, G., Reis, R.: Finfet cells with different transistor sizing techniques against pvt variations. In: Circuits and Systems (ISCAS), 2016 IEEE International Symposium on. (2016) 45–48

- 7. Nassif, S.: Process variability at the 65nm node and beyond. In: Custom Integrated Circuits Conference, 2008. CICC 2008. IEEE. (2008) 1–8

- Hariharan, A.N., Pontarelli, S., Ottavi, M., Lombardi, F.: Modeling open defects in nanometric scale cmos. In: 2010 IEEE 25th International Symposium on Defect and Fault Tolerance in VLSI Systems, IEEE (2010) 249–257

- Vaddi, R., Dasgupta, S., Agarwal, R.: Device and circuit co-design robustness studies in the subthreshold logic for ultralow-power applications for 32 nm cmos. IEEE Transactions on Electron Devices 57(3) (2010) 654–664

- Ames, S.O., Zanandrea, V., Oliveira, I.F.V., Toledo, S.P., Meinhardt, C.: Investigating pvt variability effects on full adders. In: Power and Timing Modeling, Optimization and Simulation (PATMOS), 2016 26th International Workshop on. (2016) 155–161

- Islam, A., Hasan, M.: Design and analysis of power and variability aware digital summing circuit. Volume 2. (2011) 6–14

- Alioto, M., Palumbo, G.: Delay variability due to supply variations in transmissiongate full adders. In: Circuits and Systems, 2007. ISCAS 2007. IEEE International Symposium on. (2007) 3732–3735

- Kulkarni, J.P., Kim, K., Roy, K.: A 160 mv robust schmitt trigger based subthreshold sram. IEEE Journal of Solid-State Circuits 42(10) (2007) 2303–2313

- Hays, K.I.: A 62 mv 0.13 um cmos standard-cell-based design technique using schmitt-trigger logic. (2012)

- 22 L. B. Moraes, A. L. Zimpeck, C. Meinhardt and R. Reis

- Melek, L., da Silva, A.L., Schneider, M.C., Galup-Montoro, C.: Analysis and design of the classical cmos schmitt trigger in subthreshold operation. Volume 64. IEEE (2017) 869–878

- Lotze, N., Manoli, Y.: Ultra-sub-threshold operation of always-on digital circuits for iot applications by use of schmitt trigger gates. IEEE Transactions on Circuits and Systems I: Regular Papers 64(11) (2017) 2920–2933

- Dokania, V., Islam, A.: Circuit-level design technique to mitigate impact of process, voltage and temperature variations in complementary metal-oxide semiconductor full adder cells. Volume 9. IET (2015) 204–212

- Toledo, S.P., Zimpeck, A.L., Reis, R., Meinhardt, C.: Pros and cons of schmitt trigger inverters to mitigate pvt variability on full adders. In: 2018 IEEE International Symposium on Circuits and Systems (ISCAS), IEEE (2018) 1–5

- Moraes, L.B.d., Zimpeck, A., Meinhardt, C., Reis, R.: Evaluation of variability using schmitt trigger on full adders layout. Microelectronics Reliability 88 (2018) 116–121

- Asenov, A.: Random dopant induced threshold voltage lowering and fluctuations in sub 50 nm mosfets: a statistical 3datomistic'simulation study. Volume 10. IOP Publishing (1999) 153

- Bernstein, K., Frank, D.J., Gattiker, A.E., Haensch, W., Ji, B.L., Nassif, S.R., Nowak, E.J., Pearson, D.J., Rohrer, N.J.: High-performance cmos variability in the 65-nm regime and beyond. IBM journal of research and development 50(4.5) (2006) 433–449

- Wang, W., Reddy, V., Yang, B., Balakrishnan, V., Krishnan, S., Cao, Y.: Statistical prediction of circuit aging under process variations. In: 2008 IEEE Custom Integrated Circuits Conference, IEEE (2008) 13–16

- Young, D., Christou, A.: Failure mechanism models for electromigration. IEEE Transactions on Reliability 43(2) (1994) 186–192

- Lombardo, S., Stathis, J.H., Linder, B.P., Pey, K.L., Palumbo, F., Tung, C.H.: Dielectric breakdown mechanisms in gate oxides. Journal of applied physics 98(12) (2005) 12

- Takeda, E., Suzuki, N.: An empirical model for device degradation due to hotcarrier injection. IEEE electron device letters 4(4) (1983) 111–113

- Stine, B.E., Boning, D.S., Chung, J.E.: Analysis and decomposition of spatial variation in integrated circuit processes and devices. IEEE Transactions on Semiconductor Manufacturing 10(1) (1997) 24–41

- Nassif, S.R.: Within-chip variability analysis. In: International Electron Devices Meeting 1998. Technical Digest (Cat. No. 98CH36217), IEEE (1998) 283–286

- Asenov, A., Brown, A.R., Davies, J.H., Kaya, S., Slavcheva, G.: Simulation of intrinsic parameter fluctuations in decananometer and nanometer-scale mosfets. IEEE transactions on electron devices 50(9) (2003) 1837–1852

- Frank, D.J., Dennard, R.H., Nowak, E., Solomon, P.M., Taur, Y., Wong, H.S.P.: Device scaling limits of si mosfets and their application dependencies. Proceedings of the IEEE 89(3) (2001) 259–288

- Wong, H.S., Frank, D.J., Solomon, P.M., Wann, C.H., Welser, J.J.: Nanoscale cmos. Proceedings of the IEEE 87(4) (1999) 537–570

- Frank, D.J., Wong, H.S.: Simulation of stochastic doping effects in si mosfets. In: 7th International Workshop on Computational Electronics. Book of Abstracts. IWCE (Cat. No. 00EX427), IEEE (2000) 2–3

- Brunner, T.A.: Why optical lithography will live forever. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena 21(6) (2003) 2632–2637

23

- Bhattacharya, D., Jha, N.K.: Finfets: From devices to architectures. Volume 2014. Hindawi (2014)

- Taur, Y., Ning, T.H.: Fundamentals of modern VLSI devices. Cambridge university press (2013)

- King, T.J.: Finfets for nanoscale cmos digital integrated circuits. In: ICCAD-2005. IEEE/ACM International Conference on Computer-Aided Design, 2005. (Nov 2005) 207–210

- Saha, S.K.: Modeling process variability in scaled cmos technology. IEEE Design & Test of Computers 27(2) (2010) 8–16

- Mustafa, M., Bhat, T.A., Beigh, M.: Threshold voltage sensitivity to metal gate work-function based performance evaluation of double-gate n-finfet structures for lstp technology. (2013)

- Hwang, C.H., Li, Y., Han, M.H.: Statistical variability in finfet devices with intrinsic parameter fluctuations. Microelectronics Reliability 50(5) (2010) 635–638

- Mukhopadhyay, S., Lee, Y.H., Lee, J.H.: Time-zero-variability and bti impact on advanced finfet device and circuit reliability. Microelectronics Reliability 81 (2018) 226–231

- Meinhardt, C., Zimpeck, A.L., Reis, R.A.: Predictive evaluation of electrical characteristics of sub-22 nm finfet technologies under device geometry variations. Microelectronics Reliability 54(9-10) (2014) 2319–2324

- 41. Hobbs, C.C., Fonseca, L.R., Knizhnik, A., Dhandapani, V., Samavedam, S.B., Taylor, W.J., Grant, J.M., Dip, L., Triyoso, D.H., Hegde, R.I., et al.: Fermi-level pinning at the polysilicon/metal-oxide interface-part ii. IEEE Transactions on Electron Devices 51(6) (2004) 978–984

- 42. Gusev, E.P., Narayanan, V., Frank, M.M.: Advanced high- $\kappa$  dielectric stacks with polysi and metal gates: Recent progress and current challenges. IBM Journal of Research and Development **50**(4.5) (2006) 387–410

- Gusev, E., Buchanan, D., Cartier, E., Kumar, A., DiMaria, D., Guha, S., Callegari, A., Zafar, S., Jamison, P., Neumayer, D., et al.: Ultrathin high-k gate stacks for advanced cmos devices. In: International Electron Devices Meeting. Technical Digest (Cat. No. 01CH37224), IEEE (2001) 20–1

- 44. Datta, S., Dewey, G., Doczy, M., Doyle, B., Jin, B., Kavalieros, J., Kotlyar, R., Metz, M., Zelick, N., Chau, R.: High mobility si/sige strained channel mos transistors with hfo/sub 2//tin gate stack. In: IEEE International Electron Devices Meeting 2003, IEEE (2003) 28–1

- Dadgour, H., De, V., Banerjee, K.: Statistical modeling of metal-gate work-function variability in emerging device technologies and implications for circuit design. In: 2008 IEEE/ACM International Conference on Computer-Aided Design, IEEE (2008) 270–277

- Brown, A.R., Idris, N.M., Watling, J.R., Asenov, A.: Impact of metal gate granularity on threshold voltage variability: A full-scale three-dimensional statistical simulation study. IEEE Electron Device Letters 31(11) (2010) 1199–1201

- Meinhardt, C., Zimpeck, A.L., Reis, R.: Impact of gate workfunction fluctuation on finfet standard cells. In: Electronics, Circuits and Systems (ICECS), 2014 21st IEEE International Conference on. (2014) 574–577

- Pal, I., Islam, A.: Circuit-level technique to design variation-and noise-aware reliable dynamic logic gates. IEEE Trans. on Device and Materials Reliability 18(2) (2018) 224–239

- Wang, Z.: Cmos adjustable schmitt triggers. IEEE Transactions on instrumentation and Measurement 40(3) (1991) 601–605

- 24 L. B. Moraes, A. L. Zimpeck, C. Meinhardt and R. Reis

- Steyaert, M., Sansen, W.: Novel cmos schmitt trigger. Electronics Letters 22(4) (1986) 203–204

- Zhang, C., Srivastava, A., Ajmera, P.K.: Low voltage cmos schmitt trigger circuits. Volume 39. IET (2003) 1696–1698

- 52. Kim, D., Kih, J., Kim, W.: A new waveform-reshaping circuit: an alternative approach to schmitt trigger. IEEE journal of solid-state circuits 28(2) (1993) 162– 164

- Pfister, A.: Novel cmos schmitt trigger with controllable hysteresis. Electronics Letters 28(7) (1992) 639–641

- Al-Sarawi, S.: Low power schmitt trigger circuit. Electronics letters 38(18) (2002) 1009–1010

- Pedroni, V.: Low-voltage high-speed schmitt trigger and compact window comparator. Electronics Letters 41(22) (2005) 1213–1214

- Doki, B.L.: Cmos schmitt triggers. In: IEE Proceedings G-Electronic Circuits and Systems. Volume 131. (1984) 197–202

- Clark, L.T., Vashishtha, V., Shifren, L., Gujja, A., Sinha, S., Cline, B., Ramamurthy, C., Yeric, G.: Asap7: A 7-nm finfet predictive process design kit. Volume 53. Elsevier (2016) 105–115

- Alioto, M., Consoli, E., Palumbo, G.: Variations in nanometer cmos flip-flops part ii: Energy variability and impact of other sources of variations. Volume 62. (March 2015) 835–843

- Chava, B., Rio, D., Sherazi, Y., Trivkovic, D., Gillijns, W., Debacker, P., Raghavan, P., Elsaid, A., Dusa, M., Mercha, A.: Standard cell design in n7: Euv vs. immersion. In: Design-Process-Technology Co-optimization for Manufacturability IX. Volume 9427. (2015) 94270E

- Moraes, L., Zimpeck, A., Meinhardt, C., Reis, R.: Minimum energy finfet schmitt trigger design considering process variability. In: 2019 IFIP/IEEE 27th International Conference on Very Large Scale Integration (VLSI-SoC), IEEE (2019) 88–93

- 61. : The synopsys website. [online] available:. http://www.synopsys.com