# Extending Intel-x86 Consistency and Persistency

Azalea Raad, Luc Maranget, Viktor Vafeiadis

## ▶ To cite this version:

Azalea Raad, Luc Maranget, Viktor Vafeiadis. Extending Intel-x86 Consistency and Persistency. POPL 2022 - Symposium on Principles of Programming Languages, Jan 2022, Philadelphia, United States. 10.1145/3498683. hal-03426997

# HAL Id: hal-03426997 https://inria.hal.science/hal-03426997v1

Submitted on 12 Nov 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **Extending Intel-x86 Consistency and Persistency**

Formalising the Semantics of Intel-x86 Memory Types and Non-Temporal Stores

AZALEA RAAD, Imperial College London, United Kingdom LUC MARANGET, Inria, France VIKTOR VAFEIADIS, MPI-SWS, Germany

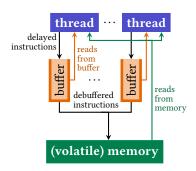

Existing semantic formalisations of the Intel-x86 architecture cover only a small fragment of its available features that are relevant for the *consistency* semantics of multi-threaded programs as well as the *persistency* semantics of programs interfacing with non-volatile memory.

We extend these formalisations to cover: (1) non-temporal writes, which provide higher performance and are used to ensure that updates are flushed to memory; (2) reads and writes to other Intel-x86 memory types, namely uncacheable, write-combined, and write-through; as well as (3) the interaction between these features. We develop our formal model in both operational and declarative styles, and prove that the two characterisations are equivalent. We have empirically validated our formalisation of the consistency semantics of these additional features and their subtle interactions by extensive testing on different Intel-x86 implementations.

CCS Concepts: • Theory of computation  $\rightarrow$  Semantics and reasoning; Concurrency; Axiomatic semantics; Operational semantics; • Hardware  $\rightarrow$  Hardware validation.

Additional Key Words and Phrases: weak memory, memory consistency, memory persistency, non-volatile memory, Intel-x86, non-temporal accesses, memory types, cacheability

#### **ACM Reference Format:**

Azalea Raad, Luc Maranget, and Viktor Vafeiadis. 2022. Extending Intel-x86 Consistency and Persistency: Formalising the Semantics of Intel-x86 Memory Types and Non-Temporal Stores. *Proc. ACM Program. Lang.* 6, POPL, Article 22 (January 2022), 31 pages. https://doi.org/10.1145/3498683

## 1 INTRODUCTION

Since the seminal work of Sewell et al. [2010], it is widely understood in the programming language literature that the Intel-x86 architecture follows the *TSO* ('total store order') memory consistency model. This, in particular, means that the annotated weakly consistent behaviour of the SB ('store buffering') program below is allowed on Intel-x86, whereas that of MP ('message passing') is not.<sup>1</sup>

$$x := 1;$$

$a := y; //0$   $y := 1;$   $b := x; //0$  (SB)  $x := 1;$   $a := y; //1$   $b := x; //0$  (MP)

This, however, constitutes a very shallow understanding of the consistency semantics of the Intel-x86 architecture. The outcomes of these litmus tests crucially depend on the *memory type* attribute of the pages containing x and y, which is set by the operating system and recorded

Authors' addresses: Azalea Raad, Imperial College London, United Kingdom, azalea@imperial.ac.uk; Luc Maranget, Inria, France, luc.maranget@inria.fr; Viktor Vafeiadis, MPI-SWS, Germany, viktor@mpi-sws.org.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for third-party components of this work must be honored. For all other uses, contact the owner/author(s).

© 2022 Copyright held by the owner/author(s).

2475-1421/2022/1-ART22

https://doi.org/10.1145/3498683

<sup>&</sup>lt;sup>1</sup>In all our examples we use x, y, z for (shared) memory locations initialised with 0, and use a, b, c for (local) registers. For readability, rather than Intel-x86 assembly instructions, we use the assignment notation and write e.g. x := v for writing v to x, and a := x to denote reading the value of x into a. The  $\sqrt{v}$  annotation after a read denotes that the value read is v.

in the page table. The most common memory type is *write-back* (wb) memory, whose semantics corresponds to TSO, as prior work has discovered [Sewell et al. 2010]. However, Intel-x86 supports other memory types such as *uncacheable* (uc) memory, which is mainly used for memory-mapped I/O; *write-combining* (wc) memory, which is meant for bulk data transfer such as displaying videos; and *write-through* (wt) memory. All these memory types have very different semantics. For example, if *x* and *y* were in wc memory, then the weak behaviour of sb would *not* be allowed, whereas that of MP would be! To restrict the additional weak behaviours of wc memory in programs such as MP, Intel-x86 provides an additional fence instruction, **sfence** (store fence), which is strictly weaker than a memory fence (**mfence**) in that it only orders store instructions. (Existing formalizations of Intel-x86 treat **sfence** simply as a NOP, since stores are already ordered under TSO.)

We note that such weaker-than-TSO effects are not observable only under these specialised memory types. Even when using wb memory, it is possible to get similar effects with *non-temporal writes* (MOVNT). Non-temporal writes provide higher performance than regular writes in cases where the written data is not expected to be used immediately, by reducing cache contention and giving more flexibility to the hardware to reorder them with respect to other accesses. Specifically, the Intel manual (see (NT) in  $\S 2$ ) explains non-temporal writes in terms of wc memory: a non-temporal write on x behaves as if x were in wc memory. The reality, however, is more complex in that when using non-temporal writes both SB and MP can exhibit their annotated weak behaviours!

Naturally, these different memory types can be used together in a program, leading to subtle interactions between them and further complicating their semantics. The semantics of such interactions is barely discussed in the Intel manuals, creating confusion even amongst seasoned programmers on these topics – as witnessed by contradicting answers to a relevant query on StackOverflow [Anonymous 2021] – and highlighting the need for their *formal*, *empirically-validated semantics*.

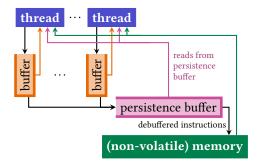

A closely related aspect of architectural semantics is memory *persistency*, which describes when and how memory stores are propagated to memory, and thus may be seen by an external device. Memory persistency is hugely important for systems with *non-volatile memory* (NVM) because it determines the possible contents of memory after a power failure. As with consistency, prior work [Raad et al. 2020] has only formalised the semantics of regular stores to wb memory and basic cache-line flushing instructions. This subset of features is quite limiting for practical purposes: other memory types and non-temporal stores are often used for better performance and/or simpler persistency semantics. In particular, the PMDK library for persistent programming [Intel 2015] (a large-scale open-source project) uses non-temporal writes to avoid cache-line flushes.

We address the shortcomings of the existing formal Intel-x86 consistency and persistency models by extending them to cover non-temporal writes and the wide range of memory types available. To our knowledge, we have developed the *first* formal semantic models of these architectural features, which we integrate into the existing x86-TSO [Sewell et al. 2010] and Px86<sub>sim</sub> [Raad et al. 2020] models. Specifically, we develop two formal models – an *operational* one in terms of a machine with a collection of buffers and a *declarative* one in terms of execution graphs – and prove their *equivalence*. Having two equivalent models is useful not only for ensuring the canonicity of the formalism, but also because one or the other formulation may be more useful for establishing different results. For instance, operational models are better suited for underpinning program logics and checking reachability of an erroneous configuration and/or robustness for finite-state programs with loops (e.g. [Abdulla et al. 2021; Bouajjani et al. 2013; Lahav and Boker 2020]), whereas declarative models are better suited for deriving stateless model checking of programs with only bounded loops (e.g. [Kokologiannakis et al. 2021, 2019b]).

We have developed our formal models through a careful reading of the Intel manuals, informal discussions/exchanges with Intel engineers, and, in the case of consistency, *empirical validation* by extensive testing of multiple Intel-x86 implementations. As setting the memory type of a page is

only possible in the kernel, the latter involved adapting the **diy** toolsuite [Alglave and Maranget 2021] to run litmus tests in kernel mode, allocate each variable on a different page, and set the page memory types accordingly. By contrast, as in previous work we could not test our persistency semantics since it requires specialised hardware to monitor the memory bus traffic (see §2).

Prevalence of Intel-x86 Non-Temporal Writes and Memory Types. Non-temporal writes provide an application-level mechanism for enforcing wc cacheability and avoiding cache pollution. Non-temporal writes are ubiquitous. For instance, searching for MOVNTI (an Intel-x86 non-temporal write) on GitHub returns over 300K results [GitHub 2021], spread across over ten languages, including C, C++ and Assembly. Searching for other non-temporal writes such as MOVNTQ, MOVNTDQ, MOVNTPS and MOVNTPD return similar results. Moreover, non-temporal writes are available in languages such as Rust [Rust 2021], which are in turn compiled to non-temporal writes on Intel-x86 machines. Another notable use of non-temporal writes is in the memset function in the C runtime [LWN 2007]. Similarly, non-temporal writes are used by memcpy in glibc (the core libraries for GNU/Linux) [Free Software Foundation 2016]. Consequently, a large body of existing code using glibc uses non-temporal writes by extension. As with PMDK [Intel 2015], other large-scale projects such as SPDK [SPDK 2021], DPDK [DPDK 2021] and DML [DML 2021] use non-temporal writes; e.g. DPDK and DML use MOVDIR64b (a non-temporal write) to atomically communicate with accelerators, while SPDK uses non-temporal writes to interface with NVM [GitHub 2019].

As we describe in §2, the Intel-x86 memory types are declared either through the page attribute table (PAT) or custom registers, and are thus used within *system-level* code, e.g. the Linux kernel [LWN 2008]. Moreover, we memory is used inside the Linux kernel for e.g. frame buffer optimisation [LWN 2016]. Similarly, the Linux kernel uses ue memory for memory-mapped I/O (MMIO) [LWN 2016]. Finally, non-wb memory types are typically used to interact with non-cache-coherent DMA (direct memory access) device drivers.

*Contributions and Outline.* Our contributions (detailed in §2) are as follows:

- §3 We develop the declarative Ex86 model as the first formal model of Intel-x86 consistency that accounts for memory types and non-temporal stores.

- §4 We develop an operational Ex86 model, which we prove equivalent to our declarative model.

- §5 We describe how we empirically validated Ex86 through extensive litmus testing.

- §6 We extend Ex86 to develop declarative and operational characterisations of the PEx86 model as the first formal model of Intel-x86 persistency that accounts for memory types and non-temporal writes, and show that the two characterisations of PEx86 are equivalent.

We discuss related and future work in §7.

*Additional Material.* The proofs of all theorems stated in the paper are given in the accompanying technical appendix [Raad et al. 2022a]. Our library of litmus tests in our validation effort is available online [Raad et al. 2022b].

### 2 OVERVIEW

Memory *consistency* models describe the permitted behaviours of programs by constraining the *volatile memory order*, i.e. the order in which memory instructions (e.g. writes) are made visible to other threads. Analogously, memory *persistency* models describe the permitted behaviours of programs upon recovering from a crash (e.g. due to power loss) in the context of the NVM technology by defining a *persistent memory order*, i.e. the order in which the effects of memory instructions are committed to persistent memory. To distinguish between the two memory orders, memory *stores* are differentiated from memory *persists*. The former denotes the process of making an instruction (e.g. a write) visible to other threads, whilst the latter denotes the process of committing

instruction effects durably to persistent memory. We proceed with an intuitive account of our *Ex86* ('extended x86') model, the first formal Intel-x86 consistency semantics that covers memory types and non-temporal writes (§2.1). We then present an overview of our *PEx86* ('persistent Ex86') model as the first formal account of Intel-x86 persistency semantics that extends to memory types and non-temporal writes. In what follows we often cite the Intel reference manual [Intel 2021] in "double quotation marks", at times including [text in square brackets] denoting our added clarification.

## 2.1 Ex86: The Extended Intel-x86 Consistency Model

Validating Ex86. We have empirically validated our Ex86 consistency model (described shortly below), including all behaviours and examples discussed in this paper. Specifically, using the diy toolsuite [Alglave and Maranget 2021], we have built a vast library of litmus tests and ran them against Ex86 and as kernel modules. Litmus testing involves running small, concurrent programs (e.g. sb in §1) that exercise specific features of consistency on a machine while simultaneously stressing the memory with heavy background traffic. With thousands of tests and hundreds of thousands of runs per test, one can observe all possible behaviours on the machine, ensuring behaviour coverage. A full catalogue of our tests and their results on various platforms is given in [Raad et al. 2022b]. As we discuss below, we have validated all Ex86 features and instructions except one instruction, flush<sub>opt</sub>, which constitutes a small fragment of Ex86. This is because on most modern hardware, including all machines available to us for testing, the flush<sub>opt</sub> implementation is commonly stronger than its specification in the Intel manual [Intel 2021]. Nevertheless, we have generated extensive tests that could be used to validate the flush<sub>opt</sub> behaviour in the future on machines that implement it more faithfully.

Intel-x86 Memory Types at a Glance. Intel-x86 processors allow any area of system memory to be cached. Moreover, for each individual page or region of memory, the caching type, also called the memory type may be specified [Intel 2021, Vol. 3A, §11.3] either through the page attribute table (PAT) or memory type range registers (MTRRs). Specifically, the memory type can be defined as strong-uncacheable (uc), uncacheable (uc-), (uncacheable) write-combining (wc), (cacheable) write-back (wb), (cacheable) write-through (wt), and write protected (wp). Although the memory type of a location may be altered during execution, doing so entails a complex mechanism invoking kernel code. As such, for simplicity we assume that memory types do not change once assigned, and thus the sets of locations associated with memory types are pairwise disjoint. As we describe below, all behaviours described below are empirically validated through extensive litmus testing [Raad et al. 2022b]. As we describe in §5, we could not support the wp memory in our validation infrastructure. Hence, to avoid speculating about the behaviour of wp memory, we forgo wp in our Ex86 formalism.

As we elaborate shortly, the uc type is the strongest of all types and its accesses follow *strong ordering* (Intel terminology). Specifically, accesses to uc memory cannot be reordered with respect to any other accesses except later (in program order) reads on wb and wt memory. As such, when all locations accessed in a program P lie in uc memory, no reordering is allowed and the P behaviours are those observed under SC ('sequential consistency') [Lamport 1979] – see Theorem 1.

(uc) "System memory locations are not cached. All reads and writes appear on the system bus and are executed in program order without reordering....[uc] is useful for memory-mapped I/O devices." [Intel 2021, Vol. 3A, p. 11-6]

Note that the interaction between uc and other types (e.g. reordering later wb/wt reads before uc writes) is not discussed in the Intel manual and we have uncovered it through our experiments.

As with uc, accesses to uc<sup>-</sup> memory follow the strong ordering (and thus follow the same ordering constraints) and they only differ in how they are selected (assigned). As accesses on uc and uc<sup>-</sup> memory are subject to the same ordering constraints, they exhibit the same behaviours and follow

the same semantics. As such, in our Ex86 formalism we forgo the uc<sup>-</sup> memory and only model uc. Nevertheless, all behaviours and semantics we ascribe to uc memory also hold of uc<sup>-</sup> memory.

(uc<sup>-</sup>) "[uc<sup>-</sup>] Has same characteristics as uc memory type, except that uc<sup>-</sup> type can be overridden by programming the MTRRs for the wc memory type." [Intel 2021, Vol. 3A, p. 11-6]

The wc memory type is the weakest of all types in that its accesses follow the *weak ordering* (Intel terminology). A main characteristic of wc memory is that it allows write-write reordering: write accesses on different wc locations may be reordered, leading to weak behaviours disallowed under both SC (governing uc memory) and TSO (governing wb memory – see below). Specifically, as we show later in Theorem 1, when all accesses in a program P are on wc memory, then the behaviours of P are those observed under a strengthening of the PSO ('partial store order') model we refer to as SPSO ('strong PSO'), where only write-write reordering on different locations is allowed.

(wc) "System memory locations are not cached (as with uc).... [wc] is appropriate for video frame buffers, where the order of writes is unimportant as long as the writes update memory so they can be seen on the graphics display." [Intel 2021, Vol. 3A, p. 11-7]

Once again, the Intel manual does not discuss the subtle interaction between wc and other memory types. For instance, as we discuss below, our tests revealed that wc writes can be reordered with respect to writes on different locations in wc/wb memory but not those in uc/wt memory.

The wb memory type provides the best performance for the typical memory access patterns of applications. When all locations in a program P lie in wb memory, the behaviours of P are those allowed under *processor ordering* (Intel terminology), also referred to as TSO [Sewell et al. 2010] – see Theorem 1. The main characteristic of TSO is that it allows write-read reordering: later reads can be reordered before earlier writes. Note that wb memory is strictly weaker than uc in terms of ordering constraints: while write-read reordering is allowed on wb, all reorderings (including write-read) are prohibited on uc. By contrast, wb and wc are incomparable: write-read reordering is allowed on wb but not on wc, write-write reordering is allowed on wc but not on wb.

(WB) "Writes and reads to and from system memory are cached ... writes are performed entirely in the cache ... Writes to a cache line are not immediately forwarded to system memory; instead, they are accumulated in the cache. The modified cache lines are written to system memory later ... [wb] provides the best performance ... " [Intel 2021, Vol. 3A, p. 11-7]

The wt memory lies between wb and uc in terms of its ordering constraints. Specifically, wt reads follow the same constraints as wb reads in that write-read reordering on wt memory is allowed. The main difference between wt and wb lies in how their writes interact with wc writes. More concretely, as we describe shortly, wb writes may be reordered with respect to wc writes. By contrast, unlike wb and as with uc memory, wt writes cannot be reordered with respect to wc writes.

(wT) "Writes and reads to and from system memory are cached. ... All writes are written to a cache line (when possible) and through to system memory. ... [wt] is appropriate for frame buffers ..." [Intel 2021, Vol. 3A, p. 11-7]

Note that as well as enforcing certain ordering constraints, memory types also prescribe memory *cacheability*. Specifically, locations in uc and wc memory are not cached (see (uc) and (wc) above); their accesses bypass the cache and directly interact with the memory. Hereafter, we refer to uc and wc memory collectively as *non-cacheable* (nc). By contrast, the locations in both wb and wt memory may be cached. As such, henceforth we refer to wb and wt memory collectively as *cacheable* (c). However, while wb writes are cached and propagated to memory only *later*, wt writes are cached and propagated to memory *immediately* (see (wb) and (wt) above).

*Intel-x86 Non-Temporal Accesses*. The Intel reference manual categorises the data referenced by a program as either *temporal* (data that will be reused, e.g. program code), or *non-temporal* (data

that will be referenced once and not reused in the immediate future, e.g. multi-media data, such as the display list in a 3-D graphics application). Ideally, to use processor caches efficiently, temporal data should be cached, whereas non-temporal data should not be cached. Filling processor caches with non-temporal data is referred to as "polluting the caches". To minimise cache pollution, Intel-x86 architectures provide several *non-temporal store instructions* that treat the memory accessed as we memory, storing data to memory directly and bypassing the caches. More concretely, if a program executes a non-temporal store on location x, and x lies in wb, wt or we memory, then the store on x is written to memory with we semantics. If, however, x lies in uc memory, then the non-temporal hint is ignored and the store follows uc semantics. Through our validation effort we have confirmed that non-temporal stores (on wb/wt/wc memory) indeed follow we semantics, as intended.

(NT) "If a program specifies a non-temporal store and the memory type of the destination region is wb, wt or wc, the processor will do the following: if the memory location being written to is present in the cache hierarchy, the data in the caches is evicted; the non-temporal data is written to memory with wc semantics."

[Intel 2021, Vol. 1, p. 10-12].

In addition to several non-temporal *store* instructions, Intel-x86 architectures provide a single non-temporal *load* instruction. However, as our private correspondence with the lead architect of the Intel instruction set system architecture has revealed, the non-temporal load instruction has been a source of implementation issues, it has not been implemented consistently, and there has been ambiguity regarding its semantics. Moreover, we have been unable to validate the behaviour of non-temporal loads (see §5). As such, rather than speculating about its ambiguous and inconsistent semantics, in our Ex86 formalism we forgo the single non-temporal load instruction.

**Litmus Test Notation.** In what follows we elaborate on the behaviour of Ex86 memory types and how they interact with one another through several representative *litmus test* programs. Given a location x and memory type  $t \in \{uc, wc, nc, wb, wt, c\}$ , we write  $x \in Loc_t$  to denote that x is in t memory. When the memory type of location x is immaterial and the exhibited behaviours hold regardless of the memory type of x, we forgo the type annotation and write  $x \in Loc$ .

In our programs we write x := v to denote writing (storing) value v to (shared) memory location x, and write a := x to denote reading (loading) the value of location x into the (thread-local) register a. Analogously, we write  $x :=_{\mathsf{NT}} v$  to denote storing v to location v with a non-temporal hint. As discussed above, the non-temporal hint is ignored if  $v \notin \mathsf{Loc}_{\mathsf{wb} \cup \mathsf{wt} \cup \mathsf{wc}}$ .

Ordering Constraints of mfence, sfence and Atomic Updates. In order to afford more control over instruction reordering, Intel-x86 provides fence instructions, including memory fences, written mfence, and store fences, written sfence. Memory fences are strictly stronger than store fences: while memory fences cannot be reordered with respect to any memory instruction, store fences may be reordered with respect to only reads. Additionally, Intel-x86 provides instructions for atomically updating the memory through 'read-modify-write' (RMW) operations such as CAS ('compare-and-set') and FAA ('fetch-and-add'). RMW instructions follow the same ordering constraints as memory fences in that they cannot be reordered with respect to any memory instruction.

Ordering between Earlier Reads and Later Memory Instructions. Earlier read instructions cannot be reordered with respect to any later memory instruction (including later reads and writes). This is illustrated in the programs of Fig. 1a and Fig. 1b, showing examples of read-read and read-write reordering, respectively. More concretely, the program in Fig. 1a depicts a variant of the canonical 'message passing' (MP) litmus test with an **mfence** between the two writes of the left thread. This intervening **mfence** ensures that the two writes cannot be reordered (regardless of the memory types of *x* and *y*), and thus the two writes are executed in program order. Let us assume it were possible for the two reads of the right thread to be reordered. Then it would be possible to

| $x, y \in \text{Loc}$                                                                                         | $x, y \in \text{Loc}$                                                                       | $x \in Loc_{c}, y \in Loc$                                                                                                        | $x \in Loc_{nc}, y \in Loc$                                                                    | $x \in Loc_c \lor y \in Loc_c$                                |  |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|

| $\begin{vmatrix} x := 1; \\ \mathbf{mfence}; \\ y := 1; \end{vmatrix}   \mathbf{a} := y; \\ \mathbf{b} := x;$ | $\begin{vmatrix} x := 2; \\ \mathbf{mfence}; \\ y := 1; \end{vmatrix} $ a := y; $ x := 1; $ | $\begin{vmatrix} x := 1; \\ \mathbf{mfence}; \\ a := y; \end{vmatrix} y := 1; \\ b := x;$                                         | $\begin{vmatrix} x := 1; \\ \mathbf{mfence}; \\ a := y; \end{vmatrix} y := 1; \\ b := x;$      | x := 1; $y := 1;$ <b>sfence</b> ; a := y; b := x;             |  |

| a=1 ∧ b=0: <b>X</b>                                                                                           | a=1 ∧ <i>x</i> =2: <b>X</b>                                                                 | a=0 ∧ b=0: <b>✓</b>                                                                                                               | a=0 ∧ b=0: <b>X</b>                                                                            | a=0 ∧ b=0: <b>✓</b>                                           |  |

| (a) <u>READ-READ</u>                                                                                          | (b) <u>read-write</u>                                                                       | (c) <u>WRITE-READ</u>                                                                                                             | (d) <u>write-read</u>                                                                          | (e) <u>SFENCE-READ</u>                                        |  |

| $x,y \in \text{Loc}_{uc \cup wb \cup wt}$                                                                     | $x, y \in Loc_{wc \cup wb}, x \in Loc_{wc} \lor y \in Loc_{wc}$                             | $x, y \in \text{Loc}_{wb  \cup  wt  \cup  wc}$                                                                                    | $x \in Loc_{wb \cup  wt \cup  wc},$ $y \in Loc_{wb \cup  wc}$                                  | $y \in Loc_{wb \cup wt \cup wc},$<br>$x \in Loc_{wb \cup wc}$ |  |

| x := 2; <b>mfence</b> ; $y := 1;$ $y := 2;$ $x := 1;$                                                         | x := 2; <b>mfence</b> ; $y := 1;$ $y := 2;$ $x := 1;$                                       | $\begin{vmatrix} x := 2; \\ \mathbf{mfence}; \\ y := 1; \end{vmatrix} \begin{vmatrix} y :=_{NT} 2; \\ x :=_{NT} 1; \end{vmatrix}$ | $\begin{vmatrix} x := 2; \\ \mathbf{mfence}; \\ y := 1; \end{vmatrix} y := 2; \\ x :=_{NT} 1;$ | x:= 2; <b>mfence</b> ;<br>$y:= 1;$ $y:=_{NT}2;$ $x:= 1;$      |  |

| $x=2 \land y=2: X$                                                                                            | $x=2 \land y=2: \checkmark$                                                                 | $x=2 \land y=2: \checkmark$                                                                                                       | $x=2 \land y=2: \checkmark$                                                                    | $x=2 \land y=2: \checkmark$                                   |  |

| (f) <u>write-write</u>                                                                                        | (g) <u>write-write</u>                                                                      | (h) <u>write-write</u>                                                                                                            | (i) <u>write-write</u>                                                                         | (j) <u>write-write</u>                                        |  |

Fig. 1. Ex86 Litmus tests illustrating possible reordering of read and write instructions and the resulting weak behaviours, where ✓ (resp. ✗) denotes that the depicted weak behaviour is (resp. is not) observed. The <u>underlined</u> subfigure captions are hyperlinks to the corresponding (class of) tests in our validation effort.

observe  $a=1 \land b=0$ : when b:=x is reordered before a:=y, then this outcome is observed when all instructions of the left thread are executed between b:=x and a:=y. However, as corroborated by our validation (see READ-READ), we ran each variant (with different memory types for x and y) of the Fig. 1a program 1.5 billion times, and never observed  $a=1 \land b=0$ . Analogously, the  $a=1 \land x=2$  behaviour was never observed in any of the variants of the program in Fig. 1b (see READ-WRITE). We therefore conclude that read-read and read-write reordering are not allowed under Ex86, regardless of the memory types of the underlying locations.

**Earlier Reads and Later sfence** ( $\checkmark$ <sup>†</sup> **in Fig. 2**). As noted by Raad et al. [2020], although **sfence** instructions are not ordered with respect to reads, reordering an earlier read after a later **sfence** does not affect the program behaviour: as earlier reads are ordered with respect to all other later instructions, reordering them after a later **sfence** does not alter the program behaviour. That is, given a program  $P \triangleq a := x$ ; **sfence**; c with  $c \neq sfence$ , the a := x read cannot be reordered after c, and reordering it after **sfence** alone does not affect the behaviour of P. As such, as in [Raad et al. 2020], we opt to order earlier reads and *all* later memory instructions, including later **sfence**.

*Write-Write Reordering*. As briefly discussed above (1) write-write reordering is allowed on wc memory; and (2) wb writes can be reordered (in both directions) with respect to wc writes. That is, write-write reordering is allowed when one write is on wc memory, and the other is on either wc or wb memory. This is illustrated in Fig. 1g: as before, the writes of the left thread cannot be reordered thanks to **mfence**; however, the two writes of the right thread may be reordered since  $x, y \in \text{Loc}_{wc} \cup \text{wb}$  and  $x \in \text{Loc}_{wc} \vee y \in \text{Loc}_{wc}$ . As such, when all instructions of the left thread execute before x := 1 and after y := 1, then the  $x = 2 \wedge y = 2$  weak behaviour shown can be observed, as confirmed by our experiments (see <u>WRITE-WRITE</u>). By contrast, write-write ordering is disallowed when neither write is on wc memory, as shown in Fig. 1f: as  $x, y \in \text{Loc}_{uc} \cup \text{wb} \cup \text{wt}$ , the writes of the right thread cannot be reordered and thus the weak behaviour  $x = 2 \wedge y = 2$  cannot be observed.

Note that since non-temporal writes follow wc semantics, write-write reordering is also allowed when one write is non-temporal (on wb/wt/wc memory) and the other is either a non-temporal write or a write on wc or wb memory. This is illustrated in the examples of Figs. 1h to 1j.

*Write-Read Reordering.* As discussed above, write-read reordering is allowed on both wb and wt. Indeed, later reads on wb and wt memory (i.e. on c memory) can be reordered before *all* writes, regardless of their memory type. This is illustrated in Fig. 1c, depicting a variant of the 'store-buffering' (SB) litmus test with an additional **mfence**. As before, the instructions of the left thread cannot be reordered due to the intervening **mfence**. However, the b:= x read on c memory ( $x \in Loc_c$ ) can be reordered before the earlier y:= 1 write regardless of the memory type of y ( $y \in Loc_c$ ). As such, when all instructions of the left thread execute between b:= x and y:= 1, then the a=0  $\wedge$  b=0 behaviour shown can be observed, as confirmed by our experiments (see WRITE-READ).

By contrast, the reads on non-cacheable (nc) memory cannot be reordered before any earlier writes, as shown in Fig. 1d. That is, unlike in Fig. 1c, the b:= x read on nc memory ( $x \in Loc_{nc}$ ) cannot be reordered before y:=1 ( $y \in Loc$ ), and thus the a=0  $\land$  b=0 weak behaviour shown is not observed, as corroborated by our experiments (see WRITE-READ).

Finally, as non-temporal writes follow wc semantics, write-read reordering is also allowed (resp. disallowed) for a non-temporal write and a read on c (resp. nc) memory. That is, if we replace y := 1 in Figs. 1c and 1d with  $y :=_{NT} 1$  ( $y \in Loc_{wb \cup wt \cup wc}$ ), then the outcomes shown will remain unchanged.

**Earlier sfence and Later Non-Cacheable Reads** ( $\sqrt{\phantom{a}}$  in Fig. 2). Although **sfence** instructions are not ordered with respect to reads, reordering a later nc read before an earlier **sfence** does not affect the program behaviour: as later nc reads are ordered with respect to all other earlier instructions under Ex86, reordering them before **sfence** does not alter the program behaviour. That is, given a program  $P \triangleq c$ ; **sfence**; a := x with  $c \neq sfence$  and  $x \in Loc_{nc}$ , the a := x read cannot be reordered before c, and reordering it before **sfence** alone does not affect the P behaviour. As such, for simplicity we opt to order *all* earlier instructions (including earlier **sfence**) and later nc reads.

By contrast, reordering a later c read before an earlier **sfence** can be observed because later c reads can be reordered before earlier writes. An example of this is illustrated in Fig. 1e, depicting a variant of SB with **sfence** instructions: without loss of generality, when  $x \in Loc_c$ , then the b := x read can be reordered before both **sfence** and y:= 1, allowing us to observe a=0  $\wedge$  b=0.

**Cache Line Instructions**. As discussed above, a location x in wb memory may be cached in that a store to x does not immediately reach the memory; rather, for better performance the store may be cached and written back (evicted) to memory at a later time (e.g. when the cache is full). In order to afford more control over when stores reach the memory, Intel-x86 architectures provide three *persist instructions* (described at length in §2.2 below) for writing back a given cache line to memory: **flush** x, **flush**<sub>opt</sub> x and **wb** x. More concretely, given a location x in cache line (set of locations) X, written  $x \in X$ , executing **flush** x, **flush**<sub>opt</sub> x or **wb** x writes back the x cache line to memory. As described in [Intel 2021] and formalised by Raad et al. [2020], persist instructions vary in strength (their constraints on instruction reordering) and performance: **flush** is the strongest of the three (enforcing additional ordering constraints), while **flush**<sub>opt</sub> and **wb** are equally weak with **wb** offering better performance than **flush**<sub>opt</sub>. That is, **flush**<sub>opt</sub> and **wb** have the same specification and exhibit equivalent behaviour; as such, as in [Raad et al. 2020], we only model **flush** and **flush**<sub>opt</sub>. Nevertheless, all behaviours and specifications ascribed to **flush**<sub>opt</sub> also hold of **wb**.

As mentioned above, **flush** instructions enforce strong ordering constraints with respect to writes and other **flush** in that they are ordered with respect to (1) *all* earlier and later **flush**; and (2) *all* earlier and later (non-temporal) writes regardless of their memory type. As such, **flush**

$<sup>^2</sup>$ In [Intel 2021], **flush** is referred to as **CLFLUSH**, **flush**<sub>opt</sub> is referred to as **CLFLUSHOPT** and **wb** is referred to as **CLWB**.

behaves as an **sfence** when inserted between two writes that could otherwise be reordered. For instance, were we to insert **flush** z between the two stores of the right threads in Figs. 1g to 1j, then they could no longer be reordered and thus the weak behaviour  $x=2 \land y=2$  could not be observed. Our tests in our validation effort have confirmed the strong ordering enforced by **flush** (see HERE).

By contrast,  $\mathbf{flush}_{opt}$  instructions are only ordered with respect to earlier writes on the same cache line. As such, unlike  $\mathbf{flush}$ , they cannot serve as an  $\mathbf{sfence}$  as they can be reordered after later writes. Although we ran extensive tests on several machines to validate the behaviour of  $\mathbf{flush}_{opt}$ , we could not observe the weak behaviours enabled by  $\mathbf{flush}_{opt}$  except in a few cases. This is because the  $\mathbf{flush}_{opt}$  implementation is commonly stronger than its specification (in the Intel manual), as was the case on all machines available to us for testing. Nevertheless, as our validation endeavour confirmed that the manual faithfully captures the behaviour of  $\mathbf{flush}$ , we chose to 'trust' the weak behaviour of  $\mathbf{flush}_{opt}$  as specified in the manual and reflected it in our Ex86 formalism, albeit without validating it. However, note that  $\mathbf{flush}_{opt}$  instructions constitute a small fragment of the Ex86 language and are the only instruction in our Ex86 model that we could not validate. As such, we argue that Ex86 is fully validated up to implementation fidelity.

Ordering between flush and flush<sub>opt</sub> ( $X^*$  in Fig. 2). An earlier version of the Intel reference manual [Intel 2019] stated that flush and flush<sub>opt</sub> on the same cache line are ordered with respect to one another, as later reflected in the Px86<sub>sim</sub> model of Raad et al. [2020]. This older version of the manual has since been removed from the Intel pages and is currently only available through the Internet Archive [Intel 2019]. However, the latest version of the manual [Intel 2021] has weakened this constraint, guaranteeing no ordering between flush and flush<sub>opt</sub>. As such, we have accordingly left out this constraint from our Ex86 model, thus minorly diverging from Px86<sub>sim</sub>.

**Putting it All Together: Ex86 Ordering Constraints.** Fig. 2 presents a summary of ordering constraints between earlier (in program order) instructions (rows) and later instructions (columns) under Ex86, where  $R_t$  and  $W_t$  denote reads and writes on t memory, respectively; MF, SF and U denote **mfence**, **sfence** and RMW (update) instructions, respectively; FL and FO denote **flush** and **flush**<sub>opt</sub> instructions, respectively; and NTW denote *non-temporal* writes. If two instructions are ordered (denoted by ✓), they cannot be reordered and thus their program order (i.e. the order in which they appear in the program) and store order (the order in which they are made visible to other threads) always agree. Conversely, if two instructions are unordered and thus can be reordered (denoted by X), then their program and store orders may disagree. The sloc (resp. scl) entries denote that two instructions are ordered if and only if they access the same location (resp. cache line). The white (not highlighted) cells in the table correspond to the Px86<sub>sim</sub> model by Raad et al. [2020]. We develop Ex86 by extending Px86<sub>sim</sub> with Intel-x86 memory types and non-temporal stores. The ordering constraints on the Ex86 extensions are denoted by the highlighted cells. All permitted reorderings (i.e. non-✓ entries), except those of **flush**<sub>opt</sub> (i.e. in the FO row or column), are annotated with links to our validation tests that witness the reordering as a weak behaviour.

#### 2.2 PEx86: The Persistent Ex86 Model

We next present PEx86, our extension of Ex86 that additionally accounts for the persistency semantics of Intel-x86 memory types and non-temporal writes in the presence of non-volatile memory. Persistency models are typically categorised along two axes: (1) strict or relaxed persistency; and (2) unbuffered or buffered persistency. Under *strict persistency*, instruction effects persist to memory in the order they become visible to other threads, i.e. the volatile and persistent memory orders coincide. By contrast, relaxed persistency allows for volatile and persistent memory orders to disagree. The second categorisation describes *when* persists occur. Under *unbuffered persistency*, persists occur *synchronously*: instruction effects are immediately committed to persistent memory

|     | Later in Program Order |                                               |                       |            |            |               |          |          |                                           |                            |             |          |            |          |            |

|-----|------------------------|-----------------------------------------------|-----------------------|------------|------------|---------------|----------|----------|-------------------------------------------|----------------------------|-------------|----------|------------|----------|------------|

|     |                        | 1                                             | 2                     | 3          | 4          | 5             | 6        | 7        | 8                                         | 9                          | 10          | 11       | 12         | 13       | 14         |

|     |                        | $R_{\sf wb}$                                  | $R_{wt}$              | $R_{uc}$   | $R_{WC}$   | $W_{wb}$      | $W_{wt}$ | $W_{uc}$ | $W_{ m wc}$                               | NTW                        | U           | MF       | SF         | FL       | FO         |

| A   | $R_{\sf wb}$           | <b>√</b>                                      | ✓                     | <b>✓</b>   | <b>\</b>   | ✓             | <b>✓</b> | <b>✓</b> | ✓                                         | ✓                          | <b>\</b>    | ✓        | ✓†         | <b>✓</b> | ✓          |

| В   | $R_{wt}$               | <b>✓</b>                                      | ✓                     | /          | /          | <b>✓</b>      | <b>✓</b> | <b>✓</b> | ✓                                         | ✓                          | <b>\</b>    | 1        | <b>✓</b> † | <b>✓</b> | ✓          |

| С   | $R_{\sf uc}$           | <b>✓</b>                                      | ✓                     | 1          | 1          | ✓             | 1        | 1        | 1                                         | ✓                          | <b>✓</b>    |          | <b>√</b> † | 1        | ✓          |

| D   | $R_{WC}$               | <b>✓</b>                                      | ✓                     | <b>\</b>   | /          | 1             | <b>✓</b> | <b>✓</b> | 1                                         | ✓                          | /           | 1        | ✓†         | 1        | 1          |

| Е   | $W_{\sf wb}$           | X                                             | Х                     | \          | /          | /             | 1        | /        | X                                         | sloc                       | /           | 1        | 1          | /        | scl        |

| 15  | Wb Wb                  | <u>1, 2</u>                                   | <u>3, 4</u>           | •          | >          | •             | •        | >        | <u>5</u> , <u>6</u> , <u>7</u> , <u>8</u> | <u>9, 10, 11, 12, 13</u>   | <b>&gt;</b> | •        | •          | ľ        | SCI        |

| F   | $W_{ m wt}$            | Х                                             | Х                     | 1          | 1          |               |          |          | 1                                         | 1                          | 1           |          | /          |          | 1          |

|     | ,, Mr                  | <u>14, 15</u>                                 | <u>16, 17</u>         | •          |            |               | •        | _        | •                                         |                            | •           | _        |            |          |            |

| G   | $W_{\sf uc}$           | X                                             | X                     | 1          | 1          |               |          |          | 1                                         | 1                          | 1           | /        | /          | 1        | 1          |

|     | " uc                   | <u>18, 19</u>                                 | <u>20</u> , <u>21</u> |            |            |               |          |          | ·                                         | <u> </u>                   | Š           | Ľ        |            |          | _          |

|     |                        | Х                                             | X                     |            |            | X             |          |          | sloc                                      | sloc                       |             |          |            |          |            |

| H   | $W_{wc}$               | <u>22, 23</u>                                 | 24, 25                | <b>\</b>   | <b>/</b>   | <u>26, 27</u> | <b>/</b> | <b>√</b> | <u>30</u> , <u>31</u> , <u>32</u>         | <u>35, 36, 37</u>          | <b>/</b>    | <b>/</b> | <b>~</b>   | <b> </b> | scl        |

|     |                        |                                               |                       |            |            | <u>28, 29</u> |          |          | <u>33, 34</u>                             | <u>38, 39, 40</u>          |             |          |            |          |            |

|     |                        | v                                             | v                     |            |            | sloc          |          |          | sloc                                      | sloc                       |             |          |            |          |            |

| Ι   | NTW                    | X                                             | X                     | 1          | 1          | 49, 50, 51    | 1        | 1        | <u>55, 56 57</u>                          | <u>60, 61, 62, 63</u>      | 1           | 1        | 1          | 1        | scl        |

|     |                        | <u>41</u> , <u>42</u> , <u>43</u> , <u>44</u> | 45, 46, 47, 48        |            |            | 52, 53, 54    |          |          | <u>58, 59</u>                             | <u>64, 65, 66, 67</u>      |             |          |            |          |            |

| T   | U                      | /                                             |                       | /          | /          | /             | /        | /        | /                                         | <u>68, 69, 70, 71</u><br>✓ | /           | /        | /          | 1        | /          |

| K   | MF                     | <b>✓</b>                                      | /                     | <u>/</u>   | <u>/</u>   | <b>/</b>      | <i>'</i> | <i>'</i> | 1                                         | <u> </u>                   | <u>/</u>    | 1        | 1          | 1        | <b>✓</b>   |

|     | IVII                   | X                                             | X                     | •          | •          | •             | •        | •        | •                                         | <u> </u>                   | •           | _        | •          | •        | •          |

| L   | SF                     | 72, 73, 74, 75                                | 80, 81, 82, 83        | <b>/</b> ‡ | <b>√</b> ‡ | /             | /        |          | 1                                         | ,                          | 1           | /        | /          | /        | 1          |

| L   | 31                     | 76, 77, 78, 79                                |                       | •          | •          | •             | •        | •        | •                                         | •                          | •           | *        | *          |          | •          |

| M   | FL                     | X <u>88</u>                                   | X 89                  | /          | /          | 1             | 1        | /        | 1                                         |                            | /           | /        | /          | /        | <b>X</b> * |

| N   | FO                     | X                                             | X                     | <u> </u>   | <u> </u>   | X             | 1        | /        | X                                         | Х                          | <b>✓</b>    | /        | /          | X*       | X          |

| - 1 | 10                     | •                                             | ,,                    | _          | •          | •             | •        |          | •                                         |                            | •           | _        |            | •        | •          |

Fig. 2. The Ex86 ordering constraints where  $\checkmark$  denotes that two instructions are ordered, X denotes they are not ordered (and thus may be reordered), and sloc (resp. scl) denotes that they are ordered iff they are on the same location (resp. cache line); see pp. 7, 8 and 9 for explanations of  $\checkmark^{\dagger}$ ,  $\checkmark^{\ddagger}$  and  $X^{*}$ , respectively. The highlighted cells denote the Ex86 extensions from Px86<sub>sim</sub> [Raad et al. 2020]. All non- $\checkmark$  entries (but those of FO) are accompanied with links to litmus tests in our validation effort that witness the associated reordering.

upon execution; i.e. execution is stalled by persists. By contrast, *buffered persistency* allows memory persists to occur *asynchronously* [Condit et al. 2009], buffering memory persists in a queue to be committed to memory at a later time. This way, persists occur after their corresponding stores and as prescribed by the persistent memory order; however, execution may proceed ahead of persists. As such, upon crash recovery, only a *prefix* of the persistent memory order may have persisted.

The persistency semantics of wb memory has been previously formalised by Raad et al. [2020] and later refined in [Cho et al. 2021; Khyzha and Lahav 2021]. As we describe shortly, wb memory follows relaxed, buffered persistency. Specifically, recall that wb writes are cached and propagated (persisted) to memory at a later time, thus following buffered persistency. Moreover, for better performance, cached wb writes may be persisted to memory in a different order than that they were cached (made visible to to other threads), thus enabling relaxed persistency.

We develop PEx86 as the first formal Intel-x86 persistency semantics that accounts for wc, wt and uc memory and non-temporal writes. As we describe below, wc, wt and uc all follow strict, unbuffered persistency. In the case of nc (wc and uc) memory, this is due to their non-cacheability: nc writes bypass the caches and directly interact with memory. As such, nc writes reach (persist

| $x, y \in Loc_{wb}$      | $x, x', y \in Loc_{wb}$    | $x, x', y \in Loc_{wb}$     | $x, x', y \in Loc_{wb}$            | $x, x', y \in Loc_{wb}$             | $x \in Loc_{wb},$<br>$y \in Loc$ |

|--------------------------|----------------------------|-----------------------------|------------------------------------|-------------------------------------|----------------------------------|

| x:= 1;                   | x:= 1;                     | x:= 1;                      | x:= 1;                             | x:= 1;                              | C ≜ x := 1;                      |

| y:= 1                    | flush $x'$ ;               | flush <sub>opt</sub> $x'$ ; | <b>flush</b> <sub>opt</sub> $x'$ ; | $\mathbf{flush}_{\mathrm{opt}} x';$ | <i>y</i> := 1                    |

|                          | y:= 1                      | y:= 1                       | $\mathbf{FAA}(y,1)$                | sfence;                             |                                  |

|                          |                            |                             |                                    | y:= 1                               |                                  |

| (a)                      | (b)                        | (c)                         | (d)                                | (e)                                 | (f)                              |

| rec: $x, y \in \{0, 1\}$ | rec: $y=1 \Rightarrow x=1$ | rec: $x, y \in \{0,1\}$     | rec: $y=1 \Rightarrow x=1$         | rec: $y=1 \Rightarrow x=1$          | rec: $x, y \in \{0,1\}$          |

| $x, x' \in Loc_{wb},$      | $x \in Loc_{WC}$           | $x \in Loc_{WC}$         | $x \in Loc_{uc \cup wt}$   | $x \in \text{Loc}_{wb \cup  wt \cup  wc}$ | $x \in Loc_{wb \cup wt \cup wc}$ |

|----------------------------|----------------------------|--------------------------|----------------------------|-------------------------------------------|----------------------------------|

| y∈Loc                      | $y \in Loc_{uc \cup wt}$   | $y \in Loc_{wc \cup wb}$ | y∈Loc                      | $y \in Loc_{uc \cup wt}$                  | $y \in Loc_{wc \cup wb}$         |

| $C_P \triangleq x := 1;$   | x := 1;                    | x := 1;                  | x := 1;                    | x := 1;                                   | x := 1;                          |

| persist $x'$ ;             | <i>y</i> := 1              | y:= 1                    | <i>y</i> := 1              | $x :=_{NT} 2;$                            | $x :=_{NT} 2;$                   |

| y:= 1                      |                            |                          |                            | y:= 1                                     | sfence;                          |

|                            |                            |                          |                            |                                           | y:= 1                            |

| (g)                        | (h)                        | (i)                      | (j)                        | (k)                                       | (1)                              |

| $rec: y=1 \Rightarrow x=1$ | rec: $y=1 \Rightarrow x=1$ | $rec: x, y \in \{0,1\}$  | rec: $y=1 \Rightarrow x=1$ | rec: $y=1 \Rightarrow x=2$                | rec: $y=1 \Rightarrow x=2$       |

Fig. 3. Examples of PEx86 programs and possible values of x, y upon recovery; in all examples x, y are locations in persistent memory where x=y=0 initially, a is a (local) register, x,  $x' \in X$  (x, x' are in cache line X),  $y \notin X$ , and persist x denotes either **flush** x or **flush**<sub>opt</sub> x;  $c_b$ , where  $c_b$  is either **mfence**, **sfence** or an atomic update (RMW). Replacing an **sfence** with **mfence** or an RMW yields the same result upon recovery.

to) memory synchronously, at which point they also become visible to other threads (i.e. the store and persist orders are one and the same), thus following strict, unbuffered persistency. Analogously, recall that wt writes are cached (made visible to other threads) and also written to memory immediately (i.e. persisting the writes synchronously and in the same order as they were made visible to other threads), therefore following strict, unbuffered persistency. Lastly, as non-temporal writes are subject to we semantics, they also follow strict, unbuffered persistency.

We next describe PEx86 persistency through several examples in Figs. 3 and 4. The rec specification below each example denotes possible values observed in memory upon recovery from a crash at an *arbitrary* program point. That is, we make no assumptions of when the crash occurs; rather, we assume that a crash may occur at any point during the execution.

**Persistency of wb Memory.** The relaxed, buffered persistency of wb is reflected in the example of Fig. 3a. Due to the buffered nature of persists, if a crash occurs during the execution of this program, at crash time either write may or may not have already persisted and thus  $x, y \in \{0, 1\}$  upon recovery. Note that the relaxed nature of wb persistency admits somewhat surprising behaviours that are not possible during normal (non-crashing) executions. In particular, at no point during the normal execution of the program the x=0,  $y\ne 1$  behaviour is observable: the two wb writes cannot be reordered under Intel-x86. Nevertheless, in case of a crash it is possible to observe y=1, x=0 after recovery. This is due to relaxed persistency of wb: the store order, describing the order in which writes are made visible to other threads (x before y), is separate from the persist order, describing the order in which writes are persisted to memory (y before x). More concretely, two wb writes may be persisted (1) in any order, when they are on distinct locations; or (2) in the store order, when they are on the same location. That is, for each wb location, its store and persist orders coincide.

In order to afford more control over when pending writes are persisted, the persist instructions, namely **flush** x and **flush**<sub>opt</sub> x, can be used to persist the pending writes on all locations in the

cache line of x. The persist behaviour of **flush** is illustrated in Fig. 3b: when  $x, x' \in X$  (i.e. x, x' are in cache line X), executing **flush** x' persists the earlier write on X (i.e. x:=1) to memory. As such, if a crash occurs during the execution of Fig. 3b and upon recovery y=1, then x=1. That is, if y:=1 has executed and persisted before the crash, then so must the earlier x:=1; **flush** x'. Note that this behaviour is guaranteed thanks to the ordering constraints on **flush** instructions. Specifically, as we discussed in §2.1, **flush** instructions are ordered with respect to all writes; as such, **flush** x' in Fig. 3b cannot be reordered with respect to either write, and thus upon recovery  $y=1 \Rightarrow x=1$ .

However, instruction reorderings mean that persist instructions may not execute at the intended program point and thus may not guarantee the intended persist ordering. For instance, recall that when  $x' \in X$ ,  $\mathbf{flush}_{\mathrm{opt}} x'$  is only ordered with respect to earlier writes on the same cache line X and thus may be reordered with respect to writes on locations in different cache lines, i.e. those not in X. This is illustrated in the example of Fig. 3c: since  $y \notin X$ , the  $\mathbf{flush}_{\mathrm{opt}} x'$  in Fig. 3c is not ordered with respect to y:=1 and may be reordered after it. Therefore, if a crash occurs after y:=1 has executed and persisted but before  $\mathbf{flush}_{\mathrm{opt}} x'$  has executed, then upon recovery it is also possible to observe y=1, x=0. That is, there is no guarantee that x:=1 persists before y:=1, despite the intervening  $\mathbf{flush}_{\mathrm{opt}} x'$ . By contrast, recall that  $\mathbf{flush}_{\mathrm{opt}}$  instructions are ordered with respect to (earlier and later) RMW,  $\mathbf{sfence}$  and  $\mathbf{mfence}$  instructions. As such,  $\mathbf{flush}_{\mathrm{opt}} x'$  in Fig. 3d cannot be reordered after  $\mathbf{FAA}(y,1)$  and thus  $y=1 \Rightarrow x=1$  upon recovery. Similarly,  $\mathbf{flush}_{\mathrm{opt}} x'$  in Fig. 3e cannot be reordered after  $\mathbf{sfence}$  and once again  $y=1 \Rightarrow x=1$  upon recovery.

In summary, given wb locations x, x' in the same cache line, to ensure that a write on x is persisted, one can use a *persist sequence* on x', written persist x', via either (1) **flush** x'; or (2) **flush**<sub>opt</sub> x';  $c_b$ , where  $c_b$  is an **mfence**/**sfence**/RMW. Conceptually, one can think of **flush** as *synchronous* (it blocks until all pending writes in its cache line have persisted), and of **flush**<sub>opt</sub> as *asynchronous* (it may not persist the pending writes at the intended program point) *unless* followed by a barrier as in (2). This pattern is shown in Fig. 3g, where persist x' ensures that x:=1 on wb memory is persisted before executing y:=1, ensuring  $y=1 \Rightarrow x=1$  on recovery. That is, regardless of the y memory type ( $y \in Loc$ ), the persist x' sequence cannot be reordered after y:=1 (as **flush**, **mfence**, **sfence** and RMWs are ordered with respect to all writes), ensuring  $y=1 \Rightarrow x=1$  on recovery. By contrast, without the persist sequence in Fig. 3f, the wb write x:=1 may not have yet persisted when executing y:=1 on arbitrary memory ( $y \in Loc$ ), and thus if a crash occurs after y:=1 has executed and persisted but before x:=1 has persisted, then one may also observe y=1, x=0 on recovery.

**Persistency of wc, uc and wt Memory**. As mentioned above, wc, uc and wt memory all follow strict, unbuffered persistency, as shown in Figs. 3h and 3j. In the case of Fig. 3h, as  $x \in Loc_{wc}$ , executing x := 1 directly writes to memory; moreover, as  $y \in Loc_{uc \cup wt}$ , the two writes cannot be reordered. As such if upon recovery y := 1 has executed and persisted (y=1), then so must the earlier x := 1 (x=1). Similarly, in the case of Fig. 3j, as  $x \in Loc_{uc \cup wt}$ , the two writes cannot be reordered and executing x := 1 directly writes to memory, and thus  $y=1 \Rightarrow x=1$  on recovery.

Note that as wc writes can be reordered with respect to wb/wc writes, it may be executed (and thus persisted) out of order. This is illustrated in Fig. 3i: as  $x \in Loc_{wc}$  and  $y \in Loc_{wc \cup wb}$ , the x := 1 can be reordered after y := 1. As such, if a crash occurs after y := 1 has executed and persisted but before x := 1 has executed, then it is also possible to observe y = 1, x = 0 upon recovery.

**Persistency of Non-Temporal Writes**. As mentioned above, as with wc memory, non-temporal writes follow strict unbuffered persistency. For instance, were we to replace x := 1 in Figs. 3h and 3j with  $x :=_{NT} 1$  such that  $x \in Loc_{wb} \cup_{wt} \cup_{wc}$ , then their recovery specifications would remain unchanged. Interestingly, a non-temporal store on  $x \in Loc_{wb}$  additionally serves as a *persist instruction* in that it persists (evicts) the pending (in-cache) writes on x to memory – see (NT) above. This is illustrated in Fig. 3k when  $x \in Loc_{wb}$ . Specifically, (1) as  $y \in Loc_{uc} \cup_{wt}$  and the first two writes are on the

| $x \in Loc_{wb}$ ,                                                     | $x \in Loc_{wb}$ ,                                                 | $x \in Loc_{WC}$                                                   | $x \in Loc_{WC}$                                                   | $x \in Loc_{uc \cup wt}$                                           | $x \in Loc_{uc \cup wt}$                                           |

|------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|

| y∈Loc                                                                  | y∈Loc                                                              | $y \in Loc_{wc \cup wb}$                                           | $y \in Loc_{uc \cup wt}$                                           | $y \in Loc_{wb}$                                                   | y ∉ Loc <sub>wb</sub>                                              |

| $C_{P} \begin{vmatrix} a := y; \\ if (a = 1) \\ z := 1; \end{vmatrix}$ | $C \begin{vmatrix} a := y; \\ if (a = 1) \\ z := 1; \end{vmatrix}$ | $C \begin{vmatrix} a := y; \\ if (a = 1) \\ z := 1; \end{vmatrix}$ | $C \begin{vmatrix} a := y; \\ if (a = 1) \\ z := 1; \end{vmatrix}$ | $C \begin{vmatrix} a := y; \\ if (a = 1) \\ z := 1; \end{vmatrix}$ | $C \begin{vmatrix} a := y; \\ if (a = 1) \\ z := 1; \end{vmatrix}$ |

| (a)                                                                    | (b)                                                                | (c)                                                                | (d)                                                                | (e)                                                                | (f)                                                                |

| $rec: x^P \wedge y \wedge y^P$                                         | $rec: x \wedge y \wedge y^P$                                       | rec: x ∧y ∧y <sup>P</sup>                                          | rec: x <sup>P</sup> ∧y <sup>P</sup>                                | rec: x <sup>P</sup> ∧ y                                            | $rec: x^P \wedge y^P$                                              |

Fig. 4. Examples of concurrent PEx86 programs and possible values of x, y, z upon recovery, where C and Cp are as defined in Fig. 3; all examples use the same notation and conventions as in Fig. 3.

same location x, all three writes are ordered with respect to one another and thus no reordering is allowed; and (2) executing  $x:=_{NT} 2$  first ensures that the earlier x:=1 is persisted to memory, and then writes 2 to x in memory. As such, if upon recovery y:=1 has executed and persisted (y=1), then so must  $x:=_{NT} 2$  (x=2). Note that if y in Fig. 3k were instead in wc/wb memory, y:=1 could be reordered before both writes on x, and on recovery it would be possible to observe  $x \in \{0, 1, 2\}$  even when y=1. To prevent this reordering, we can insert an **sfence** (or **mfence**/RMW) before y:=1, as illustrated in Fig. 3l, restoring  $y=1 \Rightarrow x=2$ .

Concurrent Persistency Examples. The examples discussed thus far all concern sequential programs and the persist orderings in the *same* thread. The example in Fig. 4 illustrates how persist orderings can be imposed on *different* threads. Note that  $C_P$  and C in the left threads of Figs. 4a to 4f are as defined in Fig. 3. Under PEx86 one can use *message-passing* between threads to enforce persist ordering. A message is passed from thread  $\tau_1$  to  $\tau_2$  when  $\tau_2$  reads a value written by  $\tau_1$ .

For instance, if the right thread in Fig. 4a reads 1 from y (written by  $C_P$  in the left thread), then the left thread passes a message to the right thread. Message passing ensures that the instruction writing the message (e.g. y:= 1) is executed (ordered) before the instruction reading it (e.g. a:= y). As such, since x:= 1; persist x' (in  $C_P$ ) is executed before y:= 1 (as in Fig. 3g), y:= 1 is executed before a:= y, and z:= 1 is executed after a:= y when a=1, we know x:= 1; persist x' is executed before z:= 1. Consequently, if upon recovery z=1 (i.e. z:= 1 has executed and persisted before the crash), then x=1 (x:= 1; persist x' must have also persisted before the crash, as given by  $x^P$ .

By contrast, in the absence of persist x' in Fig. 4b, we have  $z=1 \Rightarrow x \in \{0,1\}$ , as denoted by x. This is because as  $x \in Loc_{wb}$ , the x:=1 (in C) may persist after z:=1, even though it is executed before it. As such, if a crash occurs after z:=1 has executed and persisted but before x:=1 has persisted, it is possible to observe z=1, x=0 on recovery, even though z=1, z=0 is never possible during non-crashing executions. Similarly, if  $y \in Loc_{wb}$ , then in both Figs. 4a and 4b the y:=1 may persist after z:=1, and thus it is possible to observe z=1, y=0 on recovery, as captured by z=1. On the other hand, if z=1 is persisted to memory as soon as it is executed (z=1), then in both Figs. 4a and 4b the z=1 is persisted to memory as soon as it is executed. Therefore, if upon recovery z=1, then z=1, as denoted by z=1.

The remaining examples in Figs. 4c to 4f all use message passing and thus the values of y upon crash recovery are analogously captured by x and  $x^P$ , depending on the memory type of y. Moreover, in all Figs. 4c to 4f, x is persisted as soon as it is executed since it is in wc/uc/wt memory (subject to strict, unbuffered persistency). In Figs. 4d to 4f, the x:= 1 and y:= 1 writes in C cannot be reordered as either x or y is in uc/wt memory. As such, in Figs. 4d to 4f x:= 1 is executed before y:= 1, and (due

to message passing) y:=1 is executed before z:=1; consequently, upon recovery if z=1, then x=1 (given by  $x^P$ ). By contrast, in Fig. 4c as  $x \in Loc_{wc}$  and  $y \in Loc_{wc \cup wb}$ , the x:=1 and y:=1 writes in C may be reordered. Consequently, z:=1 may be executed after y:=1 but before x:=1, additionally allowing us to observe z=1, x=0, upon recovery (given by x).

The Challenges of Validating Persistency. As discussed in §2.1, we have successfully extended the diy toolsuite [Alglave and Maranget 2021] to validate the Ex86 consistency model, whereby litmus testing techniques are used to monitor the store order (the order in which writes are made visible to threads). Unfortunately, however, these techniques cannot currently be used to validate a persistency model: doing so involves monitoring the persist order (the order in which writes are persisted from processor caches to non-volatile memory), which is invisible to the processors. Specifically, the contents of memory cannot be observed directly while employing caches, and a program (litmus test) alone cannot distinguish volatile (in-cache) data from persistent (in-memory) data. The only reliable way to ensure a write persists is to contrive a crash (turn off the machine) and then read persistent data from memory once the machine restarts. However, this only allows one to observe the latest persisted write for each memory location, and is not sufficient to infer the order in which earlier writes persisted. Moreover, continually restarting a machine makes it infeasible to run the large number of tests required for high-coverage validation.

As such, we could not validate PEx86 using conventional litmus-testing techniques. Nevertheless, we argue that PEx86 is a faithful description of Intel-x86 persistency. First, we note that PEx86 is an extension of Px86<sub>sim</sub> (for wb persistency) which was developed in collaboration with (and endorsed by) Intel engineers [Raad et al. 2020]. Second, we formalised the PEx86 extensions (for wc/uc/wt memory and non-temporal writes) by thoroughly studying the Intel reference manual Intel [2021]. Lastly, we formalised these extensions after detailed discussions with the lead architect of the Intel instruction set system architecture, and they have confirmed that our understanding of the persistency semantics of these extensions and our reading of the manual text are accurate. Nevertheless, as we discuss in §7, we aim to validate PEx86 in the future by using custom hardware that allows us to monitor the traffic between the CPU caches and the memory, thus inferring the persist ordering. However, doing so is beyond the scope of this paper.

Verification Techniques for Ex86 and PEx86. As we discuss later, the Ex86/PEx86 models are conservative extensions of the TSO/Px86<sub>sim</sub> models, respectively, in that for programs that do not use the additional features of Ex86/Px86<sub>sim</sub> (non-temporal writes and non-wb memory types), the behaviours of Ex86 and TSO (respectively PEx86 and Px86<sub>sim</sub>) coincide. As such, existing verification techniques for TSO/Px86<sub>sim</sub> can be used to reason about such Ex86/PEx86 programs, e.g. the program logics of OGRA [Lahav and Vafeiadis 2015] and POG [Raad et al. 2020], as well as the model checkers Nidhugg [Abdulla et al. 2015a] and GenMC [Kokologiannakis et al. 2019b]. Moreover, the full Ex86/PEx86 models (including non-temporal writes and all memory types) both meet the conditions stipulated by GenMC; as such, the Ex86 (resp. PEx86) model can be fed into GenMC as-is, yielding a model-checking technique for Ex86 (resp. PEx86) for free.

## 3 THE DECLARATIVE Ex86 SEMANTICS

*Addresses, Locations and Cache Lines.* We assume a set of *addresses*, ADDR, and define memory *locations* as pairs comprising an address and a memory type. We then define *cache lines* as disjoint location sets of the same memory type.

**Definition 1** (Memory types). A memory type  $t \in MTYPE$  may be (strong)-uncacheable, uc; write-through, wt; write-back, wb; or (uncacheable)-write-combining, wc.

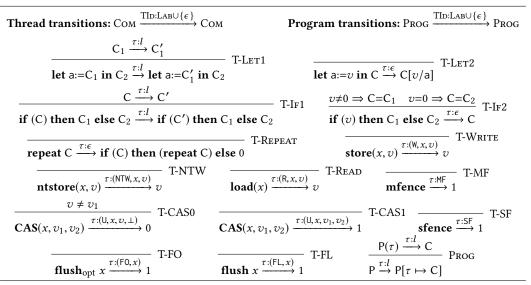

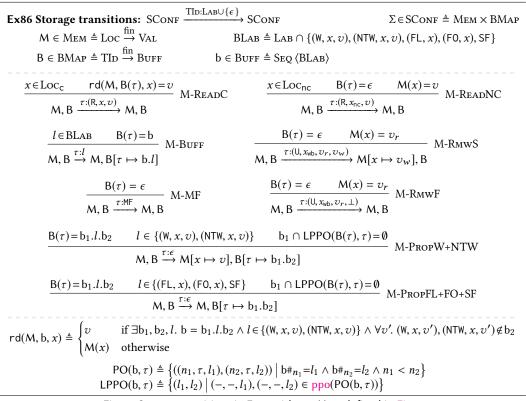

| Basic domains                                              |            | Expressions and sequential commands                                 |                                                                                  |

|------------------------------------------------------------|------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------|

| $a \in Reg$                                                | Registers  | $Exp \ni e ::= v \mid a \mid e + e \mid \cdots$                     | $x_{\sf nt} \in {\sf Loc}_{\sf wb \cup wt \cup wc}$                              |

| $v \in Val$                                                | Values     | $PCom \ni c ::= load(x)   store(x, e)   ntste$                      | $\mathbf{ore}(x_{nt}, \mathbf{e}) \mid \mathbf{CAS}(x, \mathbf{e}, \mathbf{e}')$ |

| $\tau \in TID$                                             | Thread IDs | mfence  sfence  flush <sub>or</sub>                                 | $_{\rm t} x \mid {\bf flush} x$                                                  |

| Programs                                                   | fin.       | $Com \ni C ::= e \mid c \mid \mathbf{let} \ a := C \mathbf{in} \ C$ |                                                                                  |

| Programs $P \in PROG \triangleq TID \xrightarrow{fin} COM$ |            | if (C) then C else C   re                                           | peat C                                                                           |

Fig. 5. A simple concurrent programming language for Ex86 and PEx86

**Derived memory types.** We refer to the uc and wc types collectively as *non-cacheable*:  $nc \triangleq uc \cup wc$ . Analogously, we refer to wt and wb collectively as *cacheable* types:  $c \triangleq wt \cup wb$ .

**Definition 2** (Locations and cache lines). Assume a set of *memory addresses* ADDR. The set of *memory locations*, Loc  $\subseteq$  ADDR  $\times$  MTYPE, is the largest subset of ADDR  $\times$  MTYPE such that:

$$\forall \alpha, \beta, t, t'. (\alpha, t), (\beta, t') \in Loc \land t \neq t' \Rightarrow \alpha \neq \beta$$

Assume a set of cache lines,  $CL \subseteq \mathcal{P}(Loc)$ , such that:

- (1) all locations in a cache line have the same memory type:  $\forall X \in CL$ .  $\exists t. X \subseteq Loc_t$ ; and

- (2) distinct cache lines are disjoint:  $\forall X, Y \in CL. X=Y \lor X \cap Y=\emptyset$ .

Given a memory type t, we write  $Loc_t$  for  $Loc \cap \{(\alpha, t) \mid \alpha \in ADDR\}$ ; e.g.  $Loc_{uc}$  denotes locations in uc memory. Recall from §2 that we assume that the types of locations cannot change once assigned. As such, the definition of locations above requires that the addresses in  $Loc_{uc}$ ,  $Loc_{wt}$ ,  $Loc_{wb}$  and  $Loc_{wc}$  sets be pairwise disjoint. Given a memory type t, we use  $x_t, y_t, \cdots$  as meta-variables for locations in  $Loc_t$ . We write  $x_{nt}$  when  $x \in Loc_{wb \cup wt \cup wc}$ , i.e. x is a location for which the non-temporal hint will not be ignored. When the memory type is immaterial, we simply use  $x, y, \cdots$  as meta-variables for locations in Loc; we use  $X, Y, \ldots$  as meta-variables for cache lines.