#### ETP4HPC's Strategic Research Agenda for High-Performance Computing in Europe 4

Michael Malms, Marcin Ostasz, Maike Gilliot, Pascale Bernier-Bruna, Laurent Cargemel, Estela Suarez, Herbert Cornelius, Marc Duranton, Benny Koren, Pascale Rossé-Laurent, et al.

#### ▶ To cite this version:

Michael Malms, Marcin Ostasz, Maike Gilliot, Pascale Bernier-Bruna, Laurent Cargemel, et al.. ETP4HPC's Strategic Research Agenda for High-Performance Computing in Europe 4. ETP4HPC: European Technology Platform for High Performance Computing, with the support of the EXDCI-2 project., pp.1-108, 2020, ETP4HPC White Papers, 10.5281/zenodo.4605343. hal-03354396

#### HAL Id: hal-03354396 https://inria.hal.science/hal-03354396

Submitted on 24 Sep 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# COMPUTING IN EUROPE

### 'P4HPC's STRATEGIC RESEARCH AGENDA FOR **HIGH-PERFORMANCE**

**MARCH 2020 EUROPEAN** PC RESEARCH Н RIORITIES Ρ 2021-2024

|                                                                   |                                                                        |                                                                 | Next actions                                                                      |                                                                                  |

|-------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Upstream<br>Technologies<br>focus in the<br>2021 – 2024<br>period |                                                                        | Technology<br>sourcing -<br>from chips<br>to system<br>software |                                                                                   | <b>The new</b><br><b>paradigm:</b><br>HPC in<br>the Digital<br>Continuum         |

| Operational<br>Recommendations                                    | The European<br>HPC Ecosystem<br>and other<br>supporting<br>ecosystems |                                                                 | The importance<br>of ethics<br>Building and<br>retaining skills<br>and competence | International<br>arena: HPC<br>and HPDA in<br>Europe, China,<br>the US and Japan |

#### **ETP4HPC Chairman's Message: The future role of HPC**

This issue of our Strategic Research Agenda (SRA) is special as its role now extends beyond the role of the previous SRAs. Its findings will affect the distribution of an increased amount of funding dedicated within EuroHPC to the development of HPC technology and the mechanisms used to stimulate other areas **in the period from 2021 to 2024**. This SRA lays the foundation for this process by defining the European HPC technological priorities based on the input generated by the European HPC technology stakeholders: European HPC vendors, research organisations and users as well as the stakeholders of the related technologies.

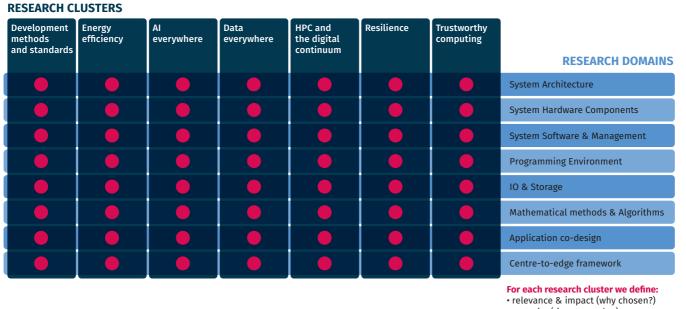

This SRA approaches research priorities from a different angle. I urge the Reader to familiarise themselves with the concept of Research Clusters - an idea that I think we should continue - which represent the current challenges in the realm what we call **"The Digital Continuum"**. Thus, we provide flexibility in the definition of the research priorities of the future HPC research work programmes. These priorities could be derived from this SRA in three ways: by analysing the contents of the traditional Research Domains, by analysing the contents of the Research Clusters or by looking at where the two concepts intertwine - **the core of our future work is constituted by the HPC solutions needed to address the complex challenges of the Continuum**.

I would like to thank all ETP4HPC experts who took part in the writing of this SRA. A special mention is in order for our collaborators from outside of ETP4HPC – our partners in BDVA, HiPEAC, AIOTI, BDEC and other entities representing the areas that will complement HPC in the solutions of the future. We are facing the challenge of working together in order to design systems, the complexity of which cross the boundaries of a single technology. We all agree that we are facing a paradigm shift, but we still need to figure out *what that 'next big thing' is going to be*. For example, will the role of HPC in the systems of the future be to enable the workflows connecting various technologies? This SRA should also instigate a discussion with our partners on how to collectively implement the infrastructure for 'The Digital Continuum' as outlined in this document. As an example, the "European Green Deal" is an area where multiple digital technologies need to collaborate horizontally in R&D projects.

Besides my role as the Chairperson of ETP4HPC, I also preside over one of the two advisory bodies of EuroHPC – its Research and Innovation Advisory Group (RIAG), in which our Association has a leading role. The RIAG will use this SRA as a reference for its recommendations to the EuroHPC Governance Board in the definition of the 2021 - 2024 Work Programmes.

In particular, I would like to thank the SRA 4 working group leaders and the members of the working groups, the ETP4HPC Office, and other experts who joined this collaborative effort facilitated by Michael Malms.

I am looking forward to working with all our contributors again.

ETP4HPC Chairman Jean-Pierre Panziera

#### **Executive summary**

This Strategic Research Agenda is the fourth High Performance Computing (HPC) technology roadmap developed and maintained by ETP4HPC, the European High-Performance Computing Platform with the support of the EXDCI-2 project. It continues the tradition of a structured approach to the identification of key research objectives. The main objective of this SRA is to identify the European technology research priorities in the area of High-Performance Computing (HPC) and High-Performance Data Analytics (HPDA), which should be used by EuroHPC to build its 2021 – 2024 Work Programme.

Over eighty HPC experts associated with member organisations of ETP4HPC created this document in collaboration with external technical leaders representing those areas of technology that together with HPC form what we have come to call **"The Digital Continuum"**. This new concept well reflects the main trend of this SRA – it is not only about developing HPC technology in order to build competitive European HPC systems but also about making our HPC solutions work together with other related technologies - the material included in this SRA is also a result of our interactions with Big Data, Internet of Things (IoT), and Artificial Intelligence (AI) and Cyber Physical Systems (CPS).

The targeted audiences of this document are:

- EuroHPC Joint Undertaking (EuroHPC JU) and in particular its Research and Innovation Advisory Group, which will use the research objectives identified in this SRA to build its Multi-Annual Strategic Plan,

- entities interested in forming project consortia in response to the EuroHPC (and related) calls,

- anyone interested in the development of HPC technology in Europe.

Apart from the well-developed eight technical focal areas of HPC related technology, this documents also presents an argument in favour of placing HPC within the context of "**The Digital Conti-nuum** spectrum". The role HPC can play in this new concept is illustrated by four advanced use cases, which emphasise the need to master a multitude of new challenges presented by the complex workflows exemplifying this Digital Continuum.

We also introduce a new approach to defining the contents of the future research programmes. We believe that the most important challenge of European HPC now is to serve the development of the Digital Continuum, i.e. the unison of HPC and related technologies. We use the concept of Research Clusters to represent the main challenges of this Continuum. We argue that the future research should focus on how HPC can serve those areas. The priorities of the future Work Programmes could be extracted from this SRA by looking at the traditional Research Domains or Research Clusters, or by looking at their intersections, where – we believe – the core challenges lie.

The current state of technology for implementing the next generation of HPC infrastructure in Europe is analysed, the challenges for the upcoming four years are outlined, and the most important research priorities explained in detail.

The advancements in HPC and HPDA in Europe are placed in the context of those in the US, China and Japan. Also, upstream technologies with the potential to impact commercially available technology within the next 5-10 years, such as nanoelectronics and photonics, are discussed. Several operational suggestions in relations to future work programmes conclude the document.

Following the issue of this SRA, ETP4HPC's plan is to reach out to the other stakeholders of the European Digital Continuum. The entire ecosystem should jointly propose synchronised research actions aimed at tackling the multi-disciplinary technical challenges which facilitate the solutions to the problems European society will face in the next ten years. Over the six months prior to the publication of this document, ETP4HPC had actively participated in a multitude of conferences and horizontal collaborative work sessions aimed at uniting the critical forces needed to achieve that objective.

#### How to read this document

This Strategic Research Agenda is the most complex one to date and, depending on the needs of the Reader, it could be read in various ways.:

The core of the SRA is contained in the chapter 5 Technical Research Priorities 2021 - 2024, which identifies the European HPC Technology research priorities for the period from 2021 to 2024. This part provides material for the definition of the corresponding Research Work Programme. The SRA provides three dimensions from which these priorities could be extracted: the traditional Research Domains, the Research Clusters, which represent the challenges of the Digital Continuum, and the intersections of both, where the main challenges lie. Those interested in the areas that ETP4HPC recommends should be addressed by the upcoming calls for proposals and research projects should read the sections under 5.3 Research Domains. Each of these concludes with a section titled Intersection with Research Clusters, which defines the cross-cutting topics which need to be researched within the given research domain and thus become part of the Research Work Programme. Additional technical expertise is included in chapter 6 Upstream technologies – focus in the 2021-2024 period.

A quick overview of the SRA can be provided by the following parts: Executive Summary, 1 Introduction, 5.1 The concept of Research Clusters and Research Domains, 6 Upstream technologies – focus in the 2021-2024 period, 3 The European HPC Ecosystem and other supporting ecosystems, 4 International arena: HPC and HPDA in Europe, China, the US and Japan and 11 Next actions.

In order to gain **a more thorough understanding** of this SRA, the Readers should familiarise themselves with the contents of our Blueprint, which is the base of this SRA – reflected in chapter 2 The new paradigm: HPC in the Digital Continuum. This part includes: Application and use case scenarios and HPC use patterns: industrial and scientific use cases. Then, we encourage the Reader to select a few parts of chapters 5 Technical Research Priorities 2021 – 2024 and 6 Upstream technologies – focus in the 2021-2024 period and possibly 3 The European HPC Ecosystem and other supporting ecosystems, 4 International arena: HPC and HPDA in Europe, China, the US and Japan, 8 The importance of ethics, 9 Building and retaining skills and competence.

Those interested in **applications and use cases** should read the section 2.3 *Examples of industrial and scientific use cases* and these two Research Domains: 5.3.6 *Mathematical Methods and Algorithms and 5.3.7 Application Co-design.*

The **recommendations** defined by ETP4HPC in relation to the **implementation** of the next Work Programme (the structure of the calls for proposals and the projects, the management and coordination of the projects) are in the chapters 10 Operational recommendations and 7 Technology sourcing – from chips to system software.

### **Table of Contents**

| 1. Introduction                                  | 1( |

|--------------------------------------------------|----|

| 1.1. EuroHPC – the driving force of European HPC | 1  |

| 1.2. The role of this Strategic Research Agenda  | 1  |

| 1.3. The structure of this document              | 1  |

| 2.   | The new paradigm: HPC in the Digital Continuum                                 | 14 |

|------|--------------------------------------------------------------------------------|----|

| 2.1. | Application and use case scenarios                                             | 15 |

|      | 2.1.1. Workflow and capabilities                                               | 16 |

|      | 2.1.2. Data life cycle and dataflow in a scientific environment:<br>an example | 19 |

| 2.2. | HPC use patterns: industrial and scientific use cases                          | 19 |

| 2.3. | Examples of industrial and scientific use cases                                | 20 |

|      | 2.3.1. USE CASE 1: Extremes' prediction in the Digital Continuum               | 21 |

|      | 2.3.2. USE CASE 2: Autonomous driving                                          | 22 |

|      | 2.3.3. USE CASE 3: AI Automation on premise                                    | 23 |

|      | 2.3.4. USE CASE 4: AQMO,: An Edge to HPC Digital Continuum for Air Quality     | 25 |

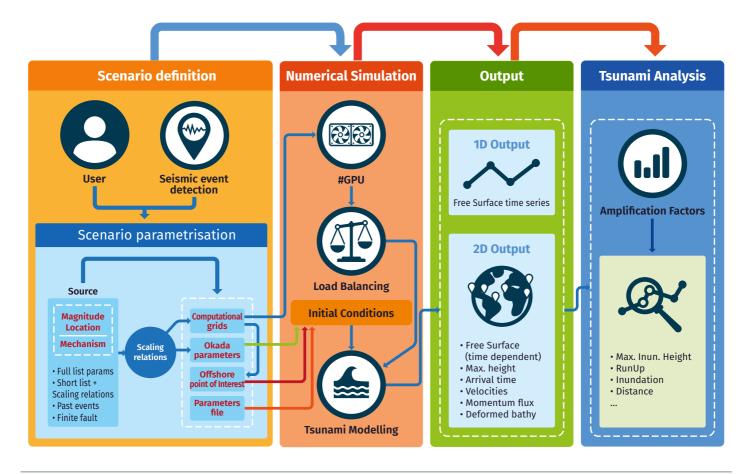

|      | 2.3.5. USE CASE 5: FTRT – Faster Than Real Time for seismic,                   |    |

|      | volcanic or tsunami events                                                     | 26 |

| 3. The European HPC Ecosystem                              |    |

|------------------------------------------------------------|----|

| and other supporting ecosystems                            |    |

| 4. International arena: HPC and HPDA in Europe,            |    |

| China, the US and Japan                                    |    |

| 4.1. International arena: looking ahead                    |    |

| 5. Technical Research Priorities 2021 – 2024               |    |

| 5.1. The concept of Research Clusters and Research Domains | 35 |

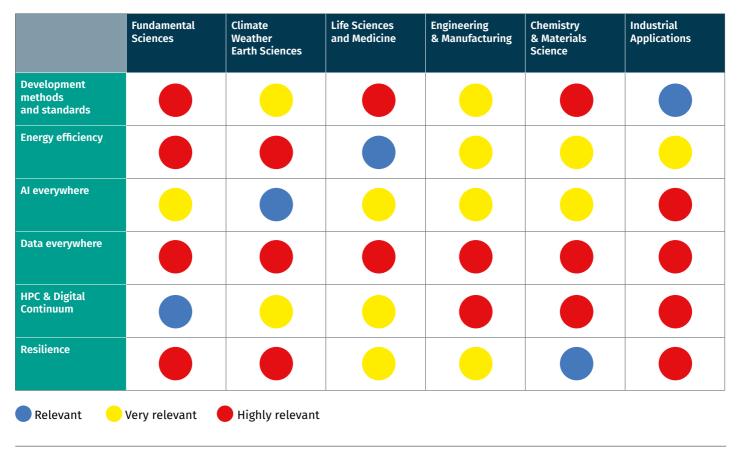

| 5.2. Research Clusters                                     | 36 |

| 5.2.1. Development methods and standards                   | 36 |

| 5.2.2. Energy efficiency                                   | 37 |

| 5.2.3. Al everywhere                                       | 39 |

| 5.2.4. Data everywhere                                     | 40 |

| 5.2.5. HPC and the Digital Continuum                       | 42 |

| 5.2.6. Resilience                                          | 45 |

| 5.2.7. Trustworthy computing                               | 46 |

| 5.3. Research Domains                                      | 48 |

| 5.3.1. System Architecture                                 | 48 |

| 5.3.2. System Hardware Components                          | 53 |

| 5.3.3. System Software and Management                      | 57 |

| 5.3.4. Programming Environment                             | 60 |

| 5.3.5. I/O and Storage                                     | 64 |

| 5.3.6. Mathematical Methods and Algorithms                 | 68 |

| 5.3.7. Application Co-design                               | 70 |

| 5.3.8. Centre-to-Edge Framework                            | 76 |

|                                                            |    |

| 6. Upstream Technologies –                                                                                                                                                                           |                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| focus in the 2021-2024 period                                                                                                                                                                        | 82                                     |

| 6.1. Context                                                                                                                                                                                         | 83                                     |

| 6.2. Progress of current technologies                                                                                                                                                                | 83                                     |

| 6.3. New architectures                                                                                                                                                                               | 83                                     |

| 6.3.1. Dataflow                                                                                                                                                                                      | 83                                     |

| 6.3.2. IMC/PIM (In Memory Computing; Processing In Memory)                                                                                                                                           | 83                                     |

| 6.3.3. Deep Learning and Neuromorphic                                                                                                                                                                | 84                                     |

| 6.3.4. Graph computing                                                                                                                                                                               | 84                                     |

| 6.3.5. Simulated annealing                                                                                                                                                                           | 84                                     |

|                                                                                                                                                                                                      |                                        |

| 6.4. Integration of new technologies with CMOS                                                                                                                                                       | 84                                     |

| 6.4. Integration of new technologies with CMOS                                                                                                                                                       |                                        |

|                                                                                                                                                                                                      | 84                                     |

| 6.41. NVMs                                                                                                                                                                                           | 84<br>84                               |

| 6.4.1. NVMs<br>6.4.2. Silicon photonics                                                                                                                                                              | 84<br>84<br>                           |

| 6.4.1. NVMs<br>6.4.2. Silicon photonics<br>6.5. New coding schemes                                                                                                                                   | 84<br>84<br>84<br>84                   |

| <ul> <li>6.4.1. NVMs</li> <li>6.4.2. Silicon photonics</li> <li>6.5. New coding schemes</li> <li>6.6. New technologies</li> </ul>                                                                    | 84<br>84<br>84<br>85<br>85             |

| <ul> <li>6.41. NVMs</li> <li>6.4.2. Silicon photonics</li> <li>6.5. New coding schemes</li> <li>6.6. New technologies</li> <li>6.6.1. Superconducting</li> </ul>                                     | 84<br>84<br>84<br>85<br>85<br>85       |

| <ul> <li>6.4.1. NVMs</li> <li>6.4.2. Silicon photonics</li> <li>6.5. New coding schemes</li> <li>6.6. New technologies</li> <li>6.6.1. Superconducting</li> <li>6.6.2. Memristive devices</li> </ul> | 84<br>84<br>84<br>85<br>85<br>85<br>85 |

| 7. Technology sourcing –<br>from chips to system software |    |

|-----------------------------------------------------------|----|

| 7.1. Open source vs. proprietary sourcing                 | 87 |

| 71.1. Motivation                                          |    |

| 7.1.2. Definitions                                        |    |

| 7.1.3. Different attributes                               |    |

| 71.4. Discussion                                          |    |

| 7.2. European vs. global sourcing                         |    |

| 8.    | The importance of ethics                                         | 91 |

|-------|------------------------------------------------------------------|----|

| 9.    | Building and retaining skills<br>and competence                  | 91 |

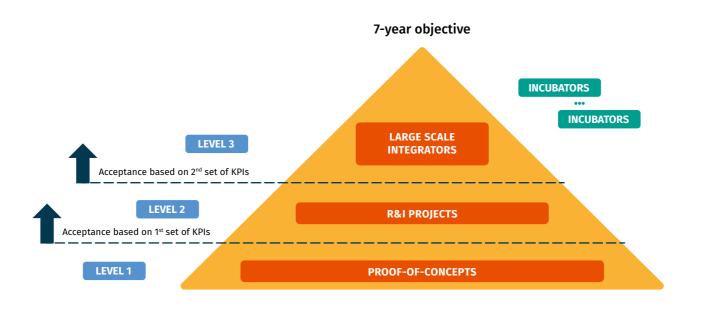

| 10.   | Operational recommendations                                      | 92 |

| 10.1. | Research projects implementation options                         | 93 |

| 10.2. | Managing the next 7-year work plan,<br>work programmes and calls | 94 |

| 11.   | Next actions                                                                        |     |

|-------|-------------------------------------------------------------------------------------|-----|

|       | A large-scale collaborative effort:<br>Transcontinuum Extreme-Scale Infrastructures |     |

| 12.   | Conclusions and Outlook                                                             |     |

| 13.   | Appendix                                                                            | 98  |

| 13.1. | Glossary                                                                            |     |

| 13.2  | Acknowledgements                                                                    | 104 |

# **1** Introduction

# EuroHPC – the driving force of European HPC

n order to position the value and purpose of this SRA, it is helpful to outline the political context it is created for. The EuroHPC Joint Undertaking, implemented in November 2018, is a joint initiative of the EU and European countries aimed at developing a World Class Supercomputing Ecosystem in Europe<sup>1</sup>. This partnership is intended to pool EU and national resources in High-Performance Computing with the initial objective of:

- Acquiring and providing a world-class petascale and pre-Exascale supercomputing and data infrastructure for Europe's scientific, industrial and public users, matching their demanding application requirements by 2020. This would be widely available to users from the public and private sector, to be used primarily for research purposes.

- 2. Supporting an ambitious research and innovation agenda to develop and maintain in the EU a world-class High-Performance Computing ecosystem, Exascale and beyond, covering all scientific and industrial value chain segments, including low-power processor and middleware technologies, algorithms and code design, applications and systems, services and engineering, interconnections, knowhow and skills for the next generation supercomputing era.

### The role of this Strategic Research Agenda

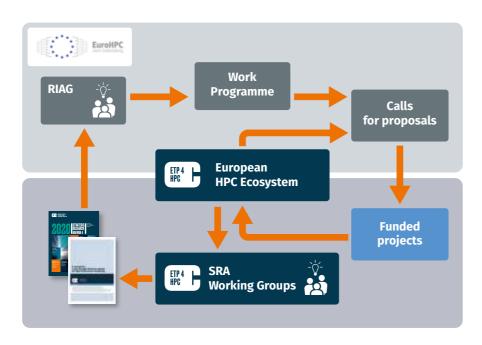

The main role of this Strategic Research Agenda extends beyond that of the previous three SRAs: besides outlining research priorities in the area of technology – hardware and software throughout the entire stack of HPC IT infrastructure for the next 3-4 years, it also develops a sophisticated vision of the evolution of HPC in the next era of deployment. As outlined in Figure 1, the document feeds this information into EuroHPC's Research and Innovation Advisory Group as recommendations for the definition of the upcoming research calls to be launched in 2021 and 2022.

The major part of the document has been developed by SRA working groups, composed of technical experts recruited from ETP4HPC member organisations. The leaders and co-leaders of these working groups are well-recognised HPC specialists within the European and international HPC community (see 13.2 *Acknowledgements* on page 104). In addition, a number of partner organisations have provided significant contributions e.g. the "Big Data and Extreme-Scale Computing" (BDEC-2) project, the "High Performance and Embedded Architecture and Compilation" (HiPEAC) project, the "Alliance for Internet Of Things innovation" (AIOTI), the "Big Data Value Association" (BDVA), the "Centres of Excellence for Computing Applications" (CoE) projects, the "Extreme Data and Computing Initiative 2" (EXDCI-2) project and the "European Organisation for Cyber Security" (ECSO) – see

chapter 3 The European HPC Ecosystem and other supporting ecosystems on page 28 for the complete list.

The SRA is meant to describe the major trends in the deployment of HPC and HPDA methods and systems, driven by economic and societal needs in Europe, taking into account the changes expected in the technologies and architectures of the expanding underlying IT infrastructure. The goal is to draw a complete picture of the state of the art and the challenges for the next 3-4 years rather than to focus on specific technologies, implementations or solutions. Any reference to products or solutions is intended as a reference in order to better explain the context and not as an implied promotion. The SRA thus remains completely agnostic in relation to brands and it maintains the diversity of implementation options. In this regard, it differs from the planning documents issued by EuroHPC and its RIAG, which delineate the implementation of research priorities in the form of work programmes and calls. These documents are driven by two factors: 1/ the political strategy agreed upon by the EC and the Participating States within EuroHPC and 2/ the relevant technical directions.

**Figure 1:** The role of SRA 4 - it reflects the principles defined in the ETP4HPC Blueprint (2019) and its main role is to feed the European HPC technology research priorities into the EuroHPC RIAG.

1. For more information on EuroHPC's mission, its organisational structure and the set-up of the RIAG, refer to the EuroHPC web site. https://eurohpc-ju.europa.eu/

#### INTRODUCTION

### The structure of this document

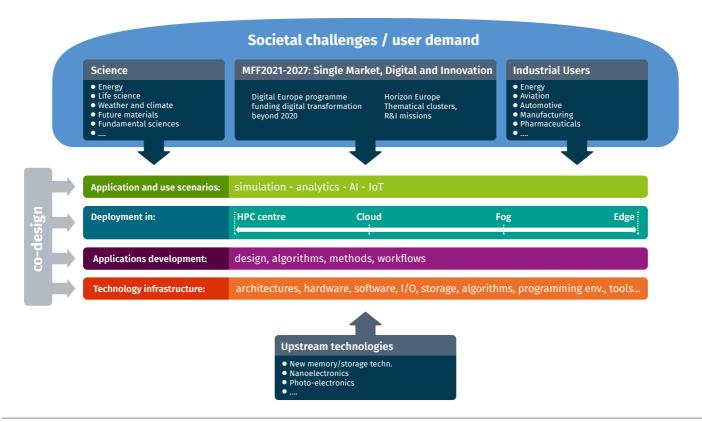

In April 2019, ETP4HPC issued a paper<sup>2</sup> titled "Blueprint for a new SRA" which outlines a layered, structured approach (Figure 2) to the identification of the research objectives in the 2021-2024 timeframe in the area of HPC and HPDA, covered by this SRA. This model includes significant collaborations with Internet of Things, Cyber Physical Systems and Artificial Intelligence. Its components are:

The top-centre layer represents the political framework which aims to extend the use of HPC and innovation in technology provision in Europe. Being part of the "Single Digital Market Strategy", the next Multi-Annual Funding Framework 2020-2027 (MFF) of the European Commission includes the "Digital Europe programme"<sup>3</sup> to fund digital transformation beyond 2020 and "Horizon Europe" with "Thematic Clusters" and "Missions" which contain societal challenges whose resolution require investment in Research and Innovation (R&I) in HPC and HPDA. Five thematic clusters address the full spectrum of global challenges through top-down collaborative R&I activities. A small number of missions with specific goals leads to a comprehensive portfolio of projects, which cut across multiple clusters. The first missions are to be introduced in the first strategic planning phase of Horizon Europe<sup>4</sup>.

- The second source of drivers of future technology improvements is represented in the upper right corner by commercial and industrial users of HPC. Especially in this category, new HPC use-patterns HPC are emerging in the context of new products and services (section 2.3 Examples of industrial and scientific use cases on page 20).

- Science has a well-established role in providing major users and driving the architectural development of HPC systems. Although some of the scientific fields are also addressed by the thematic clusters and missions, it is important to acknowledge the influence of all scientific domains (section 2.3 Examples of industrial and scientific use cases on page 20).

- The next layer down ("Application and use scenarios") translates the use-cases into application and technology use scenarios across the domains of "modelling and simulation",

Figure 2: This SRA's structured approach to derive the research priorities for HPC technology and its application.

- 2. ETP4HPC, "A Blueprint for a new Strategic Research Agenda for High Performance Computing", 2019, https://www.etp4hpc.eu/pujades/files/ Blueprint%20document\_20190904.pdf or https://www.etp4hpc.eu/hpc-vision-018.html

- 3. https://ec.europa.eu/digital-single-market/en/policies/shaping-digital-single-market

- 4. The examples shown here are preliminary and taken from the Mazzacuto report available at https://ec.europa.eu/info/sites/info/files/mazzucato\_report\_2018.pdf

"AI", "Analytics" and "Internet of things". As argued below, these domains can no longer be handled separately as they are all required to implement solutions to the social challenges and other problems.

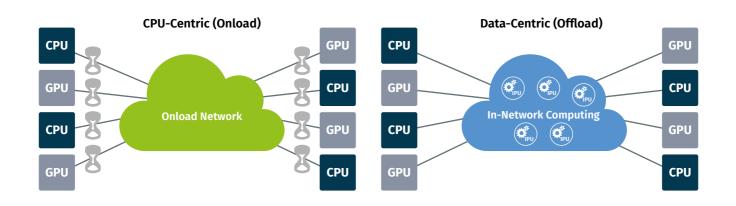

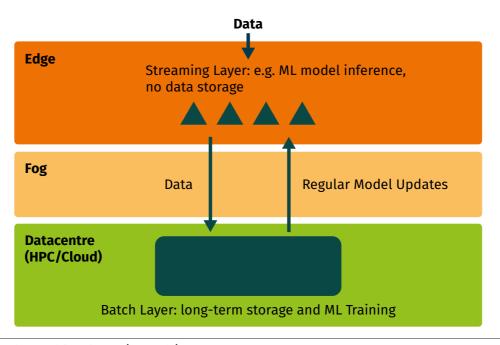

- HPC technology will not only be deployed in dedicated data centres in the future. A federation of systems and functions with a consistent communication and management mechanism across all participating systems will be required, thus creating a "continuum" of computing. The layer "Deployment" describes the challenges associated with this change whereas HPC functionality is now extended to Clouds, Fog computing and Edge computing (section 5.3.8 Centre-to-Edge Framework on page 76).

- The next layer down ("Applications development: design, algorithms, methods, workflows") addresses the software development aspects of the application portfolio (section 5.3.7 Application Co-design on page 70).

- The lower layer outlines the technologies used to implement the IT infrastructure discussed above. While most of the described components, functions and features will be deployed in data centres, local small-scale deployments (Edge/Fog) will also integrate the technology stack or a part of it. These technologies cover algorithms, programming languages and tools, system software, architectures, hardware components, I/O and storage as well as addressing critical features such as reliability and energy efficiency. This is the core of the SRA (chapter 5 Technical Research Priorities 2021 – 2024 on page 34).

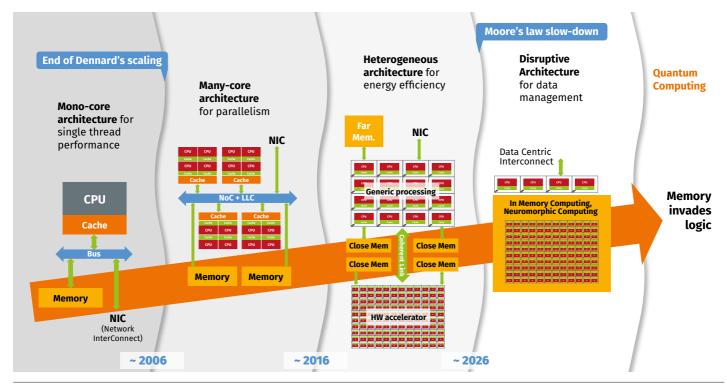

- The emergence of upstream technologies which could be applied in future HPC system/component architectures constitutes another factor which influences the entire European technology domain. These upstream technologies are expected to facilitate novel and superior solutions. The related chapter outlines those candidate technologies which are most likely to be applicable within the timeframe of Horizon Europe (chapter 6 Upstream technologies – focus in the 2021-2024 period on page 82).

This document also provides **non-technical** analyses and priorities (as opposed to the technical contents listed above), which facilitates the understanding the context of the core technical chapters:

- A separate chapter is dedicated to the international HPC and HPDA arena. It presents an overview of the most prominent ecosystems, namely those of the US, Japan and China, and their strategies and achievements in order to understand how Europe can either benefit from their work or compete with them effectively (4 International arena: HPC and HPDA in Europe, China, the US and Japan on page 32).

- ETP4HPC also presents its view on the possibilities of implementing the research priorities outline in the previous chapter. Various elements of Open Source implementations well as the realisation of a European-sourced technology roadmap are outlined (7 Technology sourcing from chips to system software on page 86).

- This SRA's operational recommendations for the implementation of Work Programme 2021/2022 are also presented. These include proposals for project types and support instruments not used in the previous HPC work programmes (10 Operational recommendations on page 92).

- Finally, the next objectives to be pursued in early 2020 are presented: ETP4HPC intends to engage with all stakeholders contributing their technologies to the "Digital Continuum" with an aim to propose large, high-TRL integration and demonstration R&I actions, which would validate the interoperability, robustness, and efficiency of the IT infrastructure supporting the Continuum (11 Next actions on page 108).

# 2 The new paradigm: HPC in the Digital Continuum

PRSN 0211 SEARCH A01 PRSN 0211 SEARCH A01

SEARCHETR/01000

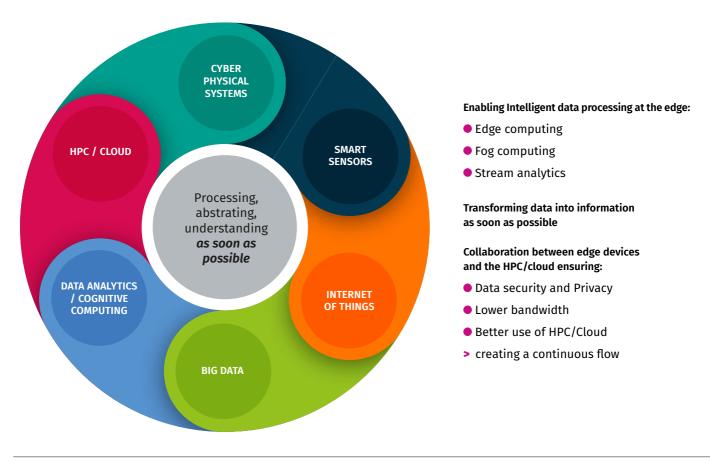

The rapid proliferation of digital data generators, the unprecedented growth in the volume and diversity of the data they generate, and the intense evolution of the methods for analysing and using that data are radically reshaping the landscape of scientific computing. The most critical problems involve the logistics of wide-area, multistage workflows that move back and forth across the computing continuum, between the multitude of distributed sensors, instruments and other devices at the network's Edge and the centralised resources of commercial clouds and HPC centres<sup>5</sup>. The objective of this SRA is to process this new paradigm of 'The Digital Continuum'.

BDEC, "Big data and extreme-scale computing: Pathways to Convergence - Toward a shaping strategy for a future software and data ecosystem for scientific inquiry", 2018, https://www.exascale.org/bdec/sites/www.exascale.org.bdec/files/ whitepapers/bdec\_pathways.pdf

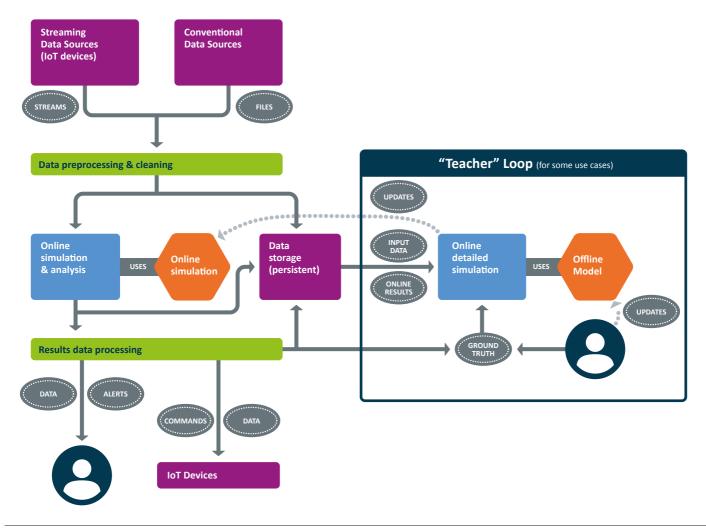

Figure 3: HPC in the loop.

Figure 3 above illustrates High-Performance Computing as one element of a complex workflow ("HPC in the loop"), starting with data generated at smart sensors in an IoT environment. Data is being locally pre-processed at the Edge and relevant parts are forwarded to decentralised "Fog nodes" close to the Edge. A subset of data is then transferred for centralised Data Analytics or simulation and modelling in centralised HPC centres or clouds. In an increasing number of use scenarios based on the concept of the "Digital Twin", a "twin-copy" of a physical entity, is maintained and continuously updated on these central compute infrastructures (see section 5.3.8 Centre-to-Edge Framework on page 76). It should be noted that in reality the dependencies between the segments of the loop shown in the Figure are not sequential in nature. The loop is not strictly repeating actions in a circular mode; the elements are cross-connected in rather complex, often fast changing event-driven flows.

The final outcome of the loop is a set of optimised actions in the "Cyber Physical Entanglement" representing physical systems (e.g. robots, vehicles, industrial processes) interconnected in complex intelligent networks.

### Application and use case scenarios

In light of the rapid evolution of technology and use cases, the term "High-Performance Computing (HPC)" needs to be redefined: In the past, it used to be synonymous with "technical computing using supercomputers" applied in order to model or simulate complex scientific or technical phenomena. While HPC will still refer to systems facilitating scaling of applications to a larger number of nodes, the main change is that HPC systems will no longer be stand-alone systems but they will be part of a larger e-infrastructure to realise complex, efficiently managed and or-chestrated workflows, including the interfaces of this structure with external devices (distributed and Edge devices), as indicated in Figure 3.

Tight integration of capabilities across individual system boundaries and between data centres and local small-scale HPC systems is expected. Each component in this integrated compute, communication and data infrastructure has different characteristics that can be summarised as:

• Simulation: relatively low amount of input data, large computation requirements (mostly in double or quadruple

precision floating point representation) with tight coupling between compute nodes (benefits from scale-up hardware and low-latency networks) and large amount of generated data (simulation results).

• **Big Data**: large amount of external input data, low-tomedium computational requirement with loose coupling between compute nodes (scale-out and "shared-nothing" models) and low amount of output data (information extracted from the input data).

• Data stream processing: streaming capabilities are becoming increasingly important for scientific and industrial HPC applications (e.g. CERN's Large Hadron Collider (LHC), Square Kilometre Array (SKA) project, astrophysics, physical simulations, digital twins, etc.), supporting important needs such as the ability to act on incoming data and computational steering. Coupling data streams produced by such experiments to computational HPC capabilities is an important challenge, and Big Data Computing's near real-time processing architectures and stream processing capabilities are able to rapidly analyse high-bandwidth, high-throughput streaming data.

- Al (for example, Machine Learning in the **training** phase): large input (local) database with very high access rate, large amount of computation (in low precision floating point representation) and relatively low amount of output data (the weights of the newly trained Neural Networks, typically a few hundreds of MBs).

- AI (for example, Machine Learning in the inference phase): medium input (depends on the application), low processing amount (reduced precision floating point or integer) and low amount of generated data.

- AI (Reinforcement learning) such as Alpha Zero system from DeepMind: the input is low (in volume, e.g. rules of a game, or physical laws or constraints), the output is also low (solution), but the system internally generates a large amount of data and computation to explore the various options and find a good solution. Simulation of the process to be optimised is in the loop to get an assessment of the quality of the solution found.

HPC has always advanced science by delivering results only made possible by the use of cutting-edge computer technologies. Throughout the last decade numerical computing has been growing rapidly in many directions: higher fidelity, coupled multiphysics and multi-scale models; a deluge of observational data from sensors and of simulated data; semi-automatic data analysis and post-processing; uncertainty quantification and newly AI-based models. Combining all these aspects will result in a highly complex application (software) architecture, which is becoming a research topic by itself.

In reference to Figure 1, this layer is driven by the thematic clusters and missions as well by industrial and scientific needs. The extraction of IT/HPC requirements out of representative and strategically important use case scenarios is necessary in order to drive HPC R&I in the right direction. They are key to assess new architectures or infrastructure as well as to provide testbeds to research and industrial teams.

In the context of promoting innovations for the HPC, HPDA and IoT ecosystem, the use cases identified must be such that we avoid alignment with technology "silos", which would strongly restrict the shaping capabilities for the R&I work program. Furthermore, fully addressing the societal challenges can only be achieved by considering end-to-end approaches where data production is integrated with data analytics, machine learning, numerical simulation, data archiving as well as the final use of the results. The use cases are based on applications which rely on complex workflows within which individual tasks are executed on a wide variety of systems and whereby the complete data management cycle is addressed.

However, many representative use case scenarios are difficult to analyse because they combine many heterogeneous components (e.g. which rely on different software stacks) as well as different resources or user governance strategies. For instance, the main challenge is presented by the existence of applications across a federation of systems - which includes HPC centres, Cloud facilities, Fog and Edge components and networks - while at the same time, preserving security and privacy from end-to-end. Furthermore, the economics aspects of the deployment of these applications must be considered.

To advance the state of the art, the supported uses cases must be able to demonstrate an application implemented over multiple entities while preserving security and privacy properties. Furthermore, their deployment should take place in an efficient manner (technically and economically).

Mapping the relationship between Simulation, Data Analytics and Machine Learning into a real environment, as illustrated in Figure 2, shows a loop of actions with HPC being one of the many elements besides Data Analytics, the Internet of Things and in many cases, cyber-physical entanglement (systems). Increasingly, computing systems act as direct controlling devices, which thus has an impact on the real world (Cyber-Physical Systems). HPC in the loop or Digital twin approaches add timing constraints so that the results of simulations can be directly used for choosing the adequate control of the system in due (real) time, and raise the stakes of validating and guaranteeing functional correctness, timing and security, because faults or breaches will have wideranging consequences in the real world.

#### 21.1 Workflow and capabilities

Understanding the workflow and dataflows is of crucial importance for an analysis of real use cases.

Each use case (e.g. autonomous driving, personalised medicine, wind park operation, etc.) is built upon some basic "functional

#### Processing and communication capabilities

- Sensing and Data Capturing

- Data Ingestion

- Numerical Simulation

- Data Analytics

- Artificial Intelligence

#### **Technology Influencing Aspects**

- Infrastructure Ownership and Tenancy

- Privacy and Security

- Standardisation and Interoperability

- Efficiency (Performance, Energy, Cost)

#### Support Capabilities

- Workflow and Dataflow Orchestration

- Data Logistics

- Data Localisation

- Dynamic Resource Allocation

- Management

Figure 4: Categories of capabilities in mixed Simulation, Analytics, AI and IoT use scenarios

capabilities" (Figure 4), which are implemented in the form of similar structures (Figure 5).

- The "Processing and Communication Capabilities" listed in Figure 4 cover all areas which require compute capabilities, be it in a data centre, an Edge or Fog node or an IoT device – each of them with a different application scope. For a given workflow (use case), the individual processing capabilities are expected to be spread accordingly across locations and systems. We distinguish between data capture from devices, data ingestion into a compute environment, the typical HPC capability of numerical simulation, and the Big Data capabilities of data analysis and artificial intelligence. To address such new compute requirements, HPC capabilities must provide the processing capabilities for the Big Data environment, which includes interactive analytics as well as batch and real-time processing of data streams.

- The "Technology Influencing Aspects" are properties that have a large impact on the design, implementation and integration of the processing capabilities but do not directly provide any data processing capabilities. These properties must be provided by the processing infrastructure in ways that satisfy the end-user requirements to result in an effective and efficient solution. The governance of compute infrastructure and data imposes policies on data processing. In most use cases, security and privacy must be considered in such an environment to comply with regulatory and enduser needs. Interoperability and standards increase trust in developed workflows and accelerate the adoption by users. The efficiency of a solution is relevant insofar that

the costs of a solution limit its adoption in use-cases with limited revenue. A well-performing, energy and cost-efficient system maximises industrial and commercial competence by enabling novel scenarios.

• "Support Capabilities" describe the crucial implementation aspects of a mixed scenario. As shown in Figure 4, the workflow reflects the interconnections of actions and data between the IoT devices, processing entities and data repositories. However, the identified capabilities for the environment discussed here are currently underdeveloped and require further R&D efforts.

The orchestration of workflows and automatic and efficient deployment across a complex hardware-landscape is required to exploit such systems. For instance, data must be placed and migrated intelligently to match the storage and processing capabilities of (IoT or Edge) systems. Alternatively, processing or computation can be distributed/mapped onto the physical infrastructure in a way that minimises data movements (moving the computation to the data instead of moving the data to the computation capability). Finally, workflows must adapt their processing capabilities dynamically depending on the input, or other external parameters such as the number of users or availability of processing capacity. This requires software layers that enable such dynamic, ad hoc changes.

We recognise that management procedures must be developed that deal with the distributed nature of computation, ownership, and conformance to standards while considering the efficiency aspects.

Figure 5: A typical mixed simulation and machine learning workflow

Figure 5 unfolds the loop shown in Figure 3 and shows three steps that are common to the use cases discussed jointly by ETP4HPC and the BDVA: in the first step, data from a multitude of realworld sensors or conventional sources (e.g. databases) is ingested, pre-processed and cleaned. This can already involve significant processing, as in situations where the analysis of correlation between independent data streams is required. All or part of the resulting data is put into storage for documentation and for use in improving the analysis/simulation models.

The second step consists of an in-depth analysis of the data from step 1 – this includes anything from image classification to computing the next status of a complex digital twin using multidiscipline simulation techniques. The online model encodes the analysis steps, and it can range from a simple rule set to a complex HPC simulation code. A part of the analysis results are again put into storage for later use.

The third step is the processing of the analysis results, and communication with human users or IoT devices/Cyber- Physical Systems (CPSs). Depending on the nature of the problem, the loop can be closed by the commands passed to a CPS affecting its sensor readings, which requires the update of the analysis in step 2. In the Digital Twin case, the analysis in step 2 keeps its own state and runs in "streaming mode", receiving updates from the real world, reconciling them with the CPS's virtual model, and sending out commands to the CPS.

The role of the "teacher loop" is very apparent for Deep Learning based analysis approaches – the online model at the heart of step 2 is created in a separate training phase and then made "live". For reinforcement learning, the online model is improved by assessing its performance and rewarding/punishing certain aspects. Taken to the next step, the online model could represent a simplified version of a car (for example), which is updated and extended/improved by a full, physically correct car model. The key idea behind splitting off the teacher loop is that it can be disconnected after a while (analogously to real life with teachers and pupils, once a certain proficiency has been achieved). The online model can then be made significantly simpler than e.g. a fully physically correct six degrees of freedom driving model, reducing the amount of processing needed per instance and consequently reducing energy requirements.

#### Data life cycle and dataflow in a scientific environment: an example

Understanding the necessity for a dataflow orchestration in mixed Simulation and Big Data use scenarios is important. The capacity of storage infrastructure, the increased sophistication and deployment of sensors, the ubiquitous availability of computer clusters, allow the development of new analysis techniques and real time capabilities to ingest "fresh" data during simulation.

There are multiple scenarios:

- Input data coming from experimentations is injected into simulation to enhance it. In this case, the improvement of the simulation will depend on the availability and the quality of this new data set.

- Data is produced by sensors in a streaming mode and local (close to the Edge) or remote HPC resources are used to train the model. The model-training frequency will depend on data source obsolescence.

- Output or step-by-step data can be extracted from simulation for new in situ processing, visualisation and simulation context modification (computational steering). in situ processing could be performed using AI for inferring on the fly pertinent structures (and by consequence reduce the amount of data to be saved, saving also energy) and performing a continuous but light training of the existing models

For these new scenarios, we observe the need for different levels of curation (sensors producing non-curated data versus use of databases with curated data):

- Unstructured data issued e.g. by major scientific instruments or experimental facilities, which may be residing outside of supercomputer centralised facilities, will require nontrivial transformations before an ingestion could be realised by a simulation or Machine Learning or other HPDA steps. Depending on the real-time availability and quality of this data, the transformation and availability for simulation need a strong coordination effort (near real time data preparation).

- Qualified structured data resources shared by the communities through archives, databases or any specifics formats accessible through the internet have a well-known preparation process to enable their use in a simulation.

The challenge here is to add and to coordinate the integration of these new data resource types in end-to-end application workflows without drastically increasing storage space dedicated to data availability. A well-balanced architecture will mostly depend on the efficiency of the dataflow and on the capability to reduce, filter, pre-process data close to the source (on Edge computing devices or Fog nodes). The objective is to limit network and global storage congestion. This distributed data transformation must be integrated in a Big Data life cycle model that includes activities aimed at combining data curation with the research life cycle more closely. The activities address planning, acquiring, preparing, analysing, preserving, and discovering data, describing the data and assuring its quality.

The relationship between scientific community data repositories and new distributed data workflows as well as the reproducibility in computational science need to be understood. Documenting data sources, experimental conditions, instruments and sensors, simulation scripts, processing of datasets, analysis parameters, thresholds, and analysis methods ensures not only a much-needed transparency of the research, but also data discovery and future data use in science.

Important as well is the notion of where data is stored and how/ where data is accessed for computation. In a federated scenario, data could be stored across distributed Edge, Fog and possibly multiple centralised "data-centre-like" systems, e.g. reflecting the data production sites or specific access policies. Solutions to allow simulation, analytics or AI applications access data across federated and heterogeneous sites must be designed and built to strike the proper balance between data access performance, cost and consistency, while at the same time satisfying access control and privacy constraints.

In conclusion, the design of a global infrastructure allowing the combination of external Edge- or peripheral environments with a central, shared infrastructure will require the analysis of the entire software environment, the identification of new data sources and of the quality of data.

## HPC use patterns: industrial and scientific use cases

Ten to fifteen years ago, only a number of selected specific domains used HPC. Today's widespread use of HPC is a result of its expansion into a wide range and scientific and industrial fields, for example:

- In engineering (e.g. automotive/aero-spatial industries), HPC is now used widely to simulate complex multi-physics systems, such as the ones used in the analysis of combustion engines, aerodynamic properties, or vehicle safety at high precision.

- In the **domain of natural resources** (the oil & gas industry, in particular) HPC is traditionally widely used in resource or production management (e.g. oil search).

- HPC is used in **industrial production** (e.g. in the pharmaceutical industry in drug design) and in the **design** and testing of complex technical processes used.

- The **financial sector** too relies heavily on HPC which is applied in real-time simulations.

An average HPC user was thus a large company, operating its own

HPC centre on its own premises, having at its disposal experts who operated the system and ran their compute intensive applications. The applications were either developed by specialised ISVs (e.g. for the automotive sector), or developed jointly with a mostly academic open source community or, in some cases, they were developed in-house and closely protected.

The change we are observing today is mainly driven by two factors:

- HPC as a service: HPC resources being available today "as a service" (typically proposed by Cloud service providers), make simulation of (multi-) physical systems available to a much wider range of users, often in a multi-tenanted set-up. In this set-up, neither ownership of the computing resources is required, nor highly specialised in-house competences in HPC<sup>6</sup>. It should be noted that sharing an HPC infrastructure between different industrial users will not only add new requirements in terms of security for providing high levels of data protection and guaranteed isolation between users but also bring new challenges for scheduling and orchestration.

- Data driven applications: Furthermore, we see an increase in a wide range of new "data driven applications" deploying functionalities such as analysis of very large data sets and machine learning (relying on large data sets for the training phase), which have given rise to a wide range of new applications. The following two examples attract a lot of attention: e-mobility, including autonomous vehicles, and customising medication and drug consumption to the personal needs of a patient. A number of sectors (e.g. designing/operating wind turbines and industrial production processes) have started to deploy the "Digital Twin" concept: digital twins are software representations of assets and processes that are used to understand, predict, and optimise performance in order to achieve improved business outcomes. Digital twins consist of three components: a data model, a set of analytics or algorithms, and knowledge<sup>7</sup>. As shown in Figure 2, HPC simulation has moved "into the loop", and become an indispensable part of a product. This trend fundamentally changes the requirements on the HPC software, systems and integration/management. The HPC systems needs to facilitate the connection of external sensors/Edge computing without compromising security and HPC systems protection.

As a consequence of this transformation, the needs of the industrial users have evolved for a number of reasons:

First, today, users rely on the provision of HPC resources for all scales of computations and flavours (Data oriented, HPC oriented). This applies not only to small users without in-house resources but is also true in the case of large companies who need a seamless integration of in-house capacities with external secured Cloud-based capacities.

- Second, as reflected by the growing use of PRACE resources by European industries, as the use of HPC by European industry grows, the use of HPC must be available to a variety of players, even without highly specialised in-house resources. These new users would need to rely on services and support to guide them how to use HPC effectively in their businesses.

- Third, the European industry needs increased support in application development: to develop effective HPC applications is intrinsically difficult – and the adoption of such codes to new hardware (for example, to accelerators such as GPUs) requires detailed expertise. Access to novel and experimental system architectures is needed to allow users and application developers to prepare their codes for the next generation of machines.

- In the definition of the strategic research topics for the upcoming Horizon Europe framework, the input from industrial users is crucial in order to (I) address their technical needs by taking into account the key requirements of future industry-relevant applications, and (II) support the European industry at large in the uptake of numerical simulations and data driven applications for their businesses.

# Examples of industrial and scientific use cases

The following **five USE CASES** illustrate how diverse and highly complex modern workflows can be. In all examples, the HPC infrastructure is used to either simulate or model, or it serves as an efficient, high performing infrastructure for Deep Learning applications. Also, besides the multi-player interdependencies at a technical level, many non-technical aspects such as security and privacy, multi-tenancy of communication and compute infrastructure and resilience are outlined.

The following are the names and the originators of the five use cases:

- USE CASE 1: Extremes prediction in the Digital Continuum by Peter Bauer, ECWMF

- USE CASE 2: Autonomous Driving by Ovidiu Vermesan, SINTEF and AIOTI

- USE CASE 3: **Al Automation on premise** by Cristiano Malossi, IBM Research

- USE CASE 4: AQMO1,2: An Edge to HPC Digital Continuum for Air Quality by Francois Bodin, IRISA and University of Rennes

- USE CASE 5: FTRT Faster Than Real Time for seismic, volcanic or tsunami events by Stephane Requena (GENCI)

The projects SHAPE, Fortissimo and Fortissimo-2 demonstrated that SMEs could benefit greatly from access to such re-sources and support to solve business problems. The Fortissimo marketplace has been developed by the projects to offer such services.

https://www.ge.com/digital/applications/digital-twin

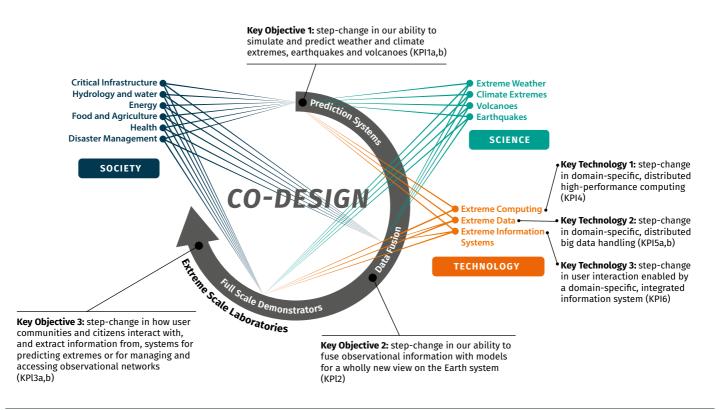

**Figure 6:** Extremes prediction loop (prediction of extreme climate conditions) from science to impact objectives, enabled by new technologies.

#### 2.3.1

#### USE CASE 1: Extremes' prediction in the Digital Continuum

Natural hazards represent some of the most important socioeconomic challenges our society is facing in the next decades. Natural hazards have caused over 1 million fatalities and over 3 trillion Euros economic loss world-wide in the last 20 years, and this trend is increasing given drastically rising resource demands and population growth. Apart from the impact of natural hazards on Europe itself, the increasing stress on global resources will enhance the political pressure on Europe through yet unprecedented levels of migration.

Dealing responsibly with extreme events does not only require a drastic change in the ways our society is solving its energy and population crises. It also requires a new capability of using present and future information on the Earth-system to reliably predict the occurrence and impact of such events. A breakthrough of Europe's prediction capability can be made manifest through science-technology solutions delivering yet unprecedented levels of predictive accuracy with real value for a society. This is the objective of the *ExtremeEarth* project proposal<sup>8</sup>.

#### 2.3.1.1

#### The relevance for Digital Europe – and beyond

The science-technology solution includes the entire loop from:

(1) basic Earth-system science, established in (2) enhanced prediction models significantly, combined with (3) the vast range of Earth observation data ranging from advanced satellite instruments to commodity devices available through the internet of things, exploiting (4) extreme-scale computing, Big Data handling, high-performance data analytics and artificial intelligence technologies, for feeding (5) impact models that translate scientific data into information close to the real users responsible for critical infrastructures, hydrology and water, energy, food and agriculture, health and disaster management. Only through the full loop can the investment in breakthrough science-technology solutions be turned into value for society. This loop is shown together with key application objectives and key enabling technologies in Figure 6. How the elements of the Digital Continuum of this SRA map onto this application use case is explained in the following.

#### 2.3.1.2

#### Physical systems

The main objective is to create a digital twin of the Earth-system that employs all available observations and high-definition simulations of the past, the present and the future in order to interactively extract information that can drive institutional and industrial processes. Near real-time data processing, on-demand high-performance computing, and integrated science-application workflows combined with high-performance data analytics capabilities form the technology backbone.

8. Full proposal for download - https://extremeearth.eu/sites/default/files/2019-07/ExtremeEarth\_FullProposal\_public.pdf

The institutional and industrial processes will allow the protection of critical infrastructures and the management of catastrophic consequence of extremes, the future design of resilient renewable energy sourcing, securing water and food supply, and the protection of human health and European society's response to political pressure caused by environmental change.

#### 2.3.1.3

#### **Smart sensors and Internet of Things**

At present, Earth-system observations already comprise hundreds of millions of observations collected daily to monitor atmosphere, oceans, cryosphere, biosphere and the solid Earth, the largest data volumes being provided by hundreds of satellite instruments. This volume is expected to increase by several orders of magnitude in the next decade, with a need to ingest such observations in digital twin systems within hours. Smart-sensor technology is highly relevant for satellite-based observations and dedicated station networks, but also for observations from commodity devices deployed on e.g. phones, car sensors and specialised industrial devices monitoring agriculture, renewable energy sources and infrastructures – made available through the internet of things. Such technology will allow outsourcing data pre-processing to Edge and Fog computing, and thus implement fully agile data management and information extraction.

#### 2.3.1.4

#### **Big data and Data Analytics**

The daily volume of Earth-system observation and simulation data already exceeds petabytes today, prohibiting effective and timely information extraction, critical for proactive and reactive response for anticipating and mitigating the effects of extremes. Both simulations and observations need to be generated and assimilated in the Earth-system's digital twin within minutes to hours of time-critical workflows towards near-real-time decision-making. Overcoming the data-transfer bottlenecks between the digital twin and downstream applications is crucial and future workflow management needs to make such applications an integral part of the observation and prediction infrastructure. Powerful data analytics technology and methodologies offer the only option to make the effective transfer between raw data and information tailored to those sectors needing to prepare and respond to extremes, namely water, food, energy, health, finance and civil protection.

#### 2.3.1.5 HPC and Cloud

Today, experimental and operational Earth-system simulations use petascale HPC infrastructures, and the expectation is that future systems will require about 1000 times more computational power for producing reliable predictions of Earth-system extremes with lead times that are sufficient for society and industry to respond. This need translates into a new software paradigm to gain full and sustainable access to low-energy processing capabilities, dense memory hierarchies as well as post-processing and data dissemination pipelines that are optimally configured across centralised and Cloud-based facilities. European leadership in this software domain offers a unique opportunity to turn the European investment in HPC digital technology into real value. 2.3.2

#### **USE CASE 2: Autonomous driving**

The entire traditional transportation ecosystem is undergoing significant changes with five main trends accelerating this transformation:

Source Sinte

New mobility modes and behaviours,

#### Autonomous Vehicle View

- Sensors, actuators, vision, maps

- Connectivity

- Vehicle architecture

- High-performance vehicle computing platform, flexible, and programmable

- Infrastructure platform

- AI design and implementation platform

- Edge computing platform and solution

- Data Center solution for fleet simulation and testing

- Pervasive security, safety trust program

Figure 7: Critical technologies and platforms for autonomous vehicle driving

- A rise in autonomous/automated driving technologies,

- Development and use of digital features impacting industry and consumers,

- The electrification of powertrains and introduction of AI techniques,

- Methods for implementing intelligent solutions and components.

For the autonomous driving capabilities at level 4 and 5, new capabilities of autonomous vehicles need to be addressed in terms of computing, control, cognition, connectivity (4C attributes). Through sensing, detection, perception, processing and decision functions vehicles need to "see" (sense/locate) the surroundings, perceive obstacles and act safely in accordance with the vehicles' perceptions.

In addition, the **integration of multipurpose in-vehicle platforms** as shown in Figure 7, and the distribution of functions between automated vehicles, other vehicles, infrastructure, Edge/Cloud platforms and HPC centres must accommodate solutions for over-the-air (OTA) updates, predictive maintenance and vehicle-to-everything (V2E) connectivity.

The **convergence of several ecosystems** and standardisation activities means that intelligent electric, connected, autonomous/ automated (ECA) vehicles will become ubiquitous devices among Internet of Vehicles (IoV) applications and services.

Vehicles will access, consume, create, enrich, direct and share digital information between businesses, people, organisations, infrastructures, vehicles, other elements of the Internet of Things (IoT) and Industrial Internet of Things (IIoT) applications. Mobile, Edge, Cloud and high-performance computing technologies together form a computing continuum for new, disruptive IoV and IoT/IIoT applications, providing an information pipeline for safety and mission-critical workflows.

These applications need an **Edge-to-Cloud Digital Continuum** where data/information flows are stored, processed and analysed, while using HPC centres for extensive traffic simulation, weather forecasting, virtual energy grid simulation and energy flow, and virtual fleet performance validation using digital twin representations of the vehicles etc. New end-to-end IoV and IoT/ IIoT applications in this computing continuum require a scalable, composable and automated intelligent infrastructure.

To illustrate **the role of HPC**, for a safe and efficient journey of many connected and autonomously vehicles driving at the same time, an emphasis needs to be put on providing optimised environmental simulation at large scale to model their movement along millions of kilometres. In addition, simulation of potentially complex scenarios and the behaviour of vehicles is required to optimise their handling in different driving conditions (sun, rain, snow, twilight, night, backlit, etc.). Exascale HPC facilities can support the use of autonomous/automated vehicles in fleets, evaluating and optimising thousands of possible impediments that vehicles might encounter (bikes, motorcycles, trains, pedestrians, stop signs, potholes, black ice, traffic circles) and the need to provide scalable computing and storage systems necessary for safety and mission-critical applications.

A challenge will be the orchestration and optimisation of processing power across HPC-, Cloud- and Edge-computing infrastructures to balance the workload, and optimise and distribute the storage capabilities, creating real-time computing environments that respond to different usage needs.

At the Edge, i.e. in the autonomous vehicles, urgent decisions based on real-time data will have to be taken locally. In this context, **advanced AI technologies** must be distributed across the computing and information continuum (optimised based on processing capabilities and latency requirements). Autonomous/ automated vehicles must be able to continuously learn and make optimal decisions under all circumstances.

One of the major challenges for future autonomous/automated vehicles and IoV applications is the dynamic orchestration and optimisation to access multiple intelligent infrastructures in the Digital Continuum and to cost-effectively manage the terabytes of information required at the right time and in the right location by users who need it for reliable, safe decision-making.

#### 2.3.3

#### USE CASE 3: AI Automation on premise<sup>9</sup>

Today, AI models are widely used in many applications. Major industries have become interested in this technology and aim to use it in their development and production environments in the immediate future. However, the know-how required to build very accurate, compact and not too computationally expensive models based on ML or DL approaches is very demanding and users lack the expertise necessary to do that on their own.

For example, in the literature the phase of construction of neural network architectures is never accounted in the actual cost and performance of the entire process, and it is assumed as a given grail. However, as a matter of fact, this is the most expensive task. For instance, despite the many years of research and the huge amount of literature published so far, no neural network architecture today is able to predict correctly more than 90% of CIFAR-100<sup>10</sup> images; in other words, the design time of a perfect architecture for CIFAR-100 is currently infinity. Moreover, most of the experience acquired by the data scientists while developing these models is not shared and becomes lost over time. This includes all the experiments (models) built and discarded during the optimisation phase. "Automation of ML" is a platform that will open the possibility to apply state-of-the-art ML/DL metho-

<sup>9.</sup> Florian Scheidegger, Luca Benini, Costas Bekas, A. Cristiano I. Malossi , NeurIPS, 2019 and Roxana Istrate, Florian Scheidegger, Giovanni Mariani, Dimitrios S. Nikolopoulos, Costas Bekas, A. Cristiano I. Malossi, AAAI Conference on Artificial Intelligence, 2019

<sup>10.</sup> The CIFAR-10 and CIFAR-100 datasets (Canadian Institute for Advanced Research) are a collection of images that are com-monly used to train and algorithms. It is one of the most widely used datasets for machine learning research.

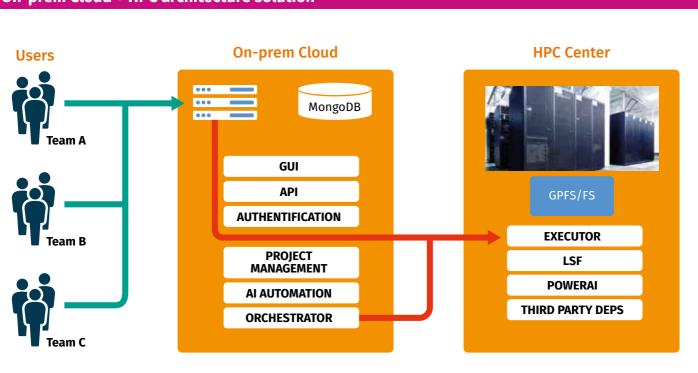

#### On-prem Cloud + HPC architecture solution

#### Figure 8: Example of an infrastructure for AI Automation

dologies, without having any expertise concerning data-science, optimisation, data preparation, hyper-parameter selection and training analysis.

The project is rooted around the idea that every time a user generates manually or semi-automatically an AI model, the system can learn from this work and improves over time. In this setting, HPC centres could become large incubators where the Automation of AI framework learns automatically from all the users developing AI models and gradually is enabled to automatically generate new models for a similar future workload. This is achieved by leveraging meta-learning information acquired during the execution of the user workloads.

The platform through which the users submit jobs must be intuitive and as simple as any tool that requires at most a few clicks of a mouse. All user-based decisions will be described by high level constraints, such as accuracy, reliability, size of model, time for inference and latency. Based on the data, and the user provided constraints the automated framework will synthesise the best model and serve it to the user.

The infrastructure used (see Figure 8) consists of:

a front-end/Cloud-similar system, to manage UI, user access, projects, and AI Automation logic. This does not require GPUs; however, it must be scalable to be used by many users at same time. It can also be containerised and should be supported by classical DBs.  a back-nd HPC system, with many nodes equipped with GPUs or FPGAs. This system is where all the compute intensive workloads occurs (e.g. model synthesis and training).

© IBM

The HPC infrastructure, typically made of many high-performance nodes and one or more submission front-end servers (with ssh access) needs to be tightly coupled with the on-premise Cloud- similar nodes, where permanent services can be run for authentication, UI, DBs, backup and orchestrators instances. Those services cannot run on the classical HPC server front-end, because they are too heavy and would compromise performance of the front-end where users expect to do ssh access for the non-Al workloads.

The coupling between Cloud-based nodes & classical HPC nodes should be made in a way that:

- There is a fast connection (e.g. Infiniband type) between the Cloud-HPC nodes

- DBs instantiated on the on-premise Cloud nodes should be visible and fast accessible from all nodes.

- The shared file system on the HPC nodes should be visible from the on-Cloud nodes.

- The on-premise Cloud nodes will run services containerised.

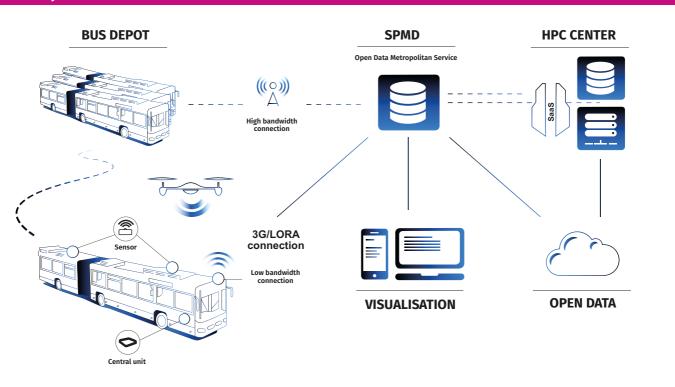

#### **AQMP Project Overview**

Figure 9: AQMO continuum overview

#### 2.3.4

#### USE CASE 4: AQMO<sup>11,12</sup>: An Edge to HPC Digital Continuum for Air Quality

Air quality improvement is a major challenge for most metropolises. Proposing efficient policies to address this challenge requires solving two issues: 1/ performing air quality measurement with a thorough temporal and spatial coverage and 2/ understanding the dispersion of the pollution as well as being able to analyse "what-if" scenarios.

The measurement issue is addressed using multiple sensors while the second one is related to the use of HPC numerical simulations. Of course, the two issues are intimately entangled. The measurements provide the basis for elaborating the model inputs and validation while the numerical dispersion model (currently the SIRANE model<sup>13</sup>) gives an insight into how the pollution reaches the citizens.

The AQMO project provides an end-to-end urban platform that extends current practices in air quality measurements. Figure 9 shows an overview of the Digital Continuum designed to implement the platform. This continuum integrates Edge technology, Cloud facilities and supercomputers. It is intended to provide citizens, local authorities, scientific organisations and private companies with new Open-Data and innovative services based on computing simulation (High-Performance Computing - HPC - and Edge Computing / IoT). These new services are a pilot implementation of a new business model called "HPC as a service" which will be analysed as a new way to access the future European Exascale HPC facilities.