# Reliability-aware energy optimization for throughput-constrained applications on MPSoC

Changjiang Gou, Anne Benoit, Mingsong Chen, Loris Marchal, Tongquan Wei

# ▶ To cite this version:

Changjiang Gou, Anne Benoit, Mingsong Chen, Loris Marchal, Tongquan Wei. Reliability-aware energy optimization for throughput-constrained applications on MPSoC. ICPADS - 24th International Conference on Parallel and Distributed Systems, Dec 2018, Sentosa, Singapore. pp.1-10. hal-01929927

# HAL Id: hal-01929927 https://inria.hal.science/hal-01929927

Submitted on 21 Nov 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Reliability-aware energy optimization for throughput-constrained applications on MPSoC

Changjiang Gou\*<sup>‡</sup>, Anne Benoit\*<sup>†</sup>, Mingsong Chen<sup>‡</sup>, Loris Marchal\* and Tongquan Wei<sup>‡</sup>

\*Univ. Lyon, CNRS, ENS de Lyon, Inria, Univ. Claude-Bernard Lyon 1, LIP UMR5668, France

†Georgia Institute of Technology, Atlanta, USA

<sup>‡</sup>MoE International Joint Lab of Trustworthy Software, East China Normal University, Shanghai, China 200062 Email: {changjiang.gou, anne.benoit, loris.marchal}@ens-lyon.fr, {mschen,tqwei}@sei.ecnu.edu.cn

Abstract—Multi-Processor System-on-Chip (MPSoC) has emerged as a promising platform to meet the increasing performance demand of embedded applications. However, due to limited energy budget, it is hard to guarantee that applications on MPSoC can be accomplished on time with a required throughput. The situation becomes even worse for applications with high reliability requirements, since extra energy will be inevitably consumed by task re-executions or duplicated tasks. Based on Dynamic Voltage and Frequency Scaling (DVFS) and task duplication techniques, this paper presents a novel energy-efficient scheduling model, which aims at minimizing the overall energy consumption of MPSoC applications under both throughput and reliability constraints. The problem is shown to be NP-complete, and several polynomial-time heuristics are proposed to tackle this problem. Comprehensive simulations on both synthetic and real application graphs show that our proposed heuristics can meet all the given constraints, while reducing the energy consumption. Index Terms—Scheduling, MPSoC, energy minimization, throughput, reliability.

# I. Introduction

Many smart applications in areas such as Internet of Things (IoT), augmented reality, and robotics, increasingly require high performance on embedded processing platforms. The three main criteria are i) computational performance, expressed as the throughput of the application; ii) reliability, i.e., most datasets must be successfully computed; and iii) energy efficiency. This is mainly because: i) applications such as audio/video coding or deep learning-based inference are delaysensitive, hence throughput should be properly guaranteed; ii) emerging safety-critical applications such as self-driving vehicles and tactile internet impose extremely stringent reliability requirements [1]; iii) devices on which smart applications are running are often battery-operated, hence systems should be energy-efficient.

In order to meet all these design constraints, Multi-Processor System-on-Chip (MPSoC) is becoming a new paradigm that enables efficient design of smart applications. By integrating multiple cores together with an interconnection fabric (e.g., Network-on-Chip) as communication backbone, MPSoC can be tailored as multiple application-specific processors with high throughputs but low energy consumption [2], [3].

As one of the most effective power management techniques, Dynamic Voltage and Frequency Scaling (DVFS) has been widely used by modern MPSoCs [4]. By properly lowering the processing voltages and frequencies of dedicatedly mapped tasks, DVFS enables smart applications to be carried out with a reduced energy consumption, while ensuring a given throughput. However, scaling down voltages and frequencies of processors generates serious reliability problems. Various phenomena such as high energy cosmic particles and cosmic rays may cause the change of binary values held by transistors within CMOS processors by mistake, resulting in notorious transient faults (i.e., soft errors). Along with the increasing number of transistors integrated on a chip according to Moore's Law, the susceptibility of MPSoC to transient faults will increase by several orders of magnitude [5]. In other words, the probability of incorrect computation or system crashes will become higher due to soft errors.

To mitigate the impact of soft errors, checkpointing and task replication techniques have been widely used to ensure system reliability [6], [7]. Tasks can be replicated if they do not have an internal state. This increases their reliability as it is extremely unlikely to have errors on two or more copies. Although checkpointing and task replication techniques are promising on enhancing the system reliability, frequent utilization of such fault-tolerance mechanisms is very time or resource consuming, which will in turn cost extra energy and degrade the system throughput. Clearly, the MPSoC design objectives (i.e., energy, reliability, and throughput) are three contradictory requirements when we need to decide the voltage and frequency level assignments for tasks. Although there exist dozens of approaches that can effectively handle the trade-off between energy and reliability issues, few of them consider the throughput requirement, see Section II. Hence, given throughput and reliability constraints, how to achieve a fault-tolerant schedule that minimizes the energy consumption for a specific DVFS-enabled MPSoC platform is becoming a major challenge for designers of smart applications.

To address the above problem, this paper proposes a novel scheduling approach that can generate energy-efficient and soft error resilient mappings for applications on a given MPSoC platform. We focus on pipelined linear chain applications, which are ubiquitous in processing of streaming datasets in the context of embedded systems [8]. Datasets continuously and periodically enter through the first task, and several datasets can be processed concurrently by different tasks. The throughput is the number of datasets that can be processed per time unit, and we consider the inverse of the throughput, called

*period*, which is the time interval at which we can periodically start processing new datasets. The three major contributions are the following:

- We propose a novel model that can formally express both performance and reliability constraints for mapping applications on MPSoCs, by bounding the expected period (for performance) and the probability of exceeding the target expected period (for reliability). The goal is to decide which tasks to duplicate, and at which speed to operate them, so that the energy consumption is minimized, while meeting the constraints.

- We prove that without performance and reliability constraints, the problem is polynomially tractable, whereas adding both constraints results in an NP-complete problem.

- 3) We design novel task scheduling heuristics for reliability-aware energy optimization on MPSoCs, which enforce the constraints and aim at minimizing the energy consumption. Extensive simulations demonstrate that heuristics can meet the constraints and considerably reduce the energy consumption compared to naive approaches.

The reminder of the paper is organized as follows. Related work is discussed in Section II. Then, we formalize the application model and optimization problem in Section III. Section IV studies the complexity of the problem variants, and in particular proves that the complete version of the problem is NP-complete. The heuristics are introduced in Section V, and they are thoroughly evaluated in Section VI on both real and synthetic applications. Finally, Section VII concludes and provides directions for future work.

# II. RELATED WORK

MPSoCs have been deployed in various embedded applications such as image processing, process control, and autonomous navigations. Typical MPSoC consists of many fully connected identical processors with independent clock domains, such as AsAP2 [9] and KiloCore [21], which has 164 and 1000 identical processors respectively, communication on-chip is accomplished by a high-throughput and lowlatency circuit-switched network and a packet router. They are especially designed for embedded multimedia applications, and featured as high energy efficiency and performance and easy to program [9]. Throughput maximization problem has been a subject of continuing interest as the demands for MPSoC-enabled high performance computing drastically increase. Zhang et al. [10] optimize the throughput in disruption tolerant networks via distributed workload dissemination, and design a centralized polynomial-time dissemination algorithm based on the shortest delay tree. Li et al. [11] specifically consider stochastic characteristics of task execution time to tradeoff between schedule length (i.e., throughput) and energy consumption. A novel Monte Carlo based task scheduling is developed to maximize the expected throughput without incurring a prohibitively high time overhead [12]. Albers et al. [13] introduce an online algorithm to further maximize throughput with parallel schedules. However, reliability issues are not considered in these works.

Reliability can be achieved by reserving some CPU time for re-executing faulty tasks due to soft errors [5]. In [14], the authors present a representative set of techniques that map embedded applications onto multicore architectures. These techniques focus on optimizing performance, temperature distribution, reliability and fault tolerance for various models. Dongarra et al. [15] study the problem of scheduling task graphs on a set of heterogeneous resources to maximize reliability and throughput, and proposed a throughput/reliability tradeoff strategy. Wang et al. [16] propose replication-based scheduling for maximizing system reliability. The proposed algorithm incorporates task communication into system reliability and maximizes communication reliability by searching all optimal reliability communication paths for current tasks. These works explore the reliability of heterogeneous multicore processors from various aspects, and present efficient reliability improvement schemes, however, these works do not investigate the energy consumed by MPSoCs, which interplays with system reliability.

Extensive research effort has been devoted to reduce energy consumption of DVFS-enabled heterogeneous multi-core platforms considering system reliability. Zhang et al. [17] propose a novel genetic algorithm based approach to improve system reliability in addition to energy savings for scheduling workflows in heterogeneous multicore systems. In [7], Spasic et al. present a novel polynomial-time energy minimization mapping approach for synchronous dataflow graphs. They use task replication to achieve load-balancing on homogeneous processors, which enables processors to run at a lower frequency and consume less energy. In [18], Das et al. propose a genetic algorithm to improve the reliability of DVFS-based MPSoC platforms while fulfilling the energy budget and the performance constraint. However, their task mapping approach tries to minimize core aging together with the susceptibility to transient errors. In [6], the authors consider the problem of achieving a given reliability target for a set of periodic real-time tasks running on a multicore system with minimum energy consumption. The proposed framework explicitly takes into account the coverage factor of the fault detection techniques and the negative impact of DVFS on the rate of transient faults leading to soft errors. In [19], the authors propose energy-efficient scheduling algorithms with reliability goal for embedded systems, but they do not consider pipelined applications, and hence do not need to consider the throughput.

Hence, although above works explore various techniques to save energy, to the best of our knowledge, none of them consider system throughput in addition to reliability and energy. Our approach is thus the first attempt to model and optimize at the same time performance, reliability, and energy for workflow scheduling on MPSoC.

# III. MODELS AND OPTIMIZATION PROBLEMS

We consider the problem of scheduling a pipelined workflow onto a homogeneous multi-core platform that is subject

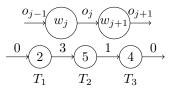

Figure 1: Linear chain workflow application.

to failures. The goal is to minimize the expected energy consumption for executing a single dataset, given some constraints on the expected and worst-case throughput of the workflow. In the following subsections, we detail how to model applications, platforms, failures, energy cost, period (which is the inverse of the throughput), and how to formally define the optimization problems.

### A. Applications

We focus on linear chain workflow applications, where task dependencies form a linear chain: each task requests an input from the previous task, and delivers an output to the next task. There are n tasks  $T_1, \ldots, T_n$ . Furthermore, the application is pipelined, i.e., datasets continuously enter through the first task, and several datasets can be processed concurrently by the different tasks.

We assume that the initial data reside in memory, and the final data stay in memory. Task  $T_j$  is characterized by a workload  $w_j$ , and the size of its output file to the next task is  $o_j$ , as illustrated in Fig. 1 (except for the last task). In the example, we have  $w_1 = 2$ ,  $w_2 = 5$ ,  $w_3 = 4$ , and  $o_1 = 3$ ,  $o_2 = 1$ . Once the first dataset reaches task  $T_3$ , while it is processed by  $T_3$ , dataset 2 is transferred between  $T_2$  and  $T_3$ , dataset 3 is processed by  $T_2$ , dataset 4 is transferred between  $T_1$  and  $T_2$ , and dataset 5 is processed by  $T_2$ . At the next period, all dataset numbers are incremented by one.

#### B. Platforms

The target platforms are embedded systems composed of p homogeneous computing cores. Each core can run at a different speed with a corresponding error rate and a power consumption. If task  $T_j$  is executed on a core operating at speed s(j) and if it is not subject to a failure, it takes a time  $\frac{w_j}{s(j)}$  to execute a single dataset.

We focus on the most widely used speed model, the discrete

We focus on the most widely used speed model, the *discrete* model, where cores have a discrete number of predefined speeds, which correspond to different voltages at which the core can be operating. Switching is not allowed during the execution of a given task, but two different executions of a task can be executed at different speeds. The set of speeds is  $\{s_{\min} = s_1, s_2, \ldots, s_K = s_{\max}\}$ . The *continuous* model is used mainly for theoretical studies, and let the speed take any value between the minimum speed  $s_{\min}$  and the maximum speed  $s_{\max}$ .

All cores are fully interconnected by a network on chip (NoC). The bandwidth  $\beta$  is the same between any two cores, hence it takes  $\frac{o_j}{\beta}$  for task  $T_j$  to communicate a dataset to task  $T_{j+1}$ . The network on chip enables cores to communicate simultaneously with others while they are computing, i.e.,

communications and computations can be overlapped. Therefore, while task  $T_j$  is processing dataset k, it is receiving the input for dataset k-1 from the previous task, and sending the output for dataset k+1 to the next task. Hence, these operations overlap, and take respectively a time  $\frac{o_{j-1}}{\beta}$  and  $\frac{o_{j}}{\beta}$ .

We follow the model of [20], [21], where cores are equipped with a router, and on which there are registers. We can use the registers to store intermediate datasets, hence having *buffers* between cores. If datasets are already stored in the input buffer of a core, and if there is empty space in the output buffer, then the core can process a dataset without having to wait for the previous or next core.

# C. Failure model and duplication

Embedded system platforms are subject to failures, and in particular transient errors caused by radiation. When subject to such errors, the system can return to a safe state and repeat the computation afterwards. According to the work of [22], radiation-induced transient failures follow a Poisson distribution. The fault rate is given by:

$$\lambda(s) = \lambda_0 e^{d\frac{s_{\max} - s}{s_{\max} - s_{\min}}},$$

where  $s \in [s_{\min}, s_{\max}]$  denotes the running speed, d is a constant that indicates the sensitivity to DVFS, and  $\lambda_0$  is the average failure rate at speed  $s_{\max}$ .  $\lambda_0$  is usually very small, of the order of  $10^{-5}$  per hour [23]. Therefore, we can assume that there are no failures when running at speed  $s_{\max}$ . We can see that a very small decrease of speed leads to an exponential increase of failure rate.

The failure probability of executing task  $T_j$  (without duplication) on a processor running at speed  $s_k$  is therefore  $f_j(s_k) = \lambda(s_k) \frac{w_j}{s_k}$ . If an error strikes, we resume the execution by reading the dataset again from local memory (i.e., the input has been copied before executing the task, we re-execute the task on the copy), and this re-execution is done at maximum speed so that no further error will strike the same dataset on this task. We assume that the time to prepare re-execution is negligible. Still, this slows down the whole workflow since other tasks may need to wait.

We propose to duplicate some tasks to mitigate the effect of failures and have a reliable execution. This means that two identical copies of a same task are executed on two distinct cores, both cores running at the same speed. In this case, if a failure occurs in only one copy, we can keep going with the successful copy. However, it may increase the energy cost and communication cost. Similarly to one execution at the maximum speed, we assume that an error on a duplicated task is very unlikely (i.e., at least one copy will be successful), and hence  $f_j(s_k) = 0$  if  $T_j$  is duplicated.

Let  $m_j=1$  if task  $T_j$  is duplicated, and  $m_j=0$  otherwise. Let  $s_k$  be the speed at which  $T_j$  is processed. The failure probability for  $T_j$  is therefore  $f_j(s_k)=(1-m_j)\lambda(s_k)\frac{w_j}{s_k}$ , i.e., it is zero if the task is duplicated, and  $\lambda(s_k)\frac{w_j}{s_k}$  otherwise (the instantaneous error rate at speed  $s_k$  times the time to execute task  $T_j$ ).

If we do not account for communications, the expected execution time of task  $T_i$  running at speed  $s_k$  is:

$$t_j = \frac{w_j}{s_k} + f_j(s_k) \frac{w_j}{s_{\text{max}}}.$$

Indeed, with duplication, at least one execution will be successful, while with a single execution, if there is a failure, we re-execute the task at maximum speed and there are no further failures.

Note that if a task  $T_j$  is duplicated, this implies that further communications may be done, but they will occur in parallel. Both processors on which  $T_j$  is executed are synchronized, and only one of them obtaining a correct result will do the output communication (to one or two processors, depending on whether  $T_{j+1}$  is duplicated or not). The copy subject to soft errors can be detected by acceptance test or sanity test [24], and the synchronization cost is assumed to be negligible.

# D. Energy

We follow a classical energy model, see for instance [25], where the dissipated dynamic power for speed  $s_k$  is  $s_k^3$ , and hence the energy consumed for a single execution of task  $T_j$  running at speed  $s_k$  is  $\frac{w_j}{s_k} \times s_k^3 = w_j s_k^2$ . We focus on the dynamic power, and ignore the leakage (or static) power, since we assume that the platform is continuously on, and we cannot switch any core off.

We further account for possible failures and duplication, hence obtaining the expected (dynamic) energy consumption for  $T_i$  running at speed  $s_k$  for one dataset:

$$E_j(s_k) = (m_j + 1)w_j s_k^2 + f_j(s_k)w_j s_{\text{max}}^2$$

.

Indeed, if task  $T_j$  is duplicated  $(m_j = 1)$ , we always pay for two executions  $(2w_js_k^2)$  but there is no energy consumed following a failure, while without duplication  $(m_j = 0)$ , we account for the energy consumed by the re-execution in case of a failure.

We assume that the energy consumed by communications and buffers is negligible compared to the energy consumed by computations [20]. Therefore, the expected energy consumption of the whole workflow to compute a single dataset is the sum of the expected energy consumption of all tasks.

# E. Period definition and constraints

As stated before, each task is mapped onto a different processor, or a pair of processors when duplicated, and different tasks are processing different datasets. In steady-state mode, the throughput is either constrained by the task with the longest execution time, or by the longest communication time, which is slowing down the whole workflow. The time required between the execution of two consecutive datasets corresponds to this bottleneck time and is called the period. It is the inverse of the throughput.

In this work, we are given a target period  $P_t$ , hence the target throughput is  $\frac{1}{P_t}$ . This corresponds for instance to the rate at which datasets are produced. We consider two different constraints: i) ensure that the expected period is not exceeding  $P_t$ , hence the target becomes a bound, and/or

ii) ensure that the probability of exceeding the target  $P_{\rm t}$  for a given dataset is not greater than  $proba_{\rm t}$ . This second constraint corresponds to real-time systems, where a dataset is lost if its execution exceeds the target period  $P_{\rm t}$ , and the probability  $proba_{\rm t}$  ( $0 \le proba_{\rm t} \le 1$ ) expresses how many losses are tolerated. If  $proba_{\rm t} = 1$ , there is no constraint, while  $proba_{\rm t} = 0$  means that no losses are tolerated.

Recall that the objective is to minimize the expected energy consumption per dataset of the whole workflow. Some tasks may be duplicated, and each task may run at a different speed. The communication between two consecutive tasks  $T_j$  and  $T_{j+1}$  takes a constant time  $\frac{o_j}{\beta}$ , and it must fit within the target period. Therefore, we assume that for all  $1 \le j < n$ ,  $\frac{o_j}{\beta} \le P_l$ .

We assume in this section that the set of duplicated tasks is known: we set  $m_i$  to 0 or 1 for each task  $T_i$ . Furthermore, let s(i) be the speed at which task  $T_i$  is executed, for  $1 \le i \le n$ .

We first consider the case without failures and express the period in this case. Then, we express the expected period when the platform is subject to failures. Note that we assume that there is a sufficient number of buffers between cores, so that a failure does not necessarily impact the period, given that the cores have access to datasets stored in buffers, and can use empty buffers to store output datasets. Finally, we explain how to compute the probability that a dataset exceeds the target period  $P_1$ .

1) Period without failures: In the case without failures, the period is determined by the bottleneck task computation or communication:  $P_{\rm nf} = \max_{1 \leq i \leq n} \left\{ \frac{w_i}{s(i)}, \frac{o_i}{\beta} \right\}$ . We denote by L the set of tasks whose execution time is

We denote by L the set of tasks whose execution time is equal to  $P_{\rm nf}$ , i.e.,  $L = \left\{ T_i \middle| \frac{w_i}{s(i)} = P_{\rm nf} \right\}$ . If the bottleneck time  $P_{\rm nf}$  is achieved by a communication, this set may be empty.

2) Expected period: We consider that each processor is equipped with three or more buffers, two of them holding an input (resp. output) dataset being received (resp. sent), and the other buffers are used for storing intermediate datasets: a buffer is filled when the task is completed, but the following processor is not yet ready to receive the next dataset (i.e., the output buffer is still in use). We consider the period in steady-state, after the initialization has been done, i.e., all processors are currently working on some datasets.

The set of tasks L is empty if the computation time for all tasks is strictly smaller than the period  $P_{\rm nf}$ . When subject to a failure, tasks not in L can use data stored in buffers and process datasets at a faster pace than the period, until they have caught up with the time lost due to the failure.

However, errors in tasks of L are impacting the period, and therefore, if such a task is subject to failure, the re-execution time is added to the period. The expected period can therefore be expressed as follows:

$$P_{\text{exp}} = P_{\text{nf}} + \sum_{j \in L} f_j(s(j)) \frac{w_j}{s_{\text{max}}}.$$

(1)

Indeed, the period  $P_{nf}$  is achieved when there is either no failure, or a failure in a task not in L. In case of a failure

while executing a task  $T_j$  in L, the period is  $P_{\rm nf} + \frac{w_j}{s_{\rm min}}$ , and this happens with a probability  $f_i(s(j))$ . As discussed before, we assume that there is no failure during re-execution, and that the probability of having two failures while executing a single dataset is negligible.

Note that this formula also holds when some tasks are duplicated. If task  $j \in L$  is duplicated  $(m_j = 1)$ , it will never fail and hence its period will be  $P_{nf}$ . In this case,  $f_i(s(j)) = 0$ by definition, hence the formula remains correct.

3) Bounding the probability of exceeding the period bound: For the second constraint, we focus on the actual period of each dataset, rather than the expected period, and we estimate the probability at which the period of a dataset exceeds  $P_t$ . We consider that  $P_{\rm nf} \leq P_{\rm t}$ , otherwise the bound can never be reached, and the probability is always one.

The actual period, denoted by  $P_{act}$ , is a random variable that ranges from  $P_{\rm nf}$  to  $\max_{1 \le i \le n} \left( \frac{w_i}{s(i)} + \frac{w_i}{s_{\rm max}} \right)$ . We define the set of tasks that may exceed the target period  $P_{\rm t}$  in case of failures:

$$S_{\text{excess}} = \left\{ T_i \mid \frac{w_i}{s(i)} + \frac{w_i}{s_{\text{max}}} > P_{\text{t}} \right\}.$$

Therefore, if a failure strikes a task in  $S_{\rm excess}$  on a given dataset, the target period  $P_t$  may not be met for this dataset. An error happens on task i with probability  $f_i(s(i))$ . Since failures are independent, the period of a dataset will not exceed the bound if and only if no task in the set  $S_{\text{excess}}$  has a failure, i.e., this happens with a probability  $\prod_{T_i \in S_{\text{excess}}} (1 - f_i(s(i)))$ . Hence, the probability of exceeding the bound is given by:

$$P(P_{\text{act}} > P_{\text{t}}) = 1 - \prod_{T_i \in S_{\text{excess}}} (1 - f_i(s(i))) \approx \sum_{T_i \in S_{\text{excess}}} f_i(s(i)),$$

(2)

considering that the failure probabilities are small, and that  $f_i(s(i)) \times f_j(s(j)) = 0$  for any  $1 \leq i, j \leq n$ . This approximation is in line with the assumption that we do not consider two consecutive failures in a same task.

Finally, the second constraint that we consider, after the one on the expected period described above, is to bound the probability of exceeding the target period  $P_t$  by the target probability  $proba_t$ :

$$P(P_{\text{act}} > P_{\text{t}}) \leq proba_{\text{t}}$$

.

# F. Optimization problems

The objective is to minimize the expected energy consumption per dataset of the whole workflow, and we consider two constraints. The goal is to decide which tasks to duplicate, and at which speed to operate each task. More formally, the problem is defined as follows:

(MINENERGY). Given a linear chain composed of n tasks, a computing platform with p homogeneous cores that can be operated with a speed within set S, a failure rate function f, and a target period  $P_t$ , the goal is to decide, for each task  $T_i$ , whether to duplicate it or not (set  $m_i = 0$  or  $m_i = 1$ ), and at which speed to operate it (choose  $s(j) \in S$ ), so that

the total expected energy consumption is minimized, under the following constraints:

- i) The expected period  $P_{exp}$  should not exceed  $P_t$ ;

- ii) The probability of exceeding the target period  $P_t$  should not exceed the target probability  $proba_t$ .

Note that if there is a task k such that  $P_{\rm t}<\frac{w_k}{s_{\rm max}}$  or  $P_{\rm t}<\frac{o_k}{\beta}$ , then there is no solution (the target period can never be met).

If  $P_t$  is large enough, the problem will not be constrained since in all solutions, the expected period will always be under the target period. This is the case for  $P_{\rm t} \geq \max(\frac{w_i}{s_{\rm min}} + \frac{w_i}{s_{\rm max}})$ and  $P_t \geq \max(\frac{o_k}{\beta})$ . In this case, each task running at the slowest possible speed, and being re-executed after a failure, will not exceed  $P_t$ . This problem without constraints is denoted as MINENERGY-NOC.

We also consider the particular cases where only one or the other constraint matters. MINENERGY-PERC is the problem where we do only consider the first constraint on the expected period while MINENERGY-PROBAC is the problem where we do only focus on the probability of exceeding the target period.

#### IV. COMPLEXITY ANALYSIS

#### A. Without errors

When the workflow is free of errors, a task  $T_j$  running at speed  $s_j$  takes exactly a time  $\frac{w_j}{s_j}$ , and consumes an energy of  $w_i s_i^2$ . Hence, to minimize the energy consumption, one must use the smallest possible speed such that the target period is not exceeded, hence  $s_j = \max\left\{\frac{w_j}{P_t}, s_{\min}\right\}$  in the continuous case. Since we consider discrete speeds, the optimal speed for task  $T_i$  is therefore the smallest speed larger than or equal to  $\frac{w_j}{P_l}$  within the set of possible speeds. This is true for all tasks, hence the problem can be solved in polynomial time.

#### B. Without constraints

We consider the MINENERGY-NOC problem, and propose the **BestEnergy** algorithm to optimally solve this problem. The idea is to use the speed that minimizes the energy consumption for each task, since we do not have any constraint about exceeding the target period. For each task, either we execute it at this optimal speed, or it may be even better (in terms of energy consumption) to duplicate it and run it at the smallest possible speed  $s_{\min}$ .

Theorem 1. MINENERGY-NOC can be solved in polynomial time, using the BestEnergy algorithm, both for the discrete and for the continuous energy model.

*Proof.* Given a task of weight w executed at speed s without duplication, the energy consumption is  $E(s) = w \times s^2 +$  $\lambda_0 w^2 s_{\max}^2 \frac{e^{d \frac{s_{\max} - s}{s_{\max}}}}{s}$ . The (continuous) speed that minimizes this energy consumption can be obtained by deriving E(s):

$$E'(s) = 2ws - \left(\frac{\lambda_0 w^2 s_{\max}^2}{s^2} + \frac{\lambda_0 dw^2 s_{\max}^2}{s(s_{\max} - s_{\min})}\right) e^{d\frac{s_{\max} - s}{s_{\max} - s_{\min}}}.$$

E'(s) is a monotonically increasing function, and we let  $s^*$ be the speed such that  $E'(s^*) = 0$ , hence  $E(s^*)$  is minimum. If the task is not duplicated, for MINENERGY-NOC-CONT, the optimal speed is  $s_{\rm opt} = \max\{s^*, s_{\rm min}\}$ . In the discrete case MINENERGY-NOC-DISC,  $s_{\rm opt}$  is simply the speed that minimizes the energy consumption, hence  $s_{\rm opt} = {\rm argmin}_{s \in \{s_{\rm min}, \dots, s_{\rm max}\}} \{E(s)\}$ .

Now, if the task is duplicated, we assume that it will not be subject to error, hence the energy consumption at speed s is  $2ws^2$ . Therefore, it is minimum when the task is executed at the minimum speed, and the corresponding energy consumption is  $2ws_{\min}^2$ , both in discrete and continuous case.

**BestEnergy** is a greedy algorithm that sets the speed of each task at  $s_{\text{opt}}$  (not using duplication), and then greedily assigns remaining processors to tasks that would gain most from being duplicated (if any), see Algorithm 1. It is easy to see that it is optimal, since any other solutions could only have a greater energy consumption. The time complexity is  $O(n \log n)$ , for sorting the tasks by possible gains. The loops take a time O(n+p) = O(n) since we cannot use more than p=2n processors.

# Algorithm 1 – BestEnergy(n, p)

```

1: for i=1 to n do

Compute s_{\text{opt}}(i) for task T_i, the speed that minimizes energy

consumption if T_i is not duplicated;

3:

s_i \leftarrow s_{\text{opt}}(i), m_i \leftarrow 0;

g_i \leftarrow E(s_i) - 2w_i s_{\min}^2 {Possible gain in energy if T_i is

duplicated};

5: end for

6: Sort tasks by non-increasing g_i, T_j is the task with max g_i;

7: p_{av} \leftarrow p - n {Number of available processors};

while g_j > 0 and p_{av} > 0 do

m_j \leftarrow 1, s_j \leftarrow s_{\min}, p_{av} \leftarrow p_{av} - 1;

j \leftarrow the index of next task in the sorted list;

10:

11: end while

12: return < s_i, m_i >;

```

#### C. With the probability constraint

**Theorem 2.** MINE-DEC is NP-complete, even when duplicating tasks is not possible.

In the decision version of MINE-DEC, the goal is to find an assignment set of speeds such that the probability of exceeding the target period  $P_{\rm t}$  does not exceed  $proba_{\rm t}$ , and such that the energy consumption does not exceed a given energy threshold  $E_{\rm t}$ . The proof, which can be found in the companion research report [26], is based on a reduction from the Partition problem, known to be NP-complete [27]. The idea is to have only two possible speeds, and one must decide at which speed to operate each task. We set as many processors as tasks, so that no duplication can be done.

# V. HEURISTICS

We provide here several heuristics, all designed for the more realistic case of discrete speeds. We start with basic heuristics that will be used as baseline. Then we design heuristics aiming at bounding the expected period, and finally heuristics for bounding the probability of exceeding the target period. All heuristics are of polynomial complexity at most  $O(n \log n)$ .

# Algorithm 2 – MaxSpeed(n, p)

```

1: for i=1 to n do

2: s_i \leftarrow s_{\max}, m_i \leftarrow 0;

3: end for

4: return < s_i, m_i >;

```

# Algorithm 3 – DuplicateAll(n, p)

```

1: if p \geq 2n then

2: for i=1 to n do

3: Choose s_i as the smallest possible speed so that \frac{w_i}{s_i} \leq P_i,

m_i \leftarrow 1;

4: end for

5: return < s_i, m_i >;

6: else

7: return failure;

8: end if

```

### A. Baseline heuristics

We first outline the baseline heuristics that will serve as a comparison point, but may not satisfy the constraints. First, the **BestEnergy** algorithm described in Section IV-B is providing a lower bound on the energy consumption, but since it means that many tasks are running at the minimum speed, we expect the period to be large, and it may well exceed the bound.

Another simple solution consists in having each task executed at the maximum speed  $s_{\text{max}}$ . We refer to this heuristic as **MaxSpeed** (see Algorithm 2).

The third baseline heuristic, **DuplicateAll** (see Algorithm 3), duplicates all tasks, assuming that there are twice more processors than tasks  $(p \ge 2n)$ , and the corresponding speeds for each tasks used in this case are the ones derived in Section IV-A. Indeed, there will not be any errors in this case, and we aim at respecting the target period  $P_{\rm t}$ .

Note that both **MaxSpeed** and **DuplicateAll** will always satisfy the bounds, since there will be no errors, and hence the expected period is equal to the period without failure. However, both heuristics may lead to a large waste of energy. They provide an upper bound on the energy consumption when using a naive approach. They both run in time O(n), provided that we have a constant number of speeds.

# B. Bounding the expected period

In this section, we focus on the constraint on the expected period, hence targeting the MINENERGY-PERC problem.

1) Heuristic Threshold: The Threshold heuristic aims at reaching the target expected period  $P_{\rm t}$  (see Algorithm 4). The first step consists in setting all task speeds to the smallest speed such that  $\frac{w_i}{s_i} \leq P_{\rm t}$ . If  $P_{\rm exp}$  is still larger than  $P_{\rm t}$ , then one of the tasks with largest duration  $(\frac{w_i}{s_i})$  is duplicated: this allows  $P_{\rm nf}$  to be smaller than  $P_{\rm t}$  and constant from this moment on. Note that in the special case of a communication time reaching  $P_{\rm t}$ , there is no need to duplicate a task to have  $P_{\rm nf} = P_{\rm t}$ .

According to Equation (1),  $P_{\text{exp}} = P_{\text{nf}} + \sum_{j \in L} f_j(s(j)) \frac{w_j}{s_{\text{max}}}$ . We made sure that  $P_{\text{nf}}$  is smaller than or equal to  $P_{\text{t}}$ . In order to make  $P_{\text{exp}} \leq P_{\text{t}}$ , each task  $T_i$  of L has to be either run at a higher speed (which removes it from L), or duplicated

# **Algorithm 4** – Threshold(n, p)

```

1: for all tasks T_i do

s_i \leftarrow the smallest speed such that \frac{w_i}{s_i} \leq P_t, m_i \leftarrow 0;

3: end for

4: p_{av} \leftarrow p - n (number of available processors);

5: if P_t > \max(\frac{o_k}{\beta}) and p_{av} \ge 1 then

Select a task T_k with largest duration (break tie by selecting

one with smallest w_k), set m_k \leftarrow 1 and p_{av} \leftarrow p_{av} - 1;

7: end if

8: if P_{\text{exp}} > P_{\text{t}} then

Q \leftarrow \{ \text{tasks of } L \text{ with } m_i = 0 \};

9:

10:

for all tasks T_j in Q do

s \leftarrow the smallest speed that is larger than s_j; g_j \leftarrow w_j*(s^2+f_j(s)s_{max}^2-2s_j^2) (Possible gain in energy if T_j is duplicated);

11:

12:

13:

Sort tasks of Q by non-increasing g_i;

14:

15:

for all task T_j in Q do

if p_{av} > 0 then

16:

17:

m_j \leftarrow 1, \, p_{av} \leftarrow p_{av} - 1;

18:

s_j \leftarrow the smallest speed that is larger than s_j;

19:

end if

20:

21:

end for

22: end if

23: for all tasks T_i with m_i = 0 do

Compute the speed s that minimizes E_i(s);

24:

25:

if s_i < s then

26:

s_i \leftarrow s;

end if

27:

28: end for

29: return < s_i, m_i >;

```

(which sets  $f_{(s(i))}$  to 0). We greedily duplicate tasks for which duplication costs less energy, until there remains no more processors. Then, we speed up other tasks. Finally, we use the same technique as in **BestEnergy** to attempt to reduce again the energy of non-duplicated tasks: if the minimum speed s for energy consumption is larger than the actual speed  $s_i$  of a task  $T_i$ , its speed is increased to s.

Here again, assuming a constant number of speeds, the complexity is dominated by the sorting at line 14, since all other loops are in O(n). The time complexity is hence  $O(n \log n)$ .

2) Heuristic Closer: The previous Threshold heuristic uses duplication: at least one task is duplicated (in order to fix  $P_{\rm nf}$ ), which requires spare processors. We propose another heuristic that does not have this requirement. In the Closer heuristic (see Algorithm 5), after setting all task speeds to the smallest ones so that  $\frac{w_i}{s_i} \leq P_{\rm t}$ , we increase the speed of all tasks in L while  $P_{\rm exp} > P_{\rm t}$  by scaling all tasks simultaneously: we set a coefficient and make sure that for each task, its speed is not smaller than  $coef \times s_i'$ , where  $s_i'$  is the initial speed of  $T_i$ . The coefficient is gradually increased until  $P_{\rm exp} \leq P_{\rm t}$ . Finally, we use the same technique as in **BestEnergy** to attempt to further reduce the energy consumption of tasks.

This heuristic is iterating while the criteria is not met, and the time to converge depends on the parameter  $\Delta s$ , and finishes at the latest when  $coef \times s_{\min} \geq s_{\max}$ , in which case tasks of set L will be set at speed  $s_{\max}$ . The number

# **Algorithm 5 Closer** $(n, p, \Delta s)$

```

1: for all tasks T_i do

s_i' \leftarrow the smallest speed such that \frac{w_i}{s_i} \leq P_t, m_i \leftarrow 0;

3: end for

4: Set coef \leftarrow 1;

5: while P_{\rm exp} > P_{\rm t} do

coef \leftarrow coef + \Delta s;

for all tasks T_i of set L do

7:

s_i \leftarrow \text{smallest speed not smaller than } coef \times s_i';

8:

9:

end for

10: end while

11: for all task T_i do

Compute the speed s that minimizes E_i(s);

if s_i < s then

13:

14:

s_i \leftarrow s;

end if

15:

16: end for

17: return < s_i, m_i >

```

of iteration is therefore bounded by  $N_{it} = \frac{1}{\Delta s} \left( \frac{s_{\max}}{s_{\min}} - 1 \right)$ , and the complexity is in  $O(N_{it} \times n)$ . If we set  $\Delta s$  such that  $N_{it} = O(\log n)$ , the time complexity is  $O(n \log n)$ .

# C. Bounding the probability of exceeding $P_t$

In this section, we design a heuristic focusing on the constraint on the probability of exceeding  $P_{\rm t}$ , thus for the MINENERGY-PROBAC problem.

**BestTrade** (see Algorithm 6) aims at finding the best tradeoff between energy consumption and the probability of exceeding  $P_{\rm t}$ . We consider for each task two critical speeds:

- $s_c^i$  is the speed such that  $w_i/s_c^i + w_i/s_{\text{max}} = P_t$ ; it corresponds to the minimum speed that a task can take without belonging to the  $S_{excess}$  set;

- $s_d^i = w_i/P_t$  is the minimum speed that can be assigned to a task: if it is set to a smaller speed, its duration will always exceed the target period.

The idea of the algorithm is first to set all tasks to the smallest speeds that are not smaller than their  $s_c^i$  speed. For some tasks, this might be equal to their minimum speed (the smallest possible speed not smaller than  $s_d^i$ ). In this case, there is no room for reducing speed again without exceeding the target period. For other tasks, we sort them by non-increasing weight: tasks with higher weights contribute the most to the energy dissipation and are thus first slowed down: we select the task  $T_i$  with the largest weight, reduce its speed to the minimum possible speed not smaller than  $w_i/P_{\rm t}$ . We continue with the tasks of smaller weight, until  $P(P_{\rm act} > P_{\rm t}) \geq proba_{\rm t}$ . At last, if  $P(P_{\rm act} > P_{\rm t}) > proba_{\rm t}$ , we undo the last move to make  $P(P_{\rm act} > P_{\rm t}) < proba_{\rm t}$ .

We then consider duplication: if duplicating a task  $T_i$  (and setting its speed to the smallest speed that is not smaller than  $s_d^i$ ) is beneficial compared to the current solution (and if a processor is available), the task is duplicated.

The only while loop is reducing at each iteration the speed of one of the tasks, so the number of iterations is bounded by n. The overall complexity is therefore  $O(n \log n)$  for the sorting at line 6.

### Algorithm 6 BestTrade(n, p)1: We assume all weights are different $(w_i \neq w_j \text{ for } i \neq j)$ ; 2: **for** j = 1 **to** j = n **do** $s_j \leftarrow \text{smallest possible speed not smaller than } w_j/(P_t$ $w_j/s_{\text{max}}), m_j = 0;$ 4: end for 5: $S_{reduce} \leftarrow$ tasks that have possible speeds between $w_i/P_t$ and $w_j/(P_{\rm t}-w_j/s_{\rm max});$ 6: Sort tasks of $S_{reduce}$ by non-increasing weight; 8: while $P(P_{act} > P_t) < proba_t$ do Reduce speed of the k-th task in $S_{reduce}$ to the smallest that is not smaller than $w_j/P_t$ ; 10: k = k + 1;11: end while 12: **if** $P(P_{act} > P_t) > proba_t$ **then** Set speed of the (k-1)-th task in $S_{reduce}$ to the smallest that is not smaller than $w_j/(P_t - w_j/s_{max})$ ; 14: end if 15: $p_{av} \leftarrow p - n$ (Number of available processors); 16: **for** j = 1 **to** j = n **do** $s_d \leftarrow$ the smallest speed that is not smaller than $w_j/P_t$ ; 17. **if** $2w_{j}s_{d}^{2} < w_{j}s_{j}^{2} + \bar{f}_{j}(s_{j})w_{j}s_{\max}^{2}$ and $p_{av} > 0$ **then** 18: 19: Duplicate $T_i$ : $m_i = 1, s_i = s_d, p_{av} \leftarrow p_{av} - 1$ ; end if 20: 21: **end for**

# VI. SIMULATION RESULTS

In this section, we evaluate all proposed algorithms through extensive simulations on both real applications and synthetic ones. For reproducibility purposes, the code is available at github.com/gouchangjiang/Pipeline on MPSoC.

Given a computing platform and an application, we set the target period  $P_t$  and probability  $proba_t$  so that all assumptions made in the model are true:

- When all tasks are executed with the minimum speed  $s_{\min}$ , the maximum failure rate is not larger than  $10^{-2}$ . With such a failure rate, the failure of two copies of a duplicated task is very unlikely, and the approximation in Equation (2) holds.

- When all tasks are processed with speed  $s_{\rm max}$ , the maximum failure rate is not larger than  $10^{-4}$ , which means that the failure of a task running at maximum speed is very unlikely.

- $P_{\rm t}$  should not be smaller than any task duration when running at maximum speed, otherwise, there is no way to meet the target period:  $P_{\rm t} \geq \frac{\max(w_i)}{s_{\rm max}}$ .

We set  $P_t = a + \kappa * (b - a)$ , where  $a = \max(w_i/s_{\max}, o_i)$  and  $b = \max(w_i/s_{\min} + w_i/s_{\max}, o_i)$ : a (respectively b) is the maximal time spent on a task (either on computation or on communication), when running at the maximum (resp. minimum) speed. This way,  $P_t$  is never smaller than a, which satisfies the third condition above. Similarly, we avoid the case  $P_t \geq b$ , in which the target is too loose, as even the minimum speed can achieve it. A small  $\kappa$  leads to a tighter target period. Under the above three conditions, we set  $\kappa$  to values from 0.05 to 0.95, by increment of 0.01. The target probability is set to

| Possible frequency/voltage | Normalized speed | Failure rate $(\times 10^{-6}/second)$ |

|----------------------------|------------------|----------------------------------------|

| 1.2 Ghz/1.3 V              | 1                | 1                                      |

| 987 Mhz/1.16 V             | 0.80             | 2.30                                   |

| 744 Mhz/1.03 V             | 0.61             | 5.29                                   |

| 502 Mhz/0.89 V             | 0.41             | 12.18                                  |

| 260 Mhz/0.75 V             | 0.21             | 28.01                                  |

| 66 Mhz/0.675 V             | 0.055            | 54.60                                  |

Table I: Configurations of computing platforms.

$proba_t = 0.05$  for synthetic applications and  $proba_t = 0.01$  for real applications.  $\Delta s$  in **Closer** is set as  $10^{-3}$ .

We use the result of heuristic **BestEnergy** described in Section IV-B as a comparison basis, as it gives the minimum energy consumption of the system without any constraints.

# A. Multi-core embedded systems

We simulate a multi-core computing platform with 512 cores. Based on AsAP2 and KiloCore, two state-of-art MP-SoCs described in Section II, the frequency/voltage options are listed in Table I. NoC on chips enables extremely fast communications. We describe the value of  $\beta$  together with the output (input) file sizes  $o_i$  below in the next subsection. The failure rate is computed as described in Section III-C as  $\lambda(s) = \lambda_0 e^{d\frac{s_{\max}-s}{s_{\max}-s_{\min}}}$ . Based on the settings in [22], we set  $\lambda_0 = 10^{-6}$  and d = 4.

# B. Streaming applications

We use a benchmark proposed in [28] for testing the **StreamIt** compiler. It collects many applications from varied representative domains, such as video processing, audio processing and signal processing. The stream graphs in this benchmark are mostly parametrized, i.e., graphs with different lengths and shapes can be obtained by varying the parameters. Table II lists some linear chain applications (or application whose major part is a linear chain) from [28]. Some applications, such as time-delay equalization, are more computation intensive than others.

Following the same idea, we also generated synthetic applications in order to test the algorithms on larger applications. We generated 3,000 linear chains, each has 0.5p nodes, where p is the number of cores. The weights of the nodes  $w_i$  follow a truncated normal distribution with mean value 2,000, where the values smaller than 100 or larger than 4,000 are removed. The standard deviation is 500. This ensures that the execution time is not too long so that failure rate is acceptable. The communication time  $(\frac{o_i}{\beta})$  follows a truncated normal distribution with mean value  $0.001*P_t$ , values that are larger than  $P_t$  are replaced by  $P_t$ . Here  $P_t = a + 0.05*(b - a)$ .

#### C. Simulation results

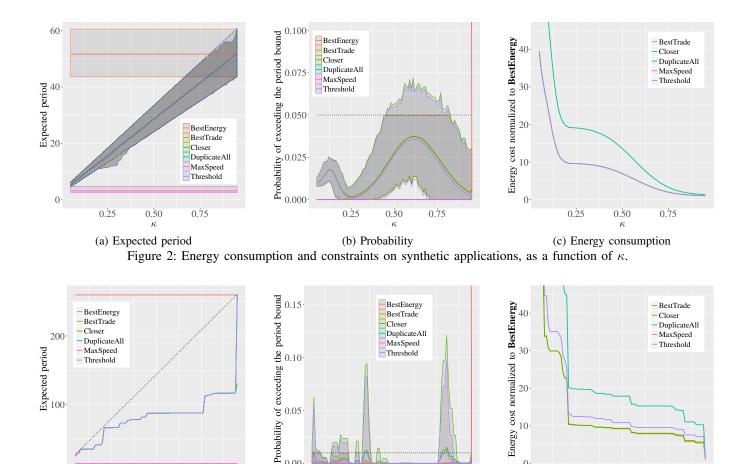

We present both results on synthetic applications and on real applications. On each plot, we show the minimum, mean, and maximum values of each heuristic. In some cases, only the mean is plotted to ease readability, when the minimum and maximum do not bring any meaningful information.

(a) Expected period (b) Probability (c) Energy consumption Figure 3: Energy consumption and constraints on real applications, as a function of  $\kappa$ .

0.50

0.75

0.25

| Application             | Size | Average         | SD              |

|-------------------------|------|-----------------|-----------------|

|                         |      | (node's weight) | (node's weight) |

| CRC encoder             | 46   | 14.20           | 3.71            |

| N-point FFT             | 13   | 1621.31         | 818.25          |

| Frequency hopping radio | 16   | 11815.81        | 19720.21        |

| 16x oversampler         | 10   | 2157.4          | 3724.84         |

| Radix sort              | 13   | 179.92          | 26              |

| Raytracer               | 5    | 142.8           | 188.59          |

| Time-delay equalization | 27   | 23264.78        | 10020.25        |

| Insertion sort          | 6    | 475.83          | 270.04          |

0.75

0.25

0.50

Table II: Real application examples.

1) Synthetic applications: Fig. 2 presents the results of all heuristics, both in terms of energy consumption, and in terms of constraints, when we vary the parameter  $\kappa$ , hence the tightness of the bound on the expected period. On Fig. 2a, the black dashed lines represent the minimum, maximum and average period bound. BestTrade, Closer and DuplicateAll are overlapped by **Threshold**. All chains have 0.5p nodes. Apart from MaxSpeed, which always meets the bound, and BestEnergy, which never meets the bound, all heuristics succeed to meet the bound on the expected period.

Fig. 2b shows the probability of exceeding the period bound, and the horizontal black dashed line is the target  $proba_t$ . **Du**plicateAll is overlapped by MaxSpeed, and only BestTrade

succeeds to always meet the bound. Closer and Threshold give very similar results, but sometimes exceed the bound (when  $0.4 \le \kappa \le 0.8$ ). **BestEnergy** may result in a probability of 0 when  $\kappa = 0.95$ , but for other values  $\kappa$ , its probability is always 1, which is not depicted in the figure.

0.25

0.50

0.75

20

10

0.

Finally, Fig. 2c depicts the energy consumption, normalized by the result of BestEnergy. It does not include the energy cost of heuristic MaxSpeed, which is 215 times larger than BestEnergy. Closer, Threshold and BestTrade are very close to each other in this set of simulations, so some of them are overlapped. DuplicateAll consumes significantly more energy than the other heuristics. Overall, Fig. 2 shows that **BestTrade** is the best heuristic for these applications: it allows us to always meet both the expected period bound and the probability bound, and it offers similar energy performance as other heuristics. Threshold and Closer are also good options, however they often exceed the probability bound.

2) Real applications: Fig. 3 shows the performance of the heuristics on real applications, as a function of  $\kappa$ . In Fig. 3a, the dashed line represents the average period bound. Best-Trade, DuplicateAll, Closer and Threshold give very similar results and thus overlap. All heuristics except BestEnergy meet the period target. For probability bound, as shown in Fig. 3b, only **BestTrade** always meets the target. **DuplicateAll** and **MaxSpeed** both give a probability of 0 as before. **Closer** and **Threshold** sometimes exceed the target probability by a large factor. Finally, Fig. 3c shows the energy required by each heuristic. In this setting, **BestTrade** is the most energy saving heuristic, closely followed by **Closer**. **Threshold** requires more energy, and **DuplicateAll** even more. Not surprisingly, **MaxSpeed** is the heuristic that costs the most energy, around 254 times larger than **BestEnergy** (so it is not included in Fig. 3c). This shows that **BestTrade** is also the best choice for real applications.

### VII. CONCLUSIONS

In this paper, we have studied the problem of optimizing the energy consumption of linear chain applications on MPSoCs, which have both reliability and performance constraints. We proposed a new model that allows us to select the frequency of the cores for different tasks and to duplicate some tasks. It takes into account the expected period, the probability of exceeding the period and the energy efficiency. We proved that minimizing the energy consumption is easy without performance and reliability constraints, but that the problem becomes NP-complete when adding these constraints and when considering a discrete set of possible speeds. We then proposed several heuristics for choosing the tasks' processing speed and which tasks to duplicate. One of the proposed heuristics, BestTrade, is able to meet the bounds on the expected period and on the probability of exceeding the target period, while reducing the energy consumption.

Future work will target more complex allocation schemes, in which several tasks may be mapped onto the same core, and more complex task graphs than linear chains (i.e., general directed acyclic graphs). Based on the present results, we expect the problems to become even more complex, but we believe that it will be possible to reuse some ideas derived from the study of linear chains.

### ACKNOWLEDGMENT

This work is supported by the National Natural Science Foundation of China (NSFC) under Grant No.61872147.

# REFERENCES

- [1] G. P. Fettweis, "The tactile internet: Applications and challenges," *IEEE Vehicular Technology Magazine*, vol. 9, pp. 64–70, 2014.

- [2] G. Blake, R. G. Dreslinski, and T. Mudge, "A survey of multicore processors," *IEEE Signal Processing Magazine*, vol. 26, pp. 26–37, November 2009.

- [3] W. Wolf, A. A. Jerraya, and G. Martin, "Multiprocessor System-on-Chip (MPSoC) Technology," *IEEE Trans. on Computer-Aided Design* of Integrated Circuits and Systems, vol. 27, no. 10, pp. 1701–1713, 2008.

- [4] G. Chen, K. Huang, and A. Knoll, "Energy Optimization for Realtime Multiprocessor System-on-chip with Optimal DVFS and DPM Combination," ACM Trans. on Embedded Computing Systems, vol. 13, pp. 111:1–111:21, 2014.

- [5] B. Zhao, H. Aydin, and D. Zhu, "Generalized reliability-oriented energy management for real-time embedded applications," in *Proc. of Design Automation Conference (DAC)*, pp. 381–386, 2011.

- [6] M. A. Haque, H. Aydin, and D. Zhu, "On reliability management of energy-aware real-time systems through task replication," *IEEE Trans.* on Parallel and Distributed Systems, vol. 28, no. 3, pp. 813–825, 2017.

- [7] J. Spasic, D. Liu, and T. Stefanov, "Energy-efficient mapping of realtime applications on heterogeneous MPSoCs using task replication," in Proc. of Int. Conf. on Hardware/Software Codesign and System Synthesis (CODES+ISSS), Oct 2016.

- [8] K. Huang, W. Haid, L. Bacivarov, M. Keller, and L. Thiele, "Embedding Formal Performance Analysis into the Design Cycle of MPSoCs for Real-time Streaming Applications," ACM Trans. on Embedded Computing Systems, vol. 11, pp. 8:1–8:23, 2012.

- [9] D. Truong, W. Cheng, T. Mohsenin, and et al., "A 167-processor 65 nm computational platform with per-processor dynamic supply voltage and dynamic clock frequency scaling," in *Proc. of IEEE Symposium on VLSI Circuits*, pp. 22–23, 2008.

- [10] S. Zhang, J. Wu, and S. Lu, "Distributed workload dissemination for makespan minimization in disruption tolerant networks," *IEEE Trans*actions on Mobile Computing, vol. 15, pp. 1661–1673, 2016.

- [11] K. Li, X. Tang, and K. Li, "Energy-efficient stochastic task scheduling on heterogeneous computing systems," *IEEE Trans. on Parallel and Distributed Systems*, vol. 25, no. 11, pp. 2867–2876, 2014.

- [12] W. Zheng and R. Sakellariou, "Stochastic DAG scheduling using a Monte Carlo approach," *Journal of Parallel and Distributed Computing*, vol. 73, no. 12, pp. 1673 – 1689, 2013.

- [13] S. Albers and M. Hellwig, "Online makespan minimization with parallel schedules," *Algorithmica*, vol. 78, pp. 492–520, 2017.

- [14] P. Marwedel, J. Teich, G. Kouveli, L. Bacivarov, L. Thiele, and et al, "Mapping of Applications to MPSoCs," in *Proc. of Int. Conf. on Hardware/Software Codesign and System Synthesis (CODES+ISSS)*, pp. 109–118, 2011.

- [15] J. J. Dongarra, E. Jeannot, E. Saule, and Z. Shi, "Bi-objective scheduling algorithms for optimizing makespan and reliability on heterogeneous systems," in *Proc. of ACM Symposium on Parallel Algorithms and Architectures*, pp. 280–288, 2007.

- [16] S. Wang, K. Li, J. Mei, G. Xiao, and K. Li, "A reliability-aware task scheduling algorithm based on replication on heterogeneous computing systems," *Journal of Grid Computing*, vol. 15, pp. 23–39, Mar 2017.

- [17] L. Zhang, K. Li, C. Li, and K. Li, "Bi-objective workflow scheduling of the energy consumption and reliability in heterogeneous computing systems," *Information Sciences*, vol. 379, pp. 241–256, 2017.

- [18] A. Das, A. Kumar, B. Veeravalli, C. Bolchini, and A. Miele, "Combined DVFS and Mapping Exploration for Lifetime and Soft-error Susceptibility Improvement in MPSoCs," in *Proc. of Design, Automation & Test* in Europe (DATE), pp. 61:1–61:6, 2014.

- [19] G. Xie, Y. Chen, X. Xiao, C. Xu, R. Li, and K. Li, "Energy-efficient fault-tolerant scheduling of reliable parallel applications on heterogeneous distributed embedded systems," *IEEE Transactions on Sustainable Computing*, pp. 1–1, 2017.

- [20] J. Hu and R. Marculescu, "Energy- and performance-aware mapping for regular NoC architectures," *IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems*, vol. 24, no. 4, pp. 551–562, 2005.

- [21] B. Bohnenstiehl, A. Stillmaker, J. Pimentel, and al., "Kilocore: A fine-grained 1,000-processor array for task-parallel applications," *IEEE Micro*, vol. 37, pp. 63–69, 2017.

- [22] D. Zhu, "Reliability-aware dynamic energy management in dependable embedded real-time systems," ACM Trans. on Embedded Computing Systems, vol. 10, pp. 26:1–26:27, 2011.

- [23] I. Assayad, A. Girault, and H. Kalla, "Tradeoff exploration between reliability, power consumption, and execution time for embedded systems," *International Journal on Software Tools for Technology Transfer*, vol. 15, pp. 229–245, 2013.

- [24] M. A. Haque, H. Aydin, and D. Zhu, "On reliability management of energy-aware real-time systems through task replication," *IEEE Transactions on Parallel and Distributed Systems*, vol. 28, pp. 813–825, March 2017.

- [25] H. Aydin and Q. Yang, "Energy-aware partitioning for multiprocessor real-time systems," in *Proc. of Int. Parallel and Distributed Processing* Symp. (IPDPS), 2003.

- [26] C. Gou, A. Benoit, M. Chen, L. Marchal, and T. Wei, "Reliability-aware energy optimization for throughput-constrained MPSoC applications," Research Report RR-9168, INRIA, Apr. 2018. Available at hal.inria.fr.

- [27] M. R. Garey and D. S. Johnson, Computers and Intractability; A Guide to the Theory of NP-Completeness. New York, USA: W. H. Freeman & Co., 1990.

- [28] W. Thies, Language and Compiler Support for Stream Programs. PhD thesis, MIT, Cambridge, MA, USA, 2009.