# ERPOT: A quad-criteria scheduling heuristic to optimize the execution time, failure rate, power consumption and temperature in multicores

Athena Abdi, Alain Girault, Hamid Zarandi

# ▶ To cite this version:

Athena Abdi, Alain Girault, Hamid Zarandi. ERPOT: A quad-criteria scheduling heuristic to optimize the execution time, failure rate, power consumption and temperature in multicores. [Research Report] RR-9196, Inria; 37. 2019, pp.1-37. hal-01848087v2

# HAL Id: hal-01848087 https://inria.hal.science/hal-01848087v2

Submitted on 5 Mar 2019  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# ERPOT: A quad-criteria scheduling heuristic to optimize the execution time, failure rate, power consumption and temperature in multicores

ABDI Athena, GIRAULT Alain, ZARANDI Hamid

RESEARCH REPORT N° 9196-v2 March 2019 Project-Teams Spades

# ERPOT: A quad-criteria scheduling heuristic to optimize the execution time, failure rate, power consumption and temperature in multicores

Abdi Athena\*, Girault Alain<sup>†</sup>, Zarandi Hamid<sup>‡</sup>

Project-Teams Spades

Research Report n° 9196-v<br/>2 — March 2019 — 37 pages

Version 2.

$^\dagger$  Univ. Grenoble Alpes, Inria, CNRS, Grenoble INP, LIG, 38000 Grenoble, France.

<sup>‡</sup> Department of Computer Engineering and Information Technology, Amirkabir University of Technology (Tehran Polytechnic), Tehran, Iran.

Inovallée 655 avenue de l'Europe Montbonnot 38334 Saint Ismier Cedex

<sup>\*</sup> Department of Computer Engineering and Information Technology, Amirkabir University of Technology (Tehran Polytechnic), Tehran, Iran.

Abstract: We investigate multi-criteria optimization and Pareto front generation. Given an application modeled as a Directed Acyclic Graph (DAG) of tasks and a multicore architecture, we produce a set of non-dominated (in the Pareto sense) static schedules of this DAG onto this multicore. The criteria we address are the execution time, reliability, power consumption, and peak temperature. These criteria exhibit complex antagonistic relations, which make the problem challenging. For instance, improving the reliability requires adding some redundancy in the schedule, which penalizes the execution time. To produce Pareto fronts in this 4-dimension space, we transform three of the four criteria into constraints (the reliability, the power consumption, and the peak temperature), and we minimize the fourth one (the execution time of the schedule) under these three constraints. By varying the thresholds used for the three constraints, we are able to produce a Pareto front of non-dominated solutions. We propose two algorithms to compute static schedules. The first is a ready list scheduling heuristic called ERPOT (Execution time, Reliability, POwer consumption and Temperature). ERPOT actively replicates the tasks to increase the reliability, uses Dynamic Voltage and Frequency Scaling to decrease the power consumption, and inserts cooling times to control the peak temperature. The second algorithm uses an Integer Linear Programming (ILP) program to compute an optimal schedule. However, because our multicriteria scheduling problem is NP-complete, the ILP algorithm is limited to very small problem instances. Comparisons showed that the schedules produced by ERPOT are on average only 10%worse than the optimal schedules computed by the ILP program, and that ERPOT outperforms the PowerPerf-PET heuristic from the literature on average by 33%.

**Key-words:** Multicore static scheduling, reliability, failure rate, power consumption, temperature, multi-objective optimization, Pareto front.

# ERPOT: Une heuristique d'ordonnancement quadri-critère pour optimiser le temps d'exécution, le taux de défaillance, la puissance électrique et la température sur les multi-cœurs

Résumé : Nous nous attaquons à l'optimisation multi-critères et à la génération de fronts de Pareto. Etant données une application modélisée sous la forme d'un graphe orienté sans cycle (DAG) de tâches et une architecture multi-cœurs, nous calculons un ensemble d'ordonnancements statiques non dominés (au sens de Pareto) de ce DAG sur ce multi-cœurs. Les critères que nous considérons sont le temps d'exécution, la fiabilité, la puissance électrique et la température de crête. Ces critères présentent des relations complexes d'antagonisme, ce qui fait de notre problème d'ordonnancement un vrai défi. Par exemple, améliorer la fiabilité requiert d'ajouter de la redondance dans l'ordonnancement, ce qui pénalise le temps d'exécution. Afin de produire des fronts de Pareto dans cet espace à quatre dimensions, nous transformons trois de ces quatre critères en contraintes (la fiabilité, la puissance électrique et la température de crête) et nous minimisons le quatrième (le temps d'exécution) sous ces trois contraintes. En faisant varier les seuils utilisés pour les trois contraintes, nous sommes capables de produire un front de Pareto de solutions non-dominées. Nous proposons deux algorithmes pour calculer des ordonnancements statiques. Le premier est une heuristique de liste appelé ERPOT (Execution time, failure Rate, POwer consumption and Temperature). ERPOT réplique activement la tâches pour améliorer la fiabilité, utilise l'Ajustement Dynamique de la Fréquence et de la Tension (ADFT) pour réduire la puissance électrique, et insère des intervalles d'inactivité pour contrôler la température de crête. Le second algorithme repose sur un Programme Linéaire en Nombres Entiers (PLNE) pour construire un ordonnancement optimal. Toutefois, dans la mesure où notre problème d'ordonnancement multi-critères est NP-complet, l'algorithme PLNE est limité à des instances de très petite taille. Les comparaisons montrent que les ordonnancements produits par ERPOT sont en moyenne 10%moins bons que les ordonnancements optimaux calculés par l'algorithme PNLE, et que ERPOT améliore en moyenne de 33% les ordonnancements produit par l'heuristique PowerPerf-PET de la littérature.

**Mots-clés :** Ordonnancement statique, multi-cœurs, fiabilité, taux de défaillance, température, puissance électrique, optimisation multi-critères, front de Pareto.

## Contents

| 1                                                                     | Introduction                                                  | 4             |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------|---------------------------------------------------------------|---------------|--|--|--|--|--|--|--|

| <b>2</b>                                                              | Pareto optimization                                           | 6             |  |  |  |  |  |  |  |

| 3                                                                     | System model<br>3.1 Application and architecture models       | <b>9</b><br>9 |  |  |  |  |  |  |  |

|                                                                       | 3.2 Static mapping and scheduling                             | 10            |  |  |  |  |  |  |  |

|                                                                       | 3.3 Reliability                                               | 10            |  |  |  |  |  |  |  |

|                                                                       | 3.4       Power consumption         3.5       Temperature     | 13<br>14      |  |  |  |  |  |  |  |

| 4 ERPOT: The Proposed Quad-Criteria Optimization Scheduling Heuristic |                                                               |               |  |  |  |  |  |  |  |

|                                                                       | 4.1 General principles of ERPOT                               | 16            |  |  |  |  |  |  |  |

|                                                                       | 4.2 Quad-criteria scheduling heuristic algorithm              | 18            |  |  |  |  |  |  |  |

|                                                                       | 4.3 Soundness of our scheduling heuristic                     | 19            |  |  |  |  |  |  |  |

|                                                                       | 4.4 Dealing with reactive systems                             | 20            |  |  |  |  |  |  |  |

|                                                                       | 4.5 Taking into account the temperature of the adjacent cores | 22            |  |  |  |  |  |  |  |

|                                                                       | 4.6 Integer Linear Program                                    | 23            |  |  |  |  |  |  |  |

| <b>5</b>                                                              | Simulation results                                            |               |  |  |  |  |  |  |  |

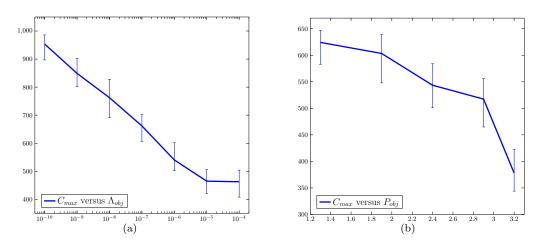

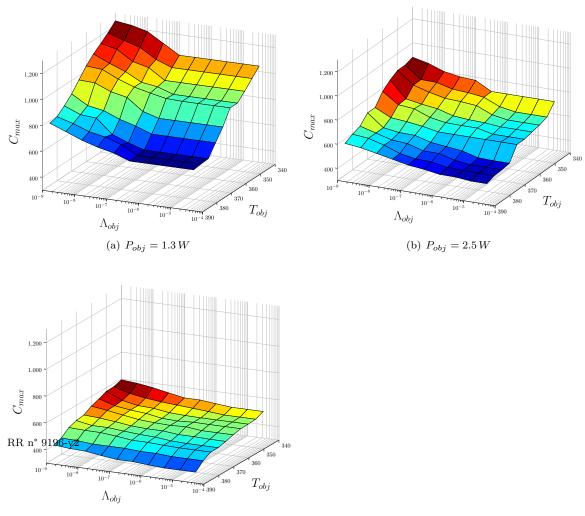

|                                                                       | 5.1 Influence of the constraints on the schedules             | 26            |  |  |  |  |  |  |  |

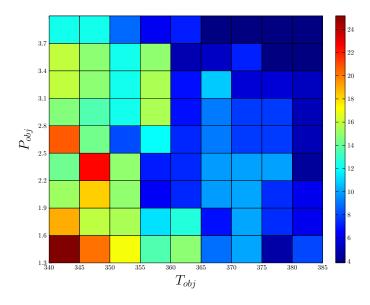

|                                                                       | 5.2 Pareto fronts obtained with ERPOT                         | 27            |  |  |  |  |  |  |  |

|                                                                       | 5.3 Comparison with PowerPerf-PET                             | 30            |  |  |  |  |  |  |  |

|                                                                       | 5.4 Evaluation of the ILP model                               | 31            |  |  |  |  |  |  |  |

| 6 Related work                                                        |                                                               |               |  |  |  |  |  |  |  |

| 7                                                                     | Conclusion                                                    |               |  |  |  |  |  |  |  |

#### Introduction 1

Multicores are widely used in modern safety critical embedded systems design. Their advantages over super-scalar processor architectures are lower power consumption, higher performance, and lower design complexity [1]. When designing safety critical applications, many non-functional criteria must be addressed. The most important ones are the total execution time (because these systems must react to inputs within a fixed delay), the *reliability* (because failures could have fatal consequences), the *power consumption* (to maximize the autonomy of the system when it operates on a battery), and the *temperature* (because of its negative influence on processing speed, reliability, and power consumption) [1, 2, 3, 4]. There are many real-life applications that motivate our study, including satellite systems, portable medical devices, and full authority digital engine control (FADEC) in aircraft.

Considering these four criteria simultaneously during the design phase is very difficult because they are *antagonistic* [5, 1, 6, 2, 7, 4, 8, 9]. For instance, the total execution time and reliability are antagonistic because increasing the reliability requires some form of redundancy (be it spatial or temporal), which negatively impacts the execution time. Similarly, the execution time and the temperature are antagonistic because adding idle times to cool the cores obviously has a negative impact on the execution time. Finally, the execution time and the power consumption are antagonistic because reducing the power consumption requires lowering the operating voltage and frequency of the cores, which increases the execution time. Those tradeoffs are easy to grasp (but difficult to address), but other tradeoffs are less obvious: for instance, lowering the operating voltage and frequency of a core (which lowers the power consumption) increases the nominal failure rate per time unit of this core. The reason is that the sensitivity of processors to energy particles leads to an increase of the failure rate at low voltage/frequency operating points [10, 11], because lowering the voltage decreases the critical charge of the circuit. As a consequence, the power consumption and the reliability are also antagonistic. Failing to take into account these antagonisms could result in bad design choices.

These antagonisms call for the computation of as many tradeoffs as possible, rather than a single tradeoff, so that the user will have a choice. We must therefore produce a *set* of solutions in the 4-dimensions space (execution time, reliability, power consumption, temperature). We rely on the notion of *Pareto dominance*, and we use a variant of the  $\varepsilon$ -constraint method [12, 13] coupled with a scheduling algorithm that accounts for the four criteria to produce the *Pareto front* in this 4D space. More precisely, we transform three criteria into *constraints* (the reliability, the power consumption, and the peak temperature), and we *minimize* the fourth one (the execution time of the schedule) under these three constraints.

Although several studies have addressed some of these parameters, none have considered these four criteria jointly in an optimization problem. For instance, some studies completely ignore the reliability [14, 4] or the temperature [2, 9]. Other studies tackle the problem as a hardware/software co-design problem, jointly optimizing the floorplan of the multicore and the schedule of the application task graph to minimize the peak temperature [14], but without considering the reliability.

We therefore propose a static scheduling heuristic method called ERPOT, an acronym that stands for Execution time, Reliability, POwer consumption and Temperature. Given an application modeled as a Directed Acyclic Graph (DAG) of tasks, a multicore architecture, and thresholds on the reliability, the power consumption, and the temperature, ERPOT generates a static schedule of this DAG onto this multicore such that each constraint is below its corresponding threshold, and such that the execution time is as small as possible. Each schedule is interpreted as a point in the 4D space (execution time, reliability, power consumption, temperature). By varying the values of the thresholds and calling iteratively ERPOT, we are able to produce a full Pareto front in this 4D space.

The problem of scheduling a DAG of tasks onto a distributed architecture is known to be NP-complete [15], and so is the multi-criteria scheduling problem, which motivates the design of a heuristic algorithm. Additionally, we present an ILP program of the optimization problem, which is used to validate ERPOT (i.e., both algorithms produce the same schedule on the same problem instance) and to assess experimentally how good ERPOT is. Comparing the results of ERPOT with the optimal results obtained by the ILP program shows that the average difference is less than 10%. However, ERPOT is much faster than the ILP program, which fails to complete even for application graphs of relatively small sizes (8 tasks at most).

The key contributions of this paper are:

- The ERPOT quad criteria scheduling heuristic, which optimizes the *execution time*, the *reliability*, the *power consumption*, and the *temperature*.

- A 4D variant of the  $\varepsilon$ -constraint method [12] to build the Pareto front of the solutions in the 4D space (execution time, reliability, power, temperature).

- An ILP program of the quad criteria optimization problem to compare the solution computed by ERPOT with the optimal solution.

ERPOT extends the heuristics proposed in [2] by taking into account the peak temperature. The first challenge of doing so lies in the intricate dependence of the temperature on the other criteria of [2], namely the failure rate, the power consumption, and the execution time. The second challenge is in the scheduling heuristic itself: each scheduling decision is made by "predicting" what will be the value of the temperature, power consumption, and failure rate at the end of the task being scheduled. However, the temperature varies during the execution of the task, because it obeys the classical thermal differential equation. Since the power consumption (and similarly the failure rate) depends on the temperature, the computation of the power consumption is inexact unless it is performed continuously during the execution of the task being scheduled, which is much too expensive. Addressing this challenge requires an over-approximation of the temperature and the proof that this is safe for the power-consumption constraint. This was not the case when only the power consumption and the failure rate were considered, making the scheduling heuristic of [2] much simpler. The third challenge resides in maintaining the peak temperature below a given threshold, which involves a combination of lowering the voltage/frequency (thanks to DVFS), inserting cooling intervals, and over-estimating the temperature when there are "holes" at the end of schedule under construction. A final contribution compared to [2] is that The ILP program of [2] does not consider the cost of the communications, while the ILP program of Section 4.6, so the comparison performed in Section 5.4 is more relevant than the one presented in [2].

The rest of this paper is organized as follows. Section 2 recalls the basics about Pareto dominance and how to compute the Pareto front with the  $\varepsilon$ -constraint method. Section 3 provides the required preliminaries including the application and architecture models and the interplay between the reliability, the power consumption, the temperature, and the execution time. Section 4 provides the proposed scheduling heuristic ERPOT, along with its ILP counterpart. Section 5 presents the results of our simulations, performed both with syntactic benchmarks and with reallife benchmarks. Finally, Section 6 surveys the related work and Section 7 gives some concluding remarks.

# 2 Pareto optimization

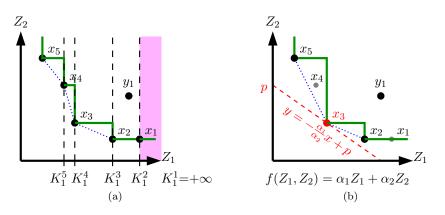

Before detailing our problem formulation, solutions, and algorithms, we give foundational background on Pareto optimization. When optimizing more than one criterion, there can be *several non-comparable* solutions, e.g., (42, 13) versus (9, 78) in the case of two criteria that must be minimized. The principle of Pareto optimization is to explore the design space by providing *as many solutions as possible*, to study the tradeoffs between these solutions. To compare solutions, we rely on the notion of *dominance* and Pareto optima, presented below in the case of two criteria that must be minimized (see Fig. 1(a)):

- The point (x, y) weakly dominates the point (x', y') iff  $(x < x' \land y = y') \lor (x = x' \land y < y')$ . E.g.,  $x_2$  weakly dominates  $x_1$ .

- The point (x, y) strongly dominates the point (x', y') iff  $(x < x' \land y < y')$ . E.g.,  $x_3$  strongly dominates  $y_1$ .

- A point is a *weak Pareto optimum* iff there does not exist another point that strongly dominates it. E.g.,  $x_1, ..., x_5$  are weak Pareto optima.

- A point is a strong Pareto optimum iff there does not exist another point that dominates it (weakly or strongly). E.g.,  $x_2$ , ...,  $x_5$  are strong Pareto optima.

- The Pareto front is the set of all weak and strong Pareto optima.

Figure 1: Two transformation methods to compute the Pareto front (2D case): (a)  $\varepsilon$ -constraint method; (b) aggregation method.

Building the whole Pareto front and considering all constraints in a multi-criteria problem is a complicated task. To do this, several approaches exist [16], including the *aggregation* method that combines all the criteria in a single cost function, the *hierarchization* method that optimizes one criteria at a time, and the *transformation* method that transforms all the criteria except one into thresholds, and optimizes the remaining criterion under the constraints that the thresholds are satisfied (this last method is also called "budget optimization"). It is also possible to use population based methods, (e.g., genetic algorithms, particle swarm, ant colony, ...) or the Normal-Boundary Intersection method (NBI) [17].

Varying the cost function in the aggregation method or varying the order of the criteria in the hierarchization method can lead to computing several Pareto points, but not the entire Pareto front, a major theoretical drawback. The aggregation method is illustrated in Fig. 1(b) where the aggregation function is  $f(Z_1, Z_2) = \alpha_1 Z_1 + \alpha_2 Z_2$ . For two given values of  $\alpha_1$  and  $\alpha_2$ , the Pareto point that is found is the one that minimizes f: geometrically, it is the point from the Pareto front intersecting the line of slope  $-\alpha_1/\alpha_2$  and having the smallest value at origin (the p in Fig. 1(b)). The problem is that the concave portions of the Pareto front will be missed, e.g., the  $x_4$  point in Fig. 1(b); more generally, this is always the case if the aggregation function is convex (which is the case of f). However, if the aggregation function is not convex, then there is no guarantee that the computed points are on the Pareto front. For instance, a non-convex aggregation function could return the point  $y_1$ .

Overall, the transformation method is an effective method to build the entire Pareto front when used in an iterative way. With two criteria, this is known as the  $\varepsilon$ -Constraint Method ( $\varepsilon$ CM) [12], depicted in Fig. 1(a). The criterion  $Z_1$  is transformed into a constraint. At iteration 1, the threshold for  $Z_1$  is set to  $K_1^1 = +\infty$ , yielding the Pareto optimum  $x_1$ . At iteration 2, the threshold  $K_1^2$  is set to the horizontal coordinate of  $x_1$ , therefore excluding the portion of the plane that is emphasized (in pink) and yielding the Pareto optimum  $x_2$ . This process repeats until all the points of the Pareto front have been found (if there is finite number of them), or until some pre-decided number of Pareto point have been found. Under the two conditions that (i) the number of Pareto optima is *finite* and that (ii) the minimization algorithm for  $Z_2$  computes the *optimal* result,  $\varepsilon$ CM computes the entire optimal Pareto front.

$\varepsilon$ CM has been later generalized to more than two criteria in [13], but at a very high computational cost:  $k^{m-1}\mathcal{O}(opt)$ , where k is the number of points in the Pareto front, m is the number of criteria, and  $\mathcal{O}(opt)$  is the complexity of the single criterion optimization algorithm. This computational complexity makes the generalized  $\varepsilon$ CM unfeasible for our problem (if only for the reason that the number of Pareto points is not bounded).

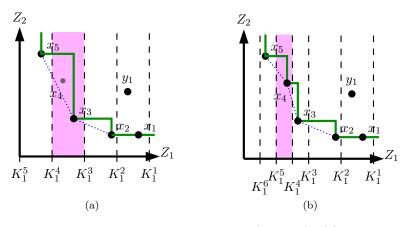

Instead, for each of the m-1 criteria turned into a constraint, we simply divide the useful range of this criterion into p equally spaced intervals, and we invoke a single criterion optimization algorithm in each of the resulting  $p^{m-1}$  zones of the search space. We call this the Grid Method, depicted in Fig. 2(a) where the  $Z_1$  axis is divided into 4 intervals,  $[K_1^5, K_1^4)$  to  $[K_1^2, K_1^1)$ . The resulting complexity therefore becomes  $p^{m-1}\mathcal{O}(opt)$ . This is still exponential in m-1 but the number of intervals p is much less than the number of Pareo points k. The number of intervals can be identical for each of the m-1 criteria or not: each range can thus be divided into  $p_i$  intervals (not even necessarily equally spaced), resulting in an overall complexity of  $(\prod_{i=1}^{m-1} p_i)\mathcal{O}(opt)$ .

Figure 2: The grid method to compute the Pareto front (2D case): (a) with a coarse regular grid; (b) with an irregular grid.

The choice of the intervals in each dimension has obviously an impact on the resulting Pareto front. For instance, the grid method illustrated in Fig 2(a) builds a Pareto front that does not include the point  $x_4$  because, in the interval  $[K_1^4, K_1^3)$  (emphasized in pink), the point that minimizes  $Z_2$  is  $x_3$ . With a different grid, the point  $x_4$  could be obtained, as shown in Fig. 2(b). On the one hand, using a finer grid will produce a Pareto front with more points, but this can become too costly. On the other hand, using an irregular grid could find more Pareto points but this seems very difficult to control a priori. It is simpler to generate the Pareto front with evenly spaced intervals in each dimension (the number of intervals depending on the time one is ready to spend to compute the Pareto front) and then, in order to improve locally the Pareto front around a particular Pareto optimum, to use either local search methods or to refine the intervals locally around this Pareto optimum. For instance, in Fig. 1, if  $x_3$  is identified as an interesting compromise, then the user can either use a local search algorithm around  $x_3$ , or he/she can divide the  $[K_1^4, K_1^3)$  interval into smaller intervals and invoke again the  $Z_2$  minimization function in these smaller intervals, which will be very likely to find the Pareto optimum  $x_4$ .

To summarize, we use Algorithm 1 to implement the grid method, in the particular case of 2 criteria as in Fig. 2(b). The function  $OPT(K_1^i)$  returns the Pareto point that minimizes  $Z_2$  under the constraint  $Z_1 < K_1^i$ . The function REMOVENONDOMINATEDPOINTS(*Res*) removes the non dominated points from the list *Res* to produce the Pareto front.

As a final remark, note that in Fig. 1 and in Fig. 2, the Pareto front is depicted as a solid green line. It delimits the portion of the plane (above it and on its right) where all the points are dominated by a known Pareto optimum. This differs from the broken line that connects the Pareto optima (depicted in dotted blue), as is demonstrated by Fig. 1(b): the point  $x_4$  is above the dotted blue line, and yet we do not know whether or not is represents a feasible compromise

```

Algorithm 1 Grid method algorithm for 2 criteria.

input: The range [K_1^{min}, K_1^{max}] and the decrement \Delta

output: The list of Pareto points Res

1: function \operatorname{GRID}(K_1^{min}, K_1^{max}, \Delta)

Res \leftarrow \emptyset; K_i^1 \leftarrow K_1^{max}; i \leftarrow 1

2:

while K_1^i \ge K_i^{min} do

3:

4:

Res \leftarrow Res \cup OPT(K_1^i)

K_1^i \leftarrow K_1^i - \Delta

5:

end while

6:

return REMOVENONDOMINATEDPOINTS(Res)

7:

8: end function

```

between  $Z_1$  and  $Z_2$ , because no Pareto optimum has been found that dominates  $x_4$ .

## 3 System model

#### 3.1 Application and architecture models

An application is modeled as a directed acyclic graph (DAG)  $\mathcal{A}lg = (\mathcal{V}, \mathcal{E})$ , where  $\mathcal{V}$  is the set of nodes and  $\mathcal{E}$  is the set of edges. Each node represents a computing task, and each edge represents data-dependencies among two tasks. All tasks are assumed to be side-effect free (this assumption is required for active replication). If  $X \to Y$  is a data-dependency, then X is predecessor of Y and Y is successor of X. X is called the source of the data-dependency and Y is called its destination. We also define the sets  $pred(X) = \{Y | (Y, X) \in \mathcal{E}\}$  and  $succ(X) = \{Y | (X, Y) \in \mathcal{E}\}$ . Tasks with no predecessor are called *input* tasks, and those with no successors are called *output* tasks.

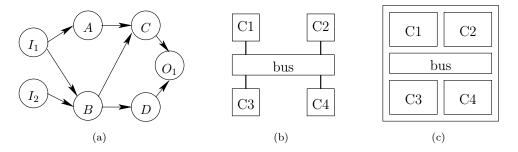

Fig. 3(a) shows an example of a DAG with two input tasks  $(I_1 \text{ and } I_2)$ , one output task  $(O_1)$  and four regular tasks (A, B, C and D).

Figure 3: (a) A sample application graph. (b) A sample architecture graph. (c) The corresponding coarse grain floorplan.

An architecture is a possibly heterogeneous multicore chip with one or more communication buses. It is modeled as a graph  $\mathcal{A}rc = (\mathcal{C}, \mathcal{B}, \mathcal{L})$ , where  $\mathcal{C}$  is the set of cores,  $\mathcal{B}$  is the set of communication buses, and each  $e \in \mathcal{L}$  is a pair  $(c, b) \in \mathcal{C} \times \mathcal{B}$  specifying that the core c is connected to the bus b. We assume that there exists a path between any two cores c and c'. An example of a target architecture made of four cores and one bus is shown in Fig. 3(b).

We are also given a function  $\mathcal{E}xe_{nom}$  that returns the nominal (corresponding to the highest frequency) worst case execution times (WCETs) of all the tasks of  $\mathcal{A}lg$  onto all the cores of  $\mathcal{A}rc$ ,

as well as the worst case communication times (WCCTs) of all the data-dependencies of  $\mathcal{A}lg$  onto all the communication buses of  $\mathcal{A}rc$ . An intra-core communication takes no time to execute. For the sake of simplicity, all execution times are assumed to be integer numbers.

Computing the WCET of a given task on a processor has been the topic of much work. It involves finding the sequence of instructions in the program of the task that leads to the longest execution time. This is achieved by extracting the control flow graph (CFG) of the program, then by giving a duration (i.e., a number of clock cycles) to each basic block of the CFG. These durations are computed based on a model of the micro-architecture of the processor. This steps includes some pessimism because of the hardware abstraction, be it in the cache replacement policy, the pipeline, the branch predictor, or the prefetch buffer. Based on this, the WCET is the length of the most weighted path in the annotated CFG. In general, the CFG contains backward edges, corresponding to the loops of the program. In this case, it is necessary to analyze the program in order to bound the number of iterations of each loop, which is classically done with abstract interpretation [18].

WCET analysis has been applied with success to real-life single-core processors actually used in embedded systems, with branch prediction [19] or with caches and pipelines [20]. These methods have later been adapted to multicores [21, 22, 23], taking into account the shared resources in the multicore (e.g., the shared memory or the bus).

Finally, the multicore is equipped with per-core DVFS. For each core, a set of (voltage, frequency) pairs  $\{(V_i, f_i)\}_{1 \le i \le \ell}$  is given. For the sake of simplicity, we assume that all the cores have the same set of (voltage, frequency) pairs. The actual execution time of a task  $\tau$  on a core c depends on the frequency f (in contrast, the buses are assumed to run at a fixed frequency denoted  $f_b$ ). To ease the computations, we transform the frequencies into scaling factors. E.g., if the set of available frequencies is  $\{900 \ MHz, 600 \ MHz, 300 \ MHz\}$ , then we use the scaling factors  $\{f_{max} = f_3 = 1, f_2 = \frac{2}{3}, f_{min} = f_1 = \frac{1}{3}\}$ . As a result, the WCET of task  $\tau$  at frequency f is given by:

$$\mathcal{E}xe(\tau, c, f) = \left[\mathcal{E}xe_{nom}(\tau, c)/f\right] \tag{1}$$

where the  $\lceil \cdot \rceil$  function guarantees that  $\mathcal{E}xe$  always returns an integer number.

#### 3.2 Static mapping and scheduling

The specifications of the system consists of Alg, Arc, and  $\mathcal{E}xe_{nom}$ . Implementing such a system involves two steps: First, we must find one or several cores of Arc to execute each task of Alg, and one or several communication buses of Arc for each data-dependency: this is the mapping. During this phase, we take into account (i) the reliability constraint by choosing how many cores must execute each task, (ii) the power consumption constraint by choosing at what frequency/voltage each component (core or bus) should execute each task and data-dependency, and (iii) the temperature constraint by inserting cooling times whenever necessary. Second, we must compute the starting time for each pair (task,proc) and each pair (data dep.,bus): this is the scheduling. This paper solves these two steps statically, i.e., at compile time, based on a ready list scheduling heuristic. Finally, as said in the introduction, we schedule under constraints on the failure rate, the power consumption, and the temperature. We note respectively  $\Lambda_{obj}$ ,  $P_{obj}$ , and  $T_{obj}$  these constraints.

#### 3.3 Reliability

Both the cores and the buses are assumed to be *fail-silent*. Classically, we adopt the failure model of Shatz and Wang [24]: failures are *transient*, and the maximal duration of a failure is

such that it affects only the current task executing onto the faulty core and not the subsequent tasks (same for the buses); this is known as the "hot" failure model.

Since the real-time systems we target are safety critical, the occurrence of failures is not acceptable and their reliability must be as close as possible to 1. One of the main causes of system failure are *transient failures* [25], which are commonly modeled by a Poisson distribution with a constant rate denoted  $\lambda$  [26]. Accordingly, the reliability of a single task or data-dependency  $\tau$  mapped onto a hardware component c (either a core or a bus) running at frequency f is:

$$R(\tau, c, f) = e^{-\lambda_c \cdot \mathcal{E}xe(\tau, c, f)}$$

(2)

where  $\lambda_c$  is the failure rate per time unit of the hardware component c, and  $\mathcal{E}xe(\tau, c, f)$  is the execution time of  $\tau$  on c at frequency f, computed with Eq. (1). When  $\tau$  is not replicated, we use Eq.(2). When  $\tau$  is actively replicated on a set  $\mathcal{K}$  of k hardware components numbered  $\{c_i\}_{1\leq i\leq k}$ , each of them operating at frequency  $f_{c_i}$ , its reliability is:

$$R(\tau, \mathcal{K}) = 1 - \left(\prod_{i=1}^{k} \left(1 - e^{-\lambda_{c_i} \cdot \mathcal{E}xe(\tau, c_i, f_{c_i})}\right)\right)$$

(3)

However, because of the operating frequency f,  $\lambda$  is not constant anymore but is instead a function of the frequency [10]:

$$\lambda_f = \lambda_0 \cdot \rho_f \quad \text{with} \quad \rho_f = 10^{\frac{b(1-f)}{1-f_{min}}} \tag{4}$$

where  $\lambda_0$  is the nominal failure rate per time unit,  $\rho_f$  is the frequency-dependent factor, b is a strictly positive constant that accounts for the susceptibility of hardware to transient faults due to frequency scaling, f is the operational frequency level, and  $f_{min}$  is the lowest frequency of the system. Recall that the frequency value f is normalized in the range [0, 1] with  $f_{max} = 1$ . This is consistent with Eq (1).

Many articles have studied the impact of the temperature on the rate of transient faults [27, 28, 29]. In addition, there are several mechanisms that lead to permanent failures, most notably electro-migration, negative bias temperature instability, stress migration, time-dependent dielectric breakdown, and thermal cycling [30, 3]. All of these phenomena can be characterized by a failure rate as an exponential function of the temperature. We take into account the effect of the temperature on the failure rate per time unit with the Arrhenius equation [3]:

$$\lambda_T = \lambda_0 \cdot \rho_T \quad \text{with} \quad \rho_T = e^{\frac{-E_a}{K} \cdot \left(\frac{1}{T(t)} - \frac{1}{T_0}\right)} \tag{5}$$

where again  $\lambda_0$  is the nominal failure rate per time unit,  $\rho_T$  is the temperature-related factor,  $E_a$  is the activation energy, K is the Boltzmann's constant, T(t) is the temperature of the system at time t in Kelvin, and  $T_0$  is the initial temperature. Of course, we will also have to take into account the effect of each core's temperature on the other cores (see Section 3.5).

Finally, we combine Eqs (4) and (5) to provide a global equation of the failure rate per time unit as a function of the frequency and the temperature. Since the frequency factor  $\rho_f$  and the temperature factor  $\rho_T$  are both dimension-less, the dimension of  $\lambda_{sys}$  is the same as  $\lambda_0$ , hence  $\lambda_{sys}$  is also a failure rate per time unit:

$$\lambda_{sys} = \lambda_0 \cdot \rho_f \cdot \rho_T = \lambda_0 \cdot 10^{\frac{b(1-f)}{1-f_{min}}} \cdot e^{\frac{-E_a}{K} \left(\frac{1}{T(t)} - \frac{1}{T_0}\right)} \tag{6}$$

When computing the reliability of a given task or data-dependency  $\tau$  on a single hardware component  $c_i$  (resp. a set  $\mathcal{K} = \{c_i\}_{1 \le i \le k}$ ), we therefore use Eq. (2) (resp. Eq. (3)) by replacing

$\lambda_{c_i}$  by  $\lambda_{sys}(c_i)$ :

$$R(\tau, c_i, f_{c_i}, t) = e^{-\lambda_{sys}(c_i) \cdot \mathcal{E}xe(\tau, c_i, f_{c_i})}$$

$$\tag{7}$$

$$R(\tau, \mathcal{K}, t) = 1 - \left(\prod_{i=1}^{k} \left(1 - e^{-\lambda_{sys}(c_i) \cdot \mathcal{E}xe(\tau, c_i, f_{c_i})}\right)\right)$$

(8)

where t is shown to make explicit the dependency of the temperature of  $c_i$  on the time in  $\lambda_{sys}(c_i)$ . In the entire paper, we take the temperature at the *task granularity*, i.e., we assume that T(t) remains constant for the entire duration of  $\tau$ . We will prove at the end of this section that doing so is safe for the  $\Lambda_{obj}$  constraint.

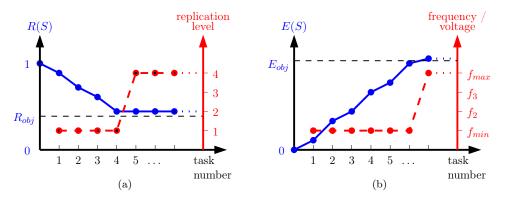

It has been demonstrated in [5, 2] that using the reliability as a constraint in the  $\varepsilon$ -constraint method *does not work*. Intuitively, this is because the reliability is not an invariant measure of the number of scheduled tasks. Indeed, computing the reliability of a schedule involves, at each mapping decision, a multiplication by a factor that is strictly less than 1: see Eq.(3). This is illustrated in Fig. 4(a), where the horizontal axis counts the task numbers in their mapping order (recall that we use a ready list scheduling algorithm). As long as the reliability is above the threshold  $R_{obj}$ , the tasks are not replicated, because this is what minimizes the schedule length; thus the replication level of tasks 1 to 4 is 1 (red dashed line). This results in a multiplicative factor significantly below 1, which causes the system's reliability to drop (blue solid line). Once task 4 has been scheduled, the reliability is very close to  $R_{obj}$ ; this causes the replication level to skyrocket up to a value sufficient for the multiplying factor to be close enough to 1, so that the system's reliability remains above  $R_{obj}$ . We call this the "funnel effect" [2].

Figure 4: Funnel effect: (a) when using the reliability, (b) when using the energy.

For this reason, instead of the reliability, we use the *Global System Failure Rate* (GSFR) [5]. Intuitively, the GSFR of a possibly partial schedule is the failure rate of the system operating under this schedule *as if* it was a single task mapped on a single core. As a consequence, we schedule under a constraint  $\Lambda_{obj}$  on the GSFR instead of a constraint  $R_{obj}$  on the reliability. For a single task  $\tau$ , the GSFR is denoted  $\Lambda(\tau)$  and is computed as:

$$\Lambda(\tau, c, f, t) = \frac{-\log(R(\tau, c, f, t))}{\mathcal{E}xe(\tau, c, f)}$$

(9)

And for a schedule S, the GSFR  $\Lambda(S)$  is computed as:

$$\Lambda(S) = \frac{-\log(R(S))}{U(S)} \quad \text{with} \quad U(S) = \sum_{(\tau,c,f) \in S} \mathcal{E}xe(\tau,c,f) \tag{10}$$

Inria

where R(S) is the reliability of the schedule S and U(S) is the overall sum of the execution times of the cores in S. The notation  $(\tau, c, f) \in S$  means that, in the schedule S, task  $\tau$  is executed on core c at frequency f. Eq.(10) is equivalent to  $R(S) = e^{-\Lambda(S) \cdot U(S)}$ , which is the same as Eq. (2) but for a schedule S instead of a single task  $\tau$ .

One key aspect of Eq. (10) is that it uses U(S) and not the schedule length. There are two reasons behind this choice: first it makes the computation of the GSFR *compositional* with respect to the structure of the schedule, and second it is consistent with the "hot" failure model [5].

The consequence of this shift from the reliability to the GSFR is that, from now on, our state space will be the 4D space (execution time, GSFR, power, temperature).

We are now ready to prove that assuming the temperature on each core  $c_j$  and on the bus b to remain constant during the duration of each task/data-dependency  $\tau$  is safe w.r.t. the  $\Lambda_{obj}$  constraint.

**Proposition 1** Let  $\tau$  be a task or a data-dependency scheduled on a hardware component c at frequency f, starting at time  $t_0$  and finishing at time  $t_f = t_0 + \mathcal{E}xe(\tau, c, f)$ . The reliability of  $\tau$  on c is computed with Eq. (7) and the GSFR with Eq. (9). (i) If the temperature increases over the interval  $[t_0, t_f]$ , then fixing  $T(t) = T(t_f)$  is safe regarding the  $\Lambda_{obj}$  constraint. (ii) If the temperature decreases over the interval  $[t_0, t_f]$ , then fixing  $T(t) = T(t_0)$  is safe regarding the  $\Lambda_{obj}$  constraint.

**Proof:** (i) In the heating mode, the temperature increases during the execution of  $\tau$ , and when it does,  $\lambda_{sys}(c)$  increases too. Since R is decreasing in function of  $\lambda_{sys}$ , we have:

$$\forall t \in [t_0, t_f], R(\tau, c, f, t) \ge R(\tau, c, f, t_f)$$

Since  $R(\tau, c, f, t) \ge R(\tau, c, f, t_f) \iff \Lambda(\tau, c, f, t) \le \Lambda(\tau, c, f, t_f)$ , we therefore have:

$$\Lambda(\tau, c, f, t_f) \leq \Lambda_{obj} \Longrightarrow \forall t \in [t_0, t_f], \Lambda(\tau, c, f, t) \leq \Lambda_{obj}$$

which proves that assuming that T(t) remains constant and equal to  $T(t_f)$  is safe regarding the  $\Lambda_{obj}$  constraint.

(ii) In the cooling mode, the proof is identical since T(t) decreases so  $\lambda_{sys}(t)$  decreases, hence assuming that T(t) remains constant and equal to  $T(t_0)$  is safe regarding the  $\Lambda_{obj}$  constraint.  $\Box$

#### 3.4 Power consumption

The power consumption of a single task (or data-dependency) running on a hardware component is composed of two aspects [10, 31]: (i) the leakage power and (ii) the dynamic power. The former depends on the leakage current, which itself mostly depends on the chip temperature, while the latter depends on the chosen pair (voltage V, frequency f). The overall power consumption  $P_{sys}$ is equal to  $P_{leak} + P_{dyn}$ , computed by Eq. (11):

$$\begin{cases} P_{sys}(t) = \alpha \cdot T(t) + \beta_h + \gamma \cdot C_{ef} \cdot V^2 \cdot f & \text{if heating} \\ P_{sys}(t) = \alpha \cdot T(t) + \beta_c + \gamma \cdot C_{ef} \cdot V^2 \cdot f & \text{if cooling} \end{cases}$$

(11)

Regarding the leakage power,  $\alpha$ ,  $\beta_h$ , and  $\beta_c$  are architecture-dependent coefficients and are determined based on the characteristics of the platform;  $\beta_h$  is used in the heating mode and  $\beta_c$  in the cooling mode [8]. Finally, T(t) is the chip temperature at time t, in Kelvin. Regarding the dynamic power, V is the supply voltage, f is the frequency,  $C_{ef}$  is the switching capacitance (a constant that depends on the chip technology), and  $\gamma$  is the activity ratio, which varies from

0 (no activity) to 1 (all gates are active at each cycle). In theory, there should be a different  $\gamma$  for each task, and our scheduling algorithm can handle it. In practice, for the sake of simplicity we take an average  $\gamma$  value, identical for all the tasks.

Recall that we take the temperature at the *task granularity*, i.e., we assume that T(t) remains constant for the entire duration of  $\tau$ . The following property states that doing this is safe regarding the  $P_{obj}$  constraint.

**Proposition 2** Let  $\tau$  be a task or a data-dependency scheduled on a hardware component c at frequency f, starting at time  $t_0$  and finishing at time  $t_f = t_0 + \mathcal{E}xe(\tau, c, f)$ . The power consumption of c during the execution of  $\tau$  is computed with Eq. (11). (i) If the temperature increases over the interval  $[t_0, t_f]$ , then fixing  $T(t) = T(t_f)$  is safe regarding the  $P_{obj}$  constraint. (ii) If the temperature decreases over the interval  $[t_0, t_f]$ , then fixing  $T(t) = T(t_f)$  is safe regarding the  $P_{obj}$  constraint.

**Proof:** (i) In the heating mode, the temperature increases during the execution of  $\tau$ , and when it does,  $P_{sys}(t)$  increases too. It follows that assuming T(t) to remain constant over the interval  $[t_0, t_f]$  and equal to  $T(t_f)$  yields  $\forall t, P_{sys}(t) \leq P_{sys}(t_f)$ . Therefore, we have:

$$P_{sys}(t_f) \le P_{obj} \Longrightarrow \forall t \in [t_0, t_f], P_{sys}(t) \le P_{obj}$$

which proves that assuming that T(t) remains constant and equal to  $T(t_f)$  is safe regarding the  $P_{obj}$  constraint.

(ii) In the cooling mode, the proof is identical since T(t) decreases so  $P_{sys}(t)$  decreases, hence assuming that T(t) remains constant and equal to  $T(t_0)$  is safe regarding the  $P_{obj}$  constraint.  $\Box$

From Eq. (11), we can then compute the energy consumed by the system when executing a schedule (possibly partial). However, the same funnel effect as with the reliability occurs if one uses the energy as a constraint in the  $\varepsilon$ -constraint method [2]. The reason again is that the energy is not an invariant measure of the number of scheduled tasks. Indeed, computing the energy consumed by a schedule involves, at each mapping decision, an addition of a term that is strictly positive. This is illustrated in Fig. 4(b): the horizontal axis counts the task numbers in their mapping order; the blue solid line depicts the cumulative energy consumed by the system; up to task 6, the energy is below the energy constraint  $E_{obj}$  so everything is fine; however, there is no possibility to schedule task 7 without violating the energy constraint. For this reason, in our multi-criteria scheduling heuristic we use the power consumption, with a constraint  $P_{obj}$ , which is an invariant measure of the number of scheduled tasks.

#### 3.5 Temperature

The instantaneous temperature of a computing system depends on the power consumption and on the current temperature (and its variations in time). For a given hardware component c (core or bus), it is computed based on the following differential equation [32]:

$$C \cdot \left(\frac{dT_c(t)}{dt}\right) + G\left(T_c(t) - T_{amb}\right) = P(t)$$

(12)

where C and G are the architecture-based constants for the heat conductivity,  $T_c$ , t,  $T_{amb}$ , and P are respectively the temperature of c, the time, the ambient temperature (assumed to be less than  $T_{obj}^{1}$ ), and the instantaneous power consumption of the system. The power consumption is the sum of the static and dynamic power, as given by Eq. (11).

<sup>&</sup>lt;sup>1</sup>If  $T_{amb} > T_{obj}$ , then putting the component in the idle mode does not allow it to cool down.

For each component c, we wish to take into account the effect of the temperature of its neighbors, according to the chip floorplan. To achieve this, we add a heat transfer term to Eq. (12):

$$C \cdot \left(\frac{dT_c(t)}{dt}\right) + G\left(T_c(t) - T_{amb}\right) + 2D\_heat = P(t)$$

(13)

and we use the coarse grain floorplan of Fig. 3(c) (similar to the spatial thermal model and floorplan of [33]) to model this two-dimension heat transfer as:

$$2D\_heat = \sum_{c' \in nbr(c)} \kappa(c, c') \cdot \left(T_c(t) - T_{c'}(t)\right)$$

(14)

where nbr(c) is the set of all neighbors of c,  $T_c$  is the temperature of c, and  $\kappa(c, c')$  is the thermal conductivity between c and c', which depends on their distance and on the chip geometry characteristics (as given in the floorplan).

Combining Eqs. (13) and (14) yields the following differential equation for  $T_c(t)$ :

$$C \cdot \left(\frac{dT_c(t)}{dt}\right) = -G \cdot \left(T_c(t) - T_{amb}\right) - \sum_{c' \in nbr(c)} \kappa(c, c') \cdot \left(T_c(t) - T_{c'}(t)\right) + C_{ef} \cdot V^2 \cdot f + \alpha \cdot T_c(t) + \beta_h$$

(15)

We then proceed as in [8] to re-write Eq. (15) as:

$$\frac{dT_c(t)}{dt} = -A \cdot T_c(t) + B, \quad \text{with} \tag{16}$$

$$A = \frac{G - \alpha + \sum_{\substack{c' \in nbr(c) \\ C}} \kappa(c, c')}{C}$$

$$B = \frac{G \cdot T_{amb} + \sum_{\substack{c' \in nbr(c) \\ C}} \kappa(c, c') \cdot T_{c'}(t) + C_{ef} \cdot V^2 \cdot f + \beta_h}{C}$$

When computing the evolution of the temperature of c during the execution of  $\tau$ , we assume that the temperatures of the neighbors remain constant for the entire duration of  $\tau$ , and equal to their respective temperature at the end of  $\tau$ . By virtue of the same reasoning as the one made in Section 3.4, this is safe regarding the  $T_{obj}$  constraint. It follows that the closed form solution to the differential equation (16) is:

$$T_{c}(t) = T_{\infty}^{heat} + (T_{0} - T_{\infty}^{heat}) \cdot e^{-A(t-t_{0})}$$

(17)

where  $T_{\infty}^{heat} = B/A$  is the heating steady state temperature and  $T_0 = T(t_0)$  is the temperature of the system at  $t_0$ . We note  $T_c^{heat}(t_0, t)$  the temperature computed with Eq. (17).

When c is idle, the computation of the temperature is identical except that the term  $C_{ef} \cdot V^2 \cdot f$ in Eq. (11) disappears and  $\beta_h$  is replaced by  $\beta_c$ , yielding the following closed form:

$$B' = \frac{G \cdot T_{amb} + \sum_{c' \in nbr(c)} T_{c'}(t) \cdot \kappa(c, c') + \beta_c}{C}$$

$$T_c(t) = T_{\infty}^{cool} + (T_0 - T_{\infty}^{cool}) \cdot e^{-A(t-t_0)}$$

(18)

where  $T_{\infty}^{cool} = B'/A$  is the cooling steady state temperature and  $T_0 = T(t_0)$  is the temperature of the system at  $t_0$ , i.e., at the start of the cooling time. We note  $T_c^{cool}(t_0, t)$  the temperature computed with Eq. (18).

# 4 ERPOT: The Proposed Quad-Criteria Optimization Scheduling Heuristic Method

The optimal mapping of a DAG of tasks on a multicore is a known NP-complete problem [15]. We therefore propose a heuristic algorithm, more precisely a ready list scheduling, for which we formally prove that each computed schedule satisfies the GSFR, power consumption, and temperature constraints (Section 4.2). In addition, in order to assess the performances of our heuristic, we implement an optimal version on top of an ILP solver (Section 4.6).

#### 4.1 General principles of ERPOT

We are given:

- (i) a DAG of tasks  $\mathcal{A}lg = (\mathcal{V}, \mathcal{E}),$

- (ii) a multicore architecture description  $\mathcal{A}rc = (\mathcal{C}, \mathcal{B}, \mathcal{L})$  along with the nominal failure rate per time unit  $\lambda_0$  of each hardware component,

- (iii) a function  $\mathcal{E}xe_{nom}$  of the nominal WCETs / WCCTs of all the tasks / data-dependencies of  $\mathcal{A}lg$  onto all the cores / buses of  $\mathcal{A}rc$ ,

- (iv) a set of frequencies for the cores  $\mathcal{F} = \{f_j\}_{1 \le j \le \ell}$  and a fixed frequency  $f_b$  for the buses, all taken as scaling factors,

- (v) three constraints  $\Lambda_{obj}$ ,  $P_{obj}$ , and  $T_{obj}$  respectively on the GSFR, the power consumption, and the temperature,

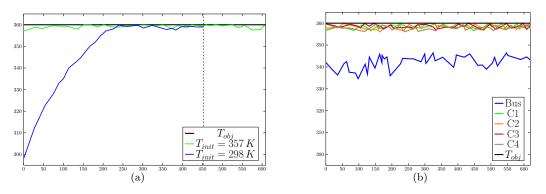

- (vi) and the initial temperature of the chip  $T_{init}$ .

The goal is to compute, if it exists, a schedule of Alg onto Arc such that the three constraints are met and the execution time is minimal<sup>2</sup>. If no solution is found, it means that the available hardware resources are not sufficient to meet the desired constraints  $\Lambda_{obj}$ ,  $P_{obj}$ , and  $T_{obj}$ . This issue is discussed in Section 4.2.

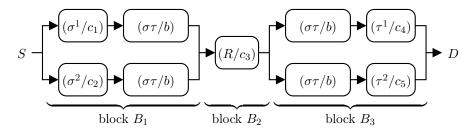

In order to keep the GSFR below  $\Lambda_{obj}$ , we use the *active replication* of tasks. We compute the reliability of a partial schedule by building the corresponding Reliability Block Diagram (RBD) [26]. An RBD is a DAG that starts with a source node S and ends with a destination node D. Between S and D, each of its nodes corresponds to one task (or data-dependency) scheduled on a core (or bus). By definition, an RBD is *operational* iff there exists at least one operational path from S to D. A path is operational iff all the blocks in this path are operational. The probability that a block is operational is its reliability, computed with Eq. (2). By construction, the probability that an RBD is operational is therefore equal to the reliability of the static schedule it represents.

Computing the reliability in this way assumes that the occurrences of the failures are *statistically independent events*. Without this hypothesis, the fact that some blocks belong to several

<sup>&</sup>lt;sup>2</sup>The execution time of the schedule is also called  $C_{max}$  or schedule length in the scheduling community.

paths from S to D makes the computation of the reliability very complex. Concerning hardware faults, this hypothesis is reasonable, but this would not be the case for software faults [34].

In general, the structure of the RBD is unspecified, which makes the reliability computation NP-complete [35]. Following [5], the solution we use to prevent this is to insert *routing* tasks (the execution time of which is 0) from each set of replicas of a predecessor task to the set of replicas of its successor task. As a result, the RBD is *serial-parallel*, which makes the reliability computation linear. For any task  $\tau$  of  $\mathcal{A}lg$ , all its replicas appear in parallel in the same block of the RBD, whose reliability is therefore computed by Eq. (3), and the RBD is composed of all these blocks in sequence (hence the serial-parallel structure). Consider for instance a simple DAG with two tasks  $X \rightarrow Y$  to be scheduled onto a six-core chip with a single bus. If X is replicated twice on cores  $c_1$  and  $c_2$  (its two replicas being denoted  $X^1$  and  $X^2$ ), and Y is replicated twice on cores  $c_4$  and  $c_5$  (its two replicas being denoted  $Y^1$  and  $Y^2$ ), then the RBD for this schedule will have the form shown in Fig. 5.

Figure 5: Reliability Block Diagram for a simple schedule with replication.

In practice, our scheduling heuristics will optimize the placement of the routing tasks so as to minimize the total execution time, for instance by mapping R to  $c_1$  or  $c_2$ .

Owing to the serial-parallel structure of the RBD, computing the reliability of a schedule (be it partial of final) is compositional. It follows that, to guarantee that the entire schedule satisfies the  $\Lambda_{obj}$  constraint, it suffices to guarantee that each block of the RBD satisfies this constraint.

In order to keep the power consumption below  $P_{obj}$ , we use two techniques: (i) on the one hand DVFS, which is available on many modern multicores such as the Intel i7-2600 quad-core or the Samsung Exynos 5422 octa-core; this allows us to lower the  $P_{dyn}$  term of Eq. (11); and (ii) on the other hand we try to keep the temperature below  $T_{obj}$ , which allows us to lower the  $P_{leak}$ term of Eq. (11). Computing the dynamic power consumption requires computing the energy consumed by the schedule (be it partial or local), and then to divide it by the schedule length. The compositionality issue raised by the GSFR computation also arises here. As demonstrated in [2], this issue can be solved by *over-estimating* the energy consumption each time that the partial schedule has a "hole" at the end, that is, each time one of the cores is idle while the other cores are busy executing their last task. Over-estimation is achieved by computing the energy consumed by such a schedule as if the "hole" was "filled" with a virtual task running at the maximal frequency.

In order to keep the temperature below  $T_{obj}$ , we insert cooling times to allow the cores to cool down [36, 8, 37] (the buses are always much less loaded than the cores, so they never need to cool down). We follow the same principle as the JUST strategy proposed in [8] for singlecore processors, with two differences: first, the target architecture is a multicore, and second, our objective is to minimize the schedule length under a maximal temperature constraint. The rationale of the JUST strategy is to insert cooling times as late as possible and only when needed, i.e., just in time. Thus, each time we want to schedule a task  $\tau$  on a core c, we evaluate the temperature of each core in the multicore at the end of this task, taking into account the planned voltage and frequency of  $\tau$  and the influence of the temperature of the neighbors of c. If it exceeds  $T_{obj}$ , then we postpone the starting time of  $\tau$  by inserting a *cooling time* in order to cool down the core c. The length of the cooling time is the *smallest length* such that the temperature at the end of  $\tau$  does not exceed  $T_{obj}$ .

Recall that a high temperature has a negative effect on the reliability (as shown in Eq. (6)) as well as on the leakage power consumption (see Eq. (11)). This makes it all the more important to limit the maximal temperature.

#### 4.2 Quad-criteria scheduling heuristic algorithm

ERPOT is a ready list scheduling algorithm implemented in MATLAB (1,300 lines of code). It works with two lists, the list  $\mathcal{R}eady^{(n)}$  of ready tasks and the list  $\mathcal{S}ched^{(n)}$  of scheduled tasks, where (n) denotes the current step of the list scheduling. At each step (n), we have  $\mathcal{R}eady^{(n)} \cap \mathcal{S}ched^{(n)} = \emptyset$ .

In a preliminary phase, we traverse the Alg graph breadth-first, from the output tasks to the input tasks, in order to compute, for each task  $\tau$ , the Longest Execution Path from  $\tau$  to the end of the graph, noted  $LEP(\tau)$ . This notion is similar to the "bottom-level" presented in [38]. Intuitively,  $LEP(\tau)$  accounts for all the "future" tasks of  $\tau$ . For each task  $\tau$ , it is computed as follows:

- If  $succ(\tau) = \emptyset$ , then we compute its LEP as  $LEP(\tau) = (\sum_{c \in \mathcal{C}} \mathcal{E}xe_{nom}(\tau, c))/|\mathcal{C}|$ . The nominal execution time of  $\tau$  is averaged over all the cores (the set  $\mathcal{C}$ ) since we do not know in advance onto which core  $\tau$  will be actually scheduled.

- If  $succ(\tau) = \{\tau'\}$ , then  $LEP(\tau) = LEP(\tau') + (\sum_{c \in \mathcal{C}} \mathcal{E}xe_{nom}(\tau, c))/|\mathcal{C}|$ . Since  $\tau$  has only one successor, its nominal execution time is added to the LEP of its only successor (again, averaged over all cores).

- If  $succ(\tau) = \{\tau_i\}_{1 \le i \le k}$  with  $k \ge 2$ , then  $LEP(\tau) = \max_{1 \le i \le k} LEP(\tau_i) + (\sum_{c \in \mathcal{C}} \mathcal{E}xe_{nom}(\tau, c))/|\mathcal{C}|$ . Since  $\tau$  has more than one successor, its averaged nominal execution time is added to the max of the LEPs of all its successors (again, averaged over all cores).

Still in the preliminary phase, we build the set  $2^{\mathcal{C}}$  of all subsets of  $\mathcal{C}$ , and for each such subset  $\{c_i\}_{1 \leq i \leq k} \in 2^{\mathcal{C}}$ , we build all the possible sets of pairs  $\{(c_i, f_j)\}_{1 \leq i \leq k, 1 \leq j \leq \ell}$ , where  $\ell$  is the number of available frequencies. We denote by  $\mathcal{Q}$  the set of all such sets of pairs (core, frequency).

In the main phase of ERPOT, we first assign to  $\mathcal{R}eady^{(0)}$  the set of input tasks of  $\mathcal{V}$ , and to  $\mathcal{S}ched^{(0)}$  the empty set. Then, at each step (n), we select the *most urgent* task to be scheduled among all the ready tasks, that is, the task  $\tau_{urg}$  for which  $LEP(\tau)$  is the largest:  $\tau_{urg} = \operatorname{argmax}_{\tau \in \mathcal{R}eady^{(n)}} LEP(\tau)$ .

The next step involves selecting the best subset of cores and their associated frequencies to execute  $\tau_{urg}$ . Each  $Q_i \in Q$  is a potential scheduling choice for  $\tau_{urg}$ , which we need to evaluate according to our three constraints and our minimization criterion. We denote by  $Q_{best}$  the best scheduling choice, by  $L^{(n)}$  the schedule length at step (n), thus before executing  $\tau$  on  $Q_{best}$ , and by  $L^{(n+1)}(\tau, Q_{best})$  the schedule length after executing  $\tau$  on  $Q_{best}$ , which we shorten into  $L^{(n+1)}$  to avoid heavy notations. Similarly, we denote by  $\Lambda^{(n)}$  the GSFR,  $E^{(n)}$  the energy, and  $T^{(n)}$  the temperature at step (n), again shortened. We further note  $\Lambda(\tau, Q_{best})$  the GSFR of the parallel block corresponding to executing  $\tau$  onto each core of  $Q_{best}$ . Recall that we have explained in Section 4.1 that the GSFR of a schedule is computed block by block, as a result of the serial-parallel structure of its RBD. With these notations,  $Q_{best}$  is given by the following

equation:

$$Q_{best} = \underset{Q_i \subseteq \mathcal{Q}}{\operatorname{argmin}} \left\{ L^{(n+1)} | \Lambda(\tau, Q_i) \leq \Lambda_{obj} \right.$$

$$\wedge \left( E^{(n+1)} - E^{(n)} \right) \leq P_{obj} \cdot \left( L^{(n+1)} - L^{(n)} \right)$$

$$\wedge T^{(n+1)} \leq T_{obj} \right\}$$

(19)

Eq. (19) might return an empty set  $Q_{best}$ . This can occur for three reasons:

- 1. Either there is no subset of cores  $Q_i$  that satisfies the GSFR criterion  $\Lambda(\tau, Q_i) \leq \Lambda_{obj}$ . In other words, the number of available cores is not sufficient to reach the required GSFR level. The heuristic fails and returns a "no solution" result. Recall that we want to find solutions in the 4D space (execution time, GSFR, power, temperature). So "no solution" only means that there will be no Pareto point at the coordinates  $(\Lambda_{obj}, P_{obj}, T_{obj})$  in the 4D space.

- 2. Either there is no subset of cores  $Q_i$  that satisfies the power consumption criterion  $(E^{(n+1)} E^{(n)}) \leq P_{obj} \cdot (L^{(n+1)} L^{(n)})$ . In other words, the available frequencies are not sufficient to reach the required power consumption level. Like in case 1 above, the heuristic fails and returns a "no solution" result.

- 3. Or there is no subset of cores  $Q_i$  that satisfies the temperature criterion  $T^{(n+1)} \leq T_{obj}$ . In this case, let  $Q'_i = \{c_j \in Q_i \mid T^{(n+1)}(c_j) > T_{obj}\}$  and let  $t_j$  be earliest time at which  $\tau$  can start on core  $c_j$ . We add to each core  $c_j \in Q'_i$  a cooling time of length  $s_j$  that starts at  $t_j$ , such that  $s_j$  is the smallest integer satisfying the inequality:

$$T_{c_i}^{cool}(t_j, s_j) + T_{c_i}^{heat}(t_j + s_j, \mathcal{E}xe(\tau, c_j, f_j)) \le T_{obj}$$

#### 4.3 Soundness of our scheduling heuristic

We prove in this section four key propositions on the produced schedules, which guarantee that the schedules generated by ERPOT satisfy the  $\Lambda_{obj}$ ,  $P_{obj}$ , and  $T_{obj}$  constraints.

**Proposition 3** Let S be a schedule of Alg onto Arc. If each task of Alg has been scheduled on the subset of cores  $Q_{best}$  defined by Eq. (19), thus satisfying the GSFR constraint  $\Lambda_{obj}$ , then the total schedule S will also meet the  $\Lambda_{obj}$  constraint.

**Proof (see [5]):** Each task  $\tau_i$  of  $\mathcal{A}lg$  is scheduled onto a subset  $Q_{best}^i$  that was selected by Eq. (19). Hence, for all  $\tau_i$  in  $\mathcal{A}lg$ , we have  $\Lambda(\tau_i, Q_{best}^i) \leq \Lambda_{obj}$ . Owing to the serial-parallel structure of the RBD corresponding to the schedule S and to the fact that the GSFR is computed compositionally from the RBD, it follows that  $\Lambda(S) \leq \Lambda_{obj}$ .

**Proposition 4** Let S be a schedule of Alg onto Arc. If each task of Alg has been scheduled on the subset of cores  $Q_{best}$  defined by Eq. (19), thus satisfying the power consumption constraint  $P_{obj}$ , then the total schedule S will also meet the  $P_{obj}$  constraint.

**Proof (see [2]):** The proof follows from Eq. (19) and from the compositionality of the power consumption (as opposed to the energy). Notice that the constraint on the power consumption in Eq. (19) is actually expressed as a constraint between the *energy increase*  $(E^{(n+1)} - E^{(n)})$  and the *schedule length increase*  $(L^{(n+1)} - L^{(n)})$ . The reason is the following: suppose that, at

step (n), the most urgent task is  $\tau_i$  with  $Q_{best}^i = \{(c_i, f_i)\}$ ; suppose also that, in the partial schedule before mapping  $\tau_i$ , the finish time  $L_{c_i}$  on core  $c_i$  is such that  $L_{c_i} + \mathcal{E}xe(\tau_i, c_i, f_i) \leq L^{(n)}$ ; in other words, scheduling  $\tau_i$  on  $c_i$  at frequency  $f_i$  does not increase the current schedule length because there is a "hole" at the end of the schedule of core  $c_i$ . Hence  $L^{(n)} = L^{(n+1)}$ . In contrast, the energy does increase when  $\tau_i$  is scheduled on  $c_i$  at frequency  $f_i$ , so  $E^{(n+1)} > E^{(n)}$ . To overcome this issue, we have proposed in [2] a solution where we "fill" each "hole" at the end of the schedule with a virtual task executing at the maximal frequency  $f_{max}$ . It follows the energy consumed by the partial schedule at each step (n) is over-estimated.

With this over-estimation, we prove the desired property by induction on (n). At step (1), the property is verified because the first task is scheduled according to Eq. (19):

$$(E^{(1)} - E^{(0)}) \le P_{obj} \cdot (L^{(1)} - L^{(0)}) \iff P^{(1)} = \frac{E^{(1)}}{L^{(1)}} \le P_{obj}$$

Then, our induction hypothesis is:

$$P^{(n)} = \frac{E^{(n)}}{L^{(n)}} \le P_{obj} \iff E^{(n)} \le P_{obj}L^{(n)}$$

$$\tag{20}$$

As a result of Eq. (19), we have:

$$(E^{(n+1)} - E^{(n)}) \le P_{obj} \cdot (L^{(n+1)} - L^{(n)})$$

$$\iff E^{(n+1)} \le E^{(n)} + P_{obj}L^{(n+1)} - P_{obj}L^{(n)}$$

Owing to the induction hypothesis (20), this implies:

$$E^{(n+1)} \leq P_{obj}L^{(n)} + P_{obj}L^{(n+1)} - P_{obj}L^{(n)}$$

$$\iff E^{(n+1)} \leq P_{obj}L^{(n+1)}$$

$$\iff P^{(n+1)} = \frac{E^{(n+1)}}{L^{(n+1)}} \leq P_{obj}$$

which concludes the proof by induction.

**Proposition 5** Let S be a schedule of Alg onto Arc with initial temperature  $T_{init}$ . If each task of Alg has been scheduled on the subset of cores  $Q_{best}$  defined by Eq. (19), thus satisfying the temperature constraint  $T_{obj}$ , and if  $T_{init} \leq T_{obj}$ , then the maximum temperature reached during one execution of S starting at  $T_{init}$  will also meet the  $T_{obj}$  constraint.

**Proof:** By hypothesis,  $T^{(0)} = T_{init} \leq T_{obj}$ . Then, the maximum temperature during S is equal to  $\max_{1 \leq i \leq n} T^{(n)}$ . Since each scheduling decision satisfies Eq. (19), it follows that  $\forall 1 \leq i \leq n, T^{(n)} \leq T_{obj}$ . As a conclusion we have  $\max_{1 \leq i \leq n} T^{(n)} \leq T_{obj}$ .

#### 4.4 Dealing with reactive systems

Propositions 3 and 4 are valid when the schedule is executed once, but also when the schedule is executed repeatedly and infinitely, as is the case for *reactive systems*. What characterizes a reactive system is that it controls some physical device (e.g., a satellite) and that it must continue to do so during the entire life of this physical device. Proposition 5 is valid when the schedule S is executed once, but not when it is repeated infinitely. The reason is due to the difference between the initial temperature  $T_{init}$  when the schedule starts and the final temperature  $T_f$ when the schedule ends (and also to the fact that the temperature curve depends on the initial temperature, as opposed to the GSFR and the power). Two cases arise:

- 1. If  $T_{init} < T_f \leq T_{obj}$ , then executing a second time the same schedule will inevitably *increase* further the temperature, so after some bounded number of executions of this schedule, the multicore temperature will violate the  $T_{obj}$  constraint. Recall that the cooling times are static and have been inserted in the schedule based on  $T_{init}$ . This is not safe.

- 2. If  $T_f < T_{init} \leq T_{obj}$ , then executing a second time the same schedule will inevitably *decrease* further the temperature, so after a large number of executions of this schedule, the multicore temperature will drop to the ambient temperature. This is *not optimal*.

Therefore, in order to be safe regarding the  $T_{obj}$  constraint and to be optimal, we should guarantee that  $T_f = T_{init}$ , which can only be achieved by being in Case 1 and then inserting on each core a cooling time until the average temperature of the multicore is equal to  $T_{init}$  (because we can cool down the multicore after executing the schedule by inserting a cooling time, while we cannot heat it). Proposition 6 generalizes Proposition 5 to the case of a schedule executed repeatedly.

**Proposition 6** Let S be a schedule of Alg onto Arc with initial temperature  $T_{init}$ , final temperature  $T_f$ , and execution time  $C_{max}$ . If each task of Alg has been scheduled on the subset of cores  $Q_{best}$  defined by Eq. (19) (thus satisfying the temperature constraint  $T_{obj}$ ), if  $T_{init} \leq T_f \leq T_{obj}$ , and if we insert a cooling time of size  $\delta$  at the end of S such that  $T^{cool}(C_{max}, \delta) = T_{init}$ , then the maximum temperature reached during an arbitrary number of executions of S starting at  $T_{init}$  will also meet the  $T_{obj}$  constraint.

**Proof:** We prove this property by induction on the number m of executions of S. Let MaxTemp(k, S) denote the maximal temperature during the k-th execution of S.

The case  $MaxTemp(1, S) \leq T_{obj}$  is proved by Proposition 5. This first execution of S is followed by a cooling time of size  $\delta$ , hence  $T(C_{max} + \delta) = T_{init}$ , which is the start time of the second execution of S.

The induction hypothesis is then:

$$\max_{1 \le k \le m} MaxTemp(k, S) \le T_{obj}$$

<sup>(21)</sup>

The *m*-th execution of *S* is followed by a cooling time of size  $\delta$ , hence  $T(m \cdot (C_{max} + \delta)) = T_{init}$ , which is the start time of the *m*+1-th execution of *S*. Applying the reasoning for MaxTemp(1, S) to the *m*+1-th execution yields  $MaxTemp(m+1, S) \leq T_{obj}$ . By the induction hypothesis, the proof is then concluded.

The size  $\delta$  of the cooling time depends on the difference between  $T_f$  and  $T_{init}$ . It is obtained by solving for  $\delta$  the equation  $T^{cool}(C_{max}, \delta) = T_{init}$ :

$$\frac{B'}{A} + \left(T_f - \frac{B'}{A}\right) \cdot e^{-A(\delta - C_{max})} = T_{init}$$

$$\iff e^{-A(\delta - C_{max})} = \frac{T_{init} - B'/A}{T_f - B'/A}$$

$$\iff \delta = C_{max} - \frac{1}{A} \cdot \log\left(\frac{T_{init} - B'/A}{T_f - B'/A}\right)$$

Since  $\delta$  must be an integer number, we round it up:

$$\delta = \left\lceil C_{max} - \frac{1}{A} \cdot \log\left(\frac{T_{init} - B'/A}{T_f - B'/A}\right) \right\rceil$$

(22)

Finally, reactive systems must comply to hard deadlines. We do not directly address this when we generate the Pareto fronts. Once the Pareto front is computed, the user can eliminate all the points that fail to meet his or her hard deadline, and then choose one solution among the remaining ones by considering the other criteria.

#### 4.5 Taking into account the temperature of the adjacent cores

In a multicore, multiple cores are located on a single chip at a very short distance from each other, so the temperature of each core impacts the other cores. This is taken into account by Eqs. (14) and (15).

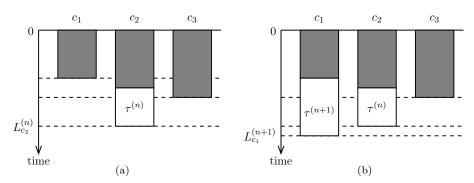

Now, one situation that can arise during our list scheduling algorithm is when the current task  $\tau^{(n)}$  is scheduled at step (n) on some core c such that c's neighbors are (partly) idle during the duration of  $\tau^{(n)}$ . This is illustrated in Fig. 6(a) where task  $\tau^{(n)}$  is scheduled on  $c_2$ . The risk is that the temperature computed at the end of  $\tau^{(n)}$  is under-estimated because the tasks that will be scheduled on the neighbors of  $c_2$  (i.e.,  $c_1$  and  $c_3$  in Fig. 6(a)) in a *future* step of the heuristic will not be accounted for. For instance, Fig. 6(b) illustrates the case of a task  $\tau^{(n+1)}$  that is scheduled on  $c_1$  at step (n+1), causing an increase of the temperature on  $c_2$  that was not taken into account when we scheduled  $\tau^{(n)}$  on  $c_2$ .

Figure 6: (a) Partial schedule at step (n) and (b) at step (n+1). A white box represents some new task  $\tau$  such that its vertical length is proportional to  $\mathcal{E}xe(\tau, c, f)$ . A gray box represents an arbitrary sequence of tasks scheduled during the previous steps.

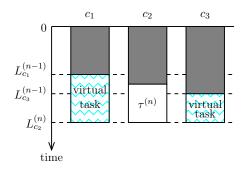

Figure 7: Temperature over-estimation by a adding virtual task to each of the neighbor of  $c_2$  because their respective finish time at step (n-1) was strictly less than  $L_{c_2}^{(n)}$ .

We solve this issue by adding *virtual tasks* on all the neighbors to *over-estimate* the temperature: each time a task  $\tau^{(n)}$  is scheduled on some core c, for each neighbor c' of c such that the current finish time on c' is strictly less than the finish time on c (denoted  $L_c^{(n)}$  — note that it can be less than  $L^{(n)}$ ), we add on c' a virtual task that finishes exactly at  $L_c^{(n)}$  and that runs at frequency  $f_{max}$ . These virtual tasks modify the value of  $T_{c'}$  in Eq. (15), therefore guaranteeing that, whatever the future scheduling decisions, the runtime temperature on core c at time  $L^{(n)}$ will actually be below the temperature computed during the step (n) of our heuristic. This is illustrated in Fig 7. Of course, when actual tasks are scheduled on these cores c' during future steps, the virtual tasks are removed and the temperature is recomputed accordingly.

Table 1 summarizes the main computations used in ERPOT.

$$\begin{array}{|c|c|c|c|} \hline & \text{Execution time } \mathcal{E}xe(\tau,c,f) = \lceil \mathcal{E}xe_{nom}(\tau,c)/f \rceil \\ \hline & \text{Failure rate } \lambda_{sys} = \lambda_0 \cdot 10^{\frac{b(1-f)}{1-f_{min}}} \cdot e^{\frac{-E_a}{K}\left(\frac{1}{T(t)} - \frac{1}{T_0}\right)} \\ \hline & \text{Reliability } R(\tau,\mathcal{K},t) = 1 - \left(\prod_{i=1}^k \left(1 - e^{-\lambda_{sys}(c_i)\cdot\mathcal{E}xe(\tau,c_i,f_{c_i})}\right)\right) \\ & (\text{computed with Reliability Block Diagrams}) \\ \hline & \text{GSFR } \Lambda(S) = -\log(R(S))/U(S) \\ \hline & \text{Utilization } U(S) = \sum_{(\tau,c,f)\in S} \mathcal{E}xe(\tau,c,f) \\ \hline & \text{Power } P_{sys}(t) = \underbrace{\alpha \cdot T(t) + \beta_h}_{leakage} + \underbrace{\gamma \cdot C_{ef} \cdot V^2 \cdot f}_{dynamic} \\ \hline & \text{Temperature differential equation} \\ \hline & C \cdot \left(\frac{dT_c(t)}{dt}\right) + G\left(T_c(t) - T_{amb}\right) + 2D\_heat = P(t) \\ \hline & \text{Heat transfer from neighbor cores} \\ & 2D\_heat = \sum_{c' \in nbr(c)} \kappa(c,c') \cdot \left(T_c(t) - T_{c'}(t)\right) \\ \hline & \text{Solution } T_c(t) = T_{\infty}^{heat} + \left(T_0 - T_{\infty}^{heat}\right) \cdot e^{-A(t-t_0)} \\ \hline & \text{Steady state temperature } T_{\infty}^{heat} = B/A \end{array}$$

Table 1: Summary of all the computations.

#### 4.6 Integer Linear Program

We now propose an ILP formulation of our scheduling problem, with the purpose of comparison with the heuristic algorithm presented in Section 4.2. The models and the assumptions used in Section 4.2 are also used here for the ILP program. The decision variables are the following:

$\begin{array}{ll} S_{ik} & \in \mathbb{N} : \text{start time of replica } k \text{ of task } i \\ F_{ik} & \in \mathbb{N} : \text{finish time of replica } k \text{ of task } i \\ Sb_{ik} \in \mathbb{N} : \text{start time of replica } k \text{ of data dependency } i \\ Fb_{ik} \in \mathbb{N} : \text{finish time of replica } k \text{ of data dependency } i \\ W & \in \mathbb{N} : \text{total execution time of the application} \\ x_{ikc} = \begin{cases} 1 & \text{if replica } k \text{ of task } i \text{ is assigned to core } c \\ 0 & \text{otherwise} \end{cases} \end{array}$

$x_{ikcfs} = \begin{cases} 1 & \text{if replica } k \text{ of task } i \text{ is assigned to core } c \text{ at frequency } f \text{ and after a cooling time } \\ & \text{of } s \text{ time units} \\ 0 & \text{otherwise} \\ 1 & \text{if replica } k \text{ of task } i \text{ starts before replica } k' \\ & \text{of task } j \\ 0 & \text{otherwise} \\ Y_{iK} &= \begin{cases} 1 & \text{if task } i \text{ is replicated } K \text{ times} \\ 0 & \text{otherwise} \\ 1 & \text{if replica } k \text{ of task } i \text{ has an outgoing } \\ data \text{ dependency} \\ 0 & \text{otherwise} \end{cases}$

The main objective of our optimization problem is minimizing the total execution time. Then, two kinds of ILP constraints must be formulated. The first kind are the constraints that guarantee the schedulability:

1. Every replica k of task i should be assigned to exactly one core c:

$$\forall i, \forall k, \sum_{c} x_{ikcfs} = 1 \tag{23}$$

2. Every replica k of task i on core c should be assigned to exactly one level of frequency and be preceded by exactly one cooling time (possibly of size 0):

$$\forall i, \forall k, \forall c, \sum_{f,s} x_{ikcfs} = x_{ikc} \tag{24}$$

3. The finish time of every replica k of task i should be less or equal than the total execution time:

$$\forall i, \forall k, F_{ik} \le W \tag{25}$$

4. The finish time of every replica k of task i is computed based on its execution time and its start time:

$$\forall i, \forall k, F_{ik} = S_{ik} + \sum_{c,f,s} x_{ikcfs} \cdot exe_c(i,c,f,s) + Fb_{ik}$$

$$\tag{26}$$

where,  $exe_c(i, c, f, s)$  is the execution time of task *i* on core *c* at the *f*-th frequency level and after a cooling time of size *s*:  $exe_c(i, c, f, s) = \mathcal{E}xe(i, c, f) + s$ .

5. Tasks can not overlap and must obey their precedence order (M is a constant greater than the largest existing number in the ILP program — "big M method" [39]):

$$\forall i \neq j, \forall k, \forall k', \sigma_{ijkk'} + \sigma_{jik'k} \le 1$$

(27)

$$\forall i, \forall j, \forall k, \forall k', S_{ik} \le S_{jk'} + (1 - \sigma_{ijkk'}) \cdot M$$

(28)

$$\forall i, \forall j, \forall k, \forall k', \forall c, F_{ik} \le (2 - x_{ikc} - x_{jk'c}) \cdot M$$

$$+S_{jk'} + (1 - \sigma_{ijkk'}) \cdot M \tag{29}$$

$$\forall i \in pred(j), \forall k, \forall k', F_{ik} \le S_{jk'} \tag{30}$$

$\forall i \in pred(j), \forall k, \forall k', \sigma_{ijkk'} = 1 \tag{31}$

Inria